(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7240008号

(P7240008)

(45)発行日 令和5年3月15日(2023.3.15)

(24)登録日 令和5年3月7日(2023.3.7)

(51)国際特許分類

H 01 L 21/52 (2006.01)

H 01 L 23/36 (2006.01)

F I

H 01 L 21/52

H 01 L 23/36B

D

請求項の数 20 (全23頁)

(21)出願番号 特願2020-519728(P2020-519728)

(86)(22)出願日 平成30年10月4日(2018.10.4)

(65)公表番号 特表2020-537343(P2020-537343

A)

(43)公表日 令和2年12月17日(2020.12.17)

(86)国際出願番号 PCT/US2018/054415

(87)国際公開番号 WO2019/071006

(87)国際公開日 平成31年4月11日(2019.4.11)

審査請求日 令和3年9月28日(2021.9.28)

(31)優先権主張番号 15/984,343

(32)優先日 平成30年5月19日(2018.5.19)

(33)優先権主張国・地域又は機関

米国(US)

(31)優先権主張番号 62/568,463

(32)優先日 平成29年10月5日(2017.10.5)

最終頁に続く

(73)特許権者 507107291

テキサス インスツルメンツ インコーポ

レイテッド

アメリカ合衆国 テキサス州 75265

- 5474 ダラス メイル ステイション

3999 ピーオーボックス 655474

(74)代理人 230129078

弁護士 佐藤 仁

クリストファー ダニエル マナック

アメリカ合衆国 75022 テキサス州

フラワー マウンド, サン メドウ ドラ

イブ 5309

(72)発明者 ナジラ ダドバンド

アメリカ合衆国 75081 テキサス州

リチャードソン, イー バッキンガム

最終頁に続く

(54)【発明の名称】マイクロ電子デバイスのための保護層を備えたダイ取り付け表面銅層

## (57)【特許請求の範囲】

## 【請求項1】

マイクロ電子デバイスであって、

構成要素表面と、前記構成要素表面の反対側に位置するダイ取り付け表面とを有する基板と、

前記構成要素表面に近接して位置する構成要素と、

前記ダイ取り付け表面上の銅含有層であって、銅含有層の占有領域が前記ダイ取り付け表面の横方向外周から窪んでいる、前記銅含有層と、

前記銅含有層上のダイ取り付け材料と、

を含み、

前記銅含有層が前記ダイ取り付け材料によってパッケージ部材に取り付けられる、マイクロ電子デバイス。

## 【請求項2】

請求項1に記載のマイクロ電子デバイスであって、

前記銅含有層が5ミクロン～10ミクロンの厚みである、マイクロ電子デバイス。

## 【請求項3】

請求項1に記載のマイクロ電子デバイスであって、

前記銅含有層と前記ダイ取り付け表面との間に中間層を更に含む、マイクロ電子デバイス。

## 【請求項4】

請求項 3 に記載のマイクロ電子デバイスであって、

前記中間層がチタンを含む、マイクロ電子デバイス。

【請求項 5】

請求項 1 に記載のマイクロ電子デバイスであって、

前記銅含有層と前記ダイ取り付け材料との間の保護金属層を更に含み、

前記保護金属層が、錫と銀とニッケルとからなる群から選択される少なくとも 1 つの金属を含む、マイクロ電子デバイス。

【請求項 6】

請求項 1 に記載のマイクロ電子デバイスであって、

前記ダイ取り付け材料がはんだを含む、マイクロ電子デバイス。

10

【請求項 7】

請求項 1 に記載のマイクロ電子デバイスであって、

前記基板が 15 ミクロン～300 ミクロンの厚みである、マイクロ電子デバイス。

【請求項 8】

マイクロ電子デバイスを形成する方法であって、

構成要素面と、前記構成要素面の反対側に位置するダイ取り付け面とを有する基板ウェハであって、前記基板が、前記構成要素面に近接する前記マイクロ電子デバイスの構成要素を含む、前記基板ウェハを提供することと、

前記ダイ取り付け面において前記基板ウェハから材料を除去することと、

前記ダイ取り付け面上に銅含有層を形成することであって、前記銅含有層の占有領域が前記マイクロ電子デバイスのためのエリアの横方向外周から窪まされている、前記銅含有層を形成することと、

20

めっきプロセスによって前記銅含有層上に保護金属層を形成することと、

を含む、方法。

【請求項 9】

請求項 8 に記載の方法であって、

前記保護金属層が、錫と銀とニッケルとからなる群から選択される少なくとも 1 つの金属を含む、方法。

【請求項 10】

請求項 8 に記載の方法であって、

30

前記基板ウェハから材料を除去することの前の前記基板ウェハの厚みが 300 ミクロンより大きく、前記基板ウェハから材料を除去することの後の前記基板ウェハの厚みが 300 ミクロン未満である、方法。

【請求項 11】

請求項 8 に記載の方法であって、

前記銅含有層を形成することが、

前記ダイ取り付け面にシード層を形成することと、

前記シード層上にめっきマスクを形成することであって、前記シード層が前記銅含有層のためのエリアを露出させる、前記めっきマスクを形成することと、

めっきプロセスによって前記めっきマスクにより露出された箇所の前記シード層上の銅をめっきすることと、

40

前記めっきマスクを除去することと、

を含む、方法。

【請求項 12】

請求項 11 に記載の方法であって、

前記銅含有層が 5 ミクロン～10 ミクロンの厚みである、方法。

【請求項 13】

請求項 11 に記載の方法であって、

前記銅含有層を形成することと同時に、前記構成要素面上に銅含有ピラーの少なくとも一部を形成することを更に含む、方法。

50

**【請求項 14】**

請求項 8 に記載の方法であって、

前記銅含有層を形成することが、前記ダイ取り付け面上に銅含有材料を堆積させるアディティブ法を含む、方法。

**【請求項 15】**

請求項 8 に記載の方法であって、

前記基板ウェハから材料を除去することの後であり前記銅含有層を形成することの前に、前記ダイ取り付け面上に中間層を形成することを更に含み、

前記銅含有層が前記中間層上に形成される、方法。

**【請求項 16】**

10

マイクロ電子デバイスを形成する方法であって、

構成要素表面と、前記構成要素表面と反対側に位置するダイ取り付け表面とを有する、300ミクロン未満の厚みの基板を提供することであって、前記基板が、前記構成要素表面に近接する構成要素を含み、前記基板が、前記ダイ取り付け表面上に銅含有層を有し、前記銅含有層の占有領域が、前記ダイ取り付け表面の横方向外周から窪んでおり、前記基板が、前記銅含有層上に保護金属層を有し、前記銅含有層が、前記ダイ取り付け表面と前記保護金属層との間に有る、前記基板を提供することと、

ダイ取り付け材料でパッケージ部材に前記基板を取り付けることと、

を含み、

前記銅含有層が前記ダイ取り付け材料によって前記パッケージ部材に取り付けられる、方法。

20

**【請求項 17】**

請求項 16 に記載の方法であって、

前記基板をパッケージ部材に取り付けることの前に、前記保護金属層を取り除くことを更に含む、方法。

**【請求項 18】**

請求項 16 に記載の方法であって、

前記銅含有層が 5 ミクロン～10 ミクロンの厚みである、方法。

**【請求項 19】**

請求項 16 に記載の方法であって、

30

前記ダイ取り付け材料がはんだを含む、方法。

**【請求項 20】**

請求項 19 に記載の方法であって、

前記基板をパッケージ部材に取り付けることが、はんだリフロープロセスを含む、方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本願は、概してマイクロ電子デバイスに関し、より詳細にはマイクロ電子デバイスにおける金属層に関する。

**【背景技術】**

40

**【0002】**

マイクロ電子デバイスの中には、低抵抗の電気的又は熱的接続を提供するために、それらの基板のダイ取り付け表面上に金属層を有するものがある。銅は、電気的及び熱的伝導率が高いため、金属層にとって望ましい要素である。しかし、基板のダイ取り付け表面上の銅は、汚染、酸化、及び腐食の問題を提起する。ダイ取り付け表面上の銅層の統合は、マイクロ電子デバイスのための製造フローに統合するのが困難であった。

**【発明の概要】****【0003】**

マイクロ電子デバイスを形成する或る方法が、基板のダイ取り付け表面からマイクロ電子デバイスの基板を薄化することと、基板のダイ取り付け表面上に銅含有層を形成するこ

50

とと、銅含有層上に保護金属層を形成することと、その後、銅含有層をパッケージダイ取り付けエリアにおけるパッケージ部材に取り付けることとを含む。保護金属層は、銅含有層をパッケージ部材に取り付ける前に、任意選択で取り除かれ得る。

【図面の簡単な説明】

【0004】

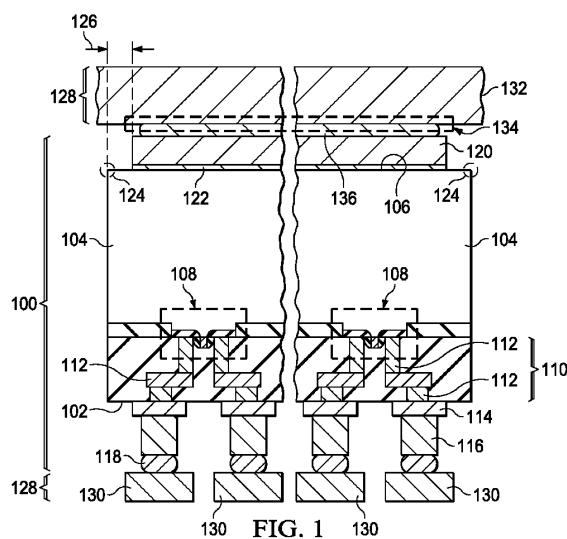

【図1】パッケージにアセンブルされた例示のマイクロ電子デバイスの断面である。

【0005】

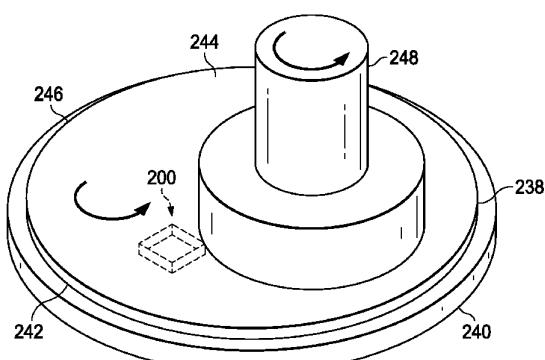

【図2A】形成の例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

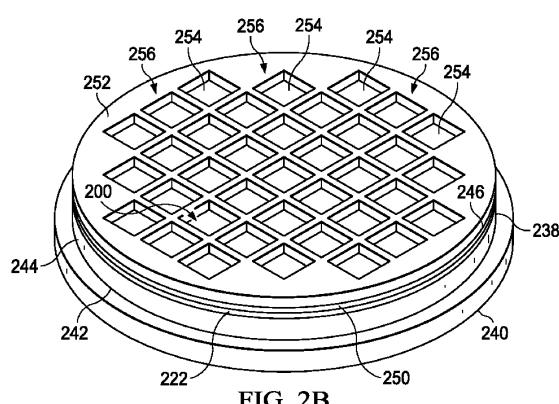

【図2B】形成の例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

10

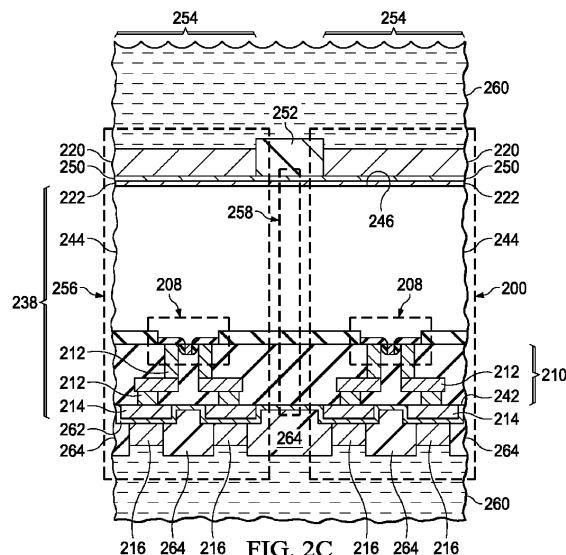

【図2C】形成の例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

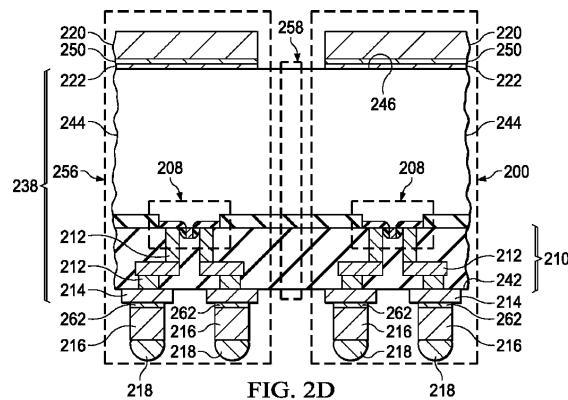

【図2D】形成の例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

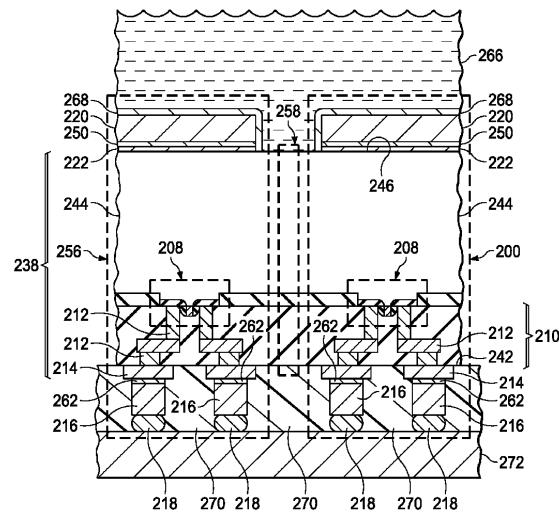

【図2E】形成の例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

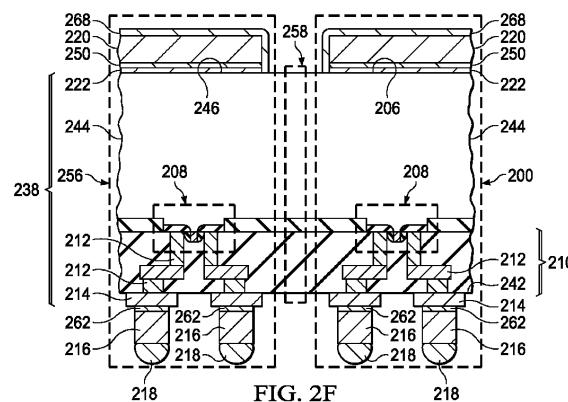

【図2F】形成の例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

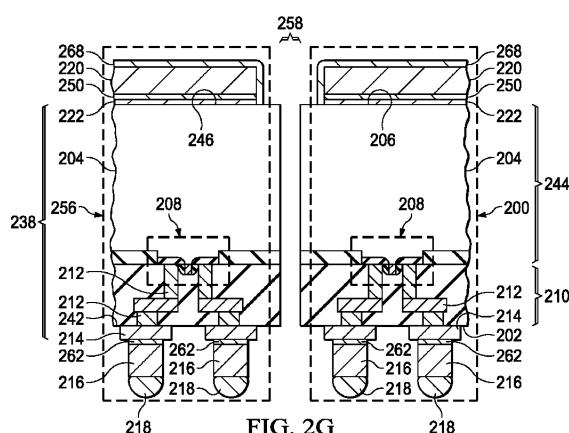

【図2G】形成の例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

【図2H】形成の例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

【図2I】形成の例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

【0006】

【図3A】形成の別の例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

【図3B】形成の別の例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

20

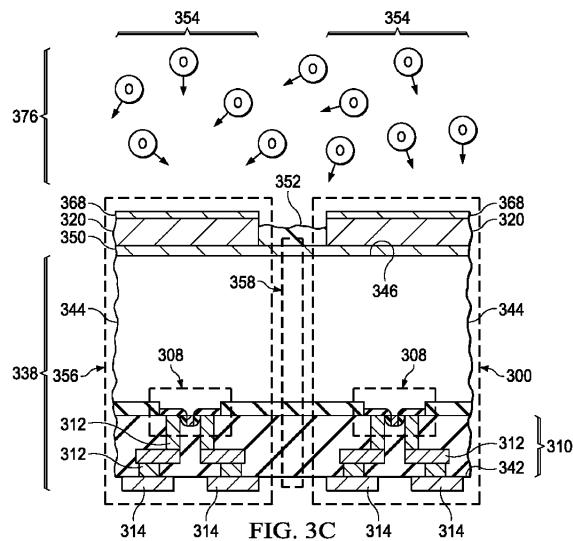

【図3C】形成の別の例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

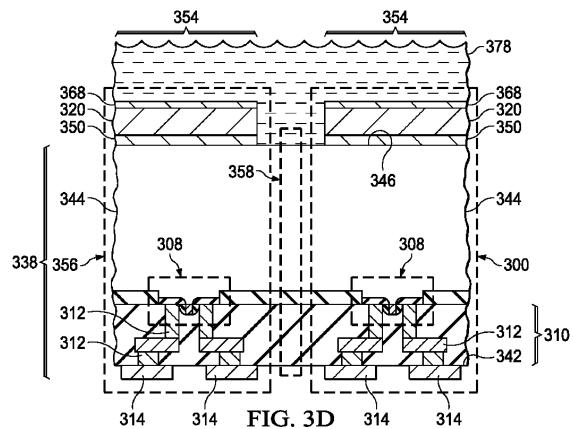

【図3D】形成の別の例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

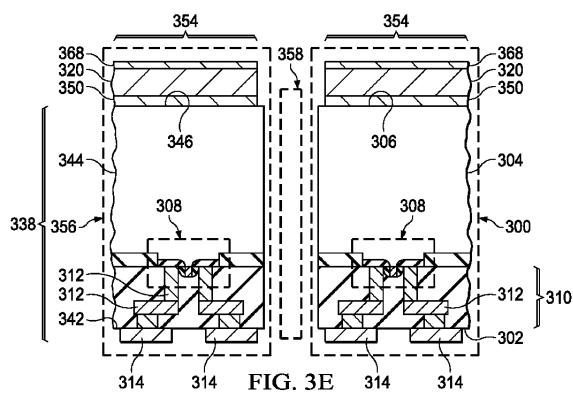

【図3E】形成の別の例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

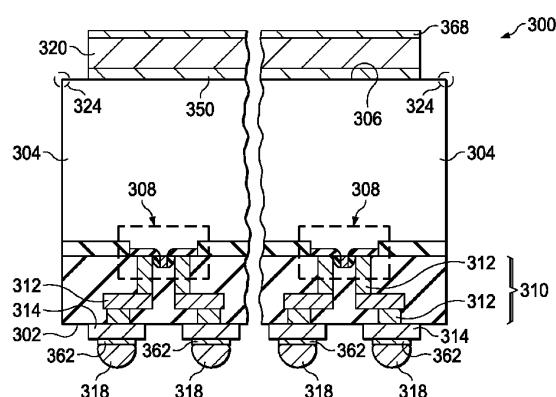

【図3F】形成の別の例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

【図3G】形成の別の例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

30

【図3H】形成の別の例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

【0007】

【図4A】形成の更なる例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

【図4B】形成の更なる例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

【図4C】形成の更なる例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

40

【図4D】形成の更なる例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

【図4E】形成の更なる例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

【図4F】形成の更なる例示的な方法の或る段階で描かれたマイクロ電子デバイスの図である。

【発明を実施するための形態】

【0008】

図面は一定の縮尺で描いてはいない。幾つかの行為又は事象が、異なる順で及び／又は他の行為又は事象と同時に起こり得るので、本記載は行為又は事象の例示される順によつ

50

て限定されない。また、幾つかの例示される行為又は事象は、本記載に従った手法を実施するために任意選択である。

【 0 0 0 9 】

マイクロ電子デバイスが、構成要素表面に近接して位置する構成要素を備える構成要素表面と、構成要素表面まで延在する入力／出力（I／O）パッドとを有する。マイクロ電子デバイスは更に、構成要素表面とは反対側のダイ取り付け表面を備える基板を有する。マイクロ電子デバイスは、マイクロ電子デバイスがシリコンウェハなどの基板ウェハに含まれる一方で、ダイ取り付け表面から基板を薄化することによって形成され得る。基板は、構成要素からダイ取り付け表面への熱的又は電気的抵抗を低減するために薄化され得る。

【 0 0 1 0 】

基板が薄化された後、マイクロ電子デバイスが基板ウェハに含まれる一方で、ダイ取り付け表面上に銅含有層が形成される。中間層が銅含有層を基板のダイ取り付け表面から分離するように、銅含有層を形成する前にダイ取り付け表面上に中間層が形成され得る。一態様において、中間層は、ダイ取り付け表面上に直接に銅含有層を有することによって提供され得るよりも、銅含有層とダイ取り付け表面との間のより良好な接着を提供し得る。別の態様において、中間層は、銅含有層から基板内に拡散する銅に対する障壁を提供し得る。銅は、半導体材料などの幾つかの基板材料に拡散するとき、望ましくない効果を有する。銅含有層は、ダイ取り付け表面の横方向外周から窪むように形成され得る。銅含有層を窪ませることは、有利にも、マイクロ電子デバイスの後続の個片化の間の基板の銅汚染を低減し得る。

【 0 0 1 1 】

銅含有層上に保護金属層が形成され、一方、基板ウェハにはマイクロ電子デバイスが含まれる。保護金属層は、例えば、錫、銀、ニッケル、コバルト、タングステン、モリブデン、セリウム、ランタン、又はそれらの任意の組み合わせを含み得る。保護金属層は、浸漬めっきプロセスによって、又は電気めっきプロセスによって形成され得る。保護金属層は、有利にも、後の製造プロセスの間、腐食又は酸化から銅含有層を保護し得る。

【 0 0 1 2 】

その後、マイクロ電子デバイスは、マイクロ電子デバイスを基板ウェハの残りの部分から分離するように個片化される。マイクロ電子デバイスがリードフレームパッケージなどのパッケージにアセンブルされる前に、個片化の前及び後に若干の時間が経過することがある。保護金属層は、有利にも、銅含有層を腐食又は酸化から保護し得る。

【 0 0 1 3 】

アッセンブリの前に、保護金属層はウェットエッチングプロセスによって取り除かれ得、銅含有層をそのまま残し、後続のダイ取り付けプロセスのためのクリーンな表面を提供し得る。マイクロ電子デバイスは、ダイ取り付けプロセスによってパッケージにアセンブルされ、銅含有層は、はんだプロセス、接着プロセス、又は別のプロセスによって、パッケージダイ取り付けエリアに取り付けられる。銅含有層のクリーンな表面を提供することは、有利にも、パッケージダイ取り付けエリアとマイクロ電子デバイスの構成要素との間に一層低い熱的又は電気的抵抗を提供し得る。

【 0 0 1 4 】

或いは、ダイ取り付けプロセスの間、保護金属層の一部又は全部が銅含有層上の適所に残され得る。保護金属層は、ダイ取り付けプロセスの前に、例えばウェットエッチングプロセスによって、洗浄され得る。保護金属層は、はんだ又は接着性ダイ取り付け材料に適した表面を提供し得る。銅含有層上に少なくとも保護金属層の一部を残すと、マイクロ電子デバイスのためのプロセスコストと複雑度が低減され得る。

【 0 0 1 5 】

基板を薄化することは、銅含有層の厚みに制約を課す。銅含有層は、パッケージダイ取り付けエリアと基板との間に低い熱的又は電気的抵抗を提供するために充分な厚みであるべきである。銅含有層は、銅含有層内の応力に起因して基板を撓ませたり歪めたりするほど厚くすべきではない。これらの制約を満たすため、銅含有層は、例えば5ミクロン～1

10

20

30

40

50

0ミクロンの厚みとし得る。保護金属層は、銅含有層における銅の腐食又は酸化からの消費を防止し、その結果、マイクロ電子デバイスが、銅含有層の厚みの有意な低減、すなわち1ミクロン未満の低減なしに、パッケージダイ取り付けエリアに取り付けられ得る。

#### 【0016】

本記載において、或る要素が別の要素「上」にあると称する場合、それは他の要素の直接上にあることもあれば、介在要素が存在することもある。また、或る要素が別の要素の「上に直接に」あると称される場合、他に意図的に配置された介在要素はない。

#### 【0017】

図1は、パッケージにアセンブルされた例示のマイクロ電子デバイスの断面である。マイクロ電子デバイス100は、構成要素表面102と、構成要素表面102とは反対に位置するダイ取り付け表面106を備える基板104とを有する。基板104は、シリコン、ガリウムヒ化物、ガリウム窒化物、又は他の半導体材料を含み得る。マイクロ電子デバイス100は、構成要素表面102に近接して位置する金属酸化物半導体(MOS)トランジスタ108として図1に描かれる構成要素108を含む。基板104は、構成要素108に対する機械的支持を提供するため、少なくとも15ミクロンの厚みとし得る。基板104は、構成要素108からダイ取り付け表面106への電気又は熱抵抗を減少させるため、厚みが300ミクロン未満とし得る。本例では、マイクロ電子デバイス100は、構成要素108から構成要素表面102まで延在する相互接続領域110を含む。相互接続領域110内のコンタクト、相互接続、及びビアなどの相互接続部材112が、構成要素108を構成要素表面102に位置するI/Oパッド114に電気的に接続する。本例では、マイクロ電子デバイス100は、I/Oパッド114に結合された銅含有ピラー116、及び、銅含有ピラー116に結合されたはんだボール118を含む。

10

20

30

#### 【0018】

マイクロ電子デバイス100は、ダイ取り付け表面106上に銅含有層120を含む。本例のマイクロ電子デバイス100は、銅含有層120とダイ取り付け表面106との間に中間層122を含む。マイクロ電子デバイス100の別の顕在化において、銅含有層120は、ダイ取り付け表面106上に直接に配置され得る。銅含有層120は、本質的に銅のみを含み得るか、又は、銅含有層120を形成するために用いられるめっきプロセスの間に混合され得る、少量の有機材料及び酸素などの他の材料を含み得る。銅含有層120は、少量の別の金属も含み得る。銅含有層120の厚みは、例えば、5ミクロン～10ミクロンとし得る。中間層122は、ダイ取り付け表面106上に直接に銅含有層120を有することによって達成されるよりも良好な、銅含有層120とダイ取り付け表面106との間の接着を提供し得る。中間層122は、銅含有層120から基板104への銅の拡散に対する障壁を提供し得る。中間層122は、例えば、チタン、チタンタングステン、ニッケル、又はクロムを含み得、50ナノメートル～500ナノメートルの厚みとし得る。

30

#### 【0019】

銅含有層120は、ダイ取り付け表面106の横方向外周124から窪ませることができる。銅含有層120を横方向外周124から窪ませることにより、マイクロ電子デバイスを基板ウェハから分離するソーイング又はレーザースクライビングなどの個片化プロセスの間、基板104内の銅汚染が有利に低減され得る。銅含有層120は、例えば、個片化プロセスにおける位置的及び寸法的変動のための公差を提供するために、5ミクロン～50ミクロンの横方向距離126窪ませることができる。存在する場合、中間層122も横方向外周124から窪ませることができる。

40

#### 【0020】

マイクロ電子デバイス100はパッケージ128に取り付けられ、これは、リード130を有するリードフレーム128、及び、図1にクリップ132として示されるパッケージ部材132として顕在化され得る。はんだボール118はリード130に直接取り付けられてもよく、銅含有層120は、はんだ層136として顕在化され得るダイ取り付け材料136によって、パッケージダイ取り付けエリア134におけるクリップ132に取り

50

付けられ得る。銅含有層 120 は、はんだ層 136 に対する強く均一なはんだ接続を提供し得、そのため、クリップ 132 と基板 104 との間に低い熱的又は電気的抵抗を提供し得る。銅含有層 120 は、例えば、薄化された基板 104 内の応力を制限することとはんだ層 136 に対する強く均一なはんだ接続をつくることとの間の所望の均衡を提供するために、5 ミクロンから 10 ミクロンの厚みとし得る。銅含有層 120 は、酸化及び腐食から保護するために銅含有層 120 につけられた保護金属層を示し得る、ダイ取り付け表面 106 にわたる 1 パーセント未満の不均一性を有し得る。酸化と腐食をなくすと、下にある銅層の厚み変動が 1 パーセントを超ることが頻繁に起こる。

#### 【0021】

図 2A ~ 図 2I は、形成の例示的な方法の種々の段階において描かれたマイクロ電子デバイスの図である。図 2A を参照すると、マイクロ電子デバイス 200 が、基板ウェハ 238 に含まれている。基板ウェハ 238 は、シリコンウェハ、ガリウムヒ化物ウェハ、又はガリウム窒化物ウェハなどの半導体ウェハとして実装され得る。基板ウェハ 238 は、図 2A に描かれているように、任意選択で、キャリアプレート 240 上に取り付けられ得る。代替として、基板ウェハ 238 は、任意選択で、テープ上に取り付けられてもよく、又は保護コーティングを有していてもよい。基板ウェハ 238 は、キャリアプレート 240 に面する構成要素面 242 と、構成要素面 242 とは反対側に位置するダイ取り付け面 246 を備える基板 244 とを有する。基板 244 は、シリコン、ガリウムヒ化物、又はガリウム窒化物などの半導体材料を含む。

10

#### 【0022】

バックグラインドオペレーションにおいて、バックグラインドツール 248 を用いて、ダイ取り付け面 246 における基板 244 から材料が取り除かれる。バックグラインドオペレーションによって基板 244 の厚みが減少されて、基板 244 の電気的又は熱的抵抗を減少させる。バックグラインドオペレーションを行う前の基板 244 の厚みは、図 2C に示される構成要素 208 の製造の間の機械的安定性を提供するために、600 ミクロンより大きくし得る。基板 244 の厚みは、基板 244 の電気的又は熱的抵抗と、後の製造オペレーションにおける基板 244 の耐久性との間の所望の均衡を提供し得る、15 ミクロン ~ 300 ミクロンまで低減され得る。ダイ取り付け面 246 における基板 244 からの材料の除去は、基板ウェハ 238 に機械的応力を導入し得、基板 244 を損傷させる恐れがある。基板 244 は、構成要素面 242 におけるワイヤボンドパッド又はバンプ結合構造によってキャリアプレート 240 から分離され得る。ワイヤボンドパッド又はバンプ結合構造は、構成要素面 242 にわたって不均一に分布され得、基板ウェハ 238 のための不充分なサポートを提供する。そのような場合、ダミーワイヤボンドパッド又はバンプ結合構造と称されることもある付加的なワイヤボンドパッド又はバンプ結合構造が、基板ウェハ 238 上に形成されて、より均一な支持を提供し得、基板 244 から材料を安全に取り除くことができる。付加的なワイヤボンドパッド又はバンプ結合構造なしに達成され得るよりも小さい、基板 244 の厚みを達成することを可能にし得る。

20

#### 【0023】

図 2B を参照すると、任意の中間層 222 が、基板 244 のダイ取り付け面 246 上に形成され得る。中間層 222 は、図 1 の中間層 122 に関して開示されるように、接着又は拡散障壁特性を有し得る。中間層 222 は、例えば、スパッタプロセスによって形成され得る。シード層 250 が、存在する場合には中間層 222 上に形成され、中間層 222 が存在しない場合には、基板 244 のダイ取り付け面 246 上に形成される。シード層 250 は、銅の後続のめっきに適した金属を含む。例えば、シード層 250 は銅層を含み得る。シード層 250 は、過度にデバイアスすることなく銅の後続のめっきの間、電流を分配するために充分な厚みであり、めっきされた銅の顕著な低減なしに後続の除去を可能にするために充分薄い。シード層 250 は、例えば、スパッタプロセスによって形成され得る。

30

#### 【0024】

40

50

シード層 250 の上にめっきマスク 252 が形成される。めっきマスク 252 は開口 254 を有し、開口 254 は、マイクロ電子デバイス 200、及び基板ウェハ 238 に含まれる類似のマイクロ電子デバイス 256 のためのエリアにおいてシード層 250 を露出させる。めっきマスク 252 は、マイクロ電子デバイス 200 のためのエリアと類似のマイクロ電子デバイス 256 との間の個片化領域のためのエリアを覆う。めっきマスク 252 は、フォトレジストを含み得、フォトリソグラフィプロセスによって形成され得る。或いは、めっきマスク 252 は、感光性のないポリマー材料を含んでもよく、インクジェットプロセスなどのアディティブ法によって形成され得る。基板ウェハ 238 が薄化された後に基板ウェハ 238 上にめっきマスクを形成することは、基板 244 の損傷を避けるために、特殊な取扱い及びサポートを必要とする場合がある。例えば、基板ウェハ 238 は、図 2B に描かれているように、キャリアプレート 240 上に残されていてもよい。基板ウェハ 238 は、スピンドルオペレーションによって基板ウェハ 238 をフォトレジストで被覆することに関与するフォトリソグラフィプロセスであり得る、めっきマスク 252 を形成するプロセスに適した別のキャリアプレート上に取り付けられてもよい。

#### 【 0025 】

図 2C を参照すると、基板ウェハ 238 は、マイクロ電子デバイス 200 と類似のマイクロ電子デバイス 256 の隣り合うインスタンスとの間の境界において断面で示されている。マイクロ電子デバイス 200 及び類似のマイクロ電子デバイス 256 は、構成要素面 242 に近接して位置する構成要素 208 と、構成要素 208 から構成要素面 242 まで延在する相互接続領域 210 とを含む。マイクロ電子デバイス 200 及び類似のマイクロ電子デバイス 256 は、構成要素 208 を構成要素面 242 に配置された I/O パッド 214 に電気的に接続するために、相互接続領域 210 において相互接続部材 212 を含み得る。

#### 【 0026 】

めっきマスク 252 は、マイクロ電子デバイス 200 と類似のマイクロ電子デバイス 256 との間に位置する個片化領域 258 の上のシード層 250 を覆う。めっきマスク 252 は、後に形成される銅含有層を個片化領域 258 から窪ませるように、マイクロ電子デバイス 200 及び類似のマイクロ電子デバイス 256 のためのエリア内へ延在する。めっきマスク 252 内の開口 254 は、マイクロ電子デバイス 200 及び類似のマイクロ電子デバイス 256 のためのエリアにおいてシード層 250 を露出させる。

#### 【 0027 】

シード層 250 は、めっきマスク 252 内の開口 254 において銅めっき槽 260 に晒される。電気めっきプロセスなどのめっきプロセス、又は無電解めっきプロセスによってめっきマスク 252 により露出された箇所の、マイクロ電子デバイス 200 上及び類似のマイクロ電子デバイス 256 上に銅含有層 220 が形成され、これにより、シード層 250 上に銅がめっきされる。銅めっき槽 260 は、銅を含み、銅含有層 220 の均一性を改善するために、レベラー、光沢剤、又は抑制剤などの添加剤を含み得る。銅含有層 220 の厚みは、基板 244 を反らせたり歪めたりすることなく、基板 244 への低い熱的又は電気的抵抗接続を提供するように選択され得る。銅含有層 220 は、例えば、5 ミクロン～10 ミクロンの厚みとし得る。

#### 【 0028 】

アンダーバンプ金属 (UBM) 層 262 が、任意選択で、構成要素面 242 上に I/O パッド 214 上に延在して形成され得る。任意選択で、ピラーめっきマスク 264 を UBM 層 262 上に形成して、銅含有ピラー 216 のためのエリアを露出させ得る。UBM 層 262 は銅めっき槽 260 に晒され得、銅含有ピラー 216 の少なくとも一部が銅含有層 220 と同時に形成され得る。銅含有ピラー 216 の最終的な厚みは、銅含有層 220 の厚みよりも大きくし得、そのため、銅含有ピラー 216 の残りの部分が、銅含有ピラー 216 上に、図 2C に示されていないはんだボールを形成するためのめっきプロセスと共に、後続のめっきオペレーションにおいて形成され得る。

#### 【 0029 】

10

20

30

40

50

続いて、めっきマスク 252 を除去して、シード層 250 上の適所に銅含有層 220 を残す。ピラーめっきマスク 264 は、めっきマスク 252 の除去と同時に取り除かれ得る。めっきマスク 252 及びピラーめっきマスク 264 は、例えば、アッシングプロセスやオゾンプロセス等の酸素ドライエッチングプロセスにより取り除かれ得る。

#### 【0030】

図 2 D を参照すると、シード層 250 は、後続の個片化プロセスの間、シード層 250 内の銅による基板 244 の汚染を低減するために、個片化領域 258 から取り除かれ得る。シード層 250 は、銅含有層 220 によって露出された箇所のシード層 250 を除去することによって、個片化領域 258 から取り除かれ得る。シード層 250 は、例えば、时限ウェットエッチングプロセスによって取り除かれ得る。中間層 222 は、存在する場合には、基板 244 の汚染を低減するために個片化領域 258 から取り除かれ得る。UBM 層 262 は、銅含有ピラー 216 によって露出された箇所で取り除かれて、I/O パッド 214 と銅含有ピラー 216 との間の適所に UBM 層 262 を残す。銅含有ピラー 216 上のはんだボール 218 は、マイクロ電子デバイス 200 のためのバンプ結合構造を提供する。

10

#### 【0031】

図 2 E を参照すると、銅含有層 220 は、銅含有層 220 上に保護金属層 268 を形成する無電解めっき槽 266 に晒される。保護金属層 268 は、銅含有層 220 を腐食又は酸化から保護する組成を有する。無電解めっき槽 266 は、例えば、錫、銀、ニッケル、又はそれらの任意の組み合わせを含み得る。

20

#### 【0032】

錫を含む無電解めっき槽 266 の変形が、塩化第一錫 (1 リットルの H<sub>2</sub>O 当たり約 3 . 8 グラム)、チオ尿素 (1 リットルの H<sub>2</sub>O 当たり約 49 . 5 グラム)、及び硫酸 (1 リットルの H<sub>2</sub>O 当たり約 12 ミリリットル) を有し得、保護金属層 268 の形成の間、25 ~ 50 に維持され得る。

#### 【0033】

銀を含む無電解めっき槽 266 の変形例が、硝酸銀 (1 リットルの H<sub>2</sub>O 当たり約 10 グラム)、25 % 水酸化アンモニウム水溶液 (1 リットルの H<sub>2</sub>O 当たり約 100 ミリリットル)、及び、チオ硫酸ナトリウム (1 リットルの H<sub>2</sub>O 当たり約 100 グラム) を有し得、保護金属層 268 の形成の間、約 50 に維持され得る。

30

#### 【0034】

ニッケルを含む無電解めっき槽 266 の変形が、塩化ニッケル (1 リットルの H<sub>2</sub>O 当たり約 20 グラム)、塩酸塩ナトリウム (1 リットルの H<sub>2</sub>O 当たり約 15 グラム)、酢酸 (1 リットルの H<sub>2</sub>O 当たり約 20 ミリリットル)、リンゴ酸 (1 リットルの H<sub>2</sub>O 当たり約 20 グラム)、グリシン (1 リットルの H<sub>2</sub>O 当たり約 5 グラム)、及び、ホウ酸 (1 リットルの H<sub>2</sub>O 当たり約 2 グラム) を有し得、必要に応じて、水酸化ナトリウム又は塩化水素酸の付加によって pH が 6 . 5 ~ 6 . 7 に調節され得、保護金属層 268 の形成の間、約 70 に維持され得る。

#### 【0035】

無電解めっき槽 266 の独自の配合のための化学物質は、様々な供給業者から市販で入手可能である。無電解めっき槽 266 の 1 つの変形は、無電解めっき槽 266 のコスト及び複雑度を低減するために、錫、銀、又はニッケルなどの金属のうちの 1 つを含み得、本質的に他の金属を含まない。無電解めっき槽 266 の別の変形が錫及び銀の両方を含み得、これにより、錫ウイスカの形成が低減され得、銀よりも少ないコストで、錫よりロバストな保護を提供し得る。無電解めっき槽 266 の更なる変形が、保護金属層 268 のより耐久性のある変形例を提供するために、ニッケルを含み得る。

40

#### 【0036】

保護金属層 268 は、無電解めっき槽 266 の配合物、無電解めっき槽 266 の温度、及び銅含有層 220 が無電解めっき槽 266 に晒される時間に応じて、例えば、0 . 5 ミクロン ~ 5 ミクロンの厚みであり得る。無電解めっき槽 266 を用いて保護金属層 268

50

を形成することは、無電解めっき槽 266 が電気めっきプロセスによって用いられる電力供給及び関連する電気機器を必要としないので、有利にもマイクロ電子デバイス 200 の製造コストを低減し得る。

【0037】

構成要素面 242、I/O パッド 214、UBM 層 262、銅含有ピラー 216、及びはんだボール 218 は、図 2E に示すように、ポリマーコーティング 270、キャリアップレート 272、又は両方の組み合わせによって、無電解めっき槽 266 から隔離され得る。

【0038】

図 2F は、保護金属層 268 が銅含有層 220 上に形成された後の、マイクロ電子デバイス 200 及び類似のマイクロ電子デバイス 256 を備える基板ウェハ 238 を示す。保護金属層 268 は、有利にも、保管、取扱い、又は処理の間の銅含有層 220 の酸化、腐食、又は汚染を低減し得る。

10

【0039】

図 2G を参照すると、SAW プロセス、レーザースクライププロセス、又はプラズマエッチ個片化プロセスなどの個片化プロセスによって、マイクロ電子デバイス 200 が基板ウェハ 238 から個片化される。個片化プロセスは、個片化領域 258 を介して基板ウェハ 238 を分離することによって、マイクロ電子デバイス 200 を、近接する類似のマイクロ電子デバイス 256 から分離する。基板ウェハ 238 の基板 244 は、個片化されたマイクロ電子デバイス 200 の基板 204 を提供する。基板ウェハ 238 の構成要素面 242 は、個片化されたマイクロ電子デバイス 200 の構成要素表面 202 を提供し、基板ウェハ 238 のダイ取り付け面 246 は、個片化されたマイクロ電子デバイス 200 のダイ取り付け表面 206 を提供する。保護金属層 268 は、個片化プロセスの間の銅含有層 220 の酸化、腐食、又は汚染を有利に低減し得る。

20

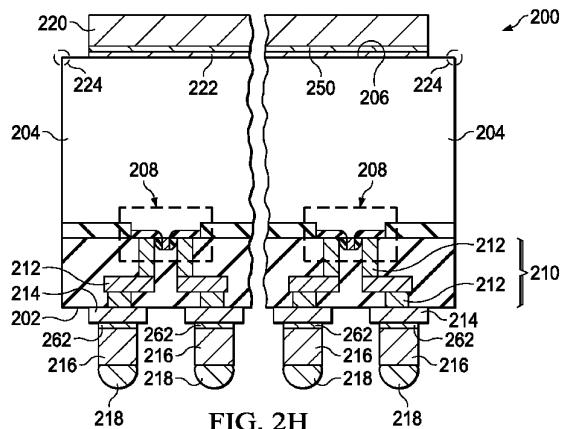

【0040】

図 2H は、マイクロ電子デバイス 200 をリードフレームなどのパッケージにアセンブルする直前の個片化されたマイクロ電子デバイス 200 を示す。図 2G の保護金属層 268 は、図 2H に示すように、任意選択で取り除かれて、銅含有層 220 を実質的にそのまま残し得る。保護金属層 268 は、ウェットエッチングプロセスによって、又は、例えは、電気化学的エッチング（逆方向めっき）プロセスによって取り除かれ得る。例示的なウェットエッチングプロセスが、硝酸（重量で約 20 パーセント）、第二鉄イオン（Fe<sup>3+</sup>、重量で約 5 パーセント）、銅（水溶液 1 リットル当たり約 1 ~ 2 グラム）、溶液内の保護金属層 268 から錫及び銀を保つための懸濁剤、及び銅含有層 220 の酸化を低減するための、変色防止剤としても知られる抑制剤を用い得る。保護金属層 268 を除去するためのエッチ溶液は、様々な供給業者から市販されている。

30

【0041】

銅含有層 220 は、図 2C のめっきマスク 252 が図 2G の個片化領域 258 に重なる結果、ダイ取り付け表面 206 の横方向外周 224 から窪まされる。シード層 250 も、図 2D に関連して開示されるように、銅含有層 220 によって露出される箇所で取り除かれる結果、ダイ取り付け表面 206 の横方向外周 224 から窪まされ得る。

40

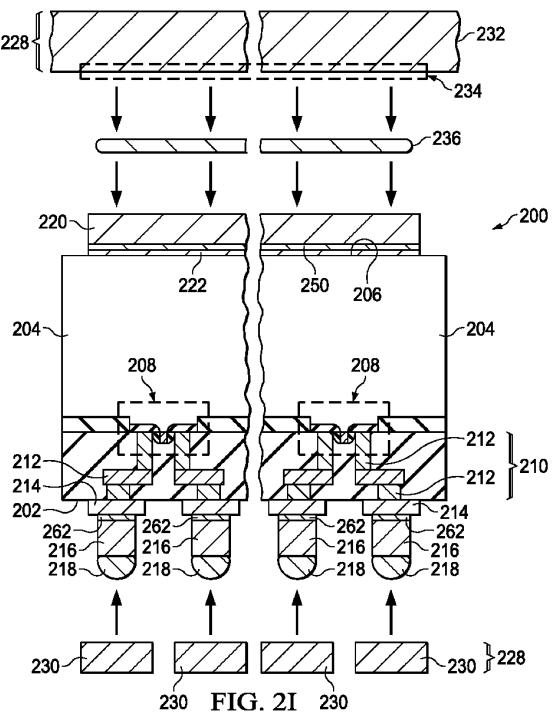

【0042】

図 2I を参照すると、マイクロ電子デバイス 200 は、図 2I においてリードフレーム 228 として示されるパッケージ 228 にアセンブルされる。リードフレーム 228 は、図 2I に概略的に示されるように、はんだボール 218 を介して銅含有ピラー 216 に取り付けられるリード 230 を含み得る。リードフレーム 228 は、銅含有層 220 に面するパッケージダイ取付けエリア 234 を備える、クリップ 232 として本例において表され得るパッケージ部材 232 を更に含み得る。クリップ 232 は、概略的に示されるように、シード層 250、存在する場合には中間層 222、銅含有層 220、及びダイ取り付け材料 236 を介して、パッケージダイ取付けエリア 234 において基板 204 に取り付けられ得る。本例では、ダイ取り付け材料 236 は、銅含有層 220 に直に接する。ダイ取り付け材料 236 は、はんだ層 236 として表され得る。マイクロ電子デバイス 20

50

0は、銅含有層220、はんだ層236、及びクリップ232を互いに接触させ、リード230をはんだボール218に接触させ、続いて熱を印加してはんだ層236及びはんだボール218をリフローさせる、はんだリフロープロセスによって、パッケージ228内にアセンブルされ得る。或いは、ダイ取り付け材料236は接着剤として表され得る。図2Gの保護金属層268で銅含有層220を保護することは、銅含有層220のためのより大きな厚み及びよりクリーンな表面を提供し得、有利にも、保護されていない銅層を用いる場合と比較して、一層低い熱的又は電気的抵抗で、基板204とクリップ232との間のより信頼性の高い接続をもたらす。

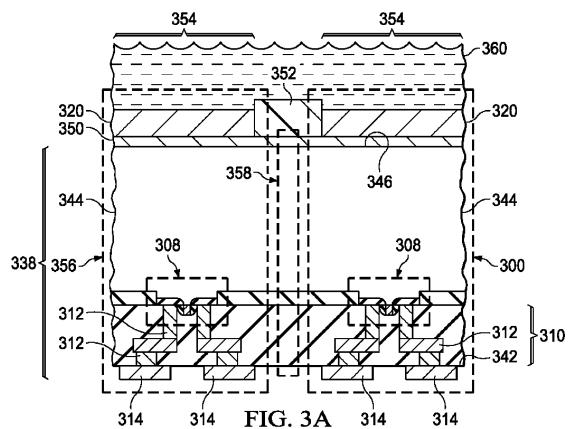

#### 【0043】

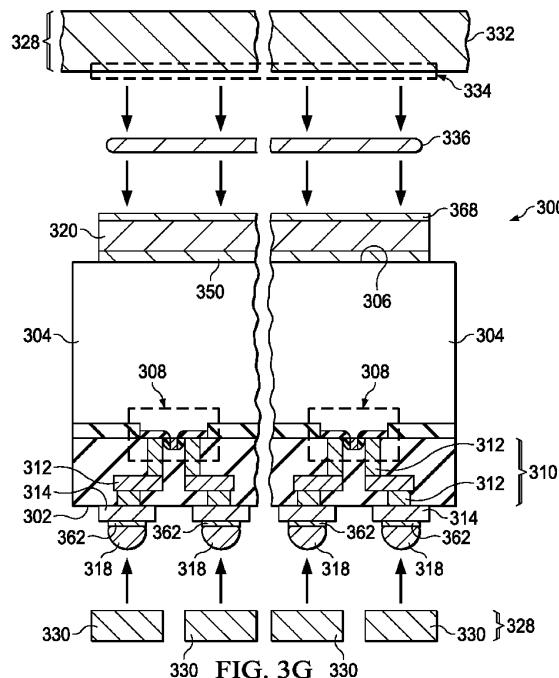

図3A～図3Hは、形成の別の例示的な方法の種々の段階で描かれたマイクロ電子デバイスの図である。図3Aを参照すると、マイクロ電子デバイス300は基板ウェハ338に含まれている。基板ウェハ338は、図2Aの基板ウェハ238に類似していてもよい。基板ウェハ338は、構成要素面342と半導体材料の基板344とを有し、ダイ取り付け面346が、構成要素面342とは反対側に位置する。図3Aは、マイクロ電子デバイス300と、近接する類似のマイクロ電子デバイス356との間の境界における基板ウェハ338を断面で示す。構成要素308は、構成要素面342に近接する基板ウェハ338内に形成される。マイクロ電子デバイス300及び類似のマイクロ電子デバイス356は、構成要素308から構成要素面342まで延在する相互接続領域310を含む。マイクロ電子デバイス300及び類似のマイクロ電子デバイス356は、構成要素308を構成要素面342に配置されるI/Oパッド314に電気的に接続するために、相互接続領域310内に相互接続部材312を含み得る。

10

#### 【0044】

基板ウェハ338は、10ミクロン～300ミクロンの厚みまで薄化される。基板ウェハ338は、例えば、図2Aに関連して説明したように、ダイ取り付け面346から材料を除去することによって薄化され得る。続いて、シード層350がダイ取り付け面346上に形成されて、電気めっきプロセスに適した導電層及び表面を提供する。シード層350は、例えば、ニッケルを含み得る。シード層は、例えば、スパッタプロセス又は蒸着プロセスによって形成され得る。

20

#### 【0045】

シード層350の上にめっきマスク352が形成される。めっきマスク352は開口354を有し、開口354は、マイクロ電子デバイス300、及び基板ウェハ338に含まれる類似のマイクロ電子デバイス356のためのエリアにおいて、シード層350を露出させる。めっきマスク352は、マイクロ電子デバイス300のエリアと類似のマイクロ電子デバイス356との間の個片化領域358のエリアを覆う。めっきマスク352は、例えばフォトリソグラフィプロセスにより形成され得、或いは、アディティブ法により形成され得る。

30

#### 【0046】

シード層350は、めっきマスク352内の開口354において銅めっき槽360に晒される。電気めっきプロセスによって、めっきマスク352によって露出されるマイクロ電子デバイス300上及び類似のマイクロ電子デバイス356上に、銅含有層320が形成される。銅めっき槽360は銅を含み、図2Cに関連して開示されるような添加剤を含み得る。銅含有層320は、基板344に対する電気及び熱インピーダンスと、基板344に対する機械的応力との均衡を保つため、5ミクロン～10ミクロンの厚みとし得る。

40

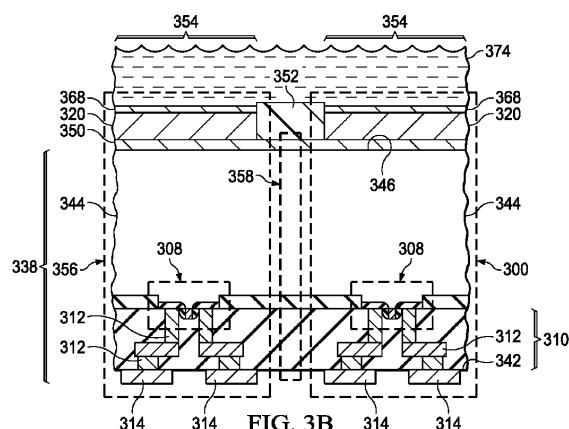

#### 【0047】

図3Bを参照すると、めっきマスク352は適所に残され、銅含有層320は、めっきマスク352内の開口354において電気めっき槽374に晒される。電気めっきプロセスによって銅含有層320上に保護金属層368が形成される。保護金属層368は、銅含有層320を腐食又は酸化から保護する組成を有する。保護金属層368は、錫、銀、ニッケル、コバルト、タングステン、モリブデン、セリウム、ランタン、又はそれらの任意の組み合わせを含み得る。効果的であることが明らかになっている保護金属層368の

50

ための特定の組成は、本質的に全て錫、数重量パーセントの銀を有する錫、本質的に全て銀、数重量パーセントのコバルトを有する銀、本質的に全てニッケル、ニッケル及び錫の組み合わせ、ニッケル及び銀の組み合わせ、数重量パーセントのタングステンを有するニッケル、本質的に全てコバルト、ニッケル及びコバルトの組み合わせ、ニッケル、コバルト、及びタングステンの組み合わせ、並びに、銀及びタングステンの組み合わせを含む。モリブデンは、保護金属層 368 内のタングステンの一部又は全てを置換してもよい。セリウム又はランタンが、ニッケルを含む保護金属層 368 の変形に追加され得る。保護金属層 368 は、銅含有層 320 に対してより多くの保護を提供するために、5ミクロン～50ミクロンの厚みとし得る。電気めっき槽 374 を用いて保護金属層 368 を形成することは、所望のプロセス制御で所望の厚みに保護金属層 368 を形成することを可能にし得る。

#### 【 0 0 4 8 】

図 3 C を参照すると、めっきマスク 352 が取り除かれる。めっきマスク 352 は、図 3 C に概略的に示すように、酸素ラジカル 376 を用いるプラズマプロセスによって取り除かれ得る。或いは、めっきマスク 352 は、ウェット洗浄プロセスにより取り除かれてもよい。めっきマスク 352 を取り除くために、酸素ラジカル 376 を用いるプラズマプロセスとウェット洗浄プロセスとの組み合わせが用いられてもよい。

#### 【 0 0 4 9 】

図 3 D を参照すると、シード層 350 は、個片化領域 358 上のエリアから取り除かれ得る。シード層 350 は、ウェットエッチ溶液 378 を用いて取り除かれ得る。ウェットエッチ溶液 378 は、銅含有層 320 又は保護金属層 368 を著しく劣化させることなく、銅含有層 320 によって露出された箇所のシード層 350 を除去するように配合し得る。或いは、シード層 350 は、電解研磨プロセスと称されることもある逆方向めっきプロセスを用いて取り除かれてもよい。

#### 【 0 0 5 0 】

図 3 E を参照すると、マイクロ電子デバイス 300 は、例えば図 2 G を参照して説明したように、基板ウェハ 338 から個片化される。個片化プロセスは、個片化領域 358 を介して基板ウェハ 338 を分離することによって、マイクロ電子デバイス 300 を、近接する類似のマイクロ電子デバイス 356 から分離する。基板ウェハ 338 の基板 344 は、個片化されたマイクロ電子デバイス 300 の基板 304 を提供する。基板ウェハ 338 の構成要素面 342 は、個片化されたマイクロ電子デバイス 300 の構成要素表面 302 を提供し、基板ウェハ 338 のダイ取り付け面 346 は、個片化されたマイクロ電子デバイス 300 のダイ取り付け表面 306 を提供する。保護金属層 368 は、個片化プロセスの間の銅含有層 320 の酸化、腐食、又は汚染を有利に低減し得る。

#### 【 0 0 5 1 】

図 3 F を参照すると、I/O パッド 314 上に UBM 層 362 が形成される。UBM 層 362 上にはんだボール 318 が形成される。本例の代替の変形において、UBM 層 362 及びはんだボール 318 は、図 3 E を参照して説明した個片化プロセスの前に形成され得る。

#### 【 0 0 5 2 】

銅含有層 320 は、図 3 A のめっきマスク 352 が図 3 E の個片化領域 358 に重なった結果、ダイ取り付け表面 306 の横方向外周 324 から窪まされる。シード層 350 は、また、図 3 E に関連して開示されるように、銅含有層 320 によって露出された箇所で取り除かれる結果として、ダイ取り付け表面 306 の横方向外周 324 から窪まされ得る。

#### 【 0 0 5 3 】

図 3 G を参照すると、マイクロ電子デバイス 300 は、図 3 G においてリードフレーム 328 として示されるパッケージ 328 にアセンブルされる。リードフレーム 328 は、図 3 G に概略的に示すように、はんだボール 218 に取り付けられるリード 330 を含み得る。リードフレーム 328 は、銅含有層 320 に面するパッケージダイ取付けエリア 334 を有する、クリップ 332 などのパッケージ部材 332 を更に含み得る。クリップ 3

10

20

30

40

50

3 2 は、概略的に示されるように、シード層 3 5 0 、銅含有層 3 2 0 、保護金属層 3 6 8 、及びダイ取り付け材料 3 3 6 を介して、パッケージダイ取付けエリア 3 3 4 において基板 3 0 4 に取り付けられ得る。本例では、ダイ取り付け材料 3 3 6 は保護金属層 3 6 8 に直に接する。ダイ取り付け材料 3 3 6 は、はんだ層 3 3 6 として表されてもよく、マイクロ電子デバイス 3 0 0 は、はんだリフロー プロセスによってパッケージ 3 2 8 にアセンブルされ得る。或いは、ダイ取り付け材料 3 3 6 は接着剤として表され得る。銅含有層 3 2 0 を保護金属層 3 6 8 で保護することは、銅含有層 3 2 0 のための所望の厚み及び均一性を提供し得、有利なことに、保護されていない銅層を用いる場合と比較して、一層低い熱的又は電気的抵抗で、基板 3 0 4 とクリップ 3 3 2 との間のより信頼性の高い接続をもたらす。

10

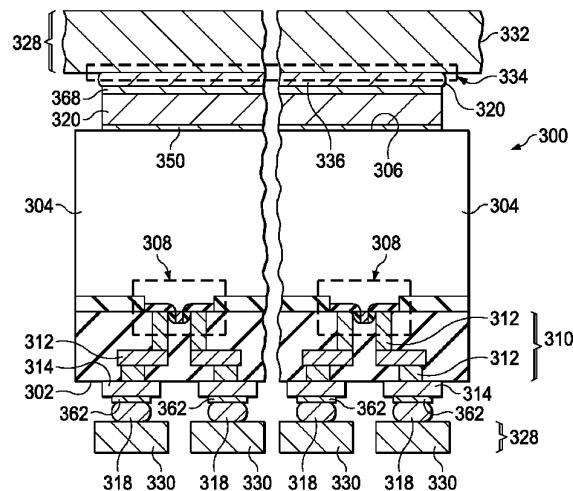

#### 【 0 0 5 4 】

図 3 H は、パッケージ 3 2 8 内にアセンブルされた後のマイクロ電子デバイス 3 0 0 の断面である。はんだボール 3 1 8 は、はんだリフロー処理によってリード 3 3 0 に取り付けられる。はんだボール 3 1 8 は、保護金属層 3 6 8 をクリップ 3 3 2 に取り付けながら、同時にリード 3 3 0 に取り付けられ得る。その後、封止材料をマイクロ電子デバイス 3 0 0 の周りに形成して、保護及び電気的隔離を提供し得る。

#### 【 0 0 5 5 】

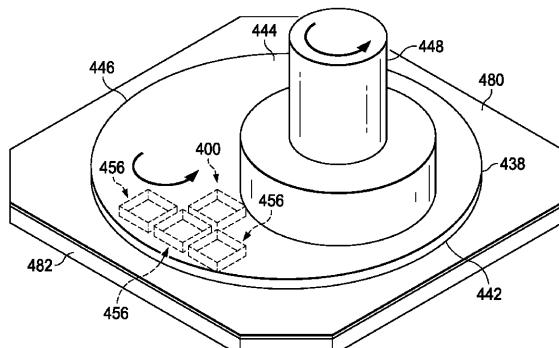

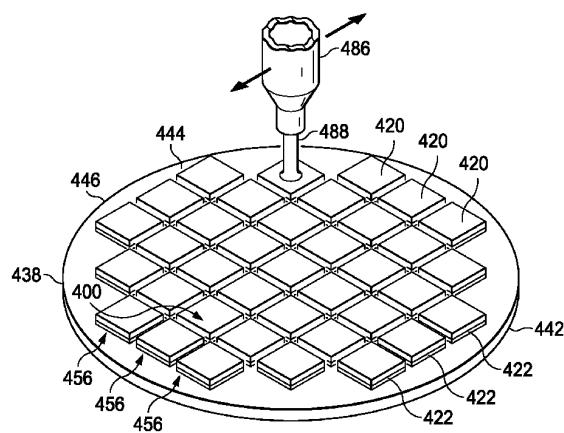

図 4 A ~ 図 4 F は、形成の更なる例示的な方法の種々の段階で描かれたマイクロ電子デバイスの図である。図 4 A を参照すると、マイクロ電子デバイス 4 0 0 は、基板ウェハ 4 3 8 に含まれている。基板ウェハ 4 3 8 は、類似のマイクロ電子デバイス 4 5 6 を含み得る。基板ウェハ 4 3 8 は、任意選択で、テープ 4 8 0 及びテープフレーム 4 8 2 上に取り付けられ得る。或いは、基板ウェハ 4 3 8 は、キャリアプレート上に取り付けられてもよく、又は保護コーティングを有していてもよい。基板ウェハ 4 3 8 は、テープ 4 8 0 に面する構成要素面 4 4 2 を有する。基板ウェハ 4 3 8 は、構成要素面 4 4 2 とは反対側に位置するダイ取り付け面 4 4 6 を備える基板 4 4 4 を含む。基板 4 4 4 は半導体材料を含む。

20

#### 【 0 0 5 6 】

材料は、バックグラインドオペレーションにおいて、バックグラインドツール 4 4 8 を用いて、ダイ取り付け面 4 4 6 において基板 4 4 4 から取り除かれる。テープ 4 8 0 は、バックグラインドオペレーションの間、構成要素面 4 4 2 を汚染から保護する。テープ 4 8 0 及びテープフレーム 4 8 2 は、バックグラインドオペレーションが完了した後に取り除かれてもよく、又は後続のオペレーションの間、機械的支持を提供するために基板ウェハ 4 3 8 上に残され得る。

30

#### 【 0 0 5 7 】

図 4 B を参照すると、中間層 4 2 2 が、マイクロ電子デバイス 4 0 0 及び類似のマイクロ電子デバイス 4 5 6 のためのエリアにおいて、ダイ取り付け面 4 4 6 上に形成される。本例では、中間層 4 2 2 は、図 4 B に示すように、個別のディスペンスツール 4 8 4 を用いる材料ジェットプロセスなどの第 1 のアディティブ法によって形成され得る。中間層 4 2 2 を形成するための他のアディティブ法も本例の範囲内である。本記載において、アディティブ法が、ナノ粒子を所望のエリアに配置し、ナノ粒子を所望のエリア外に配置しないので、ナノ粒子の最終的な所望の形状を生成するためにディスペンスされたナノ粒子の部分を除去する必要がない。アディティブプロセスは、フォトリソグラフィプロセス及び後続のエッチングプロセスなしに、所望のエリアにおいてフィルムを形成することを可能にし、従って、製造コスト及び複雑度を有利に低減し得る。アディティブ法の例には、バインダジェット、指向性エネルギー堆積、材料押出、パウダーベッドフュージョン、シートラミネーション、バット光重合、直接レーザー堆積、静電気堆積、レーザー焼結、電気化学的堆積、及び光重合押出が含まれる。中間層 4 2 2 は、揮発性材料を除去するために、又は中間層 4 2 2 におけるバインダ又は接着剤を硬化させるために、加熱オペレーションを必要とし得る。

40

#### 【 0 0 5 8 】

中間層 4 2 2 は、図 4 B に示されるように、マイクロ電子デバイス 4 0 0 と類似のマイ

50

クロ電子デバイス 456との間の個片化領域を、後続の個片化プロセスの間、基板 444 を汚染し得る材料がないように保つようにパターニングされ得る。アディティブ法は、一般に、中間層 422 をパターニングするためのマスクを形成するためのフォトリソグラフィオペレーションを必要とするプロセスよりも、工程がより少なく、より安価である。

#### 【0059】

中間層 422 は、図 4C に示されるように、ダイ取り付け面 446 と、後に形成される銅含有層 420 との間に、チタン、タンゲステン、又はナノ粒子など、良好な接着を提供するための材料を含み得る。中間層 422 は、銅含有層 420 から基板 444 への拡散を銅ための障壁を提供するために、ニッケル、コバルト、タンゲステン、又はモリブデンなどの材料を含み得る。

10

#### 【0060】

基板ウェハ 438 は、図 4B に示すように、中間層 422 の形成の間、キャリアなしで取り扱うことができる。或いは、基板ウェハ 438 は、テープ又はキャリアプレート上に取り付けられてもよい。

#### 【0061】

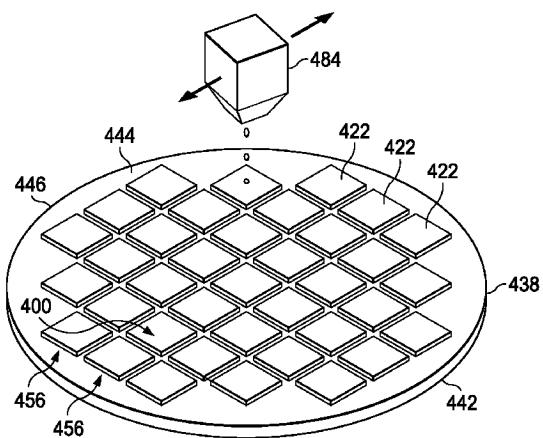

図 4C を参照すると、銅含有層 420 は、マイクロ電子デバイス 400 及び類似のマイクロ電子デバイス 456 のためのエリアにおいて、中間層 422 上に形成される。銅含有層 420 は、図 4C に示すように、材料押出ツール 486 を用いる材料押出プロセスなどの第 2 のアディティブ法によって形成され得る。第 2 のアディティブ法は、銅含有材料 488 をダイ取り付け面 446 上に、存在する場合には中間層 422 上に直接に配置する。銅含有層 420 は、銅金属の継続的な層を含み得、又は銅ナノ粒子を含み得る。銅含有層 420 の組成及び構造に応じて、銅含有層 420 は、スパッタされた銅よりも小さい応力を有し得、従って、後続の製造工程と適合しない程度まで基板ウェハ 438 を歪ませることなく、例えば、10ミクロン～25ミクロンの厚みとし得る。銅含有層 420 は、揮発性材料を除去するために、もしくは、バインダ又は接着剤を硬化させるために、加熱オペレーションを必要とし得る。

20

#### 【0062】

本例に従って形成された銅含有層 420 は、マイクロ電子デバイス 400 と類似のマイクロ電子デバイス 456 との間の個片化領域に、後続の個片化プロセスの間、基板 444 を汚染する恐れのある銅がないように保つようにパターニングされる。第 2 のアディティブ法は、マスク及びプレートオペレーションよりも一層低いコストで、銅含有層 420 のパターニングされた態様を提供し得る。

30

#### 【0063】

基板ウェハ 438 は、図 4C に示されるように、銅含有層 420 の形成の間、キャリアなしで取り扱うことができる。或いは、基板ウェハ 438 は、テープ又はキャリアプレート上に取り付けられてもよい。

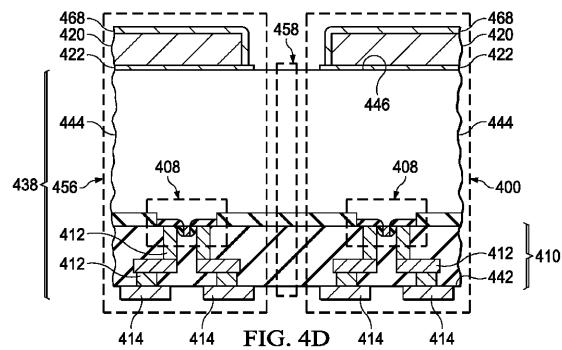

#### 【0064】

図 4D を参照すると、基板ウェハ 438 は、マイクロ電子デバイス 400 と類似のマイクロ電子デバイス 456 の隣り合うインスタンスとの間の境界において断面で示される。マイクロ電子デバイス 400 と近接する類似のマイクロ電子デバイス 456 との間に個片化領域 458 が位置する。マイクロ電子デバイス 400 及び類似のマイクロ電子デバイス 456 は、構成要素面 442 に近接して位置する構成要素 408、及び構成要素 408 から構成要素面 442 まで延在する相互接続領域 410 を含む。マイクロ電子デバイス 400 及び類似のマイクロ電子デバイス 456 は、構成要素 408 を構成要素面 442 に配置される I/O パッド 414 に電気的に接続するために、相互接続領域 410 内に相互接続部材 412 を含み得る。本例では、I/O パッド 414 は、ワイヤボンドパッド 414 として表され得る。

40

#### 【0065】

中間層 422 は、図 4D に示すように、個片化領域 458 から窪まされ得る。銅含有層 420 は、個片化領域 458 から窪んでいてもよく、また、図 4D に示されるように、中

50

間層 422 の横方向外周から窪んでいてもよい。中間層 422 及び銅含有層 420 を窪ませることは、マイクロ電子デバイス 400 を近接する類似のマイクロ電子デバイス 456 から分離する後続の個片化プロセスの間、中間層 422 及び銅含有層 420 における金属から基板 444 内への汚染を有利に低減し得る。

【0066】

銅含有層 420 上に保護金属層 468 が形成される。保護金属層 468 は、例えば、錫、銀、ニッケル、コバルト、タングステン、モリブデン、セリウム、ランタン、又はそれらの任意の組み合わせを含み得る。保護金属層 468 は、例えば図 2E に関連して開示されるように、浸漬めっきプロセスによって、又は、例えば図 3B に関連して開示されるように、電気めっきプロセスによって形成され得る。保護金属層 468 の厚みは、例えば、0.5 ミクロン～2 ミクロンとし得る。保護金属層 468 は、図 4D に示すように、個片化領域 458 内には延在していない。

10

【0067】

保護金属層 468 が形成された後、マイクロ電子デバイス 400 は、個片化プロセスによって基板ウェハ 438 から個片化される。個片化プロセスは、個片化領域 458 を介して、マイクロ電子デバイス 400 を近接する類似のマイクロ電子デバイス 456 から分離する。保護金属層 468 は、個片化プロセスの間の腐食又は汚染から銅含有層 420 を有利に保護し得る。

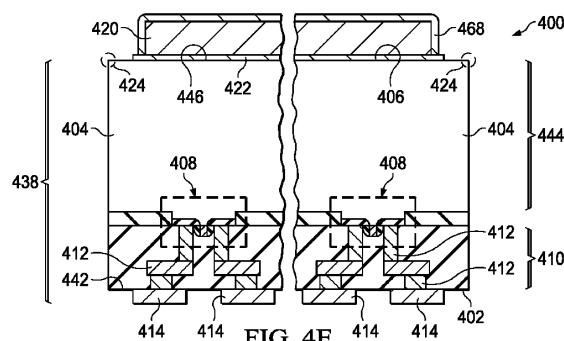

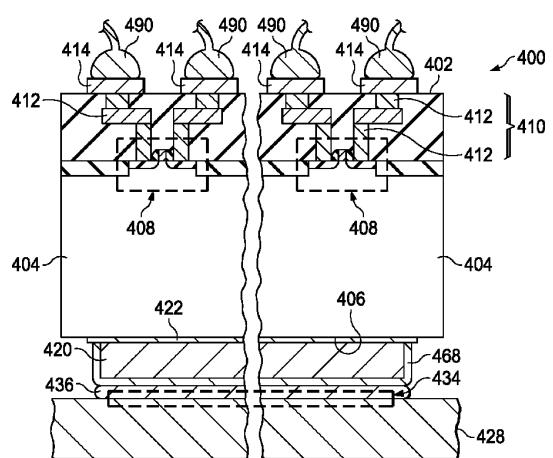

【0068】

図 4E は、個片化プロセス後のマイクロ電子デバイス 400 を示す。基板ウェハ 438 の基板 444 は、個片化されたマイクロ電子デバイス 400 の基板 404 を提供する。基板ウェハ 438 の構成要素面 442 は、個片化されたマイクロ電子デバイス 400 の構成要素表面 402 を提供し、基板ウェハ 438 のダイ取り付け面 446 は、個片化されたマイクロ電子デバイス 400 のダイ取り付け表面 406 を提供する。本例では、保護金属層 468 は、後続のアッセンブリプロセスの間、銅含有層 420 上に残され得る。銅含有層 420 は、マイクロ電子デバイス 400 と図 2C の類似のマイクロ電子デバイス 456 との間の個片化領域を銅のないように保つために、図 4C に関連して開示された第 2 のアディティブ法を行った結果として、ダイ取り付け表面 406 の横方向外周 424 から窪んでいてもよい。

20

【0069】

図 4F を参照すると、マイクロ電子デバイス 400 はパッケージ部材 428 上にアセンブルされ、これは本例ではヘッダー 428 として示されている。ヘッダー 428 は、マイクロ電子デバイス 400 を取り付けるためのパッケージダイ取り付けエリア 434 を有する。

30

【0070】

ヘッダー 428 は、概略的に示すように、中間層 422、銅含有層 420、保護金属層 468、及びはんだ層 436 を通して、パッケージダイ取り付けエリア 434 において基板 404 に取り付けられ得る。マイクロ電子デバイス 400 は、保護金属層 468 をはんだ層 436 に接触させ、はんだ層 436 をヘッダー 428 に接触させ、続いて熱を印加してはんだ層 436 をリフローさせるはんだリフロー処理によって、ヘッダー 428 上にアセンブルすることができる。保護金属層 468 の一部が、リフロー処理の間、はんだ層 436 に吸収され得る。銅含有層 420 を保護金属層 468 で保護することは、銅含有層 420 のためのより大きな厚みを提供し得、保護されていない銅層を用いることと比較して、有利にも一層低い熱的又は電気的抵抗で、基板 404 とヘッダー 428 との間のより信頼性の高い接続をもたらす。

40

【0071】

構成要素 408 に電気的接続を提供するために、ワイヤボンドパッド 414 上にワイヤボンド 490 が形成され得る。ワイヤボンド 490 は、ヘッダー 428 が基板 404 に取り付けられた後に形成され得る。

【0072】

50

本明細書に開示された例の様々な特徴は、例示的なマイクロ電子デバイスの他の顕在化において組み合わされ得る。例えば、中間層 2 2 2 を形成するためのスパッタプロセスは、中間層 4 2 2 を形成するための第 1 のアディティブ法の代わりに用いられ得、逆もまた同様である。同様に、銅含有層 2 2 0 を形成するためのめっきプロセスは、銅含有層 4 2 0 を形成するための第 2 のアディティブ法の代わりに用いられ得、逆もまた同様である。マイクロ電子デバイス 2 0 0 は、銅含有ピラー 2 1 6 及びはんだボール 2 1 8 の代わりにワイヤボンドパッドを有し得る。同様に、マイクロ電子デバイス 4 0 0 は、ワイヤボンドパッド 4 1 4 の代わりに銅含有ピラー及びはんだボールを有し得る。

【 0 0 7 3 】

本発明の特許請求の範囲内で、説明した例示の実施例に改変が成され得、他の実施例が可能である。

10

20

30

40

50

## 【义面】

【 义 1 】

【図2A】

FIG. 2A

10

20

30

## 【図2B】

### 【図2C】

40

50

【図 2 D】

FIG. 2D

【図 2 E】

FIG. 2E

10

【図 2 F】

FIG. 2F

【図 2 G】

FIG. 2G

20

30

40

50

【図 2 H】

FIG. 2H

【図 2 I】

10

20

【図 3 A】

FIG. 3A

【図 3 B】

30

40

50

【図 3 C】

【図 3 D】

10

【図 3 E】

【図 3 F】

20

30

FIG. 3F

40

50

【図 3 G】

FIG. 3G

【図 3 H】

FIG. 3H

10

20

【図 4 A】

FIG. 4A

【図 4 B】

FIG. 4B

30

40

50

【図 4 C】

FIG. 4C

【図 4 D】

10

【図 4 E】

FIG. 4E

【図 4 F】

20

FIG. 4F

30

40

50

---

フロントページの続き

(33)優先権主張国・地域又は機関

米国(US)

ロード 8 2 6 - 4 3 0

(72)発明者 サルバトーレ フランク パボネ

アメリカ合衆国 7 5 0 9 4 テキサス州 マーフィ , ドッグウッド ドライブ 8 2 1

審査官 小池 英敏

(56)参考文献 米国特許出願公開第2 0 1 2 / 0 3 2 6 2 9 7 ( U S , A 1 )

米国特許出願公開第2 0 0 6 / 0 2 1 4 2 8 6 ( U S , A 1 )

特開2 0 0 9 - 0 9 4 3 4 1 ( J P , A )

特表2 0 0 9 - 5 0 5 4 3 9 ( J P , A )

(58)調査した分野 (Int.Cl. , DB名)

H 0 1 L 2 1 / 5 2

H 0 1 L 2 3 / 3 6

H 0 1 L 2 1 / 6 0

H 0 1 L 2 3 / 1 2

H 0 1 L 2 3 / 5 0