(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4832146号

(P4832146)

(45) 発行日 平成23年12月7日(2011.12.7)

(24) 登録日 平成23年9月30日(2011.9.30)

(51) Int.Cl.

HO3K 19/0185 (2006.01)

F 1

HO3K 19/00 101E

請求項の数 9 (全 27 頁)

(21) 出願番号 特願2006-110395 (P2006-110395)

(22) 出願日 平成18年4月13日 (2006.4.13)

(65) 公開番号 特開2006-325193 (P2006-325193A)

(43) 公開日 平成18年11月30日 (2006.11.30)

審査請求日 平成21年4月7日 (2009.4.7)

(31) 優先権主張番号 特願2005-121753 (P2005-121753)

(32) 優先日 平成17年4月19日 (2005.4.19)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 納 光明

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 柳井 宏美

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 宮島 郁美

最終頁に続く

(54) 【発明の名称】 レベルシフタ回路、駆動回路、ディスプレイ、表示モジュール、電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

第1乃至第3の電源と、第1乃至第6のPチャネル型トランジスタと、第1乃至第6のNチャネル型トランジスタと、を有し、

前記第1のPチャネル型トランジスタのソースは前記第1の電源と電気的に接続され、前記第1のPチャネル型トランジスタのドレインは前記第2のPチャネル型トランジスタのソースと電気的に接続され、

前記第2のPチャネル型トランジスタのドレインは前記第3のPチャネル型トランジスタのゲート及び前記第1のNチャネル型トランジスタのドレインと電気的に接続され、

前記第1のNチャネル型トランジスタのソースは前記第2の電源と電気的に接続され、

前記第3のPチャネル型トランジスタのソースは前記第1の電源と電気的に接続され、前記第3のPチャネル型トランジスタのドレインは前記第4のPチャネル型トランジスタのソースと電気的に接続され、

前記第4のPチャネル型トランジスタのドレインは前記第1のPチャネル型トランジスタのゲート及び前記第2のNチャネル型トランジスタのドレインと電気的に接続され、

前記第2のNチャネル型トランジスタのソースは前記第2の電源と電気的に接続され、

前記第5のPチャネル型トランジスタのソースは前記第1の電源と電気的に接続され、

前記第5のPチャネル型トランジスタのドレインは直列に接続された前記第3のNチャネル型トランジスタと前記第4のNチャネル型トランジスタとを介して前記第1のNチャネル型トランジスタのゲートと電気的に接続され、

10

20

前記第4のNチャネル型トランジスタのゲートは前記第3の電源と電気的に接続され、前記第5のPチャネル型トランジスタのドレインは前記第2のPチャネル型トランジスタのゲートと電気的に接続され、

前記第6のPチャネル型トランジスタのソースは前記第1の電源と電気的に接続され、前記第6のPチャネル型トランジスタのドレインは直列に接続された前記第5のNチャネル型トランジスタと前記第6のNチャネル型トランジスタとを介して前記第2のNチャネル型トランジスタのゲートと電気的に接続され、

前記第6のNチャネル型トランジスタのゲートは前記第3の電源と電気的に接続され、前記第6のPチャネル型トランジスタのドレインは前記第4のPチャネル型トランジスタのゲートと電気的に接続され、

前記第1のNチャネル型トランジスタのゲートには第1の入力信号が入力され、前記第2のNチャネル型トランジスタのゲートには第2の入力信号が入力され、前記第5のPチャネル型トランジスタのゲート、前記第3のNチャネル型トランジスタのゲート、前記第6のPチャネル型トランジスタのゲート、及び前記第5のNチャネル型トランジスタのゲートには、同じ制御信号が入力されていることを特徴とするレベルシフタ回路。

#### 【請求項2】

請求項1において、

前記制御信号は、前記第1の入力信号が前記第1のNチャネル型トランジスタをオンさせる信号に切り替わる前に、前記第5のPチャネル型トランジスタをオンさせる信号に切り替わることを特徴とするレベルシフタ回路。

#### 【請求項3】

請求項1または請求項2において、

前記制御信号は、前記第1の電源が与える電位をハイレベルとし、前記第2の電源が与える電位をローレベルとする信号であることを特徴とするレベルシフタ回路。

#### 【請求項4】

請求項1乃至請求項3のいずれか一項において、

前記第3の電源が与える電位は、前記第2の電源が与える電位より高く、前記第1の電源が与える電位より低いことを特徴とするレベルシフタ回路。

#### 【請求項5】

請求項1乃至請求項4のいずれか一項において、

前記第1の入力信号は、前記第2の入力信号の反転信号であることを特徴とするレベルシフタ回路。

#### 【請求項6】

請求項1乃至請求項5のいずれか一項において、

前記レベルシフタ回路を複数用いたことを特徴とする駆動回路。

#### 【請求項7】

請求項1乃至請求項5のいずれか一項において、

前記レベルシフタ回路を用いたことを特徴とするディスプレイ。

#### 【請求項8】

請求項1乃至請求項5のいずれか一項において、

前記レベルシフタ回路を用いたことを特徴とする表示モジュール。

#### 【請求項9】

請求項1乃至請求項5のいずれか一項において、

前記レベルシフタ回路を用いたことを特徴とする電子機器。

#### 【発明の詳細な説明】

#### 【技術分野】

#### 【0001】

本発明は信号の振幅変換を行うレベルシフタ回路に関するものである。また、レベルシフタ回路を用いた表示装置およびその駆動回路に関するものである。

10

20

30

40

50

**【背景技術】****【0002】**

携帯電話機やPDA (Personal digital Assistant) 等の携帯機器においては、携帯性とともに、限られた電力で長時間利用できることが好ましく、日々低消費電力化が要求されている。そのため、前述のような機器を構成する集積回路 (LSI) は、1.8V～5V程度の電源電圧にて駆動されるものが少なくない。一方で、それらLSIによって駆動されるLCDやエレクトロルミネッセンス (Electro luminescence : EL) ディスプレイ等の表示装置においては、内部の駆動回路に10V～20Vといった高電源電圧にて動作する回路が少なくとも存在する。このような駆動回路においては、前述の低電源電圧回路より出力される制御信号と、高電源電圧回路とのやり取りに際し、信号の振幅を変換するレベルシフタ回路が用いられている（特許文献1参照）。 10

**【0003】**

【特許文献1】特開2001-257581号公報

**【発明の開示】****【発明が解決しようとする課題】****【0004】**

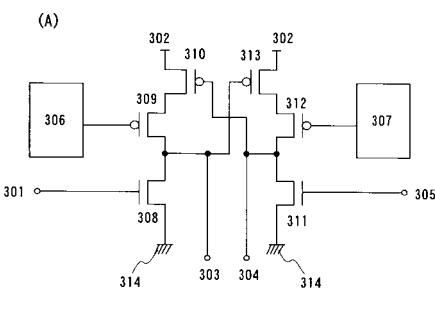

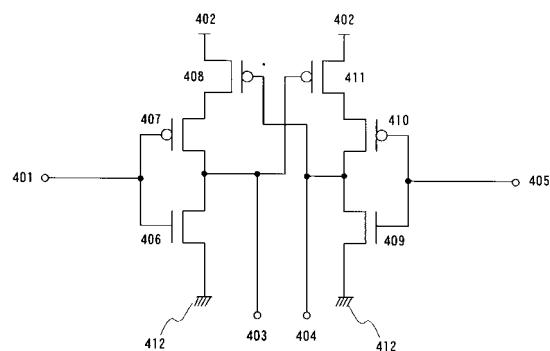

従来用いられてきているレベルシフタ回路は、図4に示す回路構成のものが一例として挙げられる。図4に示すレベルシフタ回路の構成は以下のとおりである。入力401には、VDD電位をハイ(HIGH)レベル、GND電位をロー(LOW)レベルとして当該ハイレベルとローレベルとの間で変化する（以下、VDD電源系と表記）2レベル信号が入力される。一方、入力405には、入力401に入力される信号を反転した信号が入力される。入力401および405が当該レベルシフタ回路の入力となる。 20

**【0005】**

入力405に入力される信号は、入力401に入力される信号を、インバータ等を用いて反転して生成した信号を用いればよい。

**【0006】**

図示しない電源が設けられており、同じ電源から電位が供給される電源入力部には同じ符号を付した。第1の電源（図示しない）からVDH電位が供給される電源入力部402には、P型トランジスタ408のソースおよびP型トランジスタ411のソースに接続されている。また、P型トランジスタ408のドレインはP型トランジスタ407のソースと接続され、P型トランジスタ407のドレインはN型トランジスタ406のドレインと接続され、N型トランジスタ406のソースは、第2の電源（図示しない）からGND電位が供給される電源入力部412に接続されている。また、P型トランジスタ411のドレインはP型トランジスタ410のソースと接続され、P型トランジスタ410のドレインはN型トランジスタ409のドレインと接続され、N型トランジスタ409のソースは、電源入力部412と接続されている。 30

**【0007】**

出力403からは、VDH電位をハイレベル、GND電位をローレベルとして当該ハイレベルとローレベルとの間で変化する（以下、VDH電源系と表記）2レベル信号が出力される。また、出力404からは、出力403から出力された信号が反転したVDH電源系の2レベル信号が出力される。出力403および404が当該レベルシフタ回路の出力となる。以上のように、図4のレベルシフタ回路は、VDD電源系の2レベル信号をVDH電源系の2レベル信号に変換して出力する。 40

**【0008】**

なお、レベルシフタ回路は、VDH電位、VDD電位、GND電位の2種類の電位を供給する電源を有する。VDH電位を15V、VDD電位を5V、GND電位を0Vとして、図4のレベルシフタ回路の動作を説明する。また、P型トランジスタのしきい値電圧を-1Vとし、N型トランジスタのしきい値を1Vとする。

**【0009】**

第1の期間において、入力401に入力される信号がハイレベルのとき、N型トランジスタ406およびP型トランジスタ407のゲートにはいずれもVDD電位(5V)が入力される。このとき、N型トランジスタ406がオンすることでP型トランジスタ411のゲートにはGND電位(0V)が入力され、P型トランジスタ411がオンする。出力403にはGND電位(0V)に出力される。

#### 【0010】

一方、入力405には、入力401に入力された信号の反転信号が入力されるのでローレベルとなり、N型トランジスタ409およびP型トランジスタ410のゲートにはいずれもGND電位(0V)が入力される。このとき、P型トランジスタ410がオンし、P型トランジスタ411は前述のとおりオンしているので、P型トランジスタ408のゲートにはVDH電位(15V)が入力されてオフする。出力404にはVDH電位(15V)に出力される。

#### 【0011】

第1の期間に連続する第2の期間において、入力401に入力されている信号がハイレベルからローレベルへと変化する。この過渡期においては、入力401の電位がハイレベルとローレベルの中間付近の電位となる期間が少なくとも存在する。前述したN型トランジスタ、P型トランジスタのしきい値の条件を考慮すると、入力401に入力されている信号の切り替わりの際、その電位が1Vから4Vの間にあるとき、N型トランジスタ406、P型トランジスタ407がいずれもしきい値を上回ってオンする。一方、入力405側においても同様の現象が生じ、N型トランジスタ409、P型トランジスタ410がいずれもオンする。このとき、P型トランジスタ411は、第1の期間においてオンしており、そのゲート電位は上昇しようとして、P型トランジスタ408は、第1の期間においてオフしており、そのゲート電位は下降しようとする。よって、少なくともN型トランジスタ409、P型トランジスタ410、P型トランジスタ411がいずれもオンしている期間が生ずるため、VDH電位とGND電位間に貫通電流が生ずる。

#### 【0012】

続いて、第2の期間に連続する第3の期間において、入力401に入力されている信号がローレベルからハイレベルへと変化する。この過渡期においては、同様の理由により、N型トランジスタ406、P型トランジスタ407、P型トランジスタ408がいずれもオンしている期間が生じ、VDH電位・GND電位間に貫通電流が生ずる。

#### 【0013】

このように、従来のレベルシフタ回路においては、入力信号のレベルが変化する過渡期において、瞬間的に貫通電流が生じ、この貫通電流は、電圧の高いVDH電源系で生ずるため、結果として消費電力の増大に大きく影響してしまうという問題があった。信号のレベルが変化する過渡期に生ずる貫通電流は、駆動回路で消費される電流に比べればわずかな値ではあるが、同一の構造のレベルシフタ回路が複数設けられている場合には、貫通電流の合計値は無視出来ないものとなる。

#### 【0014】

本発明は、前述の課題を鑑み、信号のレベル変化の過渡期において貫通電流を最小限に出来る構成としたレベルシフタ回路の提供を目的とする。

#### 【課題を解決するための手段】

#### 【0015】

図4に示した従来のレベルシフタ回路において、貫通電流の生ずる原因是、VDH電位とGND電位に直列に設けられたトランジスタが全てオンしてしまう期間が生ずる点にあった。具体的には、P型トランジスタ408がオンしている間に、N型トランジスタ406、P型トランジスタ407のいずれもがオンしてしまう期間、ならびに、P型トランジスタ411がオンしている間に、N型トランジスタ409、P型トランジスタ410のいずれもがオンしてしまう期間が生ずる点にあった。

#### 【0016】

本発明においては、同一の入力信号にてオン・オフ制御を行っていたN型トランジスタ

10

20

30

40

50

406、P型トランジスタ407、あるいはN型トランジスタ409、P型トランジスタ410において、一方がオフ状態からオン状態に移行する際、他方は確実にオフ状態を保証するよう、P型トランジスタ407、410の制御を行う。つまり、N型トランジスタ406、409が、それぞれ入力401、405に入力される信号によって制御されるのに対し、P型トランジスタ407、410は、別の信号を用いて制御し、N型トランジスタ406がオフ状態からオン状態へと変化する前に、P型トランジスタ407をオフさせ、N型トランジスタ409がオフ状態からオン状態へと変化する前に、P型トランジスタ410をオフさせるような構成とする。これにより、所望の入力信号によってレベルシフタ回路が動作する全ての期間を通じ、VDD電位・GND電位間に貫通電流が生ずる期間が現れないように動作させることが可能となる。

10

#### 【発明の効果】

#### 【0017】

以上、詳細に説明したとおり、本発明のレベルシフタ回路は前述の構成を設けることにより、入力信号が切り替わるタイミングに生じていた貫通電流の発生を回避することが可能であり、消費電力の低減に大きく貢献する。

#### 【発明を実施するための最良の形態】

#### 【0018】

本発明の実施形態について詳細に説明する。ただし、本発明は多くの異なる態様にて実施することが可能であり、本発明の主旨およびその技術的範囲から逸脱することなくその形態および詳細を様々に変更し得ることは、当業者にあっては容易に理解される。したがって、本実施形態の記載内容に限定して解釈されるものではない。

20

#### 【0019】

また、本発明において、接続されているとは電気的に接続されていることと同義である。したがって、本発明の構成において、所定の接続関係に加えてその間に電気的な接続を可能とする他の素子（例えばスイッチ、トランジスタ、ダイオード、容量素子、抵抗素子等）が配置されていても良い。

#### 【0020】

スイッチとしては、電流の流れを制御できる素子であれば、電気的なスイッチでも機械的なスイッチでも良く、トランジスタを用いても良いし、ダイオードを用いても良いし、他の論理回路を用いても良い。

30

#### 【0021】

また、本発明において適用可能なトランジスタの種類に限定はなく、非晶質シリコンや多結晶シリコンに代表される非単結晶半導体膜を用いた薄膜トランジスタ（TFT）、半導体基板やSOI（Silicon on Insulator）基板を用いて形成されるMOSトランジスタ、接合型トランジスタ、バイポーラトランジスタ、有機半導体やカーボンナノチューブを用いたトランジスタ、その他のトランジスタを適用することが出来る。また、トランジスタが形成される基板の種類にも限定はなく、単結晶基板、SOI基板、石英、ガラス、樹脂等でなる絶縁基板等を適用することが出来る。

#### 【0022】

#### （実施の形態1）

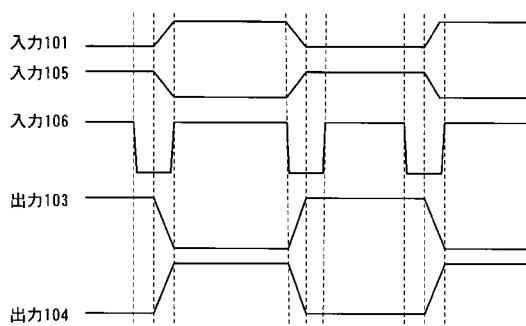

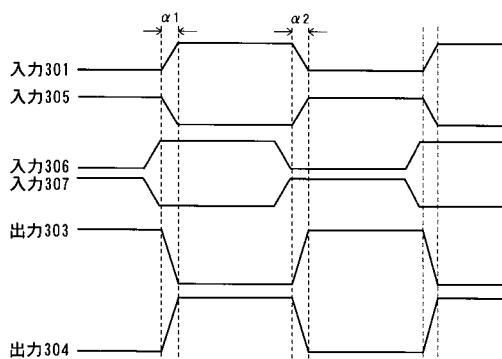

図3(A)に本発明のレベルシフタ回路の一実施形態を示す。同図の回路において、入力301はVDD電源系のハイレベル（例えば5V）とローレベル（例えば0V）との間で変化する2レベル信号が入力され、N型トランジスタ308のゲートに入力される。一方、入力305には入力301の反転信号が入力され、N型トランジスタ311のゲートに入力される。なお、図示しない電源が設けられており、同じ電源から電位が供給される電源入力部には同じ符号を付した。

40

#### 【0023】

第1の電源（図示しない）からVDH電位（例えば15V）が供給される電源入力部302には、P型トランジスタ310のソースおよびP型トランジスタ313のソースに接続されている。また、P型トランジスタ310のドレインはP型トランジスタ309のソ

50

ースと接続され、P型トランジスタ309のドレインはN型トランジスタ308のドレインと接続され、N型トランジスタ308のソースは、第2の電源（図示しない）からGND電位（例えば0V）が供給される電源入力部314に接続されている。また、P型トランジスタ313のドレインはP型トランジスタ312のソースと接続され、P型トランジスタ312のドレインはN型トランジスタ311のドレインと接続され、N型トランジスタ311のソースは第2の電源からGND電位が与えられる電源入力部314と接続されている。

#### 【0024】

入力手段306はP型トランジスタ309のゲートに入力される信号を出力する。入力手段306が出力する信号として、P型トランジスタ309のオン、オフが確実に選択出来る信号を必要とする。例えば、VDD電源系のハイレベル（例えば15V）とローレベル（例えば0V）との間で変化する2レベル信号である。10

#### 【0025】

入力手段307はP型トランジスタ312のゲートに入力される信号を出力する。入力手段307が出力する信号としては、入力手段306が出力する信号と同様、P型トランジスタのオン、オフが確実に選択出来る信号を必要とする。

#### 【0026】

出力303、304がレベルシフタ回路の出力であり、それぞれVDD電源系の2レベル信号が出力される。出力304からは、出力303から出力される信号が反転した信号が出力される。このように、図3(A)に示したレベルシフタ回路は、VDD電源系の2レベル信号をVDD電源系の2レベル信号に変換して出力する。20

#### 【0027】

図3(B)のタイミングチャートを用いて、図3(A)のレベルシフタ回路の動作を説明する。入力301に入力される信号がハイレベル(5V)であると、N型トランジスタ308がオンする。このとき、入力手段306が出力する信号はハイレベル(15V)であり、P型トランジスタ309はオフしている。よって、P型トランジスタ313のゲートにはローレベル(0V)が入力されてオンし、出力303にはGND電位(0V)に出力される。一方、入力305に入力される信号はローレベル(0V)であり、N型トランジスタ311はオフする。このとき、入力手段307が出力する信号はローレベル(0V)であり、P型トランジスタ312はオンしている。前述のとおり、P型トランジスタ313はオンしているので、P型トランジスタ310のゲートにはハイレベルが入力されてオフし、出力304にはVDD電位(15V)に出力される。30

#### 【0028】

入力301に入力される信号がローレベル(0V)のとき、入力305に入力される信号はハイレベル(5V)であり、前述と同様の動作によって、今度は出力303にはVDD電位(15V)が、出力304にはGND電位(0V)に出力される。

#### 【0029】

ここで、図3(B)を用いて、入力301に入力された信号がローレベルからハイレベルに変化する（図3(B)中、1と表記した期間）場合を考える。図4に示した従来のレベルシフタ回路においては、この過渡期において貫通電流が生じた。一方、図3(A)に示す本発明のレベルシフタ回路においては、入力301に入力された信号がローレベルからハイレベルに変化し、N型トランジスタ308のゲート電位が上昇してオンする前に、入力手段306はP型トランジスタ309をオフさせるように、ハイレベルの信号を入力する。つまり、入力301に入力される信号がローレベルからハイレベルに変化する過渡期において、P型トランジスタ310がオンしていたとしても、N型トランジスタ308がオンする前にP型トランジスタ309をオフさせることで、貫通電流の生ずる経路を遮断することが出来る。40

#### 【0030】

一方、入力301に入力された信号がハイレベルからローレベルに変化する（図3(B)中、2と表記した期間）場合を考える。このとき、入力305に入力された信号がロ50

一レベルからハイレベルに変化し、N型トランジスタ311のゲート電位が上昇してオンする前に、入力手段307はP型トランジスタ312をオフさせるように、ハイレベルの信号を入力する。つまり、入力305に入力される信号がローレベルからハイレベルに変化する過渡期において、P型トランジスタ313がオンしていたとしても、N型トランジスタ311がオンする前にP型トランジスタ312をオフさせることで、貫通電流の生ずる経路を遮断することが出来る。

#### 【0031】

なお、入力301に入力される信号と、入力305に入力される信号は、VDD電源系の2レベル信号であり、一方が他方の反転信号となっている。よって、一方をインバータを用いて反転し、他方の入力信号としても良い。

10

#### 【0032】

また、入力手段306、307によって出力される信号は、VDH電源系の2レベル信号であり、図3(B)に示すとおり、入力手段306によって出力される信号がローレベルからハイレベルに変化するタイミングが、入力301に入力される信号がローレベルからハイレベルに変化するタイミングよりも確実に早ければ良く、入力手段307によって出力される信号がローレベルからハイレベルに変化するタイミングが、入力305に入力される信号がローレベルからハイレベルに変化するタイミングよりも確実に早ければ良い。

#### 【0033】

図3(B)によると、入力手段306から出力される信号は、入力301に入力される信号に対して、1、2で示されるだけ位相をずらし、さらにVDH電源系である信号が好適な一例として挙げられる。また、入力手段307から出力される信号は、入力手段306から出力される信号を反転した信号が好適な一例として挙げられる。

20

#### 【0034】

また、図3(B)に1、2で示した期間においては、出力303あるいは304が浮遊状態となりうる期間である。よって、N型トランジスタ308とP型トランジスタ309、あるいはN型トランジスタ311とP型トランジスタ312のオン、オフの順序が前述の条件を満たす範囲で、最小限とするのが好ましい。

#### 【0035】

本発明において、VDD電位、VDH電位、GND電位の値は、レベルシフタ回路の能力や、周辺の駆動回路の構成に応じ、任意に設定すればよい。

30

#### 【0036】

##### (実施の形態2)

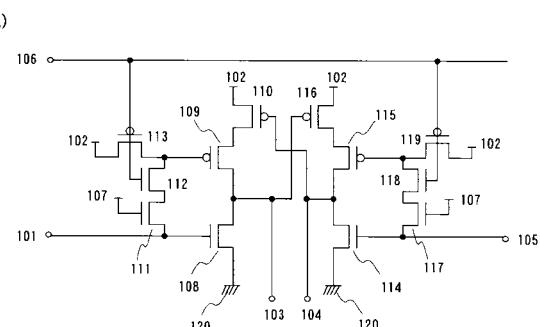

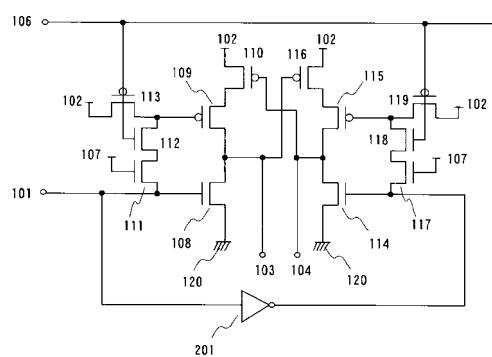

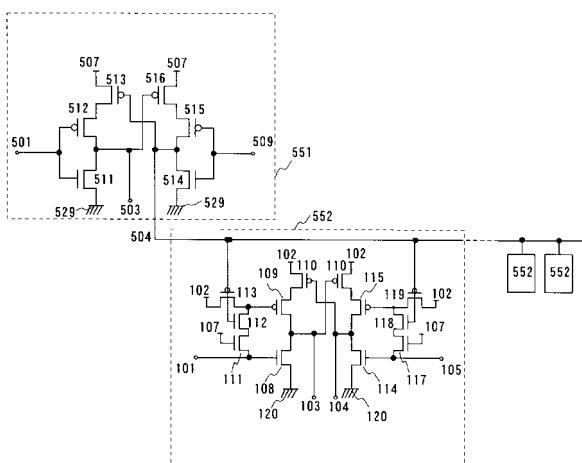

図1に、本発明のレベルシフタ回路の、他の一実施形態を示す。なお、図示しない電源が設けられており、同じ電源から電位が供給される電源入力部には同じ符号を付した。同図の回路において、入力101はVDD電源系のハイレベル(例えば5V)とローレベル(例えば0V)との間で変化する2レベル信号が入力され、N型トランジスタ108のゲートに入力される。一方、入力105には入力101の反転信号が入力され、N型トランジスタ114のゲートに入力される。

#### 【0037】

40

入力106には、N型トランジスタ112、P型トランジスタ113、N型トランジスタ118、P型トランジスタ119を介して、P型トランジスタ109、115をそれぞれ制御するための、VDH電源系のハイレベル(例えば15V)とローレベル(例えば0V)との間で変化する2レベル信号が入力される。

#### 【0038】

N型トランジスタ111、117のゲートにはそれぞれ、電源入力部107が接続され、第3の電源(図示しない)からVDD電位(例えば5V)が供給される。

#### 【0039】

第1の電源(図示しない)からVDH電位(例えば15V)が供給される電源入力部102には、P型トランジスタ110のソースおよびP型トランジスタ116のソースに接

50

続されている。また、P型トランジスタ110のドレインはP型トランジスタ109のソースと接続され、P型トランジスタ109のドレインはN型トランジスタ108のドレインと接続され、N型トランジスタ108のソースは、第2の電源（図示しない）からGND電位（例えば0V）が供給される電源入力部120に接続されている。また、P型トランジスタ116のドレインはP型トランジスタ115のソースと接続され、P型トランジスタ115のドレインはN型トランジスタ114のドレインと接続され、N型トランジスタ114のソースは第2の電源からGND電位が与えられる電源入力部120と接続されている。

#### 【0040】

N型トランジスタ111、112は直列に接続され、N型トランジスタ111のソースは入力101と接続され、N型トランジスタ112のドレインはP型トランジスタ109のゲートと接続されている。N型トランジスタ112のゲートは入力106と接続されている。P型トランジスタ113のソースは、第1の電源からVDH電位が与えられる電源入力部102と接続されている。P型トランジスタ113のドレインはP型トランジスタ109のゲートと接続され、P型トランジスタ113のゲートは入力106と接続されている。

10

#### 【0041】

N型トランジスタ117、118は直列に接続され、N型トランジスタ117のソースは入力105と接続され、N型トランジスタ118のドレインはP型トランジスタ115のゲートと接続されている。N型トランジスタ118のゲートは入力106と接続されている。P型トランジスタ119のソースは、第1の電源からVDH電位が与えられる電源入力部102と接続されている。P型トランジスタ119のドレインはP型トランジスタ115のゲートと接続され、P型トランジスタ119のゲートは入力106と接続されている。

20

#### 【0042】

出力103からは、VDH電源系の2レベル信号が出力される。また、出力104からは、出力103から出力された信号が反転したVDH電源系の2レベル信号が出力される。出力103および104がレベルシフタ回路の出力となる。このように、図1に示したレベルシフタ回路は、VDD電源系の2レベル信号をVDH電源系の2レベル信号に変換して出力する。

30

#### 【0043】

図1に示したレベルシフタ回路の動作について詳細に説明する。

#### 【0044】

入力101、105がハイレベルあるいはローレベルのいずれかの状態にあるとき、入力106はハイレベルを入力する。

#### 【0045】

入力101がハイレベルであれば、N型トランジスタ108がオンし、出力103にはGND電位に出力される。同時に、P型トランジスタ116がオンする。一方、入力105はこのときローレベルであるので、N型トランジスタ114はオフする。入力106にハイレベルが入力されることにより、P型トランジスタ113、119はいずれもオフする。N型トランジスタ117においては、ソース電位すなわち入力105がローレベルであり、ゲートにはVDD電位が入力されているのでオンする。結果、N型トランジスタ118もオンし、P型トランジスタ115のゲートにはGND電位が入力されてオンする。P型トランジスタ115、116がいずれもオンすることにより、出力104にはVDH電位に出力される。

40

#### 【0046】

一方、入力101がローレベルのとき、その反転信号である入力105がハイレベルであるので、N型トランジスタ114がオンし、出力104にはGND電位に出力される。同時に、P型トランジスタ110がオンする。一方で、N型トランジスタ108はオフする。入力106にハイレベルが入力されることにより、P型トランジスタ113、1

50

19はいずれもオフする。N型トランジスタ111においては、ソース電位すなわち入力101がローレベルであり、ゲートにはVDD電位が入力されているのでオンする。結果、N型トランジスタ112もオンし、P型トランジスタ109のゲートにはGND電位が入力されてオンする。P型トランジスタ109、110がいずれもオンすることにより、出力103にはVDH電位に出力される。

#### 【0047】

続いて、入力101、105に入力される信号が、ハイレベルからローレベル、あるいはローレベルからハイレベルへと変化する期間に關し、図1(B)を参照して説明する。

#### 【0048】

前述の、信号の変化の過渡期を含む期間で、入力106に入力される信号をローレベルとする。具体的には、入力101、105に入力される信号が変化を始める前に、入力106に入力される信号をローレベルとし、入力101、105に入力される信号の変化が完了し、ハイレベルあるいはローレベルが確定した後、入力106に入力される信号を再びハイレベルとする。入力106に入力される信号をローレベルとすることにより、N型トランジスタ112、118は、N型トランジスタ111、117の状態に関係なくオフし、P型トランジスタ113、119がオンするので、P型トランジスタ109、115のゲートにはいずれもVDH電位が入力され、オフする。

#### 【0049】

この動作により、N型トランジスタ108において、入力101に入力される信号がローレベルからハイレベル、あるいはハイレベルからローレベルに変化する過渡期には、確実にP型トランジスタ109がオフし、一方で入力105に入力される信号がローレベルからハイレベル、あるいはハイレベルからローレベルに変化する過渡期には、確実にP型トランジスタ115がオフしていることになる。よって、前述のとおり、貫通電流が生ずる経路を遮断することが出来る。

#### 【0050】

なお、図1における入力101、105は、一方が他方の反転信号となっている。ここでも、図2に示したように、インバータ201を用いて入力101の信号を反転し、N型トランジスタ114のゲートに供給しても良い。

#### 【実施例1】

#### 【0051】

実施例1では図1に示した本発明のレベルシフタ回路を用いて、複数の配線にレベルシフトさせた信号を出力する駆動回路を構成した例について説明する。このとき、複数の配線毎にレベルシフタを設ける必要がある。このような駆動回路としては、例えばマトリクス状に配置されたセルの各列(もしくは各行)毎に設けられた配線に信号を出力する駆動回路がある。具体的には、ディスプレイを構成するマトリクス状に配置された複数の画素の各列毎に設けられた信号線にビデオ信号等を出力する信号線駆動回路に適用することができる。また、ディスプレイを構成するマトリクス状に配置された複数の画素の各行毎に設けられた走査線に選択信号等を出力する走査線駆動回路に適用することができる。

#### 【0052】

ここで、駆動回路において、VDH電源系の高い信号レベルの回路(低電圧電源で動作する回路)とVDH電源系の高い信号レベルの回路(高電圧電源で動作する回路)が混在している場合に、これらの回路間で信号のやりとりを行うために信号レベルを変換する役目をするのがレベルシフタ回路である。図1のレベルシフタ回路が信号レベルを変換するためには、入力106に入力される信号はVDH電源系の信号である必要がある。これは、電源入力部102にVDH電位が第1の電源から与えられているため、入力106に入力される信号もVDH電源系の信号でなければ、P型トランジスタ113及びP型トランジスタ119のオン及びオフの切換を正確に制御できないためである。P型トランジスタ113及びP型トランジスタ119のオン及びオフの切換を正確に制御できないと、P型トランジスタ109とP型トランジスタ115のオン及びオフの切換を正確に制御できない。よって、図1のレベルシフタ回路の入力106に入力される信号は、VDD電源系か

10

20

30

40

50

ら VDH 電源系にレベル変換がされていなければならない。

【0053】

図1のレベルシフタ回路において、入力106の入力信号は図4に示すような従来のレベルシフタ回路と同様のレベルシフタ回路を使用して作り出すことが出来る。

【0054】

なお、何十～何千といった多数のレベルシフタ回路を駆動回路内に設ける必要がある場合において、当該レベルシフタ回路として図1を参照して説明した本発明のレベルシフタ回路を使用することにより、図4を参照して説明した従来のレベルシフタ回路を使用する場合に比べ、貫通電流を制御することが可能となり消費電力を低減することが出来る。

【0055】

この場合、多数の図1のレベルシフタ回路の入力106の入力信号を生成するために、図4に示す従来のレベルシフタ回路と同様のレベルシフタ回路を1個だけ使用したとしても、本発明の有効性が失われる訳ではない。

【0056】

特に、ディスプレイの信号線の本数や走査線の本数は画素が多くなるほど多くなる。そのため、これら複数の信号線や複数の走査線に対応した複数のレベルシフタ回路を必要とするディスプレイの駆動回路において、本発明は特に有効である。

【0057】

図5に複数の配線にレベルシフトさせた信号を出力する駆動回路を構成した例を示す。

【0058】

図5の駆動回路は、第1のレベルシフタ回路551と複数の第2のレベルシフタ回路552とを有する。また、図示しない電源が設けられており、同じ電源から電位が供給される電源入力部には同じ符号を付した。

【0059】

第1のレベルシフタ回路551は、図4で示したレベルシフタ回路の構成と同様である。第1のレベルシフタ回路551は、入力501には VDD 電源系の 2 レベル信号が入力される。入力501が第1のレベルシフタ回路551の入力となる。VDD 電源系の 2 レベル信号を P 型トランジスタ512のゲートと N 型トランジスタ511のゲートに入力する。電源入力部507には、第1の電源(図示しない)から VDH 電位が供給される。電源入力部507は P 型トランジスタ513のソース及び P 型トランジスタ516のソースに接続されている。

【0060】

入力509は、入力501の入力信号の反転信号が入力され、P型トランジスタ515のゲートとN型トランジスタ514のゲートに与えられる。特に図示しないが、入力509は、インバータを用いて入力501の信号を反転して生成しても良い。

【0061】

また、P型トランジスタ513のドレインは P 型トランジスタ512のソースと接続されている。P 型トランジスタ512のドレインは N 型トランジスタ511のドレインと接続されている。N 型トランジスタ511のソースは第2の電源(図示しない)から GND 電位が与えられる電源入力部529に接続されている。また、P 型トランジスタ516のドレインは P 型トランジスタ515のソースと接続される。P 型トランジスタ515のドレインは N 型トランジスタ514のドレインと接続されている。N 型トランジスタ514のソースは第2の電源から GND 電位が与えられる電源入力部529と接続されている。

【0062】

出力503からは、VDH 電源系の 2 レベル信号が出力される。また、出力504からは、出力503が反転した VDH 電源系の 2 レベル信号が出力される。出力503及び出力504は第1のレベルシフタ回路551の出力となる。

【0063】

複数の第2のレベルシフタ回路552は、第1のレベルシフタ回路551の出力の1つである出力504に接続されている。複数の第2のレベルシフタ回路552において、図

10

20

30

40

50

1と同じ部分は同じ符号を用いて示し説明は省略する。複数の第2のレベルシフタ回路552において入力106を共通とし、当該入力106は第1のレベルシフタ回路551の出力の1つである出力504と接続される。なお、出力504のかわりに出力503を用いても良い。複数の第2のレベルシフタ回路552各々の入力101にはVDD電源系の2レベル信号が入力される。

#### 【0064】

第1のレベルシフタ回路551と複数の第2のレベルシフタ回路552との動作のタイミングについて説明する。

#### 【0065】

第1のレベルシフタ回路551の出力504の信号がローレベルのとき、複数の第2のレベルシフタ回路552はレベル変換をすることができないので、入力101に入力される信号に関わらず、出力103はローレベルである。

#### 【0066】

出力504がローレベルからハイレベルに切りかわった後、わずかに遅れて第2のレベルシフタ回路552の入力101の入力信号をハイレベルとする。このとき、第2のレベルシフタ回路のP型トランジスタ109及びP型トランジスタ115はオフとなっているので、貫通電流の経路は遮断され流れない。こうして、複数の第2のレベルシフタ回路552各々の出力103はGND電位(0V)を出力し、出力104はVDH電位を出力する。また、入力101がローレベルのときは、出力103はVDH電位を出力し、出力104はGND電位(0V)を出力する。

#### 【0067】

以上の構成によって、複数の第2のレベルシフタ回路552の出力103から出力される信号または出力104から出力される信号を複数の配線に出力することができる。よって、図5に示す駆動回路は、入力されたVDD電源系の2レベル信号をVDH電源系の2レベル信号に変換して複数の配線に出力することができる。図5に示す駆動回路では、当該駆動回路が複数有するレベルシフタ回路の貫通電流を低減することが出来、駆動回路の消費電力を低減することが可能である。

#### 【0068】

本実施例は、発明を実施するための最良の形態と自由に組み合わせて実施することができる。

#### 【実施例2】

#### 【0069】

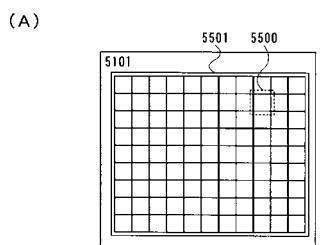

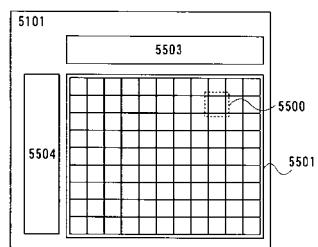

本発明のレベルシフタ回路をディスプレイの駆動回路として用いることができる。ディスプレイは複数の画素を有する。本実施例では、複数の画素が形成されたパネルについて説明する。説明には図6を用いる。図6(A)において、パネル5101は、マトリクス状に配置された複数の画素5500よりなる画素部5501を有する。画素部5501は、画素5500毎に薄膜トランジスタ等のスイッチング素子を配置したアクティブマトリクス方式の構成とすることができます。画素5500の表示素子として、エレクトロルミネッセンス素子等の発光素子を設けても良いし、液晶素子を設けても良い。

#### 【0070】

なお、図6(B)に示すように、画素部5501が形成された基板と同じ基板上に画素部5501を駆動する駆動回路を設けても良い。図6(B)において図6(A)と同じ部分は同じ符号を用いて示し説明は省略する。図6(B)では、駆動回路として信号線駆動回路5503及び走査線駆動回路5504を示した。なおこれに限定されず、信号線駆動回路5503、走査線駆動回路5504の他に更に駆動回路を設けても良い。駆動回路は、別基板上に形成された画素部5501が形成された基板上に実装されていても良い。また、駆動回路は、画素部5501が形成された基板と同一基板上に画素5500の有する薄膜トランジスタと同じ工程で形成された薄膜トランジスタを用いて形成されていても良い。薄膜トランジスタのチャネル形成領域は、多結晶半導体で形成されていてもよいし非晶質半導体で形成されていても良い。

10

20

30

40

50

**【0071】**

本実施例は、発明を実施するための最良の形態及び実施例1と自由に組み合わせて実施することが可能である。

**【実施例3】****【0072】**

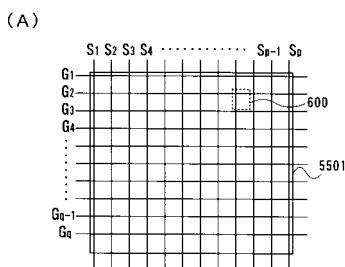

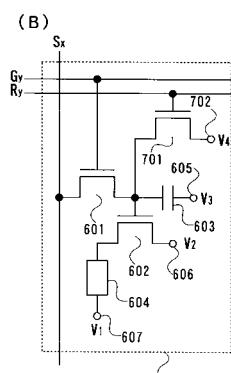

図7(A)に、図6(A)や図6(B)で示した画素部5501の構成例(以下、第1の画素構成という)を示す。画素部5501は、複数の信号線S1～Sp(pは自然数)と、複数の信号線S1～Spと交差するように設けられた複数の走査線G1～Gq(qは自然数)と、信号線S1～Spと走査線G1～Gqの交差部毎に設けられた画素600とを有する。

10

**【0073】**

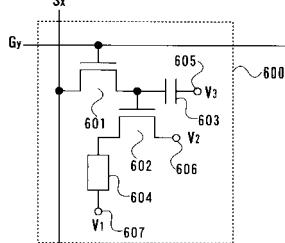

図7(A)の画素600の構成を図7(B)に示す。図7(B)では、複数の信号線S1～Spのうちの1本Sx(xはp以下の自然数)と、複数の走査線G1～Gqのうちの1本Gy(yはq以下の自然数)との交差部に形成された画素600を示す。画素600は、第1のトランジスタ601と、第2のトランジスタ602と、容量素子603と、発光素子604とを有する。なお、本実施の形態では、発光素子604として一対の電極を有し、当該一対の電極間に電流が流れることによって発光する素子を用いた例を示す。また、容量素子603として、第2のトランジスタ602の寄生容量等を積極的に利用してもよい。第1のトランジスタ601及び第2のトランジスタ602は、N型のトランジスタであってもP型のトランジスタであっても良い。画素600を構成するトランジスタとして、薄膜トランジスタを用いることができる。

20

**【0074】**

第1のトランジスタ601のゲートは信号線Sxに接続され、第1のトランジスタ601のソース及びドレインの一方は走査線Gyに接続され、他方は第2のトランジスタ602のゲート及び容量素子603の一方の電極に接続される。容量素子603の他方の電極は、電位V3が与えられる端子605に接続される。第2のトランジスタ602のソース及びドレインの一方は発光素子604の一方の電極に接続され、他方は電位V2が与えられる端子606に接続される。発光素子604の他方の電極は、電位V1が与えられる端子607に接続される。

**【0075】**

30

図7(A)及び図7(B)に示した画素部5501の表示方法について説明する。

**【0076】**

複数の走査線G1～Gqのうち1本を選択し、当該走査線が選択されている間に複数の信号線S1～Sp全てに画像信号を入力する。こうして、画素部5501の1行の画素に画像信号を入力する。複数の走査線G1～Gqを順に選択し同様の動作を行って、画素部5501の全ての画素600に画像信号を入力する。

**【0077】**

複数の走査線G1～Gqのうちの1本Gyが選択され、複数の信号線S1～Spのうちの1本Sxから画像信号が入力された画素600の動作について説明する。走査線Gyが選択されると、第1のトランジスタ601がオン状態となる。トランジスタのオン状態とはソースとドレインが導通状態であることを言い、トランジスタのオフ状態とはソースとドレインが非導通状態であることを言うものとする。第1のトランジスタ601がオン状態となると、信号線Sxに入力された画像信号は、第1のトランジスタ601を介して第2のトランジスタ602のゲートに入力される。第2のトランジスタ602は入力された画像信号に応じてオン状態またはオフ状態を選択される。第2のトランジスタ602のオン状態が選択されると、第2のトランジスタ602のドレイン電流が発光素子604に流れ、発光素子604は発光する。

40

**【0078】**

電位V2と電位V3とは、第2のトランジスタ602がオン状態となった際に電位差が常に一定となるように保たれる。電位V2と電位V3と同じ電位としてもよい。電位V

50

2と電位V3と同じ電位とする場合は、端子605と端子606と同じ配線に接続しても良い。電位V1と電位V2とは、発光素子604の発光を選択された際に所定の電位差を有するように設定される。こうして、発光素子604に電流を流し、発光素子604を発光させる。

#### 【0079】

1フレーム期間に複数のサブフレーム期間を設け、複数のサブフレーム期間各々において上記のとおりに複数の画素各々の発光または非発光を選択してもよい。こうして、1フレーム期間あたりに発光を選択される時間を制御することによって階調を表現してもよい。このような階調表示方式を時分割階調方式と呼ぶ。

#### 【0080】

本実施例は、発明を実施するための最良の形態及び実施例1及び実施例2と自由に組み合わせて実施することが可能である。

#### 【実施例4】

#### 【0081】

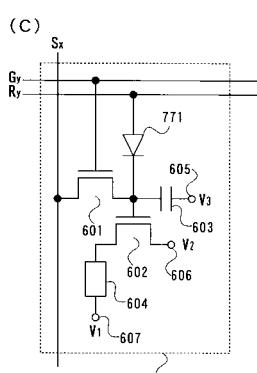

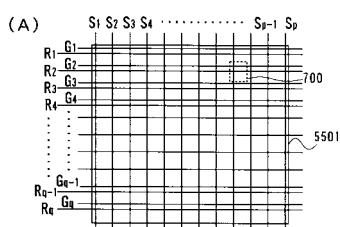

図8(A)に、図6(A)や図6(B)で示した画素部5501の構成例を示す。図8(A)では、実施例3で示した第1の画素構成とは異なる例(以下、第2の画素構成という)を示す。画素部5501は、複数の第1の信号線S1～Sp(pは自然数)と、複数の信号線S1～Spと交差するように設けられた複数の走査線G1～Gq(qは自然数)及び複数の走査線R1～Rqと、信号線S1～Spと走査線G1～Gqの交差部毎に設けられた画素700とを有する。

#### 【0082】

図8(A)の画素700の構成を図8(B)に示す。図8(B)では、複数の信号線S1～Spのうちの1本Sx(xはp以下の自然数)と、複数の走査線G1～Gqのうちの1本Gy(yはq以下の自然数)及び複数の走査線R1～Rqのうちの1本Ryとの交差部に形成された画素700を示す。なお、図8(B)に示す構成の画素において、図7(B)と同じ部分は同じ符号を用いて示し、説明は省略する。図8(B)では、図7(B)で示した画素600において、第3のトランジスタ701とを有する点で異なる。第3のトランジスタ701は、N型のトランジスタであってもP型のトランジスタであっても良い。画素700を構成するトランジスタとして、薄膜トランジスタを用いることができる。

#### 【0083】

第3のトランジスタ701のゲートは走査線Ryに接続され、第3のトランジスタ701のソース及びドレインの一方は第2のトランジスタ602のゲート及び容量素子603の一方の電極に接続され、他方は電位V4が与えられる端子702に接続される。

#### 【0084】

図8(A)及び図8(B)に示した画素部5501の表示方法について説明する。

#### 【0085】

発光素子604を発光させる方法は、実施例3で説明した方法と同じである。図8(A)及び図8(B)で示す構成の画素では、走査線Ry及び第3のトランジスタ701を有することによって、信号線Sxから入力される画像信号に関わらず、画素700の発光素子604を非発光とできる点に特徴がある。走査線Ryに入力される信号によって、画素700の発光素子604が発光する時間を設定することができる。こうして、走査線G1～Gqを順に選択し全ての走査線G1～Gqを選択する期間よりも短い発光期間を設定することができる。こうして、時分割階調方式で表示を行う場合に、短いサブフレーム期間を設定することができるので、高階調を表現することができる。

#### 【0086】

電位V4は、第3のトランジスタ701がオン状態となった際に第2のトランジスタ602がオフ状態となるように設定すれば良い。例えば、第3のトランジスタ701がオン状態となった際に、電位V3と同じ電位になるように電位V4を設定することができる。電位V3と電位V4とを同じ電位とすることによって、容量素子603に保持された電荷

10

20

30

40

50

を放電し、第2のトランジスタ602のソースとゲート間の電圧をゼロとして第2のトランジスタ602をオフ状態とすることができます。なお、電位V3と電位V4と同じ電位とする場合は、端子605と端子702と同じ配線に接続しても良い。

#### 【0087】

なお、第3のトランジスタ701は、図8(B)に示した配置に限定されない。例えば、第2のトランジスタ602と直列に第3のトランジスタ701を配置してもよい。この構成では、走査線Ryに入力される信号により、第3のトランジスタ701をオフ状態にすることによって、発光素子604に流れる電流を遮断し、発光素子604を非発光とすることができます。

#### 【0088】

図8(B)で示した第3のトランジスタ701の代わりにダイオードを用いることもできる。第3のトランジスタ701の代わりにダイオードを用いた画素の構成を図8(C)に示す。なお、図8(C)において図8(B)と同じ部分は同じ符号を用いて示し説明は省略する。ダイオード771の一方の電極は走査線Ryに接続され、他方の電極は第2のトランジスタ602のゲート及び容量素子603の一方の電極に接続されている。

#### 【0089】

ダイオード771は一方の電極から他方の電極に電流を流す。第2のトランジスタ602をP型のトランジスタとする。ダイオード771の一方の電極の電位を上昇させることによって、第2のトランジスタ602のゲートの電位を上昇させ、第2のトランジスタ602をオフ状態とすることができます。

#### 【0090】

図8(C)では、ダイオード771は、走査線Ryに接続された一方の電極から第2のトランジスタ602のゲートに接続された他方の電極に電流を流すとし、第2のトランジスタ602をP型のトランジスタとした構成を示したがこれに限定されない。ダイオード771は、第2のトランジスタ602のゲートに接続された他方の電極から第3の信号線Ryに接続された一方の電極に電流を流すとし、第2のトランジスタ602をN型のトランジスタとした構成としてもよい。第2のトランジスタ602がN型のトランジスタのときは、ダイオード771の一方の電極の電位を下降させることによって、第2のトランジスタ602のゲートの電位を下降させ、第2のトランジスタ602をオフ状態とすることができます。

#### 【0091】

ダイオード771としては、ダイオード接続されたトランジスタを用いてもよい。ダイオード接続されたトランジスタとは、ドレインとゲートが接続されたトランジスタを示すものとする。ダイオード接続されたトランジスタとしては、P型のトランジスタを用いても良いしN型のトランジスタを用いても良い。

#### 【0092】

本実施例は、発明を実施するための最良の形態及び実施例1乃至実施例3と自由に組み合わせて実施することが可能である。

#### 【実施例5】

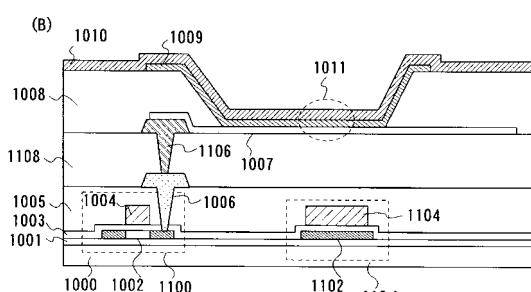

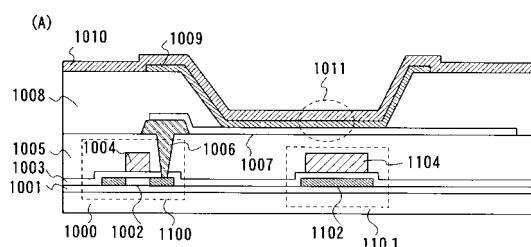

#### 【0093】

本実施例では、画素を実際に作製した例について説明する。図9(A)及び図9(B)は、実施例3及び実施例4で説明したパネルの画素の断面図である。画素に配置されるスイッチング素子としてTFTを用い、画素に配置される表示媒体として発光素子を用いた例を示す。

#### 【0094】

図9(A)及び図9(B)において、1000は基板、1001は下地膜、1002は半導体層、1102は半導体層、1003は第1の絶縁膜、1004はゲート電極、1104は電極、1005は第2の絶縁膜、1006は電極、1007は第1の電極、1008は第3の絶縁膜、1009は発光層、1010は第2の電極である。1100はTFT、1011は発光素子、1101は容量素子である。図9では、画素を構成する素子とし

10

20

30

40

50

て、TFT1100と、容量素子1101とを代表で示した。図9(A)の構成について説明する。

#### 【0095】

基板1000としては、例えばバリウムホウケイ酸ガラスや、アルミニノホウケイ酸ガラスなどのガラス基板、石英基板、セラミック基板等を用いることができる。また、ステンレスを含む金属基板または半導体基板の表面に絶縁膜を形成したものを用いても良い。プラスチック等の可撓性を有する合成樹脂からなる基板を用いても良い。基板1000の表面を、CMP法などの研磨により平坦化しておいても良い。

#### 【0096】

下地膜1001としては、酸化珪素や、窒化珪素または窒化酸化珪素などの絶縁膜を用いることができる。下地膜1001によって、基板1000に含まれるNaなどのアルカリ金属やアルカリ土類金属が半導体層1002に拡散し TFT1100の特性に悪影響をおよぼすのを防ぐことができる。図9では、下地膜1001を単層の構造としているが、2層あるいはそれ以上の複数層で形成してもよい。なお、石英基板など不純物の拡散がさして問題とならない場合は、下地膜1001を必ずしも設ける必要はない。

10

#### 【0097】

半導体層1002及び半導体層1102としては、結晶性半導体膜や非晶質半導体膜を用いて形成することができる。結晶性半導体膜は非晶質半導体膜を結晶化して得ることができる。結晶化方法としては、レーザ結晶化法、RTA又はファーネスアーニール炉を用いる熱結晶化法、結晶化を助長する金属元素を用いる熱結晶化法等を用いることができる。半導体層1002は、チャネル形成領域と、導電型を付与する不純物元素が添加された一対の不純物領域とを有する。なお、チャネル形成領域と一対の不純物領域との間に、前記不純物元素が低濃度で添加された不純物領域を有していてもよい。半導体層1102には、全体に導電型を付与する不純物元素が添加された構成とすることができる。

20

#### 【0098】

第1の絶縁膜1003としては、酸化珪素、窒化珪素または窒化酸化珪素等を用い、単層または複数の膜を積層させて形成することができる。

#### 【0099】

ゲート電極1004及び電極1104としては、Ta、W、Ti、Mo、Al、Cu、Cr、Ndから選ばれた一種の元素または該元素を複数含む合金若しくは化合物からなる単層または積層構造を用いることができる。

30

#### 【0100】

TFT1100は、半導体層1002と、ゲート電極1004と、半導体層1002とゲート電極1004との間の第1の絶縁膜1003とによって構成される。図9では、画素を構成するTFTとして、発光素子1011の第1の電極1007に接続されたTFT1100のみを示したが、複数のTFTを有する構成としてもよい。また、本実施例では、TFT1100をトップゲート型のトランジスタとして示したが、半導体層の下方にゲート電極を有するボトムゲート型のトランジスタであっても良いし、半導体層の上下にゲート電極を有するデュアルゲート型のトランジスタであっても良い。

#### 【0101】

40

容量素子1101は、第1の絶縁膜1003を誘電体とし、第1の絶縁膜1003を挟んで対向する半導体層1102と電極1104とを一対の電極として構成される。なお、図9では、画素の有する容量素子として、一対の電極の一方をTFT1100の半導体層1002と同時に形成される半導体層1102とし、他方の電極をTFT1100のゲート電極1004と同時に形成される電極1104とした例を示したが、この構成に限定されない。

#### 【0102】

第2の絶縁膜1005としては、無機絶縁膜や有機絶縁膜の単層または積層を用いることができる。無機絶縁膜としては、CVD法により形成された酸化シリコン膜や、SOG(Spin On Glass)法により塗布された酸化シリコン膜などを用いることが

50

でき、有機絶縁膜としてはポリイミド、ポリアミド、B C B (ベンゾシクロブテン)、アクリルまたはポジ型感光性有機樹脂、ネガ型感光性有機樹脂等の膜を用いることができる。

### 【0103】

また、第2の絶縁膜1005として、シリコン(Si)と酸素(O)との結合で骨格構造が構成される材料を用いることができる。この材料の置換基として、少なくとも水素を含む有機基(例えばアルキル基、芳香族炭化水素)が用いられる。置換基として、フルオロ基を用いてもよい。または置換基として、少なくとも水素を含む有機基と、フルオロ基とを用いてもよい。

### 【0104】

電極1006としては、Al、Ni、C、W、Mo、Ti、Pt、Cu、Ta、Au、Mnから選ばれた一種の元素または該元素を複数含む合金からなる単層または積層構造を用いることができる。

### 【0105】

第1の電極1007及び第2の電極1010の一方もしくは両方を透明電極とすることができます。透明電極としては、酸化タンゲステンを含むインジウム酸化物(IWO)、酸化タンゲステンを含むインジウム亜鉛酸化物(IWZO)、酸化チタンを含むインジウム酸化物(ITUO)、酸化チタンを含むインジウム錫酸化物(ITTIO)などを用いることができる。勿論、インジウム錫酸化物(ITO)、インジウム亜鉛酸化物(IZO)、酸化ケイ素を添加したインジウム錫酸化物(ITSO)なども用いることができる。

### 【0106】

第1の電極1007及び第2の電極1010の他方は、透光性を有さない材料で形成されていてもよい。例えば、LiやCs等のアルカリ金属、およびMg、Ca、Sr等のアルカリ土類金属、これらを含む合金(Mg:Ag、Al:Li、Mg:Inなど)、およびこれらの化合物(フッ化カルシウム、窒化カルシウム)の他、YbやEr等の希土類金属を用いることができる。

### 【0107】

第3の絶縁膜1008としては、第2の絶縁膜1005と同様の材料を用いて形成することができる。第3の絶縁膜1008は、第1の電極1007の端部を覆うように第1の電極1007の周辺に形成され、隣り合う画素において発光層1009を分離する機能を有する。

### 【0108】

発光層1009は、単数または複数の層で構成されている。発光層は、正孔注入輸送層、発光層、電子注入輸送層など、機能の異なる複数の層を用いて構成することが好ましい。なお各層の境目は必ずしも明確である必要はなく、互いの層を構成している材料が一部混合し、界面が不明瞭になっている場合もある。

### 【0109】

正孔注入輸送層は、ホール輸送性の有機化合物材料と、その有機化合物材料に対して電子受容性を示す無機化合物材料とを含む複合材料で形成することが好ましい。このような構成とすることで、本来内在的なキャリアをほとんど有さない有機化合物に多くのホールキャリアが発生し、極めて優れたホール注入性・輸送性が得られる。この効果により、従来よりも駆動電圧を低くすることができる。また、駆動電圧の上昇を招くことなく正孔注入輸送層を厚くすることができるため、ゴミ等に起因する発光素子の短絡も抑制することができる。

### 【0110】

ホール輸送性の有機化合物材料としては、4,4',4'''-トリス[N-(3-メチルフェニル)-N-フェニルアミノ]トリフェニルアミン(略称:MTDATA)、1,3,5-トリ[N,N-ジ(m-トリル)アミノ]ベンゼン(略称:m-MTDAB)、N,N'-ジフェニル-N,N'-ビス(3-メチルフェニル)-1,1'-ビフェニル-4,4'-ジアミン(略称:TPD)、4,4'-ビス[N-(1-ナフチル)-N-

10

20

30

40

50

フェニルアミノ]ビフェニル(略称:NPB)などが挙げられるが、これらに限定されることはない。

#### 【0111】

電子受容性を示す無機化合物材料としては、酸化チタン、酸化ジルコニウム、酸化バナジウム、酸化モリブデン、酸化タンクス滕、酸化レニウム、酸化ルテニウム、酸化亜鉛などが挙げられる。特に酸化バナジウム、酸化モリブデン、酸化タンクス滕、酸化レニウムは真空蒸着が可能で扱いやすいため、好適である。

#### 【0112】

電子注入輸送層は、電子輸送性の有機化合物材料を用いて形成する。具体的には、トリス(8-キノリノラト)アルミニウム(略称:Alq<sub>3</sub>)、トリス(4-メチル-8-キノリノラト)アルミニウム(略称:Almq<sub>3</sub>)などが挙げられるが、これらに限定されることはない。

#### 【0113】

発光層は、9,10-ジ(2-ナフチル)アントラセン(略称:DNA)、9,10-ジ(2-ナフチル)-2-tert-ブチルアントラセン(略称:t-BuDNA)、4,4'-ビス(2,2-ジフェニルビニル)ビフェニル(略称:DPVBi)、クマリン30、クマリン6、クマリン545、クマリン545T、ペリレン、ルブレン、ペリフランテン、2,5,8,11-テトラ(tert-ブチル)ペリレン(略称:TBP)、9,10-ジフェニルアントラセン(略称:DPA)、5,12-ジフェニルテトラセン、4-(ジシアノメチレン)-2-メチル-[p-(ジメチルアミノ)スチリル]-4H-ピラン(略称:DCM1)、4-(ジシアノメチレン)-2-メチル-6-[2-(ジュロリジン-9-イル)エテニル]-4H-ピラン(略称:DCM2)、4-(ジシアノメチレン)-2,6-ビス[p-(ジメチルアミノ)スチリル]-4H-ピラン(略称:BisDCM)等が挙げられる。また、ビス[2-(4',6'-ジフルオロフェニル)ピリジナト-N,C<sup>2'</sup>]イリジウム(ピコリナート)(略称:FIrpic)、ビス{2-[3',5'-ビス(トリフルオロメチル)フェニル]ピリジナト-N,C<sup>2'</sup>}イリジウム(ピコリナート)(略称:Ir(CF<sub>3</sub>ppy)<sub>2</sub>(pic))、トリス(2-フェニルピリジナト-N,C<sup>2'</sup>)(略称:Ir(ppy)<sub>3</sub>)、ビス(2-フェニルピリジナト-N,C<sup>2'</sup>)イリジウム(アセチルアセトナート)(略称:Ir(ppy)<sub>2</sub>(acac))、ビス[2-(2'-チエニル)ピリジナト-N,C<sup>3'</sup>]イリジウム(アセチルアセトナート)(略称:Ir(thp)<sub>2</sub>(acac))、ビス(2-フェニルキノリナト-N,C<sup>2'</sup>)イリジウム(アセチルアセトナート)(略称:Ir(pq)<sub>2</sub>(acac))、ビス[2-(2'-ベンゾチエニル)ピリジナト-N,C<sup>3'</sup>]イリジウム(アセチルアセトナート)(略称:Ir(btp)<sub>2</sub>(acac))などの熒光を放出できる化合物用いることもできる。

#### 【0114】

その他に、発光層の形成に用いることができる高分子系の電界発光材料は、ポリパラフェニレンビニレン系、ポリパラフェニレン系、ポリチオフェン系、ポリフルオレン系が挙げられる。

#### 【0115】

いずれにしても、発光層の層構造は変化しうるものであり、特定の正孔又は電子注入輸送層や発光層を備えていない代わりに、もっぱらこの目的用の電極層を備えたり、発光性的材料を分散させて備えたりする変形は、発光素子としての目的を達成し得る範囲において許容されうるものである。

#### 【0116】

発光素子1011は、発光層1009と、発光層1009を介して重なる第1の電極1007及び第2の電極1010とによって構成される。第1の電極1007及び第2の電極1010の一方が陽極に相当し、他方が陰極に相当する。発光素子1011は、陽極と陰極の間にしきい値電圧より大きい電圧が順バイアスで印加されると、陽極から陰極に電流が流れて発光する。

**【0117】**

図9(B)の構成について説明する。なお、図9(A)と同じ部分は同じ符号を用いて示し、説明は省略する。

**【0118】**

図9(B)は、図9(A)において、第2の絶縁膜1005と第3の絶縁膜1008の間に絶縁膜1108を有する構成である。電極1006と第1の電極1007とは、絶縁膜1108に設けられたコンタクトホールにおいて、電極1106によって接続されている。

**【0119】**

絶縁膜1108は、第2の絶縁膜1005と同様の構成とすることができます。電極1106は、電極1006と同様の構成とすることができます。10

**【0120】**

本実施例は、発明を実施する最良の形態及び実施例1乃至実施例4と自由に組み合わせて実施することができる。

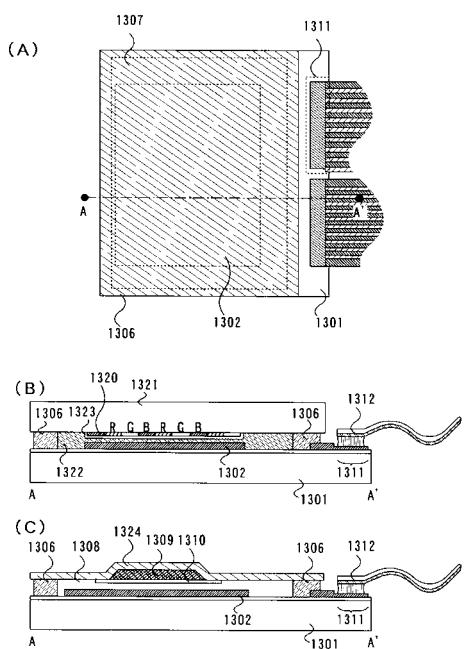

**【実施例6】****【0121】**

本実施例では、画素の形成された基板の封止を行った構成について、図10を用いて説明する。図10(A)は、画素の形成された基板を封止することによって形成されたパネルの上面図であり、図10(B)、図10(C)はそれぞれ図10(A)のA-A'における断面図である。図10(B)と図10(C)とは、異なる方法で封止を行った例である。20

**【0122】**

図10(A)乃至図10(C)において、基板1301上には、複数の画素を有する画素部1302が配置され、画素部1302を囲むようにしてシール材1306が設けられシーリング材1307が貼り付けられている。画素の構造については、上述の実施例で示した構成を用いることができる。

**【0123】**

図10(B)の表示パネルでは、図10(A)のシーリング材1307は、対向基板1321に相当する。シール材1306を接着層として用いて透明な対向基板1321が貼り付けられ、基板1301、対向基板1321及びシール材1306によって密閉空間1322が形成される。対向基板1321には、カラーフィルタ1320と該カラーフィルタを保護する保護膜1323が設けられる。画素部1302に配置された発光素子から発せられる光は、該カラーフィルタ1320を介して外部に放出される。密閉空間1322は、不活性な樹脂もしくは液体などで充填される。なお、密閉空間1322に充填する樹脂として、吸湿材を分散させた透光性を有する樹脂を用いても良い。また、シール材1306と密閉空間1322に充填される材料とを同一の材料として、対向基板1321の接着と画素部1302の封止とを同時に行っても良い。30

**【0124】**

図10(C)に示した表示パネルでは、図10(A)のシーリング材1307は、シーリング材1324に相当する。シール材1306を接着層として用いてシーリング材1324が貼り付けられ、基板1301、シール材1306及びシーリング材1324によって密閉空間1308が形成される。シーリング材1324には予め凹部の中に吸湿剤1309が設けられ、上記密閉空間1308の内部において、水分や酸素等を吸着して清浄な雰囲気に保ち、発光素子の劣化を抑制する役割を果たす。この凹部は目の細かいメッシュ状のカバー材1310で覆われている。カバー材1310は空気や水分は通すが、吸湿剤1309は通さない。なお、密閉空間1308は、窒素もしくはアルゴン等の希ガスで充填しておけばよく、不活性であれば樹脂もしくは液体で充填することも可能である。40

**【0125】**

基板1301上には、画素部1302等に信号を伝達するための入力端子部1311が設けられ、該入力端子部1311へはFPC(フレキシブルプリントサーキット)50131

2を介して映像信号等の信号が伝達される。入力端子部1311では、基板1301上に形成された配線とFPC1312に設けられた配線とを、導電体を分散させた樹脂（異方性導電樹脂：ACF）を用いて電気的に接続してある。

#### 【0126】

画素部1302が形成された基板1301上に、画素部1302に信号を入力する駆動回路が一体形成されても良い。画素部1302に信号を入力する駆動回路をICチップで形成し、基板1301上にCOG（Chip On Glass）で接続しても良いし、ICチップをTAB（Tape Auto Bonding）やプリント基板を用いて基板1301上に配置しても良い。

#### 【0127】

本実施例は、発明を実施するための最良の形態、実施例1乃至実施例5と自由に組み合わせて実施することができる。

#### 【実施例7】

#### 【0128】

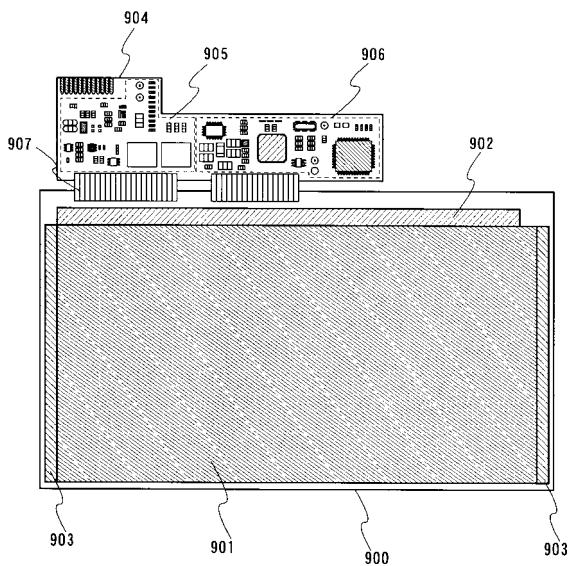

本発明は、パネルに信号を入力する回路を実装した表示モジュールに適用することができる。

#### 【0129】

図11はパネル900と回路基板904を組み合わせた表示モジュールを示している。図11では、回路基板904上にコントローラ905や信号分割回路906などが形成されている例を示した。回路基板904上に形成される回路はこれに限定されない。パネルを制御する信号を生成する回路であればどのような回路が形成されていてもよい。

#### 【0130】

回路基板904上に形成されたこれらの回路から出力された信号は、接続配線907によってパネル900に入力される。

#### 【0131】

パネル900は、画素部901と、信号線駆動回路902と、走査線駆動回路903とを有する。パネル900の構成は、実施例1や実施例2等で示した構成と同様とすることができます。図11では、画素部901が形成された基板と同一基板上に、信号線駆動回路902及び走査線駆動回路903が形成されている例を示した。しかし、本発明の表示モジュールはこれに限定されない。画素部901が形成された基板と同一基板上に走査線駆動回路903のみが形成され、信号線駆動回路は回路基板上に形成されていても良い。信号線駆動回路及び走査線駆動回路の両方が回路基板上に形成されていても良い。

#### 【0132】

このような表示モジュールを組み込んで、様々な電子機器の表示部を形成することができる。

#### 【0133】

本実施例は、発明を実施するための最良の形態、実施例1乃至実施例6と自由に組み合わせて実施することができる。

#### 【実施例8】

#### 【0134】

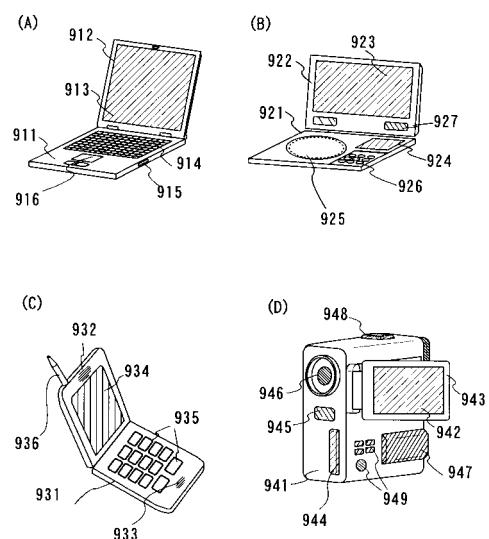

本発明は、様々な電子機器に適用することができる。電子機器としては、カメラ（ビデオカメラ、デジタルカメラ等）、プロジェクター、ヘッドマウントディスプレイ（ゴーグル型ディスプレイ）、ナビゲーションシステム、カーステレオ、パソコンコンピュータ、ゲーム機器、携帯情報端末（モバイルコンピュータ、携帯電話機または電子書籍等）、記録媒体を備えた画像再生装置（具体的にはDigital Versatile Disc（DVD）等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置）などが挙げられる。電子機器の例を図12に示す。

#### 【0135】

図12(A)は、ノート型パソコンコンピュータであり、本体911、筐体912、表示部913、キーボード914、外部接続ポート915、ポインティングマウス916

10

20

30

40

50

等を含む。本発明は、表示部 913 に適用される。本発明を用いることによって、表示部の消費電力を低減することができる。

**【0136】**

図 12 (B) は記録媒体を備えた画像再生装置（具体的には DVD 再生装置）であり、本体 921、筐体 922、第 1 の表示部 923、第 2 の表示部 924、記録媒体（DVD 等）読み込み部 925、操作キー 926、スピーカー部 927 等を含む。第 1 の表示部 923 は主として画像情報を表示し、第 2 の表示部 924 は主として文字情報を表示する。本発明は、第 1 の表示部 923、第 2 の表示部 924 に適用される。本発明を用いることによって、表示部の消費電力を低減することができる。

**【0137】**

図 12 (C) は携帯電話機であり、本体 931、音声出力部 932、音声入力部 933、表示部 934、操作スイッチ 935、アンテナ 936 等を含む。本発明は、表示部 934 に適用される。本発明を用いることによって、表示部の消費電力を低減することができる。

**【0138】**

図 12 (D) はカメラであり、本体 941、表示部 942、筐体 943、外部接続ポート 944、リモコン受信部 945、受像部 946、バッテリー 947、音声入力部 948、操作キー 949 等を含む。本発明は、表示部 942 に適用される。本発明を用いることによって、表示部の消費電力を低減することができる。

**【0139】**

本実施は、発明を実施するための最良の形態、実施例 1 乃至実施例 7 と自由に組み合わせて実施することができる。

**【図面の簡単な説明】**

**【0140】**

【図 1】第 2 の実施の形態を示す回路図。

【図 2】第 2 の実施の形態を示す回路図。

【図 3】第 1 の実施の形態を示す回路図。

【図 4】従来のレベルシフタの回路図。

【図 5】第 1 の実施例を示す回路図。

【図 6】第 2 の実施例を示す図。

30

【図 7】第 3 の実施例を示す図。

【図 8】第 4 の実施例を示す図。

【図 9】第 5 の実施例を示す図。

【図 10】第 6 の実施例を示す図。

【図 11】第 7 の実施例を示す図。

【図 12】第 8 の実施例を示す図。

**【符号の説明】**

**【0141】**

101 入力

40

102 電源入力部

103 出力

104 出力

105 入力

106 入力

107 電源入力部

108 N 型トランジスタ

109 P 型トランジスタ

110 P 型トランジスタ

111 N 型トランジスタ

112 N 型トランジスタ

50

|       |             |    |

|-------|-------------|----|

| 1 1 3 | P型トランジスタ    |    |

| 1 1 4 | N型トランジスタ    |    |

| 1 1 5 | P型トランジスタ    |    |

| 1 1 6 | P型トランジスタ    |    |

| 1 1 7 | N型トランジスタ    |    |

| 1 1 8 | N型トランジスタ    |    |

| 1 1 9 | P型トランジスタ    |    |

| 1 2 0 | 電源入力部       |    |

| 2 0 1 | インバータ       |    |

| 3 0 1 | 入力          | 10 |

| 3 0 2 | 電源入力部       |    |

| 3 0 3 | 出力          |    |

| 3 0 4 | 出力          |    |

| 3 0 5 | 入力          |    |

| 3 0 6 | 入力手段        |    |

| 3 0 7 | 入力手段        |    |

| 3 0 8 | N型トランジスタ    |    |

| 3 0 9 | P型トランジスタ    |    |

| 3 1 0 | P型トランジスタ    |    |

| 3 1 1 | N型トランジスタ    | 20 |

| 3 1 2 | P型トランジスタ    |    |

| 3 1 3 | P型トランジスタ    |    |

| 3 1 4 | 電源入力部       |    |

| 4 0 1 | 入力          |    |

| 4 0 2 | 電源入力部       |    |

| 4 0 3 | 出力          |    |

| 4 0 4 | 出力          |    |

| 4 0 5 | 入力          |    |

| 4 0 6 | N型トランジスタ    |    |

| 4 0 7 | P型トランジスタ    | 30 |

| 4 0 8 | P型トランジスタ    |    |

| 4 0 9 | N型トランジスタ    |    |

| 4 1 0 | P型トランジスタ    |    |

| 4 1 1 | P型トランジスタ    |    |

| 4 1 2 | 電源入力部       |    |

| 5 0 1 | 入力          |    |

| 5 0 3 | 出力          |    |

| 5 0 4 | 出力          |    |

| 5 0 7 | 電源入力部       |    |

| 5 0 9 | 入力          | 40 |

| 5 1 1 | N型トランジスタ    |    |

| 5 1 2 | P型トランジスタ    |    |

| 5 1 3 | P型トランジスタ    |    |

| 5 1 4 | N型トランジスタ    |    |

| 5 1 5 | P型トランジスタ    |    |

| 5 1 6 | P型トランジスタ    |    |

| 5 2 9 | 電源入力部       |    |

| 5 5 1 | 第1のレベルシフタ回路 |    |

| 5 5 2 | 第2のレベルシフタ回路 |    |

| 6 0 0 | 画素          | 50 |

|         |                        |    |

|---------|------------------------|----|

| 6 0 1   | 第 1 のトランジスタ            |    |

| 6 0 2   | 第 2 のトランジスタ            |    |

| 6 0 3   | 容量素子                   |    |

| 6 0 4   | 発光素子                   |    |

| 6 0 5   | 端子                     |    |

| 6 0 6   | 端子                     |    |

| 6 0 7   | 端子                     |    |

| 7 0 0   | 画素                     |    |

| 7 0 1   | 第 3 のトランジスタ            |    |

| 7 0 2   | 端子                     | 10 |

| 7 7 1   | ダイオード                  |    |

| 9 0 0   | パネル                    |    |

| 9 0 1   | 画素部                    |    |

| 9 0 2   | 信号線駆動回路                |    |

| 9 0 3   | 走査線駆動回路                |    |

| 9 0 4   | 回路基板                   |    |

| 9 0 5   | コントローラ                 |    |

| 9 0 6   | 信号分割回路                 |    |

| 9 0 7   | 接続配線                   |    |

| 9 1 1   | 本体                     | 20 |

| 9 1 2   | 筐体                     |    |

| 9 1 3   | 表示部                    |    |

| 9 1 4   | キー ボード                 |    |

| 9 1 5   | 外部接続ポート                |    |

| 9 1 6   | ポインティングマウス             |    |

| 9 2 1   | 本体                     |    |

| 9 2 2   | 筐体                     |    |

| 9 2 3   | 第 1 の表示部               |    |

| 9 2 4   | 第 2 の表示部               |    |

| 9 2 5   | 記録媒体 ( D V D 等 ) 読み込み部 | 30 |

| 9 2 6   | 操作キー                   |    |

| 9 2 7   | スピーカー部                 |    |

| 9 3 1   | 本体                     |    |

| 9 3 2   | 音声出力部                  |    |

| 9 3 3   | 音声入力部                  |    |

| 9 3 4   | 表示部                    |    |

| 9 3 5   | 操作スイッチ                 |    |

| 9 3 6   | アンテナ                   |    |

| 9 4 1   | 本体                     |    |

| 9 4 2   | 表示部                    | 40 |

| 9 4 3   | 筐体                     |    |

| 9 4 4   | 外部接続ポート                |    |

| 9 4 5   | リモコン受信部                |    |

| 9 4 6   | 受像部                    |    |

| 9 4 7   | バッテリー                  |    |

| 9 4 8   | 音声入力部                  |    |

| 9 4 9   | 操作キー                   |    |

| 1 0 0 0 | 基板                     |    |

| 1 0 0 1 | 下地膜                    |    |

| 1 0 0 2 | 半導体層                   | 50 |

|         |          |

|---------|----------|

| 1 0 0 3 | 第 1 の絶縁膜 |

| 1 0 0 4 | ゲート電極    |

| 1 0 0 5 | 第 2 の絶縁膜 |

| 1 0 0 6 | 電極       |

| 1 0 0 7 | 第 1 の電極  |

| 1 0 0 8 | 第 3 の絶縁膜 |

| 1 0 0 9 | 発光層      |

| 1 0 1 0 | 第 2 の電極  |

| 1 0 1 1 | 発光素子     |

| 1 1 0 0 | TFT      |

| 1 1 0 1 | 容量素子     |

| 1 1 0 2 | 半導体層     |

| 1 1 0 4 | 電極       |

| 1 1 0 6 | 電極       |

| 1 1 0 8 | 絶縁膜      |

| 1 3 0 1 | 基板       |

| 1 3 0 2 | 画素部      |

| 1 3 0 6 | シール材     |

| 1 3 0 7 | シーリング材   |

| 1 3 0 8 | 密閉空間     |

| 1 3 0 9 | 吸湿剤      |

| 1 3 1 0 | カバー材     |

| 1 3 1 1 | 入力端子部    |

| 1 3 1 2 | FPC      |

| 1 3 2 0 | カラーフィルタ  |

| 1 3 2 1 | 対向基板     |

| 1 3 2 2 | 密閉空間     |

| 1 3 2 3 | 保護膜      |

| 1 3 2 4 | シーリング材   |

| 5 1 0 1 | パネル      |

| 5 5 0 0 | 画素       |

| 5 5 0 1 | 画素部      |

| 5 5 0 3 | 信号線駆動回路  |

| 5 5 0 4 | 走査線駆動回路  |

【図1】

【図2】

(B)

【 図 3 】

(B)

【 図 4 】

【 図 5 】

【図6】

(B)

【図7】

(B)

【図8】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

(56)参考文献 特開平09-093114(JP,A)

特開2004-343396(JP,A)

特開平04-269011(JP,A)

特開平06-318055(JP,A)

特開平04-253417(JP,A)

特開2001-298356(JP,A)

特開2003-298408(JP,A)

特開2005-354428(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03K19/00, 19/01-19/082, 19/092-19/096