(19) 대한민국특허청(KR)

(12) 공개특허공보(A)

(11) 공개번호 10-2012-0046085

(43) 공개일자 2012년05월09일

(51) 국제특허분류(Int. Cl.)

*H01L 43/02* (2006.01)

(21) 출원번호 10-2011-0112327

(22) 출원일자 2011년10월31일

심사청구일자 2011년10월31일

(30) 우선권주장

12/916,738 2010년11월01일 미국(US)

(71) 출원인

시게이트 테크놀로지 엘엘씨

미국 캘리포니아 95104 쿠퍼티노 사우쓰 디 엔자

블러바드 10200

(72) 발명자

정, 원준

미국 55420 미네소타 블루밍턴 그랜드 애브뉴 사

우쓰 9741 #316

정, 유안카이

미국 94539 캘리포니아 프리몬트 스타 스트리트

43162

가오, 정

미국 95123 캘리포니아 샌어제이 마카티 씨클

5537

(74) 대리인

남상선

전체 청구항 수 : 총 20 항

(54) 발명의 명칭 **수직 이방성 및 향상층을 갖는 자기 터널 접합 셀들**

### (57) 요 약

장자성 자유층; 적어도 약 15 Å의 두께를 갖는 향상층; 산화물 배리어층; 및 장자성 기준층을 포함하는 자기 터널 접합 셀이 제공되며, 여기서 상기 향상층 및 상기 산화물 배리어층은 상기 장자성 기준층과 장자성 자유층 사이에 위치되고, 상기 산화물 배리어층은 상기 장자성 기준층에 인접하게 위치되고, 상기 장자성 자유층, 상기 장자성 기준층, 및 상기 향상층은 모두 평면외에 있는 자화 배향들을 갖는다.

**대 표 도** - 도1a

## 특허청구의 범위

### 청구항 1

자기 터널 접합 셀로서,

장자성 자유층(free layer);

적어도 약 15 Å의 두께를 갖는 향상층(enhancement layer);

산화물 배리어층; 및

장자성 기준층(reference layer)

을 포함하며, 상기 향상층 및 상기 산화물 배리어층은 상기 장자성 기준층과 장자성 자유층 사이에 위치되고,

상기 산화물 배리어층은 상기 장자성 기준층에 인접하게 위치되고,

상기 장자성 자유층, 상기 장자성 기준층, 및 상기 향상층은 모두 평면외(out-of-plane)에 있는 자화 배향들을

갖는, 자기 터널 접합 셀.

### 청구항 2

제1항에 있어서,

상기 향상층은 상기 장자성 자유층에 바로 인접하게 위치되는, 자기 터널 접합 셀.

### 청구항 3

제1항에 있어서,

상기 향상층은 상기 장자성 자유층으로부터 약간 분리되는(slightly decoupled), 자기 터널 접합 셀.

### 청구항 4

제1항에 있어서,

상기 향상층은 적어도 약 20 Å 두께인, 자기 터널 접합 셀.

### 청구항 5

제1항에 있어서,

상기 향상층은 약 15 Å 내지 20 Å 두께인, 자기 터널 접합 셀.

### 청구항 6

제1항에 있어서,

상기 향상층은 NiFe, CoFe, 또는 CoFeB를 포함하는, 자기 터널 접합 셀.

### 청구항 7

제1항에 있어서,

상기 장자성 기준층에 바로 인접한 피닝층(pinning layer)을 더 포함하는, 자기 터널 접합 셀.

### 청구항 8

제1항에 있어서,

상기 장자성 자유층과 상기 향상층 사이에 위치되는 삽입층을 더 포함하는, 자기 터널 접합 셀.

### 청구항 9

제8항에 있어서,

상기 삽입층은 탄탈륨, 루테늄, 크롬, 또는 마그네슘 산화물을 포함하는, 자기 터널 접합 셀.

#### 청구항 10

제1항에 있어서,

상기 강자성 자유층 및 상기 강자성 기준층은,

TbCoFe, GdCoFe, 또는 FePt의 단일층들; 및

Co/PtCo/Ni의 적층된 층들

로부터 선택되는, 자기 터널 접합 셀.

#### 청구항 11

제10항에 있어서,

상기 강자성 자유층 및 상기 강자성 기준층 모두는 약 35 내지 60 원자 퍼센트의 철(Fe) 함량을 갖는 FePt를 포함하는, 자기 터널 접합 셀.

#### 청구항 12

제10항에 있어서,

상기 강자성 자유층 및 상기 강자성 기준층 모두는 약 20 내지 약 35 원자 퍼센트의 테르븀(Tb) 함량 및 약 40 내지 약 75 원자 퍼센트의 철(Fe) 함량을 갖는 TbCoFe를 포함하는, 자기 터널 접합 셀.

#### 청구항 13

소자(device)로서,

강자성 자유층;

적어도 약 15 Å의 두께를 갖는 향상층;

산화물 배리어층; 및

강자성 기준층

을 포함하는 자기 터널 접합 셀 ? 상기 향상층 및 상기 산화물 배리어층은 상기 강자성 기준층과 강자성 자유층 사이에 위치되고, 상기 산화물 배리어층은 상기 강자성 기준층에 인접하게 위치되고, 상기 강자성 자유층, 상기 강자성 기준층, 및 상기 향상층 모두는 평면외에 있는 자화 배향들을 가짐 ? ; 및

트랜지스터 ? 상기 트랜지스터는 상기 자기 터널 접합 셀에 전기적으로 연결됨 ?

를 포함하는, 소자.

#### 청구항 14

제13항에 있어서,

상기 향상층은 상기 강자성 자유층에 바로 인접하게 위치되는, 소자.

#### 청구항 15

제13항에 있어서,

상기 향상층은 적어도 약 20 Å 두께인, 소자.

#### 청구항 16

제13항에 있어서,

상기 향상층은 약 15 Å 내지 20 Å 두께인, 소자.

### 청구항 17

제13항에 있어서,

상기 향상층은 NiFe, CoFe, 또는 CoFeB를 포함하는, 소자.

### 청구항 18

메모리 어레이로서,

다수의 평행 도전성 비트 라인들;

일반적으로 상기 비트 라인들에 직교하는 다수의 평행 도전성 워드 라인들; 및

다수의 자기 터널 접합 셀들

을 포함하며, 각각의 자기 터널 접합 셀은,

강자성 자유층;

적어도 약 15 Å의 두께를 갖는 향상층;

산화물 배리어층; 및

강자성 기준층

을 포함하고, 상기 향상층 및 상기 산화물 배리어층은 상기 강자성 기준층과 강자성 자유층 사이에 위치되고, 상기 산화물 배리어층은 상기 강자성 기준층에 인접하게 위치되고, 상기 강자성 자유층, 상기 강자성 기준층, 및 상기 향상층 모두는 평면외에 있는 자화 배향들을 가지며, 상기 다수의 자기 터널 접합 셀들 각각은 상기 비트 라인들 및 워드 라인들의 교차점들에 배치되는, 메모리 어레이.

### 청구항 19

제18항에 있어서,

상기 향상층은 적어도 약 20 Å 두께인, 메모리 어레이.

### 청구항 20

제18항에 있어서,

상기 향상층은 NiFe, CoFe, 또는 CoFeB를 포함하는, 메모리 어레이.

## 명세서

### 기술분야

[0001] 본 발명은 자기 터널 접합 셀들에 관한 것으로서, 특히, 수직 이방성 및 향상층을 갖는 자기 터널 접합 셀들에 관한 것이다.

### 배경기술

[0002] 새로운 타입들의 메모리는 공통적으로 이용되는 메모리 형태들과 경합할 상당한 가능성을 보여주었다. 예를 들어, 비휘발성 스핀-전달 토크 랜덤 액세스 메모리(본 명세서에서 ST-RAM으로서 지칭됨)는 "범용(universal)" 메모리로서 논의되었다. 자기 터널 접합(MTJ: magnetic tunnel junction) 셀들은 그들의 고속, 상대적 고밀도 및 저전력 소모로 인하여, ST-RAM에서 그들의 애플리케이션에 대하여 많은 주의를 끌었다.

[0003] 대부분의 동작들은 평면내(in-plane) 자기 이방성들을 갖는 MTJ 셀들에 집중되었다. 그러나, 적절한 열적 안정성을 위하여 스위칭 전류가 얼마나 낮을 수 있는지에 대한 제한들이 존재하며, 이는, 궁극적으로 메모리 어레이의 밀도를 제한하는 CMOS 트랜지스터들의 크기를 추가로 제한한다. 또한, 셀 형상 및 에지 조도(roughness)의 매우 낮은 공차(tolerance)가 존재하며, 이는 포토리소그래픽 기술들에서 문제시될 수 있다. 자기 터널 접합

셀 구조들 및 물질들을 향상시키도록 설계되는 기술들, 설계들, 및 변형들은 ST-RAM의 장점들을 최대화하기 위하여 중요한 발전 분야로 남아있다.

### 발명의 내용

[0004] 본 개시물은 흔히 자기 터널 접합 셀들로서 지칭되는 자기 스핀-토크 메모리 셀들과 관련되며, 이는 "평면외에 (out-of-plane)" 또는 웨이퍼 평면에 수직하게 정렬되는 연관된 강자성층들의 자기 이방성들(즉, 자화 배향)을 갖는다.

[0005] 본 개시물의 특정 일 실시예는, 강자성 자유층(free layer); 적어도 약 15 Å의 두께를 갖는 향상층(enhancement layer); 산화물 배리어층; 및 강자성 기준층(reference layer)을 포함하는 자기 터널 접합 셀에 관한 것이며, 여기서 향상층 및 산화물 배리어층은 강자성 기준층과 강자성 자유층 사이에 위치되고, 산화물 배리어층은 강자성 기준층에 인접하게 위치되고, 강자성 자유층, 강자성 기준층, 및 향상층은 모두 평면외에 있는 자화 배향들을 갖는다.

[0006] 본 개시물의 다른 특정 실시예는, 강자성 자유층, 적어도 약 15 Å의 두께를 갖는 향상층, 산화물 배리어층, 및 강자성 기준층을 포함하는 자기 터널 접합 셀? 여기서, 향상층 및 산화물 배리어층은 강자성 기준층과 강자성 자유층 사이에 위치되고, 산화물 배리어층은 강자성 기준층에 인접하게 위치되고, 강자성 자유층, 강자성 기준층, 및 향상층 모두는 평면외에 있는 자화 배향들을 가짐? ; 및 트랜지스터? 트랜지스터는 자기 터널 접합 셀에 전기적으로 연결됨? 를 포함하는 소자에 관한 것이다.

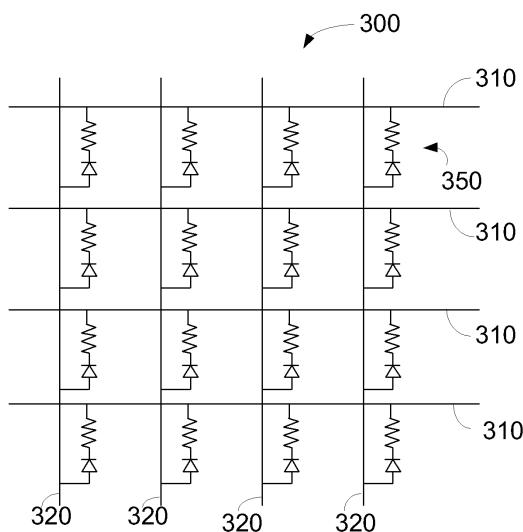

[0007] 본 개시물의 또 다른 특정 실시예는, 다수의 평행 도전성 비트 라인들; 일반적으로 비트 라인들에 직교하는 다수의 평행 도전성 워드 라인들; 및 다수의 자기 터널 접합 셀들을 포함하는, 메모리 어레이에 관한 것이며, 여기서 각각의 자기 터널 접합 셀은, 강자성 자유층; 적어도 약 15 Å의 두께를 갖는 향상층; 산화물 배리어층; 및 강자성 기준층을 포함하고, 향상층 및 산화물 배리어층은 강자성 기준층과 강자성 자유층 사이에 위치되고, 산화물 배리어층은 강자성 기준층에 인접하게 위치되고, 강자성 자유층, 강자성 기준층, 및 향상층 모두는 평면외에 있는 자화 배향들을 가지며, 다수의 자기 터널 접합 셀들 각각은 비트 라인들 및 워드 라인들의 교차지점들에 배치된다.

[0008] 이러한 그리고 다양한 다른 피쳐들 및 장점들이 하기의 상세한 설명의 관독으로부터 명백해질 것이다.

[0009] 개시물은 첨부 도면들과 함께 개시물의 다양한 실시예들에 대한 다음의 상세한 설명을 고려하여 보다 완벽하게 이해될 수 있다.

### 도면의 간단한 설명

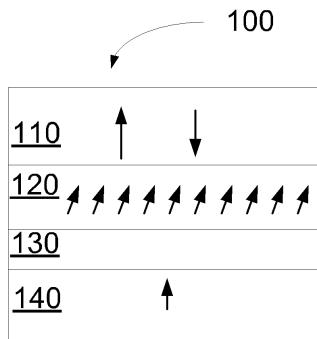

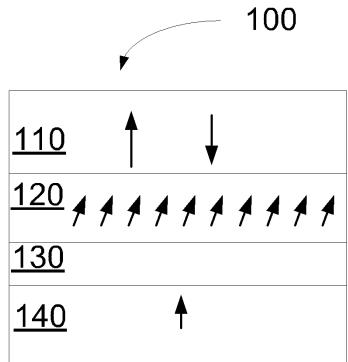

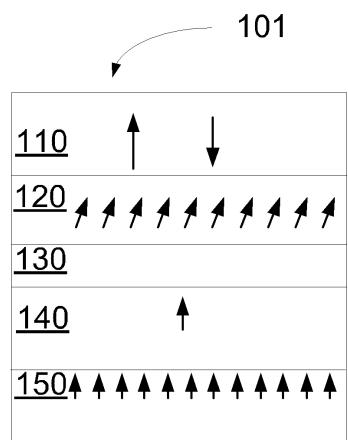

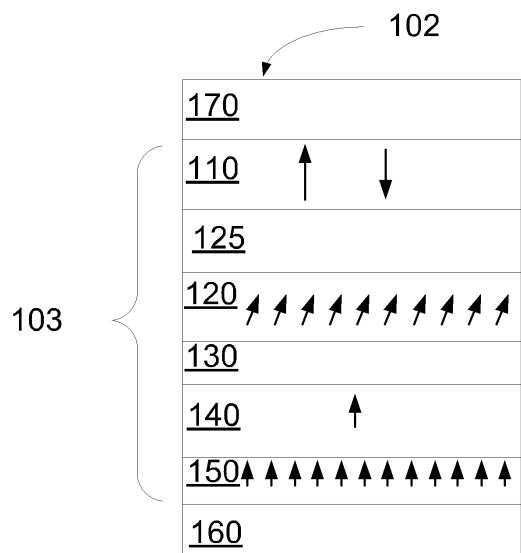

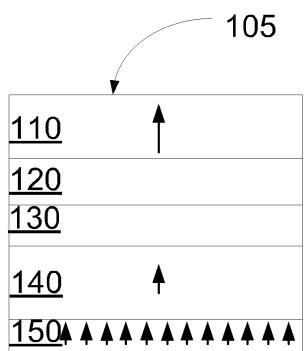

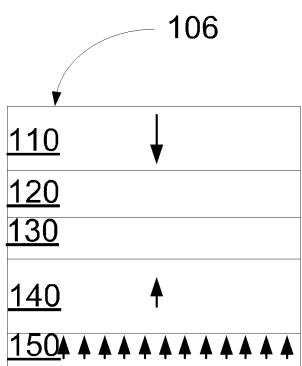

[0010] 도 1a는 예증적 MTJ 셀의 개략도이다; 도 1b는 선택적 피닝층(pinning layer)을 포함하는 예증적 MTJ 셀의 개략도이다; 도 1c는 선택적 향상층과 제1 및 제2 전극들을 포함하는 예증적 MTJ 셀의 개략도이다; 도 1d는 낮은 저항 상태의 평면외 자화 배향을 갖는 예증적 MTJ 셀의 개략도이다; 그리고 도 1e는 높은 저항 상태의 예증적 자기 터널 접합 메모리 셀의 개략적 측면도이다.

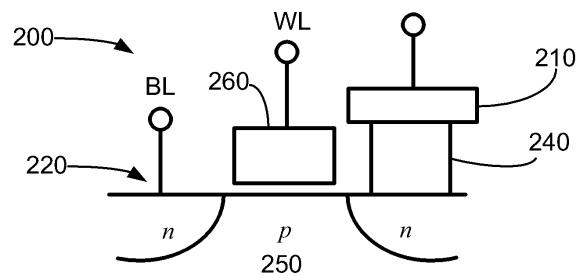

도 2는 메모리 셀 및 반도체 트랜지스터를 포함하는 예증적 메모리 유닛의 개략도이다.

도 3은 예증적 메모리 어레이의 개략도이다.

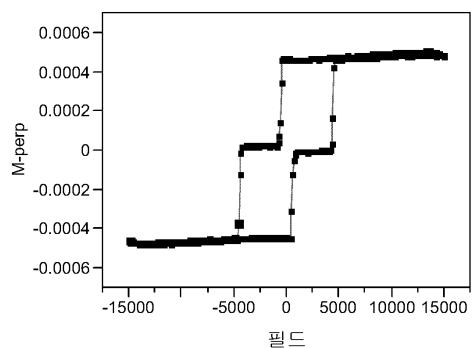

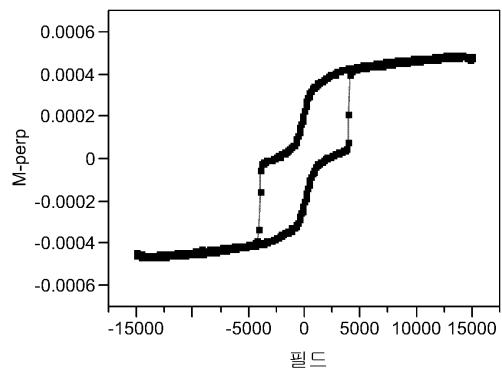

도 4a(10 Å CoFeB 향상층) 및 4b(20 Å CoFeB 향상층)는 0 Å CoFeB 향상층(도 4a) 및 20 Å CoFeB 향상층(도 4b)을 갖는 MTJ 셀에 대한 수직 자기 모멘트 대 인가된 자계의 그래프들이다.

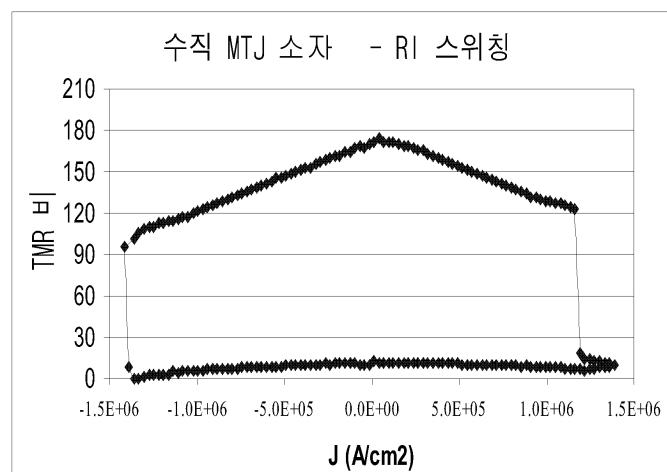

도 5는 20 Å CoFeB 향상층을 갖는 MTJ 셀에 대한 TMR 비 및 스위칭 전류( $A/cm^2$ )를 도시한다.

### 발명을 실시하기 위한 구체적인 내용

[0011] 도면들은 필수적으로 축적에 따르지는 않는다. 도면들에서 사용되는 동일한 번호들은 동일한 컴포넌트들을 지칭한다. 그러나, 주어진 도면에서 컴포넌트를 지칭하기 위한 번호의 사용이 동일한 번호로 라벨 붙여진 다른 도면의 컴포넌트를 제한하도록 의도되는 것은 아님을 이해할 것이다.

[0012] 본 개시물은 연관된 강자성층들의 자화 배향이 "평면외" 또는 웨이퍼 평면에 수직하게 정렬되게 야기시키는 자기 이방성들을 갖는 자기 터널 저합(MTJ) 셀들의 다양한 실시예들에 관련된다.

[0013] 하기의 설명에서, 발명의 일부분을 형성하며 예시로서 다수의 특정 실시예들이 도시되는 도면들의 첨부 세트에 대한 참조가 이루어진다. 본 개시물의 범위 또는 정신을 벗어나지 않고 다른 실시예들이 고려되고 이루어질 수 있다는 것을 이해할 것이다. 따라서 하기의 상세한 설명은 제한의 의미로 취해져서는 안 된다. 본 명세서에 제공되는 임의의 정의들은 본 명세서에 자주 사용되는 특정 용어들의 이해를 용이하게 하기 위한 것이며, 본 발명의 범위를 제한하는 것을 의미하는 것은 아니다.

[0014] 달리 표시되지 않는 한, 명세서 및 청구항들에서 사용되는 피쳐 크기들, 양들, 및 물리적 특성들을 표현하는 모든 숫자들은 "약"이라는 용어에 의하여 모든 예시들에서 변형되는 것으로 이해될 것이다. 따라서, 반대로 표시되지 않는 한, 전술한 설명 및 첨부되는 청구항들에서 진술되는 수치적 파라미터들은 본 명세서에 개시되는 교지들을 이용하는 본 기술분야의 당업자에 의하여 획득되려 하는 원하는 특성들에 따라 변화할 수 있는 근사치들이다.

[0015] 본 명세서 및 첨부된 청구항들에서 사용될 때, 단수 형태들("a", "an", 및 "the")은 내용이 명확하게 다르게 전술되지 않는 한, 다수의 지시대상들을 갖는 실시예들을 포함한다. 본 명세서 및 첨부되는 청구항들에서 사용될 때, "또는"이라는 용어는 일반적으로 내용이 명확하게 다르게 전술되지 않는 한, "및/또는"을 포함하는 의미로 이용된다.

[0016] 본 개시물은 이에 제한되는 것은 아니지만, 개시물의 다양한 양상들의 이해는 하기에 제공되는 실시예들의 논의를 통해 얻어질 것이다.

[0017] 도 1a는 수직 또는 평면외 자기 배향을 갖는 예시적인 MTJ 셀을 예시한다. MTJ 셀(100)은 상대적으로 연성인(soft) 강자성 자유층(110), 강자성 기준(예를 들어, 고정) 층(140)을 포함한다. 강자성 자유층(110) 및 강자성 기준층(140)은 산화물 배리어층(130) 또는 비자성 터널 배리어에 의하여 분리된다. 또한, MTJ 셀(100)은 향상층(120)을 포함한다. 향상층(120)은 산화물 배리어층(130)에 인접하게, 자유층(110)에 인접하게, 또는 산화물 배리어층(130) 및 자유층(110) 모두에 인접하게 위치될 수 있다. MTJ 셀(100)은 또한 향상층으로서 개시될 수 있으며, 산화물 배리어층은 강자성 기준층과 강자성 자유층 사이에 위치되고; 산화물 배리어층은 강자성 기준층에 인접하게 위치된다.

[0018] 자유층(110), 기준층(140), 및 향상층(120) 각각은 연관되는 자화 배향을 갖는다. 층들(110, 120, 및 140)의 자화 배향들은 메모리 셀(100)이 형성되는 웨이퍼 기판의 평면에 대하여 그리고 층 연장부에 대하여 비평행하게 배향된다. 몇몇 실시예들에서, 층들(110, 120, 및 140)의 자화 배향들은 "평면외"로서 지칭될 수 있다. 몇몇 실시예들에서, 층들(110, 120, 및 140)의 자화 배향들은 "수직"일 수 있다. 몇몇 실시예들에서, 층들(110 및 140)의 자화 배향들은 "수직"일 수 있고, 층(120)의 자화 배향은 "평면외"에 있거나 또는 "적어도 실질적으로 수직"일 수 있다. 자유층(110)의 자화 배향은 기준층(140) 및 향상층(120) 모두의 자화 배향보다 더욱 손쉽게 스위칭가능하다. 시드(seed) 또는 캡핑(capping) 층들과 같은 다른 선택적 층들은 명료성을 위하여 이러한 도면들에 도시되지 않는다.

[0019] 자유층(110) 및 기준층(140)은 독립적으로 예를 들어, Fe, Co 또는 Ni와 같은 임의의 유용한 강자성(FM) 물질, 및 NiFe 및 CoFe와 같은 이들의 합금들로 만들어질 수 있다. 자유층(110) 및 기준층(140) 중 하나 또는 둘 모두는 단일층이거나 또는 다중층들일 수 있다. 자유층 및 고정층(fixed layer)으로 만들어질 수 있는 물질들의 특정 실시예들은 TbCoFe, GdCoFe, 및 FePt와 같은 수직 이방성을 갖는 단일층들; Co/Pt Co/N 다중층들과 같은 적층된 층들; 및 Co/Fe 및 CoFeB 합금들과 같은 높은 스핀 분극 강자성 물질들이 적층된 수직 이방성 물질들을 포함할 수 있다.

[0020] 실시예들에서, 적어도 자유층(110)(및 실시예들에서 또한 기준층(140))으로 만들어지는 물질의 조성은 보상 온도들, 수직 이방성 및 인접한 향상층과의 교환 결합(exchange coupling)을 향상시키도록 선택될 수 있다. 적어도 자유층에 대하여 이용될 수 있는 FePt의 예시적인 조성은 35 내지 60 원자 퍼센트 범위인 철(Fe) 함량; 40 내지 65 원자 퍼센트 범위의 백금(Pt) 함량을 가질 수 있다. 적어도 자유층에 대하여 이용될 수 있는 TbCoFe의 예시적인 조성은 20 내지 35 원자 퍼센트 범위인 테르븀(Tb) 함량, 40 내지 75 원자 퍼센트 범위의 철(Fe) 함량; 및 5 내지 40 원자 퍼센트 범위의 코발트(Co) 함량을 가질 수 있다.

[0021] 자유층(110) 및 기준층(140)은 일반적으로 적어도 20 Å의 두께를 가질 수 있다. 실시예들에서, 자유층(110) 및 기준층(140)은 적어도 50 Å의 두께를 가질 수 있다. 실시예들에서, 자유층(110) 및 기준층(140)은 80 Å의 두께를 가질 수 있다. 실시예들에서, 자유층(110) 및 기준층(140)은 80 Å의 두께를 가지고, 예를 들어,

TbCoFe로 만들어질 수 있다.

[0022] 배리어층(130)은 예를 들어, 산화물 물질(예를 들어,  $Al_2O_3$ ,  $TiO_x$  또는  $MgO_x$ ) 또는 반도체 물질과 같은 전기적 절연 물질로 만들어질 수 있다. 배리어층(130)은 단일층일 수 있거나, 또는 다른 산화물 또는 금속(예를 들어,  $Mg/MgO$  이중층)이 적층되는 층일 수 있다. 배리어층(130)은 프로세스 실행가능성 및 소자 신뢰성에 따라, 선택적으로 자유층(110)으로 또는 기준층(140)으로 패터닝될 수 있다.

[0023] 향상층(120)은 자유층(110)에 근접하게 위치될 수 있다. 실시예들에서, 향상층(120)은 자유층(110)에 바로 인접하게 위치될 수 있다. 향상층(120)은 자유층의 스픈 분극을 향상시키도록 기능할 수 있으며, 이는 더 높은 터널링 자기 저항(TMR)을 초래할 수 있다. 개시되는 향상층들(120)은 자유층(110)으로부터 살짝 분리될 수 있다. 이것은 상대적으로 두껍고, (자유층(110)에 관하여) 살짝 기울어진(slightly canted) 자기 모멘트를 갖거나, 또는 이들의 조합된 특성을 갖는 향상층(120)에 의하여 달성될 수 있다. 자유층(110)에 관하여 향상층(120)의 살짝 기울어진 자기 모멘트는 또한 웨이퍼 기판에 대하여 단지 실질적으로 수직한 것으로 특징화될 수 있다.

[0024] 실시예들에서, 향상층(120)은 상대적으로 두꺼울 수 있다. 실시예들에서, 향상층(120)은 적어도 15 옹스트롬(Å) 두께일 수 있다. 실시예들에서, 향상층(120)은 적어도 20 Å 두께일 수 있다. 실시예들에서, 향상층(120)은 15 Å 내지 25 Å 두께일 수 있다. 실시예들에서, 향상층은 18 Å 내지 22 Å 두께일 수 있다. 향상층(120)의 두께, 즉, 적어도 15 Å 두께는 자유층(110)과 향상층(120) 사이의 교환 결합을 약하게 할 수 있으며, 이는 향상층의 자기 모멘트가 다소 기울어지게 한다. 향상층 두께의 이러한 영향력은 도 1a에서 개략도에서 화살표들에 의하여 보여질 수 있으며, 이는 향상층(120)의 자기 모멘트가 자유층(110)의 자기 모멘트로부터 살짝 축에서 벗어난(off axis) 것을 표시한다. 향상층의 기울어진 자기 모멘트는 향상층이 TMR을 여전히 증가시키지만, 동시에 스위칭 전류를 감소시키게 허용한다.

[0025] 향상층(120)은 일반적으로 임의의 강자성 물질들로 만들어질 수 있다. 실시예들에서, 향상층(120)은 높은 스픈 분극을 갖는 강자성 물질로 만들어질 수 있다. 예를 들어, 향상층(120)은 Fe, Co 또는 Ni 및 예를 들어, NiFe, CoFe, 또는 CoFeB 합금들과 같은 이들의 합금들로 만들어질 수 있다. 실시예들에서, 향상층(120)은 20 내지 86 원자 퍼센트의 Co 조성, 10 내지 60 퍼센트의 Fe 조성, 및 4 내지 20 퍼센트의 B 조성을 갖는 CoFeB 합금일 수 있다. 일 실시예에서, 향상층(120)은 CoFeB로 만들어지며, 15 Å 내지 25 Å의 두께를 갖는다.

[0026] 향상층(120)은 또한 선택적으로 임의의 두께를 가질 수 있으나, 자유층의 수직축으로부터 살짝 벗어나는 자기 모멘트로 형성될 수 있다. 이것은 도 1a에 개략적으로 도시된다. 그러한 일 실시예에서, 반드시 향상층의 효과뿐만 아니라, 스위칭 전류 감소를 초래할 수 있는 보다 효율적인 스픈 토크 전달을 가능하게 할 수 있는 향상층 자신의 자기 모멘트가 필수적인 것은 아니다.

[0027] 도 1b는 MTJ 셀의 다른 예시적인 실시예를 예시한다. 이러한 MTJ 셀(101)은 기준층(140)에 근접하게 또는 인접하게 배치되는 선택적 피닝층(150)을 포함한다. 존재한다면, 피닝층(150)은 기준층(140)의 자화 배향을 피닝(pin)한다. 몇몇 실시예들에서, 그러한 피닝층(150)은 제로 자화(zero magnetization)를 가질 수 있으나, 여전히 기준층(140) 자화를 피닝할 수 있다. 존재한다면, 피닝층은 PtMn, IrMn, 및 다른 것들과 같은 반강자성으로 정렬된 물질(AMF)일 수 있다.

[0028] 도 1c는 상기 개시되는 바와 같이 MTJ 셀(103)을 포함하는 예시적인 적층물 또는 소자(102)를 도시한다. 그러한 소자(102)는 강자성 자유층(110)과 전기적으로 접촉하는 제1 전극(170) 및 강자성 기준층(140) 또는 이러한 특정 실시예에서 피닝층(150)과 전기적으로 접촉하는 제2 전극(160)을 포함한다. 전극들(160, 170)은 층들(110, 140)을 통해 판독 및 기록 전류들을 제공하는 제어 회로에 강자성 자유 및 기준 층들(110, 140)을 전기적으로 연결한다. MTJ 셀(103)에 걸친 저항은 강자성 층들(110, 140)의 자화 배향들 또는 자화 백터들의 상대적 배향에 의하여 결정된다. 예시되는 실시예에서, 강자성 기준층(140)의 자화 배향은 피닝층(150)에 의하여 미리 결정된 방향으로 피닝되는 반면, 강자성 자유층(110)의 자화 배향은 스픈 토크의 영향하에서 자유롭게 회전한다.

[0029] 실시예들에서, 도 1c에 개시되는 것과 같이, 자유층(110) 및 향상층(120)은 선택적 삽입층(125)에 의하여 분리될 수 있다. 선택적 삽입층(125)은 배리어 품질을 향상시키고, 층간 결합(interlayer coupling)을 감소시키며, 부식 저항(corrosion resistance)을 향상시키도록 기능하여, 높은 자기저항비를 획득할 수 있다. 삽입층은 금속, 반도체, 또는 절연 물질들로 이루어질 수 있다. 예시적인 물질들은 예를 들어, 탄탈륨(Ta), 루테늄(Ru), 크롬(Cr), 또는 마그네슘 산화물( $MgO$ )을 포함할 수 있다.

[0030] 도 1d는 자기 터널 접합 메모리 셀(105)이 낮은 저항 상태에 있는 것을 보여주며, 여기서 자유층(110)의 자화 배향은 기준층(140)의 자화 배향과 동일한 방향에 있다. 도 1e에서, 자기 터널 접합 셀(106)은 높은 저항 상태에 있으며, 여기서 자유층(110)의 자화 배향은 기준층(140)의 자화 배향과 반대 방향에 있다. 몇몇 실시예들에서, 낮은 저항 상태는 "0" 데이터 상태일 수 있으며, 높은 저항 상태는 "1" 데이터 상태에 있을 수 있는 반면, 다른 실시예들에서, 낮은 저항 상태가 "1"일 수 있고, 높은 저항 상태가 "0"일 수 있다.

[0031] 저항 상태의 스위칭 및 이에 따른 스핀-전달을 통한 자기 터널 접합 메모리 셀(105)의 데이터 상태는, 자기 터널 접합 메모리 셀(105)의 자기층을 통과하는 전류가 스핀 분극되고 자유층(110)상에 스핀 토크를 전달할 때 발생한다. 충분한 스핀 토크가 자유층(110)에 인가될 때, 자유층(110)의 자화 배향은 2개의 대향되는 방향들 사이에서 스위칭될 수 있고, 이에 따라, 자기 터널 접합 메모리 셀(105)은 낮은 저항 상태와 높은 저항 상태 사이에서 스위칭될 수 있다.

[0032] 도 2는 전기적 도전성 엘리먼트(240)를 통해 반도체 기반 트랜지스터와 같은 트랜지스터(220)에 전기적으로 연결되는 메모리 엘리먼트(210)를 포함하는 예증적 메모리 유닛(220)의 개략도이다. 메모리 엘리먼트(210)는 본 명세서에 개시되는 MTJ 셀들 중 임의의 것일 수 있다. 트랜지스터(220)는 도핑된 영역들 사이에서 도핑된 영역들(예를 들어, n-도핑된 영역들로서 예시됨) 및 채널 영역(예를 들어, p-도핑된 채널 영역으로서 예시됨)을 갖는 반도체 기판(250)을 포함한다. 트랜지스터(220)는 비트 라인(BL)으로부터 메모리 엘리먼트(210)로의 흐름을 선택하고 전류가 흐르도록 허용하기 위해 워드 라인(WL)에 전기적으로 연결되는 게이트(260)를 포함한다. 프로그래밍 가능한 금속배선(metallization) 메모리 유닛들(220)의 어레이는 반도체 제작 기술들을 이용하는 반도체 기판상에 형성될 수 있다.

[0033] 도 3은 예증적 메모리 어레이(300)의 개략적 회로도이다. 본 명세서에 개시되는 다수의 메모리 유닛들(350)은 메모리 어레이(300)를 형성하기 위하여 어레이로 정렬될 수 있다. 메모리 어레이(300)는 다수의 평행한 도전성 비트 라인들(310)을 포함한다. 메모리 어레이(300)는 비트 라인들(310)에 일반적으로 직교하는 다수의 평행한 도전성 워드 라인들(320)을 포함한다. 워드 라인들(320) 및 비트 라인들(310)은 각각의 교차점에 메모리 유닛(350)이 배치되는 교차점 어레이를 형성한다. 메모리 유닛(350) 및 메모리 어레이(300)는 종래의 반도체 제작 기술들을 사용하여 형성될 수 있다.

[0034] 본 명세서에 개시되는 바와 같은 MTJ 셀들은 예를 들어, 플라즈마 기상 증착(PVD), 증발, 및 분자 빔 에피택시(MBE)를 포함하는 다양한 기술들을 사용하여 제작될 수 있다.

[0035] 본 명세서에 개시되는 바와 같은 MTJ 셀들은 MRAM 애플리케이션들, 레코딩 헤드들, 및 여전히 열적 안정성 및 제작의 용이성을 필요로 하면서 큰 MR 비율들을 이용하는 임의의 애플리케이션들에서 사용될 수 있다. 그러한 다양한 애플리케이션들은 예를 들어 센서 애플리케이션들 및 오실레이터 애플리케이션들을 포함할 수 있다.

[0036] 80 Å TbCoFe층 및 10 Å CoFeB 향상층을 갖는 MTJ 셀, 및 80 Å TbCoFe층 및 20 Å CoFeB 향상층을 갖는 MTJ 셀의 수직 자기 모멘트가 인가된 자계의 함수로서, 비교된다. 이러한 결과들은 도 4a(10 Å CoFeB 향상층) 및 4b(20 Å CoFeB 향상층)에서 보여질 수 있다. 더 평활한 천이들에 의하여 도시되는 바와 같이, 자유층에 대한 향상층의 결합력은 20 Å CoFeB 향상층을 갖는 MTJ 셀에서와 같이 강하지 않다. 도 4c는 20 Å CoFeB 향상층을 갖는 MTJ 셀에 대한 TMR 비율 및 스위칭 전류( $A/cm^2$ )를 도시한다. 도 5에서 보여지는 바와 같이, 20 Å CoFeB 향상층을 갖는 MTJ 셀은  $35 \Omega/\mu m^2$ 의 RA 곱(product)을 갖는 160%의 MR 비율을 달성하였다. 그러한 MTJ 셀이 MRAM 애플리케이션에서 사용될 때, 임계 스위칭 전류는  $1.5 \times 10^6 A/cm^2$  만큼 낮을 수 있으며, 이는 낮은 에너지 소모 메모리를 제공하기 위하여 매우 유용할 수 있다.

[0037] 본 개시물에서, 수직 자기 이방성을 갖는 자기 터널 접합 셀들의 다양한 구조적 설계들이 제공된다. 설계들 및 패터닝 프로세스들은 적절한 열적 안정성을 갖는 감소된 스위칭 전류를 허용하며, 프로세스 변수들에 대한 증가된 공차를 갖는 높은 영역 밀도를 가능하게 한다.

[0038] 따라서, 수직 이방성 및 향상층을 갖는 자기 터널 접합 셀들의 실시예들이 개시된다. 상기 개시되는 구현들 및 다른 구현들이 하기의 청구항들의 범위 내에 존재한다. 본 기술분야의 당업자는 본 발명이 개시되는 것과 다른 실시예들을 이용하여 실행될 수도 있다는 것을 인지할 것이다. 개시되는 실시예들은 제한이 아닌 예시를 목적으로 제시되며, 본 발명은 하기의 청구항들에 의해서만 제한된다.

도면

도면 1a

도면 1b

## 도면1c

## 도면1d

## 도면1e

도면2

도면3

도면4a

도면4b

도면5