(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4982562号

(P4982562)

(45) 発行日 平成24年7月25日(2012.7.25)

(24) 登録日 平成24年4月27日(2012.4.27)

|                       |                |

|-----------------------|----------------|

| (51) Int.Cl.          | F 1            |

| HO4N 5/378 (2011.01)  | HO4N 5/335 780 |

| HO1L 27/148 (2006.01) | HO1L 27/14 B   |

| HO4N 5/372 (2011.01)  | HO4N 5/335 720 |

| HO4N 5/374 (2011.01)  | HO4N 5/335 740 |

請求項の数 3 (全 14 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2009-520819 (P2009-520819)  |

| (86) (22) 出願日 | 平成19年7月18日 (2007.7.18)        |

| (65) 公表番号     | 特表2009-544230 (P2009-544230A) |

| (43) 公表日      | 平成21年12月10日 (2009.12.10)      |

| (86) 国際出願番号   | PCT/US2007/016280             |

| (87) 国際公開番号   | W02008/011064                 |

| (87) 国際公開日    | 平成20年1月24日 (2008.1.24)        |

| 審査請求日         | 平成22年7月14日 (2010.7.14)        |

| (31) 優先権主張番号  | 11/488,961                    |

| (32) 優先日      | 平成18年7月19日 (2006.7.19)        |

| (33) 優先権主張国   | 米国(US)                        |

|           |                                                                                                       |

|-----------|-------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 510215606<br>オムニヴィジョン テクノロジーズ イン<br>コーポレイテッド<br>アメリカ合衆国 カリフォルニア州 95<br>054 サンタ クララ バートン ドラ<br>イヴ 4275 |

| (74) 代理人  | 110001210<br>特許業務法人 YK1 国際特許事務所                                                                       |

| (72) 発明者  | パークス クリストファー<br>アメリカ合衆国 ニューヨーク ロチェス<br>ター ケンタッキー クロシング 113                                            |

| (72) 発明者  | マッカーテン ジョン ピー<br>アメリカ合衆国 ニューヨーク ペンフィ<br>ールド ティンバーライン ドライブ 1<br>38                                     |

最終頁に続く

(54) 【発明の名称】イメージセンサ

## (57) 【特許請求の範囲】

## 【請求項 1】

イメージセンサであって、

(a) 入射光子を電荷に変換するための複数の画素と、

(b) 少なくとも 1 以上の前記画素からの余剰電荷を排出するオーバーフロードラインと、

(c) 2 以上の前記画素からの電荷を加算するためのメカニズムと、

(d) 直列接続された複数の抵抗素子を含み、第一の基板電圧を生成する第一の抵抗素子ネットワークであって、複数の抵抗素子の少なくとも 1 つは、並列して、伝導リンクまたは開放リンクを有し、当該伝導リンクまたは当該開放リンクは、それぞれ、外的刺激に応答して開放リンクまたは伝導リンクとなり、直列接続された複数の抵抗素子の中間接続点から前記第一の基板電圧を出力する、第一の抵抗素子ネットワークと、 10(e) 複数の抵抗素子を含み、前記第一の抵抗素子ネットワークの前記中間接続点に接続され、第二の基板電圧を生成する第二の抵抗素子ネットワークであって、直列接続された複数の抵抗素子の中間接続点から抵抗分割された電圧を出力することで、前記第二の基板電圧は前記第一の基板電圧の何分の一かである、第二の抵抗素子ネットワークと、

を備えることを特徴とするイメージセンサ。

## 【請求項 2】

請求項 1 に記載のイメージセンサであって、

さらに、複数の追加の抵抗素子ネットワークを備えることを特徴とするイメージセンサ

。

**【請求項 3】**

請求項 1 に記載のイメージセンサであって、

カメラ内に配置されることを特徴とするイメージセンサ。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は一般に、電荷結合素子の分野に関し、より詳しくは、画素加算モードにおける最適なアンチブルーミング保護のために 1 つより多い基板電圧基準を提供することに関する。

10

**【背景技術】****【0002】**

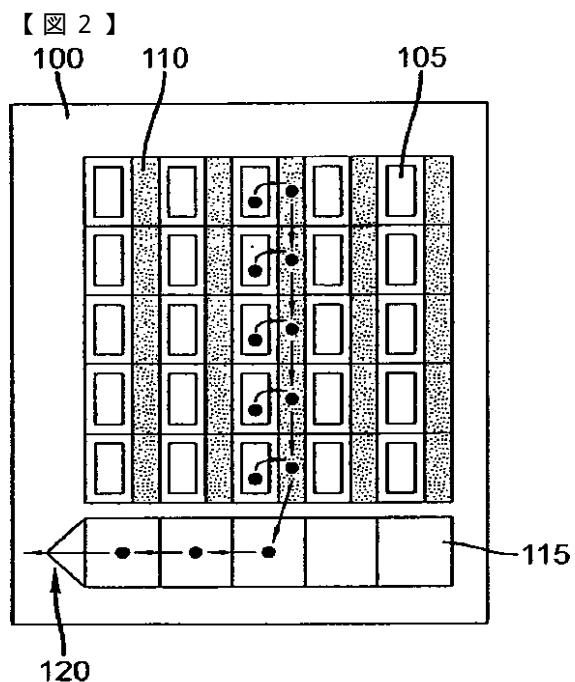

図 2 は、インターライン電荷結合素子 (CCD) 100 を示す。これは、垂直 CCD 110 (VCCD) に接続されたフォトダイオード 105 のアレイを備える。画像読み取りプロセスは、電荷をフォトダイオード 105 から隣接する VCCD 110 に転送することによって始まる。次に、1 度に 1 本のラインずつ水平 CCD (HCCD) 115 に転送される。HCCD は電荷を逐次的に出力電荷感知アンプ 120 に転送する。

**【0003】**

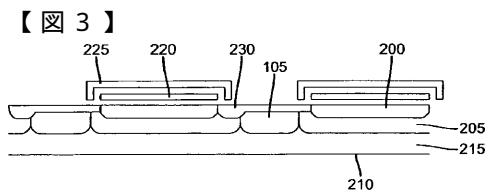

図 3 は、図 2 の中の 1 つのインターライン CCD 画素の断面図である（分かりやすくするために、近隣画素の一部も示されている）。フォトダイオード 105 は、光生成電荷を集め。電荷は、表面ピニング p+ インプラント 230 と垂直オーバーフロードレイン 215 によってフォトダイオード 105 の中に閉じ込められる。フォトダイオード 105 の近隣に、n 型基板 210 の上の p 型ウェル 205 内に構築された、VCCD 埋め込みチャネル 200 がある。VCCD 110 を通じた電荷の転送は、ゲート 220 によって制御される。VCCD 110 は、不透明な金属層 225 によって遮光される。

20

**【0004】**

オーバーフロードレイン 215 は、製造工程可変性の高い、低ドープ領域である。可変性が非常に高いため、基板 210 に印加される電圧は、1 つのイメージセンサと次のイメージセンサとで変化させなければならない。基板電圧は、フォトダイオード 105 の中にどれだけの電荷を保持できるかを制御する。フォトダイオードの電荷容量が大きすぎると、明るい光のスポットにより、VCCD 110 に保持可能な量以上の電荷が生成される。これが VCCD のブルーミングの原因となる。電荷容量が小さすぎると、出力アンプ 120 はまったく飽和状態に到達しない。基板電圧が各イメージセンサについて調整され、アンチブルーミング保護と飽和信号レベルとのバランスが最良になるようにフォトダイオードの電荷容量が最適化される。

30

**【0005】**

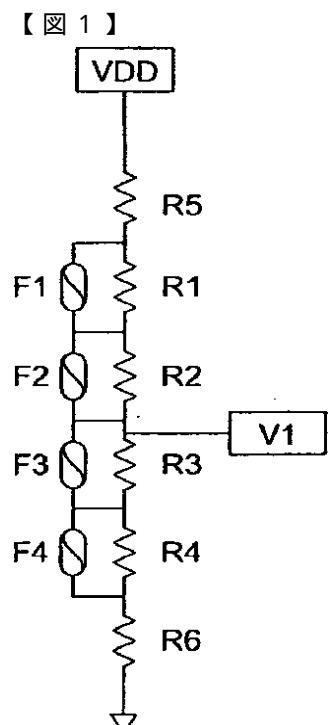

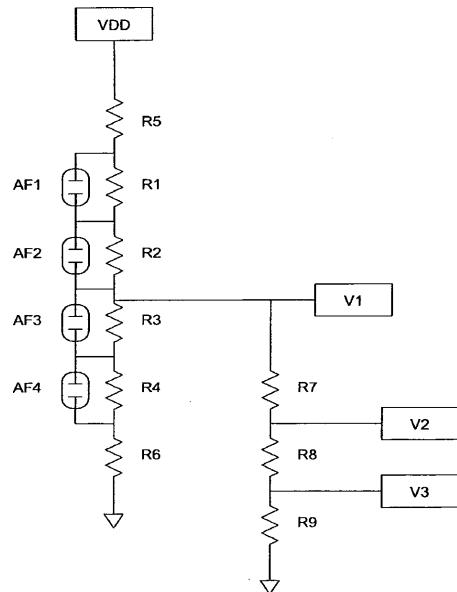

これまで、イメージセンサは基板基準電圧生成回路を備えるように製造してきた。そのような回路の 1 つが図 1 に示される。この回路では、直列抵抗器群 R1 から R4 にわたって 4 つのヒューズ F1 から F4 が備えられている。これらのヒューズのうちの 1 つまたはいくつかが切れることで、16 通りの基準電圧の組み合わせ V1 が発生しうる。そして、この基準電圧が、最適なアンチブルーミングと飽和信号のためにイメージセンサの基板に接続される。

40

**【0006】**

イメージセンサのための上記のような分圧器型ヒューズまたはアンチヒューズ設定回路の例は数多くある。たとえば、特許文献 1、特許文献 2、特許文献 3、特許文献 4、特許文献 5 である。先行技術から、抵抗器の代わりに、ゲートをトランジスタのソースまたはドレインに連結させた MOSFET トランジスタを用いてもよいことが明白である。

**【0007】**

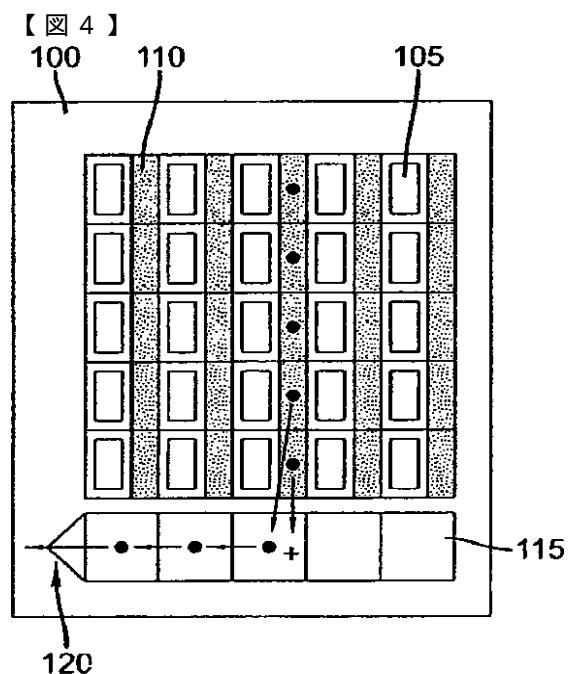

先行技術の 1 つの大きな欠点は、インターライン CCD を使って画素加算を行う場合である。簡単な例を図 4 に示す。図のインターライン CCD 100 では、VCCD 110 か

50

らの 2 行分の電荷が加算されて H C C D 1 1 5 へ送られる。この加算工程により、H C C D 1 1 5 の電荷容量を超過して、水平電荷ブルーミングが発生することがある。また、V C C D 内の画素を加算して、フレームレートを増大させることも可能である。V C C D での画素加算によって、V C C D の電荷容量を超えることがある。画素加算時のV C C D または H C C D のブルーミング防止のための良く知られた解決策は、画素加算モード時に基板電圧をさらに上昇させることである。

【 0 0 0 8 】

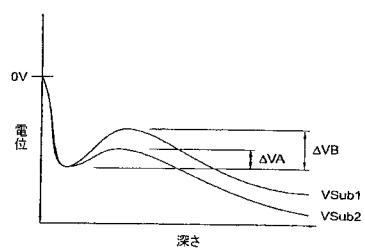

図 5 は、フォトダイオード 1 0 5 のチャネル電位対シリコンウェハ内の深さを示す。表面において、ピニング層 2 3 0 は電位を 0 V に保つ。n 型フォトダイオード 1 0 5 と低ドープオーバーフロードレイン 2 1 5 は、フォトダイオードと基板 2 1 0 の間に電位障壁を形成する。基板電圧が V S u b 1 に設定されたとき、フォトダイオードの容量はより大きい V B となる。イメージセンサが画素加算モードに変わると、基板電圧は V S u b 2 に上昇し、その結果フォトダイオードの電荷容量は V A に減少する。

【 0 0 0 9 】

問題は、第二の基準電圧をどのように発生するか、である。明白な解決策は、図 1 に示されるようなイメージセンサ上に第二の基準電圧発生器全体を設置することである。これは、イメージセンサにさらに多くのヒューズを加えるのに、ヒューズを設定可能にするためのウェハプローブテスト用の余分なボンディングパッドが必要となるため、好ましくない。レーザトリムヒューズを使用した場合でも、ヒューズを追加することにより、センサの製造歩留まりが低下し、ヒューズ設定工程からの細塵が画素アレイを汚染する可能性が高くなる。そこで、ヒューズの数を増やすこと、画素加算イメージセンサのための 1 つより多い基準電圧を供給できる新たな回路が必要である。

【 0 0 1 0 】

【特許文献 1】米国特許第 5 , 1 5 0 , 2 1 6 号明細書

【特許文献 2】米国特許第 5 , 8 6 7 , 0 5 5 号明細書

【特許文献 3】米国特許第 6 , 1 8 8 , 0 9 2 号明細書

【特許文献 4】特開平 6 - 1 5 3 0 7 9 号公報

【特許文献 5】特開 2 0 0 2 - 2 3 1 8 8 9 号公報

【発明の開示】

【課題を解決するための手段】

【 0 0 1 1 】

本発明は、上記の問題の 1 つまたはいくつかを克服することに関する。要約すると、本発明の 1 つの態様によれば、本発明は、

イメージセンサであって、

( a ) 入射光子を電荷に変換するための複数の画素と、

( b ) 少なくとも 1 以上の前記画素からの余剰電荷を排出するオーバーフロードレインと、

( c ) 2 以上の前記画素からの電荷を加算するためのメカニズムと、

( d ) 直列接続された複数の抵抗素子を含み、第一の基板電圧を生成する第一の抵抗素子ネットワークであって、複数の抵抗素子の少なくとも 1 つは、並列して、伝導リンクまたは開放リンクを有し、当該伝導リンクまたは当該開放リンクは、それぞれ、外的刺激に応答して開放リンクまたは伝導リンクとなり、直列接続された複数の抵抗素子の中間接続点から前記第一の基板電圧を出力する、第一の抵抗素子ネットワークと、

( e ) 複数の抵抗素子を含み、前記第一の抵抗素子ネットワークの前記中間接続点に接続され、第二の基板電圧を生成する第二の抵抗素子ネットワークであって、直列接続された複数の抵抗素子の中間接続点から抵抗分割された電圧を出力することで、前記第二の基板電圧は前記第一の基板電圧の何分の一かである、第二の抵抗素子ネットワークと、を備えるイメージセンサである。

【 0 0 1 2 】

本発明の上記およびその他の態様、目的、特徴、利点は、以下に示す好ましい実施例の

10

20

30

40

50

詳細な説明と付属の特許請求範囲を読み、添付の図面を参照することによって、より明確に理解、認識されるであろう。

【発明の効果】

【0013】

本発明は、プログラム可能なヒューズ素子の数を増やすことなく、複数の基板基準電圧を供給できる単純なイメージセンサ基板電圧回路の利益を提供する。

【発明を実施するための最良の形態】

【0014】

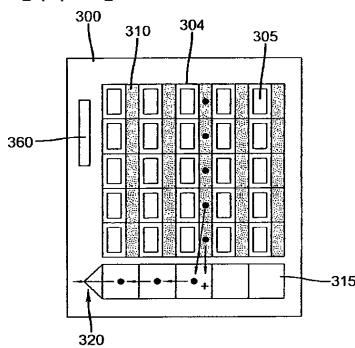

図6は、本発明によるインターラインCCDイメージセンサ300を示し、本発明による基板基準電圧回路360が同じシリコン基板上に集積されている。イメージセンサ300はフォトダイオード305からなる画素アレイ304を有し、画素アレイ304はフォトダイオードから電荷を受け取る垂直CCDシフトレジスタ310に隣接し、入射光(つまり、光子)に応答して電荷を収集する。水平CCDシフトレジスタ315は、垂直CCDシフトレジスタ310から電荷を受け取り、電荷を逐次的に出力電荷感知ノード320に転送する。垂直CCD310は、垂直CCD310内の2つまたはそれ以上のフォトダイオード305からの電荷を加算することができる。

10

【0015】

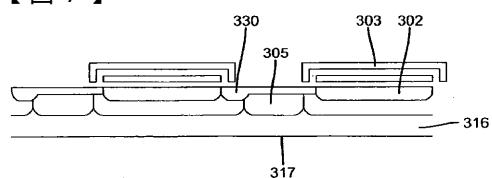

図7は、画素304の中の1つの水平断面図である。これは、n型表面ピニング層330の下でn型基板317の中の低ドープ垂直オーバーフロードレイン316の上にn型フォトダイオード305を備える。不透明な遮光手段303が、CCDシフトレジスタの埋め込まれたチャネル302が感光するのを防止する。これと同等のイメージセンサは、シリコンドーピング極性(n型とp型)のすべてを交換したものでもよい。

20

【0016】

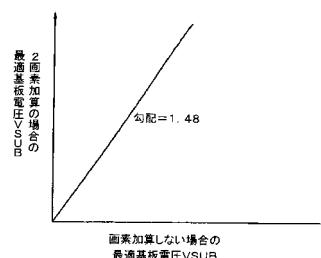

複数の基板電圧について十分に評価するために、各種の電圧基準の間の関係を理解することが有益である。まず、2つのイメージングモードで動作できるイメージセンサを考える。第一のモードは、画素が加算されないフル解像度撮影モードである。第二のモードは、2つの画素を加算し、フレームレートまたは感度を高めるモードである。2画素加算モードのための最適な基板電圧設定は、フォトダイオードの容量が画素加算しないモードのときの約半分になるものであろう。両方のモードの最適な基板電圧に関するデータを収集することにより、2つの電圧が結合されることが明らかとなる。図8は、2画素加算の場合の最適基板電圧と画素加算しない場合の最適基板電圧の間の関係を示す。これは、原点を通る直線である。

30

【0017】

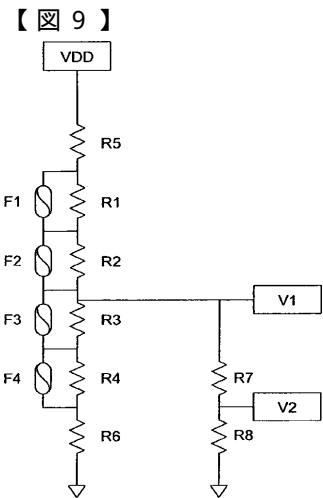

図9は、図8の直線を再現できる第二の電圧V2を生成する回路を示す。ヒューズF1からF4によって設定されるV1とV2の数値として考えられるものは計算可能である。V2は、フル解像度非加算(un-summed)画像のための最適基板電圧であり、V1は2画素加算の場合の最適基板電圧である。

【0018】

VDD電源から流れる電流は、次式により得られる。

【数1】

40

$$i = \frac{VDD}{F_1R_1 + F_2R_2 + \frac{1}{\frac{1}{R_7 + R_8} + \frac{1}{F_3R_3 + F_4R_4 + R_6}}}$$

【0019】

式中、F1からF4は、ヒューズF1からF4が伝導しているか、切れているかに応じて、1または0の数値である。V1とV2の出力電圧は次式により得られる。

【数2】

$$V1 = VDD - i(R_3 + F_1 R_1 + F_2 R_2)$$

【数3】

$$V2 = \frac{R_8}{R_7 + R_8} V1$$

【0020】

以上のように、V1とV2は直線関係にあり、原点を通る。図9の回路は先行技術と同じ数のヒューズを用いるが、画素加算および非画素加算モードのためのまさに正しい数値の2つの基準電圧を供給する。

10

【0021】

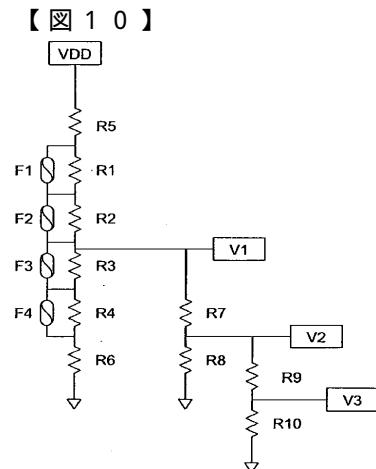

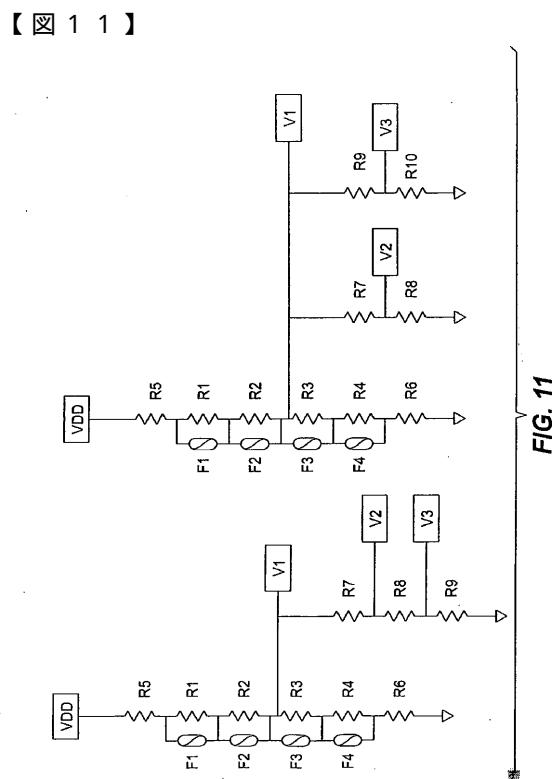

インターラインCCDは、2つだけの画素の加算に限定されない。1つのセンサが複数のレベルの画素加算を行うことも可能である。たとえば、あるイメージセンサがフル解像度の写真を撮影し、さらに2, 4または8画素加算を行うビデオモードを有することがある。類似色の3×3(9画素)のサブアレイを加算するベイヤカラーフィルタパターンを有するカラーイメージセンサのように、奇数の画素加算も可能である。これらの画素加算モードはすべて、1つのイメージセンサについての基準電圧を必要とする。その解決策は、図9の回路を図10に示す回路に拡張することであり、図10の回路では、V2の電圧で動作する別の分圧器が第三の電圧V3を生成する。図11は第三の電圧V3を生成できる、図10の回路の2つの変形を示す。これらの例から、より多くの基板電圧基準を生成するために、無限の数の分圧器を追加する方法が明らかとなるはずである。

20

【0022】

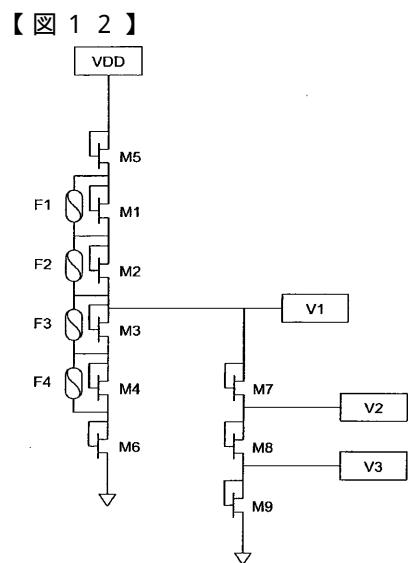

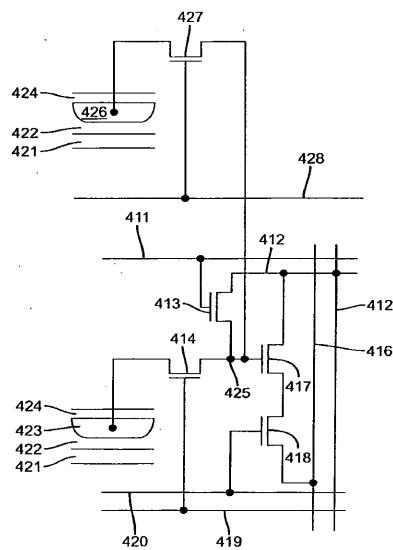

図12の回路によって示されるような電界効果トランジスタ(FET, field effect transistor)を抵抗器の代わりに使用しても同じである。別の変形が図13に示されている。ここでは、アンチヒューズAF1からAF4がヒューズに取って代わっている。ヒューズは、当初は伝導リンクであり、その後、高電流パルスやレーザ切断ビーム等の外的刺激を用いて伝導リンクを開く。アンチヒューズは、当初は開放リンクであり、その後、2つの伝導プレートの間の絶縁層を破壊する高電圧等の外的刺激によって融合する。

30

【0023】

本発明は、CCD型イメージセンサのみに限定されない。CMOS型イメージセンサも本発明の恩恵を受けることができる。図14は、2つのCMOSイメージセンサ画素を示す。各画素について1つのフォトダイオード426, 423がある。フォトダイオードは、表面ピニング層424と垂直オーバーフロードレイン422を有する。フォトダイオード426, 423の電荷容量は、オーバーフロードレイン422の障壁の高さによって調整され、障壁の高さは基板421に印加される電圧によって制御される。フォトダイオード426からの電荷は、信号線428によって制御される転送ゲート427により、共有されるフローティングディフュージョン425に転送される。フォトダイオード423からの電荷は、信号線419によって制御される転送ゲート414により、共有されるフローティングディフュージョン425に転送される。各フォトダイオードの信号電荷は、フローティングディフュージョン425に独立して転送することによって読み出され、あるいは画素加算動作では、両方の転送ゲート414, 427が2つの画素の加算と同時にオンにされる。フローティングディフュージョン425は、信号線411によって制御されるトランジスタ413によってリセットされる。トランジスタ417は、好ましくは、電源線412に接続されるソースフォロワ(source follower)の一部である。トランジスタ418は、信号線420によってオンにされ、ソースフォロワを信号出力線416に接続するための行選択トランジスタである。

40

【0024】

このCMOS画素構造により、2画素加算または非画素加算読取モードが可能となる。これはまた、3または4画素加算オプションも可能になるように拡張できる。画素加算の

50

場合、オーバーフロードレイン基準電圧回路の発明を使用して、画素加算モードの各々のための基準電圧を供給することが好ましい。

【0025】

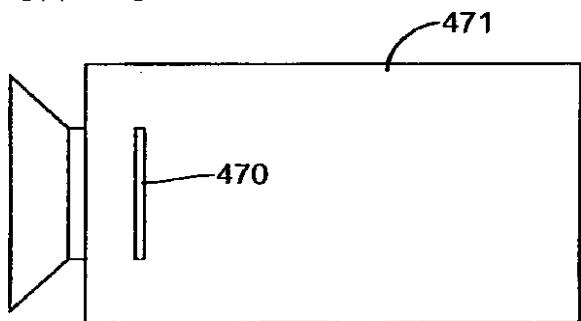

図15は、本発明によるオーバーフロードレイン電圧基準回路を組み込んだイメージセンサ470を用いるカメライメージングシステム471(好ましくは、デジタルカメラ)を示す。本発明により、デジタルカメラシステム471は、フル解像度撮影モードのほか、最適なアンチブルーミング保護と飽和信号レベルを用いたより低解像度の画素加算動画ビデオ撮影モードでの動作が可能となる。なお、以下に、付記として本発明の構成の例を示す。

(付記1)

10

イメージセンサであって、

(a) 入射光子を電荷に変換するための複数の画素と、

(b) 少なくとも1以上の前記画素からの余剰電荷を排出するオーバーフロードレインと、

(c) 2以上の前記画素からの電荷を加算するためのメカニズムと、

(d) 第一のオーバーフロードレイン電圧を生成する第一の抵抗素子ネットワークであって、抵抗素子の少なくとも1つは、外的刺激に応答して、複数の画素が加算されたときの画素アンチブルーミング保護と飽和信号レベルのための最適なオーバーフロードレイン電圧を供給するよう開くことのできるヒューズを並列して有する第一の抵抗素子ネットワークと、

(e) 前記第一の抵抗素子ネットワークに接続され、第二のオーバーフロードレイン電圧を生成する第二の抵抗素子ネットワークであって、第二のオーバーフロードレイン電圧は前記第一のオーバーフロードレイン電圧の何分の一かであり、第二のオーバーフロードレイン電圧は、複数の画素がまったく、またはほとんど加算されない場合の画素アンチブルーミングおよび飽和信号レベルのための最適なオーバーフロードレイン電圧を供給する第二の抵抗素子ネットワークと、

を備えることを特徴とするイメージセンサ。

(付記2)

20

付記1に記載のイメージセンサであって、

さらに、複数の追加の抵抗素子ネットワークを備えることを特徴とするイメージセンサ。

(付記3)

30

付記1に記載のイメージセンサであって、

前記抵抗素子の少なくとも1つは抵抗器であることを特徴とするイメージセンサ。

(付記4)

付記1に記載のイメージセンサであって、

前記抵抗素子の少なくとも1つは電界効果トランジスタであることを特徴とするイメージセンサ。

(付記5)

40

付記1に記載のイメージセンサであって、

前記ヒューズの少なくとも1つの代わりにアンチヒューズを用いることを特徴とするイメージセンサ。

(付記6)

付記1に記載のイメージセンサであって、

前記複数の画素は電荷結合素子を形成することを特徴とするイメージセンサ。

(付記7)

付記1に記載のイメージセンサであって、

前記複数の画素はそれぞれ、電界効果トランジスタのゲートに直接接続されるか、あるいは転送ゲートとフローティングディフュージョンを通じて電界効果トランジスタのゲートに間接的に接続されることを特徴とするイメージセンサ。

50

## (付記 8 )

付記 1 に記載のイメージセンサであって、

加算される複数の画素の数は 2 であることを特徴とするイメージセンサ。

## (付記 9 )

付記 1 に記載のイメージセンサであって、

加算される複数の画素の数は 3 であることを特徴とするイメージセンサ。

## (付記 10 )

付記 1 に記載のイメージセンサであって、

加算される複数の画素の数は 4 であることを特徴とするイメージセンサ。

## (付記 11 )

付記 2 に記載のイメージセンサであって、

前記抵抗素子の少なくとも 1 つは抵抗器であることを特徴とするイメージセンサ。

## (付記 12 )

付記 2 に記載のイメージセンサであって、

前記抵抗素子の少なくとも 1 つは電界効果トランジスタであることを特徴とするイメージセンサ。

## (付記 13 )

付記 2 に記載のイメージセンサであって、

前記ヒューズの少なくとも 1 つの代わりにアンチヒューズが使用されることを特徴とするイメージセンサ。

## (付記 14 )

付記 2 に記載のイメージセンサであって、

前記複数の画素は電荷結合素子を形成することを特徴とするイメージセンサ。

## (付記 15 )

付記 2 に記載のイメージセンサであって、

前記複数の画素はそれぞれ、電界効果トランジスタのゲートに直接接続されるか、あるいは転送ゲートとフローティングディフュージョンを通じて電界効果トランジスタのゲートに間接的に接続されることを特徴とするイメージセンサ。

## (付記 16 )

付記 2 に記載のイメージセンサであって、

加算される複数の画素の数は 2 であることを特徴とするイメージセンサ。

## (付記 17 )

付記 2 に記載のイメージセンサであって、

加算される複数の画素の数は 3 であることを特徴とするイメージセンサ。

## (付記 18 )

付記 2 に記載のイメージセンサであって、

加算される複数の画素の数は 4 であることを特徴とするイメージセンサ。

## (付記 19 )

イメージセンサを備えるカメラであって、

イメージセンサは、

( a ) 入射光子を電荷に変換するための複数の画素と、

( b ) 少なくとも 1 以上の前記画素からの余剰電荷を排出するオーバーフロードレインと、

( c ) 2 以上の前記画素からの電荷を加算するためのメカニズムと、

( d ) 第一のオーバーフロードレイン電圧を生成する第一の抵抗素子ネットワークであって、抵抗素子の少なくとも 1 つは、外的刺激に応答して、複数の画素が加算された場合の画素アンチブルーミング保護と飽和信号レベルのための最適なオーバーフロードレイン電圧を供給するように開くことのできるヒューズを並列して有する第一の抵抗素子ネットワークと、

( e ) 前記第一の抵抗素子ネットワークに接続され、第二のオーバーフロードレイン電

10

20

30

40

50

圧を生成する第二の抵抗素子ネットワークであって、第二のオーバーフロードレイン電圧は前記第一のオーバーフロードレイン電圧の何分の一かであり、第二のオーバーフロードレイン電圧は、複数の画素がまったく、または略まったく加算されない場合の画素アンチブルーミングおよび飽和信号レベルのための最適なオーバーフロードレイン電圧を供給する第二の抵抗素子ネットワークと、

を備えることを特徴とするカメラ。

(付記 20)

付記 19 に記載のカメラであって、

さらに、複数の追加の抵抗素子ネットワークを備えることを特徴とするカメラ。

(付記 21)

10

付記 19 に記載のカメラであって、

前記抵抗素子の少なくとも 1 つは抵抗器であることを特徴とするカメラ。

(付記 22)

付記 19 に記載のカメラであって、

前記抵抗素子の少なくとも 1 つは電界効果トランジスタであることを特徴とするカメラ

。

(付記 23)

付記 19 に記載のカメラであって、

前記ヒューズの少なくとも 1 つの代わりにアンチヒューズが用いられることを特徴とするカメラ。

20

(付記 24)

付記 19 に記載のカメラであって、

前記複数の画素は電荷結合素子を形成することを特徴とするカメラ。

(付記 25)

付記 19 に記載のカメラであって、

前記複数の画素はそれぞれ、電界効果トランジスタのゲートに直接接続されるか、あるいは転送ゲートとフローティングディフュージョンを通じて電界効果トランジスタのゲートに間接的に接続されることを特徴とするカメラ。

(付記 26)

付記 19 に記載のカメラであって、

30

加算される複数の画素の数は 2 であることを特徴とするカメラ。

(付記 27)

付記 19 に記載のカメラであって、

加算される複数の画素の数は 3 であることを特徴とするカメラ。

(付記 28)

付記 19 に記載のカメラであって、

加算される複数の画素の数は 4 であることを特徴とするカメラ。

(付記 29)

付記 20 に記載のカメラであって、

さらに、複数の追加の抵抗素子ネットワークを備えることを特徴とするカメラ。

40

(付記 30)

付記 20 に記載のカメラであって、

前記抵抗素子の少なくとも 1 つは抵抗器であることを特徴とするカメラ。

(付記 31)

付記 20 に記載のカメラであって、

前記抵抗素子の少なくとも 1 つは電界効果トランジスタであることを特徴とするカメラ

。

(付記 32)

付記 20 に記載のカメラであって、

前記ヒューズの少なくとも 1 つの代わりにアンチヒューズが用いられることを特徴とす

50

るカメラ。

(付記 3 3)

付記 2 0 に記載のカメラであって、

前記複数の画素は電荷結合素子を形成することを特徴とするカメラ。

(付記 3 4)

付記 2 0 に記載のカメラであって、

前記複数の画素はそれぞれ、電界効果トランジスタのゲートに直接接続されるか、あるいは転送ゲートとフローティングディフュージョンを通じて電界効果トランジスタのゲートに間接的に接続されることを特徴とするカメラ。

(付記 3 5)

10

付記 2 0 に記載のカメラであって、

加算される複数の画素の数は 2 であることを特徴とするカメラ。

(付記 3 6)

付記 2 0 に記載のカメラであって、

加算される複数の画素の数は 3 であることを特徴とするカメラ。

(付記 3 7)

付記 2 0 に記載のカメラであって、

加算される複数の画素の数は 4 であることを特徴とするカメラ。

【図面の簡単な説明】

【0 0 2 6】

20

【図 1】先行技術による基板電圧基準回路の概略図である。

【図 2】先行技術によるインターライン C C D の上面図である。

【図 3】図 2 の画素の断面図である。

【図 4】2 つの画素の加算を示す、先行技術によるインターライン C C D の上面図である。

。

【図 5】インターライン C C D フォトダイオード電位対シリコンの深さを示すグラフである。

【図 6】本発明のイメージセンサの上面図である。

【図 7】図 6 の断面図である。

【図 8】2 つの画素を加算する場合の最適な基板電圧と画素加算を行わない場合の最適な基板電圧との関係を示すグラフである。

30

【図 9】本発明によるデュアル基板基準電圧回路を示す概略図である。

【図 1 0】本発明によるマルチ基板基準電圧回路を示す概略図である。

【図 1 1】本発明による抵抗器を用いたマルチ基板基準電圧回路を示す概略図である。

【図 1 2】F E T を用いたマルチ基板基準電圧回路を示す概略図である。

【図 1 3】本発明によるアンチヒューズを用いたマルチ基板基準電圧回路を示す概略図である。

【図 1 4】本発明による電荷加算機能を伴う C M O S イメージセンサの画素の概略図である。

【図 1 5】本発明によるマルチ基板基準電圧を有するイメージセンサを用いたカメライメージングシステムを示す図である。

40

【符号の説明】

【0 0 2 7】

1 0 0 電荷結合素子、1 0 5 , 3 0 5 , 4 2 3 , 4 2 6 フォトダイオード、1 1 0 垂直電荷結合素子、1 1 5 水平電荷結合素子、1 2 0 アンプ、2 0 0 埋め込みチャネル、2 0 5 p 型ウェル、2 1 0 , 3 1 7 , 4 2 1 基板、2 1 5 , 3 1 6 , 4 2 2 オーバーフロードレイン、2 2 0 ゲート、2 2 5 不透明な金属層、2 3 0 , 3 3 0 , 4 2 4 ピニング層、3 0 0 , 4 7 0 イメージセンサ、3 0 2 埋め込みチャネル、3 0 3 遮光手段、3 0 4 画素、3 1 0 垂直 C C D シフトレジスタ、3 1 5 水平 C C D シフトレジスタ、3 2 0 出力電荷感知ノード、3 6 0 電圧回路、4 1 1 , 4 1 9

50

, 420, 428 信号線、412 電源線、413 リセットトランジスタ、414, 427 転送ゲート、416 出力線、417, 418 トランジスタ、425 フローティングディフュージョン、471 カメライメージングシステム。

**FIG. 2**

**PRIOR ART**

**FIG. 1**

**PRIOR ART**

**FIG. 3**

PRIOR ART

**FIG. 4**

**【図 5】**

**【図 7】**

**FIG. 7**

**【図 8】**

**【図 6】**

**FIG. 6**

FIG. 10

FIG. 9

FIG. 11

FIG. 12

【図 1 3】

FIG. 13

【図 1 4】

FIG. 14

【図 1 5】

FIG. 15

---

フロントページの続き

審査官 若林 治男

(56)参考文献 特開平08-084252(JP, A)

特開2005-123965(JP, A)

特開2000-236475(JP, A)

(58)調査した分野(Int.Cl., DB名)

H04N 5/30 -5/378

H04N 5/222-5/257

H01L 27/148