심사관 :

안철흥

# (19) 대한민국특허청(KR)

# (12) 등록특허공보(B1)

(51) Int. Cl.

**H01L 51/50** (2006.01)

(21) 출원번호 10-2007-0027818

(22) 출원일자 2007년03월21일

심사청구일자 2007년03월21일

(65) 공개번호10-2007-0118946(43) 공개일자2007년12월18일

(43) 공개일자(30) 우선권주장

10 2006 027 884.4 2006년06월13일 독일(DE)

(56) 선행기술조사문헌

KR1020040104653 A

KR1020050111999 A KR1020060051740 A

전체 청구항 수 : 총 11 항

(45) 공고일자 2008년02월20일

(11) 등록번호 10-0804540

(24) 등록일자 2008년02월12일

(73) 특허권자

삼성에스디아이 주식회사

경기 수원시 영통구 신동 575

삼성에스디아이 저머니 게엠베하

독일 베를린 데-12459 오스트엔트쉬트라쎄 1-14

(72) 발명자

레데커 미하엘

독일 뮌헨 81739, 돈뢰쉔슈트라쎄 21베

피셔 외르그

독일 베를린 13053, 디트리히슈트라쎄 4

(뒷면에 계속)

(74) 대리인

리앤목특허법인

(54) 균일한 결정의 유기 반도체충을 구비하는 전자 소자, 상기유기 반도체충을 제조하기 위한 콜로이드 현탁액 및 상기유기 반도체충의 제조방법

### (57) 요 약

본 발명은 균일한 결정(homogenous-crystalline)의 유기 반도체층을 구비하는 전자 소자, 상기 유기 반도체층을 제조하기 위한 콜로이드 현탁액, 및 상기 유기 반도체층의 제조방법에 관한 것이다. 상기 균일한 결정의 유기 반도체층은,

(i) 유기 반도체 30 내지 200 중량부; 및

(ii) 전기적으로 비도전성이고 상기 유기 반도체와 반대로 비활성인 나노입자들 1 내지 5 중량부;를 포함한다.  $\mathbf{UHE}$  -  $\mathbf{SI}$

# (72) 발명자

# 마테아 아르투르

독일 베를린 14197, 쉴랑엔바티 슈트라쎄 24데

# 쉐디히 마르쿠스

독일 쾨리히스 부스터하우젠, 포츠다머 슈트라쎄

### 특허청구의 범위

### 청구항 1

유기 반도체(OSC) 30 내지 200 중량부, 및

비도전성이고 비활성인 나노입자들 1 내지 5 중량부를 포함하는 유기 반도체층을 구비하는 전자소자.

### 청구항 2

제 1 항에 있어서, 상기 나노입자들이  $SiO_2$ ,  $SnO_2$ ,  $TiO_2$ ,  $ZrO_2$ , 글래스,  $Al_2O_3$ ,  $CaF_2$ ,  $BaF_2$  및 MgO로 이루어진 군에서 선택되는 적어도 어느 하나인 유기 반도체층을 구비하는 전자소자.

### 청구항 3

제 1 항에 있어서, 상기 나노입자들의 평균 입자 크기가 3 내지 100nm 인 유기 반도체층을 구비하는 전자소자.

### 청구항 4

제 1 항에 있어서, 상기 나노입자들은 단분산 형태로 존재하는 유기 반도체층을 구비하는 전자소자.

### 청구항 5

제 1 항 내지 제 4 항 중 어느 한 항에 있어서, 상기 전자 소자는 유기 박막 트랜지스터인 전자 소자.

### 청구항 6

제 5 항에 있어서, 상기 유기 박막 트랜지스터는

### 기판;

상기 기판 상에 형성된 상기 유기 반도체층;

상기 유기 반도체층 상에 형성된 절연층; 및

상기 절연층 상에 형성된 게이트 전극;을 포함하는 전자 소자.

### 청구항 7

유기 반도체(OSC) 30 내지 200 중량부; 및

비도전성이고 비활성인 나노입자들 1 내지 5 중량부;를 분산매에 포함하는 유기 반도체층 제조용 콜로이드 현탁 액.

### 청구항 8

제 7 항에 있어서, 상기 분산매는 유기 용매인 콜로이드 현탁액.

### 청구항 9

제 8 항에 있어서, 상기 분산매는 톨루엔인 콜로이드 현탁액.

### 청구항 10

제 7 항 내지 제 9 항 중 어느 한 항에 있어서, 상기 분산매는 유기 반도체 1 내지 5 중량%를 포함하는 콜로이 드 현탁액.

### 청구항 11

제 7 항 내지 제 9 항 중 어느 한 항의 콜로이드 현탁액을 준비하는 단계;

기판 상에 상기 콜로이드 현탁액을 증착하는 단계; 및

상기 분산매를 제거하는 단계;를 포함하는 유기 반도체층을 기판상에 형성하는 방법.

### 명 세 서

### 발명의 상세한 설명

### 발명의 목적

# 발명이 속하는 기술 및 그 분야의 종래기술

- <3> 본 발명은 균일한 결정의 유기 반도체층(OSC layer; OSC=organic semiconductor)을 구비하는 유기 박막 트랜지 스터(OTFT=organic thin film transistor)와 같은 전자 소자, 상기 균일한 결정의 유기 반도체층 제조를 위한 콜로이드 현탁액 및 상기 균일한 결정의 유기 반도체층의 제조 방법에 관한 것이다.

- 얼광 다이오드, 전계 효과 트랜지스터 또는 광전지와 같은 다양한 기술의 적용 단계들에서 유기 반도체들(OSC)의 결정 구조는 일반적으로 알려져 있으나, 기술적인 측면에서 유기 반도체들의 배열은 최적화를 요한다. 일반적으로, 트랜지스터에 사용되는 유기 반도체는 배치에 적합한 전도성 반응을 형성하기 위해 결정 변이 (Crystalline modification)의 높은 질서도(order degree)를 갖도록 제공되어야 한다. 질서도는 물질의 결정화 및 응집에 의해 결정될 수 있다. 이를 위해, 물질 자체적으로 응집 공정의 개시/자기 질서로 향하는 경향을 갖는다. 예를 들어, 기체 상태로부터 분리하는 방법에 의해 펜타센(pentacene)의 결정화, 유기 반도체들을 구비하는 액정 구조의 형성뿐 아니라 폴리(알킬사이오펜)(poly(thiophenes)의 일정한 얇은 판 구조의 형성은 알려진바 있다.

- <5> 대부분의 액정 물질들, 트랜지스터에 사용되는 상기 물질들은 유기 반도체층의 전체 길이 이상으로 충분하게 넓게 형성되지 않는다. 이와 같은 사실을 해결하기 위하여, 형성되어야 하는 유기 반도체층에 원하는 거시적 (macroscopic) 질서도를 유도하도록 추가층을 형성하는 방법이 알려져 있다.

- <6> 3차원 결정화 시스템에서, 입자들 및 표면 결함은 결정의 개시 점들을 형성한다. 상기 결정화 점들의 밀도에 따라, 유기 반도체층 영역들은 예를 들어 OTFT의 전체 소스-드레인 구조 이상으로 신장되며 충분히 넓게 지속적으로 제조될 수 있다. 그러나 결정 점들의 형태 및 양은 제어하기 어려우며, 제조 공정에서 불량 및 전기적 도전용량의 변화 폭이 커진 트랜지스터들을 생산하는 문제들을 야기한다.

### 발명이 이루고자 하는 기술적 과제

<7> 본 발명은 상기 살펴본 바와 같이 종래 상태의 문제들을 극복하고자, 최적의 질서도를 갖는 균일한 결정 변이 (homogeneous-crystalline modification)의 유기 반도체층을 구비하는 전자소자, 상기 유기 반도체층을 제조하기 위한 콜로이드 현탁액 및 상기 유기 반도체층의 제조방법을 제공하고자 한다.

### 발명의 구성 및 작용

- <8> 본 발명의 일 실시예에 따르면, 균일한 결정의(Homogenous-crystalline) 유기 반도체충(OSC layer)을 구비하는 전자 소자를 제공한다.

- <9> 본 발명에 관한 균일한 결정의 유기 반도체층은,

- <10> (i) 유기 반도체(OSC) 30 내지 200 중량부; 및

- <11> (ii) 전기적으로 비도전성을 가지고 상기 OSC와 반대로 비활성인 나노입자들 1 내지5 중량부;를 포함한다.

- <12> 상기 나노입자들의 존재는 OSC층의 전기적 특성에 영향을 미치지 않거나 또는 미세하게 영향을 미친다. 제조 동안 상기 나노입자들의 존재는 그들 자체가 결정의 근원 역할을 하며, 따라서 균일한 결정 시스템을 생성한다. 다시 말해, 상기 유기 반도체층의 나노입자들이 결정 과정을 제어함으로써 유기 박막 트랜지스터에 유용하게 사용될 수 있다. 본 발명에 관한 유기 반도체층에서 하전 캐리어 이동도의 표준 편차는 다른 유사한 조건에서 나노입자들의 적용 없이 제조된 유기 반도체층의 경우보다 현저히 작다. 따라서 상기와 같은 유기 반도체층은 다이오드, 트랜지스터, 광전지 및 유기발광 다이오드와 같은 전기적 구조의 소자들에 용이하게 적용될 수 있다.

- <13> 본 발명에서 유기 반도체는 페르미 에너지(Fermi-energy)가 밴드 갭에 놓이고 하전 캐리어들의 열 활성화 (thermal activation)가 가능한 (산화물, 탄산, 탄화물을 제외한)탄소 화합물을 의미한다. 상기 반도체 물질들은 분자 크기에 따라 분류될 수 있다; 즉, 일부는 펜타센(pentacene) 또는 안드라센(anthracene)과 같은 저분자들로, 나머지는 트랜스-폴리아세틸렌(trans-polyacetylene) 또는 폴리(티오펜)(poly(thiophene))과 같은 고분

자들로 분류될 수 있다. 본 발명의 목적을 위해서, 고분자들 및 저분자들이 반도체 물질들로 사용될 수 있다.

- <15> 본 발명에서 나노입자들은 나노미터 범위의 크기를 갖는 몇 천개의 원자들 또는 분자들의 일부 화합물을 의미한다. 바람직하게, 평균 입자 크기는 3 내지 100nm 이고, 더욱 바람직하게는 5 내지 20nm이다. 이때, 상기 나노입자들은 단분산 형태로, 복수의 입자들 중 한 개 입자의 크기를 의미한다. 상기와 같은 나노입자들의 제조는 알려져 있어 이하 상기 제조 공정을 상세히 설명하지 않는다.

- <16> 본 발명의 목적을 위한 나노입자들은 전도성을 갖지 않아야 하며, 유기 반도체와 반대로 비활성이어야 한다.

즉, 유기 반도체의 전기적 특성들은 가능하면 나노입자들의 작은 부분에 의해 바뀌지 않아야 하며, 유기 반도체와 화학 반응이 일어나지 않아야 한다.

- <17> 바람직하게, 나노입자들의 물질은 OTFT에서 항상 상기 층의 또 다른 구성들과 전자기적 작용을 하지 않는 밴드 구조들을 갖는다.

- <18> 상기 나노입자들은 SiO<sub>2</sub>, SnO<sub>2</sub>, TiO<sub>2</sub>, 글래스, Al<sub>2</sub>O<sub>3</sub>, MgO, 및 CaF<sub>2</sub>로 이루어진 군에서 하나 이상 선택되는 물질을 포함한다. 더욱 바람직하게는, 상기 나노입자들은 SiO<sub>2</sub>, 글래스, Al<sub>2</sub>O<sub>3</sub>, MgO, CaF<sub>2</sub> 및 BaF<sub>2</sub>로 이루어진 군에서 선택되는 하나 이상의 물질을 구성한다.

- 본 발명에 따른 상기 전자 소자들로 다이오드, 트랜지스터, 광전지 및 유기발광 다이오드와 같은 전기적 구조의 소자들이 있다. 상기 전자 소자들은 균일한 결정의 유기 반도체층을 구비한다. 상기 유기 반도체층은 높은 질서 도를 가지며, 캐리어 이동도의 편차가 감소하여 상기 유기 반도체층을 포함하는 전자 소자들은 그 신뢰성을 증 진할 수 있다.

- <20> 상기 전자 소자의 한 예로, 유기 박막 트랜지스터(OTFT)를 제공한다.

- \*21> 박막 트랜지스터(FET)는 도체, 절연체, 반도체 물질 및 기판을 포함한다. 반도체층이 유기 분자들 및 폴리머들로 이루어질 때 전계 효과 트랜지스터를 유기 박막 트랜지스터라 한다. 박막 트랜지스터는 게이트 전극들이 탑(top) 또는 바텀(bottom)에 놓여짐에 따라 탑 게이트 및 바텀 게이트로 구분될 수 있다. 유기 박막 트랜지스터들은 기판, 절연층, 및 게이트 전극을 포함한다. 상기 기판으로서 플라스틱, 유리, 또는 도전성의 실리콘 웨이퍼를 사용할 수 있으며, 게이트 전극은 도전성 물질로서 금속 또는 불순물이 도핑된 폴리실리콘 등을 사용할 수 있다. 또한, 절연층으로 SiO<sub>2</sub>층 등을 사용할 수 있다. 금속(예를 들어, 금)으로 이루어진 소스 및 드레인 전극들은 상기 유기 반도체층 상에 패터닝되어 증착된다. 유기 반도체층은 상층에서 기상 증착되거나(예를 들어, 펜타센) 스핀 코팅(예를 들어 폴리시오펜)된다.

- <22> 상기 전계 효과 트랜지스터들의 기본 기능은 순수하게 무기물들로 이루어진 종래 전계 효과 트랜지스터의 기능과 유사하다. 게이트 전압을 인가하면, 반도체와 절연물 사이 경계층에 하전 캐리어들이 축적되어 매우 얇은 도전성 채널을 형성함으로써 전류가 소스 전극으로부터 드레인 전극으로 통하게 된다.

- <23> 전류량은 하전 캐리어의 속도 측정 단위인 물질 특성으로서, 캐리어의 이동도 뿐 아니라 하전 캐리어의 수를 결정하는 게이트 전압에 따라 달라진다.

- <24> 모든 종래 유기 전계 효과 트랜지스터들은 하전 캐리어 축적의 원리에 기반한다. 정공 컨덕터들 또는 p형 반도체들은 전류를 빠르게 통하도록 할 수 있으며 실질적으로 n형 반도체보다 더욱 안전하다. 이와 같은 이유 때문에 대부분의 유기 전계 효과 트랜지스터는 p형 트랜지스터들이다.

- <25> 전하 수송의 메카니즘은 종합적인 분석 시험의 주제이다; 고분자에서, 모든 정공은 비주기 시스템의 복잡한 루트를 이동한다. 정공들은 고분자 체인들을 따라 이동할 수 있으며, 끝에서 다음 고분자로 터널링하여야 한다. 따라서 고분자의 공간상 배열은 캐리어의 이동을 위해 매우 중요하다; 질서도가 높으면 하전 캐리어의 이동도가

높아진다. 유기 저분자들(예를 들어, 펜타센)에서 약  $2 \text{cm}^2/\text{Vs}$  정공 이동도가 측정되었으며, 고분자들에서는 정공 이동도가  $10^{-4}$  내지  $0.1 \text{ cm}^2/\text{Vs}$  범위의 값을 나타내었다. 그 결과, 유기 반도체의 큰 질서도 변화는 하전 캐리어의 이동도에 즉시 영향을 미친다. 상기 나노입자들의 배열로 인해, 질서도 변화에 관련된 요인이 감소하게 되었다. 이와 같은 높은 질서도는 본 발명에서 균일한 결정(homogenous-crystalline)을 의미한다. 따라서, 본 발명에 관한 유기 반도체층이 균일한 결정, 즉 높은 질서도를 가짐으로써 하전 캐리어의 이동도 편차를 감소시킬 수 있다. 이는 상기 유기 반도체층을 포함하는 전자 소자의 신뢰성을 증진할 수 있는 것이다.

- <26> 본 발명의 다른 실시예에 따르면 기판상에 균일한 결정의(homogenous-crystalline) 유기 반도체충을 제조하는 방법을 제공한다. 상기 방법은 다음 단계들을 포함한다.

- <27> (i) 분산매에 유기 반도체(OSC) 30 내지 200 중량부 및 전기적 끌림이 없고 상기 유기 반도체와 반대로 비활성인 나노입자들 1 내지 5 중량부를 포함하는 콜로이드 현택액을 제조하는 단계;

- <28> (ii) 기판상에 상기 콜로이드 현탁액의 도포하는 단계;

- <29> (iii) 상기 분산매를 제거하는 단계.

- <30> (i) 단계에서, 결과적으로 분산매에 나노입자들과 유기 반도체의 적어도 2 가지 조성 성분들을 포함하는 콜로이드 현탁액을 제공한다. 이때, 유기 반도체는 분산매에 용해되나, 나노입자들은 콜로이드 현탁액의 고체상 영역을 형성한다.

- <31> 상기 콜로이드 현탁액은 예를 들어 유기 반도체를 용매에 용해한 제1 용액과, 나노입자들을 액상의 분산매에 분산한 제2 용액을 혼합함으로써 제조될 수 있다. 바람직하게, 상기 제1 용액의 용매와 상기 제2 용액의 분산매는 동일한 조성을 갖는다. 또한, 상기 콜로이드 현탁액은 나노입자들이 용해/응집되거나 또는 상기 유기 반도체가 참전되지 않도록 하는 첨가물을 더 혼합할 수 있다. 바람직하게, 제1 용액의 용매 또는 제2 용액의 분산매는 유기 용매, 더욱 바람직하게는 톨루엔을 사용할 수 있다.

- <32> 또한, 상기 제2 용액의 분산매는 0.1 내지 5 중량%의 유기 반도체를 포함할 수 있으며, 상기 제2 용액의 분산매는 비도전성이고 비활성인 나노입자들 1 내지 5 중량부를 포함한다. 콜로이드 현탁액은 상기 방법의 중간체로서 청구되기 때문에 별도로 설명하지 않는다.

- <33> (ii) 단계에서 콜로이드 현탁액을 기판상에 도포한다. 이때, 도포 방법으로 스핀 코팅, 딥 코팅 도는 프린트 방법 등을 이용할 수 있다.

- <34> 상기 도포 후, 분산매는 열에너지를 주입하고 부압(subpressure)을 적용하여 (iii) 단계에서 제거한다.

- <35> 이하, 본 발명을 도면을 참조하여 상세히 설명한다.

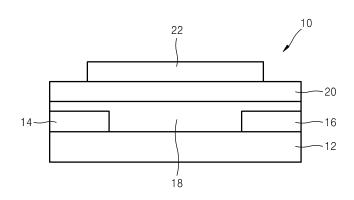

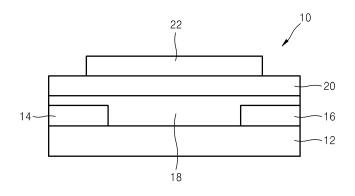

- <36> 도 1은 유기 박막 트랜지스터(OTFT, 10)의 단면도를 나타낸다. 본 실시예에서는 본 발명에 관한 유기 반도체층을 포함하는 전자 소자로 유기 박막 트랜지스터를 예시하였지만, 이에 한정되는 것은 아니며 반도체층을 포함하는 다양한 전자 소자들도 본 발명에 포함된다.

- <37> OTFT는 유리로 이루어진 기판(12)을 구비한다. 금으로 이루어진 소스 전극(14) 및 드레인 전극(16)은 유기 반도체로 이루어진 유기 반도체층(18)을 둘러싼다. 상기 구성들은 절연층(20)에 의해 덮인다. 게이트 전극(22)은 절연층(20)상에 형성된다. 상기 3개 전극들(14,16,22)은 종래 방법에 의해 연결된다(미도시).

- <38> 다음 단계는 개략적으로 도시된 OTFT(10)의 제조를 위해 적용될 수 있다.

- <39> 소스 및 드레인 전극들(14,16, Cr 10nm와 40nm)을 구비하는 기판(12)은 종래 습식 화학 방법에 의해 세정되었다.

- <40> 균일한 결정의 유기 반도체층(18)을 제조하기 위해 콜로이드 현탁액은 다음과 같이 제조되었다.

- <41> 14nm의 평균 입자 크기를 갖는 단분산 SiO<sub>2</sub> 입자들(sigma-Aldrich에서 구입 가능)을 0.025 중량% 톨루엔에 가하고, 초음파 처리하에 분산하였다. 톨루엔에 유기 반도체 비스-(트리소-프로필실리에틸)펜타센(bis-(triso-propylsilylethinyl)pentacene)을 가한 2 중량% 용액을 제조하고 여과하였다. 상기 두 용액들을 1:1의 부피피로 서로 혼합하여 콜로이드 현탁액을 완성하였다.

- <42> 기판(12)은 산소-플라즈마 처리로 활성화되고, 표면은 2-프로판올(2-propanol)에 2,3,4,5,6-펜타플루오르티오핀

올(2,3,4,5,6-pentafluorthiophenol, 중량%, Sigma-Aldrich에서 구입 가능)을 가한 용액으로 기능화하였다.

- <43> 건조 후, 유기 반도체충(18)으로 콜로이드 현탁액을 스핀 코팅 증착하고, 80℃의 히팅 플레이트 상에서 가열하였다.

- <44> 이후, 절연층(20)으로 폴리(1,1,2,4,4,5,5,6,7,7-데카플루오로-3-옥사-1,6-헵타디엔)(poly(1,1,2,4,4,5,5,6,7,7-decafluoro-2-oxa-1,6-heptadiene; Sigma-Aldrich에서 구입 가능)을 퍼플루오르트리부틸아민(perfluortributylamine)에서 스핀 코팅 증착하고, 120℃의 히팅 플레이트 상에서 가열하였다.

- <45> 마지막으로, 40nm의 두께를 갖는 금 컨택은 열 증착 방법으로 증착하여 게이트 전극(22)을 형성하였다. 게이트 전극의 구조는 새도우 마스크를 이용하여 형성하였다.

- <46> 대조군으로서 OTFT는 나노입자들을 함유하는 본 발명의 콜로이드 현탁액의 사용을 제외하고, 대신 분산매 톨루 엔에 유기 반도체를 혼합한 용액을 균일하게 얇게 형성하여 본 발명의 방법과 동일하게 제조되었다.

- <47> 측정된 활성 채널의 길이-폭 비율은 소스 드레인 전극들의 구조 및 배열에 따라 달라졌다. 다른 길이-폭 비율들 도 측정하여 이것이 결과에 중요한 영향을 미치지 않음을 보였다.

- <48> 유기 박막 트랜지스터들의 전기적 특성은 반도체 테스터 케이슬레이 4200(Semiconductor Tester Keithley 4200)으로 측정되었으며, 원하는 트랜지스터 파라미터들, 바람직하게는 개별적인 OTFT들의 하전 캐리어 이동도를 측정하였다.

- <49> 표준 편차 σ는 다음과 같이 결정되었다.

- <50> 1. 유사하게 설계된 일부 유기 트랜지스터들의 하전 캐리어 이동도 결정.

- <51> 2. 이에 더하여, 유사하게 설계된 일부 유기 트랜지스터들의 하전 캐리어 이동도들의 표준 편차 계산.

- <52> 표준 편차 σ는 하기 표와 같다.

### 丑 1

<53>

|     | W/L 1800:25에서 σ | W/L 1800:50에서 σ | W/L 6000:50에서 σ | W/L 450:45에서 σ |

|-----|-----------------|-----------------|-----------------|----------------|

| 대조군 | 0.12            | 0.08            | 0.11            | 0.29           |

| 실시예 | 0.06            | 0.02            | 0.01            | 0.2            |

- <54> 상기 살펴본 바와 같이, 본 발명에 관한 반도체층에서 하전 캐리어 이동도의 표준 편차 σ는 현저히 감소하였다.

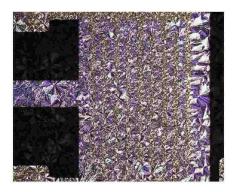

- <55> 도 2 및 3의 현미경 사진들은 이 효과를 반영한다; 도 2는 반도체층의 가장자리 및 중앙 영역에서 다른 결정 크기를 갖는 OSC 층의 비균일(non-homogenous) 구조를 나타낸다. 도 3은 유기 반도체층이 나노입자를 포함하여 제조되었을 때 탑 게이트 OTFT에서 균일(homogenous) 분포를 보여준다.

### 발명의 효과

- <56> 상기 살펴 본 바와 같이, 본 발명은 결정 점으로 나노입자들을 포함함으로써, 높은 질서도의 균일한 결정 분포를 갖는 유기 반도체층, 이를 용이하게 제조하는 방법 및 상기 유기 반도체층을 제조하기 위한 콜로이드 현탁액을 제공할 수 있다.

- <57> 또한, 본 발명은 균일한 결정 분포를 갖는 상기 유기 반도체층을 포함하는 유기 박막 트랜지스터와 같은 전자소자를 제공함으로써 하전 캐리어 이동도의 표준 편차를 줄일 수 있다. 따라서 상기 전자 소자의 신뢰성을 증진할 수 있다.

- <58> 본 발명은 도면에 도시된 실시예를 참고로 설명되었으나 이는 예시적인 것에 불과하며, 당해 기술 분야에서 통상의 지식을 가진 자라면 이로부터 다양한 변형 및 균등한 다른 실시예가 가능하다는 점을 이해할 것이다. 따라서, 본 발명의 진정한 기술적 보호 범위는 첨부된 특허청구범위의 기술적 사상에 의하여 정해져야 할 것이다.

### 도면의 간단한 설명

<!> 도 1은 본 발명의 일 실시예에 관한 유기 박막 트랜지스터(OTFT)의 단면도이다.

<2> 도 2 및 3은 각각 종래 방법에 따라 제조된 탑 게이트 OTFT 및 본 발명의 방법에 따라 제조된 탑 게이트 OTFT의 현미경 사진들이다.

# 도면

# 도면1

# 도면2

도면3