#### (12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

# (19) World Intellectual Property Organization International Bureau

### (43) International Publication Date 4 September 2003 (04.09.2003)

## **PCT**

# (10) International Publication Number WO 03/073507 A2

(51) International Patent Classification<sup>7</sup>: H01L 27/00

(21) International Application Number: PCT/US03/03277

(22) International Filing Date: 4 February 2003 (04.02.2003)

(25) Filing Language: English

(26) Publication Language: English

(30) Priority Data:

60/359,263

20 February 2002 (20.02.2002)

US

10/217,798

12 August 2002 (12.08.2002)

US

10/307,106

27 November 2002 (27.11.2002)

US

10/347,149

17 January 2003 (17.01.2003)

US

(71) Applicant (for all designated States except US): PLANAR SYSTEMS, INC. [US/US]; 1195 NW Compton Drive, Beaverton, OR 97006 (US).

- (72) Inventor; and

- (75) Inventor/Applicant (for US only): DEN BOER, Willem [NL/US]; 2721 NE Charlois, Hillsboro, OR 97124 (US).

- (74) Agent: FERRIS, Kassim, M.; Stoel Rives LLP, 900 SW Fifth Avenue, Suite 2600, Portland, OR 97204-1268 (US).

- (81) Designated States (national): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, OM, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

- (84) Designated States (regional): ARIPO patent (GH, GM, KE, LS, MW, MZ, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian patent (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European patent (AT, BE, BG, CH, CY, CZ, DE, DK, EE,

[Continued on next page]

#### (54) Title: IMAGE SENSOR WITH PHOTOSENSITIVE THIN FILM TRANSISTORS

(57) Abstract: An image sensor array includes image sensors having photo TFTs to generate photocurrent in response to received images. The photo TFTs each have their respective gate electrodes shorted to source electrodes to increase generated photocurrent. Storage capacitors are coupled to each photo TFT and discharged upon generation of a photocurrent. Each storage capacitor is coupled to a readout TFT that passes a current from the storage capacitor to a data line. Data lines indicate location of the received image on the image sensor array.

# WO 03/073507 A2

ES, FI, FR, GB, GR, HU, IE, IT, LU, MC, NL, PT, SE, SI, SK, TR), OAPI patent (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.

#### Published:

without international search report and to be republished upon receipt of that report

#### IMAGE SENSOR WITH PHOTOSENSITIVE THIN FILM TRANSISTORS

## Technical Field

**[0001]** The present invention relates to image sensors and, more specifically, to flat panel image sensors employing photosensitive thin film transistors.

# Background of the Invention

[0002] Flat panel image sensors are commercially successful products that are able to effectively detect electromagnetic radiation in and near the visible light spectrum. Flat panel image sensors are fabricated by depositing and patterning various metals, insulators, and semiconductors on glass substrates as is done in flat panel displays. Such sensors commonly employ photosensitive elements, such as amorphous silicon (a-Si) PIN diodes. The photosensitive element is coupled to a readout switch, such as thin film transistor (TFT), that provides data indicative of received light.

[0003] A common use for flat panel image sensors is for medical and industrial applications to detect X-rays. The image sensor includes a phosphorescent screen that overlays an array of image sensing elements. The phosphorescent screen converts received X-rays to visible light. The array receives the visible light and generates a photocurrent responsive to the light. The photocurrent is read out as data indicative of the sensed light.

[0004] The arrays are difficult to manufacture since separate process steps are required to construct the PIN diodes and the TFTs. The total mask count may be 8 or more which is burdensome while the yields are low. Furthermore, a-Si PIN diodes are not a standard device in flat panel display processing which increases manufacturing expense. It would therefore be advantageous to use a standard process to greatly reduce the cost of flat panel image sensors.

[0005] Manufacturing TFTs for flat panel applications is a common process. A common use for TFTs is in active matrix liquid crystal displays (AMLCDs). Each TFT

functions as a switch for a pixel in a matrix display. The voltage across each pixel is controlled independently and at a high contrast ratio. TFTs may be fabricated by depositing and patterning metals, insulators, and semiconductors on substrates through methods well known in the art. TFTs typically employ a-Si, polycrystalline silicone, or CdSe film as the semiconductor material. A-Si is typically used in flat panel applications as it is easily deposited on large area glass substrates at temperatures below 350 centigrade.

**[0006]** TFTs are more economical to fabricate than a-Si PIN diodes and are well suited for flat panel applications. The present inventors have recognized that if both the image sensing element and the readout switch of an image sensor array were incorporated as TFTs, fewer photomasks would be required and manufacturing costs would be greatly reduced.

TFTs have not commonly been used as photosensitive elements. United States Patent Application Publication Nos. 2001/0055008 and 2001/0052597, both to Young et al. (hereinafter the "Young applications"), disclose the use of TFTs as light sensing elements for a display device. The light sensing elements provide feedback to progressively adjust the current flow through display elements to control light output. However, the use of TFTs exclusively for an image sensor is not disclosed. Since a TFT is more economical to manufacture and has already been successfully incorporated into flat panel applications, the present inventors have recognized that it would be advantageous to employ TFTs in image sensors.

### Summary of the Invention

[0008] An image sensor array includes image sensors disposed on a substrate and arranged to receive and sense an image. Each image sensor represents a pixel for a received image. The image sensors each include a photo TFT that generates a photocurrent in response to the image. The photo TFT may be manufactured using common processes for TFTs in flat panel applications. The photo TFT has a gate electrode which is shorted to its source electrode to obtain a photocurrent that is substantially independent of source-drain bias. The photo TFT may also be configured with interdigitated source and drain electrodes to increase the photosensitivity.

**[0009]** Each photo TFT is coupled to a bias line to enable operation and a storage capacitor to store a charge and discharge upon generation of a photocurrent. The storage capacitor is coupled to a readout TFT that is also manufactured using known

processes. The readout TFT passes a charge from the storage capacitor to a data line. Operation of the readout TFT is enabled by a select line which is coupled to the gate electrode of the readout TFT. A light shield may be disposed over the channel of the readout TFT to prevent a charge leaking through the readout TFT.

- **[0010]** The photo TFTs can provide an effective and economical alternative to conventional photodiodes. Photo TFTs may be manufactured with corresponding readout TFTs using conventional methods thereby reducing mask counts and costs. Photo TFTs may further yield photocurrents greater than that of photodiodes.

- **[0011]** Additional aspects and advantages of this invention will be apparent from the following detailed description of preferred embodiments thereof, which proceeds with reference to the accompanying drawings.

- **[0012]** Additional aspects and advantages of this invention will be apparent from the following detailed description of preferred embodiments, which proceeds with reference to the accompanying drawings.

# Brief Description of the Drawings

- [0013] Non-exhaustive embodiments of the invention are described with reference to the figures in which:

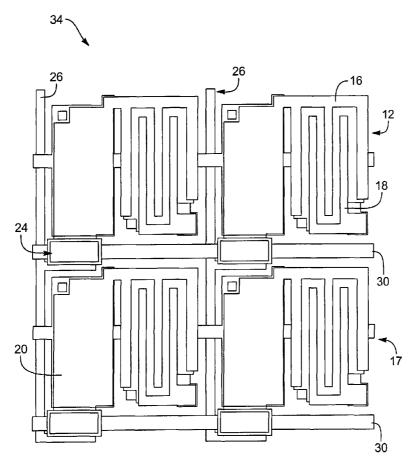

- [0014] Figure 1A is a schematic diagram of an embodiment of a sensor element;

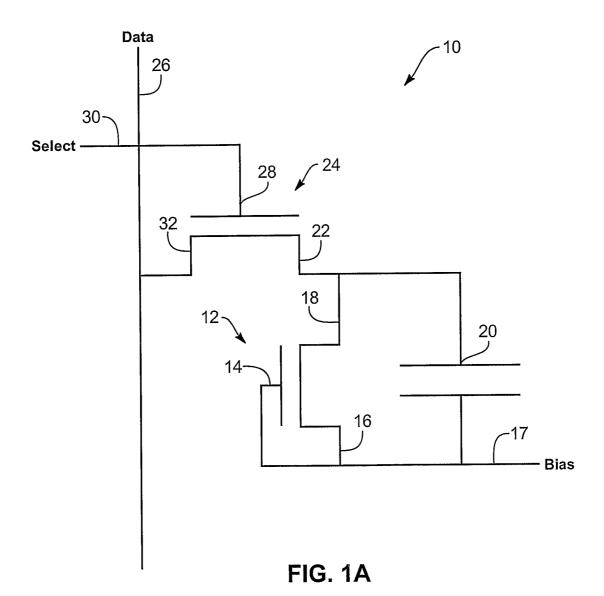

- [0015] Figure 1B is a schematic diagram of an alternative embodiment of a sensor element;

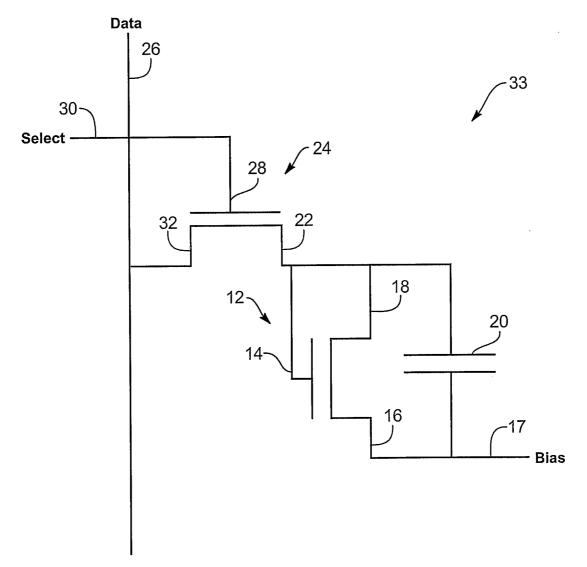

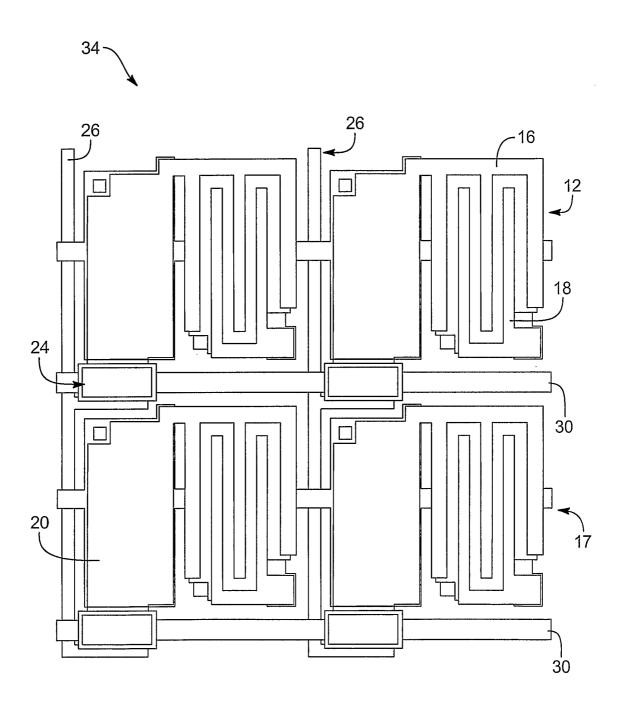

- [0016] Figure 2 is a schematic diagram of an array of sensor elements;

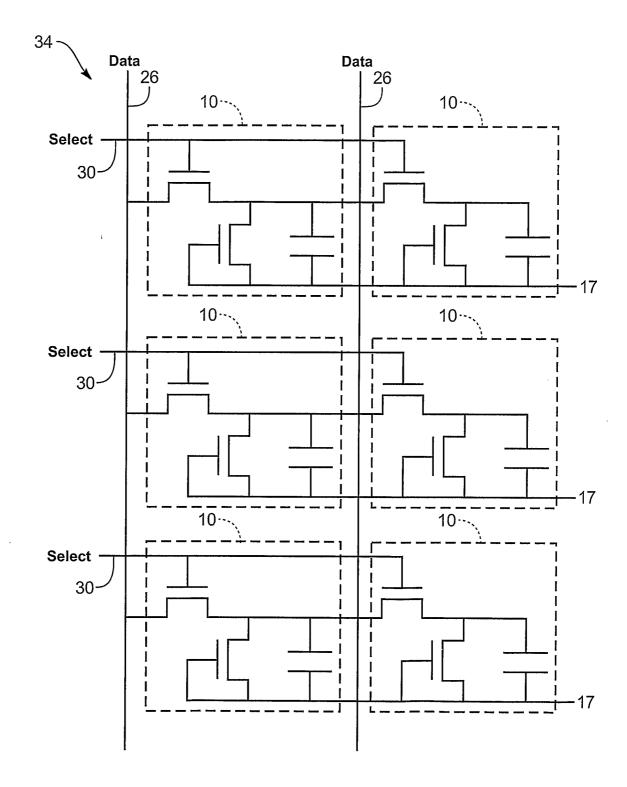

- [0017] Figure 3 is a plan view of an embodiment of sensor elements for use in an image sensor array;

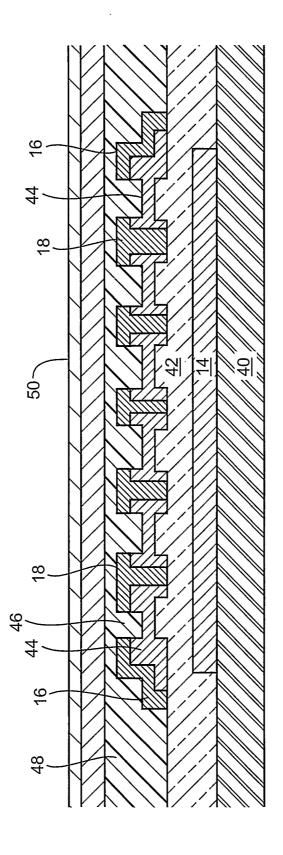

- [0018] Figure 4 is a cross-sectional view of one embodiment of a photo TFT;

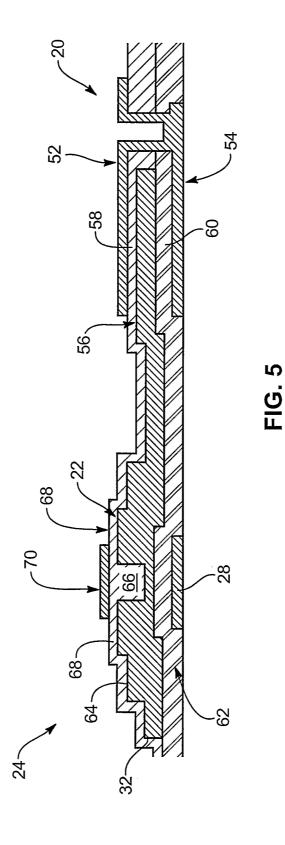

- **[0019]** Figure 5 is a cross-sectional view of one embodiment of a readout TFT and a storage capacitor; and

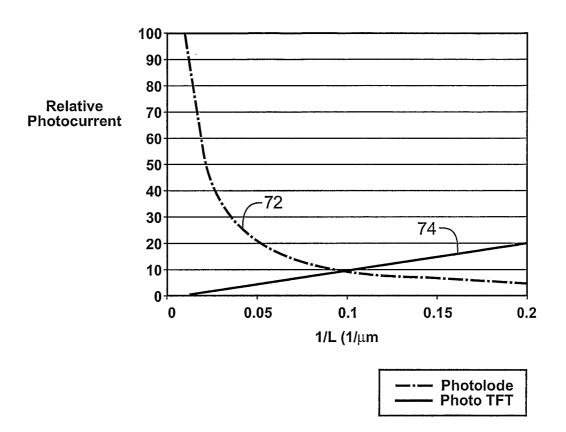

- **[0020]** Figure 6 is a graph comparing the photocurrent for a PIN photodiode with the photocurrent for a photo TFT.

# Detailed Description of Preferred Embodiments

- **[0021]** Reference is now made to the figures in which like reference numerals refer to like elements. For clarity, the first digit or digits of a reference numeral indicates the figure number in which the corresponding element is first used.

- [0022] Throughout the specification, reference to "one embodiment" or "an embodiment" means that a particular described feature, structure, or characteristic is

included in at least one embodiment of the present invention. Thus, appearances of the phrases "in one embodiment" or "in an embodiment" in various places throughout this specification are not necessarily all referring to the same embodiment.

[0023] Furthermore, the described features, structures, or characteristics may be combined in any suitable manner in one or more embodiments. Those skilled in the art will recognize that the invention can be practiced without one or more of the specific details, or with other methods, components, materials, etc. In other instances, well-known structures, materials, or operations are not shown or not described in detail to avoid obscuring aspects of the invention.

[0024] Referring to Figure 1A, an embodiment of a sensor element 10 is shown suitable for use in an image sensor matrix array. The sensor element 10 includes a photo TFT 12 that generates a photocurrent in response to received light. The photo TFT 12 is easily fabricated using common thin film layers. In the embodiment shown, the photo TFT 12 is a gated device having similarly doped contact regions and an intrinsic semiconductor region disposed between. The photo TFT 12 has a gate electrode 14 that is coupled directly to the source electrode 16. The coupling of the gate and source electrodes 14, 16 creates a generated photocurrent that, for short channel lengths, exceeds that of an a-Si PIN photodiode. The photocurrent is a secondary photocurrent and has a potential gain of more than one whereas an a-Si PIN photodiode typically has a gain of less than one. The source electrode 16 is coupled to a bias line 17 which is common to all photosensitive elements in an array. In operation, the bias line 17 may be coupled to a negative voltage.

[0025] The source and drain electrodes 16, 18 of the photo TFT 12 are coupled to a storage capacitor 20 which is discharged when the photo TFT 12 is exposed to light. The storage capacitor 20 is coupled to the source electrode 22 of a readout TFT 24. The charge on the storage capacitor 20 is read out periodically through the readout TFT 24 and a data line 26. As shown, the gate electrode 28 of the readout TFT 24 is coupled to a select line 30 to enable the readout TFT 24. A drain electrode 32 is coupled to the data line 26 to readout a charge.

[0026] The photo TFT 12 and the readout TFT 24 may be manufactured using common TFT manufacturing methods, such as in AMLCD applications. The TFTs 12, 24 generally include substantially co-planar source and drain electrodes, a semiconductor layer between the source and drain electrodes, and a gate electrode in proximity to the semiconductor layer but electrically insulated by a gate insulator.

Current flow between the source and drain electrodes is controlled by the application of a voltage to the gate electrode. The voltage to the gate electrode produces an electric field which accumulates a charged region near the semiconductor-gate insulator interface. This charged region forms a current conducting channel in the semiconductor layer through which the device current is conducted.

[0027] Referring to Figure 1B an alternative embodiment of a sensor element 33 is shown. The sensor element 33 differs from the previously shown embodiment in that the gate electrode 14 is coupled directly to the drain electrode 18. In operation, the bias line 17 has a positive voltage bias. Operation of the sensor element 33 is similar to that of sensor element 10. The storage capacitor 20 is discharged when the photo TFT 12 is exposed to light. The charge on the storage capacitor 20 is read out periodically through the readout TFT 24 and the data line 26.

[0028] Referring to Figure 2, a schematic is shown of an image sensor array 34 that includes regularly-spaced sensor elements 10 of Figure 1A. Although elements 10 of Figure 1A are shown, sensor elements of Figure 1B may be used as well. The sensor elements 10 are arranged at intersections between rows and columns with each element corresponding to an individual pixels. The rows are designated by the select lines 30 and the columns are designated by the data lines 26. Individual sensor elements respond to received light and generate a data signal that is transmitted on an associated data line 26. As data signals pass through the data lines 26 to a control circuit, an image sensor array 34 determines the location of a received image on the array 34.

**[0029]** The array 34 is for illustrative purposes only as an image sensor would have far more sensor elements. The select lines 30 may be in communication with an address circuit to address individual readout TFTs.

[0030] Referring to Figure 3, a plan view of four sensor elements 10 is shown. The photo and readout TFTs 12, 24 may be embodied as various structures which may be manufactured using processes similar to that for TFTs in an AMLCD. The plan view provides a view of components relative to one another. As shown, the photo TFT 12 has a source electrode 16 and drain electrode 18 configured with extending members. The extending members are disposed relative to one another to form an interdigitated pattern.

[0031] Referring to Figure 4, a cross-sectional view of one embodiment of a photo TFT 12 of Figure 3 is shown. The photo TFT 12 may be used in either sensor

elements 10, 33 of Figures 1A or 1B. The photo TFT 12 includes a gate electrode 14 deposited and patterned on an insulating transparent substrate 40, such as glass, quartz, sapphire, or the like. The gate electrode 14 may include metals such as Cr, Cu, Al, Ta, Ti or the like. A gate insulator 42 insulates the gate electrode 14 from a semiconductor layer 44. The gate insulator 42 may include various materials well known in the art, such as silicon nitride, silicon oxide, or the like.

[0032] A semiconductor layer 44 is stacked on the gate insulator 42 above the gate electrode 14 and may include a-Si, p-Si, amorphous silicon carbide (SiC), tellurium (Te), selenium (Se), cadmium sulfide (CdS), cadmium selenide (CdSe), or the like. However, a-Si is well suited to large area fabrication on glass substrates at temperatures below 350 centigrade and exhibits a very high, dark resistivity. The semiconductor layer 44 may be deposited in accordance with methods known in the art including sputtering or deposition, such as plasma-enhanced chemical vapor deposition. The semiconductor layer 44 may be patterned through known methods, such as by use of a mask and photolithographic processing.

[0033] The semiconductor layer 44 may include an n+ layer that contacts the source and drain electrodes 16, 18. The n+ layer may be deposited on opposing ends of the semiconductor layer 44 where contact exists with the source and drain electrodes 16, 18. The n+ layer provides a low resistance contact for the source and drain electrodes 16, 18, and suppresses hole injection at negative gate voltage.

[0034] The source and drain electrodes 16, 18 are patterned at a certain distance from one another so that the electrodes 16, 18 are separated by a co-planar region of semiconductor material 44 in order to form a gate controlled current channel. The semiconductor layer 44 may be configured as shown in Figure 4, to provide contact between alternating source and drain electrode extending members 16, 18. As such, the semiconductor layer 44 and source and drain electrode extending members 16, 18 are patterned and etched to form multiple channels 46. The interdigitated pattern increases the photosensitivity of the photo TFT 12, although one of skill in the art will appreciate that the photo TFT 12 may have an alternative configuration such as a simple inverted staggered structure, trilayer type inverted staggered structure, or other known structures.

[0035] In one embodiment, a passivation layer 48 is formed on an upper surface of the photo TFT 12 to cover and protect the channels 46. The passivation layer 48

may include silicon nitride, silicon oxide, and combinations thereof. The passivation layer 48 may extend and cover the electrodes 16, 18 as well.

[0036] The present invention has particular application in detecting x-ray emissions in the industrial and medical industries. The photo TFT 12 may be used to detect x-ray emissions by covering the TFT 12 with a screen 50 to convert x-rays to light. The screen 50 includes scintillator material that absorbs x-rays and converts the energy to visible light. Scintillator material may yield many light photons for each received x-ray photon. The scintillator material usually consists of a high-atomic number material, which has high x-ray absorption, and a low-concentration activator that provides direct band transitions to facilitate visible photon emission.

[0037] Acceptable scintillator materials include granular like phosphors or crystalline like cesium iodide (CsI). Phosphors glow when exposed to x-rays. Various grain sizes and chemical mixtures may be used to produce a variety of resolution and brightness varieties. CsI provides a better combination of resolution and brightness. Because cesium has a high atomic number, it is an excellent x-ray absorber and is very efficient at converting x-ray to visible light. The scintillator material may be mixed with a glue binder and coated onto plastic sheets to form the screen 50. In one embodiment the scintillator material includes relatively low cost external phosphor such as Kodak® LANEX, which has a Gd<sub>2</sub>O<sub>2</sub>S:Tb layer to convert X-rays to green light with a wavelength of 544 nm.

[0038] In operation, the dark current of the photo TFT 12 may be significant and create noise in an image. In order to compensate, the dark image may be stored in a memory and subtracted from the light image. The dark current may also exhibit some drift over time, which affects the gray scale accuracy and image quality. This may be minimized by periodically, e.g. every minute, interrupting the light exposure and retaking the dark reference image.

[0039] Referring to Figure 5, a cross-sectional view of an embodiment of a storage capacitor 20 and a readout TFT 24 coupled to one another is show. The storage capacitor 20 may be embodied as a stacked capacitor having multiple layers and is deposited on a substrate 40. A stacked capacitor increases the dynamic range of the sensor element 10 and requires less space thereby increasing the space available for the photo TFT 12. In one embodiment, the capacitor 20 has a top electrode 52, bottom electrode 54, and a center electrode 56. The center electrode 56 is separated from the top and bottom electrodes 52, 54 by first and

second dielectric layers 58, 60. The center electrode 56 may include Ni or a Ni alloy and, in the embodiment shown, couples to the source electrode 22 of the readout TFT 24.

[0040] The readout TFT 24 may have a conventional structure and a manufacturing process similar to that of a TFT in an array for an AMLCD. The TFT 24 includes a gate electrode 28 deposited on the upper surface of the insulating substrate 40. The gate electrode 28 may include Cu, Cr, Al, Ta, Ti, or combinations thereof and is deposited through known methods such as sputtering or vapor deposition. The gate electrode may then be patterned by photolithography or other known methods. A gate insulator 62 covers the gate electrode 28 and may include silicon nitride, silicon oxide, tantalum oxide, or combinations thereof. The gate insulator 62 may be the same layer that serves as a dielectric layer 60 for the storage capacitor 20.

[0041] A semiconductor layer 64 is deposited on the gate insulator 62 above the gate electrode 28 using known sputtering and deposition methods. The semiconductor layer 64 may include a-Si, p-Si, or the like and further include a doping layer, such as a n+ layer, that contacts the source and drain electrodes 22, 32. The source and drain electrodes 22, 32 are deposited and patterned using known methods and, with the semiconductor layer 64, form a channel 66.

[0042] A passivation layer 68, which may also be the same layer as passivation layer 48, covers and protects the channel 66. The passivation layer 68 may include silicon nitride, silicon oxide, or other suitable dielectric material and may also extend and serve as a dielectric layer 58 for the storage capacitor 20.

[0043] In one embodiment, which departs from conventional TFT structures, a light shield 70 may be disposed on the upper surface of the passivation layer 68 to cover the channel 66. The readout TFT 24 may be exposed to the same light level as the photo TFT 12. Shielding prevents a charge from leaking from the storage capacitor 20 through the readout TFT 24. The light shield 70 is opaque and may include Cr or other suitable material. In an alternative embodiment, the light shield 70 may also extend and serve as the top electrode 52 or as an additional electrode for the storage capacitor 20. An additional electrode increases the value of the storage capacitor 20.

**[0044]** Referring to Figure 6, a graph is shown illustrating the relative photocurrents of an a-Si photodiode and an a-Si photo TFT as an inverse function of

channel length (L). The photo TFT is configured with its gate electrode 14 coupled to its source electrode 16 as taught by the present invention. As illustrated, the resulting photocurrent of the photo TFT exceeds that of the photodiode for certain values of L. In the photodiode, the photocurrent 72 is proportional to L, whereas, in the photo TFT, the photocurrent 74 is proportional to 1/L.

[0045] At a certain value of L, which is approximately 10 to  $20~\mu m$ , the conversion efficiency of photons into current becomes equal for the two devices. For smaller values of L, the photo TFT becomes more efficient. This is because the photocurrent 72 in the photo diode is a primary photocurrent with a gain that cannot exceed unity. One photon generates not more than one electron-hole pair, since the photo diode has blocking contacts for electrons and holes when reverse biased. Therefore, only one charge carrier can contribute to the photocurrent per absorbed photon. In the photo TFT, the source and drain contacts may be embodied as n+layers so that electrons can be injected from the contacts and replenish the photocurrent. Thus, a secondary electron photocurrent occurs which can have a gain more than 1 when the electron lifetime exceeds the transit time from source to drain.

[0046] According to the present invention, there is provided an image sensor array having a substrate with addressable pixels. Each pixel defined by a sensor element 10 that has a photo TFT 12, storage capacitor 20, and a readout TFT. Each sensor element 10 is in electrical communication with a control circuit (not shown) to operate the sensor elements. The photo TFT 12 includes a doped semiconductor material that generates a current channel in response to receive light and effectively discharges the storage capacitor 20.

[0047] TFT manufacturing for flat panel applications is a standard process which reduces the cost of the image sensor of the present invention. Whereas PIN diodes and TFTs require separate processes to manufacture and can require 8 or more photomasks, an image sensor of the present invention can be constructed with 3 to 5 photomasks. A photo TFT can yield photocurrents that exceed that of a PIN diode.

[0048] It will be obvious to those having skill in the art that many changes may be made to the details of the above-described embodiments of this invention without departing from the underlying principles thereof. The scope of the present invention should, therefore, be determined only by the following claims.

## <u>Claims</u>

- 1. An image sensor for sensing received image, comprising:

- a substrate;

- a photo TFT disposed on the substrate to generate a photocurrent responsive to the received image, the photo TFT including,

- a gate electrode,

- a source electrode coupled to the gate electrode,

- a drain electrode, and

- a semiconductor layer coupled to the source and drain electrodes; and

- a storage capacitor disposed on the substrate and coupled to the source electrode and drain electrode of the photo TFT, the storage capacitor storing a charge generated by the photocurrent.

- 2. The image sensor of claim 1 wherein the storage capacitor comprises a stacked capacitor.

- 3. The image sensor of claim 1 wherein the semiconductor layer includes a n+ layer in contact with the source and drain electrodes.

- 4. The image sensor of claim 1 wherein the source electrode and the drain electrode of the photo TFT each include a plurality of extending members, the extending members of the source electrode interdigitated with the extending members of the drain electrode.

- 5. The image sensor of claim 1 wherein the semiconductor layer of the photo TFT includes amorphous silicon.

- 6. The image sensor of claim 1 wherein the photo TFT includes a gate insulator disposed between the respective gate electrode and semiconductor layer and preventing contact between the gate electrode and the semiconductor layer.

- 7. The image sensor of claim 1 wherein the gate electrode is selected from a group consisting of Cu, Cr, Al, Ta, and Ti.

- 8. The image sensor of claim 1 further comprising a passivation layer disposed on the photo TFT.

- 9. The image sensor of claim 8 wherein the passivation layer is selected from the group consisting of silicon nitride, silicon oxide, and tantalum oxide.

- 10. The image sensor of claim 1 further comprising a screen disposed adjacent the photo TFT to convert received x-rays to visible light.

- 11. An image sensor for sensing a received image, comprising:

a substrate;

a photo TFT disposed on the substrate to generate a photocurrent responsive to the received image, the photo TFT including,

- a gate electrode,

- a source electrode coupled to the gate electrode,

- a drain electrode, and

- a semiconductor layer coupled to the source and drain electrodes;

a storage capacitor disposed on the substrate and coupled to the source electrode and drain electrode of the photo TFT, the storage capacitor storing a charge generated by the photocurrent; and

- a readout TFT disposed on the substrate, including,

- a gate electrode coupled to a select line,

- a source electrode coupled to the drain electrode of the photo TFT,

- a drain electrode coupled to a data line, and

- a semiconductor layer coupled to the source and drain electrodes.

- 12. The image sensor of claim 11 wherein the storage capacitor comprises a stacked capacitor.

- 13. The image sensor of claim 12 wherein the storage capacitor includes a center electrode coupled to the source electrode of the readout TFT.

- 14. The image sensor of claim 11 wherein the semiconductor layer of the photo TFT includes a n+ layer in contact with the source and drain electrodes.

- 15. The image sensor of claim 11 wherein the source electrode and the drain electrode of the photo TFT each include a plurality of extending members, the extending members of the source electrode interdigitated with the extending members of the drain electrode.

- 16. The image sensor of claim 11 wherein the semiconductor layer of the photo TFT includes amorphous silicon.

- 17. The image sensor of claim 11 wherein the photo TFT and the readout TFT each include a gate insulator disposed between the respective gate electrode and semiconductor layer and preventing contact between the gate electrode and the semiconductor layer.

- 18. The image sensor of claim 11 wherein the gate electrode is selected from a group consisting of Cu, Cr, Al, Ta, and Ti.

19. The image sensor of claim 11 further comprising a passivation layer disposed on the photo TFT and the readout TFT.

- 20. The image sensor of claim 19 wherein the passivation layer is selected from the group consisting of silicon nitride, silicon oxide, and tantalum oxide.

- 21. The image sensor of claim 19 further comprising a light shield disposed on the passivation layer substantially above the readout TFT.

- 22. The image sensor of claim 11 further comprising a screen disposed adjacent the photo TFT to convert received x-rays to visible light.

- 23. An image sensor for sensing a received image, comprising:

- a substrate;

- a plurality of bias lines disposed on the substrate;

- a plurality of data lines disposed on the substrate;

- a plurality of select lines disposed on the substrate;

- a plurality of photo TFTs disposed on the substrate to generate a photocurrent responsive to the received image, each photo TFT including,

- a gate electrode coupled to a corresponding bias line,

- a source electrode,

- a drain electrode, and

- a semiconductor layer coupled to the source and drain electrodes;

- a plurality of storage capacitors disposed on the substrate, each storage capacitor coupled to the source electrode and drain electrode of a corresponding photo TFT, each storage capacitor storing a charge generated by a photocurrent; and

- a plurality of readout TFTs disposed on the substrate, each readout TFT including,

- a gate electrode coupled to a corresponding select line,

- a source electrode coupled to the drain electrode of a corresponding photo TFT and coupled to the storage capacitor,

- a drain electrode coupled to a corresponding data line, and

- a semiconductor layer coupled to the source and drain electrodes, wherein each readout TFT passes a current to a corresponding date line in

- 24. The image sensor of claim 23 wherein the gate electrode and the source electrode of the photo TFT are coupled to one another.

response to the discharge of a corresponding storage capacitor.

25. The image sensor of claim 23 wherein the semiconductor layers of each photo TFT and readout TFT include amorphous silicon.

- 26. The image sensor of claim 23 wherein the storage capacitors include a stacked capacitor.

- 27. The image sensor of claim 26 wherein each storage capacitor includes a center electrode coupled to the source electrode of a corresponding readout TFT.

- 28. The image sensor of claim 23 wherein the source electrode and the drain electrode of the photo TFTs each include a plurality of extending members, the extending members of the source electrode interdigitated with the extending members of the drain electrode.

- 29. The image sensor of claim 23 wherein each photo TFT and readout TFT include a gate insulator disposed between the respective gate electrode and semiconductor layer and preventing contact between the gate electrode and the semiconductor layer.

- 30. The image sensor of claim 23 further comprising a passivation layer disposed on each photo TFT and readout TFT.

- 31. The image sensor of claim 31 further comprising a plurality of light shields disposed on the passivation layer substantially above a corresponding readout TFT.

- 32. The image sensor of claim 23 further comprising a screen disposed adjacent to the photo TFTs to convert received X-rays to visible light.

- 33. An image sensor for sensing received image, comprising: a substrate;

- a photo TFT disposed on the substrate to generate a photocurrent responsive to the received image, the photo TFT including,

- a gate electrode,

- a source electrode,

- a drain electrode coupled to the gate electrode, and

- a semiconductor layer coupled to the source and drain electrodes; and

- a storage capacitor disposed on the substrate and coupled to the source electrode and drain electrode of the photo TFT, the storage capacitor storing a charge generated by the photocurrent.

- 34. The image sensor of claim 33 wherein the storage capacitor comprises a stacked capacitor.

35. The image sensor of claim 33 wherein the semiconductor layer includes a n+ layer in contact with the source and drain electrodes.

- 36. The image sensor of claim 33 wherein the source electrode and the drain electrode of the photo TFT each include a plurality of extending members, the extending members of the source electrode interdigitated with the extending members of the drain electrode.

- 37. The image sensor of claim 33 wherein the semiconductor layer of the photo TFT includes amorphous silicon.

- 38. The image sensor of claim 33 wherein the photo TFT includes a gate insulator disposed between the respective gate electrode and semiconductor layer and preventing contact between the gate electrode and the semiconductor layer.

- 39. The image sensor of claim 33 wherein the gate electrode is selected from a group consisting of Cu, Cr, Al, Ta, and Ti.

- 40. The image sensor of claim 33 further comprising a passivation layer disposed on the photo TFT.

- 41. The image sensor of claim 40 wherein the passivation layer is selected from the group consisting of silicon nitride, silicon oxide, and tantalum oxide.

- 42. The image sensor of claim 33 further comprising a screen disposed adjacent the photo TFT to convert received x-rays to visible light.

FIG. 1B

FIG. 2

4/7

FIG. 3

FIG. 4

7/7

FIG. 6