(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3870129号

(P3870129)

(45) 発行日 平成19年1月17日(2007.1.17)

(24) 登録日 平成18年10月20日(2006.10.20)

(51) Int.C1.

F 1

|             |             |                  |      |      |      |

|-------------|-------------|------------------|------|------|------|

| <b>G09G</b> | <b>3/22</b> | <b>(2006.01)</b> | G09G | 3/22 | H    |

| <b>G09G</b> | <b>3/20</b> | <b>(2006.01)</b> | G09G | 3/20 | 612K |

| <b>HO4N</b> | <b>5/66</b> | <b>(2006.01)</b> | G09G | 3/20 | 612U |

| <b>HO4N</b> | <b>9/12</b> | <b>(2006.01)</b> | G09G | 3/20 | 622C |

G09G 3/20 (2006.01)

G09G 3/20 (2006.01)

G09G 3/20 (2006.01)

G09G 3/20 (2006.01)

請求項の数 11 (全 100 頁) 最終頁に続く

|              |                               |           |                                            |

|--------------|-------------------------------|-----------|--------------------------------------------|

| (21) 出願番号    | 特願2002-190675 (P2002-190675)  | (73) 特許権者 | 000001007<br>キヤノン株式会社<br>東京都大田区下丸子3丁目30番2号 |

| (22) 出願日     | 平成14年6月28日 (2002.6.28)        | (74) 代理人  | 100085006<br>弁理士 世良 和信                     |

| (65) 公開番号    | 特開2003-228317 (P2003-228317A) | (74) 代理人  | 100100549<br>弁理士 川口 嘉之                     |

| (43) 公開日     | 平成15年8月15日 (2003.8.15)        | (74) 代理人  | 100106622<br>弁理士 和久田 純一                    |

| 審査請求日        | 平成15年10月10日 (2003.10.10)      | (72) 発明者  | 阿部 直人<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社 内  |

| (31) 優先権主張番号 | 特願2001-210066 (P2001-210066)  | (72) 発明者  | 嵯峨野 治<br>東京都大田区下丸子3丁目30番2号 キ<br>ヤノン株式会社 内  |

| (32) 優先日     | 平成13年7月10日 (2001.7.10)        |           |                                            |

| (33) 優先権主張国  | 日本国 (JP)                      |           |                                            |

| (31) 優先権主張番号 | 特願2001-232591 (P2001-232591)  |           |                                            |

| (32) 優先日     | 平成13年7月31日 (2001.7.31)        |           |                                            |

| (33) 優先権主張国  | 日本国 (JP)                      |           |                                            |

| (31) 優先権主張番号 | 特願2001-364562 (P2001-364562)  |           |                                            |

| (32) 優先日     | 平成13年11月29日 (2001.11.29)      |           |                                            |

| (33) 優先権主張国  | 日本国 (JP)                      |           |                                            |

前置審査

最終頁に続く

(54) 【発明の名称】表示器の駆動方法及びそれを利用した表示装置

## (57) 【特許請求の範囲】

## 【請求項 1】

複数の走査配線と複数の変調配線とを有する表示器を駆動するための駆動方法において、

水平走査期間毎に、前記複数の走査配線から選択された走査配線に走査選択信号を供給する工程と、

水平走査期間毎に、前記複数の変調配線に少なくともパルス幅を変調した変調信号を供給する工程と、を含み、

前記走査配線に前記走査選択信号が供給される期間が、前記変調配線に供給される変調信号の最大継続期間に対応した長さになるように定められ、

前記変調信号は、水平同期信号を分周して得たクロック信号をカウントすることで決まるパルス幅を有することを特徴とする駆動方法。

## 【請求項 2】

前記水平走査期間の和によって定まる表示画像のフレーム走査期間を、少なくとも複数のフレーム走査期間に亘って一定の値に維持する請求項 1 に記載の駆動方法。

## 【請求項 3】

前記水平走査期間に下限値を定め、当該水平走査期間に前記変調配線に供給される変調信号の最大継続期間が該下限値に満たない場合に、当該変調信号にブランкиング期間を追加する請求項 1 又は 2 に記載の駆動方法。

## 【請求項 4】

前記水平走査期間に下限値を定め、当該水平走査期間における前記走査選択信号の選択期間が該下限値に満たない場合に、当該走査選択信号にランクイング期間を追加する請求項1又は2に記載の駆動方法。

**【請求項5】**

前記水平走査期間に上限値を定め、当該水平走査期間に前記変調配線に供給される変調信号の最大継続時間が該上限値を越えないように、前記変調信号の継続時間を定める請求項1～4のうち何れかに記載の駆動方法。

**【請求項6】**

複数の走査配線と複数の変調配線とを有する表示器を駆動するための表示器の駆動方法において、

10

水平走査期間毎に、前記複数の走査配線から選択された走査配線に走査選択信号を供給する工程と、

水平走査期間毎に、前記複数の変調配線に画像データに基づいて変調された変調信号を供給する工程と、を含み、

画像データに基づいて、前記表示器の画面中央の走査配線上の画素の水平走査期間が、少なくとも、前記画面上方又は下方にある別の走査配線上の画素の水平走査期間よりも長くなるよう制御することを特徴とする駆動方法。

**【請求項7】**

画像データを、各水平走査期間に対応して設定された倍率でゲイン調整した後に、変調駆動回路に供給する請求項1～5のうち何れかに記載の駆動方法。

20

**【請求項8】**

表示装置において、

複数の走査配線と複数の変調配線とを有する表示器と、

水平走査期間毎に、前記複数の走査配線から選択された走査配線に走査選択信号を供給する走査駆動回路と、

水平走査期間毎に、前記複数の変調配線に少なくともパルス幅を変調した変調信号を供給する変調駆動回路と、

前記走査配線に前記走査選択信号が供給される期間が、前記変調配線に供給される変調信号の最大継続時間に対応した長さになるように制御する駆動制御回路と、を含み、

30

前記変調駆動回路は、水平同期信号を分周して得たクロック信号をカウントして前記変調信号のパルス幅を決定することを特徴とする表示装置。

**【請求項9】**

表示装置において、

複数の走査配線と複数の変調配線とを有する表示器と、

水平走査期間毎に、前記複数の走査配線から選択された走査配線に走査選択信号を供給する走査駆動回路と、

水平走査期間毎に、前記複数の変調配線に少なくともパルス幅を変調した変調信号を供給する変調駆動回路と、

入力された映像信号に基づいて各々の画素の輝度を補正するための補正画像データを算出する補正画像データ算出部と、

40

前記補正画像データに基づいて少なくとも2つの前記走査選択信号の選択期間を、垂直走査期間内において、互いに異ならしめるように前記走査駆動回路を制御する駆動制御回路と、を含み、

前記変調駆動回路は、水平同期信号を分周して得たクロック信号をカウントして前記変調信号のパルス幅を決定することを特徴とする表示装置。

**【請求項10】**

複数の走査配線と複数の変調配線とを有する表示器を備える表示装置の駆動制御方法であって、

水平走査期間毎に、前記複数の走査配線から選択された走査配線に走査選択信号を供給する工程、

50

水平走査期間毎に、前記複数の変調配線に画像データに基づいて変調された変調信号を供給する工程、

画像データに基づいて少なくとも2つの水平走査期間及びそれら水平走査期間における前記走査選択信号の選択期間を、垂直走査期間内において、互いに異ならしめるか、

少なくとも2つの行上の画素の輝度を異ならせるべく、それらに対応した少なくとも2つの水平走査期間及び／又はそれら水平走査期間における前記走査選択信号の選択期間を、垂直走査期間内で、互いに異ならしめるように、

前記水平走査期間を決定するためのタイミング信号を生成する工程、

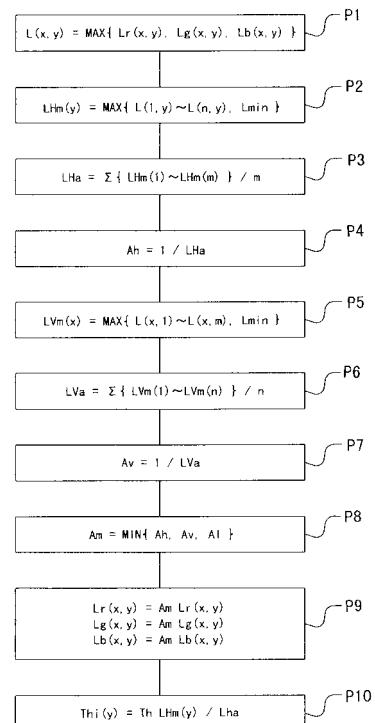

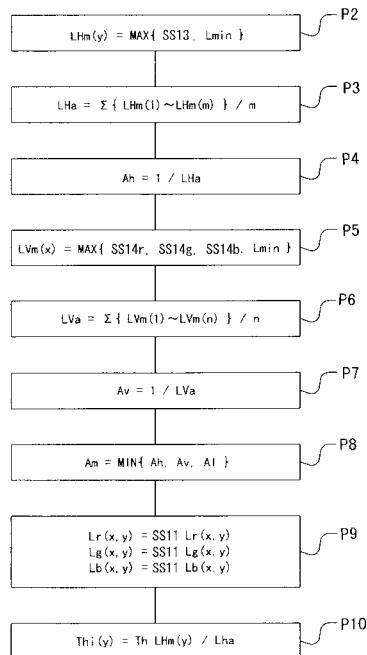

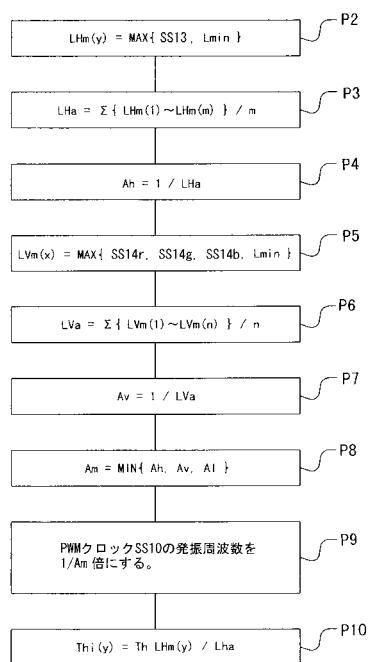

行毎の画素の最大画像データと平均画像データから水平輝度レベル係数（A<sub>h</sub>）を求め、

10

水平輝度レベル係数（A<sub>h</sub>）及び係数の上限値（A<sub>1</sub>）から輝度レベル係数の最小値（A<sub>m</sub>）を求め、

各画素の画像データを前記輝度レベル係数の最小値（A<sub>m</sub>）を基に補正する工程、

を含むことを特徴とする駆動制御方法。

#### 【請求項 11】

複数の走査配線と複数の変調配線とを有する表示器を備える表示装置の駆動制御方法であって、

水平走査期間毎に、前記複数の走査配線から選択された走査配線に走査選択信号を供給する工程、

水平走査期間毎に、前記複数の変調配線に画像データに基づいて変調された変調信号を供給する工程、

画像データに基づいて少なくとも2つの水平走査期間及びそれら水平走査期間における前記走査選択信号の選択期間を、垂直走査期間内において、互いに異ならしめるか、

少なくとも2つの行上の画素の輝度を異ならせるべく、それらに対応した少なくとも2つの水平走査期間及び／又はそれら水平走査期間における前記走査選択信号の選択期間を、垂直走査期間内で、互いに異ならしめるように、

前記水平走査期間を決定するためのタイミング信号を生成する工程、

行毎の画素の最大画像データと平均画像データから水平輝度レベル係数（A<sub>h</sub>）を求め、

列毎の画素の最大画像データと平均画像データから垂直輝度レベル係数（A<sub>v</sub>）を求め、

30

これら水平輝度レベル係数（A<sub>h</sub>）、垂直輝度レベル係数（A<sub>v</sub>）及び係数の上限値（A<sub>1</sub>）から輝度レベル係数の最小値（A<sub>m</sub>）を求め、

各画素の画像データを前記輝度レベル係数の最小値（A<sub>m</sub>）を基に補正する工程、

を含むことを特徴とする駆動制御方法。

#### 【発明の詳細な説明】

##### 【0001】

##### 【発明の属する技術分野】

本発明は、電子放出素子、エレクトロルミネッセンス（EL）素子、LED素子、プラズマ発光素子、液晶素子などを用いた表示素子に画像を表示する表示装置及びその駆動方法に関するものである。

##### 【0002】

特に、自発光型の複数の表示素子をマトリクス状に配したマトリクス型表示器のマルチプレキシング駆動方法に関するものである。

##### 【0003】

##### 【従来の技術】

上述した複数の表示素子は、複数の行配線（走査配線）と複数の列配線（変調配線）とかなるマトリクス配線に供給する信号を制御して、表示を行う。

##### 【0004】

以下、蛍光体を発光させて画像を形成する自発光型の表示器を例に挙げて説明する。

50

**【0005】**

この種の表示器では、電子放出素子などから放出された粒子のエネルギーを利用して蛍光体を励起するが、この蛍光体を励起する励起強度および／又は励起時間によって明るさが変わる。

**【0006】**

このような表示装置は、例えば、特開平7-235256号公報（米国特許第6,313,571号）、特開平8-45415号公報、特開2000-29425号公報（ヨーロッパ公開特許第936,596号）、特開平8-248920号公報等に開示されている。

**【0007】**

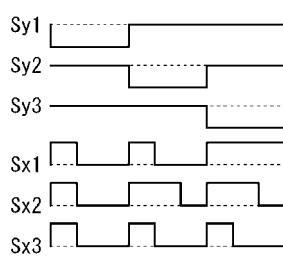

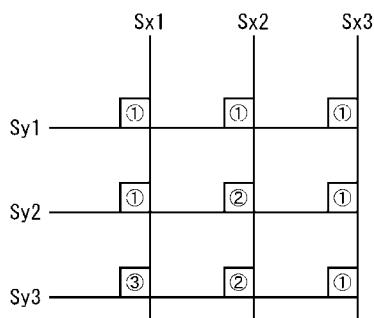

図76は、従来の表示器を駆動するための駆動信号の一例を示し、図77はその駆動信号により駆動される3行3列のマトリクスの表示器の表示状態を示している。

**【0008】**

ここでは、1フレームの画像を表示するための1垂直走査期間は、3つの水平走査期間からなり、S<sub>y1</sub>、S<sub>y2</sub>、S<sub>y3</sub>は、それぞれ走査配線に供給される走査信号を示している。ここでは、各走査配線において、負の電圧が印加される選択期間が水平走査期間となっており、全ての走査配線において、各選択期間は一定の値になっている。

**【0009】**

S<sub>x1</sub>、S<sub>x2</sub>、S<sub>x3</sub>は、それぞれ変調配線に供給される変調信号（データ信号）を示している。ここでは、画素の輝度レベル（階調レベル）に応じてパルス幅を変調するパルス幅変調方式による変調信号の例を示しており、変調信号S<sub>x1</sub>は表示すべき輝度レベルが1、1、3の信号であり、これが変調配線に時系列的に供給される。同様に、変調信号S<sub>x2</sub>は表示すべき輝度レベルが1、2、2の信号であり、変調信号S<sub>x3</sub>は表示すべき輝度レベルが1、1、1の信号である。

**【0010】**

こうして、走査配線を順次選択しながら、各水平走査期間において、選択された行上有る3つの画素の輝度を定める。ここでは、輝度レベル3の点灯を行う3行目1列上の画素が最も明るく点灯することになる。

**【0011】**

一般的に、表示装置は明るい画面が好まれる傾向がある。特に、暗い画像の中に部分的に明るい個所が含まれる場合、画像の暗い部分の詳細を十分な画質で表示するために明るい部分の輝度（ピーク輝度）は相対してより明るく表示できることが望ましい。

**【0012】****【発明が解決しようとする課題】**

しかしながら、上述したように、時分割で走査配線を順次選択する、所謂、線順次走査を行う表示装置の場合、一般的に各画素の点灯時間の最大値は水平走査期間内の選択期間に制限されるので表示装置の表示輝度もこれに対応して制限される。

**【0013】**

また、走査選択信号が印加されてはいても変調信号が印加されない期間は、他の処理に必要なブランкиング期間を除くと、画素の点灯には寄与しないが走査配線には電圧が印加される無駄な期間となっている。

**【0014】**

本発明の目的は、表示する画像のピーク輝度を大きくして、良好な画像を得ることができる表示器の駆動方法及びそれを利用した表示装置を提供することにある。

**【0015】**

本発明の目的は、無駄な期間の発生を抑制して、良好な画像を得ることができる表示器の駆動方法及びそれを利用した表示装置を提供することにある。

**【0016】****【課題を解決するための手段】**

本発明の骨子は、

複数の走査配線と複数の変調配線とを有する表示器を駆動するための表示器の駆動方法において、

水平走査期間毎に、前記複数の走査配線から選択された走査配線に走査選択信号を供給する工程、

水平走査期間毎に、前記複数の変調配線に画像データに基づいて変調された変調信号を供給する工程、

を含み、

少なくとも2つの水平走査期間における前記走査選択信号の選択期間を、垂直走査期間内で、互いに異ならしめたことを特徴とする。

#### 【0017】

10

特に、複数の走査配線と複数の変調配線とを有する表示器を駆動するための表示器の駆動方法において、水平走査期間毎に、前記複数の走査配線から選択された走査配線に走査選択信号を供給する工程、水平走査期間毎に、前記複数の変調配線に画像データに基づいて変調された変調信号を供給する工程、を含み、画像データに基づいて少なくとも2つの水平走査期間及びそれら水平走査期間における前記走査選択信号の選択期間を、垂直走査期間内で、互いに異ならしめるか、少なくとも2つの行上の画素の輝度を異ならせるべく、それらに対応した少なくとも2つの水平走査期間及びノ又はそれら水平走査期間における前記走査選択信号の選択期間を、垂直走査期間内で、互いに異ならしめるとより良い。

#### 【0018】

本発明においては、必要に応じて、以下の構成を採用することも好ましいものである。

20

#### 【0019】

水平走査期間に各変調配線に供給される変調信号のうちその継続時間が最も長い最大継続期間に対応した長さになるように、当該水平走査期間に前記走査配線に供給される前記走査選択信号の選択期間を定める。

#### 【0020】

前記走査配線に供給される前記走査選択信号の選択期間を設定し、設定された選択期間に合わせて、水平走査期間に前記変調配線に供給される変調信号の継続期間を定める。

#### 【0021】

水平走査期間を設定し、設定された水平走査期間に合わせて、当該水平走査期間に前記走査配線に供給される前記走査選択信号の選択期間と、当該水平走査期間に前記変調配線に供給される変調信号の継続期間を定める。

30

#### 【0022】

選択された走査配線上の各画素における、表示輝度又は補正画像データの最大値に応じて、当該走査配線に供給される前記走査選択信号の選択期間を定める。

#### 【0023】

水平走査期間の上限値又は下限値のうち少なくとも何れか一方を定め、それによって定められる可変範囲内で水平走査期間を変更する。

#### 【0024】

前記水平走査期間の和によって定まる表示画像のフレーム走査期間を、少なくとも複数のフレーム走査期間に亘って一定の値に維持する。

40

#### 【0025】

前記水平走査期間に下限値を定め、当該水平走査期間に前記変調配線に供給される変調信号の最大継続時間が該下限値に満たない場合に、当該変調信号にブランкиング期間を追加する。

#### 【0026】

前記水平走査期間に下限値を定め、当該水平走査期間における前記走査選択信号の選択期間が該下限値に満たない場合に、当該走査選択信号にブランкиング期間を追加する。

#### 【0027】

前記水平走査期間に上限値を定め、当該水平走査期間に前記変調配線に供給される変調信号の最大継続時間が該上限値を越えないように、前記変調信号の継続時間を定める。

50

**【0028】**

前記上限値は、前記水平走査期間から所定のプランギング期間を引いた値である。

**【0029】**

前記水平走査期間は、クロック数を基準にして、その長さが制御される。

**【0030】**

前記画像データは入力された映像信号の輝度データを含み、当該輝度データに応じて、少なくとも前記変調信号の継続時間が変調される。

**【0031】**

前記画像データは入力された映像信号の輝度データと補正データとを含み、これら輝度データ及び補正データに応じて、少なくとも前記変調信号の継続時間が定められる。 10

**【0032】**

前記補正データは、所望の輝度と表示輝度の差を補償するための補正データである。

**【0033】**

前記補正データは、前記走査配線に生じる電圧降下により表示素子に印加される電圧の変化を補償するための補正データである。

**【0034】**

入力された映像信号の輝度データ及び補正データに応じて定められた各水平走査期間のゲイン調整及び／又は上限値調整を行う。

**【0035】**

前記水平走査期間の和によって定まる表示画像の垂直走査期間が所定の値を超えないよう 20 に、入力された映像信号の輝度データ及び補正データに応じて定められた各水平走査期間のゲイン調整を行う。

**【0036】**

前記表示器の画面中央の走査配線上の画素の水平走査期間が、少なくとも、前記画面上方又は下方にある別の走査配線上の画素の水平走査期間よりも長い。

**【0037】**

前記画像データを、各水平走査期間に対応して設定された倍率でゲイン調整した後に、変調駆動回路に供給する。

**【0038】**

クロック信号の周波数を変更することにより、前記水平走査期間を決める。 30

**【0039】**

本発明の別の骨子は、

表示装置において、

複数の走査配線と複数の変調配線とを有する表示器と、

水平走査期間毎に、前記複数の走査配線から選択された走査配線に走査選択信号を供給する走査駆動回路と、

水平走査期間毎に、前記複数の変調配線に画像データに基づいて変調された変調信号を供給する変調駆動回路と、

を有し、

少なくとも2つの水平走査期間における前記走査選択信号の選択期間が、垂直走査期間内において、互いに異なるように前記走査駆動回路を制御する駆動制御回路を備えたことを特徴とする。 40

**【0040】**

特に、画像データに基づいて少なくとも2つの水平走査期間及びそれら水平走査期間における前記走査選択信号の選択期間を、垂直走査期間内で、互いに異ならしめるか、少なくとも2つの行上の画素の輝度を異ならせるべく、それらに対応した少なくとも2つの水平走査期間及び／又はそれら水平走査期間における前記走査選択信号の選択期間を、垂直走査期間内で、互いに異ならしめるように、前記走査駆動回路を制御する駆動制御回路を備えることが好ましいものである。

**【0041】**

本発明においては、必要に応じて、以下の構成を採用することも好ましいものである。

**【0042】**

前記駆動制御回路は、入力された映像信号から各水平走査期間における輝度データの最大値を検出し、その最大値に基づいて、前記走査選択信号の選択期間を設定する。

**【0043】**

前記駆動制御回路は、入力された映像信号から各水平走査期間における輝度データを補正して得られる補正画像データの最大値を検出し、その最大値に基づいて、前記走査選択信号の選択期間を設定する。

**【0044】**

前記駆動制御回路は、水平走査期間を変更し得る可変範囲内で設定された水平走査期間に合わせて、前記走査選択信号の選択期間及び前記変調信号の継続期間を定める。 10

**【0045】**

前記駆動制御回路は、入力された映像信号から各水平走査期間における輝度データを補正して得られる補正画像データの最大値を検出し、その最大値に基づいて、前記走査選択信号の選択期間を設定するとともに、

前記水平走査期間の和によって定まる表示画像の垂直走査期間が、所定の値となるように少なくとも一つの水平走査期間を調整する。

**【0046】**

前記少なくとも一つの水平走査期間を調整するゲイン調整器及び／又はリミッターを備えている。 20

**【0047】**

前記駆動制御回路は、水平走査期間を調整するために、入力された映像信号から各水平走査期間における輝度データを補正して得られる補正画像データを1フレーム分格納するフレームメモリを備えている。

**【0048】**

前記フレームメモリは、2つのフレームメモリを有しており、一方にデータを書き込む間に、他方からデータを読み出すように、制御される。

**【0049】**

前記フレームメモリから、1水平走査期間の補正画像データを複数層に分けて並列に読み出し。 30

前記各層に対応して設けられた複数のシフトレジスタに入力する。

**【0050】**

前記駆動制御回路は、設定された各水平走査期間に応じて、前記走査選択信号の選択期間と、前記変調信号の継続時間とを定める。

**【0051】**

前記水平走査期間の和によって定まる表示画像の垂直走査期間が、少なくとも、複数の垂直走査期間に亘って一定の値に維持される。

**【0052】**

前記表示器の画面中央の走査配線上の画素の水平走査期間が、少なくとも、前記画面上方又は下方にある別の走査配線上の画素の水平走査期間よりも長い。 40

**【0053】**

前記駆動制御回路は、前記画像データを、設定された水平走査期間に合わせて調整する。

**【0054】**

前記画像データの調整後に、前記変調駆動回路により、該画像データから前記変調信号を生成する。

**【0055】**

前記表示器は、自発光型の表示器である。

**【0056】**

前記表示器は、電子放出素子を含む表示素子を複数有する。

**【0057】**

50

クロック信号の周波数を変更することにより、前記水平走査期間を決める。

**【0058】**

本発明の更に別の骨子は、

上述した表示装置に利用される駆動制御方法において、

前記水平走査期間を決定するためのタイミング信号を生成することを特徴とする。

**【0059】**

本発明においては、必要に応じて、以下のような構成を採用することも好ましいものである。

**【0060】**

所定の走査期間内の最大画像データに基づいて、前記タイミング信号を生成する。 10

**【0061】**

前記画像データは、輝度データと補正データとを含む。

**【0062】**

行毎の画素の最大画像データと平均画像データに基づいて、前記水平走査期間を定める。

**【0063】**

少なくとも行又は列毎の最大画像データに基づいて、画像データを調整し、メモリに格納された画像データを調整された調整画像データに置き換える。

**【0064】**

行毎の画素の最大画像データと平均画像データから水平輝度レベル係数（A<sub>h</sub>）を求め、水平輝度レベル係数（A<sub>h</sub>）及び係数の上限値（A<sub>1</sub>）から輝度レベル係数の最小値（A<sub>m</sub>）を求める。 20

各画素の画像データを前記輝度レベル係数の最小値（A<sub>m</sub>）を基に調整する。

**【0065】**

行毎の画素の最大画像データと平均画像データから水平輝度レベル係数（A<sub>h</sub>）を求め、列毎の画素の最大画像データと平均画像データから垂直輝度レベル係数（A<sub>v</sub>）を求め、これら水平輝度レベル係数（A<sub>h</sub>）、垂直輝度レベル係数（A<sub>v</sub>）及び係数の上限値（A<sub>1</sub>）から輝度レベル係数の最小値（A<sub>m</sub>）を求める。

各画素の画像データを前記輝度レベル係数の最小値（A<sub>m</sub>）を基に調整する。

**【0066】**

又、画像データは、最小値（A<sub>m</sub>）を基にして決定される調整用クロックに応じて調整されると良い。 30

**【0067】**

クロック信号の周波数を変更することにより、前記水平走査期間を決める。

**【0068】**

上記駆動制御方法をプログラムにより実行する。

**【0069】**

上記駆動制御方法を集積回路により実行する。

**【0070】**

上記駆動制御方法を実行する集積回路を設計するための設計資産。

**【0071】**

40 【発明の実施の形態】

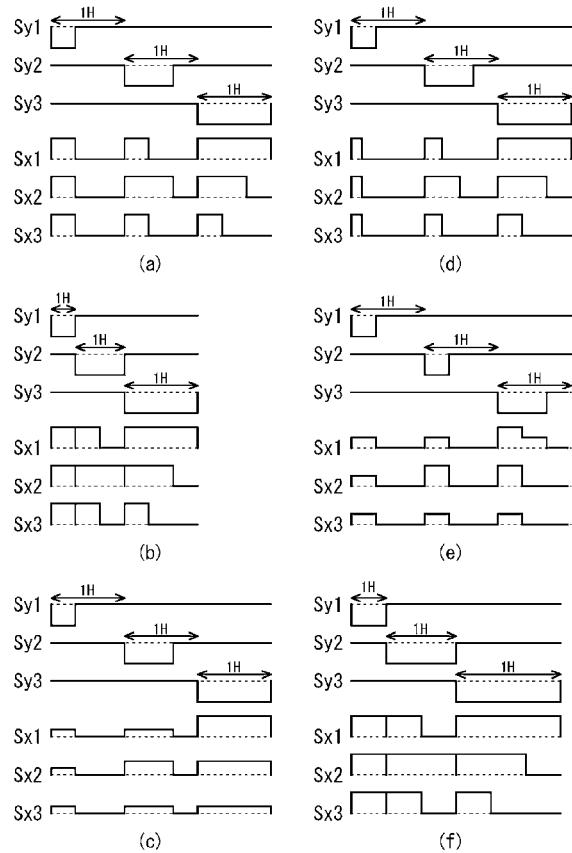

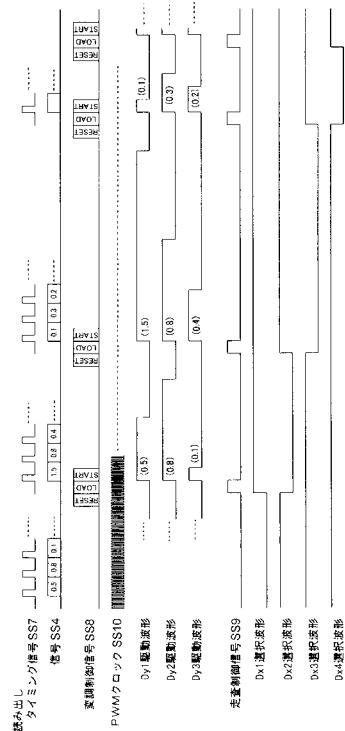

図1(a)～図1(f)は、表示装置に用いられる駆動信号の形態を示しており、それぞれ図77と同様に表示状態を呈するための駆動信号を示している。

**【0072】**

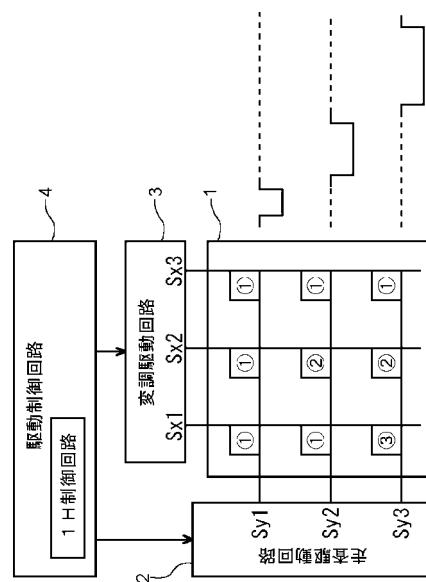

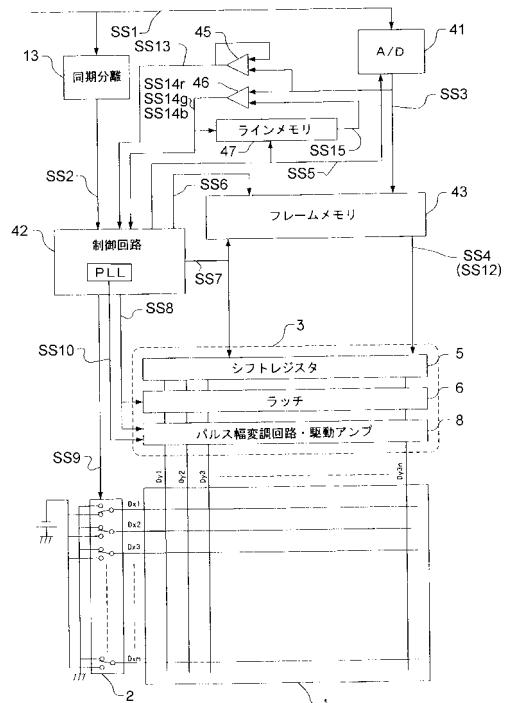

図2は、本発明の表示装置を示しており、1は表示器、2は走査信号S<sub>y1</sub>, S<sub>y2</sub>, S<sub>y3</sub>を表示器1に供給するための走査駆動回路、3は変調信号S<sub>x1</sub>, S<sub>x2</sub>, S<sub>x3</sub>を表示器1に供給するための変調駆動回路であり、これらの回路は水平走査期間1Hの選択期間を制御する1H制御回路を有する駆動制御回路4により制御される。

**【0073】**

要するに、図2に示す表示装置は、複数の走査配線と複数の変調配線とを有する表示器1 50

と、水平走査期間 1 H 毎に、複数の走査配線から選択された走査配線に走査選択信号を供給する走査駆動回路 2 と、水平走査期間毎に、前記複数の変調配線に画像データに基づいて変調された変調信号を供給する変調駆動回路 3 と、を有し、少なくとも 2 つの水平走査期間における前記走査選択信号の選択期間が、垂直走査期間 1 V 内において、互いに異なるように前記走査駆動回路を制御する駆動制御回路 4 を備えたことを特徴とする。

#### 【0074】

図 1 ( a ) の形態においては、走査信号 S y 1 , S y 2 , S y 3 は、水平走査期間 1 H における対応する走査配線が選択される選択期間の長さ（ここでは、ローレベルになっている期間）が異なっており、何れかの変調配線にハイレベルの変調信号が印加されている期間のみに、ローレベルの走査選択信号が印加されるようになっている。ここでは、画素の輝度レベルに応じてパルス幅を変調するパルス幅変調方式による変調信号の例を示しており、変調信号 S x 1 は輝度レベルが 1 、 1 、 3 の信号であり、変調信号 S x 2 は輝度レベルが 1 、 2 、 2 の信号であり、変調信号 S x 3 は輝度レベルが 1 、 1 、 1 の信号である。水平走査期間 1 H 内において走査選択信号が印加されていない期間はブランкиング期間となっている。

#### 【0075】

各水平走査期間 1 H においては、3 本の変調配線に供給される変調信号のうち、そのパルス幅（継続時間）が最大となる変調信号に合わせて、走査選択信号の選択期間が互いに相違していることがわかる。ここでは、入力映像信号に依存して決まる画素の輝度レベルに応じて、水平走査期間 1 H を異ならしめることが好ましいものである。

#### 【0076】

図 1 ( b ) の形態においては、走査信号 S y 1 , S y 2 , S y 3 の、走査選択信号が供給されるローレベルの選択期間が水平走査期間 1 H となっている。3 つの水平走査期間 1 H の長さはそれぞれ異なっており、図 1 ( a ) の水平走査期間と比べると、順に 1 / 3 , 2 / 3 , 3 / 3 の長さとなっている。そして、何れかの変調配線に変調信号 S x 1 , S x 2 , S x 3 が印加されている期間のみに、走査選択信号が印加されるようになっている。

#### 【0077】

このように、図 1 ( b ) の形態では、走査選択信号が印加されない期間を短縮し、1 垂直走査期間、即ち 1 フレーム期間を短くすることにより、フレーム周波数を上げて、輝度をより一層向上させている。更には、各水平走査期間を任意の倍率で伸ばして、元の 1 フレーム期間と等しくなるように調整することも好ましいものである。

#### 【0078】

図 1 ( c ) の形態は、走査信号 S y 1 , S y 2 , S y 3 として、図 1 ( a ) と同様の信号を採用し、変調信号 S x 1 , S x 2 , S x 3 としては、画素の輝度レベルに応じて電圧振幅を変調する振幅変調方式による変調信号の例を示している。変調信号 S x 1 は輝度レベルが 1 、 1 、 3 の信号であり、変調信号 S x 2 は輝度レベルが 1 、 2 、 2 の信号であり、変調信号 S x 3 は輝度レベルが 1 、 1 、 1 の信号ではあるが、選択期間の長さが異なっているので、輝度の差はより大きくなっている。各選択期間に同期している変調信号 S x 1 , S x 2 , S x 3 のハイレベルの電圧振幅は、輝度レベルに応じて 3 つの電圧値の中から選択される。

#### 【0079】

図 1 ( d ) の形態は、走査信号 S y 1 , S y 2 , S y 3 として、図 1 ( c ) と同様の信号を採用し、変調信号 S x 1 , S x 2 , S x 3 としては、画素の輝度レベルに応じてパルス幅を変調するパルス幅変調方式による変調信号の例を示している。変調信号 S x 1 は輝度レベルが 1 、 1 、 3 の信号であり、変調信号 S x 2 は輝度レベルが 1 、 2 、 2 の信号であり、変調信号 S x 3 は輝度レベルが 1 、 1 、 1 の信号ではあるが、選択期間の長さが異なっているので、輝度の差はより大きくなっている。

#### 【0080】

図 1 ( c ) 、図 1 ( d ) の形態においては、同じ輝度データを表示する場合であったとしても、ユーザーの要求や予め設定した仕様に応じて、所定の行上の画素の表示輝度を他の

10

20

30

40

50

行上の画素の表示輝度より高める場合などに、より好ましく用いられる。

#### 【0081】

図1(e)の形態は、変調信号S<sub>x</sub>1, S<sub>x</sub>2, S<sub>x</sub>3として、画素の輝度レベルに応じてパルス幅及び電圧振幅の両方を変調する変調方式による変調信号の例を示している。変調信号S<sub>x</sub>1は輝度レベルが1、1、3の信号であり、変調信号S<sub>x</sub>2は輝度レベルが1、2、2の信号であり、変調信号S<sub>x</sub>3は輝度レベルが1、1、1の信号であり、図77と同じ表示状態を呈するための信号となっている。輝度レベルの上昇に伴い、その電圧振幅をスロット単位で増大させる。それが所定の振幅値となってからは、パルス幅をスロット単位で長くし、そのパルス幅を所定数スロットにする。一方、走査信号S<sub>y</sub>1, S<sub>y</sub>2, S<sub>y</sub>3は、水平走査期間1H内の変調信号のパルス幅に合わせて、選択期間を定めている。10

#### 【0082】

また、必要に応じて図1(c)～図1(e)の形態を変更し、図1(b)と同様に走査選択電圧が印加されていないプランキング期間を短縮することで水平走査期間を短縮し、1フレーム期間を短くすることも好ましく、更には、各水平走査期間が一定のプランキング期間を持つようにすることも好ましいものである。或いは、プランキング期間を無くすか短くした後、元の1フレーム期間と同じになるように各水平走査期間にゲインをかけるか、基準クロック信号の周波数を変更して各水平走査期間を延ばすことも好ましいものである。この方法により図1(b)を変形した波形を図1(f)に示す。図1(f)の形態の1フレーム期間は、図1(a)と同じであり、図1(b)より長い。20

#### 【0083】

以上のように、本発明においては、複数の走査配線と複数の変調配線とを有する表示器1を駆動するための表示器の駆動方法において、水平走査期間1H毎に、前記複数の走査配線から選択された走査配線に走査選択信号を供給する工程、水平走査期間1H毎に、前記複数の変調配線に画像データに基づいて変調された変調信号を供給する工程、とを含み、少なくとも2つの水平走査期間における前記走査選択信号の選択期間を、垂直走査期間1V内で、互いに異ならしめたことを特徴とする。

#### 【0084】

図1(a)～図1(f)の形態はいずれも、各画素にて点灯すべき輝度レベルに応じて水平走査期間を決め、それに応じて、走査選択信号の選択期間と変調信号の最大継続期間としてのパルス幅とを定めるものである。特に、図1(a)～図1(f)の形態は水平走査期間に変調配線に供給される変調信号の最大継続期間(パルス幅)に合うように、当該水平走査期間に走査配線に供給される走査選択信号の選択期間を定める場合に好ましく用いられる。30

#### 【0085】

また、図1(c)～図1(e)の形態は、走査配線に供給される走査選択信号の選択期間を予め設定し、設定された選択期間に合うように、水平走査期間に変調配線に供給される変調信号の最大継続期間を定める場合により好ましく用いることができる。

#### 【0086】

本発明の表示器に用いられる表示素子としては、表面伝導型の電子放出素子や電界放出型の電子放出素子と、蛍光体と、を組み合わせた表示素子が好ましく用いられるが、それ以外のプラズマ表示素子、無機EL表示素子、有機EL表示素子、LED表示素子、液晶表示素子、プラズマアドレス型液晶表示素子、マイクロミラー素子などを用いることができる。40

#### 【0087】

本発明に用いられる電子放出素子としては、米国特許第5,066,883号公報、特開平2-257551号公報、特開平4-28137号公報などに開示されている表面伝導型の電子放出素子、或いは、BSD型、Spindt型、MIS型、MIM型、ダイヤモンド粒子型、カーボンナノチューブやグラファイトナノファイバー他の炭素繊維型などの電子放出素子が挙げられる。50

**【 0 0 8 8 】**

本発明に用いられる走査信号としては、変調信号と協働して、駆動すべき表示素子に応じた走査選択電圧と走査非選択電圧とを印加できる信号であればよく、図1(a)～図1(f)に図示した波形、或いは後述する実施形態の波形に限定されるものではない。

**【 0 0 8 9 】**

本発明に用いられる変調信号としては、表示すべき画素の輝度が大きいほど表示のための電圧レベルが印加される継続期間(パルス幅)を長くするパルス幅変調信号、又は、表示すべき画素の輝度が大きいほど電圧振幅(波高値)を大きくする振幅変調信号が挙げられ、或いは、パルス幅変調信号と振幅変調信号とを組み合わせた変調信号を用いることも好ましいものである。パルス幅変調信号と振幅変調信号とを組み合わせた変調方式は、例え 10 ば、特開平10-39825号公報などに開示されている。

**【 0 0 9 0 】**

更には、表示すべき画素の輝度が大きいほど表示素子に流す電流を大きくする電流変調信号を用いることもできる。

**【 0 0 9 1 】**

本発明においては、水平走査期間における走査選択信号が供給される選択期間の長さは、入力される映像信号に応じて定めることができる。或いは、入力される映像信号とは別に、表示特性に応じて定めることもできる。つまり、前者の場合には、画像が変われば、その変化に対応した走査配線における選択期間、更には必要に応じて、水平走査期間が変更される。後者の場合には、走査配線毎に選択期間、更には必要に応じて水平走査期間が予め決められているので、変調信号は、その決められた選択期間内で適宜変調されることになる。 20

**【 0 0 9 2 】**

更に、各走査配線における水平走査期間の選択期間の長さを入力される映像信号に応じて定める場合、走査配線毎に最適化を行って定めてもよし、全画素の輝度を考慮して最適化を行っても良い。これらの場合、選択期間或いは水平走査期間は、選択された走査配線上の画素に供給されるべき変調信号のパルス幅が最大となるところの変調信号に合わせて、決められるが、各輝度レベル(階調レベル)に一対一に対応させる必要はなく、連続する複数の輝度レベルに対して一つの値の水平走査期間を割り当てても良い。

**【 0 0 9 3 】**

また、選択期間或いは水平走査期間に上限値又は下限値の少なくとも何れか一方の値を決めておき、その値をそれぞれ超過しない範囲内において、選択期間或いは水平走査期間を変更することも好ましいものである。 30

**【 0 0 9 4 】**

1垂直走査期間を一定にする場合には、各走査配線における選択期間を所定の倍率で伸縮させるゲイン調整を行うことも好ましいものである。また、画素を消灯状態とするプランギング期間の長さを伸縮することにより水平走査期間を調整して、1垂直走査期間を調整することも好ましいものである。

**【 0 0 9 5 】**

実際の信号処理においては、入力映像信号から直接、或いは、入力映像信号を変換して、表示器の各画素において点灯すべき輝度データを抽出し、その輝度データを基に変調信号を生成する。 40

**【 0 0 9 6 】**

本発明に用いられる変調信号は、画像データ即ち輝度データのみに基づいて変調された信号に限定されるものではなく、補正データなどを加味した画像データ(補正画像データ)を基にして変調されたものであってもよい。

**【 0 0 9 7 】**

画素の表示輝度が本来表示したい所望の輝度からズレて、差が生じてしまう場合には、その差を補償するように変調信号を補正することも好ましいものである。例えば、走査配線及び/又は変調配線の抵抗とそこに流れる電流による電圧降下によって、画素を構成する 50

素子へ印加される実効駆動電圧が減少してしまう場合には、その減少分を補償するよう に、予め変調信号を補正しておくことが好ましい。この減少量は同一走査配線上の画素の表示状態にも依存する。変調信号のパルス幅を長くすることで補償を行う場合には、補正後の変調信号に応じて、水平走査期間の選択期間を定めることが好ましいものである。具体的には、変調前に画像データを補正しておいて、その補正された画像データに基づいて変調を行えばよい。

#### 【0098】

以下、より具体的な実施形態について説明する。

#### 【0099】

##### (第1の実施形態)

10

行方向にN個、列方向にM個の合計 $N \times M$ 個の冷陰極素子（表示素子）を2次元的にマトリクス状に配列し、それらを行方向に設けられたM本の行配線（走査配線）と列方向に設けられたN本の列配線（変調配線）により単純マトリクス配線してなるマルチ電子源を備えた構成のものが知られている。

#### 【0100】

マトリクス配線された多数の冷陰極素子をマルチプレキシング駆動する方法としては、マトリクスの1行分の素子群（1行分の素子群は1本の行配線に接続されている）を同時に駆動する。

#### 【0101】

すなわち、1本の行配線に所定の選択電圧を印加すると共に、その行配線に接続されたN個の冷陰極素子のうち駆動対象となるものに接続している列配線のみに所定の変調電圧を印加し、行配線電位と列配線電位との電位差によって1行分の複数の素子を同時に駆動する。そして、選択行配線を次々と切り替えて全ての行を走査していく、視覚の残像現象を利用して2次元的な画像を形成するのである。

20

#### 【0102】

この方法によれば、1素子ずつ選択していく方法と比較して、各素子に割り当てられる駆動時間がN倍長く確保されるため、画像表示装置の輝度を高くすることができるという利点がある。

#### 【0103】

ところで、上記構成にあっては、1行分のN個の冷陰極素子は1本の行配線に接続されており、各素子ごとにその接続位置が異なっている。したがって、1行分の素子群を同時に駆動する場合には、配線抵抗による電圧降下の影響を受けて、各素子の輝度にバラツキが生じてしまう。具体的にいえば、行配線の両端側から選択電圧を印加する構成の場合、行配線の中央付近ほど電圧降下が大きく、両端に向かうほど電圧降下が小さくなるので、N本の列配線に同じ電位の変調電圧を印加したとしても、中央付近の輝度が両端付近の輝度に比べて暗くなってしまうのである。

30

#### 【0104】

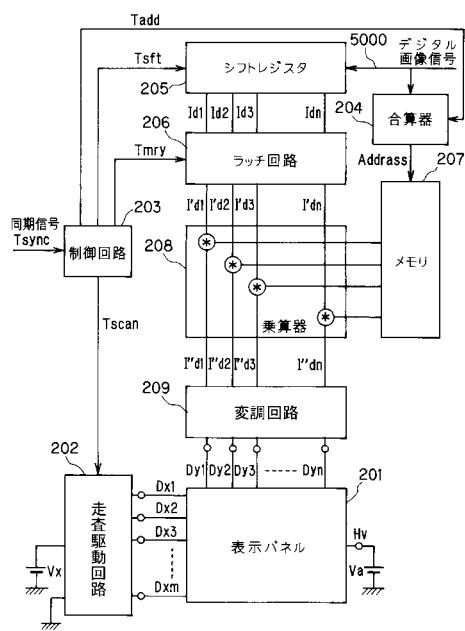

このため、例えば特開平8-248920号公報には、行配線の配線抵抗による電圧降下に起因する輝度低下を補償するために、統計演算により補正データを算出し、入力画像データと補正データとを合成する構成が開示されている。同公報では、図3に示すように、メモリ手段207から出力された補正データを、各列配線毎に設けられた乗算器208にて画像データに乗算し、その補正後の画像データを変調回路209に転送する構成となっている。

40

#### 【0105】

ここで、201は表示器、202は走査駆動回路、203は制御回路、204は合算器、205はシフトレジスタ、206はラッチ回路である。

#### 【0106】

行配線の電圧降下に起因する輝度低下分を補償するために行う補正では、上記公報のように入力画像データに対して補正データを乗算するか、あるいは補正データを加算することが特開平8-248920号公報で開示されているが、このとき、ディジタル回路に特有

50

のオーバーフローの問題が生ずることがある。

**【0107】**

すなわち、画像データに対して補正データを乗算または加算して得た補正後の画像データをそのまま従来の変調信号発生器に入力すると、変調信号発生器で取り扱うことのできるデータ幅を超えてしまった場合に、ビットの折り返しが起こり、表示画像の反転などが生じてしまうのである。

**【0108】**

具体的な例で説明すると、1水平走査期間内をたとえば8 bitのデータ幅で回路が設計してある場合、取り扱うことのできるデータの最大値は「255（十進数）」である。ここで画像データとして「250」が入力され、それに加算すべき補正データが「33」であったとすると、補正画像データは「283」となるが、変調信号発生器で出力するパルス幅は「283」とはならず、ビットの折り返しが起こり「27」となってしまう。このように、補正画像データを変調信号発生器に入力すると、本来高輝度であるはずの部分が暗く表示されてしまい画像に乱れが生ずる場合がある。

10

**【0109】**

この場合には、画像データの最大値を制限するリミッタを設けたり、画像データに一律にゲインをかけたりルックアップテーブル（LUT）を用いた補正を行うなどしてデータ値を予め小さくしておくことにより、オーバーフローを未然に防止したり、補正された画像データに対して、オーバフローしないように一律にゲインをかけたりするとよい。

**【0110】**

20

ビットの折り返しが起こり、表示画像の反転などの画像の乱れが生ずるという基本的な問題は、本発明者らによる検討の結果、防ぐことが可能となり、電圧降下による補正をかけ良好な画質で表示が可能になった。しかしながら厳密に表示画像を観察すると、リミッタによる方法やLUT補正による方法では、最大値を超える画像データが全て同じ輝度で表示される等、画像によっては階調性が失われ不自然な画像再現となってしまうことがある。また、ゲインをかける方法では、画像によっては輝度が損なわれたりすることがあった。

**【0111】**

つまり、走査配線に生じる電圧降下を補正するということは、電圧降下による輝度の低下を駆動時間を増やすことによって補正していることに他ならない。しかしながら、駆動時間を延ばさなくてはならない補正に対して、現実的に決まっている水平走査時間により制限される駆動時間の最大時間に抑えることは、即ち輝度を低下させることに他ならないのである。

30

**【0112】**

本実施の形態は上述した問題を解決するに適した表示装置として、水平走査期間を制御する駆動方法を採用したものである。即ち、本形態の表示装置は、複数の表示素子を複数の走査配線と複数の変調配線によってマトリクス状に結線してなる表示器と、入力された画像データに対し、前記走査配線の抵抗分によって発生する電圧降下の影響を補正した補正画像データを算出する補正画像データ算出手段と、前記補正画像データの最大値を各走査配線毎に検出するライン最大値検出手段と、該ライン最大値検出手段によって検出された補正画像データの最大値に応じて各走査配線の選択期間を決定する選択期間制御手段と、該選択期間制御手段によって決定された各走査配線の選択期間に従って各走査配線の走査を行う走査駆動回路と、前記補正画像データに応じてパルス幅変調した変調信号を各変調配線に印加する変調駆動回路と、を備えたものである。

40

**【0113】**

また、本実施形態による表示装置の駆動方法は、複数の表示素子を複数の走査配線と複数の変調配線によってマトリクス状に結線してなる表示器を備えた表示装置の駆動方法であって、入力された画像データに対し、前記走査配線の抵抗分によって発生する電圧降下の影響を補正した補正画像データを算出するステップと、前記補正画像データの最大値を各走査配線毎に検出するステップと、検出された補正画像データの最大値に応じて各走査配

50

線の選択時間を決定するステップと、決定された各走査配線の選択時間に従って各走査配線の走査を行い、前記補正画像データに応じてパルス幅変調した変調信号を各変調配線に印加するステップと、を含む。

**【0114】**

本実施形態の補正回路において、入力画像データに応じて電圧降下のために生じる表示画像の品質低下を計算し、それを補償するための補正データを求め、画像データに補正を施す。

**【0115】**

さらに、この補正回路は、補正を施した画像データ（補正画像データ）の水平走査ライン毎の最大値を検出し、その最大値に応じて各走査配線の選択時間の割り当てを行う。

10

**【0116】**

以下、本実施の形態に係る画像表示装置の表示パネルの概観、表示パネルの電気的接続、表面伝導型放出素子の特性、表示パネルの駆動方法、及び、このような表示パネルによって画像を表示する際の走査配線の電気抵抗に起因する駆動電圧の低下の機構について説明した後に、本実施形態の特徴である電圧降下の影響に対する補正方法及び装置について詳しく説明する。

**【0117】**

（画像表示装置の概観）

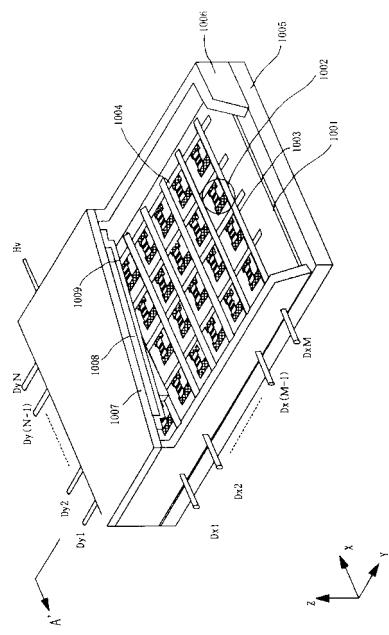

図4は、本実施の形態に用いられる表示パネルの斜視図であり、内部構造を示すためにパネルの一部を切り欠いて示している。図中、1005はリアプレート、1006は側壁、1007はフェースプレートであり、1005～1007により表示パネルの内部を真空中に維持するための気密容器を形成している。

20

**【0118】**

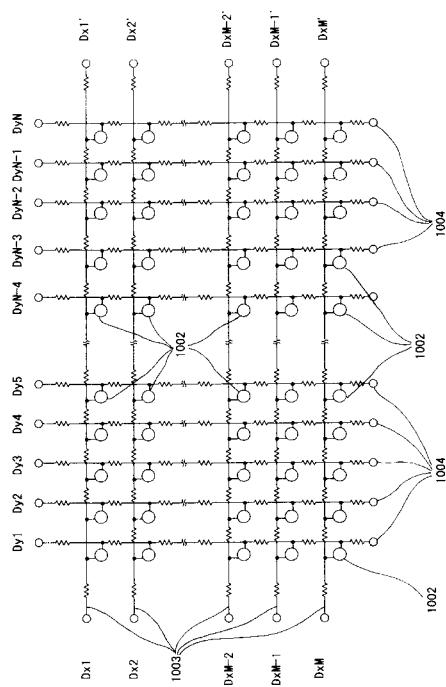

リアプレート1005には、基板1001が固定されているが、該基板上には冷陰極素子1002がN×M個形成されている。行配線（走査配線）1003、列配線（変調配線）1004及び冷陰極素子は図5のように接続されている。

**【0119】**

また、フェースプレート1007の下面には、蛍光膜1008が形成されている。本実施の形態に係る画像表示装置はカラー表示装置であるため、蛍光膜1008の部分にはCRTの分野で用いられる赤、緑、青、の3原色の蛍光体が塗り分けられている。蛍光体は、リアプレートの各画素（絵素）に対応してマトリクス状に形成された、冷陰極素子からの放出電子（放出電流）の照射される位置に対して、画素を形成するように構成されている。

30

**【0120】**

蛍光膜1008の下面にはメタルバック1009が形成されている。

**【0121】**

Hvは高圧端子でありメタルバックに電気的に接続されている。Hv端子に高電圧を印加することによりリアプレートとフェースプレートの間に高電圧が印加される。

**【0122】**

本実施の形態では、画素に冷陰極素子としての表面伝導型放出素子を有する構成を採用する。

40

**【0123】**

（表面伝導型放出素子の特性）

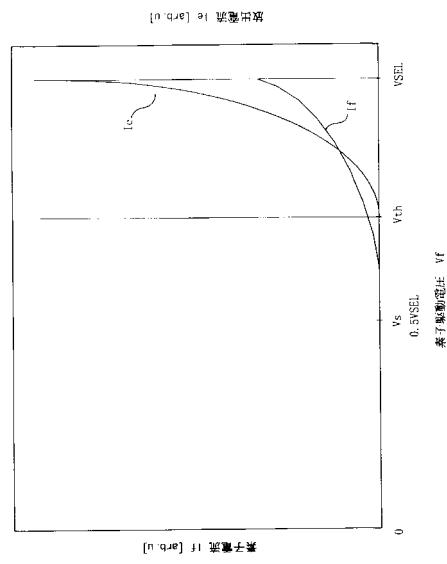

表面伝導型放出素子は、図6のような放出電流Ie対素子印加電圧Vf特性、および素子電流If対素子印加電圧Vf特性を有する。なお、放出電流Ieは素子電流Ifに比べて著しく小さく、同一尺度で図示するのが困難であるため、2つのグラフは各々異なる尺度で図示した。

**【0124】**

すなわち、放出電流Ieに関して以下に述べる3つの特性を有している。

**【0125】**

50

第一に、ある電圧（これを閾値電圧  $V_{th}$  と呼ぶ）以上の電圧を素子に印加すると急激に放出電流  $I_e$  が増加するが、一方、閾値電圧  $V_{th}$  未満の電圧では放出電流  $I_e$  はほとんど検出されない。すなわち、放出電流  $I_e$  に関して、明確な閾値電圧  $V_{th}$  を持った非線形素子である。

**【0126】**

また第二に、放出電流  $I_e$  は素子に印加する電圧  $V_f$  に依存して変化するため、電圧  $V_f$  を可変することにより、放出電流  $I_e$  の大きさを制御できる。

**【0127】**

また第三に、冷陰極素子は高速な応答性を有しているため、電圧  $V_f$  の印加時間により放出電流  $I_e$  の放出時間を制御できる。

**【0128】**

図4に示した表示パネルを用いた表示装置において、第一の特性を利用すれば、表示画面を順次走査して表示を行うことが可能である。すなわち、駆動中の素子には所望の発光輝度に応じて閾値電圧  $V_{th}$  以上の電圧を適宜印加し、非選択状態の素子には閾値電圧  $V_{th}$  未満の電圧を印加する。駆動する素子を順次切り替えることにより、表示画面を順次走査して表示を行うことが可能である。

**【0129】**

また、第二の特性を利用することにより、素子に印加する電圧  $V_f$  により、蛍光体の発光輝度を制御することができ、画像表示を行うことができる。

**【0130】**

また、第三の特性を利用することにより、素子に電圧  $V_f$  を印加する時間により、蛍光体の発光時間を制御することができ、画像の表示を行うことができる。

**【0131】**

本実施形態の表示装置では表示パネルの電子ビームの量を上記第三の特性を用いて変調を行った。

**【0132】**

（表示パネルの駆動方法）

図7を用いて本実施形態の表示パネルの駆動方法を具体的に説明する。

**【0133】**

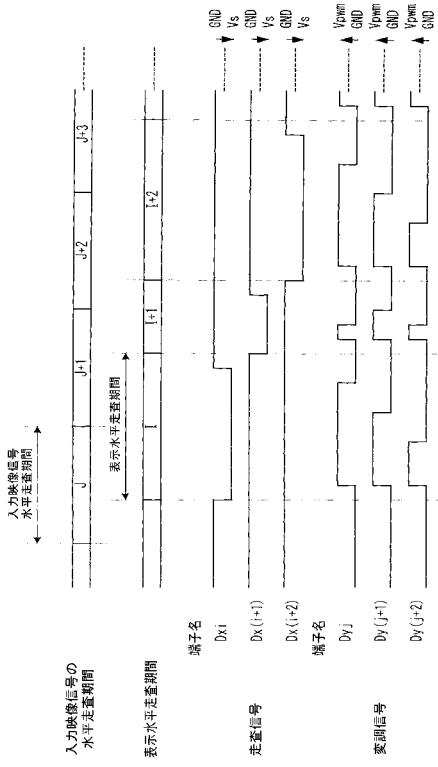

図7は本実施形態の表示パネルを駆動するための駆動信号のタイミングチャートである。

**【0134】**

$J$ 、 $J + 1$ 、 $J + 2$ 、 $J + 3$ は、表示装置に外部から入力される入力映像信号の水平走査期間を示している。一方、表示水平走査期間  $T$  は、表示装置の  $i$  行目の画素を発光させるための選択期間である。

**【0135】**

詳しくは後述するが、各々の表示水平走査期間は対応する走査配線上の変調配線の最大のパルス幅の時間より長くなるように割り当てられている。

**【0136】**

$i$  行目の画素を発光させるためには、 $i$  行目の走査配線の電圧供給端子  $D \times i$  に走査選択電圧  $V_s$  のパルスを印加して選択状態とする。また、それ以外の走査配線の電圧供給端子  $D \times k$  ( $k = 1, 2, \dots, M$ 、但し  $k \neq i$ ) は、非選択電圧  $V_{ns}$  のパルスを印加して非選択状態とする。

**【0137】**

本例では、選択電圧  $V_s$  を図6の電圧  $V_{SEL}$  の半分の -0.5V<sub>SEL</sub> に設定し、非選択電圧  $V_{ns}$  の電位は接地電位 GND とする。

**【0138】**

また変調配線の電圧供給端子には、電圧振幅  $V_{pwm}$  のパルス幅変調信号を供給した。 $j$  番目の変調配線に供給するパルス幅変調信号のパルス幅は、表示する画像の第  $i$  行第  $j$  列の画素の画像データの大きさ（輝度レベル）に応じて決定し、すべての変調配線に各々の画素の画像データの大きさに応じたパルス幅変調信号を供給する。

10

20

30

40

50

**【0139】**

本実施の形態では、電圧V<sub>pwm</sub>の電圧は+0.5V<sub>SEL</sub>に設定する。

**【0140】**

表面伝導型放出素子は、図6に示したように素子の両端に電圧V<sub>SEL</sub>が印加されると電子を放出させるが、印加電圧が放出閾値V<sub>th</sub>よりも小さい電圧ではまったく電子を放出しない。

**【0141】**

また、電圧V<sub>th</sub>は図6に示すように、0.5V<sub>SEL</sub>よりも大きいという特徴がある。

**【0142】**

このため、非選択電圧V<sub>ns</sub>が印加されている走査配線に接続された表面伝導型放出素子からは電子は放出されない。 10

**【0143】**

また同じように、パルス幅変調手段の出力が接地電位である期間（以降、出力が“L”の期間と呼ぶ）は、選択された走査配線上の表面伝導型放出素子の両端に印加される電圧パルスの電圧はV<sub>s</sub>であるため、電子は放出されない。

**【0144】**

選択電圧V<sub>s</sub>が印加された走査配線上の表面伝導型放出素子からは、パルス幅変調手段の出力がV<sub>pwm</sub>である期間（以降、出力が“H”的期間と呼ぶ）に応じて電子が放出される。電子が放出されれば放出された電子ビームの量に応じて前述の蛍光体が発光するため、放出された時間に応じた輝度で画素を発光させることができる。 20

**【0145】**

このような表示パネルの行を順次選択する線順次走査を行い、パルス幅変調することによって画像を表示する。

**【0146】**

表示水平走査期間のうち、選択電圧V<sub>s</sub>が印加される選択期間は、変調信号に応じてその長さが異なっており、選択電圧V<sub>s</sub>が印加されない期間は、必要に応じて設けられる一定のブランкиング期間となっている。 20

**【0147】**

こうして、表示水平走査期間Iは、その期間において、端子Dy1～DyNに供給される変調信号のパルス幅の最大値に応じた期間となっており、表示水平走査期間I+1は、端子Dy1～DyNに供給される変調信号のパルス幅の最大値に応じた短い期間となっており、表示水平走査期間I+2は、端子Dy1～DyNに供給される変調信号のパルス幅の最大値に応じて長い期間となっている。 30

**【0148】**

よって、表示水平走査期間I+2の輝度が向上している。

**【0149】**

（走査配線での電圧降下について）

上述したように、表示パネルの走査配線における電圧降下によって、走査配線上の電位が上昇することにより、表面伝導型放出素子に印加される電圧が減少するため、表面伝導型放出素子からの放出電流が低減してしまうことがある。 40

**【0150】**

表面伝導型放出素子の設計仕様や製法によても異なるが、表面伝導型放出素子の1素子分の素子電流は電圧V<sub>SEL</sub>を印加した場合に数100μA程度である。

**【0151】**

このため、ある水平走査期間において選択された走査配線上の1画素のみを発光させ、それ以外の画素は発光させない場合には、変調配線から選択行の走査配線に流入する素子電流は1画素分の電流（すなわち上述の数100μA）だけであるため、電圧降下はほとんど生じることではなく、発光輝度が低下することはない。

**【0152】**

しかし、ある水平走査期間において、選択された行の全画素を発光させる場合には、全変 50

調配線から選択状態としている走査配線に対し、全画素分の電流が流入するため、電流の総和は数 100 mA ~ 数 A となり、走査配線の配線抵抗によって走査配線上に大きな電圧降下が発生する。

#### 【 0153 】

走査配線上に電圧降下が発生すれば、表面伝導型放出素子の両端に印加される電圧が低下する。このため表面伝導型放出素子から発光される放出電流が低下してしまい、結果として発光輝度が低下してしまう。

#### 【 0154 】

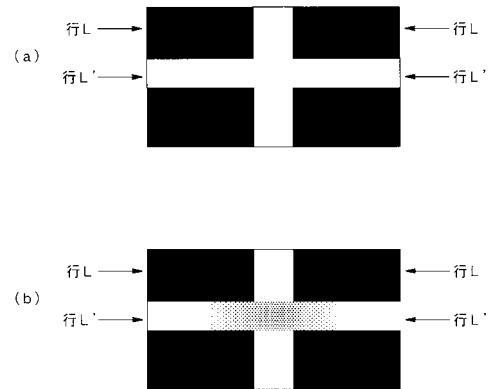

具体的に、表示画像として、図 8 ( a ) に示すような黒の背景に白い十字状のパターンを表示する場合、行 L を選択する際には、点灯させる画素の数が少ないため、その行の走査配線上にはほとんど電圧降下が生じない。その結果各画素の表面伝導型放出素子からは所望の量の放出電流が放出され、所望の輝度で発光させることができる。10

#### 【 0155 】

一方、行 L' を駆動する際には、その行 L' 上の全ての画素が点灯するため、走査配線上に電圧降下が発生し、各ピクセルの表面伝導型放出素子からの放出電流が減少する。その結果、行 L' 上の画素は輝度が低下することとなる。

#### 【 0156 】

このように、1 走査配線毎にそのラインの画像データの違いにより、電圧降下によって受ける影響が変化するため、図 8 ( a ) のような十字パターンを表示する際には図 8 ( b ) のような画像が表示されてしまっていた。20

#### 【 0157 】

なおこの現象は十字パターンに限るものではなく、たとえばウインドウパターンや、自然画像を表示した際にも発生するものである。

#### 【 0158 】

また、さらに複雑なことに、電圧降下の大きさはパルス幅変調によって変調を行うことにより 1 水平走査期間の中でも変化する性質を持っている。

#### 【 0159 】

各列に供給するパルス幅変調信号が、図 7 に示したように入力されるデータに対し、そのデータの大きさに対応したパルス幅の、立ち上がりが同期したパルス幅変調信号を出力する場合には、入力画像データにもよるが一般的には、1 水平走査期間のなかでは、パルスの立ち上がり直後ほど点灯している画素の数が多く、その後輝度の低い箇所から順に消灯していくため、点灯する画素の数は 1 水平走査期間の中では、時間を追って減少する。30

#### 【 0160 】

したがって走査配線上に発生する電圧降下の大きさも、1 水平走査期間の初めほど大きく次第に減少する傾向がある。

#### 【 0161 】

パルス幅変調信号は変調の 1 階調に相当する時間ごとに出力が変化するため、電圧降下の時間的な変化もパルス幅変調信号の 1 階調に相当する単位時間毎に変化する。

#### 【 0162 】

( 電圧降下の計算方法 )

電圧降下については以下の特徴がある。

#### 【 0163 】

i ) 一水平走査期間のある時点においては、走査配線上に発生する電圧降下は走査配線上で空間的に連続的な量であり非常に滑らかなカーブである。

#### 【 0164 】

i i ) 電圧降下の大きさは表示画像によって異なるが、パルス幅変調の 1 階調に相当する時間毎に変化するが、概略的には、パルスの立ち上がり部分ほど大きく、時間的には次第に小さくなるか、もしくはその大きさを維持するかのどちらかである。すなわち、図 7 のような駆動方法では、各変調配線に供給される変調信号が同時に立ち上がるため、1 水平走査期間の中で電圧降下の大きさが増加することはない。50

**【0165】**

そこで以下のような近似モデルにより簡略化して計算を行うことによって、計算量の低減を試みた。

**【0166】**

まず、 $i$ ) の特徴から、ある時点の電圧降下の大きさを計算するのに際して、数千本もの変調配線を数本～数十本の変調配線に集中化した縮退モデルによって近似的に簡略化して計算することを試みた。

**【0167】**

また、 $i$ i) の特徴から、1水平走査期間のなかに複数の基準時刻を設け、各基準時刻に対し電圧降下を計算することで電圧降下の時間変化を概略的に予測した。 10

**【0168】**

具体的には以下で説明する縮退モデルによる電圧降下の計算を複数の基準時刻に対して計算することによって、電圧降下の時間変化を概略的に予測した。

**【0169】**

(縮退モデルによる電圧降下の計算)

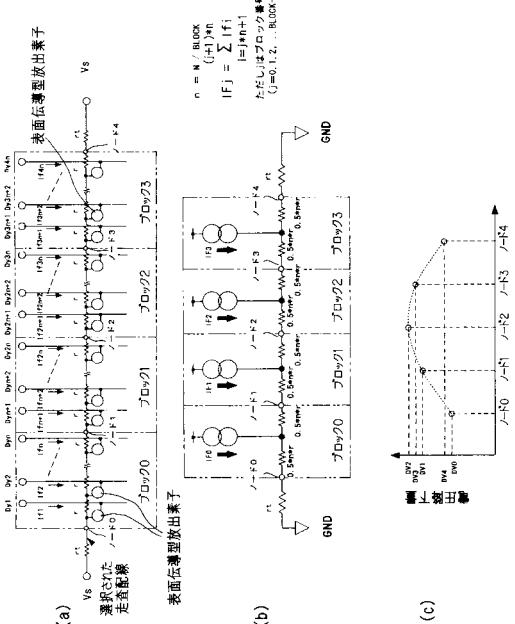

図9(a)は、本発明の縮退を行う際のブロック及びノードを説明するための図である。

**【0170】**

図9では簡略化するため、選択された走査配線と各変調配線およびその交差部に接続される表面伝導型放出素子のみを記載した。 20

**【0171】**

いま一水平走査期間の中のある時刻であって、選択された走査配線上の各画素の点灯状態(すなわち変調手段の出力が“H”であるか、“L”であるか)がわかっているものとする。

**【0172】**

この点灯状態において、各変調配線から選択された走査配線へ流れ込む素子電流を $I_{fi}$

( $i = 1, 2, \dots, N$ ;  $i$ は列番号)と定義する。

**【0173】**

また、同図に示すように、 $n$ 本の変調配線と選択された走査配線のそれと交差する部分及び、その交点に配置される表面伝導型放出素子を1つのグループとしてブロックを定義する。本例では、ブロック分けを行うことで4つのブロックに分割された。 30

**【0174】**

また、各々のブロックの境界位置においてノードという位置を設定した。ノードとは、縮退モデルにおいて走査配線上に発生する電圧降下量を離散的に計算するための水平位置(基準点)である。

**【0175】**

本例ではブロックの境界位置に、ノード0～ノード4の5つのノードを設定した。

**【0176】**

図9(b)は縮退モデルを説明するための図である。

**【0177】**

縮退モデルでは図9(a)の1ブロックに含まれる $n$ 本の変調配線を1本に縮退化し、縮退化された1本の変調配線が、走査配線のブロックの中央に位置するように接続した。 40

**【0178】**

また、縮退化された各々のブロックの変調配線には電流源が接続されており、各電流源から各々のブロック内の電流の総和 $I_{F0} \sim I_{F3}$ が流れ込むものとした。

**【0179】**

即ち、 $I_{Fj}$  ( $j = 0, 1, \dots, 3$ )は、数1の(式1)のように表される電流である。

**【数1】**

$$IF_j = \sum_{i=j \times n+1}^{(j+1) \times n} If_i \quad (\text{式 } 1)$$

## 【 0 1 8 0 】

また、走査配線の両端の電位が図 9 ( a ) の例では、行駆動回路の出力電圧  $V_s$  と同じであるのに対し、図 9 ( b ) では GND 電位としているのは、縮退モデルでは、変調配線から選択した走査配線に流れ込む電流を上記電流源によりモデリングしたことにより、走査配線上の各部の電圧降下量は、その給電部を基準電位 ( GND ) として各部の電圧 ( 電位差 ) を算出することにより計算できるためである。つまり、電圧降下を算出するまでの基準電位として規定した。10

## 【 0 1 8 1 】

また、表面伝導型放出素子を省略しているのは、選択された走査配線から見た場合に、変調配線から同等の電流が流れ込めば、表面伝導型放出素子の有無によらず、発生する電圧降下自体は変わらないためである。従って、ここでは、各ブロックの電流源から流れ込む電流値を各ブロック内の素子電流の総和の電流値 ( 式 1 ) に設定することで表面伝導型放出素子を無視した。

## 【 0 1 8 2 】

また、各ブロックの走査配線の配線抵抗は一区間の走査配線の配線抵抗  $r$  の  $n$  倍とした。20

ここで一区間とは走査配線の、ある変調配線との交差部とその隣の変調配線との交差部の間のことを探している。また本例では、一区間の走査配線の配線抵抗は均一であるものとした。

## 【 0 1 8 3 】

このような縮退モデルにおいて、走査配線上の各ノードにおいて発生する電圧降下量  $DV_0 \sim DV_4$  は数 2 に示すような積和形式の式により、簡単に計算することができる。

## 【 数 2 】

$$\begin{aligned} DV_0 &= a_{00} \times IF_0 + a_{01} \times IF_1 + a_{02} \times IF_2 + a_{03} \times IF_3 \\ DV_1 &= a_{10} \times IF_0 + a_{11} \times IF_1 + a_{12} \times IF_2 + a_{13} \times IF_3 \\ DV_2 &= a_{20} \times IF_0 + a_{21} \times IF_1 + a_{22} \times IF_2 + a_{23} \times IF_3 \\ DV_3 &= a_{30} \times IF_0 + a_{31} \times IF_1 + a_{32} \times IF_2 + a_{33} \times IF_3 \\ DV_4 &= a_{40} \times IF_0 + a_{41} \times IF_1 + a_{42} \times IF_2 + a_{43} \times IF_3 \end{aligned}$$

30

## 【 0 1 8 4 】

数 2 の式は、すなわち数 3 の ( 式 2 ) のように示すことができる。

## 【 数 3 】

$$DV_i = \sum_{j=0}^3 a_{ij} \times IF_j \quad (\text{式 } 2)$$

40

## 【 0 1 8 5 】

ただし、( 式 2 )において、 $a_{ij}$  は縮退モデルにおいて  $j$  番目のブロックだけに単位電流を注入したときに、 $i$  番目のノードに発生する電圧である。( 以下、これを  $a_{ij}$  の定義とする。 )  $a_{ij}$  はキルヒホフの法則により以下のように簡単に導出できる。

## 【 0 1 8 6 】

即ち、図 9 ( b )において、ブロック  $i$  の電流源からみた走査配線の左側の供給端子までの配線抵抗を  $r_{1i}$  ( $i = 0, 1, 2, 3, 4$ ) , 右側の供給端子までの配線抵抗を  $r_{ri}$  50

$i ( i = 0, 1, 2, 3, 4 )$ , ブロック 0 と左の供給端子との間の配線抵抗及びブロック 4 と右の供給端子との間の配線抵抗をいずれも  $r_t$  と定義すれば、数 4 のようになる。

## 【数 4】

```

r10 = rt + 0.5×n×r

rr0 = rt + 3.5×n×r

r11 = rt + 1.5×n×r

rr1 = rt + 2.5×n×r

r12 = rt + 2.5×n×r

rr2 = rt + 1.5×n×r

r13 = rt + 3.5×n×r

rr3 = rt + 0.5×n×r

```

10

## 【0 1 8 7】

さらに、数 5 のようにおくと、 $a_{ij}$  は、数 6 に示す（式 3）のように簡単に導出できる。ただし、数 5 において、 $A // B$  は、抵抗  $A$  と抵抗  $B$  の並列の抵抗値を表す記号であつて、 $A // B = A \times B / (A + B)$  である。

20

## 【数 5】

```

a = r10 // rr0 = r10×rr0 / (r10+rr0)

b = r11 // rr1 = r11×rr1 / (r11+rr1)

c = r12 // rr2 = r12×rr2 / (r12+rr2)

d = r13 // rr3 = r13×rr3 / (r13+rr3)

```

30

## 【数 6】

a00 = a × rt / r10

a10 = a × (rt + 3 × n × r) / rr0

a20 = a × (rt + 2 × n × r) / rr0

a30 = a × (rt + 1 × n × r) / rr0

a40 = a × rt / rr0

a01 = b × rt / r11

a11 = b × (rt + n × r) / r11

a21 = b × (rt + 2 × n × r) / rr1 10

a31 = b × (rt + n × r) / rr1

a41 = b × rt / rr1

a02 = c × rt / r12

a12 = c × (rt + n × r) / r12

a22 = c × (rt + 2 × n × r) / r12

a32 = c × (rt + n × r) / rr2

a42 = c × rt / rr2 20

a03 = d × rt / r13

a13 = d × (rt + n × r) / r13

a23 = d × (rt + 2 × n × r) / r13

a33 = d × (rt + 3 × n × r) / r13

a43 = d × rt / rr3

## 【0 1 8 8】

(式2)はブロック数が4でない場合においても、 $a_{i,j}$ の定義を顧みれば、キルヒホフの法則によって簡単に算出することができる。また本例のように走査配線の両側に給電端子を備えず片側のみに備える場合においても、 $a_{i,j}$ の定義に従って計算することにより簡単に算出できる。

## 【0 1 8 9】

なお、(式3)によって定義されるパラメータ $a_{i,j}$ は計算を行うたびに計算し直す必要はなく、一度計算してテーブルとして記憶しておけばよい。

## 【0 1 9 0】

さらに、(式1)で定めた各ブロックの総和電流 $I_{F0} \sim I_{F3}$ に対し、数7に示す(式4)のような近似を行った。

## 【数7】

$$I_{Fj} = \sum_{i=j \times n+1}^{(j+1) \times n} If_i = IFS \times \sum_{i=j \times n+1}^{(j+1) \times n} Count_i \quad (式4)$$

## 【0 1 9 1】

ただし、(式4)において $Count_i$ は選択された走査線上の $i$ 番目のピクセルが点灯状態である場合には1をとり、消灯状態である場合には0をとる変数である。 $IFS$ は表面伝導型放出素子1素子の両端に電圧 $VSEL$ を印加したときに流れる素子電流 $I_F$ に対し、0~1の間の値をとる係数をかけた量である。

10

20

30

40

50

## 【0192】

すなわち、数8に示す(式5)のように定義した。

## 【数8】

$$IFS = \alpha \times IF \quad (式5)$$

## 【0193】

(式4)は選択された走査配線に対し各ブロックの変調配線から該ブロック内の点灯数に比例した素子電流が流れ込むものとしている。この際1素子の素子電流IFに係数 $\alpha$ をかけたものを1素子の素子電流IFSとしたのは、電圧降下により走査配線の電圧が上昇することにより、素子電流の量が減少することを考慮した。10

## 【0194】

図9(c)は、ある点灯状態において、縮退モデルにより各ノードの電圧降下量DV0~DV4を計算した結果の一例である。

## 【0195】

電圧降下は非常に滑らかなカーブとなるため、ノードとノードの間の電圧降下は近似的には図の点線に示したような値をとると想定される。

## 【0196】

このように、本縮退モデルを用いれば、入力された画像データに対し所望の時点でのノードの位置での電圧降下を計算することが可能である。20

## 【0197】

以上、ある点灯状態における電圧降下量を、縮退モデルを用いて簡単に計算した。

## 【0198】

選択された走査配線上に発生する電圧降下は一水平走査期間内で時間的に変化するが、これについては前述したように一水平走査期間中のいくつかの時刻に対して、その時の点灯状態を求め、その点灯状態に対し縮退モデルを用いて電圧降下を計算することにより予測した。

## 【0199】

なお、一水平走査期間のある時点での各ブロック内の点灯数は各ブロックの画像データを参照すれば簡単に求めることができる。30

## 【0200】

いま、1つの例としてパルス幅変調回路への入力データのビット数が8ビットであるものとし、パルス幅変調回路は、入力データの大きさに対してリニアなパルス幅を出力するものとする。

## 【0201】

すなわち入力データが0のときは、出力は“L”となり、入力データが255のとき一水平走査期間の間は“H”を出力し、入力データが128のときには一水平走査期間のうち初めの半分の期間は“H”を出力し、後の半分の期間は“L”を出力するものとする。

## 【0202】

このような場合、パルス幅変調信号の開始時刻(本例の変調信号の例では立ち上がりの時刻)の点灯数は、パルス幅変調回路への入力データが0よりも大きいものの数をカウントすれば簡単に検出できる。40

## 【0203】

同様に一水平走査期間の中央の時刻の点灯数は、パルス幅変調回路への入力データが128よりも大きいものの数をカウントすれば簡単に検出できる。

## 【0204】

このように画像データをある閾値に対してコンパレートし、コンパレータの出力が真である数をカウントすれば、任意の時間における点灯数が簡単に計算することができる。

## 【0205】

ここで以降の説明を簡単化するため、タイムスロットという時間量を定義する。50

**【0206】**

すなわち、タイムスロットとは、一水平走査期間のなかのパルス幅変調信号の開始時刻（上述の例ではパルスの立ち上がり）からの時間を表しており、「タイムスロット = 0」とは、パルス幅変調信号の開始時刻直後の時刻を表すものと定義する。

**【0207】**

「タイムスロット = 64」とは、パルス幅変調信号の開始時刻から、64階調分の時間が経過した時刻を表すものと定義する。

**【0208】**

同様に「タイムスロット = 128」とは、パルス幅変調信号の開始時刻から、128階調分の時間が経過した時刻を表すものと定義する。 10

**【0209】**

なお、本例ではパルス幅変調は立ち上がり時刻を基準として、そこからのパルス幅を変調した例を示したが、同様に、パルスの立ち下がり時刻を基準として、パルス幅を変調する場合でも、時間軸の進む方向とタイムスロットの進む方向が逆となるが、同様に適用することができることはいうまでもない。

**【0210】**

## (電圧降下量から補正データの計算)

上述したように、縮退モデルを用いて繰り返し計算を行うことで一水平走査期間中の電圧降下の時間変化を近似的かつ離散的に計算することができた。

**【0211】**

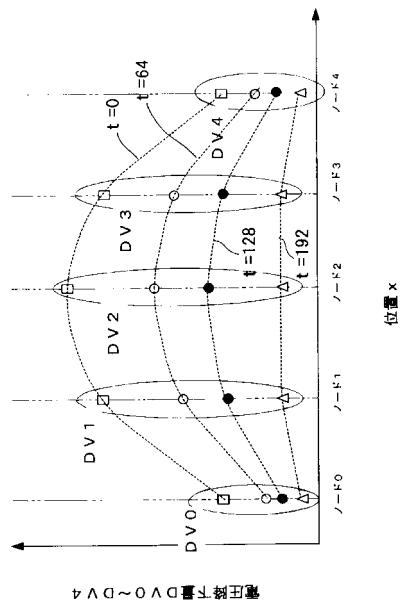

図10は、ある画像データに対して、電圧降下を繰り返し計算し、走査配線での電圧降下の時間変化を計算した例である（ここに示されている電圧降下及びその時間変化は、ある画像データに対する一例であって、別の画像データに対する電圧降下は、また別の変化をすることは当然である。）。 20

**【0212】**

同図ではタイムスロット = 0, 64, 128, 192 の4つの時点に対して、各々縮退モデルを適用して計算を行うことに、それぞれの時刻の電圧降下を離散的に計算した。

**【0213】**

図10では各ノードにおける電圧降下量を点線で結んでいるが、点線は図を見やすくするために記載したものであって、本縮退モデルにより計算された電圧降下は、で示した各ノードの位置において離散的に計算した。 30

**【0214】**

発明者らは、電圧降下の大きさとその時間変化を計算可能となった次の段階として、電圧降下量から画像データを補正する補正データを算出する方法を試みた。

**【0215】**

図11は、選択した走査配線上に図10に示した電圧降下が発生した際に、点灯状態にある表面伝導型放出素子から放出される放出電流を見積もったグラフである。

**【0216】**

縦軸は電圧降下がないときに放出される放出電流の大きさを100%として、各時間、各位置の放出電流の量を百分率で表しており、横軸は水平位置を表している。 40

**【0217】**

図11に示すように、ノード2の水平位置（基準点）において、

タイムスロット = 0 の時の放出電流を  $I_{e0}$ 、

タイムスロット = 64 の時の放出電流を  $I_{e1}$ 、

タイムスロット = 128 の時の放出電流を  $I_{e2}$ 、

タイムスロット = 192 の時の放出電流を  $I_{e3}$

とする。

**【0218】**

同図は図10の電圧降下量と図6の“駆動電圧対放出電流”的グラフから計算した。具体的には電圧VSELから電圧降下量を引いた電圧が印加された際の放出電流の値を単に機

械的にプロットしたものである。

【0219】

したがって、同図はあくまで点灯状態にある表面伝導型放出素子から放出される電流を意味しており、消灯状態にある表面伝導型放出素子が電流を放出することはない。

【0220】

以下に、電圧降下量から画像データを補正する補正データを算出する方法として、二つの方法について説明する。

【0221】

ア) 第1の補正データ算出方法

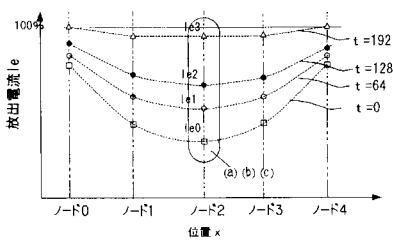

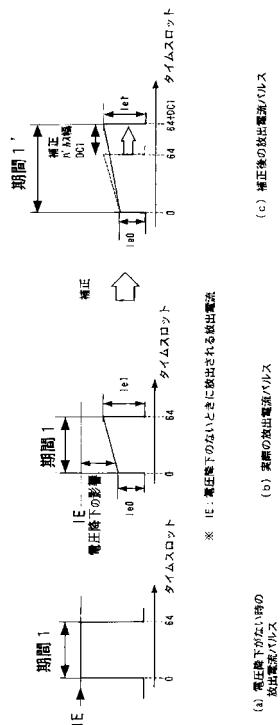

図12(a), (b), (c)は、図11の放出電流の時間変化から、電圧降下の補正データを計算する第1の方法を説明するための図である。 10

【0222】

図12(a)は、ノード2の位置における、大きさが64の画像データに対する補正データの算出方法を説明するための図である。同図はパルス幅変調された放出電流のパルス波形を模式的に表しており、パルス波形の波高は放出電流の量を、パルス波形のパルス幅は放出電流の放出される時間を表しており、パルス波形のパルス幅は64階調に相当する時間となっている。なお、説明を簡略化するために、たとえば、パルス幅変調信号の64階調に相当する長さであることを簡略化して、パルス幅が64と記載することがある。

【0223】

ここで、ノード2位置において、パルス幅が64のパルス幅変調信号を出力する場合に、20 電圧降下に起因する放出電流の低下分Lossは、近似的に同図(a)のLoss1で示した台形の面積として計算することとした。この計算式(式6)を数9に示す。

【数9】

$$\text{Loss} = \text{Loss1} = (\Delta I_{e0} + \Delta I_{e1}) \times 64 \times \Delta t \times 0.5 \quad (\text{式6})$$

ただし、

$$\Delta I_{e0} = IE - I_{e0}$$

$$\Delta I_{e1} = IE - I_{e1}$$

IE: 電圧降下がないときにON状態の表面伝導型放出素子から放出される

放出電流値

$\Delta t$ : パルス幅変調の1階調に相当する時間

30

【0224】

そこで、この放出電流の損失の総和を補うように、変調信号のパルス幅を伸ばすために変調信号に追加すべきパルス幅、すなわち画像データに加算すべき補正データCDataを近似的に数10の(式7)のように計算した。

【数10】

$$CData = Loss / I_{e1} / \Delta t \quad (\text{式7})$$

40

【0225】

(式7)で損失LossをIe1で除算しているのは、タイムスロットが64の時点の放出電流がIe1であるからであり、補正によりパルス幅が拡張される期間における放出電流の量がIe1に等しいと近似をした。

【0226】

同じように、ノード2の位置においてパルス幅が128のパルス幅変調信号を出力する場合、電圧降下に起因する放出電流量の低下分Lossは、近似的に同図(b)のLoss1とLoss2で示した2つの台形の和として計算した。すなわち、数11の(式8)の

50

ように計算した。

【数11】

$$\begin{aligned} \text{Loss} &= \text{Loss1} + \text{Loss2} \\ \text{Loss1} &= (\Delta I_{e0} + \Delta I_{e1}) \times 64 \times \Delta t \times 0.5 && \text{(式8)} \\ \text{Loss2} &= (\Delta I_{e1} + \Delta I_{e2}) \times 64 \times \Delta t \times 0.5 \end{aligned}$$

ただし、

$$\Delta I_{e2} = IE - I_{e2}$$

10

【0227】

そこで、追加すべきパルス幅、すなわち大きさ128の画像データに加算すべき補正データCDataを近似的に数12の(式9)のように計算した。

【数12】

$$CData = Loss / I_{e2} / \Delta t && \text{(式9)}$$

【0228】

同じように、ノード2の位置においてパルス幅が192のパルス幅変調信号を出力する場合、電圧降下に起因する放出電流量の低下分Lossは、近似的に同図(c)のLoss1とLoss2とLoss3で示した3つの台形の和として計算した。すなわち、数13の(式10)のように計算した。

【数13】

$$\begin{aligned} \text{Loss} &= \text{Loss1} + \text{Loss2} + \text{Loss3} \\ \text{Loss1} &= (\Delta I_{e0} + \Delta I_{e1}) \times 64 \times \Delta t \times 0.5 && \text{(式10)} \\ \text{Loss2} &= (\Delta I_{e1} + \Delta I_{e2}) \times 64 \times \Delta t \times 0.5 \\ \text{Loss3} &= (\Delta I_{e2} + \Delta I_{e3}) \times 64 \times \Delta t \times 0.5 \end{aligned}$$

ただし、

$$\Delta I_{e3} = IE - I_{e3}$$

30

【0229】

そこで、大きさ192の画像データに対する補正データCDataは近似的に数14の式11のように計算できる。

【数14】

$$CData = Loss / I_{e3} / \Delta t && \text{(式11)}$$

【0230】

また、変調信号のパルス幅が0の時には、当然ながら放出電流に対する電圧降下の影響はないため、補正データは0とし画像データに加算する補正データも0とした。

【0231】

このような作業を繰り返し行うことにより、すべてのノードにおける、パルス幅が0, 64, 128, 192の変調信号に対する補正データを離散的に計算した。

【0232】

本例ではタイムスロット0, 64, 128, 192の4点に対して縮退モデルを適用して、各時刻の電圧降下量を計算したことにより、補正データもパルス幅が0, 64, 128, 192の4点に対して求めることができた。

【0233】

40

50

しかし、好ましくは縮退モデルにより電圧降下を計算する時間の間隔を細かくすることで、電圧降下の時間変化をより精密に扱うことができ、近似計算の誤差を低減することができる。

#### 【0234】

なおその際には同様な考え方立って、(式6)～(式11)を変形して計算を行えばよい。

#### 【0235】

図13(a)は、上述の方法により、ある入力データに対し、各々のノードの位置における、画像データ = 0, 64, 128, 192に対する補正データを離散的に計算した結果の一例である。

10

#### 【0236】

なお、同図では同一の画像データに対する離散補正データを、図を見やすくするために、点線の曲線で結んで記載した。

#### 【0237】

##### イ) 第2の補正データ算出方法

図14(a), (b), (c)は図11の放出電流の時間変化から、電圧降下量の補正データを計算する第2の方法を説明するための図である。同図は大きさが64の画像データに対する補正データを算出した例である。

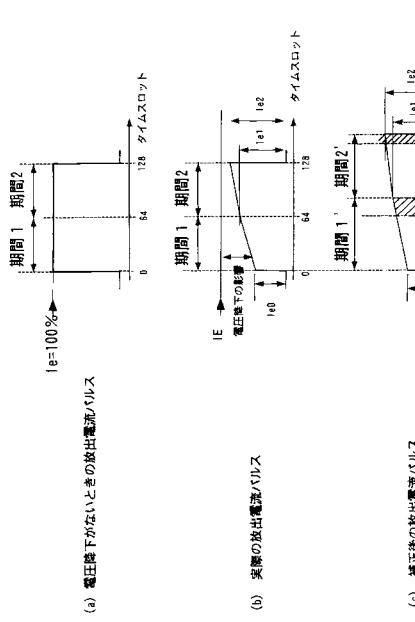

#### 【0238】

輝度の発光量は、放出電流パルスによる放出電流を時間的に積分した、放出電荷量に他ならない。したがって以降では、電圧降下による輝度の変動を考えるためにあたって、放出電荷量をもとに説明を行う。

20

#### 【0239】

いま、電圧降下の影響がない場合の放出電流をIE、パルス幅変調の1階調に相当する時間をtとするならば、画像データが64のときの、放出電流パルスによって放出されるべき放出電荷量Q0は放出電流パルスの振幅IEにパルス幅(64×t)をかけて、数15の(式12)のようにあわらすことができる。

#### 【数15】

$$Q_0 = IE \times 64 \times \Delta t \quad (\text{式}12)$$

30

#### 【0240】

しかし、実際には、走査配線上の電圧降下によって放出電流が低下する現象が発生する。

#### 【0241】

電圧降下の影響を考慮した放出電流パルスによる放出電荷量は、近似的には次のように計算できる。すなわち、ノード2のタイムスロット = 0, 64の放出電流をそれぞれIe0、Ie1とし、0～64の間の放出電流はIe0とIe1の間を直線的に変化するものと近似すれば、この間の放出電荷量Q1は図14(b)の台形の面積、すなわち、数16の(式13)のように計算できる。

#### 【数16】

40

$$Q_1 = (I_{e0} + I_{e1}) \times 64 \times \Delta t \times 0.5 \quad (\text{式}13)$$

#### 【0242】

次に、図14(c)に示すように、電圧降下による放出電流の低下分を補正するために、パルス幅をDC1だけ伸ばしたとき、電圧降下の影響を除去できたとする。

#### 【0243】

また、電圧降下の補正を行い、パルス幅を伸ばした場合には、各タイムスロットにおける放出電流量は変化すると考えられるが、ここでは簡単化のため、図14(c)のように、タイムスロット = 0では、放出電流がIe0、タイムスロット = (64 + DC1)における

50

る放出電流が  $I_{e1}$  になるものとする。

【0244】

また、タイムスロット 0 とタイムスロット (64 + DC1) の間の放出電流は、2 点の放出電流を直線で結んだ線上の値をとるものと近似する。すると、補正後の放出電流パルスによる放出電荷量  $Q_2$  は、数 17 の(式 14)のように計算できる。

【数 17】

$$Q_2 = (I_{e0} + I_{e1}) \times (64 + DC1) \times \Delta t \times 0.5 \quad (\text{式 } 14)$$

【0245】

これが前述の  $Q_0$  と等しいとすれば、数 18 の式のようになり、この式を DC1 について解けば、数 19 の(式 15)となる。

【数 18】

$$IE \times 64 \times \Delta t = (I_{e0} + I_{e1}) \times (64 + DC1) \times \Delta t \times 0.5$$

【数 19】

$$DC1 = ((2 \times IE - I_{e0} - I_{e1}) / (I_{e0} + I_{e1})) \times 64 \quad (\text{式 } 15)$$

10

【0246】

このようにして、画像データが 64 の場合の補正データを算出した。

【0247】

すなわち、ノード 2 の位置の大きさが 64 の画像データに対しては(式 15)に記載のように、CData = DC1 だけ補正量 CData を加算すればよい。

【0248】

図 15 は計算された電圧降下量から、大きさが 128 の画像データに対する補正データを算出した例である。

【0249】

いま、電圧降下の影響がない場合、画像データが 128 のときに放出電流パルスによって放出されるべき放出電荷量  $Q_3$  は、数 20 の(式 16)のように計算できる。

20

【数 20】

$$Q_3 = IE \times 128 \times \Delta t = 2 \times Q_0 \quad (\text{式 } 16)$$

【0250】

一方、電圧降下の影響を受けた、実際の放出電流パルスによる投入電荷量は、近似的には次のように計算することができる。

【0251】

すなわち、ノード 2 のタイムスロット = 0, 64, 128 の放出電流量をそれぞれ  $I_{e0}$ ,  $I_{e1}$ ,  $I_{e2}$  とする。また、0 ~ 64 の間の放出電流は  $I_{e0}$  と  $I_{e1}$  の間を直線的に変化し、64 ~ 128 の間は  $I_{e1}$  と  $I_{e2}$  の間を直線で結んだ線上を変化するものと近似すれば、0 ~ 128 までのタイムスロットの間の放出電荷量  $Q_4$  は図 15 (b) の 2 つの台形の面積の和、すなわち、数 21 の(式 17)のように計算できる。

40

【数 21】

$$Q_4 = (I_{e0} + I_{e1}) \times 64 \times \Delta t \times 0.5 \\ + (I_{e1} + I_{e2}) \times 64 \times \Delta t \times 0.5 \quad (\text{式 } 17)$$

【0252】

50

一方、電圧降下の補正量を以下のように計算した。

【0253】

タイムスロット0～64に相当する期間を期間1、64～128に相当する期間を期間2と定義する。

【0254】

補正を施した際に、期間1の部分がDC1だけ伸びて期間1に伸長され、期間2の部分がDC2だけ伸びて、期間2に伸長されるものと考える。

【0255】

この際におののの期間は補正を施されることにより、放出電荷量が前述のQ0と同じになるものとする。

10

【0256】

また、各期間の始めと終わりの放出電流は、補正を行うことで変化することは言うまでもないが、ここでは計算を簡単化するため、変化しないものと仮定した。

【0257】

すなわち、期間1の始めの放出電流はIe0、期間1の終わりの放出電流はIe1、期間2の始めの放出電流はIe1、期間2の終わりの放出電流はIe2であるものとする。

【0258】

すると、DC1は(式15)と同様にして計算することができる。

【0259】

また、DC2は、同様な考え方により、数22の(式18)のように計算することができる。

20

【数22】

$$DC2 = ((2 \times IE - Ie1 - Ie2) / (Ie1 + Ie2)) \times 64 \quad (\text{式}18)$$

【0260】

結果としてノード2の位置の大きさが128の画像データに対しては、数23の(式19)により求まる補正量CDataを加算すればよい。

【数23】

30

$$CData = DC1 + DC2 \quad (\text{式}19)$$

【0261】

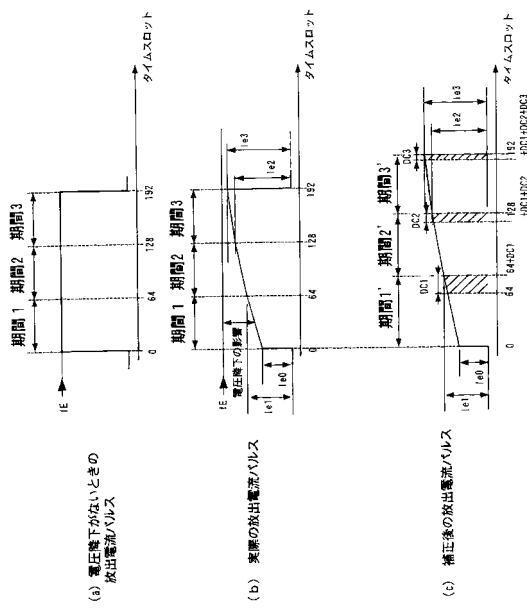

図16は計算された電圧降下量から、大きさが192の画像データに対する補正データを算出した例である。

【0262】

いま、画像データが192のときに期待される放出電流パルスによる放出電荷量Q5は、数24のようになる。

【数24】

40

$$Q5 = IE \times 192 \times \Delta t = 3 \times Q0$$

【0263】

一方、電圧降下の影響を受けた、実際の放出電流パルスによる放出電荷量は、近似的には次のように計算することができる。

【0264】

すなわち、ノード2のタイムスロット=0の時の放出電流をIe0、タイムスロット=64のときの放出電流をIe1、タイムスロット=128の時の放出電流をIe2、タイムスロット=192の時の放出電流をIe3とし、0～64の間の放出電流はIe0とIe

50

1の間を直線的に変化し、64～128の間はI<sub>e1</sub>とI<sub>e2</sub>の間を直線で結んだ線上を変化し、128～192の間はI<sub>e2</sub>とI<sub>e3</sub>の間を直線で結んだ線上を変化するものと近似すれば、0～192までのタイムスロットの間の投入電荷量Q<sub>6</sub>は図16(c)の3つの台形の面積、すなわち、数25の(式20)のように計算できる。

## 【数25】

$$\begin{aligned} Q_6 = & (I_{e0} + I_{e1}) \times 64 \times \Delta t \times 0.5 \\ & + (I_{e1} + I_{e2}) \times 64 \times \Delta t \times 0.5 \quad (\text{式20}) \\ & + (I_{e2} + I_{e3}) \times 64 \times \Delta t \times 0.5 \end{aligned}$$

10

## 【0265】

一方、電圧降下の補正量を以下のように計算した。

## 【0266】

タイムスロット0～64に相当する期間を期間1、64～128に相当する期間を期間2、128～192に相当する期間を期間3と定義する。

## 【0267】

先ほどと同様に、補正を施した後には、期間1の部分がDC1だけ伸びて期間1に伸長され、期間2の部分がDC2だけ伸びて、期間2に伸長され、期間3の部分がDC3だけ伸びて期間3に伸張されるものと考える。

## 【0268】

この際、おののの期間は補正を施されることにより、放出電荷量が前述のQ<sub>0</sub>と同じになるものとする。

20

## 【0269】

また、各期間の始めと終わりの放出電流は、補正の前後で変わらないものと仮定した。

## 【0270】

すなわち、期間1の始めの放出電流はI<sub>e0</sub>、期間1の終わりの放出電流はI<sub>e1</sub>、期間2の始めの放出電流はI<sub>e1</sub>、期間2の終わりの放出電流はI<sub>e2</sub>、期間3の始めの放出電流はI<sub>e3</sub>、期間3の終わりの放出電流はI<sub>e4</sub>であるものとする。

## 【0271】

すると、DC1, DC2はそれぞれ(式15), (式18)と同様に計算することができる。

30

## 【0272】

また、DC3については、数26の(式21)のように計算することができる。

## 【数26】

$$DC3 = ((2 \times IE - I_{e2} - I_{e3}) / (I_{e2} + I_{e3})) \times 64 \quad (\text{式21})$$

## 【0273】

結果としてノード2の位置の大きさが192の画像データに加算する補正データCDataとしては、数27の(式22)により求まる値を加算すればよい。

40

## 【数27】

$$CData = DC1 + DC2 + DC3 \quad (\text{式22})$$

## 【0274】

以上のようにしてノード2の位置に対する画像データ64, 128, 192の補正データCDataを算出した。

## 【0275】

また、パルス幅が0の時には、当然ながら放出電流に対する電圧降下の影響はないため、補正データは0とし画像データに加算する補正データCDataも0とした。

50

**【0276】**

以上、離散的な水平位置（ノード）における、離散的な画像データの大きさに対する補正データの算出法について2つの方法を説明した。

**【0277】**

なお、いずれの方法においても、このように0, 64, 128, 192というように、とびとびの画像データに対して補正データを計算しているのは、計算量を減らすことを狙ったものである。

**【0278】**

すなわち任意のすべての画像データに対して同様の計算を行っては、非常に計算量が大きくなり、計算を行うためのハードウェア量が非常に大きくなってしまう。

10

**【0279】**

一方、あるノードの位置においては、画像データが大きいほど、補正データも大きくなる傾向がある。これにより、任意の画像データに対する補正データを算出する際には、その画像データの近傍のすでに補正データが算出されている点と点を直線近似により補間すれば、計算量を大幅に減少させることができるためである。なお、この補間については離散補正データ補間手段を説明する際に詳しく説明する。

**【0280】**

また、同様な考え方をすべてのノードの位置において適用すれば、すべてのノードの位置における、画像データ = 0, 64, 128, 192 の補正データを算出できる。

**【0281】**

なお、このように補正データを算出されている離散的な画像データのことを画像データ基準値と呼ぶ。

20

**【0282】**

本例ではタイムスロットを0, 64, 128, 192の4点に対して縮退モデルを適用して、各時刻の電圧降下量を計算したことにより、補正データも画像データが0, 64, 128, 192の4つの画像データ基準値に対する補正データを求めることができた。

**【0283】**

しかし、好ましくは縮退モデルにより電圧降下を計算する時間の間隔を細かくすることで、電圧降下の時間変化をより精密に扱うことができ、離散的な画像データ基準値の個数が増加する一方、近似計算の誤差を低減することができる。

30

**【0284】**

具体的には、図14～図16では、図を簡略化するためにタイムスロット0, 64, 128, 192の4点のみにおいて計算を行ったが、実際には、タイムスロット0～255のうち16タイムスロットおきに計算を行ったところ（すなわち画像データの基準値を画像データの大きさで16ごとに設定した）、好ましかった。

**【0285】**

なお、その際には同様な考え方にして、（式6）～（式11）もしくは、（式12）～（式22）を変形して計算を行えばよい。

**【0286】**

上述の方法により、ある入力データに対し、各々のノードの位置における、画像データ = 0, 64, 128, 192に対する補正データを離散的に計算すると、図13(a)と同様の結果が得られた。

40

**【0287】**

（離散補正データの補間方法）

離散的に算出された補正データは、各ノードの位置に対する離散的なものであって、任意の水平位置（列配線番号）における補正データを与えるものではない。またそれと同時に、各ノード位置においていくつかの予め定められた画像データの基準値の大きさをもつ画像データに対する補正データであって実際の画像データの大きさに応じたに対する補正データをあたえるものではない。

**【0288】**

50

ここでは各列配線における入力画像データの大きさに適合した補正データを、離散的に算出した補正データを補間することにより算出した。

【0289】

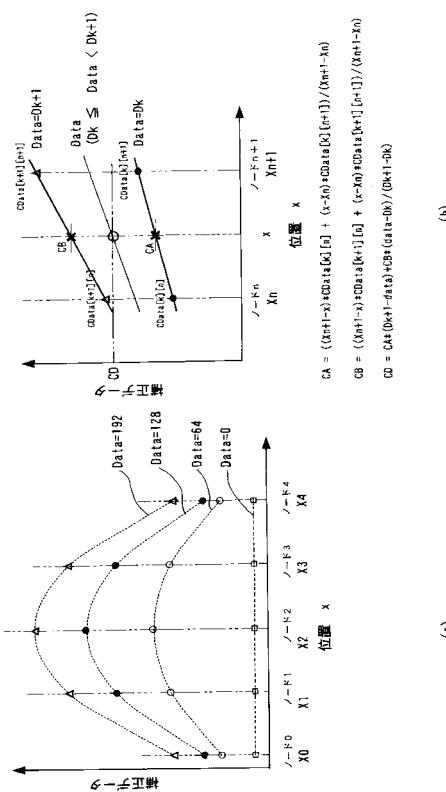

図13(b)はノードnとノードn+1の間に位置するxという位置における、画像データDataに相当する補正データを算出する方法を示した図である。

【0290】

なお前提として、補正データはすでにノードn及びノードn+1の位置Xn及びXn+1において離散的に計算されているものとする。

【0291】

また、画像データDataはすでに離散的に補正データが算出されている画像データである、画像データ基準値のDkとDk+1の間の値をとるものとする。 10

【0292】

いま、ノードnのk番目の画像データの基準値に対する離散的補正データをCData[k][n]と表記するならば、位置xにおけるパルス幅Dkの補正データCAは、CData[k][n]とCData[k][n+1]の値を用いて、直線近似により、数28の(式23)のように計算できる。

【数28】

$$CA = \frac{(X_{n+1}-x) \times CData[k][n] + (x-X_n) \times CData[k][n+1]}{X_{n+1} - X_n}$$

20

(式23)

【0293】

ただし、Xn、Xn+1はそれぞれノードn、(n+1)の水平表示位置であって、前述したブロックを決定するときに定められる定数である。

【0294】

また位置xにおける画像データDk+1の補正データCBは、数29の(式24)のように計算できる。

【数29】

$$CB = \frac{(X_{n+1}-x) \times CData[k+1][n] + (x-X_n) \times CData[k+1][n+1]}{X_{n+1} - X_n}$$

30

(式24)

【0295】

CAとCBの補正データを直線近似することにより、位置xにおける画像データDataに対する補正データCDは、数30の(式25)のように計算できる。

【数30】

$$CD = \frac{CA \times (D_{k+1}-Data) + CB \times (Data-D_k)}{D_{k+1} - D_k}$$

40

【0296】

以上のように、離散的補正データから実際の位置や画像データの大きさに適合した補正データを算出するためには、式23～式25に記載した方法により簡単に計算できる。

【0297】

このようにして算出した補正データを画像データに加算して画像データを補正し、補正後の画像データ(補正画像データ)に応じてパルス幅変調を行えば、従来からの課題であつ

50

た表示画像における電圧降下による影響を低減することができ、画質を向上させることができる。

#### 【0298】

また予てからの課題であった補正のためのハードウェアについても、これまで説明してきたような縮退化などの近似を導入することにより、計算量を低減化することができるため非常に小規模なハードウェアで構成することができるというすぐれたメリットがある。

#### 【0299】

ところで、上記補正手法によって走査配線の電圧降下に起因する輝度低下の問題を解決できることが明らかとなったわけであるが、かかる機能を実現する回路を作製するにあたり、留意しなければならない点がある。

10

#### 【0300】

ディジタル回路においては、その回路で取り扱うことのできるデータ幅（ビット数）に制限がある。このデータ幅は一般的にハードウェアのコスト等との兼ね合いから決定される。

#### 【0301】

補正データを加算することによる補正画像データの増大により、いわゆるオーバーフローの問題が生ずることがある。すなわち、画像データに対して補正データを単純に加算したときに、その演算結果がパルス幅変調器（変調回路8）で取り扱うことのできるデータ幅を超えてしまうと、ビットの折り返しなどが起こり、表示画像の反転などの画像の乱れが生ずるのである。

20

#### 【0302】

このため、本実施の形態では、あらかじめ補正画像データの最大値を計算し、その最大値に対応するビット幅を持ったパルス幅変調器を設ける。

#### 【0303】

しかしながら、駆動時間を延ばさなくてはならない補正に対して、現実的に決まっている水平走査時間（入力される画像信号により決まっている水平走査時間）により制限される駆動時間の最大時間に抑えることにより輝度が低下することによって、表示画像全体の輝度が低下してしまう。

#### 【0304】

そこで、本実施の形態では、前述したように、水平走査ライン（走査配線）毎の補正画像データの最大値に応じて各走査配線の走査時間（選択時間）をフレーム単位で適宜に割り当てる。

30

#### 【0305】

（システム全体と各部分の機能説明）

次に、補正データ算出手段を内蔵した画像表示装置のハードウェアについて説明する。

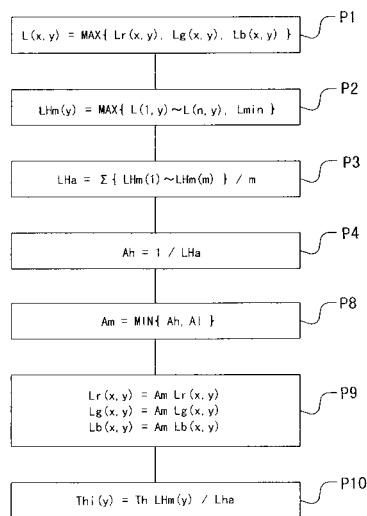

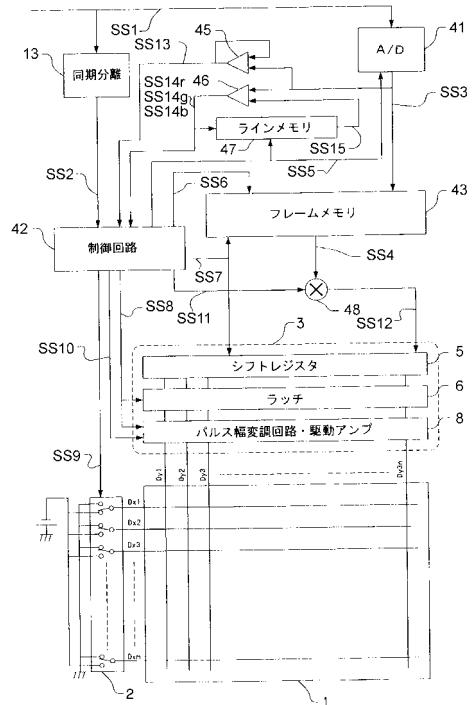

#### 【0306】

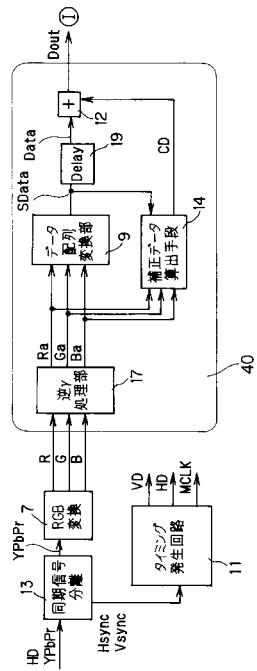

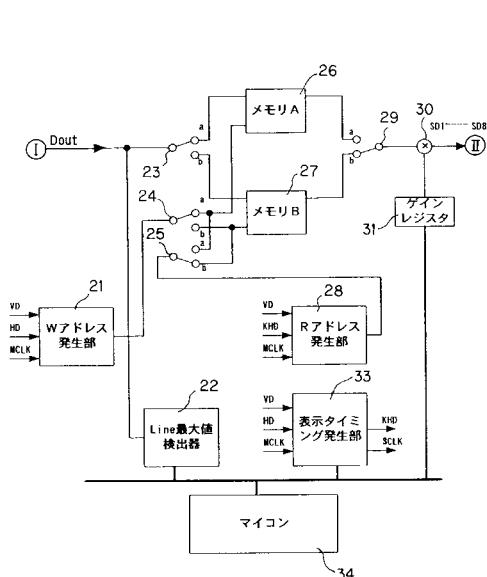

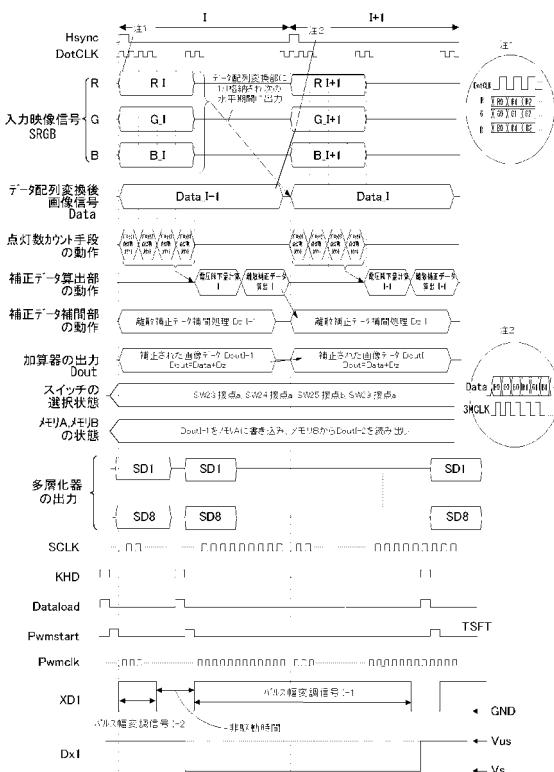

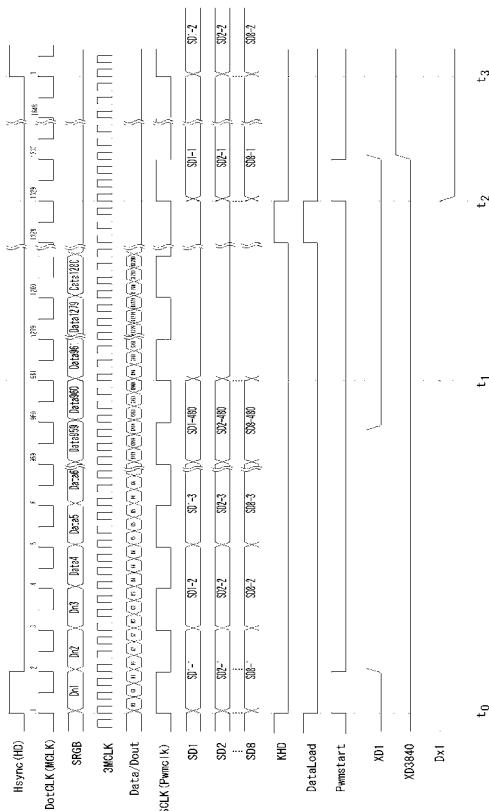

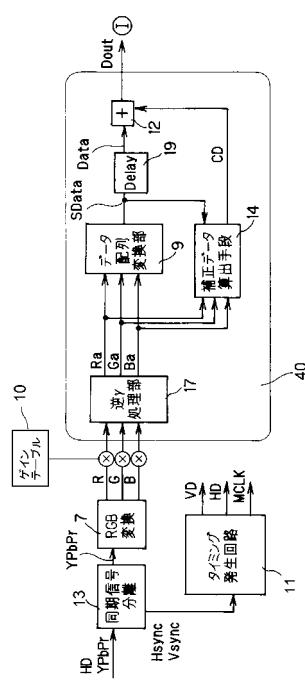

図17、図18、図19はその回路構成の概略を示すブロック図である。図17は、映像信号の入力と、入力された映像信号の補正に係る信号処理回路を、図18は、走査配線の選択期間、すなわち水平走査期間の決定に係る駆動制御回路を、図19は、表示パネル、走査駆動回路および変調駆動回路に係る部分をそれぞれ示している。図17に示す回路の出力Doutは、図18に示す回路に入力される。また、図18に示す回路の出力SD1～SD8は、図19に示す回路に入力される。

40

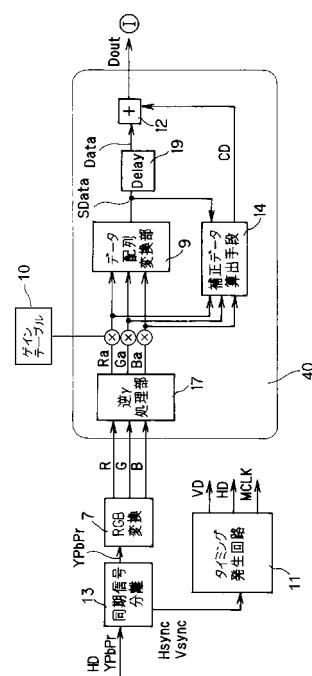

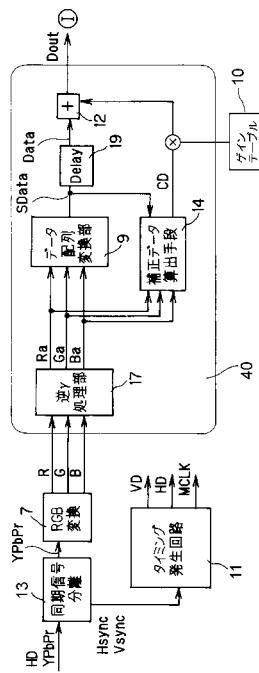

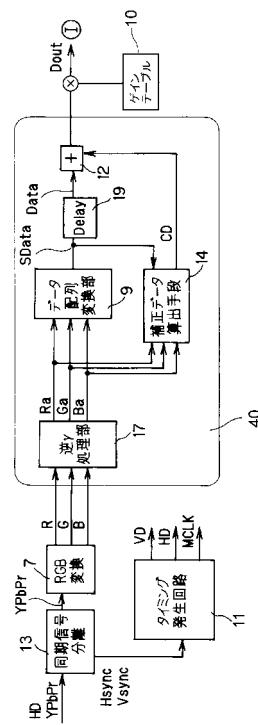

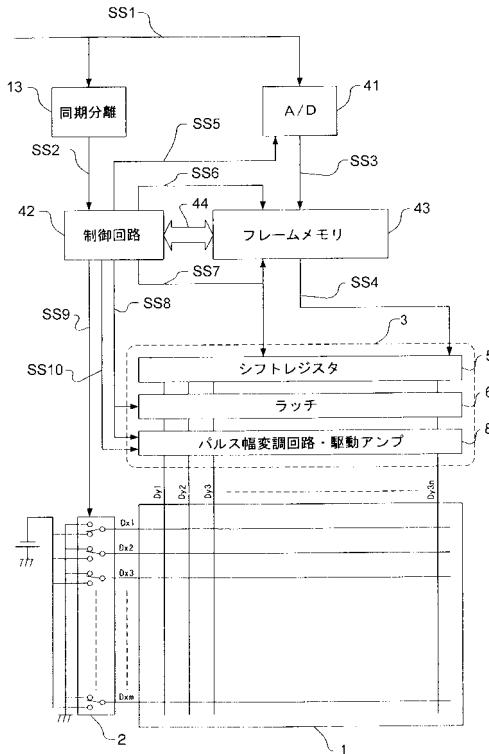

#### 【0307】

図17において、13は入力映像信号を映像信号と同期信号とに分離する同期信号分離回路、11は同期信号分離回路13で分離された同期信号に基づき各部のタイミング信号を発生するタイミング発生回路、7は同期信号分離回路13により分離された輝度及び色差信号（YPbPr）を3原色信号（RGB）に変換するRGB変換手段を示す。

#### 【0308】

コンピュータの映像出力などはパラレル3原色信号（RGB）として入力されるので、この場合には、RGB変換手段7を介する必要はない。

50

**【0309】**

また、17はRGB信号に逆変換を施す逆処理部、9はRGBのパラレル信号をシリアル信号にするデータ配列変換部、14は入力画像データに基づいて走査配線の電圧降下を補正するため補正データを算出する補正データ算出手段、19は遅延回路、12は補正データ算出手段14によって算出された補正データを用いて画像データを補正する加算器を示す。

**【0310】**

また、同図においてR,G,BはRGBパラレルの入力映像データ、Ra,Ga,Baは逆変換処理を施したRGBパラレルの映像データ、SDataはデータ配列変換部9によりパラレル・シリアル変換されたシリアル画像データ、Dataは遅延されたシリアル画像データ、CDは補正データ算出手段14により算出された補正データ、Doutは加算器12によりシリアル画像データDataに補正データCDを加算することにより、補正された画像データ（補正画像データ）である。10

**【0311】**

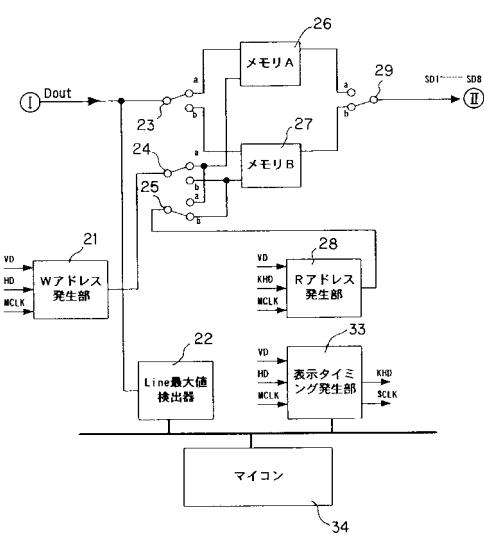

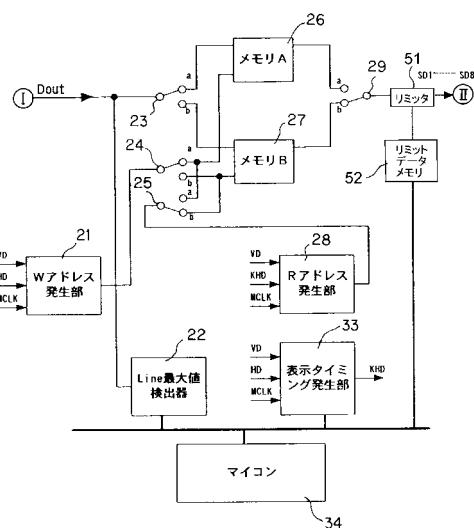

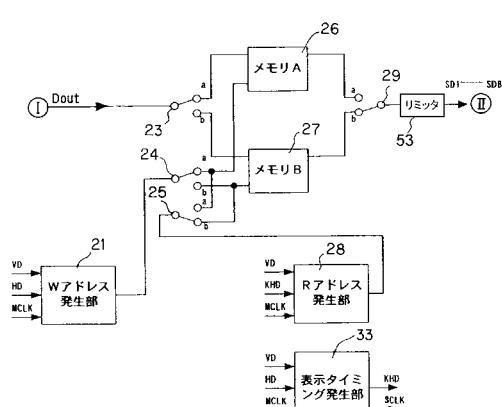

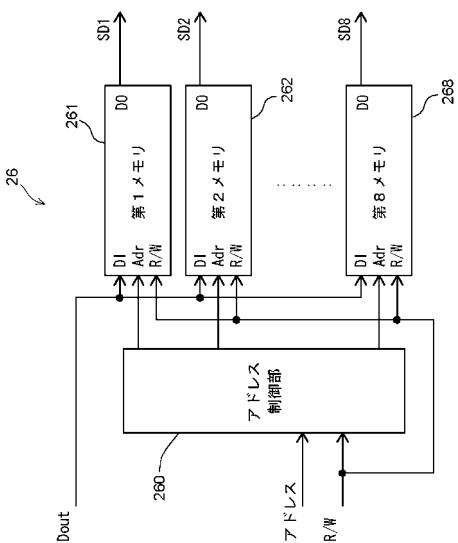

図18において、26,27はそれぞれ補正画像データを一時的に記憶しておくフレームメモリたるメモリA,メモリB、21はメモリA,Bの書き込み用アドレス信号を発生するWアドレス発生部、28はメモリA,Bからの読み出し用アドレス信号を発生するRアドレス発生部、23,24,25,29はそれぞれメモリA,Bの入出力を適宜切り替えるスイッチを示す。

**【0312】**

また、同図において、22は補正画像データの最大値を各水平走査ライン（走査配線）毎に検出するライン最大値検出器、34はライン最大値検出器22によって検出された補正画像データの最大値に応じて各水平走査ライン（走査配線）の走査時間を演算処理するマイコン、33はマイコン34の演算結果を受けて表示タイミング信号を発生する表示タイミング発生部を示す。20

**【0313】**

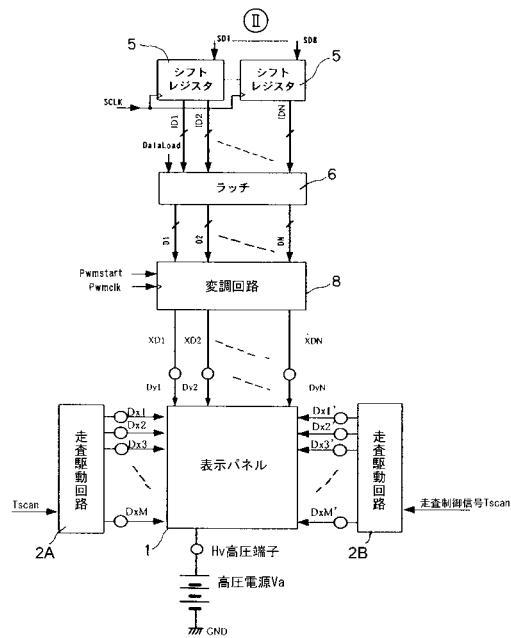

図19において、1は図4に示したような表示パネル、Dx1～DxM及びDx1～DxMは表示パネルの走査配線の電圧供給端子、Dy1～DyNは表示パネルの変調配線の電圧供給端子、Hvはフェースプレートとリアプレートの間に加速電圧を印加するための高圧供給端子、Vaは高圧電源を示す。また、2A、2Bは各走査配線に走査信号を供給する走査駆動回路である。5は、メモリA26又はメモリB27からの出力SD1～SD8がそれぞれ入力される8個のシフトレジスタ、6は画像データ1ライン分のラッチ回路、8は補正画像データに応じてパルス幅変調した変調信号（電圧パルス）を表示パネル1の各変調配線に出力するパルス幅変調回路を示し、シフトレジスタ5、ラッチ回路6、変調回路8により、変調駆動回路が構成されている。30

**【0314】**

（同期信号分離回路、タイミング発生回路）

本実施の形態の画像表示装置は、NTSCや、PAL、SECAM、HDTVなどのテレビジョン信号や、コンピュータの出力であるVGAなどの何れをに表示することができる。

**【0315】**

図17では、720pのHDTV方式が入力された一例について記載している。

**【0316】**

入力画像信号720pのフレーム周波数は60Hz、水平周波数は45kHzである。すなわち、全走査線数は750ラインであり、そのうちの720ラインは有効走査線数である。

**【0317】**

入力された720pの映像信号からは、まず同期信号分離回路13により同期信号Vsync,Hsyncを分離される。同期分離された垂直同期信号Vsyncと水平同期信号Hsyncはタイミング発生回路11に供給され、同期分離された映像信号はRGB変換

手段7に供給される。RGB変換手段7の内部には、輝度及び色差信号YPbPrから3原色信号RGBへの変換回路の他に、不図示のローパスフィルタやA/D変換器などが設けられており、信号YPbPrをデジタルRGB信号へと変換し、逆処理部17へと供給する。

#### 【0318】

タイミング発生回路11は、PLL回路を内蔵しており、様々な映像ソースの同期信号に同期したタイミング信号を発生し、各部の動作タイミング信号を発生する回路である。

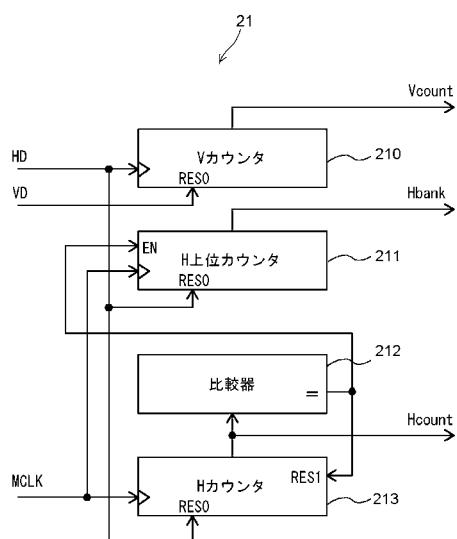

#### 【0319】

タイミング発生回路11が発生するタイミング信号としては、所定のサンプリング周波数のサンプリングクロックMCLK、水平走査用のタイミング信号HD、垂直走査用のタイミング信号VDなどがある。

10

#### 【0320】

本実施の形態では、1水平走査期間(1H)のサンプルクロック数を1648個に設計し、その中の1280個を有効画素数とする。したがって、サンプリング周波数MCLKは、PLL回路により水平同期信号に分周比1:1648で分周して発生させ、74.16MHzのサンプリング周波数のサンプリングクロックMCLKを得る。

#### 【0321】

(逆処理部)

CRTは入力に対しほぼ2.2乗の発光特性(以降逆特性とよぶ)を備えている。

#### 【0322】

20

そのため、入力映像信号はCRTのこのような特性が既に考慮されており、CRTに表示した際にリニアな発光特性となるように一般に0.45乗の特性にしたがって変換される。

#### 【0323】

一方、本実施形態の表示パネルは駆動電圧の印加時間により変調を施す場合、印加時間の長さに対しほぼリニアな発光特性を有しているため、入力映像信号を逆特性にもとづいて変換(以降逆変換とよぶ)する必要がある。

#### 【0324】

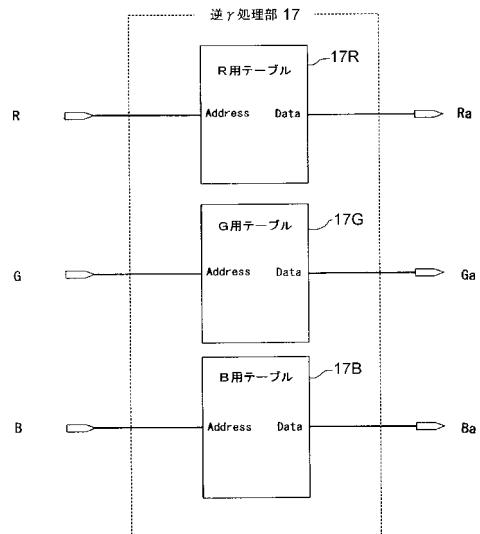

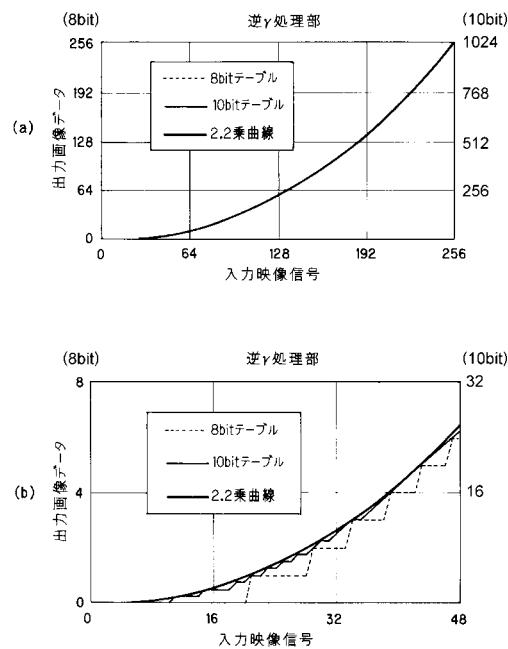

図20は、入力映像信号を逆変換するための逆処理部17の構成を示すブロック図である。

30

#### 【0325】

本実施の形態の逆処理部17は、上記逆変換処理をメモリによって構成した。

#### 【0326】

逆処理部17は、図17、図20に示すように、映像信号R,G,Bのビット数を8ビットとし、逆処理部17の出力である映像信号Ra,Ga,Baのビット数を同じく8ビットとして、アドレス8ビット、データ8ビットのメモリを各色ごと用いることにより構成している。

#### 【0327】

各メモリには、R用テーブル17R、G用テーブル17G、B用テーブル17Bとして、図21に記載した逆特性を記憶させている。なお同図21(a)は本変換テーブルの入力映像信号が0~255の範囲の該テーブル17R、17G、17Bに記載したデータである。また、同図21(b)は入力画像データが0~48の範囲を拡大して表示したものである。

40

#### 【0328】

なお、本実施の形態では、逆処理部17を8ビット入力、8ビット出力のメモリとして構成したが、逆処理の変換精度を上げるために例えば8ビット入力、10ビット出力のメモリで逆処理部を構成することもできる。このとき同メモリには、図21に示した8ビット入力、10ビット出力の入出力特性のテーブルを記憶させるとよい。なお図21では8ビットのテーブルと、10ビットのテーブルを比較しやすいように、8ビットテーブルのグラフの縦軸の左側のスケール、10ビットテーブルのグラフの縦軸を図21の右側

50

のスケールにして表示している。

#### 【0329】

##### (データ配列変換部)

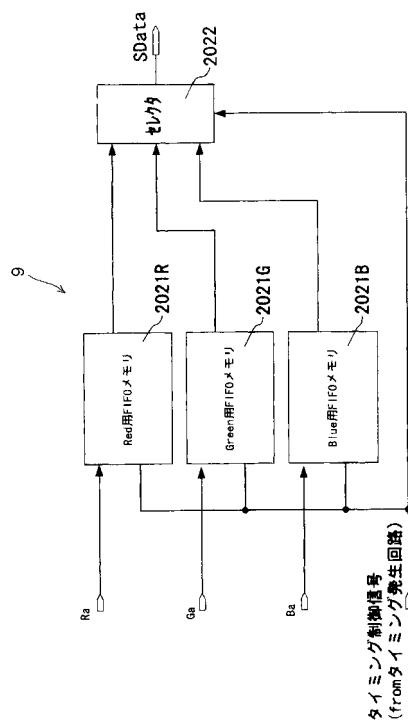

データ配列変換部9は、RGBパラレル映像信号Ra, Ga, Baを表示パネル1の画素配列に合わせてパラレル・シリアル変換する回路である。データ配列変換部9の構成は図22に示したように FIFO(First In First Out)メモリ2021R, 2021G, 2021Bとセレクタ2022から構成される。

#### 【0330】

図22では図示していないが、FIFOメモリは水平画素数ワードのメモリを奇数ライン用と偶数ライン用の2本備えている。奇数行目の映像データが入力された際には、奇数ライン用のFIFOにデータが書き込まれる一方、偶数ライン用のFIFOメモリから一つ前の水平走査期間に蓄積された画像データが読み出される。偶数行目の映像データが入力された際には偶数ライン用のFIFOにデータが書き込まれる一方、奇数ライン用FIFOメモリから一つ前の水平走査期間に蓄積された画像データが読み出される。

#### 【0331】

FIFOメモリから読み出されたデータは、セレクタ2022により表示パネルの画素配列にしたがって、パラレル・シリアル変換され、RGBのシリアル画像データSDataとして出力される。詳細については記載しないが、タイミング発生回路11からのタイミング制御信号に基づいて動作する。

#### 【0332】

##### (補正データ算出手段)

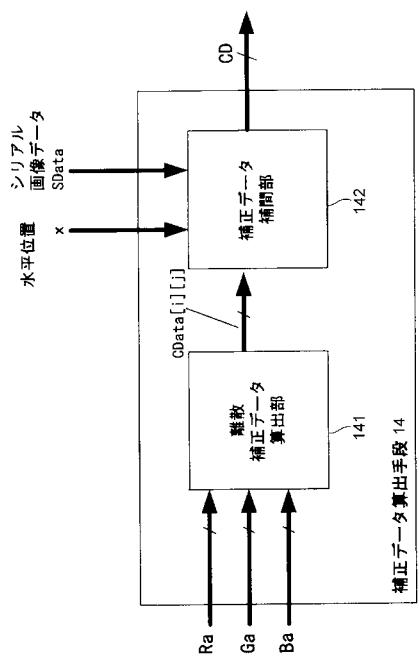

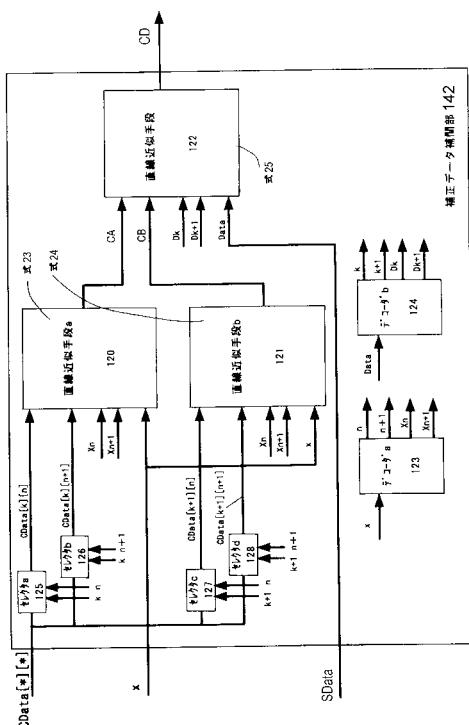

補正データ算出手段14は前述した補正データ算出方法により、電圧降下の補正データを算出する回路である。補正データ算出手段は図23に示すように離散補正データ算出部141と補正データ補間部142の2つのブロックから構成される。

#### 【0333】

離散補正データ算出部141は、入力された画像信号から電圧降下量を算出し、電圧降下量から補正データを離散的に計算する手段である。同手段は計算量やハードウェア量を減少させるために、前述の縮退モデルの概念を導入して、補正データを離散的に算出する。

#### 【0334】

離散的に算出された補正データは補正データ補間部142により補間され、画像データの大きさやその水平表示位置xに適合した補正データCDが算出される。

#### 【0335】

##### (離散補正データ算出部)

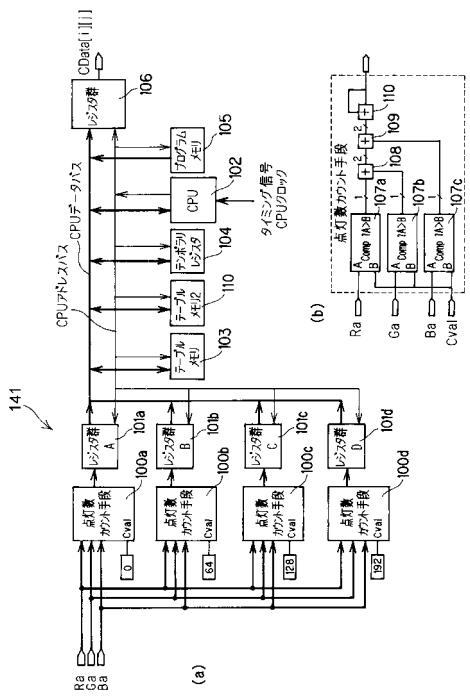

図24は本実施の形態の離散補正データを算出するための離散補正データ算出部141の回路構成の概略を示すブロック図である。

#### 【0336】

離散補正データ算出部141は、以下に述べるように、画像データをブロックわけし、ブロックごとの統計量（点灯数）を算出するとともに、統計量から各ノードの位置における、電圧降下量の時間変化を計算する電圧降下量算出部としての機能と、各時間ごとの電圧降下量を発光輝度量に変換する機能、および発光輝度量を時間方向に積分して、発光輝度総量を算出する機能、およびそれらから離散的な基準点における、画像データの基準値に対する補正データを算出する手段である。

#### 【0337】

図24(a)において100a～100cは点灯数カウント手段、101a～101cは各ブロックごとの各時刻における点灯数を格納するレジスタ群、102はCPU、103は(式2)及び(式3)で記載したパラメータaijを記憶するためのテーブルメモリ、104は計算結果を一時記憶するためのテンポラリレジスタ、105はCPUのプログラムが格納されているプログラムメモリ、110は、電圧降下量を放出電流量に変換する変換データが記載されたテーブルメモリ、106は、前述した離散補正データの計算結果を格納するためのレジスタ群である。

10

20

40

50

**【0338】**

点灯数カウント手段 100a ~ 100c は、図 24 (b) に記載したようなコンパレータと加算器などから構成されている。パラレル映像信号 Ra, Ga, Ba はそれぞれコンパレータ 107a ~ 107c に入力され、逐次 Cva1 の値と比較される。なお、Cva1 は前述してきた画像データに対して設定した、画像データ基準値に相当する。

**【0339】**

コンパレータ 107a ~ 107c は Cva1 と画像データの比較を行い画像データの方が大きければ High を出力し小さければ Low を出力する。

**【0340】**

コンパレータ 107a ~ 107c の出力は加算器 108 及び 109 により互いに加算され 10 、さらに加算器 110 によりブロックごとに加算をおこない、ブロックごとの加算結果を各々のブロックごとの点灯数としてレジスタ群 101a ~ 101c へと格納する。

**【0341】**

点灯数カウント手段 100a ~ 100c にはコンパレータの比較値 Cva1 として、それぞれ 0, 64, 128, 192 が入力されている。結果として、点灯数カウント手段 100a は画像データのうち、0 より大きい画像データの個数をカウントしそのブロックごとの総計をレジスタ 101a に格納する。

**【0342】**

同様に、点灯数カウント手段 100b は画像データのうち、64 より大きい画像データの個数をカウントし、そのブロックごとの総計をレジスタ 101b に格納する。 20

**【0343】**

同様に、点灯数カウント手段 100c は画像データのうち、128 より大きい画像データの個数をカウントし、そのブロックごとの総計をレジスタ 101c に格納する。

**【0344】**

同様に、点灯数カウント手段 100d は画像データのうち、192 より大きい画像データの個数をカウントし、そのブロックごとの総計をレジスタ 101d 格納する。

**【0345】**

ブロックごと、時間ごとの点灯数がカウントされると、CPU102 はテーブルメモリ 103 に格納されたパラメータテーブル aij を随時読み出して、(式2) ~ (式5) に従い、電圧降下量を計算し、計算結果をテンポラリレジスタ 104 に格納する。 30

**【0346】**

本例では CPU102 に(式2)の計算を円滑におこなうための積和演算機能を設けた。

**【0347】**

(式2)に挙げた演算を実現する手段としては、CPU102 で積和演算を行うのではなく、例えば、その積和演算の計算結果を予め格納したメモリを用いて実現しても構わない。この場合は、各ブロックの点灯数を入力とし、考えられるすべての入力パターンに対し、各ノード位置の電圧降下量をメモリに記憶しておくのである。

**【0348】**

電圧降下量の計算が完了するとともに、CPU102 はテンポラリレジスタ 104 から、各時間、各ブロックごとの電圧降下量をよみだし、テーブルメモリ 2 (110) を参照して、電圧降下量を放出電流量に変換し、(式6) ~ (式11) (もしくは(式12) ~ (式22)) に従って、離散補正データを算出した。 40

**【0349】**

計算した離散補正データは、レジスタ群 106 に格納した。

**【0350】**

(補正データ補間部)

図 25 は、図 23 に示した補正データ補間部 142 の詳細な構成を説明するための図である。

**【0351】**

補正データ補間部 142 は、画像データの表示される位置 (水平位置) 及び、画像データ 50

の大きさに適合した補正データを算出するための手段である。同手段は離散的に算出された補正データを補間することにより、画像データの表示位置（水平位置）及び、画像データの大きさに応じた補正データを算出する。

#### 【0352】

同図において、123は画像データの表示位置（水平位置） $x$ から、補間に用いる離散補正データのノード番号n及びn+1を決定するためのデコーダであり、124は画像データの大きさから、（式23）～（式25）のkおよびk+1を決定するためのデコーダである。

#### 【0353】

また、セレクタ125～128は、離散補正データを選択して、直線近似手段に供給するためのセレクタである。10

#### 【0354】

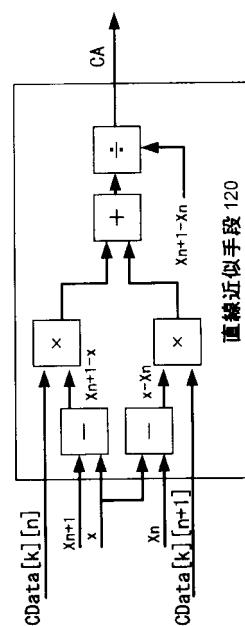

また、121～123は、それぞれ（式23）～（式25）の直線近似を行うための直線近似手段である。

#### 【0355】

図26に直線近似手段120の構成例を示す。一般に直線近似手段は（式23）～（式25）の演算子にあらわされるように、減算器、積算器、加算器、割り算器などによって構成可能である。直線近似手段121、122も、直線近似手段120と同様の構成である。20

#### 【0356】

しかし、望ましくは離散補正データを算出するノードとノードの間の列配線本数や、離散補正データを算出する画像データ基準値の間隔（すなわち電圧降下を算出する時間間隔）が2のべき乗になるように構成するとハードウェアを非常に簡単に構成できる。それらを2のべき乗に設定すれば、図26に示した割り算器において、 $X_{n+1} - X_n$ は2のべき乗の値となるので、ビットシフトにより割り算を実現できるからである。

#### 【0357】

また、 $X_{n+1} - X_n$ の値がいつも一定の値であって、2のべき乗で表される値であるならば、加算器の加算結果をべき乗の乗数分だけシフトして出力すればよく、あえて割り算器を作製する必要がない。

#### 【0358】

またこれ以外の箇所でも離散補正データを算出するノードの間隔や、画像データの間隔を2のべき乗とすることにより、たとえばデコーダ123～124を簡単に作製することが可能となるとともに、図26の減算器で行っている演算を簡単なビット演算に置き換えることができる。30

#### 【0359】

（遅延回路19）

図17に示したようにデータ配列変換部9により並び替えが行われた画像データSDat aは補正データ算出手段14と遅延回路19に入力される。補正データ算出手段14の補正データ補間部は、タイミング制御回路からの水平位置情報xと画像データSDat aの値を参照して、それらにあった補正データCDを算出する。40

#### 【0360】

遅延回路19は、補正データ算出にかかる時間を吸収するために設けられており、加算器12で画像データに補正データが加算される際に、画像データにそれに対応した補正データが正しく加算されるよう遅延を行う手段である。同手段はフリップフロップを用いることにより構成できる。

#### 【0361】

（加算器12）

加算器12は補正データ算出手段14からの補正データCDと画像データDat aを加算する手段である。加算を行うことにより画像データDat aは補正が施され、補正画像データDoutとしてメモリA26又はメモリB27へ出力される（図17、図18参照）50

。

**【0362】**

(水平走査期間の制御について)

従来の表示装置では、入力映像信号に含まれる水平同期信号により定まる1水平走査期間に基づいて、全ての走査配線に一律に同一の表示水平走査時間を割り当てていた。

**【0363】**

これに対して、本実施形態では、補正画像データの最大値に応じて各走査配線の走査時間を適応的に割り当てるこことによって、走査配線の電圧降下を高精度に補正し、かつ輝度低下を抑えて画像を表示するという、相反する要求を解決することができる。

**【0364】**

現実には、全ての走査配線を同一の表示走査時間で走査しなくても、表示される画像にはほとんど違和感を感じることがない。

**【0365】**

また、TV信号等の自然画の画像信号などにおいては、補正によるオーバーフローが懸念されるような大きな値のデータが現れることはさほど多くなく、水平走査ライン毎に見ればそれぞれの補正画像データの最大値にはかなりのバラツキがあるので、従来のように全ての走査配線を同じ水平走査時間で走査することは、効率的でない。

**【0366】**

従って、本実施形態の駆動方法を適用しても、表示上の問題は無い。そして、各走査配線に対応する変調信号のパルス幅の最大値により決定した表示水平走査期間で走査することによって輝度の低下を抑えることができる。

**【0367】**

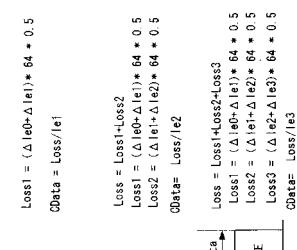

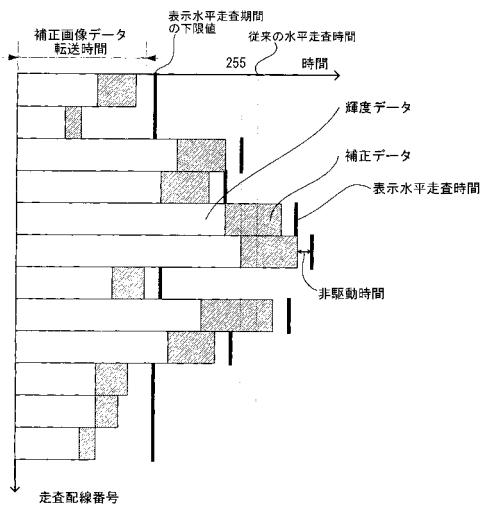

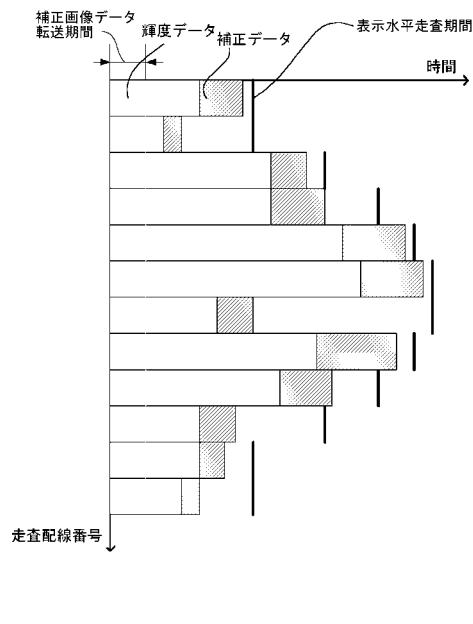

図27は、本実施形態に用いられる水平走査期間を説明するための模式図である。同図のグラフの縦軸は各水平走査配線に対応している。同図では、説明を簡略化するために水平走査配線が12本の例を挙げる。また、同グラフの横軸は時間(パルス幅)を表している。説明をわかりやすくするため、画像データ幅は8bitとし輝度データに補正データが加算されている様子をわかりやすく示した。

**【0368】**

同グラフにおいて、各水平走査配線に対応している棒グラフは対応する水平走査配線上の画素における最大の変調信号のパルス幅、即ち最大の補正画像データを図示してある。白抜き矩形部分は、その水平走査配線に係る1ライン分の入力画像データ(輝度データ)を示し、ハッチング矩形部分は、その入力画像データに対する補正データを示している。

**【0369】**

同図に示すように、各水平走査配線ごとに補正画像データの最大値にはバラツキがあるので、全ての水平走査配線に一律に走査時間を割り当てるのではなく、各水平走査配線ごとにその補正画像データの最大値が収まるように個別に表示走査時間を割り当たればよいことがわかる。個別に水平走査配線毎に割り当たった表示水平走査時間の総和が表示の1フレーム時間以下であれば、1フレーム時間内に1フレームの画像が表示できる。言い換えれば表示水平走査時間の平均が従来の水平走査期間(図27においては255+ブランкиング期間)であれば、1フレーム時間内に1フレームの画像が表示できる。そして、表示1フレームの時間が、入力された画像の1フレームの時間と大きく変わらないので動画表示もスムースである。

**【0370】**

もちろん、表示フレーム時間は入力映像の1フレーム時間と必ずしも同一でなくてもよいので、表示フレーム時間を若干伸縮することもできる。その場合、個別に水平走査配線毎に割り当たった表示水平走査時間のNフレームの総和が、入力された映像データのNフレーム時間以下であればよい(ここでNは2以上の自然数)。

**【0371】**

このようにして割り当たった表示水平走査時間を、同グラフ中、太線にて示す。なお、走査配線の切り替えと変調配線の駆動を同時に行うと表示パネル内の駆動波形が乱れ、素子に

10

20

30

40

50

過大な電圧がかかる可能性があるため、補正画像データの最大値よりも所定の時間的余裕（変調配線の非駆動時間）を持たせて表示水平走査時間を設定することが望ましい。また、変調駆動回路への補正画像データのデータ転送に要する時間（シフトレジスタ5へのデータシフト時間）等を確保するために、図27のように、表示水平走査時間の下限値も定めるとよい。

#### 【0372】

走査配線抵抗が5程度、表面伝導型放出素子の素子電流を0.1mA程度、素子数 $720 \times 1280 \times 3$ (RGB)において、8bit幅の画像データ(最大:255)を補正した補正画像データの最大値は350程度となる。そのためパルス幅変調器のbit幅を9bitに設計する。10

#### 【0373】

(ライン最大値検出器、マイコンにおける走査時間演算処理)

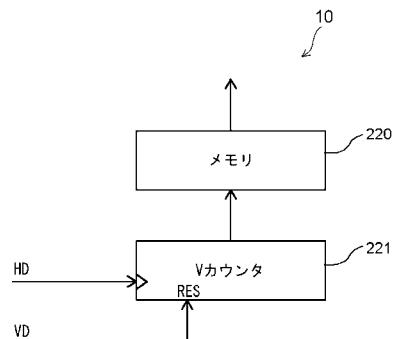

加算器12から出力された補正画像データDoutは、ライン最大値検出器22に入力される(図18)。ライン最大値検出器22は、1ライン分の補正画像データのうちから最大値を検出する処理を、各水平走査配線上の画素のデータごとに行う。

#### 【0374】

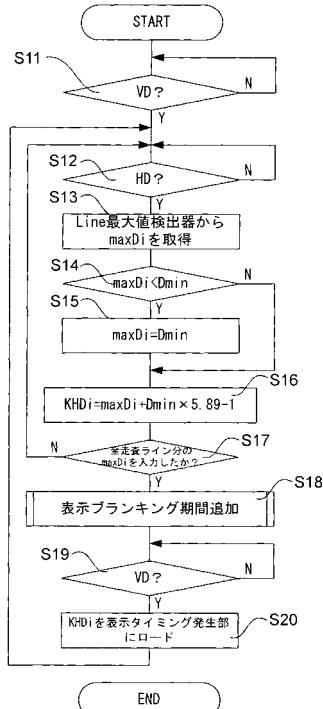

そして、マイコン34は、ライン最大値検出器22によって検出された補正画像データの最大値を用いて、図28のフローチャートにしたがい、各走査配線の走査時間を算出する。20

#### 【0375】

マイコン34は、垂直同期信号VDが現れるまでループを行い待機する(ステップS11)。垂直同期信号VDを受け取ると、水平同期信号HDが現れるまでループを行い待機する(ステップS12)。水平同期信号HDを受け取ると1ライン分の処理を開始する。

#### 【0376】

まず、ライン最大値検出器22から当該水平走査配線の補正画像データの最大値 $m_{a \times D_i}$ (i:ライン番号)を取得する(ステップS13)。なお、 $m_{a \times D_i}$ は、補正画像データの値をパルス幅変調のためのクロック数(Pwmclk数)に換算した値となっている。

#### 【0377】

ステップS13で取得した補正画像データの当該水平走査配線の最大値 $m_{a \times D_i}$ と $D_{min}$ とを比較し(ステップS14)、 $m_{a \times D_i}$ が $D_{min}$ より小さければ、 $m_{a \times D_i} = D_{min}$ とし(ステップS15)、それ以外の場合、 $m_{a \times D_i}$ は変更しない。30

#### 【0378】

ここで、 $D_{min}$ とは、上述した変調駆動回路へのデータの転送時間や非駆動時間を考慮して最低限割り当てなければならない表示走査時間(KHDMin)を考えたときに、その最低限の表示走査時間(KHDMin)で表示可能な画像データの値(Pwmclk数)のことである。

#### 【0379】

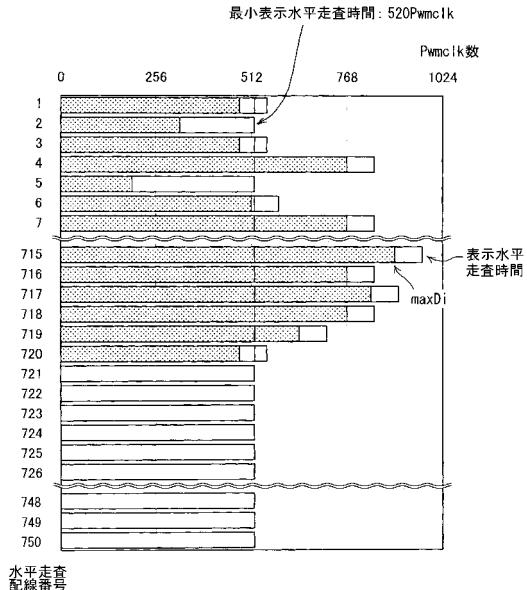

本実施の形態では、シフトレジスタ5のシフトクロックSCLKはMCLKを1/2分周したものであり(詳しくは後述する)、またメモリA26,メモリB27の出力を8層に分けてシフトレジスタ5に転送する。したがって、1ライン分のデータを転送するためのシフト時間は、 $1280\text{個} \times 3$ (RGB) / 8層 = 480クロック(SCLK数)となる。そして、シフト時間に加えて、その他の処理のために40クロックは使用すると見越し、最低限の表示走査時間(KHDMin)として520クロック(SCLK数)を確保する(以降最小表示水平走査期間と記すこともある)。40

#### 【0380】

この、520クロックは入力画像の水平走査時間の0.63倍( $= 520 / (1648 / 2)$ )である。

#### 【0381】

なお、本実施の形態では、パルス幅変調のためのクロックPwmclkは、入力映像信号50

(720P)の水平同期信号に位相ロックをかけ以下のように作成した。

#### 【0382】

本実施の形態では、パルス幅変調のためのクロックPwmckの1水平走査期間(1H)のクロック数を280個に設計した。従来の駆動方法ではこのうち256クロック数で決まる時間でパルス幅変調し、残りの24クロックは走査回路内の駆動時間等の時間(非駆動時間: 1.9μsec)として割り当てている。

#### 【0383】

したがって、Pwmckの周波数は、水平同期信号に分周比1:280でPLL回路により位相ロックをかけて発生させ、12.6MHzの周波数を得る。

#### 【0384】

さらに、この表示水平走査時間内に非駆動時間を考慮しなければならない。変調配線の非駆動時間としては2μsec程度設けることが望ましい。本実施の形態では、Pwmckの周期は約79nsecであるので、非駆動時間として24クロック(Pwmck数)を確保する(非駆動時間は1.9μsec)。したがって、最低限の表示水平走査時間(KHDmin)で表示可能な画像データの値Dminは、都合、 $280 \times 0.63 - 24 = 153$ クロック(Pwmck数)となる。

#### 【0385】

すなわち、1ラインの補正画像データの最大値maxDiが153(Dmin)より小さかったとしても、表示走査時間としては最低限177(=280×0.63)クロック(Pwmck数)分の時間(KHDmin)を割り当てなければならない。

#### 【0386】

S14, S15のステップは、この最小表示水平走査時間(KHDmin)を確保するためのものである。つまり、当該水平走査ラインの補正画像データの最大値maxDiとDminを比較し、maxDiがDminより小さい場合は、maxDiにDminを代入し、表示水平走査期間の下限値となる最小表示水平走査時間(KHDmin)を確保する。

#### 【0387】

S16のステップは、表示水平走査時間(KHDi)の計算をする。

#### 【0388】

すなわち、Pwmck単位で計算されているmaxDiから、MCLK単位で表示水平走査時間(KHDi)を計算する。具体的には入力映像信号の水平同期信号の周波数から決まる水平走査期間のクロック数が、Pwmck: 280、MCLK: 1648の比から、Pwmck単位のmaxDiに $5.89 (= 1648 / 280)$ 倍して求める。

#### 【0389】

なお、参考までに、入力される映像信号720pに基づく1水平走査期間の時間は、 $1648 / 2 = 824$ クロック(SCLK数)である。

#### 【0390】

このようにしてi番目のラインの補正画像データの最大値maxDiに基づきステップS16までの処理がすんだら、当該ラインが画像データの最終ラインか否か、すなわち全走査配線分のmaxDiを入力してupDiを算出したか否かを判定する(ステップS17)。ここで最終ラインまで達していないと判定されると再びステップS12~S16の処理を繰り返し、全走査配線について最小表示水平走査時間(KHDmin)が確保された表示水平走査時間(KHDi)が計算される。

#### 【0391】

ステップS18では、全走査配線の総水平走査時間が所定の時間に収まるように各走査配線の水平走査時間を調整する処理を行う。この所定の時間とは入力映像信号720pのフレーム周波数(60Hz)に相当する時間のことである。

#### 【0392】

つまり、ライン最大値検出器22で検出した補正画像データの最大値maxDiを含むように各走査配線の水平走査時間を単純に割り当てた場合、その総走査時間が入力映像信号

10

20

30

40

50

の1フレーム期間に足りない場合もあり得る。

**【0393】**

このように算出された表示水平走査時間( $KHD_i$ )はステップS18で、総和を求められ、入力映像信号の1フレームの時間と比較される。そして、入力画像信号の1フレームの時間に満たない分、表示ブランкиング期間として、例えば最小表示水平走査時間( $KHD_{min}$ )を追加して( $KHD_{721}, KHD_{722} \dots$ の追加)入力画像のフレーム時間と、表示フレーム時間を合わせる。

**【0394】**

このようにして各走査ラインの表示水平走査時間 $KHD_i$ の計算を終えたら、垂直同期信号 $VD$ が現れるまでループを行う(ステップS19)。

10

**【0395】**

垂直同期信号 $VD$ を受け取り1フレームの終了を確認したら、次フレームの開始前に、各走査ラインの表示水平走査時間 $KHD_i$ を表示タイミング発生部33にロードする(ステップS20)。

**【0396】**

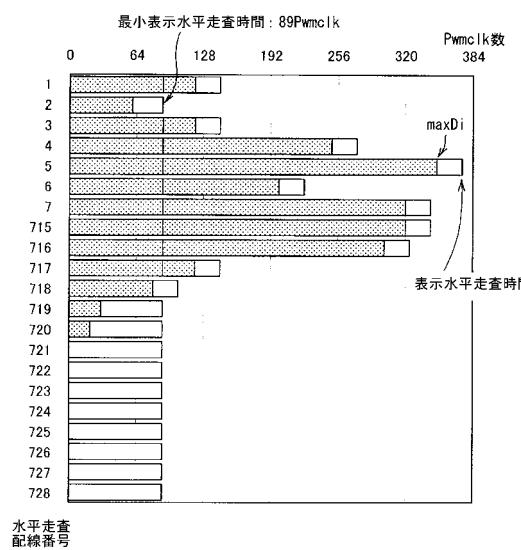

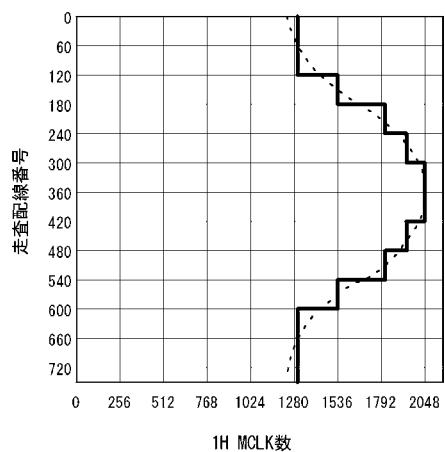

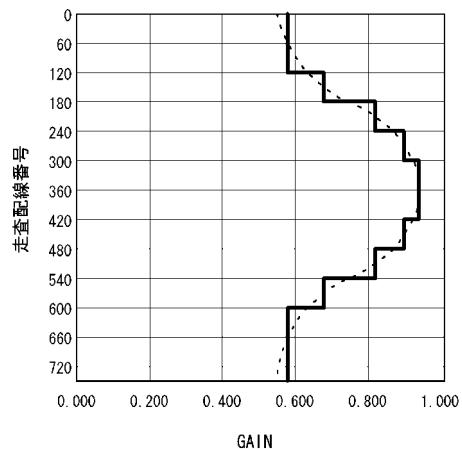

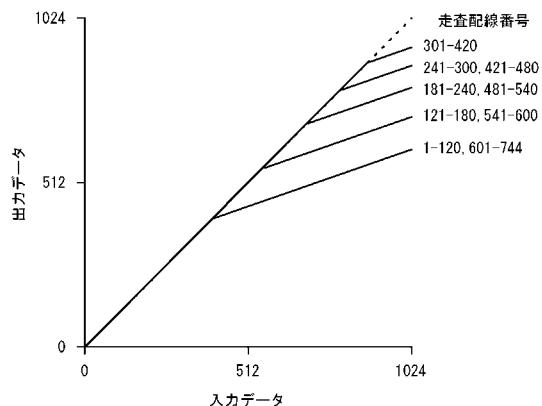

以上の処理により算出した各水平走査ラインの表示走査時間 $KHD_i$ の一例を図29の表および図30に示す。

**【0397】**

本実施の形態では、マイコン34で行う処理は、離散補正データ算出部のCPU102で実行しマイコン34を省略することも可能である。

20

**【0398】**

本実施の形態では1水平走査期間のサンプルクロック数(MCLK数)を1648個に設計したので、1フレームのMCLK数は、 $750 \times 1648 = 1236000$ クロックとなる。Pwmclk数は、その( $280 / 1648$ )倍の210000クロックである。

**【0399】**

図29の表に示すように、1ライン中の補正画像データの最大値 $maxDi$ に非駆動時間24クロック(Pwmclk数)を加算した値、またはシフト時間とその他の処理に要する時間(最小表示水平走査時間)89クロック(Pwmclk数)のいずれか長いほうが、1Hの時間(表示水平走査時間)となる。

**【0400】**

30

たとえば、1ライン目については、 $maxDi$ に非駆動時間を加算した値120が最小表示水平走査時間( $KHD_{min}$ )：89を上回るので、表示水平走査時間は144クロック(Pwmclk数)となり、2ライン目については、 $maxDi$ に非駆動時間を加算した値60が最小表示水平走査時間( $KHD_{min}$ )：89を下回るので、表示水平走査時間は89クロック(Pwmclk数)となる。

**【0401】**

また、図30は図29の表をグラフ化したものである。補正画像データの最大値が大きいラインほど長い表示水平走査時間が割り当てられていること、補正画像データの最大値が小さいラインについても最小表示水平走査時間( $KHD_{min}$ )：89クロックが確保されていることなどがわかる。

40

**【0402】**

また、表示ブランкиング期間を721～728ラインに付加して最小表示水平走査時間( $KHD_{min}$ )を設けたが、補正画像データの各水平走査ラインの最大値( $maxDi$ )によっては表示ブランкиング期間を変させることも好ましいものである。

**【0403】**

なお、本実施の形態では、図18に示すように、各々1フレーム分の補正画像データを記憶することができる2つのフレームメモリ(メモリA26, メモリB27)を設けており、上述した水平走査時間の演算処理を行っている間、1フレーム分の補正画像データを一時的に記憶させておく。

**【0404】**

50

これら 2 つのフレームメモリは、一方のフレームメモリ（例えばメモリ A 2 6）にデータを書き込んでいる際に、他方のフレームメモリ（メモリ B 2 7）からデータを読み出すことができるよう設計してある。具体的には、奇数フレームでは、スイッチ 2 3, 2 4, 2 5, 2 9 の接点をそれぞれ a, a, b, b に選択し、偶数フレームではその逆にする。

#### 【0405】

加算器 1 2 から出力された補正画像データ D o u t は、W アドレス発生部 2 1 が発生する書き込み用アドレス信号に従って、奇数フレームの場合はメモリ A 2 6 に、偶数フレームの場合はメモリ B 2 7 に書き込まれる。W アドレス発生部 2 1 は、水平同期信号 H D から書き込み用アドレスを決定し、M C L K に同期して書き込み用アドレス信号を発生させる。10

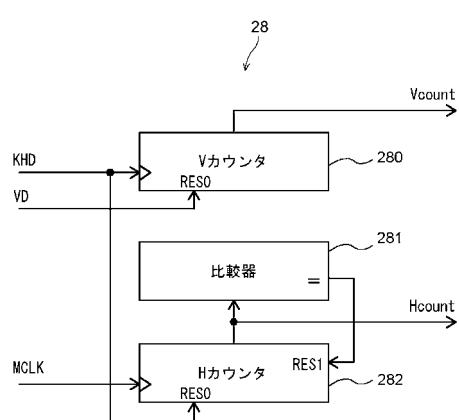

#### 【0406】

また、メモリ A 2 6, メモリ B 2 7 に書き込まれた補正画像データは、R アドレス発生部 2 8 が発生する読み出し用アドレス信号に従って読み出される。R アドレス発生部 2 8 は、各水平走査ライン用のラインデータの読み出しタイミングを、入力映像信号に含まれる水平同期信号 H D ではなく、上記で個別に算出した走査時間 K H D i ( i は水平ライン番号であって、 $i = 0, 1, 2 \dots$  ) に従って決定する。

#### 【0407】

このデータ読み出しのタイミング信号、すなわち表示タイミング信号 K H D は、次に述べる表示タイミング発生部 3 3 にて作られる。

#### 【0408】

(表示タイミング発生部)

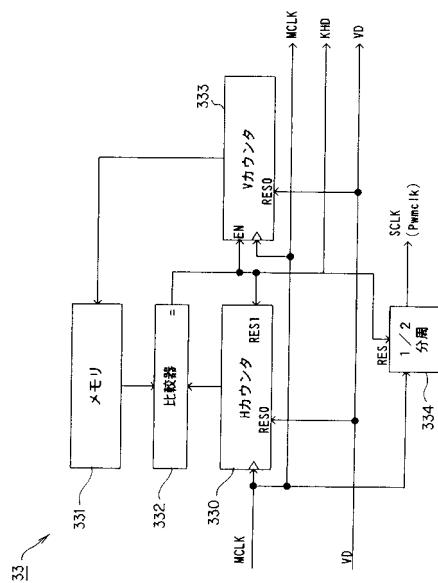

図 3 1 は、表示タイミング発生部 3 3 の回路構成を概略的に示すブロック図である。

#### 【0409】

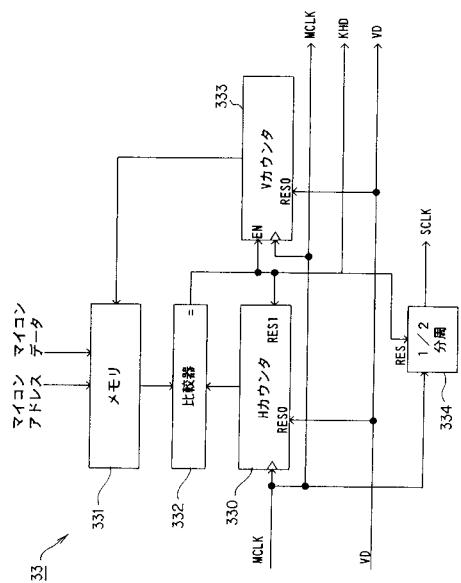

同図に示すように、表示タイミング発生部 3 3 は、H カウンタ 3 3 0 と、メモリ 3 3 1 と、比較器 3 3 2 と、V カウンタ 3 3 3 と、1 / 2 分周器 3 3 4 とを有して構成される。

#### 【0410】

H カウンタ 3 3 0 は、M C L K をカウントし、そのカウンタ値を比較器 3 3 2 に出力する。H カウンタ 3 3 0 のカウンタ値は、垂直同期信号 V D または比較器 3 3 2 の出力の入力を受けてリセットされる。

#### 【0411】

メモリ 3 3 1 は、マイコン 3 4 から各水平走査ラインの水平走査時間 K H D i がロードされる記憶手段である。メモリ 3 3 1 は、アドレス 0 に 1 ライン目の水平走査ラインの表示水平走査時間 K H D 1 を、アドレス 1 に 2 ライン目の表示水平走査ラインの水平走査時間 K H D 2 を、以下順番にアドレス ( i - 1 ) に i ライン目の水平走査ラインの表示水平走査時間 K H D i を格納する。そして、V カウンタ 3 3 3 からアドレス i を入力されると比較器 3 3 2 に表示水平走査時間 K H D i を出力する。30

#### 【0412】

比較器 3 3 2 は、H カウンタ 3 3 0 から入力された値 ( M C L K のカウント値 ) とメモリ 3 3 1 から入力された値 ( 表示水平走査時間 K H D i ) とを比較し、両者が一致した場合にのみ信号を出力する。また、この出力信号は、H カウンタ 3 3 0, V カウンタ 3 3 3 および 1 / 2 分周器 3 3 4 に入力される。40

#### 【0413】

V カウンタ 3 3 3 は、比較器 3 3 2 の出力信号をカウントし、そのカウンタ値をメモリ 3 3 1 に出力する。V カウンタ 3 3 3 のカウンタ値は、垂直同期信号 V D の入力を受けてリセットされる。

#### 【0414】

1 / 2 分周器 3 3 4 は、M C L K を 1 / 2 分周して、シフトレジスタ 5 の動作クロック S C L K を発生する。なお、1 / 2 分周器 3 3 4 は、比較器 3 3 2 の出力信号でリセットされる。

#### 【0415】

10

20

30

40

50

このように構成された表示タイミング発生部 33 は、次のように動作する。

**【0416】**

まず、マイコン 34 から各水平走査ラインの表示水平走査時間  $KHD_i$  が次フレームの開始前（垂直同期信号  $VD$  が入力される前）にメモリ 331 にロードされる。そして、垂直同期信号  $VD$  が入力されると、 $H$  カウンタ 330 と  $V$  カウンタ 333 のカウンタ値がリセットされ、1 フレームの処理が開始される。

**【0417】**

$MCLK$  に同期して、 $V$  カウンタ 333 はカウンタ値 0 をメモリ 331 に出力し、それを受けてメモリ 331 が 1 ライン目の表示水平走査時間  $KHD_1$  を比較器 332 に出力する。一方、 $H$  カウンタ 330 は、 $MCLK$  をカウントし、そのカウンタ値  $N$  を比較器 332 に出力する。10

**【0418】**

$H$  カウンタ 330 のカウンタ値  $N$  が表示水平走査時間  $KHD_1$  に等しくなったときに、比較器 332 から信号が出力される。表示水平走査時間  $KHD_1$  は  $MCLK$  数であり、ここでの比較処理は  $MCLK$  に同期して行われるので、この比較器 332 からの出力信号が 1 ライン目の終了（または 2 ライン目の開始）に相当する表示タイミング信号  $KHD$  となる。。

**【0419】**

そして、表示タイミング信号  $KHD$  が出力されると、 $H$  カウンタ 330 のカウンタ値がリセットされ、 $V$  カウンタ 333 のカウンタ値がインクリメントされる。したがってここからは、 $V$  カウンタ 333 はカウンタ値 1 をメモリ 331 に出力し、メモリ 331 は 2 ライン目の表示水平走査時間  $KHD_2$  を比較器 332 に出力することとなる。 $H$  カウンタ 330 は再び 0 から  $MCLK$  のカウントを開始するので、上記と同様にしてそのカウント値が  $KHD_2$  となったときに比較器 332 から表示タイミング信号  $KHD$ （2 ライン目の終了（または 3 ライン目の開始）に相当する）が出力される。20

**【0420】**

この処理を順次繰り返し、1 フレームに含まれる全ラインについて、各々の表示水平走査時間  $KHD_i$  に従った  $MCLK$  数をもつ表示タイミング信号  $KHD$  を発生させるのである。。

**【0421】**

このように発生させた表示タイミング信号  $KHD$  は、 $R$  アドレス発生部 28 に入力される。 $R$  アドレス発生部 28 は、表示タイミング信号  $KHD$  にしたがって読み出し用アドレス信号を発生し、その信号をスイッチ 25 を介して読み出し側のメモリに出力する。30

**【0422】**

なお、メモリ A26, メモリ B27 からデータを読み出す際の総ライン数は、有効走査線数の 720 本以上であることが望ましく、より好適には、タイミング設計のマージンから 725 ~ 750 本程度にするのがよい（読み出す際の総ライン数を少なくすれば、1 ラインに割り当てる表示水平走査時間が増え、輝度を上げることができることはいうまでもない。）。本実施の形態では、あるフレームの読み出しライン数は 728 本であった。また、1 フレームの総  $Pwmck$  数が一定となるように（各フレームごとに変化しないように）、表示タイミング信号  $KHD$  を発生させることとした。40

**【0423】**

（シフトレジスタ、ラッチ回路）

メモリ A26, メモリ B27 の出力は、1 ライン分の補正画像データを 8 出力に層分けし、各層の補正画像データ  $SD_1 \sim SD_8$  を並列に出力する。また、シフトレジスタ 5 は 8 個のシフトレジスタから構成され、各層の補正画像データ  $SD_1 \sim SD_8$  をそれぞれ別々のシフトレジスタで受け取るようになっている（図 18、図 19 参照）。

**【0424】**

かかる構成により、メモリ A26, メモリ B27 からシフトレジスタ 5 へのデータ転送時間（シフト時間）を短くすることができる。これにより、上記走査時間演算処理における50

「最小表示水平走査時間」(K H D m i n)を短くでき、各ラインに割り当てる表示水平走査時間の自由度を高めることができる。なお、層分けを行わずに、フレームメモリの出力、シフトレジスタをともに1つにして、フレームメモリの読み出し時間を書き込み時間よりも短くするようにしても同様の効果を得ることができる。

#### 【0425】

シフトレジスタ5は、シリアルに入力された補正画像データS D 1～S D 8を各変調配線ごとのパラレルな画像データ(I D 1～I D N)へとシリアル／パラレル変換し、ラッチ回路6へ出力する。ラッチ回路6では1水平走査期間が開始される直前にタイミング信号Data l o a dにより、シフトレジスタ5からのデータをラッチする。ラッチ回路6の出力は、パラレルな画像データD 1～D Nとして変調回路8へと供給される。

10

#### 【0426】

なお本実施の形態では画像データI D 1～I D N、D 1～D Nはそれぞれ9ビットの画像データとした。

#### 【0427】

また、シフトレジスタ5の動作タイミングは上記表示タイミング発生部33からのシフトクロックS C L Kに基づく。

#### 【0428】

##### (変調回路の詳細)

ラッチ回路6の出力であるパラレル画像データD 1～D Nは変調回路8へと供給される。

#### 【0429】

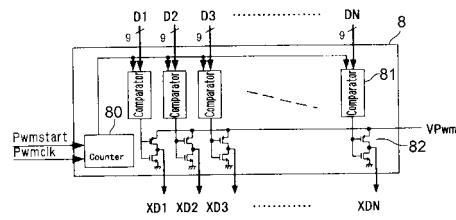

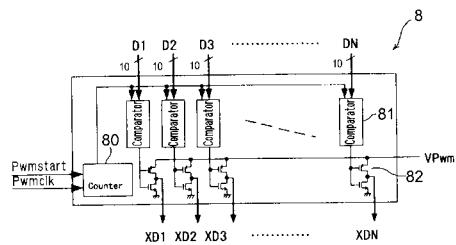

変調回路8は、図32に示すように、P W Mカウンタ80と、各変調配線ごとにコンパレータ81とF E Tなどのスイッチ82を備えたパルス幅変調回路(P W M回路)であって、ラッチ回路6から供給された補正画像データD 1～D Nに応じてパルス幅変調した変調信号(電圧パルス)を各変調配線に印加するものである。

20

#### 【0430】

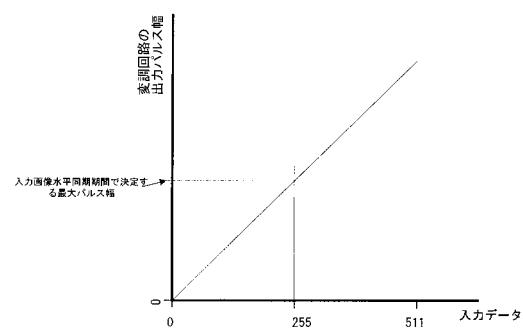

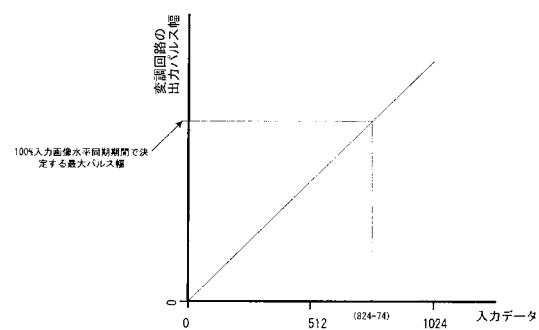

画像データD 1～D Nと変調回路8の出力パルス幅の関係は、図33のようなリニアな関係にある。

#### 【0431】

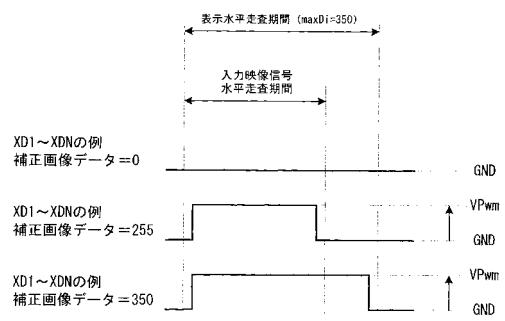

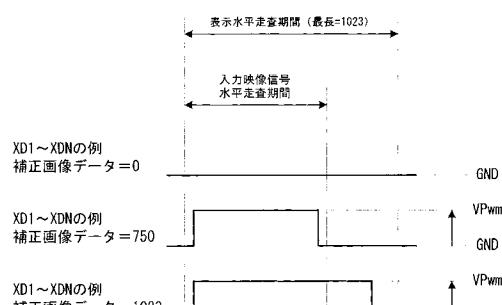

図34に変調回路8から出力される変調信号の出力波形の例を3つ示す。

#### 【0432】

30

同図において上側の波形は、変調回路8への入力データが0の時の波形、中央の波形は、変調回路8への入力データが255(これは、入力映像信号の水平走査時間から非駆動時間を引いた値であり、従来の駆動方法における水平走査時間では最大の値である)の時の波形、下側の波形は、変調回路8への入力データが350の時の波形である。

#### 【0433】

なお、変調回路8への入力データが350の時には、入力映像信号の水平走査時間より長くなっているのが図でよくわかる。

#### 【0434】

図32において、D 1～D Nはラッチ回路6から供給された変調配線の各列1～Nに対応する補正画像データ、P w m s t a r tはP W Mカウンタの同期クリア信号、P w m c l kはP W Mカウンタのクロックである。また、X D 1～X D Nは変調回路8の第1～第N列(N=1 2 8 0 × 3)の出力を表している。

40

#### 【0435】

1水平走査期間が始まると、ラッチ回路6は画像データをラッチするとともに変調回路8へデータを転送する。

#### 【0436】

P W Mカウンタ80は、P w m s t a r t、P w m c l kに基づいてカウントを開始する。

#### 【0437】

各列毎に設けられているコンパレータ81は、P W Mカウンタのカウント値と各列の画像

50

データを比較し、PWMカウンタの値が画像データ以上のときHighを出力し、それ以外の期間はLowを出力する。

#### 【0438】

コンパレータ81の出力は、各列のCMOSインバータからなるスイッチのゲートに接続されており、コンパレータの出力がLowの期間は同図の上側(V PWM側)のpMOSトランジスタがON、下側(GND側)のnMOSトランジスタがOFFとなり、変調配線を電圧V PWMを与える基準電圧源に接続する。

#### 【0439】

逆にコンパレータの出力がHighの期間は、同図の上側のpMOSトランジスタがOFFし、下側のnMOSトランジスタがONするとともに、変調配線をGND電位を与える基準電圧源に接続する。各部が以上のように動作することで、変調回路8が出力するパルス幅変調信号は、図34に示すような、パルスの立ち上がりが同期した波形となる。

#### 【0440】

なお、特に図示してはいないが、上記のData1oadおよびPwmstartは、表示タイミング信号KHDに同期していることはいうまでもない。

#### 【0441】

##### (走査駆動回路)

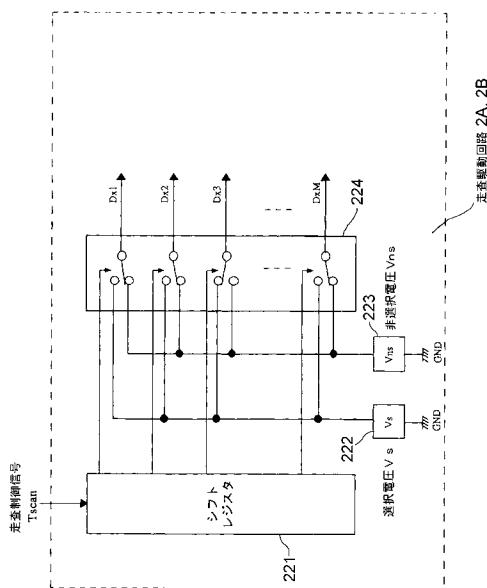

走査駆動回路2A及び2Bは、表示パネルを1水平走査期間に1行ずつ順次走査選択するために、接続端子Dx1～DxMに対して基準電圧源222、223から供給された選択電圧Vsまたは非選択電圧Vnsを選択的に出力する回路である(図35参照)。

#### 【0442】

走査駆動回路2A及び2Bは、走査制御信号信号Tscanに同期して、1水平走査期間ごとに、選択している走査配線を順次切り替え、1フレーム期間、ここでは1垂直走査期間に全ての走査配線の走査選択駆動を行う。

#### 【0443】

なお、走査制御信号Tscanは、表示タイミング発生部33で生成された各走査配線の表示タイミング信号KHDに同期した信号である。走査制御信号Tscanとして表示タイミング信号KHDそのものを用いることもできる。

#### 【0444】

走査駆動回路2A及び2Bは、図35に示すようにそれぞれM個のスイッチアレイ224とシフトレジスタ221などから構成される。これらのスイッチはバイポーラトランジスタやFETにより構成するのが好ましい。

#### 【0445】

なお、走査配線での電圧降下を低減するためには、走査駆動回路は図19に示したように、表示パネル1の走査配線の両端に接続され、両端からドライブされることが好ましい。この場合には、1チップ集積回路が、いずれの端にも簡単に実装できるように、出力端子から出力される走査信号の出力順序を反転し得る回路構成を採用することが好ましい。このような回路構成は、双方向シフトレジスタを用いれば簡単に設計できる。

#### 【0446】

このような表示装置により画像の表示を行ったところ、従来からの課題であった走査配線における電圧降下量を補正することができ、それに起因する表示画像の劣化を改善することができる。

#### 【0447】

また、離散的に補正データを算出し、離散的に計算した点と点の間はそれを補間して求めることにより、補正データを非常に簡単に計算させることができ、さらに非常に簡単なハードウェアでそれを実現できるなど、非常に優れた効果がある。

#### 【0448】

そして走査配線に生じる電圧降下を補正し、かつ、走査配線の抵抗値が0に対する輝度で画像を表示すること(走査配線抵抗により電圧降下している状態で駆動した場合より輝度が大きく表示すること)を両立できる。

10

20

30

40

50

**【0449】**

(第2の実施の形態)

上記第1の実施の形態では、表示走査時間演算処理において、前述したように、ライン最大値検出器22で検出した補正画像データの最大値 $m_a \times D_i$ を含むように各ラインの表示水平走査時間を割り当てた。そして、走査配線の電圧降下補正し、かつ輝度低下の無い画像表示が可能となった。しかしながら、画像によっては、割り当てを行った表示水平走査時間の1フレーム分の和である総表示水平走査時間が入力映像の1フレーム時間を超過してしまうことが、生じることがあった。本実施の形態は、この点を改善するものである。

**【0450】**

10

本実施の形態と、上記第1の実施の形態との違いは、各々の水平走査ラインの当該走査配線の補正画像データの最大値 $m_a \times D_i$ を含むように各走査ラインの表示走査時間を単純に割り当てた時、その総水平走査時間が入力映像信号の1フレーム期間を超過してしまうことが予想される場合に、1フレーム期間に収まるように、各表示水平走査時間、補正画像データを調整する点である。

**【0451】**

本実施の形態に係る画像表示装置の表示パネルの概観、表示パネルの電気的接続、表面伝導型放出素子の特性、表示パネルの駆動方法等、重複する部分は、第1の実施形態と同じである。

**【0452】**

20

なお、ここでは、表示装置の価格を下げるために、図36に示すように、片側走査の構成とした場合を例に挙げて説明する。

**【0453】**

デジタル回路においては、その回路で取り扱うことのできるデータ幅(ビット数)に制限がある。このデータ幅は一般的にハードウェアのコスト等との兼ね合いから決定される。特に、本実施の形態のごとく補正画像データに応じてパルス幅変調を行う構成の場合、1水平走査期間に収るようにパルス幅を変調する必要があることから、補正にともなうデータ幅の増加、すなわち階調数の増加により変調回路の動作クロックの高速化が要求されることがある。そのため、不要輻射や電力消費量が大きくなる可能性があるが、必要に応じてディザ法等の使用によってパルス幅変調器に入力するデータ幅を少なくすることによって動作クロックは下げることができる。

30

**【0454】**

一方、補正画像データの増大により、いわゆるオーバーフローの問題が生ずることがある。すなわち、画像データに対して補正データを単純に加算したときに、その演算結果がパルス幅変調器で取り扱うことのできるデータ幅を超えると、ビットの折り返しなどが起こり、表示画像の反転などの画像の乱れが生ずるのである。

**【0455】**

このため、本実施の形態では、あらかじめ補正画像データの最大値を計算して定め、最大値に対応するビット幅を持ったパルス幅変調器を設ける。

**【0456】**

40

そして、総表示水平走査時間が入力映像信号の1フレーム期間を超過しないように、各表示水平走査時間、補正画像データを調整する。

**【0457】**

(システム全体と各部分の機能説明)

補正データ算出手段を内蔵した本実施の形態の画像表示装置の信号処理回路ハードウェアについて説明する。

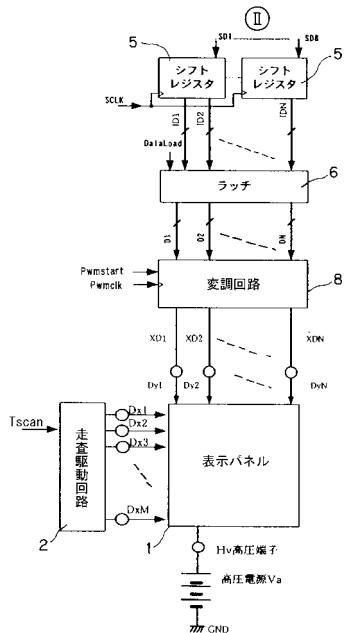

**【0458】**

図37はその回路構成の概略を示すブロック図である。図37は、走査配線の走査時間決定に係る回路を示している。図37に示す回路の入力(I)は図17に示したものと同じ回路からの出力である。また、図37に示す回路の出力(II)は、図36に示す回路に

50

入力(II)される。基本構成は図18と同じである。

【0459】

そして、31はマイコン34の演算結果を受けて補正画像データの調整を行う画像データ調整手段たるゲインレジスタであり、この部分が図18の構成と異なる点である。

【0460】

以下に、図17、図37、図36を参照しつつ、本実施形態の表示装置の構成について詳しく説明する。

【0461】

(同期信号分離回路、タイミング発生回路、逆処理部)

第1の実施の形態と同じである。

10

【0462】

(データ配列変換部)

第1の実施の形態と同じである。

【0463】

(補正データ算出手段)

第1の実施の形態と同じである。

【0464】

(離散補正データ算出部)

第1の実施の形態と同じである。

【0465】

(補正データ補間部)

第1の実施の形態と同じである。

20

【0466】

(遅延回路19)

第1の実施の形態と同じである。

【0467】

(加算器12)

第1の実施の形態と同じである。

【0468】

(水平走査期間の制御について)

30

図36に示した実際に検討した構成において、走査配線抵抗が5程度、表面伝導型放出素子の素子電流を0.5mA程度、素子数 $720 \times 1280 \times 3$ (RGB)とし、8bit幅の画像データ(最大:255)を補正した補正画像データの最大値は1000程度になる。そのためパルス幅変調器のbit幅を10bitと設計する。ここで、パルス幅変調器のbit幅を従来どおり8bitとし下位2bitをディザ法等を用い階調を表現してもよい。

【0469】

(ライン最大値検出器、マイコンにおける走査時間演算処理)

加算器12から出力された補正画像データDoutは、ライン最大値検出器22に入力される(図37)。ライン最大値検出器22は、1ライン分の補正画像データのうちから最大値を検出する処理を、各ラインデータごとに行う。

40

【0470】

そして、マイコン34は、ライン最大値検出器22によって検出された補正画像データの最大値を用いて、図38のフローチャートにしたがい、各走査配線の水平走査時間を算出する。

【0471】

マイコン34は、垂直同期信号VDが現れるまでループを行い待機する(ステップS21)。垂直同期信号VDを受け取ると、水平同期信号HDが現れるまでループを行い待機する(ステップS22)。水平同期信号HDを受け取ると1ライン分の処理を開始する。

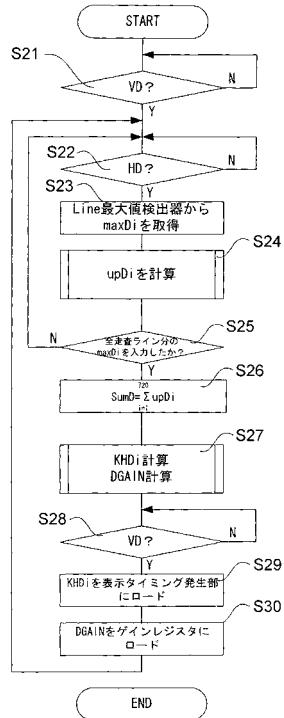

【0472】

50

まず、ライン最大値検出器 22 から当該走査配線の補正画像データの最大値  $\max D_i$  ( $i$  : ライン番号) を取得し(ステップ S23)、 $upDi$  を演算する(ステップ S24)。なお、 $\max D_i$  は、補正画像データの値をパルス幅変調のためのクロック数( $Pwmck$  数)に換算した値となっている。

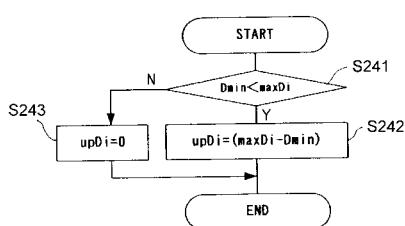

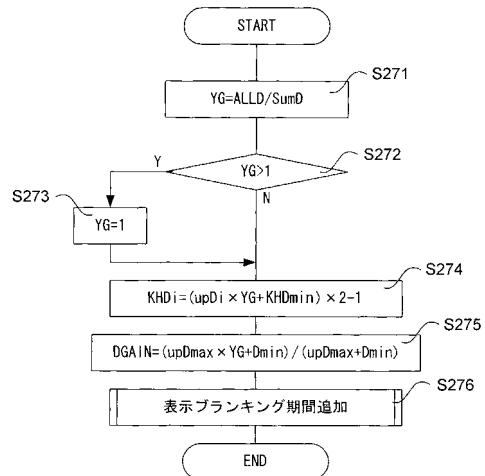

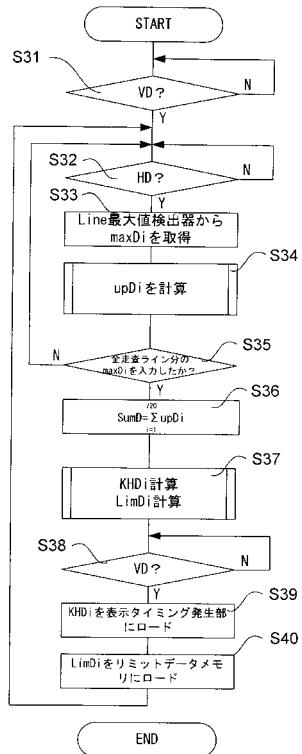

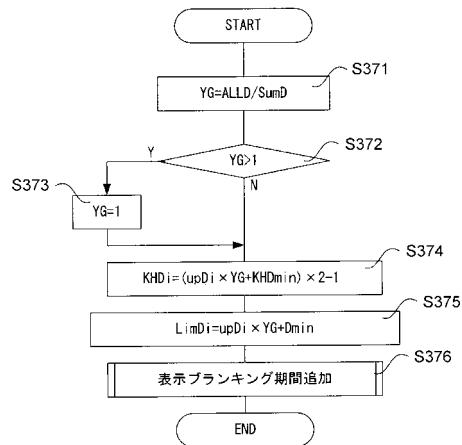

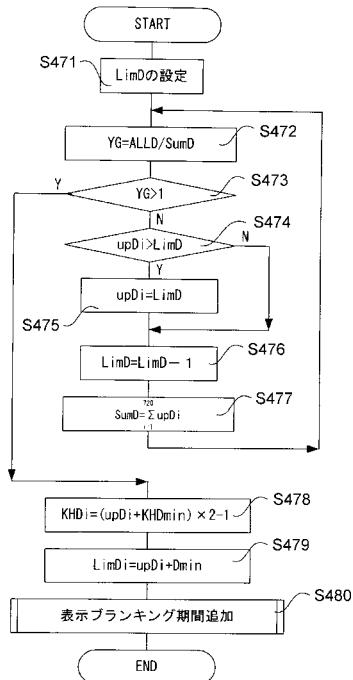

#### 【0473】

$upDi$  の計算は、図 39 のフローチャートに従って行われる。ステップ S23 で取得した補正画像データの当該走査配線の最大値  $\max D_i$  と  $Dmin$  とを比較し(ステップ S241)、 $\max D_i$  が  $Dmin$  より大きければ、その差( $\max D_i - Dmin$ )を  $upDi$  にセットし(ステップ S242)、それ以外の場合は  $upDi$  に 0 をセットする(ステップ S243)。

10

#### 【0474】

ここで、 $Dmin$  とは、上述した変調手段へのデータの転送時間や非駆動時間を考慮して最低限割り当てなければならない表示水平走査時間( $KHDmin$ )を考えたときに、その最低限の表示水平走査時間( $KHDmin$ )で表示可能な画像データの値( $Pwmck$  数)のことである。

#### 【0475】

本実施の形態では、シフトレジスタ 5 のシフトクロック  $SCLK$  は  $MCLK$  を 1 / 2 分周したものであり(詳しくは後述する)、またメモリ A26, メモリ B27 の出力を 8 層に分けてシフトレジスタ 5 に転送する。したがって、1 ライン分のデータを転送するためのシフト時間は、 $1280$  個  $\times 3$  (RGB) / 8 層 = 480 クロック( $SCLK$  数)となる。そして、シフト時間に加えて、その他の処理のために 40 クロックは使用すると見越し、最低限の表示水平走査時間( $KHDmin$ )として 520 クロック( $SCLK$  数)を確保する(以降最小表示水平走査期間と記すこともある)。なお、本実施の形態では、パルス幅変調のためのクロック  $Pwmck$  はシフトクロック  $SCLK$  同じ周波数のものを用いた。

20

#### 【0476】

さらに、この表示水平走査時間内に非駆動時間を考慮しなければならない。変調配線の非駆動時間としては  $2 \mu sec$  程度設けることが望ましい。本実施の形態では、 $Pwmck$  の周期は約  $27nsec$  であるので、非駆動時間として 74 クロック( $Pwmck$  数)を確保すればよい。したがって、最低限の表示水平走査時間( $KHDmin$ )で表示可能な画像データの値  $Dmin$  は、都合、 $520 - 74 = 446$  クロック( $Pwmck$  数)となる。すなわち、1 ラインの補正画像データの最大値  $\max D_i$  が  $446$  ( $Dmin$ ) より小さかったとしても、表示水平走査時間としては最低限 520 クロック( $Pwmck$  数)分の時間( $KHDmin$ )を割り当てなければならない。

30

#### 【0477】