(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5121574号

(P5121574)

(45) 発行日 平成25年1月16日(2013.1.16)

(24) 登録日 平成24年11月2日(2012.11.2)

(51) Int.Cl.

H05K 3/28 (2006.01)

H01L 23/14 (2006.01)

F 1

H05K 3/28

H01L 23/14B

R

請求項の数 14 (全 30 頁)

(21) 出願番号 特願2008-138910 (P2008-138910)

(22) 出願日 平成20年5月28日 (2008.5.28)

(65) 公開番号 特開2009-289849 (P2009-289849A)

(43) 公開日 平成21年12月10日 (2009.12.10)

審査請求日 平成23年2月3日 (2011.2.3)

(73) 特許権者 000190688

新光電気工業株式会社

長野県長野市小島田町80番地

(74) 代理人 100070150

弁理士 伊東 忠彦

(72) 発明者 山本 貴之

長野県長野市小島田町80番地 新光電気

工業株式会社内

審査官 飛田 雅之

最終頁に続く

(54) 【発明の名称】配線基板及び半導体パッケージ

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁層と、前記絶縁層上に形成された配線と、前記配線の少なくとも一部を覆うように前記絶縁層上に形成されたソルダーレジスト層と、を有し、

前記ソルダーレジスト層が複数の層から構成されている配線基板であって、

前記複数の層は最大粒径の異なるフィラーを含有し、前記複数の層を構成する最内層の層厚は前記配線の層厚よりも厚く、前記最内層に含有される前記フィラーの最大粒径は、隣接する前記配線同士の最短間隔よりも小さいことを特徴とする配線基板。

## 【請求項 2】

前記最内層に含有される前記フィラーの最大粒径は、前記複数の層を構成する他の層に含有される前記フィラーの最大粒径よりも小さいことを特徴とする請求項1記載の配線基板。 10

## 【請求項 3】

前記最内層に含有される前記フィラーの量は、前記複数の層を構成する他の層に含有される前記フィラーの量と同一であることを特徴とする請求項1又は2記載の配線基板。

## 【請求項 4】

前記フィラーの二次凝集物は、前記最内層に含有されていないことを特徴とする請求項1乃至3の何れか一項記載の配線基板。

## 【請求項 5】

前記最内層は、前記配線を被覆して前記絶縁層上に形成されており、

前記最内層上に、前記複数の層を構成する他の層が積層されている請求項 1 乃至 4 の何れか一項記載の配線基板。

**【請求項 6】**

前記複数の層を構成する他の層に含有される前記フィラーの最大粒径は、印刷性、耐水性、クラック発生の防止に基づいて決定されている請求項 1 乃至 5 の何れか一項記載の配線基板。

**【請求項 7】**

前記ソルダーレジスト層は、前記配線のパッドとなる領域を露出して形成されている請求項 1 乃至 6 の何れか一項記載の配線基板。

**【請求項 8】**

絶縁層と、前記絶縁層上に形成された配線と、前記配線の少なくとも一部を覆うように前記絶縁層上に形成されたソルダーレジスト層と、を有し、

前記ソルダーレジスト層が複数の層から構成されている半導体パッケージであって、

前記絶縁層は、回路形成面側に電極パッドを備えた半導体チップの、前記回路形成面を覆うように形成されており、

前記配線と前記電極パッドとが電気的に接続されており、

前記複数の層は最大粒径の異なるフィラーを含有し、前記複数の層を構成する最内層の層厚は前記配線の層厚よりも厚く、前記最内層に含有される前記フィラーの最大粒径は、隣接する前記配線同士の最短間隔よりも小さいことを特徴とする半導体パッケージ。

**【請求項 9】**

前記最内層に含有される前記フィラーの最大粒径は、前記複数の層を構成する他の層に含有される前記フィラーの最大粒径よりも小さいことを特徴とする請求項 8 記載の半導体パッケージ。

**【請求項 10】**

前記最内層に含有される前記フィラーの量は、前記複数の層を構成する他の層に含有される前記フィラーの量と同一であることを特徴とする請求項 8 又は 9 記載の半導体パッケージ。

**【請求項 11】**

前記フィラーの二次凝集物は、前記最内層に含有されていないことを特徴とする請求項 8 乃至 10 の何れか一項記載の半導体パッケージ。

**【請求項 12】**

前記最内層は、前記配線を被覆して前記絶縁層上に形成されており、

前記最内層上に、前記複数の層を構成する他の層が積層されている請求項 8 乃至 11 の何れか一項記載の半導体パッケージ。

**【請求項 13】**

前記複数の層を構成する他の層に含有される前記フィラーの最大粒径は、印刷性、耐水性、クラック発生の防止に基づいて決定されている請求項 8 乃至 12 の何れか一項記載の半導体パッケージ。

**【請求項 14】**

前記ソルダーレジスト層は、前記配線のパッドとなる領域を露出して形成されている請求項 8 乃至 13 の何れか一項記載の半導体パッケージ。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、配線基板及び半導体パッケージに関し、特に、複数の層から構成されているソルダーレジスト層を有する配線基板及び半導体パッケージに関する。

**【背景技術】**

**【0002】**

例えば、ビルドアップ配線を有する配線基板上に半導体チップを搭載した半導体パッケージにおいて、配線基板の最外層にはソルダーレジスト層が形成されている。ソルダーレ

10

20

30

40

50

ジスト層には、感光性を有するフォトソルダーレジスト材料を用いることが一般的である。又、ソルダーレジスト層は、十分な厚さの層を形成するために二層構造とするのが一般的である。

#### 【0003】

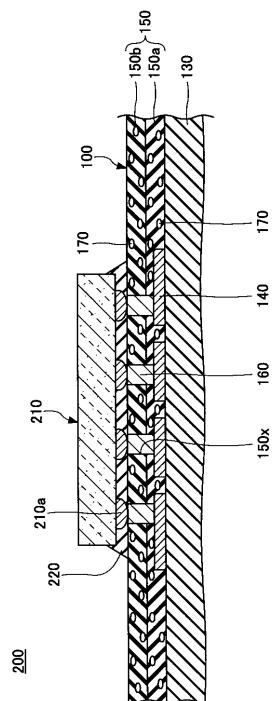

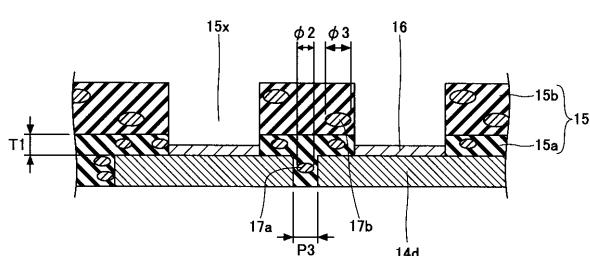

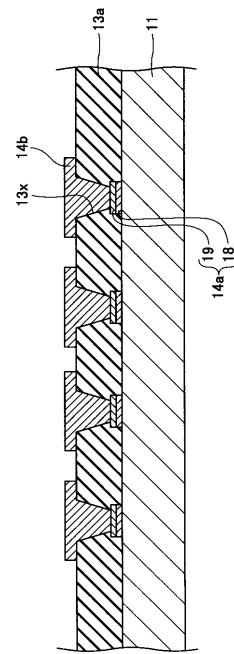

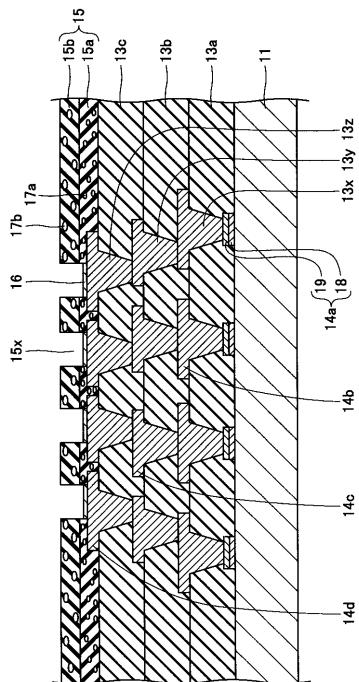

図1は、従来の半導体パッケージを部分的に例示する断面図である。図1を参照するに、半導体パッケージ200は、配線基板100と、半導体チップ210と、アンダーフィル樹脂220とを有する。配線基板100は、絶縁層130と、配線140と、ソルダーレジスト層150と、金属層160とを有する。ソルダーレジスト層150は内層150aと外層150bとの二層から構成されている。ソルダーレジスト層150を構成する内層150a及び外層150bはフィラー170を含有している。

10

#### 【0004】

配線基板100において、絶縁層130上には配線140が形成され、更に、配線140の一部を露出する開口部150xを有するソルダーレジスト層150が形成されている。ソルダーレジスト層150の開口部150xには、金属層160が形成されている。金属層160は、配線140と電気的に接続されている。

#### 【0005】

半導体チップ210は、ボール状端子210aを有する。半導体チップ210は、シリコン等からなる薄板化された半導体基板(図示せず)上に半導体集積回路(図示せず)や電極パッド(図示せず)が形成され、電極パッド(図示せず)上には電極となるボール状端子210aが形成されたものである。半導体チップ210のボール状端子210aは、配線基板100の金属層160と電気的に接続されている。半導体チップ210とソルダーレジスト層150との間にはアンダーフィル樹脂220が充填されている。

20

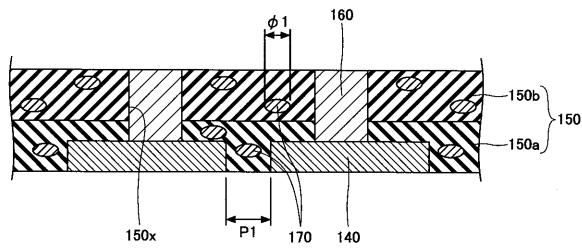

#### 【0006】

図2は、図1に示す半導体パッケージを部分的に例示する断面図である。図2において、図1と同一部品については、同一符号を付し、その説明は省略する場合がある。P1は配線140の最短間隔を示している。1はフィラー170の粒径を示している。なお、粒径とは最大粒径を指す。すなわち、粒径とはフィラーの寸法のうち最も長い部分を指す。例えば、フィラーが球形であれば直径、フィラーの断面が楕円形の場合には長径のことを意味する。又、複数のフィラーが存在する場合には、その中の最大粒径を指す。

30

#### 【0007】

ソルダーレジスト層150を構成する内層150a及び外層150bは、粒径1のフィラー170を含有している。フィラー170は、ソルダーレジスト層150の粘度の適正化、印刷性の向上、耐水性の向上、クラック発生の防止等を目的としてソルダーレジスト層150に含有されている。フィラー170の粒径1は、配線140の最短間隔P1よりも小さい。フィラー170の粒径1は、例えば、 $20\mu m$ であり、配線140の最短間隔P1は、例えば、 $30\mu m$ である(例えば、特許文献1参照)。

【特許文献1】特開2000-31628号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

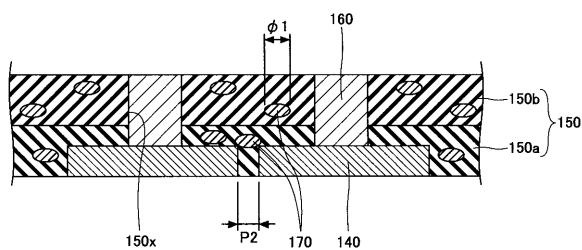

#### 【0008】

しかしながら、半導体パッケージ200の小型化、薄型化が進むにつれて、配線140のピッチは狭くなりつつある。図3は、図2に示す配線のピッチが狭くなった様子を例示する断面図である。図3において、図2と同一部品については、同一符号を付し、その説明は省略する場合がある。P2は配線140の最短間隔を示している。

40

#### 【0009】

配線140の狭ピッチ化が進むと、図3に示すように、フィラー170の粒径1は、相対的に配線140の最短間隔P2よりも大きくなるため、フィラー170が隣接する配線140に接する位置に存在する場合があり得る。

#### 【0010】

ところで、ソルダーレジスト層150に外部から水分が浸入する場合があるが、そのよ

50

うな状態で半導体パッケージ 200 を構成する配線基板 100 に電圧が印加されると、配線 140 を構成する Cu 等の金属がイオン化して再結晶化する所謂マイグレーションが発生する場合がある。

#### 【0011】

水分は、フィラー 170 と内層 150a との界面から内層 150a に浸入しやすいため、図 3 に示すようにフィラー 170 が隣接する配線 140 に接する位置に存在すると、マイグレーションが発生した場合に配線 140 を構成する Cu 等の金属のイオン化が加速される。イオン化した金属は、フィラー 170 と内層 150a との界面に沿って内層 150a を容易に移動して再結晶化するため、隣接する配線 140 間の絶縁抵抗が急激に低下し、隣接する配線 140 は電気的に短絡するに到る。

10

#### 【0012】

このように、従来の半導体パッケージ 200 を構成する配線基板 100 において、ソルダーレジスト層 150 に含有されるフィラー 170 の粒径 1 は、ソルダーレジスト層 150 に覆われた配線 140 の最短間隔 P2 よりも大きい場合がある。このため、フィラー 170 の存在に起因してマイグレーションが進行するという問題があった。

#### 【0013】

又、上記問題を解決するために、ソルダーレジスト層 150 に含有されるフィラー 170 の粒径 1 を配線 140 の最短間隔 P2 よりも小さくすると、ソルダーレジスト層 150 の粘度の適正化、印刷性の向上、耐水性の向上、クラック発生の防止等のフィラー 170 を含有する本来の目的を十分に果たせなくなるという問題があった。

20

#### 【0014】

本発明は、上記に鑑みてなされたもので、フィラーを含有する本来の目的を十分に果たしつつ、マイグレーションの進行を防止することが可能な配線基板及び半導体パッケージを提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0015】

本発明の一の形態は、絶縁層と、前記絶縁層上に形成された配線と、前記配線の少なくとも一部を覆うように前記絶縁層上に形成されたソルダーレジスト層と、を有し、前記ソルダーレジスト層が複数の層から構成されている配線基板であって、前記複数の層は最大粒径の異なるフィラーを含有し、前記複数の層を構成する最内層の層厚は前記配線の層厚よりも厚く、前記最内層に含有される前記フィラーの最大粒径は、隣接する前記配線同士の最短間隔よりも小さいことを特徴とする。

30

#### 【0018】

本発明の他の形態は、絶縁層と、前記絶縁層上に形成された配線と、前記配線の少なくとも一部を覆うように前記絶縁層上に形成されたソルダーレジスト層と、を有し、前記ソルダーレジスト層が複数の層から構成されている半導体パッケージであって、前記絶縁層は、回路形成面側に電極パッドを備えた半導体チップの、前記回路形成面を覆うように形成されており、前記配線と前記電極パッドとが電気的に接続されており、前記複数の層は最大粒径の異なるフィラーを含有し、前記複数の層を構成する最内層の層厚は前記配線の層厚よりも厚く、前記最内層に含有される前記フィラーの最大粒径は、隣接する前記配線同士の最短間隔よりも小さいことを特徴とする。

40

#### 【発明の効果】

#### 【0019】

本発明によれば、フィラーを含有する本来の目的を十分に果たしつつ、マイグレーションの進行を防止することが可能な配線基板及び半導体パッケージを提供することができる。

#### 【発明を実施するための最良の形態】

#### 【0020】

以下、図面を参照して、本発明を実施するための最良の形態の説明を行う。

#### 【0021】

50

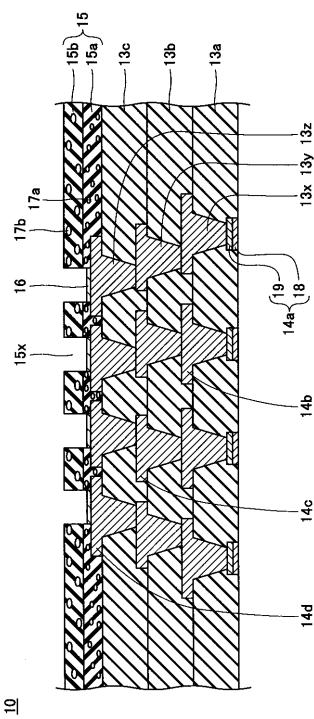

### 第 1 の実施の形態

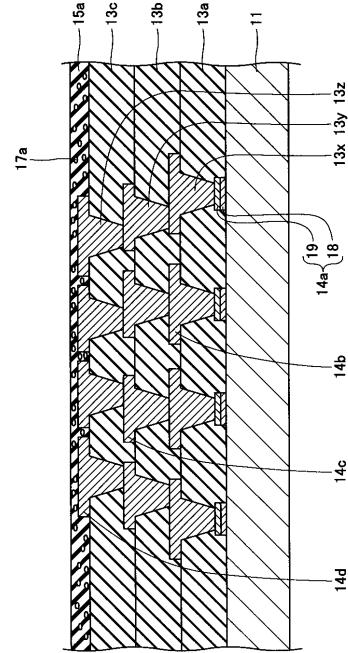

第 1 の実施の形態では、本発明を多層配線層（ビルドアップ配線層）を有する配線基板に適用する例を示す。図 4 は、本発明の第 1 の実施の形態に係るビルドアップ配線層を有する配線基板を例示する断面図である。図 4 を参照するに、配線基板 10 は、第 1 絶縁層 13a と、第 2 絶縁層 13b と、第 3 絶縁層 13c と、配線 14a と、配線 14b と、配線 14c と、配線 14d と、ソルダーレジスト層 15 と、金属層 16 とを有するビルドアップ配線層を備えた配線基板である。

#### 【 0 0 2 2 】

配線基板 10 において、最下層である配線層（以下、「第 1 配線層」とする）には、配線 14a が形成されている。配線 14a を覆うように第 1 絶縁層 13a が形成され、第 1 絶縁層 13a 上には配線 14b が形成されている。更に、配線 14b を覆うように第 2 絶縁層 13b が形成され、第 2 絶縁層 13b 上には配線 14c が形成されている。更に、配線 14c を覆うように第 3 絶縁層 13c が形成され、第 3 絶縁層 13c 上には配線 14d が形成されている。配線 14a は第 1 絶縁層 13a から露出しており、マザーボード等と接続される電極パッドとして機能する。

#### 【 0 0 2 3 】

配線 14a と配線 14b とは、第 1 絶縁層 13a に形成された第 1 ビアホール 13x を介して電気的に接続されている。又、配線 14b と配線 14c とは、第 2 絶縁層 13b に形成された第 2 ビアホール 13y を介して電気的に接続されている。又、配線 14c と配線 14d とは、第 3 絶縁層 13c に形成された第 3 ビアホール 13z を介して電気的に接続されている。

#### 【 0 0 2 4 】

配線 14d を覆うように、開口部 15x を有するソルダーレジスト層 15 が形成されている。ソルダーレジスト層 15 は、フィラー 17a を含有する内層 15a 及びフィラー 17b を含有する外層 15b から構成されている。ソルダーレジスト層 15 の開口部 15x 内の配線 14d 上には、金属層 16 が形成されている。金属層 16 は、例えば、ソルダーレジスト層 15 の開口部 15x 内の配線 14d 上に Niめっき層と Auめっき層をこの順に積層した Ni / Auめっき層等とすることができます。

#### 【 0 0 2 5 】

金属層 16 が形成されている面は、半導体チップが実装される半導体チップ実装面となる。ソルダーレジスト層 15 の開口部 15x 内に露出する金属層 16 は、電極パッドとして機能し、半導体チップの対応する電極と電気的に接続される。

#### 【 0 0 2 6 】

図 5 は、図 4 に示す配線基板を部分的に例示する断面図である。図 5 において、図 4 と同一部品については、同一符号を付し、その説明は省略する場合がある。2 はフィラー 17a の粒径を示している。3 はフィラー 17b の粒径を示している。P 3 は配線 14d の最短間隔を示している。T 1 は内層 15a の上面から配線 14d の上面までの厚さを示している。

#### 【 0 0 2 7 】

なお、本発明でいう粒径とは最大粒径を指す。すなわち、粒径とはフィラーの寸法のうち最も長い部分を指す。例えば、フィラーが球形であれば直径、フィラーの断面が楕円形の場合には長径のことを意味する。又、複数のフィラーが存在する場合には、その中の最大粒径を指す。

#### 【 0 0 2 8 】

ソルダーレジスト層 15 を構成する内層 15a は、粒径 2 のフィラー 17a を含有している。フィラー 17a は、凝集して全体的に球形等をなす所謂二次凝集物を形成し、実質的に粒径が大きくなる場合があるが、本発明では、係る二次凝集物は予め除去されているため、ソルダーレジスト層 15 を構成する内層 15a は、フィラー 17a の二次凝集物を含有していない。厚さ T 1 は、フィラー 17a の粒径 2 よりも厚くすることが好ましい。

10

20

30

40

50

## 【0029】

ソルダーレジスト層15を構成する外層15bは、粒径3のフィラー17bを含有している。フィラー17a及び17bは、ソルダーレジスト層15の粘度の適正化、印刷性の向上、耐水性の向上、クラック発生の防止等を目的としてソルダーレジスト層15を構成する内層15a及び外層15bに含有されている。

## 【0030】

フィラー17aの粒径2は、配線14dの最短間隔P3よりも小さい。フィラー17bの粒径3は、配線14dの最短間隔P3にかかわらず任意で良いが、ソルダーレジスト層15の粘度の適正化、印刷性の向上、耐水性の向上、クラック発生の防止等の目的を考慮すれば、従来の半導体パッケージ200を構成する配線基板100におけるフィラー170の粒径1(図2参照)と同程度であることが好ましい。10

## 【0031】

例えば、配線14dの最短間隔P3が8μmであるとすれば、フィラー17aの粒径2は最短間隔P3=8μmよりも小さくする必要があり、例えば、6μm以下とすることが可能である。フィラー17bの粒径3は従来の半導体パッケージ200を構成する配線基板100におけるフィラー170の粒径1と同程度で、例えば、20μmとすることが可能である。

## 【0032】

なお、ソルダーレジスト層15を構成する内層15aは、フィラー17aを含有しなくても構わない。その場合には、ソルダーレジスト層15の粘度の適正化、印刷性の向上、耐水性の向上、クラック発生の防止等の目的は、フィラー17bを含有する外層15bにより達成することができる。20

## 【0033】

ソルダーレジスト層15を構成する内層15a及び外層15bとしては、例えば、エポキシ系樹脂やイミド系樹脂等を含む感光性樹脂組成物を用いることができる。更に揮発性の溶媒を含有させても構わない。フィラー17a及び17bとしては、例えば、酸化珪素、酸化チタン、酸化アルミニウム、窒化アルミニウム、炭化珪素、チタン酸カルシウム、ゼオライト等の無機化合物、又は、有機化合物等を用いることができる。

## 【0034】

フィラー17aとフィラー17bとは同一の材料で構成しても構わないし、異なる材料で構成しても構わない。内層15aに含有されるフィラー17aの量と、外層15bに含有されるフィラー17bの量とは略同一であっても構わないし、異なる量であっても構わない。ここでいう量とは、例えば、内層15a又は外層15bを構成する感光性樹脂組成物の重量に対するフィラー17a又はフィラー17bの重量(重量%)等である。30

## 【0035】

このように、ソルダーレジスト層15を内層15a及び外層15bから構成する。そして、内層15aは配線14dの最短間隔P3よりも粒径2の小さいフィラー17aを含有し、外層15bは従来の半導体パッケージ200を構成する配線基板100の場合と同程度の粒径3のフィラー17bを含有する。その結果、ソルダーレジスト層15を構成する内層15aに外部から水分が浸入した状態で配線基板10に電圧が印加され、何らかの要因で配線14dを構成するCu等の金属がイオン化して再結晶化する所謂マイグレーションが発生しても、マイグレーションの進行を防止することができる。それと同時に、ソルダーレジスト層15の粘度の適正化、印刷性の向上、耐水性の向上、クラック発生の防止等の目的も達成することができる。40

## 【0036】

より詳しく説明すれば、水分がフィラー17aと内層15aとの界面から内層15aに浸入しても、図5に示すようにフィラー17aは隣接する配線14dに接することが無いため、配線14dを構成するCu等の金属のイオン化が加速されることはない。

## 【0037】

従って、イオン化した金属が、フィラー17aと内層15aとの界面に沿って内層1550

aを移動して再結晶化することもない。よって、隣接する配線14d間の絶縁抵抗は正常な値を維持し、隣接する配線14dが電気的に短絡することなく、マイグレーションの進行を防止することができる。

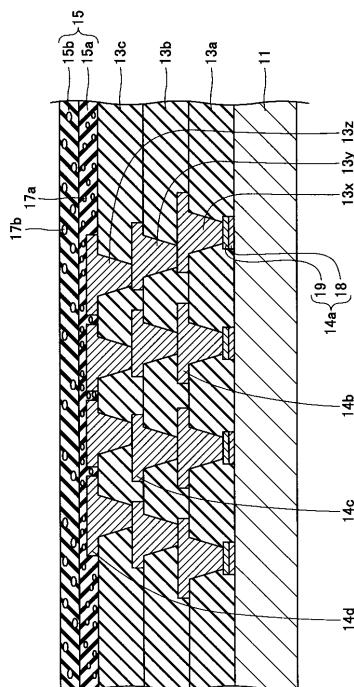

#### 【0038】

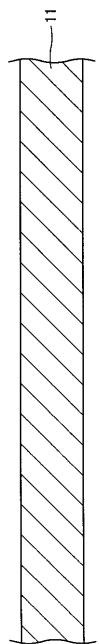

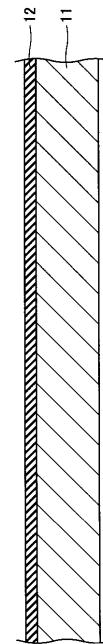

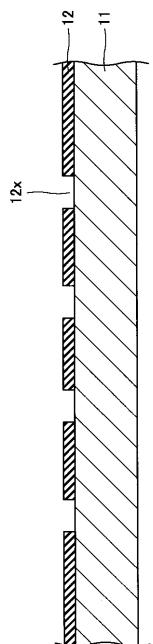

続いて、配線基板10の製造方法について説明する。図6～図18は、本発明の第1の実施の形態に係る配線基板の製造工程を例示する図である。図6～図18において、図4及び図5と同一部品については、同一符号を付し、その説明は省略する場合がある。

#### 【0039】

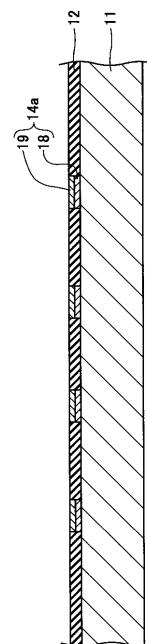

始めに、図6に示す工程では、支持体11を用意する。本実施形態では支持体11として銅箔を用いる。銅箔の厚さは、例えば、35～100μmとすることができます。次いで、図7に示す工程では、支持体11上に、レジスト膜12を形成する。レジスト膜12としては、例えば、ドライフィルム等を用いることができる。

#### 【0040】

次いで、図8に示す工程では、レジスト膜12に対してパターニング処理を行い、配線14aの形成位置に対応する部分に開口部12xを形成する。なお、ドライフィルム状のレジスト膜12に対して予め開口部12xを形成しておき、開口部12xが形成されたレジスト膜12を支持体11に配設してもよい。

#### 【0041】

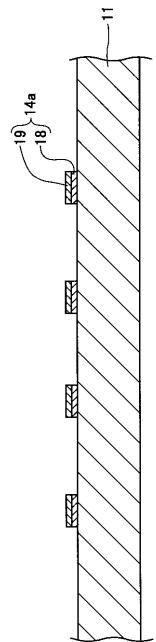

次いで、図9に示す工程では、支持体11をめっき給電層に利用する電解めっき法等により、支持体11上の第1配線層に配線14aを形成する。配線14aは、レジスト膜12に形成された開口部12x内に形成されており、表面めっき層18及びパッド本体19から構成されている。

#### 【0042】

表面めっき層18は、例えば、Au膜、Pd膜、Ni膜をこの順番で順次積層した構造を有している。よって、配線14aを形成するには、先ずAu膜、Pd膜、Ni膜を順にめっきすることにより表面めっき層18を形成し、続いて、表面めっき層18上にCu等からなるパッド本体19をめっきにより形成する。次いで、図10に示す工程では、図9に示すレジスト膜12を除去する。

#### 【0043】

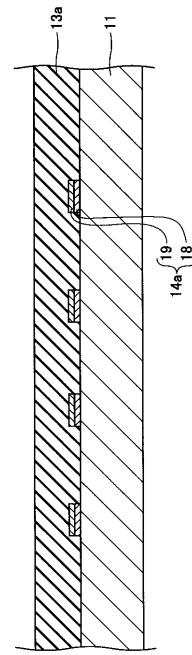

次いで、図11に示す工程では、支持体11に配線14aを被覆する第1絶縁層13aを形成する。第1絶縁層13aの材料としては、エポキシ系樹脂、ポリイミド系樹脂などの樹脂材を用いることができる。第1絶縁層13aの形成方法の一例としては、支持体11に樹脂フィルムをラミネートした後に、樹脂フィルムをプレス(押圧)し、その後、190程度の温度で熱処理して硬化させることにより第1絶縁層13aを得ることができる。

#### 【0044】

次いで、図12に示す工程では、支持体11に形成された第1絶縁層13aに、配線14aが露出するようにレーザ加工法等を用いて第1ビアホール13xを形成する。なお、第1絶縁層13aとして感光性樹脂膜を用い、フォトリソグラフィによりパターニングして第1ビアホール13xを形成する方法を用いてもよいし、スクリーン印刷により開口部が設けられた樹脂膜をパターニングして第1ビアホール13xを形成する方法を用いてもよい。

#### 【0045】

次いで、図13に示す工程では、第1絶縁層13a上に、第1配線層である配線14aに第1ビアホール13xを介して接続される配線14bを形成する。配線14bとしては、例えば、銅(Cu)等を用いることができる。配線14bは、例えば、セミアディティブ法により形成される。

#### 【0046】

配線14bを、セミアディティブ法により形成する例を、より詳しく説明すると、先ず、無電解めっき法又はスパッタ法により、第1ビアホール13x内及び第1絶縁層13a

10

20

30

40

50

の上に Cu シード層（図示せず）を形成した後に、配線 14 b に対応する開口部を備えたレジスト膜（図示せず）を形成する。次いで、Cu シード層をめっき給電層に利用した電解めっき法により、レジスト膜の開口部に Cu 層パターン（図示せず）を形成する。

#### 【0047】

続いて、レジスト膜を除去した後に、Cu 層パターンをマスクにして Cu シード層をエッチングすることにより、配線 14 b を得る。なお、配線 14 b の形成方法としては、上述したセミアディティブ法の他にサブトラクティブ法などの各種の配線形成方法を用いることができる。

#### 【0048】

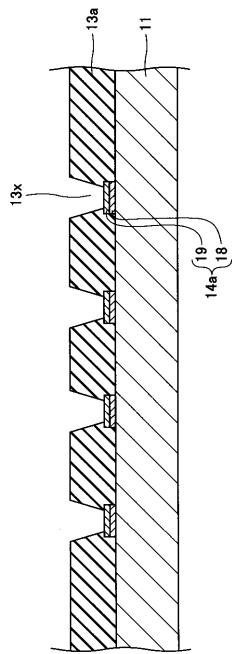

次いで、図 14 に示す工程では、上記と同様な工程を繰り返すことにより、第 1 配線層 ~ 第 4 配線層（配線 14 a ~ 14 d）及び絶縁層 13 a ~ 13 c を積層する。すなわち、支持体 11 に第 2 配線層の配線 14 b を被覆する第 2 絶縁層 13 b を形成した後に、配線 14 b 上の第 2 絶縁層 13 b の部分に第 2 ビアホール 13 y を形成する。10

#### 【0049】

更に、第 2 絶縁層 13 b 上に、第 2 ビアホール 13 y を介して配線 14 b に接続される第 3 配線層である配線 14 c を形成する。配線 14 c としては、例えば、銅（Cu）等を用いることができる。配線 14 c は、例えば、セミアディティブ法により形成される。

#### 【0050】

更に、配線 14 c を被覆する第 3 絶縁層 13 c を形成した後に、配線 14 c 上の第 3 絶縁層 13 c の部分に第 3 ビアホール 13 z を形成する。更に、第 3 絶縁層 13 c 上に、第 3 ビアホール 13 z を介して配線 14 c に接続される第 4 配線層である配線 14 d を形成する。配線 14 d としては、例えば、銅（Cu）等を用いることができる。配線 14 d は、例えば、セミアディティブ法により形成される。20

#### 【0051】

このようにして、支持体 11 上の第 1 配線層の上に所定のビルドアップ配線層が形成される。本実施例では、4 層のビルドアップ配線層（第 1 配線層 ~ 第 4 配線層）を形成したが、n 層（n は 1 以上の整数）のビルドアップ配線層を形成してもよい。

#### 【0052】

次いで、図 15 に示す工程では、配線 14 d を被覆するように第 3 絶縁層 13 c 上に、粒径が 2 であるフィラー 17 a を含有するソルダーレジストを塗布しソルダーレジスト層 15 を構成する内層 15 a を形成する。内層 15 a としては、例えば、エポキシ系樹脂やイミド系樹脂等を含む感光性樹脂組成物を用いることができる。更に揮発性の溶媒を含有させても構わない。フィラー 17 a としては、例えば、酸化珪素、酸化チタン、酸化アルミニウム、窒化アルミニウム、炭化珪素、チタン酸カルシウム、ゼオライト等の無機化合物、又は、有機化合物等を用いることができる。30

#### 【0053】

次いで、図 16 に示す工程では、内層 15 a 上に、粒径が 3 であるフィラー 17 b を含有するソルダーレジスト 15 b を塗布しソルダーレジスト層 15 を構成する外層 15 b を形成する。外層 15 b としては、例えば、エポキシ系樹脂やイミド系樹脂等を含む感光性樹脂組成物を用いることができる。40

#### 【0054】

更に揮発性の溶媒を含有させても構わない。フィラー 17 b としては、例えば、酸化珪素、酸化チタン、酸化アルミニウム、窒化アルミニウム、炭化珪素、チタン酸カルシウム、ゼオライト等の無機化合物、又は、有機化合物等を用いることができる。これで、内層 15 a 及び外層 15 b から構成されるソルダーレジスト層 15 が形成される。

#### 【0055】

次いで、図 17 に示す工程では、ソルダーレジスト層 15 を露光、現像することで開口部 15 x を形成する。これにより、配線 14 d は、ソルダーレジスト層 15 の開口部 15 x 内に露出する。次いで、図 18 に示す工程では、ソルダーレジスト層 15 の開口部 15 x 内の配線 14 d 上に金属層 16 を形成する。金属層 16 は、例えば、ソルダーレジスト50

層 15 の開口部  $15 \times$  内の配線 14 d 上に Ni めっき層と Au めっき層をこの順に積層した Ni / Au めっき層等とすることができます。金属層 16 は、半導体チップ等と接続される電極パッドとして機能する。

#### 【0056】

次いで、図 18 に示す支持体 11 を除去することで、図 4 に示す本発明の第 1 の実施の形態に係る配線基板 10 が製造される。支持体 11 の除去は、塩化第二鉄水溶液、塩化第二銅水溶液又は過硫酸アンモニウム水溶液などを用いたウェットエッチングにより行うことができる。この際、配線 14 a は、最表面に表面めっき層 18 が形成されているため、配線 14 a に対し、支持体 11 を選択的にエッチングして除去することができる。これにより、配線 14 a は第 1 絶縁層 13 a から露出され、マザーボード等と接続される電極パッドとして機能する。10

#### 【0057】

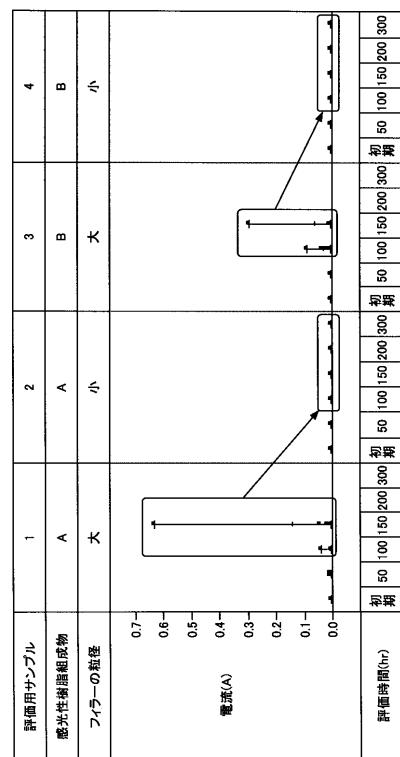

続いて、HAST 試験を実施し、ソルダーレジスト層に配線の最短間隔よりも粒径の小さいフィラー（図 5 のフィラー 17 a に相当）を含有する場合と、配線の最短間隔よりも粒径の大きいフィラー（図 5 のフィラー 17 b に相当）を含有する場合とでマイグレーションの進行が異なるか否かを確認する実験を行った。

#### 【0058】

##### 【表 1】

20

| 評価用サンプル | 感光性樹脂組成物 | フィラーの粒径 |

|---------|----------|---------|

| 1       | A        | 大       |

| 2       | A        | 小       |

| 3       | B        | 大       |

| 4       | B        | 小       |

30

始めに、表 1 に示す 4 種類の評価用サンプル 1 ~ 4 を各 10 個ずつ用意した。表 1 に示す評価用サンプル 1 ~ 4 は、基板上に所定の櫛型パターンを有する配線を形成し、所定の粒径のフィラーを含有する感光性樹脂組成物で被覆したものである。評価用サンプル 1 ~ 4 において、配線は Cu から構成されており、所定の配線の間隔（図 5 の P 3 に相当）は  $8 \mu m$ 、配線の幅は  $8 \mu m$ 、配線の厚さは  $12 \mu m$  である。

#### 【0059】

感光性樹脂組成物としては、感光性樹脂組成物 A と、感光性樹脂組成物 A よりも絶縁性の高い感光性樹脂組成物 B の 2 種類を用意した。感光性樹脂組成物 A 及び感光性樹脂組成物 B は、ともにエポキシ系樹脂である。感光性樹脂組成物の厚さは  $15 \mu m$  とした。表 1 において、フィラーの粒径「大」は、フィラーの粒径が配線の間隔よりも大きいことを意味し、フィラーの粒径「小」は、フィラーの粒径が配線の間隔よりも小さいことを意味する。40

#### 【0060】

すなわち、評価用サンプル 1 は、配線の間隔よりも大きい粒径のフィラーを含有する感光性樹脂組成物 A により、配線を被覆したものである。評価用サンプル 2 は、配線の間隔よりも小さい粒径のフィラーを含有する感光性樹脂組成物 A により、配線を被覆したものである。

#### 【0061】

評価用サンプル 3 は、配線の間隔よりも大きい粒径のフィラーを含有する感光性樹脂組成物 B により、配線を被覆したものである。50

成物 B により、配線を被覆したものである。評価用サンプル 4 は、配線の間隔よりも小さい粒径のフィラーを含有する感光性樹脂組成物 B により、配線を被覆したものである。

#### 【 0 0 6 2 】

次いで、H A S T 試験（高加速高温高湿試験）を行った。試験条件は 130 、 85% R H 、 5 V 印加である。評価用サンプル 1 ~ 4 について、試験開始から 50 、 100 、 150 、 200 、 300 時間後に、隣接する配線間に流れる電流を確認した。図 19 は、 H A S T 試験の結果を例示する図である。

#### 【 0 0 6 3 】

図 19 において、横軸は評価時間 ( h r ) 、縦軸は電流 ( A ) である。電流 ( A ) は配線間の抵抗値 ( ) から計算されたものであり、絶縁性の劣化具合を数値化したものである。前述のように、表 1 に示す 4 種類の評価用サンプル 1 ~ 4 は各 10 個ずつ用意されており、図 19 は、評価用サンプル 1 ~ 4 について各 10 個のデータを各評価時間に測定しプロットしたものである。10

#### 【 0 0 6 4 】

図 19 に示すように、評価用サンプル 1 と評価用サンプル 2 とを比較すると、評価用サンプル 2 は、評価時間が経過しても電流がほとんど変化しないことがわかる。同様に、評価用サンプル 3 と評価用サンプル 4 とを比較すると、評価用サンプル 4 は、評価時間が経過しても電流がほとんど変化しないことがわかる。

#### 【 0 0 6 5 】

すなわち、同じ感光性樹脂組成物を使用しても、配線の間隔よりも小さい粒径のフィラーを含有することにより、マイグレーションの進行を防止できることが確認された。なお、評価用サンプル 1 と評価用サンプル 3 とを比較すると、評価用サンプル 3 の方が、評価時間が経過しても電流の変化が小さい。これは、感光性樹脂組成物 B は感光性樹脂組成物 A よりも樹脂自体の絶縁性が高いためと考えられる。20

#### 【 0 0 6 6 】

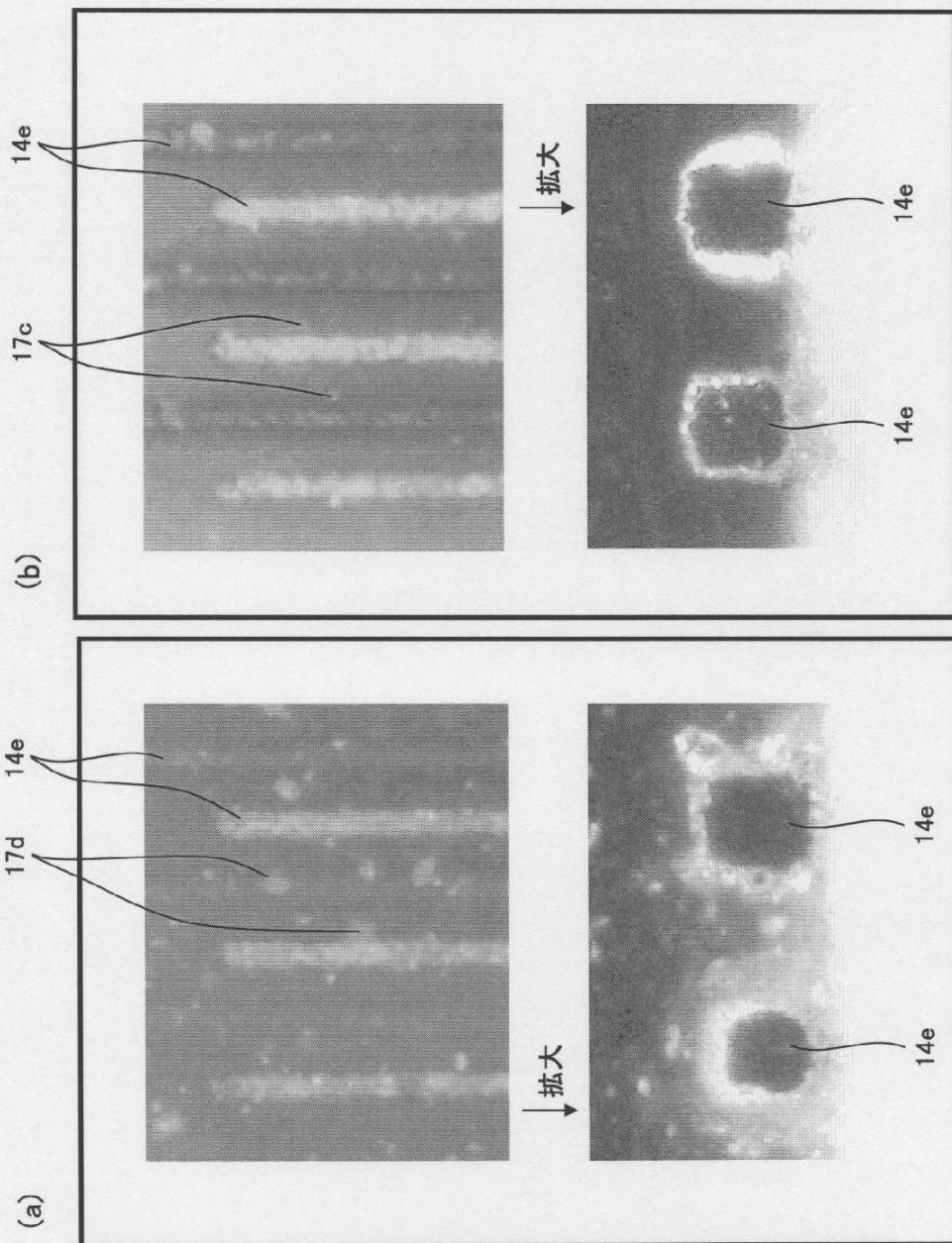

図 20 は、H A S T 試験後の評価用サンプルの外観を例示する図である。図 20 において、 14 e は配線を、 17 c は配線 14 e の間隔よりも小さい粒径のフィラーを、 17 d は配線 14 e の間隔よりも大きい粒径のフィラーを示している。図 20 ( a ) は、評価用サンプル 1 の評価時間 300 時間後の外観を示しており、図 20 ( b ) は、評価用サンプル 2 の評価時間 300 時間後の外観を示している。30

#### 【 0 0 6 7 】

図 20 ( a ) 及び図 20 ( b ) において、上側は平面図であり下側は断面図である。図 20 ( a ) に示すように、感光性樹脂組成物が配線 14 e の間隔よりも大きい粒径のフィラー 17 d を含有する場合には、配線 14 e よりイオン化した Cu がフィラー 17 d の周囲で再結晶化している。そのため、配線 14 e 間の距離が擬似的に狭くなり絶縁劣化に到る。

#### 【 0 0 6 8 】

図 20 ( b ) に示すように、感光性樹脂組成物が配線 14 e の間隔よりも小さい粒径のフィラー 17 c を含有する場合には、図 20 ( a ) に示すような再結晶化は確認できない。そのため、配線 14 e 間の距離が擬似的に狭くなることはなく絶縁劣化には到らない。このように図 20 からも、同じ感光性樹脂組成物を使用しても、配線の間隔よりも小さい粒径のフィラーを含有することにより、マイグレーションの進行を防止できることが確認された。40

#### 【 0 0 6 9 】

本発明の第 1 の実施の形態に係る配線基板 10 によれば、ソルダーレジスト層 15 を内層 15 a 及び外層 15 b から構成する。そして、内層 15 a は配線 14 d の最短間隔 P 3 よりも粒径 2 の小さいフィラー 17 a を含有する。その結果、ソルダーレジスト層 15 を構成する内層 15 a に外部から水分が浸入した状態で配線基板 10 に電圧が印加され、何らかの要因で配線 14 d を構成する Cu 等の金属がイオン化して再結晶化する所謂マイグレーションが発生しても、マイグレーションの進行を防止することができる。50

**【0070】**

又、外層15bは従来の半導体パッケージ200を構成する配線基板100の場合と同程度の粒径3のフィラー17bを含有する。その結果、ソルダーレジスト層15の粘度の適正化、印刷性の向上、耐水性の向上、クラック発生の防止等の目的も達成することができる。

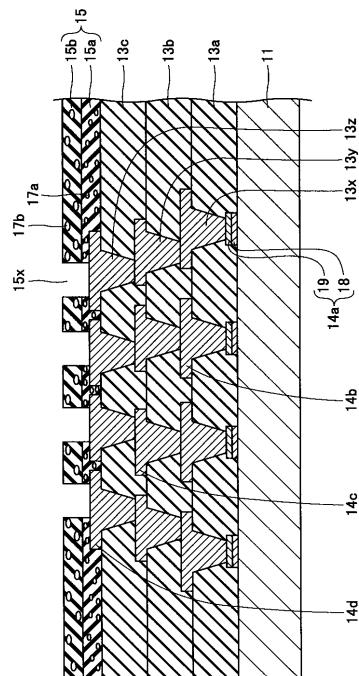

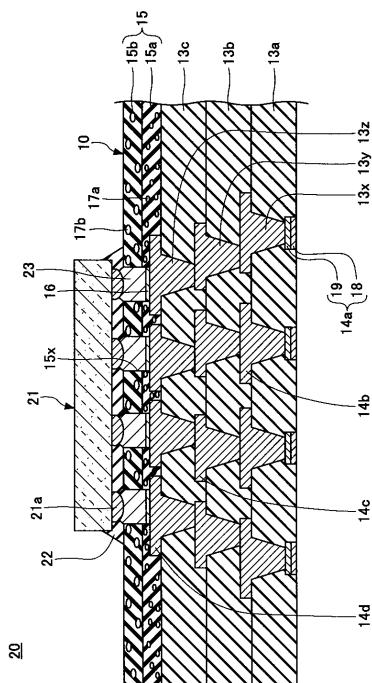

**【0071】****第2の実施の形態**

第2の実施の形態では、本発明をビルドアップ配線層を有する配線基板を備えた半導体パッケージに適用する例を示す。図21は、本発明の第2の実施の形態に係る半導体パッケージを例示する断面図である。図21において、図4と同一部品については、同一符号を付し、その説明は省略する場合がある。図21を参照するに、半導体パッケージ20は、図4に示す配線基板10と、半導体チップ21と、アンダーフィル樹脂22とを有する。配線基板10の金属層16上には、はんだペースト塗布等によりプレソルダ23が形成されている。金属層16とプレソルダ23とは、電気的に接続されている。

10

**【0072】**

半導体チップ21は、シリコン等からなる薄板化された半導体基板(図示せず)上に半導体集積回路(図示せず)や電極パッド(図示せず)が形成され、電極パッド(図示せず)上には電極となるボール状端子21aが形成されたものである。半導体チップ21のボール状端子21aは、プレソルダ23と電気的に接続されている。半導体チップ21とソルダーレジスト層15との間にはアンダーフィル樹脂22が充填されている。

20

**【0073】**

なお、半導体チップ21のボール状端子21aが、はんだから構成されている場合には、半導体チップ21の実装時に、ボール状端子21a及びプレソルダ23は溶融し合金となり、一つのバンプが形成される。

**【0074】**

図22は、本発明の第2の実施の形態に係る半導体パッケージの製造工程を例示する図である。図22において、図21と同一部品については、同一符号を付し、その説明は省略する場合がある。

**【0075】**

始めに、図4に示す配線基板10を用意し、金属層16上に、プレソルダ23を形成する。プレソルダ23は、金属層16に、はんだペーストを塗布しリフロー処理することにより得られる。又、金属層16に、はんだボールを実装しても構わない。次いで、図22に示すように、半導体チップ21のボール状端子21aと配線基板10の金属層16上に形成されたプレソルダ23とを電気的に接続する。

30

**【0076】**

半導体チップ21のボール状端子21aと配線基板10の金属層16上に形成されたプレソルダ23との電気的な接続は、例えば、230℃に加熱し、はんだを融解させることにより行う。なお、半導体チップ21のボール状端子21aが、はんだから構成されている場合には、ボール状端子21a及びプレソルダ23は溶融し合金となり、一つのバンプが形成される。次いで、半導体チップ21とソルダーレジスト層15との間にアンダーフィル樹脂22を充填することにより、図21に示す半導体パッケージ20が完成する。

40

**【0077】**

本発明の第2の実施の形態に係る半導体パッケージ20によれば、本発明の第1の実施の形態に係る配線基板10を用いて半導体パッケージを構成するため、本発明の第1の実施の形態と同様の効果を奏する。

**【0078】**

又、ソルダーレジスト層15を構成する外層15bは、従来の半導体パッケージ200を構成する配線基板100の場合と同程度の粒径3のフィラー17bを含有する。その結果、フィラー17bの一部がソルダーレジスト層15を構成する外層15bの表面に突出するため、アンダーフィル樹脂22との密着性を維持することができる。

50

## 【0079】

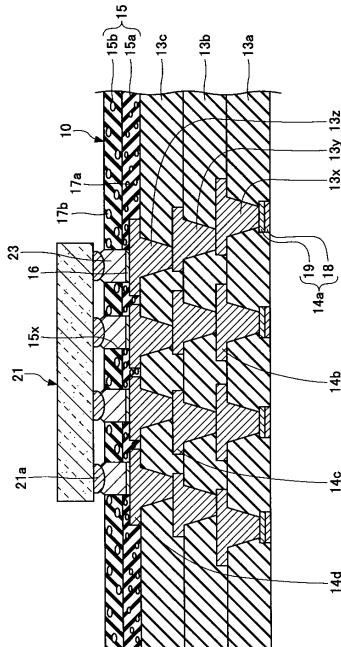

## 第3の実施の形態

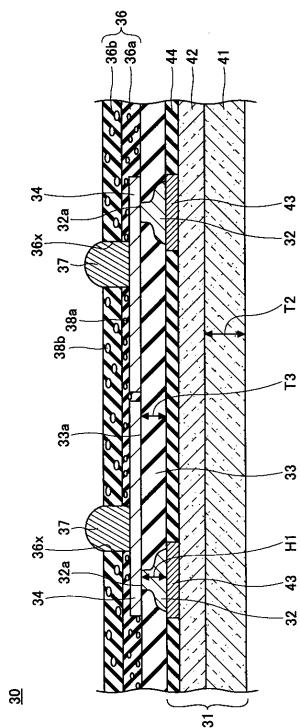

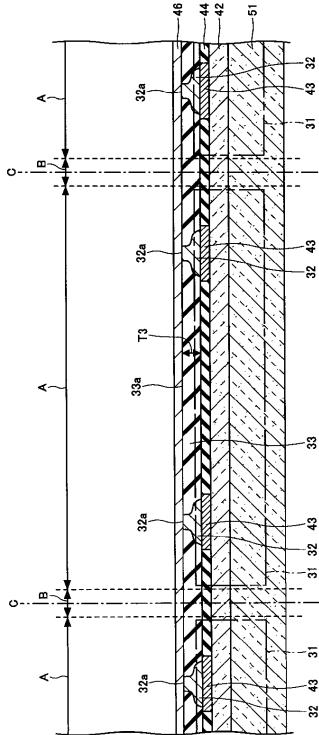

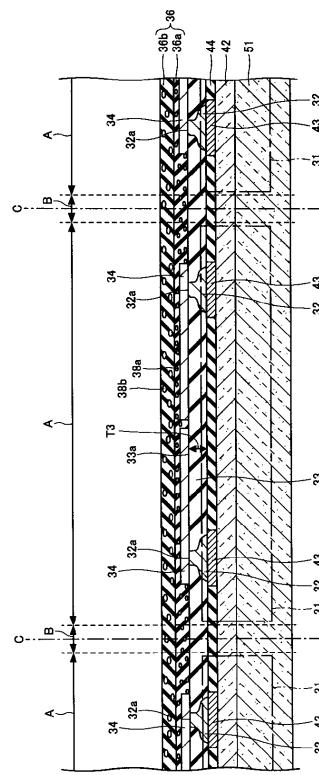

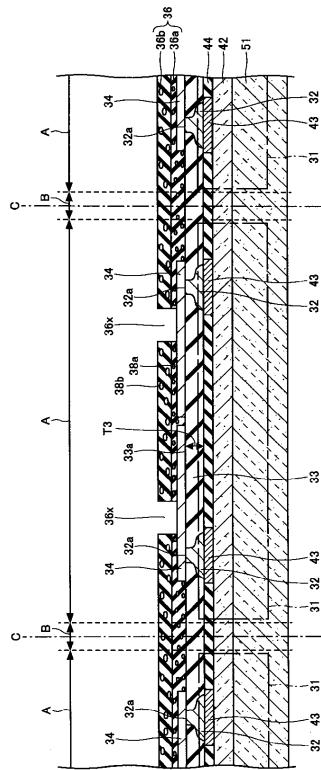

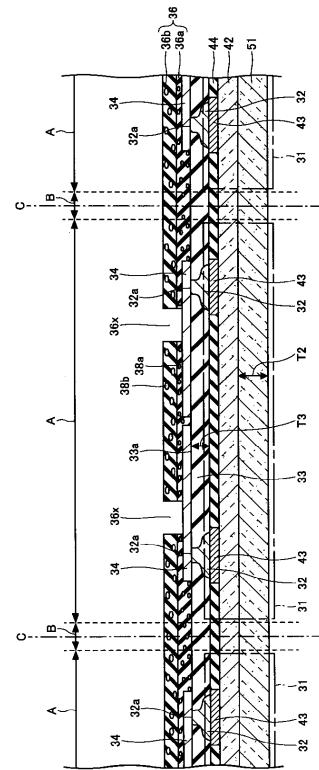

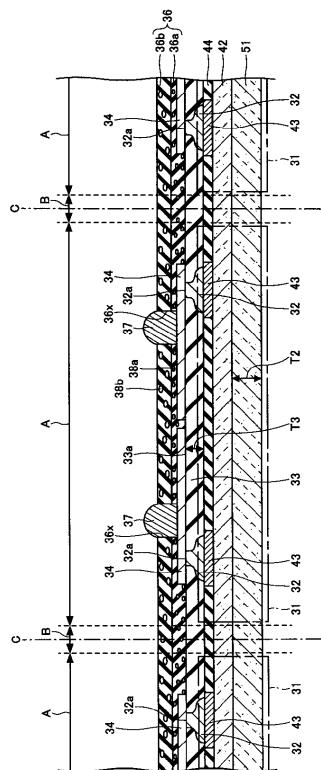

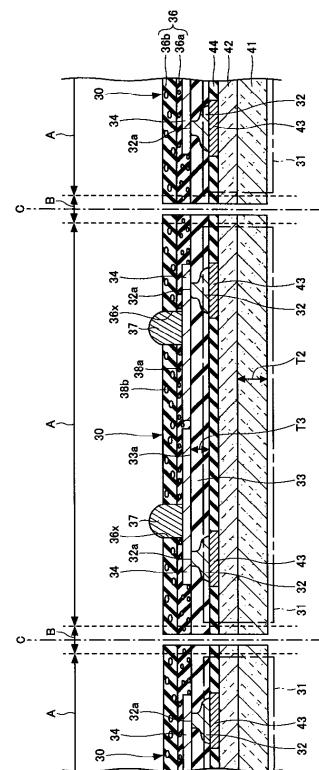

第3の実施の形態では、本発明を平面視した状態で半導体チップと略同じ大きさとされたチップサイズの半導体パッケージ（所謂チップサイズパッケージ：CSP）に適用する例を示す。図23は、本発明の第3の実施の形態に係る半導体パッケージを例示する断面図である。図23を参照するに、半導体パッケージ30は、半導体チップ31と、内部接続端子32と、絶縁層33と、配線34と、ソルダーレジスト層36と、外部接続端子37とを有する。

## 【0080】

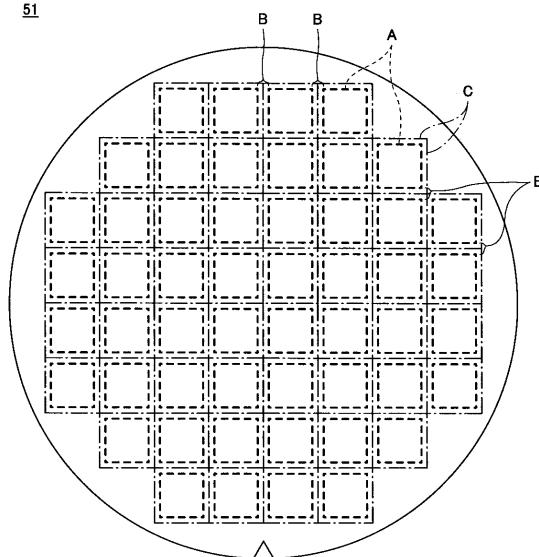

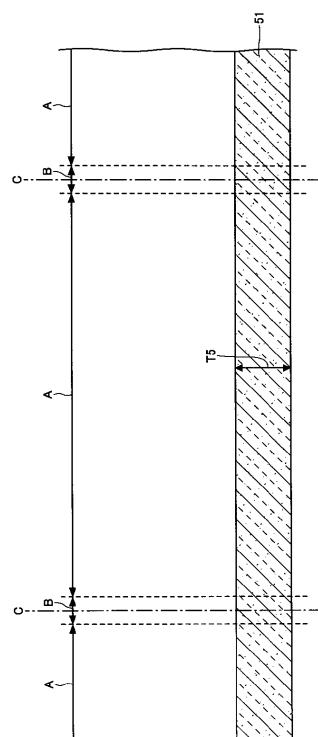

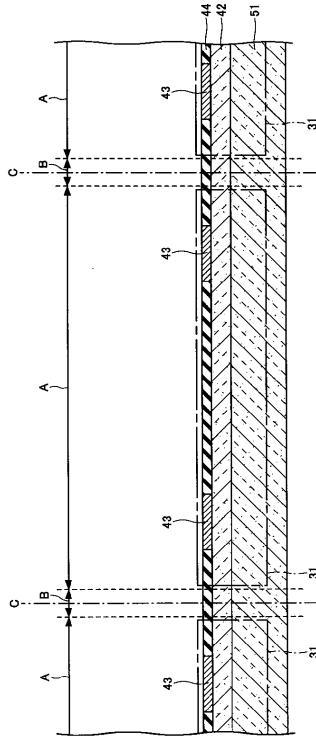

図24は、本発明の第3の実施の形態に係る半導体パッケージが形成される半導体基板の平面図である。図24において、51は半導体基板、Cはダイサーが半導体基板51を切断する位置（以下、「基板切断位置C」とする）を示しており、半導体基板51は、複数の半導体パッケージ形成領域Aと、複数の半導体パッケージ形成領域Aを分離する、基板切断位置Cを含むスクライプ領域Bとを有する。複数の半導体パッケージ形成領域Aは、半導体パッケージ30が形成される領域である。半導体基板51は、薄板化され、かつ基板切断位置Cにおいて切断されることにより、図23に示す半導体基板41となる基板である。

10

## 【0081】

図23において、半導体チップ31は、半導体基板41と、半導体集積回路42と、複数の電極パッド43と、保護膜44とを有する。半導体基板41は、半導体集積回路42を形成するための基板である。半導体基板41は、薄板化されている。半導体基板41の厚さT2は、例えば、 $100\text{ }\mu\text{m} \sim 300\text{ }\mu\text{m}$ とすることができる。半導体基板41は、例えば、薄板化されたSiウエハが個片化されたものである。

20

## 【0082】

半導体集積回路42は、半導体基板41の表面側に設けられている。半導体集積回路42は、半導体基板41に形成された拡散層（図示せず）、半導体基板41上に積層された絶縁層（図示せず）、及び積層された絶縁層に設けられたビア（図示せず）及び配線等（図示せず）から構成されている。

## 【0083】

電極パッド43は、半導体集積回路42上に複数設けられている。電極パッド43は、半導体集積回路42に設けられた配線（図示せず）と電気的に接続されている。電極パッド43の材料としては、例えば、Al等を用いることができる。

30

## 【0084】

保護膜44は、半導体集積回路42上に設けられている。保護膜44は、半導体集積回路42を保護するための膜であり、パッシベーション膜と呼ばれる場合もある。保護膜44としては、例えば、SiN膜、PSG膜等を用いることができる。又、SiN膜やPSG膜等からなる層に、更にポリイミド等からなる層を積層しても構わない。

## 【0085】

内部接続端子32は、電極パッド43上に設けられている。内部接続端子32は、半導体集積回路42と配線34とを電気的に接続するためのものである。内部接続端子32の高さH1は、例えば、 $10\text{ }\mu\text{m} \sim 60\text{ }\mu\text{m}$ とすることができる。内部接続端子32としては、例えば、Auバンプ、Auめっき膜、無電解めっき法により形成されたNi膜とそれを覆うAu膜から構成される金属膜等を用いることができる。Auバンプは、例えば、ワイヤボンディング装置を用いて、ボンディングワイヤにより形成することができる。又、めっき法により形成することもできる。

40

## 【0086】

絶縁層33は、半導体チップ31の回路形成面（正面）を保護すると共に、配線34を形成する際のベース材となるものである。絶縁層33は、内部接続端子32の上面32aを除く内部接続端子32及び半導体チップ31を覆うように設けられている。内部接続端子32の上面32aは、絶縁層33から露出している。絶縁層33の上面33aは、内部

50

接続端子 3 2 の上面 3 2 a と略面一とされている。

【0087】

絶縁層 3 3 としては、例えば、粘着性を有したシート状の絶縁樹脂（例えば、NCF（Non Conductive Film））や、ペースト状の絶縁樹脂（例えば、NCP（Non Conductive Paste））等を用いることができる。絶縁層 3 3 の厚さ T 3 は、例えば、 $10 \mu m \sim 60 \mu m$  とすることができます。

【0088】

配線 3 4 は、いわゆる再配線と呼ばれる場合があり、電極パッド 4 3 の位置と外部接続端子 3 7 の位置とを異ならせるため（ファンイン及び任意の位置への端子配置をするため）に設けられる。配線 3 4 の材料としては、例えば、Cu 等を用いることができる。 10

【0089】

配線 3 4 は、内部接続端子 3 2 の上面 3 2 a と接触するように、絶縁層 3 3 の上面 3 3 a に設けられている。配線 3 4 は、内部接続端子 3 2 を介して半導体集積回路 4 2 と電気的に接続されている。配線 3 4 の厚さは、例えば、 $12 \mu m$  とすることができます。

【0090】

配線 3 4 を覆うように、開口部 3 6 x を有するソルダーレジスト層 3 6 が形成されている。ソルダーレジスト層 3 6 は、フィラー 3 8 a を含有する内層 3 6 a 及びフィラー 3 8 b を含有する外層 3 6 b から構成されている。ソルダーレジスト層 3 6 の開口部 3 6 x 内の配線 3 4 上に、例えば、Ni めっき層と Au めっき層をこの順に積層した Ni / Au めっき層等を形成しても良い。 20

【0091】

外部接続端子 3 7 は、開口部 3 6 x 内に露出する配線 3 4 上に設けられている。外部接続端子 3 7 は、マザーボード等の実装基板（図示せず）に設けられたパッドと電気的に接続される端子である。外部接続端子 3 7 としては、例えば、はんだバンプ等を用いることができる。外部接続端子 3 7 の材料としては、例えば、Pb を含む合金、Sn と Cu の合金、Sn と Ag の合金等を用いることができる。

【0092】

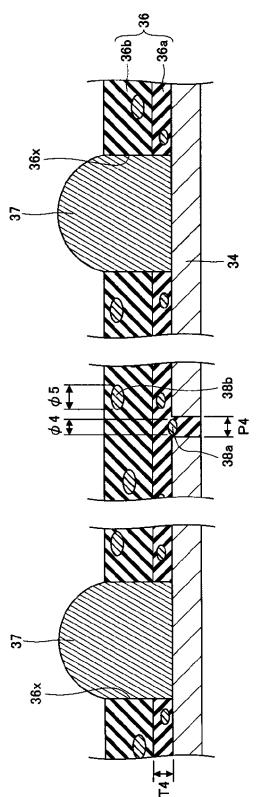

図 2 5 は、図 2 3 に示す半導体パッケージを部分的に例示する断面図である。図 2 5において、図 2 3 と同一部品については、同一符号を付し、その説明は省略する場合がある。4 はフィラー 3 8 a の粒径を示している。5 はフィラー 3 8 b の粒径を示している。P 4 は配線 3 4 の最短間隔を示している。T 4 は内層 3 6 a の上面から配線 3 4 の上面までの厚さを示している。 30

【0093】

ソルダーレジスト層 3 6 を構成する内層 3 6 a は、粒径 4 のフィラー 3 8 a を含有している。フィラー 3 8 a は、凝集して全体的に球形等をなす所謂二次凝集物を形成し、実質的に粒径が大きくなる場合があるが、本発明では、係る二次凝集物は予め除去されているため、ソルダーレジスト層 3 6 を構成する内層 3 6 a は、フィラー 3 8 a の二次凝集物を含有していない。厚さ T 4 は、フィラー 3 8 a の粒径 4 よりも厚くすることが好ましい。

【0094】

ソルダーレジスト層 3 6 を構成する外層 3 6 b は、粒径 5 のフィラー 3 8 b を含有している。フィラー 3 8 a 及び 3 8 b は、ソルダーレジスト層 3 6 の粘度の適正化、印刷性的向上、耐水性の向上、クラック発生の防止等を目的としてソルダーレジスト層 3 6 を構成する内層 3 6 a 及び外層 3 6 b に含有されている。 40

【0095】

フィラー 3 8 a の粒径 4 は、配線 3 4 の最短間隔 P 4 よりも小さい。フィラー 3 8 b の粒径 5 は、配線 3 4 の最短間隔 P 4 にかかわらず任意で良いが、ソルダーレジスト層 3 6 の粘度の適正化、印刷性的向上、耐水性の向上、クラック発生の防止等の目的を考慮すれば、従来の半導体パッケージ 2 0 0 を構成する配線基板 1 0 0 におけるフィラー 1 7 0 の粒径 1（図 2 参照）と同程度であることが好ましい。 50

## 【0096】

例えば、配線34の最短間隔P4が8μmであるとすれば、フィラー38aの粒径4は最短間隔P4=8μmよりも小さくする必要があり、例えば、6μm以下とすることができる。フィラー38bの粒径5は従来の半導体パッケージ200を構成する配線基板100におけるフィラー170の粒径1と同程度で、例えば、20μmとすることができる。

## 【0097】

なお、ソルダーレジスト層36を構成する内層36aは、フィラー38aを含有しなくても構わない。その場合には、ソルダーレジスト層36の粘度の適正化、印刷性の向上、耐水性の向上、クラック発生の防止等の目的は、フィラー38bを含有する外層36bにより達成することができる。10

## 【0098】

ソルダーレジスト層36を構成する内層36a及び外層36bとしては、例えば、エポキシ系樹脂やイミド系樹脂等を含む感光性樹脂組成物を用いることができる。更に揮発性の溶媒を含有させても構わない。フィラー38a及び38bとしては、例えば、酸化珪素、酸化チタン、酸化アルミニウム、窒化アルミニウム、炭化珪素、チタン酸カルシウム、ゼオライト等の無機化合物、又は、有機化合物等を用いることができる。

## 【0099】

フィラー38aとフィラー38bとは同一の材料で構成しても構わないし、異なる材料で構成しても構わない。内層36aに含有されるフィラー38aの量と、外層36bに含有されるフィラー38bの量とは略同一であっても構わないし、異なる量であっても構わない。ここでいう量とは、例えば、内層36a又は外層36bを構成する感光性樹脂組成物の重量に対するフィラー38a又はフィラー38bの重量(重量%)等である。20

## 【0100】

このように、ソルダーレジスト層36を内層36a及び外層36bから構成する。そして、内層36aは配線34の最短間隔P4よりも粒径4の小さいフィラー38aを含有し、外層36bは従来の半導体パッケージ200を構成する配線基板100の場合と同程度の粒径5のフィラー38bを含有する。

## 【0101】

その結果、ソルダーレジスト層36を構成する内層36aに外部から水分が浸入した状態で半導体パッケージ30に電圧が印加され、何らかの要因で配線34を構成するCu等の金属がイオン化して再結晶化する所謂マイグレーションが発生しても、マイグレーションの進行を防止することができる。それと同時に、ソルダーレジスト層36の粘度の適正化、印刷性の向上、耐水性の向上、クラック発生の防止等の目的も達成することができる。30

## 【0102】

より詳しく説明すれば、水分がフィラー38aと内層36aとの界面から内層36aに浸入しても、図25に示すようにフィラー38aは隣接する配線34に接することができないため、配線34を構成するCu等の金属のイオン化が加速されることはない。

## 【0103】

従って、イオン化した金属が、フィラー38aと内層36aとの界面に沿って内層36aを移動して再結晶化することもない。よって、隣接する配線34間の絶縁抵抗は正常な値を維持し、隣接する配線34が電気的に短絡することなく、マイグレーションの進行を防止することができる。40

## 【0104】

図26～図38は、本発明の第3の実施の形態に係る半導体パッケージの製造工程を例示する図である。図26～図38において、図23に示す半導体パッケージ30と同一構成部分には同一符号を付し、その説明を省略する場合がある。図26～図38において、Cはダイシングブレードが半導体基板51を切断する位置(以下、「基板切断位置C」とする)、Aは複数の半導体パッケージ形成領域(以下、「半導体パッケージ形成領域A」50

とする)、Bは複数の半導体パッケージ形成領域Aを分離する、基板切断位置Cを含むスクライプ領域(以下、「スクライプ領域B」とする)を示している。

#### 【0105】

始めに、図26に示す工程では、複数の半導体パッケージ形成領域Aと、複数の半導体パッケージ形成領域Aを分離する、基板切断位置Cを含むスクライプ領域Bとを有する半導体基板51を準備する(図24参照)。半導体基板51は、薄板化され、かつ基板切断位置Cにおいて切断されることにより、先に説明した半導体基板41(図23参照)となるものである。半導体基板51としては、例えば、Siウエハ等を用いることができる。半導体基板51の厚さT5は、例えば、500μm~775μmとすることができます。

#### 【0106】

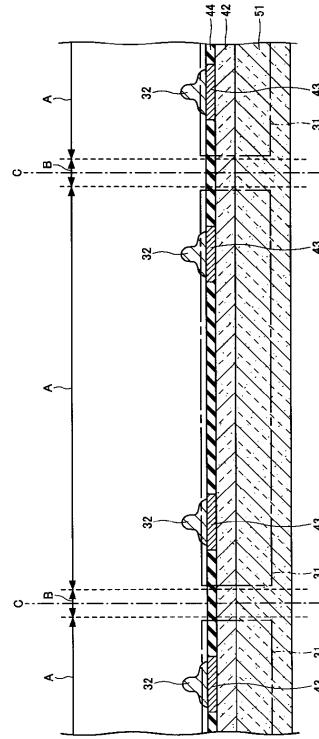

次いで、図27に示す工程では、半導体パッケージ形成領域Aに対応する半導体基板51の表面側に、周知の手法により、半導体集積回路42、電極パッド43、及び保護膜44を有する半導体チップ31を形成する。電極パッド43の材料としては、例えば、Al等を用いることができる。保護膜44としては、例えば、SiN膜やPSG膜等を用いることができる。又、SiN膜やPSG膜等からなる層に、更にポリイミド等からなる層を積層しても構わない。

#### 【0107】

次いで、図28に示す工程では、複数の半導体パッケージ形成領域Aに設けられた複数の電極パッド43上にそれぞれ内部接続端子32を形成する。内部接続端子32としては、例えば、Auバンプ、Auめっき膜、無電解めっき法により形成されたNi膜とNi膜上に積層されるAu膜から構成される金属膜等を用いることができる。Auバンプは、例えば、ワイヤボンディング装置を用いて、ボンディングワイヤにより形成することができる。又、めっき法により形成することもできる。なお、図28に示す工程で形成された複数の内部接続端子32には、高さばらつきが存在する。

#### 【0108】

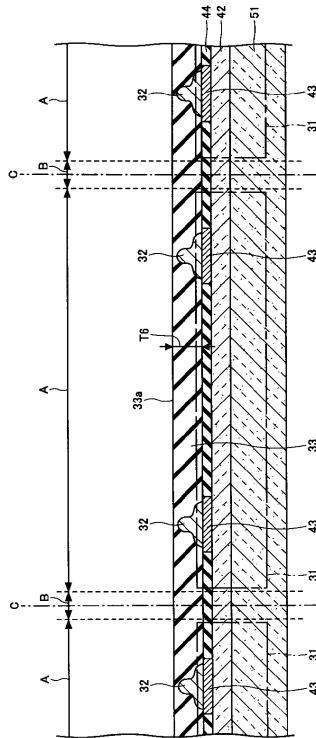

次いで、図29に示す工程では、内部接続端子32が設けられた側の複数の半導体チップ31及び内部接続端子32を覆うように絶縁層33を形成する。絶縁層33としては、例えば、粘着性を有したシート状の絶縁樹脂(例えば、NCF(Non Conductive Film))や、ペースト状の絶縁樹脂(例えば、NCP(Non Conductive Paste))等を用いることができる。絶縁層33の厚さT6は、例えば、20μm~100μmとすることができます。

#### 【0109】

絶縁層33として粘着性を有するシート状の絶縁樹脂を用いた場合は、図28に示す構造体の上面側にシート状の絶縁樹脂を貼り付けることで絶縁層33を形成する。また、絶縁層33としてペースト状の絶縁樹脂を用いた場合は、図28に示す構造体の上面側に印刷法によりペースト状の絶縁樹脂を形成し、その後、プリベークして絶縁樹脂を半硬化させる。この半硬化した絶縁樹脂は、接着性を有する。

#### 【0110】

次いで、図30に示す工程では、図29に示す構造体を加熱した状態で、絶縁層33を絶縁層33の上面33a側から押圧する(図30の矢印参照)。これにより、図30に示す構造体の上面(具体的には、絶縁層33の上面33a及び内部接続端子32の上面32a)は、平坦な面になる。

#### 【0111】

又、図30に示す構造体を加熱することにより、絶縁層33は硬化する。押圧後の絶縁層33の厚さT3は、例えば、10μm~60μmとすることができます。内部接続端子32の上面32aに絶縁層33を構成する材料の一部が付着している場合には、エッチング等を施し、内部接続端子32の上面32aを絶縁層33から完全に露出させる。必要に応じて、絶縁層33の上面33aを粗面化しても良い。

#### 【0112】

次いで、図31に示す工程では、絶縁層33の上面33aに金属層46を形成する。金

10

20

30

40

50

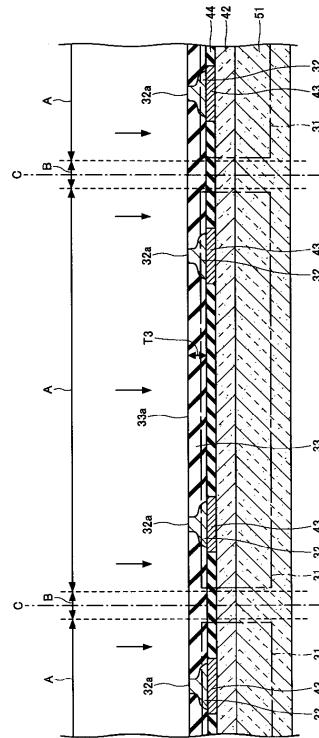

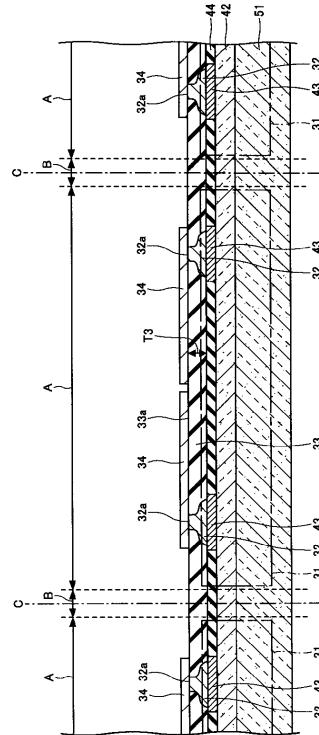

属層 4 6 は、後述する図 3 2 に示す工程において、エッチングされて配線パターン 3 4 となるものである。次いで、図 3 2 示す工程では、金属層 4 6 をエッチングによりパターニングして、配線 3 4 を形成し、その後、配線パターン 3 4 の粗化処理を行う。

#### 【 0 1 1 3 】

具体的には、金属層 4 6 上にパターニングされたレジスト膜を形成し、次いで、このレジスト膜をマスクとして、金属層 4 6 をエッチングして配線パターン 3 4 を形成する。配線パターン 3 4 の粗化処理は、黒化処理又は粗化エッチング処理のいずれかの方法により行うことができる。上記粗化処理は、配線パターン 3 4 の上面及び側面に形成されるソルダーレジスト層 3 6 と配線パターン 3 4 との密着性を向上させるためのものである。

#### 【 0 1 1 4 】

次いで、図 3 3 に示す工程では、配線 3 4 を被覆するように絶縁層 3 3 上に、粒径が 4 であるフィラー 3 8 a を含有するソルダーレジストを塗布しソルダーレジスト層 3 6 を構成する内層 3 6 a を形成する。内層 3 6 a としては、例えば、エポキシ系樹脂やイミド系樹脂等を含む感光性樹脂組成物を用いることができる。更に揮発性の溶媒を含有させて構わない。フィラー 3 8 a としては、例えば、酸化珪素、酸化チタン、酸化アルミニウム、窒化アルミニウム、炭化珪素、チタン酸カルシウム、ゼオライト等の無機化合物、又は、有機化合物等を用いることができる。

#### 【 0 1 1 5 】

次いで、図 3 4 に示す工程では、内層 3 6 a 上に、粒径が 5 であるフィラー 3 8 b を含有するソルダーレジストを塗布しソルダーレジスト層 3 6 を構成する外層 3 6 b を形成する。外層 3 6 b としては、例えば、エポキシ系樹脂やイミド系樹脂等を含む感光性樹脂組成物を用いることができる。更に揮発性の溶媒を含有させて構わない。

#### 【 0 1 1 6 】

フィラー 3 8 b としては、例えば、酸化珪素、酸化チタン、酸化アルミニウム、窒化アルミニウム、炭化珪素、チタン酸カルシウム、ゼオライト等の無機化合物、又は、有機化合物等を用いることができる。これで、内層 3 6 a 及び外層 3 6 b から構成されるソルダーレジスト層 3 6 が形成される。

#### 【 0 1 1 7 】

次いで、図 3 5 に示す工程では、ソルダーレジスト層 3 6 を露光、現像することで開口部 3 6 x を形成する。これにより、配線 3 4 は、ソルダーレジスト層 3 6 の開口部 3 6 x 内に露出する。ソルダーレジスト層 3 6 の開口部 3 6 x 内の配線 3 4 上に、例えば、Ni めっき層と Au めっき層をこの順に積層した Ni / Au めっき層等を形成しても良い。

#### 【 0 1 1 8 】

次いで、図 3 6 に示す工程では、半導体基板 5 1 の裏面側から半導体基板 5 1 を研磨又は研削して、半導体基板 5 1 を薄板化する。半導体基板 5 1 の薄板化には、例えば、バッカサイドグラインダー等を用いることができる。薄板化後の半導体基板 5 1 の厚さ T 2 は、例えば、 $100 \mu m \sim 300 \mu m$  とすることができる。なお、図 3 6 に示す工程は削除される場合もある。

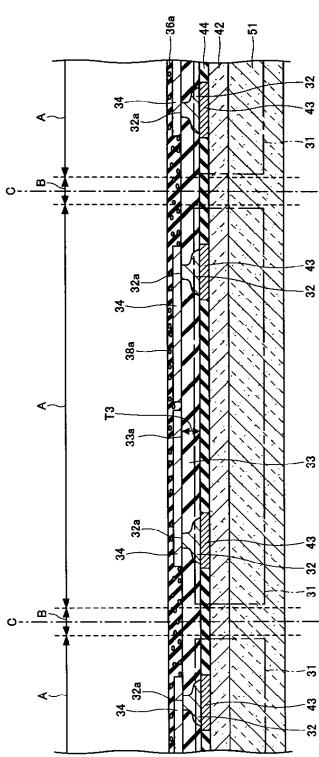

#### 【 0 1 1 9 】

次いで、図 3 7 に示す工程では、開口部 3 6 x 内に露出する配線 3 4 上に外部接続端子 3 7 を形成する。外部接続端子 3 7 は、マザーボード等の実装基板（図示せず）に設けられたパッドと電気的に接続される端子である。外部接続端子 3 7 としては、例えば、はんだバンプ等を用いることができる。外部接続端子 3 7 の材料としては、例えば、Pb を含む合金、Sn と Cu の合金、Sn と Ag の合金等を用いることができる。

#### 【 0 1 2 0 】

これにより、複数の半導体パッケージ形成領域 A に半導体パッケージ 3 0 に相当する構造体が形成される。なお、図 3 6 に示す工程と図 3 7 に示す工程とは、順番を入れ替えて構わない。次いで、図 3 8 に示す工程では、図 3 7 に示す構造体のスクライブ領域 B に対応する半導体基板 5 1 を基板切断位置 C に沿ってダイシング等により切断することで、複数の半導体パッケージ 3 0 が製造される。

10

20

30

40

50

**【 0 1 2 1 】**

本発明の第3の実施の形態に係る半導体パッケージ30によれば、ソルダーレジスト層36を内層36a及び外層36bから構成する。そして、内層36aは配線34の最短間隔P4よりも粒径4の小さいフィラー38aを含有する。その結果、ソルダーレジスト層36を構成する内層36aに外部から水分が浸入した状態で半導体パッケージ30に電圧が印加され、何らかの要因で配線34を構成するCu等の金属がイオン化して再結晶化する所謂マイグレーションが発生しても、マイグレーションの進行を防止することができる。

**【 0 1 2 2 】**

又、外層36bは従来の半導体パッケージ200を構成する配線基板100の場合と同程度の粒径5のフィラー38bを含有する。その結果、ソルダーレジスト層36の粘度の適正化、印刷性の向上、耐水性の向上、クラック発生の防止等の目的も達成することができる。10

**【 0 1 2 3 】**

以上、本発明の好ましい実施の形態について詳説したが、本発明は、上述した実施の形態に制限されることではなく、本発明の範囲を逸脱することなく、上述した実施の形態に種々の変形及び置換を加えることができる。

**【 0 1 2 4 】**

例えは、第1の実施の形態では、本発明をビルドアップ工法により製造された支持体を有さない多層配線基板に適用する例を、第2の実施の形態では、本発明をビルドアップ工法により製造された支持体を有さない多層配線基板を有する半導体パッケージに適用する例を、第3の実施の形態では、本発明を平面視した状態で半導体チップと略同じ大きさとされたチップサイズの半導体パッケージ（所謂チップサイズパッケージ：CSP）に適用する例を示した。しかし、本発明は、これらに限定されることなく、様々な配線基板及び半導体パッケージに適用することができる。例えは、支持体を有する多層配線基板、片面のみに配線層が形成された片面（一層）配線基板、基板の両面に配線層が形成された両面（二層）配線基板、スルーピアで各配線層を接続する貫通多層配線基板、IVH（Intersitial Via Hole）で特定の配線層を接続するIVH多層配線基板等の様々な配線基板及び前記配線基板を有する半導体パッケージに適用することができる。20

**【 0 1 2 5 】**

又、第1の実施の形態～第3の実施の形態では、ソルダーレジスト層を2層構成とする例を示したが、ソルダーレジスト層は3層以上から構成しても構わない。その場合、絶縁層側が最内層である。30

**【 0 1 2 6 】**

又、第1の実施の形態においては、配線をセミアディティブ法で形成する例を示したが、配線は、セミアディティブ法の他にサブトラクティブ法等の各種の方法を用いて形成することができる。

**【 図面の簡単な説明 】****【 0 1 2 7 】**

【図1】従来の半導体パッケージを部分的に例示する断面図である。

40

【図2】図1に示す半導体パッケージを部分的に例示する断面図である。

【図3】図2に示す配線のピッチが狭くなった様子を例示する断面図である。

【図4】本発明の第1の実施の形態に係るビルドアップ配線層を有する配線基板を例示する断面図である。

【図5】図4に示す配線基板を部分的に例示する断面図である。

【図6】本発明の第1の実施の形態に係る配線基板の製造工程を例示する図（その1）である。

【図7】本発明の第1の実施の形態に係る配線基板の製造工程を例示する図（その2）である。

【図8】本発明の第1の実施の形態に係る配線基板の製造工程を例示する図（その3）で50

ある。

【図 9】本発明の第 1 の実施の形態に係る配線基板の製造工程を例示する図（その 4）である。

【図 10】本発明の第 1 の実施の形態に係る配線基板の製造工程を例示する図（その 5）である。

【図 11】本発明の第 1 の実施の形態に係る配線基板の製造工程を例示する図（その 6）である。

【図 12】本発明の第 1 の実施の形態に係る配線基板の製造工程を例示する図（その 7）である。

【図 13】本発明の第 1 の実施の形態に係る配線基板の製造工程を例示する図（その 8）10である。

【図 14】本発明の第 1 の実施の形態に係る配線基板の製造工程を例示する図（その 9）である。

【図 15】本発明の第 1 の実施の形態に係る配線基板の製造工程を例示する図（その 10）である。

【図 16】本発明の第 1 の実施の形態に係る配線基板の製造工程を例示する図（その 11）である。

【図 17】本発明の第 1 の実施の形態に係る配線基板の製造工程を例示する図（その 12）である。

【図 18】本発明の第 1 の実施の形態に係る配線基板の製造工程を例示する図（その 13）20である。

【図 19】H A S T 試験の結果を例示する図である。

【図 20】H A S T 試験後の評価用サンプルの外観を例示する図である。

【図 21】本発明の第 2 の実施の形態に係る半導体パッケージを例示する断面図である。

【図 22】本発明の第 2 の実施の形態に係る半導体パッケージの製造工程を例示する図である。

【図 23】本発明の第 3 の実施の形態に係る半導体パッケージを例示する断面図である。

【図 24】本発明の第 3 の実施の形態に係る半導体パッケージが形成される半導体基板の平面図である。

【図 25】図 23 に示す半導体パッケージを部分的に例示する断面図である。30

【図 26】本発明の第 3 の実施の形態に係る半導体パッケージの製造工程を例示する図（その 1）である。

【図 27】本発明の第 3 の実施の形態に係る半導体パッケージの製造工程を例示する図（その 2）である。

【図 28】本発明の第 3 の実施の形態に係る半導体パッケージの製造工程を例示する図（その 3）である。

【図 29】本発明の第 3 の実施の形態に係る半導体パッケージの製造工程を例示する図（その 4）である。

【図 30】本発明の第 3 の実施の形態に係る半導体パッケージの製造工程を例示する図（その 5）である。40

【図 31】本発明の第 3 の実施の形態に係る半導体パッケージの製造工程を例示する図（その 6）である。

【図 32】本発明の第 3 の実施の形態に係る半導体パッケージの製造工程を例示する図（その 7）である。

【図 33】本発明の第 3 の実施の形態に係る半導体パッケージの製造工程を例示する図（その 8）である。

【図 34】本発明の第 3 の実施の形態に係る半導体パッケージの製造工程を例示する図（その 9）である。

【図 35】本発明の第 3 の実施の形態に係る半導体パッケージの製造工程を例示する図（その 10）である。50

【図36】本発明の第3の実施の形態に係る半導体パッケージの製造工程を例示する図(その11)である。

【図37】本発明の第3の実施の形態に係る半導体パッケージの製造工程を例示する図(その12)である。

【図38】本発明の第3の実施の形態に係る半導体パッケージの製造工程を例示する図(その13)である。

【符号の説明】

【0128】

|                                                    |          |

|----------------------------------------------------|----------|

| 10                                                 | 1 0 配線基板 |

| 1 1 支持体                                            |          |

| 1 2 レジスト膜                                          |          |

| 1 2 x , 1 5 x , 3 6 x 開口部                          |          |

| 1 3 a 第1絶縁層                                        |          |

| 1 3 b 第2絶縁層                                        |          |

| 1 3 c 第3絶縁層                                        |          |

| 1 3 x 第1ビアホール                                      |          |

| 1 3 y 第2ビアホール                                      |          |

| 1 3 z 第3ビアホール                                      |          |

| 1 4 a , 1 4 b , 1 4 c , 1 4 d , 1 4 e , 3 4 配線     |          |

| 1 5 , 3 6 ソルダーレジスト層                                | 20       |

| 1 5 a , 3 6 a 内層                                   |          |

| 1 5 b , 3 6 b 外層                                   |          |

| 1 6 , 4 6 金属層                                      |          |

| 1 7 a , 1 7 b , 1 7 c , 1 7 d , 3 8 a , 3 8 b フィラー |          |

| 1 8 表面めっき層                                         |          |

| 1 9 パッド本体                                          |          |

| 2 0 , 3 0 半導体パッケージ                                 |          |

| 2 1 , 3 1 半導体チップ                                   |          |

| 2 1 a ポール状端子                                       |          |

| 2 2 アンダーフィル樹脂                                      | 30       |

| 2 3 プレソルダ                                          |          |

| 3 2 内部接続端子                                         |          |

| 3 2 a , 3 3 a 上面                                   |          |

| 3 3 絶縁層                                            |          |

| 3 7 外部接続端子                                         |          |

| 4 1 , 5 1 半導体基板                                    |          |

| 4 2 半導体集積回路                                        |          |

| 4 3 電極パッド                                          |          |

| 4 4 保護膜                                            |          |

| A 半導体パッケージ形成領域                                     | 40       |

| B スクライブ領域                                          |          |

| C 基板切断位置                                           |          |

| H 1 高さ                                             |          |

| P 3 , P 5 最短間隔                                     |          |

| T 1 , T 2 , T 3 , T 4 , T 5 , T 6 厚さ               |          |

| 2 , 3 , 4 , 5 粒径                                   |          |

【図1】

従来の半導体パッケージを部分的に例示する断面図

【図2】

図1に示す半導体パッケージを部分的に例示する断面図

【図3】

図2に示す配線のピッチが狭くなった様子を例示する断面図

【図4】

本発明の第1の実施の形態に係る

ビルドアップ配線層を有する配線基板を例示する断面図

【図5】

図4に示す配線基板を部分的に例示する断面図

【図6】

本発明の第1の実施の形態に係る

配線基板の製造工程を例示する図(その1)

【図7】

本発明の第1の実施の形態に係る

配線基板の製造工程を例示する図(その2)

【図8】

本発明の第1の実施の形態に係る

配線基板の製造工程を例示する図(その3)

【図9】

本発明の第1の実施の形態に係る

配線基板の製造工程を例示する図(その4)

【図 10】

本発明の第1の実施の形態に係る

配線基板の製造工程を例示する図(その5)

【図 11】

本発明の第1の実施の形態に係る

配線基板の製造工程を例示する図(その6)

【図 12】

本発明の第1の実施の形態に係る

配線基板の製造工程を例示する図(その7)

【図 13】

本発明の第1の実施の形態に係る

配線基板の製造工程を例示する図(その8)

【図14】

本発明の第1の実施の形態に係る

配線基板の製造工程を例示する図(その9)

【図15】

本発明の第1の実施の形態に係る

配線基板の製造工程を例示する図(その10)

【図16】

本発明の第1の実施の形態に係る

配線基板の製造工程を例示する図(その11)

【図17】

本発明の第1の実施の形態に係る

配線基板の製造工程を例示する図(その12)

【図18】

本発明の第1の実施の形態に係る

配線基板の製造工程を例示する図(その13)

【図19】

HAST試験の結果を例示する図

【図21】

本発明の第2の実施の形態に係る半導体パッケージを例示する断面図

【図22】

本発明の第2の実施の形態に係る半導体パッケージの製造工程を例示する図

【図23】

本発明の第3の実施の形態に係る半導体パッケージを例示する断面図

【図24】

本発明の第3の実施の形態に係る

半導体パッケージが形成される半導体基板の平面図

【図25】

図23に示す半導体パッケージを部分的に例示する断面図

【図26】

本発明の第3の実施の形態に係る

半導体パッケージの製造工程を例示する図(その1)

【図 27】

本発明の第3の実施の形態に係る

半導体パッケージの製造工程を例示する図(その2)

【図 28】

本発明の第3の実施の形態に係る

半導体パッケージの製造工程を例示する図(その3)

【図 29】

本発明の第3の実施の形態に係る

半導体パッケージの製造工程を例示する図(その4)

【図 30】

本発明の第3の実施の形態に係る

半導体パッケージの製造工程を例示する図(その5)

【図3-1】

本発明の第3の実施の形態に係る

半導体パッケージの製造工程を例示する図(その6)

【図32】

### 本発明の第3の実施の形態に係る 半導体パッケージの製造工程を例示する図(その7)

【図33】

### 本発明の第3の実施の形態に係る 半導体パッケージの製造工程を例示する図(その8)

【図3-4】

本発明の第3の実施の形態に係る

半導体パッケージの製造工程を例示する図(その9)

【図35】

本発明の第3の実施の形態に係る

半導体パッケージの製造工程を例示する図(その10)

【 図 3 6 】

本発明の第3の実施の形態に係る

半導体パッケージの製造工程を例示する図(その11)

【図37】

本発明の第3の実施の形態に係る

半導体パッケージの製造工程を例示する図(その12)

【図38】

本発明の第3の実施の形態に係る

半導体パッケージの製造工程を例示する図(その13)

【図20】

HAST試験後の評価用サンプルの外観を例示する図

---

フロントページの続き

(56)参考文献 特開2000-031628(JP,A)

特開2008-084920(JP,A)

米国特許出願公開第2008/0176035(US,A1)

特開2002-043723(JP,A)

特開2000-294921(JP,A)

特開2007-180105(JP,A)

(58)調査した分野(Int.Cl., DB名)

|        |         |

|--------|---------|

| H 05 K | 3 / 28  |

| H 01 L | 23 / 14 |

| H 01 L | 23 / 12 |

| H 05 K | 1 / 05  |