(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6210801号

(P6210801)

(45) 発行日 平成29年10月11日(2017.10.11)

(24) 登録日 平成29年9月22日(2017.9.22)

(51) Int.Cl.

F 1

|         |       |           |         |       |         |

|---------|-------|-----------|---------|-------|---------|

| B 4 1 J | 2/447 | (2006.01) | B 4 1 J | 2/447 | 1 O 1 D |

| B 4 1 J | 2/45  | (2006.01) | B 4 1 J | 2/45  |         |

| G 0 3 G | 15/04 | (2006.01) | G 0 3 G | 15/04 | 1 1 1   |

| H 0 4 N | 1/036 | (2006.01) | H 0 4 N | 1/036 | A       |

| H 0 1 L | 33/00 | (2010.01) | H 0 1 L | 33/00 | L       |

請求項の数 11 (全 9 頁) 最終頁に続く

(21) 出願番号

特願2013-181015 (P2013-181015)

(22) 出願日

平成25年9月2日(2013.9.2)

(65) 公開番号

特開2015-47780 (P2015-47780A)

(43) 公開日

平成27年3月16日(2015.3.16)

審査請求日

平成28年7月4日(2016.7.4)

(73) 特許権者 000001007

キヤノン株式会社

東京都大田区下丸子3丁目30番2号

(74) 代理人 100096828

弁理士 渡辺 敏介

(74) 代理人 100110870

弁理士 山口 芳広

(72) 発明者 池田 宏治

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

(72) 発明者 山下 孝教

東京都大田区下丸子3丁目30番2号 キ

ヤノン株式会社内

最終頁に続く

(54) 【発明の名称】露光光源及び画像形成装置

## (57) 【特許請求の範囲】

## 【請求項 1】

一列に配列された複数の画素回路と、走査信号を出力する走査回路と、前記走査信号を前記複数の画素回路に供給する走査線と、を含む回路部と、前記複数の画素回路に接続された複数の発光素子と、引き出し線を介して前記複数の画素回路にデータ信号を供給する複数のデータ線と、を有し、

前記複数のデータ線を含むデータ線群と、前記複数の発光素子を含む発光素子群と、前記回路部とが、前記複数の画素回路の配列方向と垂直な方向に沿って、この順で配置され、

前記回路部は、前記画素回路および前記発光素子に電源電圧を供給する複数の電源配線を更に有し、前記複数の電源配線のうち第一の電圧が印加される第一電源配線は、前記画素回路の前記走査回路側に配置されていることを特徴とする露光光源。

## 【請求項 2】

前記複数の画素回路と前記走査回路が、前記発光素子群側から、前記画素回路の配列方向と垂直な方向に沿って、この順で配置されていることを特徴とする請求項 1 に記載の露光光源。

## 【請求項 3】

前記複数のデータ線は、前記画素回路の配列方向に延伸し、前記引き出し線は、前記画素回路の配列方向と垂直な方向に延伸することを特徴とする請求項 1 または 2 に記載の露光光源。

**【請求項 4】**

前記データ線群の、前記画素回路の配列方向と垂直な方向の長さは、前記画素回路の前記長さ、前記走査回路の前記長さ、前記第一電源配線の前記長さよりも長いことを特徴とする請求項 1 乃至 3 のいずれか一項に記載の露光光源。

**【請求項 5】**

前記発光素子群は、千鳥配列されていることを特徴とする請求項 1 乃至 4 のいずれか一項に記載の露光光源。

**【請求項 6】**

前記画素回路は、前記発光素子に駆動電流を供給する駆動トランジスタと、前記データ信号を前記駆動トランジスタに供給する選択トランジスタを備え、前記駆動トランジスタは前記第一電源配線と接続し、前記選択トランジスタのゲート電極は前記走査線に接続することを特徴とする請求項 1 乃至 5 のいずれか一項に記載の露光光源。 10

**【請求項 7】**

前記複数の画素回路は、互いに隣接する複数の画素回路からなる複数のブロックに分割され、前記走査回路は、前記複数の画素回路を前記ブロック単位で走査することを特徴とする請求項 1 乃至 6 のいずれか一項に記載の露光光源。

**【請求項 8】**

前記走査回路に接続された保護素子と、前記画素回路の配列方向に沿って配置された複数の端子部を有し、

前記複数の端子部は、前記複数のデータ線に接続された第 1 の端子部群と、前記走査回路に接続された第 2 の端子部群とを有し、前記第 1 の端子部群は、前記第 2 の端子部群の前記複数の画素回路側に配置されており、 20

前記第 2 の端子部群から、前記走査回路と前記第 2 の端子部群とを前記保護素子を介して接続する信号線が、前記第 1 の端子部群から前記データ線が延伸する方向と反対の方向に延伸し、

前記保護素子は、前記第 1 の端子部群の、前記第 1 の端子部群から前記データ線が延伸する方向と反対側の領域に配置されていることを特徴とする請求項 1 乃至 7 のいずれか一項に記載の露光光源。

**【請求項 9】**

前記第 1 の端子部群及び第 2 の端子部群から、ショートリングを構成する配線が、前記第 1 の端子部群から前記データ線が延伸する方向に延伸していることを特徴とする請求項 8 に記載の露光光源。 30

**【請求項 10】**

請求項 1 乃至 9 のいずれか一項に記載の露光光源を備えることを特徴とする露光ヘッド。

。

**【請求項 11】**

請求項 10 に記載の露光ヘッドを備えることを特徴とする画像形成装置。

**【発明の詳細な説明】****【技術分野】****【0 0 0 1】**

本発明は、露光光源及び画像形成装置に関するものである。 40

**【背景技術】****【0 0 0 2】**

有機エレクトロルミネセンス(EL)素子等の発光素子を用い、例えばプリンタ等に搭載される露光光源は、発光素子を有する画素を基板上に複数個、直線状に配置して構成される。そのため、露光光源は、一般的に、画素の配列方向に長く、アスペクト比が高い形状となる。従って、データ線を露光光源の長手方向に沿って配線する場合、データ線が長くなり寄生容量が大きくなりやすいが、高速駆動を行うためにはこの寄生容量を小さくする必要がある。特許文献 1 には、データ線の寄生容量を小さくする露光光源の構成が開示されている。 50

**【先行技術文献】****【特許文献】****【0003】****【特許文献1】特開2006-123493号公報****【発明の概要】****【発明が解決しようとする課題】****【0004】**

しかし、特許文献1の構成では、走査線とデータ線が交差し、この交差部で寄生容量が形成されるため、駆動の更なる高速化が難しいという問題がある。

**【0005】**

10

本発明は、上記従来の問題点に鑑みてなされたもので、発光素子を駆動するための回路の寄生容量を低減した露光源を提供することを目的とする。

**【課題を解決するための手段】****【0006】**

上記課題を解決するために、本発明は、一列に配列された複数の画素回路と、走査信号を出力する走査回路と、前記走査信号を前記複数の画素回路に供給する走査線と、を含む回路部と、前記複数の画素回路に接続された複数の発光素子と、引き出し線を介して前記複数の画素回路にデータ信号を供給する複数のデータ線と、を有し、

前記複数のデータ線を含むデータ線群と、前記複数の発光素子を含む発光素子群と、前記回路部とが、前記複数の画素回路の配列方向と垂直な方向に沿って、この順で配置され

20

前記回路部は、前記画素回路および前記発光素子に電源電圧を供給する複数の電源配線を更に有し、前記複数の電源配線のうち第一の電圧が印加される第一電源配線は、前記画素回路の前記走査回路側に配置されていることを特徴とする露光源を提供するものである。

**【発明の効果】****【0007】**

本発明によれば、データ線の寄生容量を非常に小さくすることができる。従って、露光ヘッドを高速駆動させることができる。

**【図面の簡単な説明】**

30

**【0008】****【図1】本発明の露光源の構成の一例を示す概略図である。****【図2】画素の回路を示す一例図である。****【図3】本発明の露光源の構成の他の例を示す概略図である。****【図4】本発明の露光源を有する画像形成装置の概略図である。****【発明を実施するための形態】****【0009】**

以下、図面を用いて本発明を詳細に説明する。

**【0010】****露光源**

40

**[第一実施形態]**

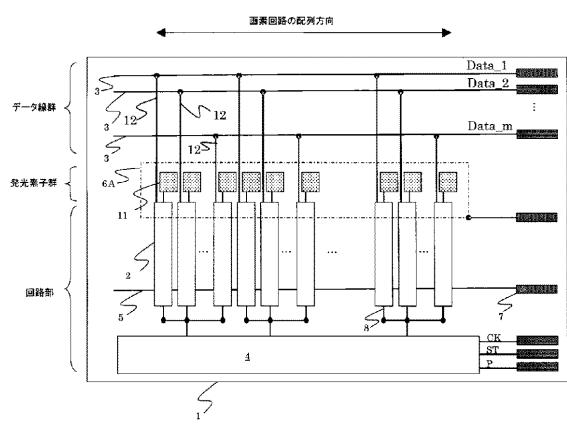

図1を用いて、感光ドラムに光照射して潜像を露光するための、本発明にかかる露光源の例について説明する。図1は本実施形態にかかる露光源の構成を示す概略図である。

**【0011】**

本発明の露光源は、基板1の上に、画素回路2が一方向に並ぶように複数形成されている。基板1として、例えば、ガラス基板やシリコン基板等を用いることができる。画素回路2のそれぞれには発光素子11が接続され、画素回路2と発光素子11で画素を構成している。発光素子11は、画素回路2の配列方向に一列に並ぶように配列されているが、発光素子11は必ずしも一列に配列されている必要はなく、例えば、千鳥配置等させていてもよい。発光素子11としては、例えば、発光ダイオード(LED)、無機EL素子

50

、有機 E L 素子等を用いることができる。

**【 0 0 1 2 】**

画素回路 2 は、画素回路 2 の配列方向の長さよりも、画素回路 1 0 の配列方向と垂直な方向の長さが長い。図 1 で示す画素回路 2 は略長方形形状となっている。画素回路 2 は、隣接する複数の画素回路からなる複数のブロックに分割されている。具体的には、画素回路 2 は、互いに隣接する  $m$  個 ( $m$  は 2 以上の整数) の画素で 1 ブロックとしてまとめられており、全体で  $N$  ブロック ( $N$  は 2 以上の整数) 配置されている。さらに、各ブロックは、画素回路 2 の配列方向と同じ方向に一列に配列されている。

**【 0 0 1 3 】**

本実施形態では 1 ブロックを構成する画素回路 2 の数に対応して、データ信号を伝送するデータ線 3 が  $m$  本並んでいる。データ線 3 と画素回路 2 は引き出し線 1 2 により接続されている。本実施形態では、一本のデータ線 3 にブロック数に対応した  $N$  本の引き出し線 1 2 が接続されており、データ信号が各ブロックの画素回路 2 に供給される。本実施形態では、データ線 3 は、画素回路 2 の配列方向に延伸し、引き出し線 1 2 は、画素回路 2 の配列方向と垂直な方向に延伸している。

10

**【 0 0 1 4 】**

クロック信号 C K、C K B やゲート信号 S T、P 等の制御信号が走査回路 4 に入力され、ブロック毎に走査線 8 に走査信号を出力し、画素回路 2 に走査信号を供給する。走査回路 4 内にはシフトレジスタを含み、走査信号がブロック単位でタイミングをシフトして出力される。走査回路 4 内のシフトレジスタは、画素回路 2 の配列方向に信号が進むように配置されている。なお、図 1 では 1 本の走査線 8 により 1 種の走査信号を画素回路 2 に入力する構成となっているが、走査線 8 の数は、これに限るものではない。

20

**【 0 0 1 5 】**

ここで、露光光源は、面積が小さいほど量産時に多面取りでき、コストが下がるため好ましい。特に、短手方向の長さの変動は面積に及ぼす影響が大きく、この長さを少しでも短くした方が好ましい。同時に、露光光源には、プリント速度の高速化等、高速駆動も求められている。これらを実現するには、複数のデータ線で複数画素にまとめてデータを書き込むブロック駆動が好ましい。

**【 0 0 1 6 】**

全ての画素回路 2 と発光素子 1 1 へは、第一電源配線 5 と第二電源配線とを介して電源電圧が供給される。複数の第二電源配線は領域 6 A に配置されており、領域 6 A は、発光素子 1 1 や画素回路 2 と重なるように設けられている。第二電源配線は、この領域 6 A の、データ線 3、引き出し線 1 2、画素回路 2 の配線と異なる層に形成されている。上記の信号や電源電圧は、各端子部 7 により基板 1 上に供給される。尚、第二電源配線は、端子部 7 の付近で、他の層に乗り換え、端子部 7 に接続している。

30

**【 0 0 1 7 】**

図 1 に示す様に、本発明の露光光源は、データ線 3 を複数含むデータ線群と、発光素子 1 1 を複数含む発光素子群と、画素回路 2 と走査回路 4 と走査線 8 を含む回路部が、画素回路 2 の配列方向と垂直な方向に沿って、この順で配置されている。回路部が画素回路 2 と走査回路 4 とを含み、かつ、データ線群が回路部と異なる領域に配置されているため、走査線 8 がデータ線 3 と交差することなく、画素回路 2 に接続されている。その結果、データ線 3 の寄生容量を低減することができる。また、本実施形態では、画素回路 2 と走査回路 4 が、発光素子 1 1 側から、画素回路 2 の配列方向と垂直な方向に沿って、この順で配置されている。更に、本実施形態では、回路部が第一の電圧が印加される第一電源配線 5 を含み、第一電源配線 5 は、画素回路 2 の走査回路 4 側に配置されている。そのため、引き出し線 1 2 が、第一電源配線 5、走査線 8、走査回路 4 と交差することなく、画素回路 2 に接続されている。その結果、引き出し線 1 2 の寄生容量を低減することができる。尚、引き出し線 1 2 は、領域 6 A において第二電源配線と交差しているが、例えば、その間に平坦化膜を設け、引き出し線 1 2 と第二電源配線との層間の間隔を離す等により、寄生容量を小さくすることができる。

40

50

## 【0018】

また、本発明の露光光源は、データ線群と回路部の間に発光素子群を配置しているため、画素回路2の配列方向と垂直な方向の基板1の長さを短くすることができる。即ち、一般的に発光素子、特に有機EL素子は、水分や酸素と触れると劣化しやすくなるので、それらを遮断する為にキャップガラスや薄膜などの封止部材により封止を行う。その際、封止部材と基板1との接触領域として発光素子の周囲にある程度の封止スペースが必要となるが、本発明の露光光源では、発光素子群の両側のデータ線群や回路部の上に重ねて封止スペースを設けることができる。そのため、封止スペースを別途確保する必要がなく、画素回路2の配列方向と垂直な方向の基板1の長さを短くすることができる。

## 【0019】

10

ここで、発光素子群の両側の領域を封止スペースとして利用するためには、発光素子11を、基板1の画素回路2の配列方向に垂直な方向の、なるべく中央に配置することが望ましい。この観点より、データ線群の、画素回路2の配列方向と垂直な方向の長さが、走査回路4、画素回路2、第一電源配線5それぞれの、画素回路2の配列方向と垂直な方向の長さよりも長いことが好ましい。即ち、画素回路2の配列方向と垂直な方向の長さがデータ線群より短い走査回路4等を、発光素子群の片側にまとめて配置することで、発光素子11をなるべく中央に配置することができる。

## 【0020】

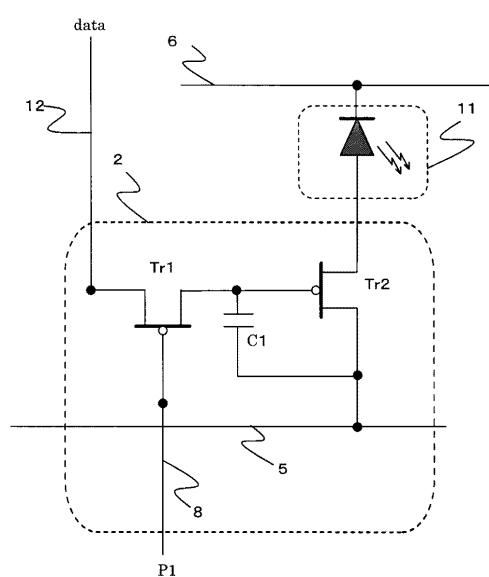

図2は画素回路2と発光素子11からなる画素の回路を示す一例図である。回路構成について説明する。画素回路2は2つのPMOSトランジスタと1つの保持容量C1から構成される。選択トランジスタであるスイッチトランジスタTr1のゲート電極に走査信号P1が入力され、ソースまたはドレインの一方にデータ線3が接続される。ソースまたはドレインの他方は、発光素子11に駆動電流を供給する駆動トランジスタTr2のゲートに接続され、Tr2のソースは第一電源配線5に、ドレインは発光素子11のアノード電極に接続される。Tr2のゲートとソース間に保持容量C1が配置され、画素回路2内に書き込まれたデータ電圧を保持する。さらに、発光素子11のカソードは全画素共通に設けられた共通電位である第二電源配線6に接続される。アノード電極、又はカソード電極のどちらか一方は、光取り出し面とするため、透明電極（例えば酸化インジウムスズ（ITO）やインジウム亜鉛酸化物（IZO）など）によって形成する。図2では、第一電源配線5に電源電圧を印加し、第二電源配線6をグランド（GND）としているが、第一電源配線5をGNDとし第二電源配線6に電源電圧を印加する回路構成であっても構わない。

20

## 【0021】

回路動作について説明する。データ線3に該当画素に対応するデータを設定したタイミングで、スイッチトランジスタTr1がONする。そしてデータが保持容量C1に書き込まれる。その後、Tr1がOFFすることで、データが画素回路2内に保持される。同時に、駆動トランジスタTr2のゲートソース間電圧に応じた電流がTr2から発光素子11に流れる。本実施形態では、画素回路2はPMOSで構成された例を示したが、このトランジスタ（Tr）極性に限定されない。具体的には、NMOSの単チャンネルで構成した回路や、NMOSおよびPMOSが混在した回路でも良い。

30

## 【0022】

40

上記実施形態では、発光素子の種類について限定はしていないが、本発明は、有機EL素子の点灯を制御する露光光源に好適に用いられるものである。

## 【0023】

## 〔第二の実施形態〕

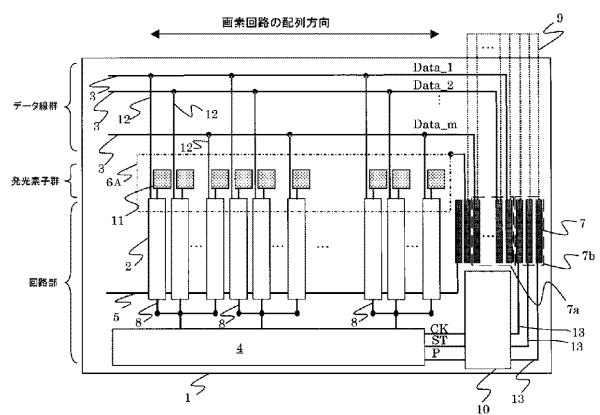

図3を用いて、本発明の露光光源の他の例について説明する。図3は本実施形態にかかる露光光源の構成を示す概略図である。

## 【0024】

本実施形態では、端子部7と走査回路4の間に、保護素子10としてESD（静電気放電）保護素子を有し、静電気により走査回路4が破壊されることを防いでいる。また、シ

50

ヨートリング9を有し、端子部7同士を低抵抗な配線で接続して同電位になるようにし、製造過程での静電気から基板1を保護している。尚、ショートリング9は、完成時には、基板1の端部である切断ラインで切断され、各端子部7間が分離される。

#### 【0025】

図3に示す様に、端子部7は、画素領域（画素回路2と発光素子11からなる画素が配置された領域）外であって、画素領域の、画素回路2の配列方向と垂直な方向の延長線上の領域外に、画素回路2の配列方向に沿って配置されている。また、端子部7は、データ線3に接続された第1の端子部群7aと、走査回路4に接続された第2の端子部群7bとを有し、第1の端子部群7aは、第2の端子部群7bの画素回路2側に配置されている。

#### 【0026】

データ線3は、第1の端子部群7aから、画素回路2の配列方向と垂直な方向に延伸し、垂直に折れ曲がって、画素領域の、画素回路2の配列方向と垂直な方向の延長線上の領域では、画素回路2の配列方向に延伸する。また、走査回路4と第2の端子部群7bとを保護素子10を介して接続する信号線13は、第2の端子部群7bから、画素回路2の配列方向と垂直な方向であって、第1の端子部群7aからデータ線3が延伸する方向と反対の方向に延伸している。その結果、第1の端子部群7aの、第1の端子部群7aからデータ線3が延伸する方向と反対側の領域（図3では、第1の端子部群7aの下側の領域）にスペースが生じる。ESD保護素子等の保護素子10は、一般的に画素回路2内のトランジスタ等と比べて非常に大きく、配置には大きな面積を必要とするが、本実施形態では、このスペースに保護素子10を配置することで、基板サイズの大型化を防止することができる。

10

#### 【0027】

更に、本実施形態では、ショートリング9を構成する配線が、第1の端子部群7a及び第2の端子部群7bから、画素回路2の配列方向と垂直な方向であって、第1の端子部群7aからデータ線3が延伸する方向に延伸している。一般的に、ショートリング9を構成する配線は低抵抗の配線層であるため、保護素子10を構成する配線層と同じ層に形成される。よって、ショートリング9と保護素子10を同じ場所に配置する事は、困難であるため、保護素子10を配置する領域には、ショートリング9を構成する配線を形成しない方が好ましい。但し、ショートリング9を保護素子10と全く干渉しない配線層で配線できる場合は、ショートリング9と保護素子10を重ねて配置することができるので、ショートリング9を構成する配線の延伸方向は、特に限定されない。

20

#### 【0028】

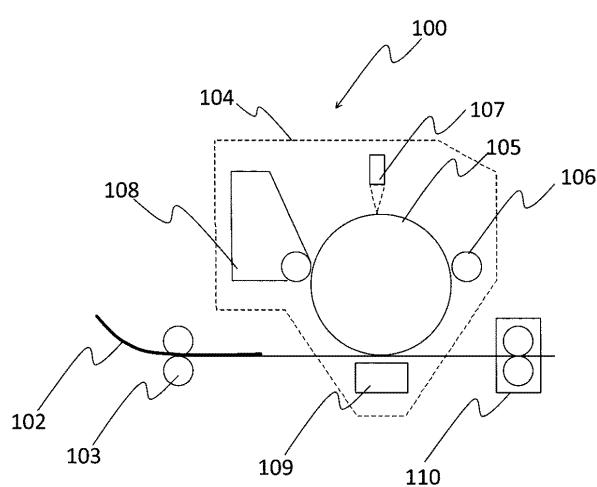

##### 画像形成装置

本発明の露光光源を用いた露光ヘッドを備える画像形成装置の一実施形態を、図4を用いて説明する。画像形成装置100は、感光ドラム105と、帯電器106と、本発明の露光光源を備えた露光ヘッド107と、現像器108と、転写器109と、を備える記録ユニット104を有する。また、搬送ローラー103と、定着器110と、を有する。露光ヘッド107は、露光光源に、露光光源の発光素子が発する光を感光ドラム105に結像する結像ユニットを設けたものである。

30

#### 【0029】

記録ユニット104では、まず、円柱状の感光ドラム105の表面を帯電器106で均一に帯電させ、露光ヘッド107がデータに応じて発光して静電潜像を感光ドラム105に形成する。静電潜像は露光ヘッド107の感光量（照度、時間）によって制御することができる。次に、記録ユニット104では、現像器108によって静電潜像にトナーを付着させ、転写器109によって静電潜像に付着したトナーを用紙102に転写する。このようにして、記録ユニット104を介して画像データが転写された用紙102は、定着器110によってトナーが定着され、排出される。なお、用紙102が搬送ローラー103によって記録ユニット103に搬送されるタイミングは適宜設定できる。本実施形態においては、記録ユニット104が1つのモノクロ画像形成装置を例にして説明したが、それに限るものではなく、記録ユニット104を複数備えたカラー画像形成装置でもかまわな

40

50

い。

【符号の説明】

【0030】

1：基板、2：画素回路、3：データ線、4：走査回路、5：第一電源配線、6：第二電源配線、7：端子部、8：走査線、9：ショートリング、10：保護素子、11：発光素子、12：引き出し線、13：信号線、100：画像形成装置、107：露光ヘッド

【図1】

【図2】

【図3】

【図4】

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 51/50 (2006.01) H 05 B 33/14 A

H 05 B 33/06 (2006.01) H 05 B 33/06

(72)発明者 井関 正己

東京都大田区下丸子3丁目30番2号 キヤノン株式会社内

審査官 大浜 登世子

(56)参考文献 特開2008-126589 (JP, A)

特開平11-274569 (JP, A)

特開2009-006718 (JP, A)

国際公開第2007/010816 (WO, A1)

特開2006-123493 (JP, A)

米国特許第05410146 (US, A)

(58)調査した分野(Int.Cl., DB名)

|        |         |

|--------|---------|

| B 41 J | 2 / 447 |

| B 41 J | 2 / 45  |

| G 03 G | 15 / 04 |

| H 01 L | 33 / 00 |

| H 01 L | 51 / 50 |

| H 04 N | 1 / 036 |

| H 05 B | 33 / 06 |