(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6726180号

(P6726180)

(45) 発行日 令和2年7月22日(2020.7.22)

(24) 登録日 令和2年6月30日(2020.6.30)

(51) Int.Cl.

F 1

H01L 21/02 (2006.01)

H01L 27/12 (2006.01)H01L 27/12

H01L 21/02B

B

請求項の数 33 (全 18 頁)

(21) 出願番号 特願2017-526096 (P2017-526096)

(86) (22) 出願日 平成27年11月16日 (2015.11.16)

(65) 公表番号 特表2017-538288 (P2017-538288A)

(43) 公表日 平成29年12月21日 (2017.12.21)

(86) 國際出願番号 PCT/US2015/060854

(87) 國際公開番号 WO2016/081356

(87) 國際公開日 平成28年5月26日 (2016.5.26)

審査請求日 平成30年10月26日 (2018.10.26)

(31) 優先権主張番号 62/081,352

(32) 優先日 平成26年11月18日 (2014.11.18)

(33) 優先権主張国・地域又は機関

米国(US)

(73) 特許権者 518112516

グローバルウェーハズ カンパニー リミテッド

Global Wafer s Co., Ltd.

台灣 30075 シンチュ シンチュ

サイエンス パーク インダストリー イ

ー. ロード セカンド ナンバー8

(74) 代理人 100101454

弁理士 山田 阜二

(74) 代理人 100112911

弁理士 中野 晴夫

前置審査

最終頁に続く

(54) 【発明の名称】高抵抗率半導体・オン・インシュレータウエハおよび製造方法

## (57) 【特許請求の範囲】

## 【請求項 1】

その一方が単結晶半導体ハンドル基板の表面であり、他方が前記単結晶半導体ハンドル基板の裏面である2つの主要な、ほぼ平行な面と、前記単結晶半導体ハンドル基板の前記表面と前記裏面を接合する外縁と、前記単結晶半導体ハンドル基板の前記表面と前記裏面の間の中心平面と、および前記単結晶半導体ハンドル基板の前記表面と前記裏面の間のバルク領域と、を含む単結晶半導体ハンドル基板であって、少なくとも3000 · cmの最小バルク領域抵抗率を有する単結晶半導体ハンドル基板と、

少なくとも20モル%のモルパーセントでゲルマニウムを含み、前記単結晶半導体ハンドル基板の前記表面に界面接觸している緩和されたアモルファス半導体層と、

前記緩和されたアモルファス半導体層に界面接觸している多結晶シリコン層を含み、少なくとも1000 · cmの抵抗率を有する電荷トラップ層と、

前記多結晶シリコン層を含む前記電荷トラップ層に界面接觸している誘電体層と、

前記誘電体層に界面接觸している単結晶半導体デバイス層と、

を含む多層構造。

## 【請求項 2】

前記単結晶半導体ハンドル基板は、3000 · cm ~ 1000,000 · cmのバルク抵抗率を有する単結晶シリコンウエハを含む請求項1に記載の多層構造。

## 【請求項 3】

前記単結晶半導体ハンドル基板は、約3000 · cm ~ 約10,000 · cmのバ

10

20

ルク抵抗率を有する請求項 1 に記載の多層構造。

**【請求項 4】**

前記単結晶半導体ハンドル基板は、約 3 0 0 0 ～ cm ~ 約 5 0 0 0 ～ cm のバルク抵抗率を有する請求項 1 に記載の多層構造。

**【請求項 5】**

前記緩和されたアモルファス半導体層は、シリコンゲルマニウムを含み、ゲルマニウムのモルパーセントは、少なくとも 50 モル% である請求項 1 に記載の多層構造。

**【請求項 6】**

前記緩和されたアモルファス半導体層は、シリコンゲルマニウムを含み、ゲルマニウムのモルパーセントは、少なくとも 90 モル% である請求項 1 に記載の多層構造。 10

**【請求項 7】**

前記緩和されたアモルファス半導体層は、シリコンゲルマニウムを含み、ゲルマニウムのモルパーセントは、少なくとも 99.9 モル% である請求項 1 に記載の多層構造。

**【請求項 8】**

前記緩和されたアモルファス半導体層は、本質的にゲルマニウムから成る請求項 1 に記載の多層構造。

**【請求項 9】**

前記緩和されたアモルファス半導体層は、臨界厚さより厚い請求項 1 に記載の多層構造。 20

**【請求項 10】**

前記緩和されたアモルファス半導体層の平均厚さは、少なくとも約 10 ナノメートルである請求項 1 に記載の多層構造。

**【請求項 11】**

前記緩和されたアモルファス半導体層の平均厚さは、約 10 ナノメートル～約 3 0 0 0 ナノメートルである請求項 1 に記載の多層構造。

**【請求項 12】**

前記誘電体層は、二酸化ケイ素、窒化ケイ素、酸化ハフニウム、酸化チタン、酸化ジルコニウム、酸化ランタン、酸化バリウム、およびそれらの組合せから成るグループから選択される請求項 1 に記載の多層構造。

**【請求項 13】**

前記誘電体層は、約 10 ナノメートル～約 10,000 ナノメートル、約 10 ナノメートル～約 5 0 0 0 ナノメートル、または約 100 ナノメートル～約 4 0 0 ナノメートルの厚さを有する埋め込み酸化物層を含む請求項 1 に記載の多層構造。 30

**【請求項 14】**

前記誘電体層は、二酸化シリコンを含む請求項 1 に記載の多層構造。

**【請求項 15】**

前記二酸化シリコンは、約 10 ナノメートル～約 10,000 ナノメートル、約 10 ナノメートル～約 5 0 0 0 ナノメートル、または約 100 ナノメートル～約 4 0 0 ナノメートルの厚さを有する請求項 14 に記載の多層構造。

**【請求項 16】**

75 ～ 3 0 0 の範囲の温度における化学気相堆積によって、単結晶半導体ハンドル基板の表面に界面接触するようにアモルファス半導体層を形成するステップであって、前記単結晶半導体ハンドル基板は、その一方が単結晶半導体ハンドル基板の表面であり、他方が前記単結晶半導体ハンドル基板の裏面である 2 つの主要な、ほぼ平行な面と、前記単結晶半導体ハンドル基板の前記表面と前記裏面を接合する外縁と、前記単結晶半導体ハンドル基板の前記表面と前記裏面の間の中心平面と、および前記単結晶半導体ハンドル基板の前記表面と前記裏面の間のバルク領域と、を含む単結晶半導体ハンドル基板であって、少なくとも 3 0 0 0 ～ cm の最小バルク領域抵抗率を有し、更に、前記アモルファス半導体層は、少なくとも 20 モル% のゲルマニウムのモルパーセントでゲルマニウムを含むステップと。 40

前記アモルファス半導体層を少なくとも部分的に緩和するため、前記単結晶半導体ハンドル基板の前記表面に界面接觸している前記アモルファス半導体層を有する前記単結晶半導体ハンドル基板を、600以上の温度で1秒～1時間の期間アニールし、それによつて緩和されたアモルファス半導体層を形成するステップと、

前記緩和されたアモルファス半導体層に界面接觸している多結晶シリコン層を含み、少なくとも1000・cmの抵抗率を有する電荷トラップ層を形成するステップと、

単結晶半導体ドナー基板の表面上の誘電体層を前記単結晶半導体ハンドル基板の前記多結晶シリコン層に接合させることによって接合構造を形成するステップであつて、前記単結晶半導体ドナー基板は、その一方が前記半導体ドナー基板の表面であり、他方が前記半導体ドナー基板の裏面である2つの主要な、ほぼ平行な面と、前記半導体ドナー基板の前記表面と前記裏面を接合する外縁と、前記半導体ドナー基板の前記表面と前記裏面の間の中心平面と、を含み、更に、前記半導体ドナー基板の前記表面は、前記誘電体層を含むステップと、

を含む多層構造の製造方法。

#### 【請求項17】

前記単結晶半導体ハンドル基板は、3000・cm～100,000・cmのバルク抵抗率を有する単結晶シリコンウエハを含む請求項16に記載の方法。

#### 【請求項18】

前記単結晶半導体ハンドル基板は、チョクラルスキー法またはフローディングゾーン法によって成長した単結晶シリコンインゴットからスライスされたシリコンウエハを含む請求項16に記載の方法。

#### 【請求項19】

前記単結晶半導体ハンドル基板は、約3000・cm～約10,000・cmのバルク抵抗率を有する請求項16に記載の方法。

#### 【請求項20】

前記単結晶半導体ハンドル基板は、約3000・cm～約5000・cmのバルク抵抗率を有する請求項16に記載の方法。

#### 【請求項21】

前記緩和されたアモルファス半導体層は、シリコングルマニウムを含み、ゲルマニウムのモルパーセントは、少なくとも50モル%である請求項16に記載の方法。

#### 【請求項22】

前記緩和されたアモルファス半導体層は、シリコングルマニウムを含み、ゲルマニウムのモルパーセントは、少なくとも90モル%である請求項16に記載の方法。

#### 【請求項23】

前記緩和されたアモルファス半導体層は、シリコングルマニウムを含み、ゲルマニウムのモルパーセントは、少なくとも99.9モル%である請求項16に記載の方法。

#### 【請求項24】

前記緩和されたアモルファス半導体層は、ゲルマニウムを含む請求項16に記載の方法。

#### 【請求項25】

単結晶半導体ドナー基板の表面上の前記誘電体層に接合させるステップの前に前記多結晶シリコン層を含む電荷トラップ層を酸化させるステップを更に含む請求項16に記載の方法。

#### 【請求項26】

前記半導体ドナー基板の前記誘電体層と前記単結晶半導体ハンドル基板の前記表面上の前記多結晶シリコン層を含む電荷トラップ層との間の接合を強化するのに十分な温度で、および十分な期間、前記接合構造を加熱するステップを更に含む請求項16に記載の方法。

#### 【請求項27】

前記単結晶半導体ドナー基板は、イオン注入されたダメージ層を含み、

10

20

30

40

50

前記方法は、

前記単結晶半導体ドナー基板の前記イオン注入されたダメージ層で前記接合構造を機械的に劈開し、それによって前記単結晶半導体ハンドル基板と、前記緩和されたアモルファス半導体層と、前記緩和されたアモルファス半導体層に接触している前記多結晶シリコン層を含む電荷トラップ層と、前記誘電体層と、前記誘電体層に接触している単結晶半導体デバイス層と、を含む劈開構造を製造するステップと、

前記単結晶半導体デバイス層と前記単結晶半導体ハンドル基板との間の接合を強化するのに十分な温度で、および十分な期間、前記劈開構造を加熱するステップと、を含む請求項16に記載の方法。

**【請求項28】**

10

前記緩和されたアモルファス半導体層は、ミスフィット転位、貫通転位、およびそれらの組合せから成るグループから選択される転位を含み、転位の密度は、 $1 \times 10^5 \sim 1 \times 10^{10} / \text{cm}^2$  である請求項1に記載の多層構造。

**【請求項29】**

前記緩和されたアモルファス半導体層は、0.1モル%～5モル%の濃度で炭素を含む請求項1に記載の多層構造。

**【請求項30】**

前記緩和されたアモルファス半導体層は、0.5モル%～1モル%の濃度で炭素を含む請求項1に記載の多層構造。

**【請求項31】**

20

前記緩和されたアモルファス半導体層は、ミスフィット転位、貫通転位、およびそれらの組合せから成るグループから選択される転位を含み、転位の密度は、 $1 \times 10^5 \sim 1 \times 10^{10} / \text{cm}^2$  である請求項16に記載の方法。

**【請求項32】**

前記緩和されたアモルファス半導体層は、0.1モル%～5モル%の濃度で炭素を含む請求項16に記載の方法。

**【請求項33】**

前記緩和されたアモルファス半導体層は、0.5モル%～1モル%の濃度で炭素を含む請求項16に記載の方法。

**【発明の詳細な説明】**

30

**【関連出願の相互参照】**

**【0001】**

この出願は、2014年11月18日に出願された米国仮出願第62/081,352の優先権を主張し、その開示全体が参照により本明細書に組み込まれる。

**【技術分野】**

**【0002】**

本発明は、一般的に、半導体ウエハ製造の分野に関する。特に、本発明は、電荷トラップ層を含む半導体・オン・インシュレータ（例えば、シリコン・オン・インシュレータ）構造を形成する方法に関する。

**【背景技術】**

40

**【0003】**

半導体ウエハは、一般的に、単結晶インゴット（例えばシリコンインゴット）から製造される。このインゴットは、トリミングおよび研磨され、後続の手順の中でウエハを適切に方向付けるための1つ以上のフラットまたはノッチを有する。次に、インゴットは、スライスされて個々のウエハになる。本明細書ではシリコンから構成された半導体ウエハについて述べるが、ゲルマニウム、シリコンカーバイド、シリコンゲルマニウム、またはガリウム砒素などの他の材料を使用して半導体ウエハを製造してもよい。

**【0004】**

半導体ウエハ（例えばシリコンウエハ）は、複合層構造の製造に利用され得る。複合層構造（例えば、半導体・オン・インシュレータ、特にシリコン・オン・インシュレータ（

50

SOI構造)は、一般的に、ハンドルウエハまたはハンドル層、デバイス層、およびハンドル層とデバイス層の間の絶縁(すなわち、誘電体)膜(典型的には酸化物層)を含む。一般的に、デバイス層は、0.01~20マイクロメートルの厚さ、例えば0.05~20マイクロメートルの厚さである。一般的に、シリコン・オン・インシュレータ(SOI)、シリコン・オン・サファイア(SOS)、およびシリコン・オン・クオーツなどの複合層構造は、2つのウエハを密に接触させ、繰り返して熱処理を行って結合を強化することによって製造される。

#### 【0005】

熱アニールの後、接合された構造は、更に処理を受け、ドナーウエハの実質的な部分を除去して層の転写を達成する。例えば、しばしばバックエッチングSOI(すなわち、BESOI)と呼ばれるウエハ薄化技術、例えばエッチングまたはグライディングが使用されるが、ここではシリコンウエハは、ハンドルウエハに接合され、その後、ハンドルウエハ上のシリコンの薄い層のみが残るまでゆっくりとエッチング除去される。例えば、その開示全体が説明されたものとして本明細書に取り込まれる、米国特許第5,189,500を参照せよ。この方法は、時間およびコストがかかり、1つの基板を無駄にし、および一般的に、数ミクロンよりも薄い層に対して適切な厚さの均一性を有さない。

10

#### 【0006】

層の転写を実現する別の一般的な方法は、水素注入とそれに続く熱誘起層分離を利用する。粒子(例えば、水素原子または水素とヘリウム原子の組合せ)は、ドナーウエハの表面の下の特定の深さに注入される。注入された粒子は、注入された特定の深さでドナーウエハの中に劈開面を形成する。ドナーウエハの表面は洗浄され、注入プロセス中にウエハ上に堆積した有機化合物を除去する。

20

#### 【0007】

次に、ドナーウエハの表面は、ハンドルウエハに接合され、親水性の接合プロセスにより接合ウエハを形成する。接合の前に、ドナーウエハおよび/またはハンドルウエハは、ウエハの表面を例えば酸素および窒素を含むプラズマに暴露することによって活性化される。プラズマへの暴露は、しばしば表面活性化と呼ばれるプロセスの中で表面の構造を変化させるが、ここで活性化プロセスは、ドナー水およびハンドルウエハの一方または双方の表面を親水性にするものである。次に、ウエハは共に圧縮され、ウエハ間に接合が形成される。この接合は比較的弱く、異なる処理が行われる前に強化されなければならない。

30

#### 【0008】

いくつかのプロセスでは、ドナーウエハとハンドルウエハ(すなわち接合ウエハ)の間の親水性の接合は、接合ウエハのペアを加熱またはアニールすることによって強化される。いくつかのプロセスでは、ウエハ接合は、約300~500などの低温で行われてもよい。いくつかのプロセスでは、ウエハ接合は、約800~1100などの高温で行われてもよい。上昇した温度は、ドナーウエハの隣接表面とハンドルウエハとの間に共有結合を形成し、ドナーウエハとハンドルウエハとの間の接合を凝固させる。接合ウエハの加熱またはアニールと同時に、ドナーウエハに先に注入された粒子は、劈開面を弱める。

#### 【0009】

40

次にドナーウエハの一部は、接合ウエハから劈開面に沿って分離されて(すなわち劈開されて)、SOIウエハを形成する。劈開は、接合ウエハの対向する側に対して垂直に機械的な力が加えられる固定具の中に、接合ウエハを置くことによって行われ、ドナーウエハの一部を接合ウエハから引き剥がす。いくつかの方法によると、機械的な力を加えるために吸着カップが利用される。ドナーウエハの一部の分離は、劈開面の結合されたウエハの縁に機械的くさびを当てることによって開始され、劈開面に沿って亀裂の伝播を開始させる。次に、吸着カップによって加えられる機械的な力は、接合ウエハからドナーウエハの一部を引き離し、SOIウエハを形成する。

#### 【0010】

他の方法によると、接合されたペアは、代わりに一定時間にわたって高温にさらされ、

50

接合ウエハからドナーウエハの一部を分離してもよい。高温にさらすことは、劈開面に沿って亀裂の伝播を開始させ、ドナーウエハの一部を分離させる。この方法は、転写された層のより良好な均一性を可能にし、ドナーウエハのリサイクルを可能にするが、典型的には、注入され結合されたペアを 500 °C に近い温度に加熱することを必要とする。

#### 【0011】

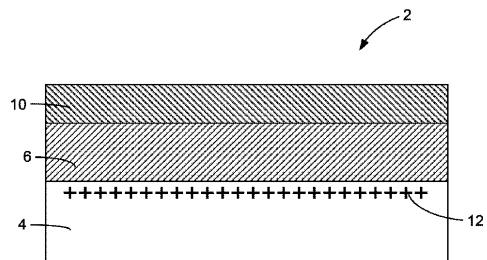

アンテナスイッチなどの RF 関連デバイスに対する高抵抗率半導体・オン・インシュレータ（例えばシリコン・オン・インシュレータ）ウエハの使用は、コストおよび集積の点で従来の基板に優る恩恵を提供する。高周波用途のために導電性基板を使用する場合に、寄生電力損失を低減し、および固有の高調波ひずみを最小にするためには、それだけでは不十分ではあるが、高抵抗率の基板ウエハを使用することが必要である。したがって、RF デバイスについてのハンドルウエハの抵抗率は、一般的に、約 500 °C より大きい。<sup>10</sup> ここで図 1 を参照すると、シリコン・オン・インシュレータ構造 2 は、非常に高い抵抗率のシリコンウエハ 4、埋め込み酸化物（BOX）層 6、およびシリコンデバイス層 10 を含む。このような基板は、BOX / ハンドル界面に自由キャリア（電子またはホール）を発生させる高伝導率の電荷反転層または蓄積層 12 を形成しやすく、デバイスが RF 周波数で動作する場合に、基板の実効抵抗率を減らし、寄生的な電力損失およびデバイスの非線形性を生じさせる。これらの反転 / 蓄積層は、BOX 固定電荷、酸化物トラップ電荷、界面トラップ電荷、およびデバイス自体に印加される DC バイアスにより生じ得る。

#### 【0012】

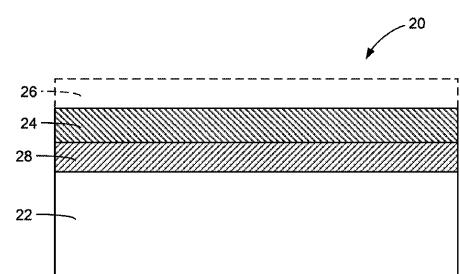

したがって、誘導された反転または蓄積層に電荷をトラップし、非常に近い表面領域の中でも基板の高抵抗率を維持する方法が必要とされる。高抵抗率ハンドル基板と埋め込み酸化物（BOX）との間の電荷トラップ層（CTL）は、SOI ウエハを使用して製造された RF デバイスの性能を向上させ得ることが知られている。これらの高界面トラップ層を形成するための多くの方法が提案されている。例えば、ここで図 2 を参照すると、RF デバイス用途のための CTL を有する半導体・オン・インシュレータ構造 20（例えば、シリコン・オン・インシュレータ、または SOI）を生成する 1 つの方法は、高抵抗率を有するシリコン基板 22 上の非ドープ多結晶シリコン膜 28 を堆積させること、および次に酸化物スタック 24 とその上の最上部のシリコン層 26 とを形成することに基づく。多結晶シリコン層 28 は、シリコン基板 22 と埋め込み酸化物層 24 との間の高抵抗率層として機能する。<sup>20</sup> 図 2 を参照すると、シリコン・オン・インシュレータ構造 20 の中の高抵抗率基板 22 と埋め込み酸化物層 24 との間の電荷トラップ層として使用するための多結晶シリコン膜を示している。別の方法は、重イオンを注入して、近接した表面ダメージ層を作ることである。無線周波数デバイスなどのデバイスは、最上部シリコン層 26 の中に組み込まれる。

#### 【0013】

学術研究では、酸化物と基板との間にある多結晶シリコン層が、デバイス分離性を改善し、伝送路損失を減少させ、高調波ひずみを減少させることが示されている。例えば、H. S. Gamble 他 “Low-loss CPW lines on surface stabilized high resistivity silicon,” Microwave Guided Wave Lett., 9(10), pp.395-397, 1999、D. Lederer, R. Lobet および J.-P. Raskin, “Enhanced high resistivity SOI wafers for RF applications,” IEEE Int'l. SOI Conf., pp.46-47, 2004、D. Lederer および J.-P. Raskin, “New substrate passivation method dedicated to high resistivity SOI wafer fabrication with increased substrate resistivity,” IEEE Electron Device Letters, vol.26, no.11, pp.805-807, 2005、D. Lederer, B. Aspar, C. Laghae および J.-P. Raskin, “Performance of RF passive structures and SOI MOSFETs transferred on a passivated HR SOI substrate,” IEEE International SOI Conference, pp.29-30, 2006、および、Daniel C. Kerr 他 “Identification of RF harmonic distortion on Si substrates and its reduction using a trap-rich layer”, Silicon Monolithic Integrated Circuits in RF Systems, 2008. Si RF 2008 (IEEE Topical Meeting), pp.151-154, 2008、を参照せよ。<sup>40</sup>

#### 【発明の概要】

10

20

30

40

50

## 【0014】

簡潔にいえば、本発明は、多層構造に関する。この多層構造は、その一方が単結晶半導体ハンドル基板の表面であり、他方が単結晶半導体ハンドル基板の裏面である2つの主要な、ほぼ平行な面と、単結晶半導体ハンドル基板の表面と裏面を接合する外縁と、単結晶半導体ハンドル基板の表面と裏面の間の中心平面と、および単結晶半導体ハンドル基板の表面と裏面の間のバルク領域と、を含む単結晶半導体ハンドル基板であって、少なくとも500・cmの最小バルク領域抵抗率を有する単結晶半導体ハンドル基板と、ゲルマニウムを含み、単結晶半導体ハンドル基板の表面に界面接触している緩和半導体層と、緩和半導体層に界面接触している多結晶シリコン層と、多結晶シリコン層に界面接触している誘電体層と、誘電体層に界面接触している単結晶半導体デバイス層と、を含む。

10

## 【0015】

本発明は、更に、多層構造の製造方法に関する。この方法は、単結晶半導体ハンドル基板の表面に界面接觸するように半導体層を形成するステップであって、単結晶半導体ハンドル基板は、その一方が単結晶半導体ハンドル基板の表面であり、他方が単結晶半導体ハンドル基板の裏面である2つの主要な、ほぼ平行な面と、単結晶半導体ハンドル基板の表面と裏面を接合する外縁と、単結晶半導体ハンドル基板の表面と裏面の間の中心平面と、および単結晶半導体ハンドル基板の表面と裏面の間のバルク領域と、を含む単結晶半導体ハンドル基板であって、少なくとも500・cmの最小バルク領域抵抗率を有し、更に、半導体層は、少なくとも20モル%のゲルマニウムを含むステップと、半導体層を少なくとも部分的に緩和するのに十分な温度および時間で、単結晶半導体ハンドル基板の表面に界面接觸している半導体層を有する単結晶半導体ハンドル基板をアニールし、それによつて緩和半導体層を形成するステップと、緩和半導体層に界面接觸している多結晶シリコン層を形成するステップと、単結晶半導体ドナー基板の表面上の誘電体層を単結晶半導体ハンドル基板の多結晶シリコン層に接合させることによつて接合構造を形成するステップであつて、単結晶半導体ドナー基板は、その一方が半導体ドナー基板の表面であり、他方が半導体ドナー基板の裏面である2つの主要な、ほぼ平行な面と、半導体ドナー基板の表面と裏面を接合する外縁と、半導体ドナー基板の表面と裏面の間の中心平面と、を含み、更に、半導体ドナー基板の表面は、誘電体層を含むステップと、を含む。

20

## 【0016】

本発明は、なお更に、多層構造に関し、この構造は、その一方が単結晶半導体ハンドル基板の表面であり、他方が単結晶半導体ハンドル基板の裏面である2つの主要な、ほぼ平行な面と、単結晶半導体ハンドル基板の表面と裏面を接合する外縁と、単結晶半導体ハンドル基板の表面と裏面の間の中心平面と、および単結晶半導体ハンドル基板の表面と裏面の間のバルク領域と、を含む単結晶半導体ハンドル基板であつて、少なくとも500・cmの最小バルク領域抵抗率を有する単結晶半導体ハンドル基板と、シリコングルマニウムを含み、単結晶半導体ハンドル基板の表面に界面接觸している半導体層と、シリコンおよびゲルマニウムを含む半導体層に界面接觸している誘電体層と、誘電体層に界面接觸している単結晶半導体デバイス層と、を含む。

30

## 【0017】

本発明は、なお更に、多層構造の製造方法に関する。この方法は、単結晶半導体ハンドル基板の表面に界面接觸するように半導体層を堆積させるステップであつて、単結晶半導体ハンドル基板は、その一方が単結晶半導体ハンドル基板の表面であり、他方が単結晶半導体ハンドル基板の裏面である2つの主要な、ほぼ平行な面と、単結晶半導体ハンドル基板の表面と裏面を接合する外縁と、単結晶半導体ハンドル基板の表面と裏面の間の中心平面と、および単結晶半導体ハンドル基板の表面と裏面の間のバルク領域と、を含む単結晶半導体ハンドル基板であつて、少なくとも500・cmの最小バルク領域抵抗率を有し、更に、半導体層は、シリコングルマニウムを含み、更に、シリコングルマニウムを含む半導体層の中のゲルマニウムのモルパーセントは、少なくとも5モル%であるステップと、単結晶半導体ドナー基板の表面に界面接觸している誘電体層を単結晶半導体ハンドル基板の表面に界面接觸しているシリコングルマニウムを含む半導体層に接合せることによ

40

50

つて接合構造を形成するステップであって、単結晶半導体ドナー基板は、その一方が半導体ドナー基板の表面であり、他方が半導体ドナー基板の裏面である2つの主要な、ほぼ平行な面と、半導体ドナー基板の表面と裏面を接合する外縁と、半導体ドナー基板の表面と裏面の間の中心平面と、を含み、更に、半導体ドナー基板の表面は、誘電体層を含むステップと、を含む。

#### 【0018】

本発明の他の目的および特徴は、一部は明白であり、一部は以下に指摘される。

#### 【図面の簡単な説明】

#### 【0019】

【図1】高抵抗率基板および埋め込み酸化物層を含むシリコン・オン・インシュレータウエハの図である。 10

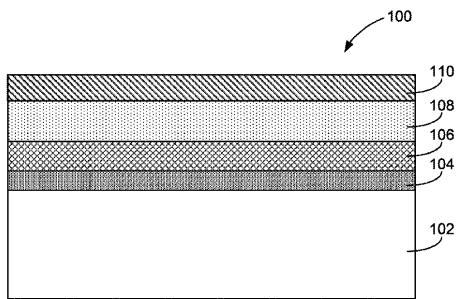

【図2】高抵抗率基板と埋め込み酸化物層との間に多結晶シリコン電荷トラップ層を含むシリコン・オン・インシュレータウエハの図である。

【図3】本発明によるシリコン・オン・インシュレータウエハの図である。

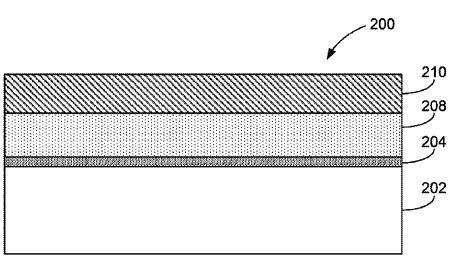

【図4】本発明によるシリコン・オン・インシュレータウエハの図である。

#### 【発明を実施するための形態】

#### 【0020】

本発明によると、単結晶半導体ハンドル基板、例えば単結晶半導体ハンドルウエハの上に電荷トラップ層を製造する方法が提供される。電荷トラップ層を含む単結晶半導体ハンドル基板、例えば単結晶半導体ハンドルウエハは、半導体・オン・インシュレータ（例えば、シリコン・オン・インシュレータ）構造の製造に役立つ。本発明によると、単結晶半導体ハンドル基板、例えば単結晶半導体ハンドルウエハの中の電荷トラップ層は、酸化界面付近の領域に形成される。有利には、本発明の方法は、非常に欠陥のある電荷トラップ層を提供するが、この層は、半導体・オン・インシュレータ基板およびデバイスの製造に続く熱処理ステップなどの熱処理に対して安定する。 20

#### 【0021】

いくつかの具体例では、本発明は、無線周波数（RF）デバイス用途に適した半導体・オン・インシュレータ構造（例えば、シリコン・オン・インシュレータ（SOI））を形成する方法を目的とする。半導体・オン・インシュレータ構造は、デバイス層、埋め込み酸化物層、および高抵抗率シリコンハンドルウエハを含む。さらに、高抵抗率ハンドルは、SOI構造のBOX層とハンドルウエハとの界面に隣接しているハンドル表面の上に形成された電荷をトラップすることができる多結晶シリコン層をも含む。本発明のいくつかの具体例では、高抵抗率ハンドルウエハと多結晶シリコン層との間に高濃度のSiGeまたは純Geの完全緩和層が形成され、SOI製造の中に含まれる高温処理ステップの間、多結晶シリコン電荷トラップ層の再結晶化を防止する転位ネットワークを提供する。 30

#### 【0022】

いくつかの具体例では、本発明は、反転層の形成に対して改善された耐性を有する高抵抗率の単結晶半導体ハンドル基板を形成する方法を目的とする。高抵抗率の単結晶半導体ハンドル基板は、BOX / 基板界面に高濃度のゲルマニウムを有するように製造される。ゲルマニウムは、酸化物との界面において極めて低い電子移動度を示す。さらに、Ge / SiO<sub>2</sub>界面は、電荷トラップとして機能する高い界面欠陥を有する。その結果、N型反転層の形成が抑制される。最後に、もしN型反転層が形成されたとしても、電子移動度が低いため、Ge層を通る導電率は低い。結果として、Ge層を含む単結晶半導体ハンドル基板を使用して作製されたRFデバイスは、改善された性能を有する。 40

#### 【0023】

本発明で使用する基板は、半導体ハンドル基板、例えば単結晶半導体ハンドルウエハと、半導体ドナー基板、例えば単結晶半導体ドナーウエハとを含む。半導体・オン・インシュレータ複合構造の中の半導体デバイス層は、半導体ドナー基板、例えば単結晶半導体ドナーウエハから得られる。半導体デバイス層は、半導体ドナー基板エッチングなどのウエハ薄化技術によって、またはダメージ面を含む半導体ドナー基板を劈開することによって 50

、半導体ハンドル基板上に転写されてもよい。一般的に、単結晶半導体ハンドルウエハおよび単結晶半導体ドナーウエハは、2つの主要な、ほぼ平行な面を含む。平行面の一方は基板の表面であり、平行面の他方は基板の裏面である。基板は、表面と裏面を接合する外縁と、表面と裏面の間の中心平面とを含む。基板は、更に、中心平面に垂直な仮想の中心軸と、中心軸から外縁まで延びる半径方向長さとを含む。さらに、半導体基板、例えばシリコンウエハは、典型的に、いくらかの総膜厚ばらつき (total thickness variation) (TTV)、たわみ、および反りを有するため、表面上のすべての点と裏面上のすべての点との間の中間点は、正確には平面内にはない。しかしながら、実際には、TTV、たわみ、および反りは、典型的にはわずかであるため、中間点は、表面と裏面との間のほぼ等距離の仮想中心平面内にあると近似できる。

10

#### 【0024】

本明細書に記載のいずれかの操作の前には、基板の表面および裏面は、実質的に同一であってもよい。面は、単に便宜のために、「表面 (front surface)」または「裏面 (back surface)」と称され、本発明の方法の操作が行われる面を一般的に区別する。本発明に関して、単結晶半導体ハンドル基板、例えば単結晶シリコンハンドルウエハの「表面」は、接合構造の内側の面になる基板の主要な面を指す。この表面の上には、電荷トラップ層が形成されている。したがって、単結晶半導体ハンドル基板、例えばハンドルウエハの「裏面」は、接合構造の外側の面になる主要な面を指す。同様に、単結晶半導体ドナー基板、例えば単結晶シリコンドナーウエハの「表面」は、接合構造の内側の面になる単結晶半導体ドナー基板の主要な面を指す。単結晶半導体ドナー基板の表面は、しばしば誘電体層、例えばシリコン酸化物層を含むが、これは最終構造の中で埋め込み酸化物 (BOX) 層を形成する。単結晶半導体ドナー基板、例えば単結晶シリコンドナーウエハの「裏面」は、接合構造の外側になる主要な面を指す。従来の接合およびウエハ薄化ステップが完了すると、単結晶半導体ドナー基板は、半導体・オン・インシュレータ (例えば、シリコン・オン・インシュレータ) 複合構造の半導体デバイス層を形成する。

20

#### 【0025】

単結晶半導体ハンドル基板および単結晶半導体ドナー基板は、単結晶半導体ウエハであってもよい。いくつかの具体例では、半導体ウエハは、シリコン、シリコンカーバイド、シリコンゲルマニウム、ガリウム砒素、ガリウム窒素、インジウムリン、インジウムガリウム砒素、ゲルマニウム、およびこれらの組合せから成るグループから選択された材料を含む。いくつかの好適な具体例では、半導体ウエハは、シリコン、シリコンカーバイド、およびシリコンゲルマニウムの中から選択された半導体材料を含む。本発明の単結晶半導体ウエハ、例えば単結晶シリコンハンドルウエハおよび単結晶シリコンドナーウエハは、典型的には、少なくとも約150mm、少なくとも約200mm、少なくとも約300mm、または少なくとも約450mmの公称直径を有する。ウエハの厚さは、約250マイクロメートル～約1500マイクロメートル、例えば約300マイクロメートル～約1000マイクロメートル、適切には約500マイクロメートル～約1000マイクロメートルの範囲内で変動してもよい。いくつかの特定の具体例では、ウエハの厚さは、約725マイクロメートルであってもよい。

30

#### 【0026】

特に好適な具体例では、単結晶半導体ウエハは、従来のチョクラルスキー結晶成長法またはフローティングゾーン法によって成長した単結晶インゴットからスライスされた単結晶シリコンウエハを含む。この方法は、標準的なシリコンのスライス、ラッピング、エッチング、および研磨技術と共に、例えば、(参照により本明細書に取り込まれた) F. Shimura, Semiconductor Silicon Crystal Technology, Academic Press, 1989、およびSilicon Chemical Etching, (J. Grabmaier編) Springer-Verlag, N.Y., 1982の中で開示されている。好適には、ウエハは、当業者に知られている標準的な方法によって研磨されおよび洗浄される。例えば、W.C.O'Mara他, Handbook of Semiconductor Silicon Technology, Noyes Publicationsを参照せよ。必要に応じて、ウエハは、例えば標準的なSC1/SC2溶液の中で洗浄される。いくつかの具体例では、本発明の単結晶シリコンウエハは、

40

50

従来のチョクラルスキー (Cz) 結晶成長法によって成長した単結晶インゴットからスライスされた単結晶シリコンウエハであり、典型的には、少なくとも約 150 mm、少なくとも約 200 mm、少なくとも約 300 mm、または少なくとも約 450 mm の公称直径を有する。好適には、単結晶シリコンハンドルウエハおよび単結晶シリコンドナーワエハの両方は、傷、大きなパーティクルなどの表面欠陥のない鏡面磨きされた表面仕上がりを有する。ウエハの厚さは、約 250 マイクロメートル～約 1500 マイクロメートル、例えば約 300 マイクロメートル～約 1000 マイクロメートル、適切には約 500 マイクロメートル～約 1000 マイクロメートルの範囲内で変動してもよい。いくつかの特定の具体例では、ウエハの厚さは、約 725 マイクロメートルであってもよい。

## 【0027】

10

いくつかの具体例では、単結晶半導体ウエハ、すなわちハンドルウエハおよびドナーワエハは、チョクラルスキー成長法によって一般的に得られる濃度の格子間酸素を含む。いくつかの具体例では、半導体ウエハは、約 4 PPMA～約 18 PPMA の濃度の酸素を含む。いくつかの具体例では、半導体ウエハは、約 10 PPMA～約 35 PPMA の濃度の酸素を含む。好適には、単結晶シリコンハンドルウエハは、約 10 PPMA 以下の濃度の酸素を含む。格子間酸素は、SEMI MF 1188-1105 によって測定されてもよい。

## 【0028】

いくつかの具体例では、半導体ハンドル基板、例えば単結晶シリコンハンドルウエハなどの単結晶半導体ハンドル基板は、比較的高い最小バルク抵抗率を有する。高抵抗率ウエハは、一般的に、チョクラルスキー法またはフローティングゾーン法によって成長した単結晶インゴットからスライスされる。Cz 成長シリコンウエハは、約 600 ～約 1000 の範囲の温度で熱アニールを受け、結晶成長中に取り込まれた酸素によって引き起こされた熱ドナーを消滅させてよい。いくつかの具体例では、単結晶半導体ハンドルウエハは、少なくとも約 1000 cm<sup>-3</sup>、少なくとも約 10000 cm<sup>-3</sup>、少なくとも約 5000 cm<sup>-3</sup>、少なくとも約 10000 cm<sup>-3</sup>、または更には少なくとも約 30000 cm<sup>-3</sup>、例えば約 10000 cm<sup>-3</sup>～約 10000000 cm<sup>-3</sup>、または約 50000 cm<sup>-3</sup>～約 10000000 cm<sup>-3</sup>、または約 10000000 cm<sup>-3</sup>～約 10000000 cm<sup>-3</sup>、または約 5000000 cm<sup>-3</sup>～約 10000000 cm<sup>-3</sup>、または約 7500000 cm<sup>-3</sup>～約 10000000 cm<sup>-3</sup>、または約 10000000 cm<sup>-3</sup>～約 10000000 cm<sup>-3</sup>、約 20000000 cm<sup>-3</sup>～約 10000000 cm<sup>-3</sup>、または約 30000000 cm<sup>-3</sup>～約 10000000 cm<sup>-3</sup>、または約 30000000 cm<sup>-3</sup>～約 50000000 cm<sup>-3</sup>などの最小バルク抵抗率を有する。高抵抗率ウエハを製造する方法は、当該技術分野において公知であり、そのような高抵抗率ウエハは、SunEdison Semiconductor Ltd (ミズーリ州セントピーターズ、元MEMC Electronic Materials, Inc) などの商業的供給業者から得ることができる。

20

## 【0029】

30

いくつかの具体例では、単結晶半導体ハンドル基板は、p 型または n 型のドーパントを含む。適切なドーパントは、砒素、リン、およびホウ素を含む。いくつかの具体例では、単結晶半導体ハンドル基板は、p 型ドーパントを含む。いくつかの具体例では、単結晶半導体ハンドル基板は、ホウ素などの p 型ドーパントを含む単結晶シリコンウエハである。ホウ素ドーパントは、例えば  $1 \times 10^{14}$  atoms/cm<sup>3</sup>、好適には  $1 \times 10^{13}$  atoms/cm<sup>3</sup> の比較的低い濃度で存在し、高抵抗率ハンドル基板を得る。

40

## 【0030】

いくつかの具体例では、単結晶半導体ハンドルウエハの表面は、サンドブラストプロセスまたは腐食性エッティングによって意図的に損傷され得る。いくつかの具体例では、単結晶半導体ハンドルウエハの表面は、電荷トラップ層の堆積前に、熱酸化（そこで単結晶半導体材料の一部が消費される）および / または CVD 酸化物堆積などの従来の酸化方法によって酸化されてもよい。

## 【0031】

50

本発明の方法によると、電荷トラップ層は、単結晶半導体ハンドル基板の表面上に堆積される。いくつかの具体例では、半導体材料は、選択的に露光酸化表面層を含み得る単結

晶半導体ハンドルウエハの露光表面の上に堆積される。半導体・オン・インシュレータデバイスの中に電荷トラップ層を形成する際に使用するのに適切な半導体材料は、製造されたデバイスの中に、高度に欠陥のある層を適切に形成することができる。そのような材料は、単結晶半導体材料、多結晶半導体材料、およびアモルファス半導体材料を含む。単結晶、多結晶、またはアモルファスの半導体材料は、シリコン、ゲルマニウム、またはシリコンとゲルマニウムとの組合せを含む。シリコン、ゲルマニウム、またはシリコンとゲルマニウムとの組合せを含む単結晶半導体材料は、当該技術分野において慣用されているエピタキシャル技術によって堆積されてもよい。多結晶材料は、ランダム結晶配向を有する小さな結晶を含む材料を意味する。多結晶質粒子は、約 20 ナノメートルほどの小さいサイズであってもよい。本発明の方法によると、堆積された多結晶材料の結晶粒径が小さいほど、電荷トラップ層の欠陥率が高くなる。アモルファス材料は、シリコンおよびゲルマニウムの非晶同素体を含み、短距離秩序および長距離秩序を欠くものである。約 10 ナノメートル未満の結晶化度を有する粒も、本質的にアモルファスであると考えられる。多結晶材料およびアモルファス材料は、有機金属化学気相堆積 (MOCVD)、物理気相堆積 (PVD)、化学気相堆積 (CVD)、定圧化学気相堆積 (LPCVD)、プラズマ増殖型化学気相堆積 (PECVD)、または分子線エピタキシャル (MBE) を用いて堆積されてもよい。シリコンゲルマニウムは、任意のモル比のシリコンとゲルマニウムのシリコングルマニウムの合金を含む。シリコンおよびゲルマニウムを含む半導体材料は、炭素ドープされてもよい。好適には、電荷トラップ層は、少なくとも約 1000 . cm、または少なくとも約 3000 . cm、例えば約 1000 . cm ~ 約 100,000 . cm、約 1000 . cm ~ 約 10,000 . cm、約 3000 . cm ~ 約 10,000 . cm、または約 3000 . cm ~ 約 5000 . cm などの抵抗率を有する。

### 【0032】

いくつかの具体例では、特に単結晶半導体ハンドル基板上に多結晶シリコン電荷トラップ層が統いて堆積される具体例では、半導体材料は、シリコンおよびゲルマニウムを含むが、ここでゲルマニウムのモルパーセントは、少なくとも 20 モル% である。いくつかの具体例では、半導体材料は、シリコンおよびゲルマニウムを含むが、ここでゲルマニウムのモルパーセントは、少なくとも約 50 モル%、少なくとも約 90 モル%、例えば少なくとも約 99.9 % である。いくつかの具体例では、半導体材料は、本質的にゲルマニウムから成る。ここでは、本質的にゲルマニウムから成る半導体材料は、ゲルマニウム前駆体を用いた堆積によって形成される。本質的にゲルマニウムから成る最終的な半導体材料は、約 0.1 モル% 未満、好適には約 0.01 モル% 未満の微量不純物を含むが、これは好適にはゲルマニウム層の物理的および電気的性質に影響を与えない。シリコン、ゲルマニウム、またはシリコンとゲルマニウムとの組合せを含む半導体材料は、臨界厚さ、すなわち、ひずみ緩和熱アニールの間に格子不整合による弾性ひずみが緩和され得る厚さを超える厚さまで堆積されてもよい。臨界厚さは、ゲルマニウム濃度に依存してもよい。ゲルマニウム濃度が低くなれば、臨界厚さは大きくなる。したがって、シリコンと少なくとも約 20 モル% の Ge を有するゲルマニウムとを含む堆積された半導体層は、一般的に、約 1 ナノメートル ~ 約 3000 ナノメートル、例えば約 10 ナノメートル ~ 約 3000 ナノメートル、約 10 ナノメートル ~ 約 1000 ナノメートルの厚さまで堆積される。Ge 濃度が増加するにつれて、臨界厚さはより小さくなり得る。100 モル% の Ge 層については、厚さは、約 0.1 ナノメートル ~ 約 1000 ナノメートル、例えば約 1 ナノメートル ~ 約 1000 ナノメートル、または約 10 ナノメートル ~ 約 500 ナノメートルである。

### 【0033】

いくつかの具体例では、半導体層は、シリコンおよびゲルマニウムを含むが、ここでゲルマニウム含有量は、少なくとも約 5 モル% である。いくつかの具体例では、半導体層は、シリコンおよびゲルマニウムを含むが、ここでゲルマニウム含有量は、約 20 モル% 未満、例えば約 5 モル% ~ 約 20 モル% である。いくつかの具体例では、ゲルマニウムリッチシリコン層は、単結晶半導体ハンドル基板の表面上に堆積され、単独で電荷トラップ層

として機能する。より低い濃度のGeでは、例えば約5ナノメートル～約4000ナノメートル、または約10ナノメートル～約3000ナノメートル、または約20ナノメートル～約1000ナノメートルなど、緩和を確実にするために層をより厚く堆積させてもよい。いくつかの具体例では、ゲルマニウムリッチシリコン層は、約0.1モル%～約5モル%、例えば約0.5モル%～約1モル%の炭素を含んでもよい。そのような具体例では、層は、約10ナノメートル～約8000ナノメートル、または約10ナノメートル～約6000ナノメートル、または約20ナノメートル～約3000ナノメートルの厚さを有してもよい。

#### 【0034】

単結晶半導体ハンドルウェハの表面上に堆積されて電荷トラップ層を形成するための材料は、当該技術分野において公知の方法によって堆積されてもよい。例えば、半導体材料は、エピタキシャル堆積、有機金属化学気相堆積(MOCVD)、物理気相堆積(PVD)、化学気相堆積(CVD)、定圧化学気相堆積(LPCVD)、プラズマ増殖型化学気相堆積(PECVD)、または分子線エピタキシャル(MBE)を用いて堆積されてもよい。LPCVDまたはPECVDのためのシリコン前駆体は、特に、メチルシラン、シリコンテトラハイドライド(シラン)、トリシラン、ジシラン、ペンタシラン、ネオペンタシラン、テトラシラン、ジクロロシラン(SiH<sub>2</sub>C<sub>1</sub><sub>2</sub>)、四塩化ケイ素(SiC<sub>1</sub><sub>4</sub>)を含む。例えば、多結晶シリコンは、約550～約690、例えば約580～約650の温度範囲内でシラン(SiH<sub>4</sub>)を熱分解することによって、表面酸化層の上に堆積されてもよい。チャンバ圧力は、約70～400mTorrの範囲であってもよい。アモルファスシリコンは、一般的に約75～約300の範囲の温度で、プラズマ増殖型化学気相堆積(PECVD)によって堆積されてもよい。シリコンゲルマニウム、特にアモルファスシリコンゲルマニウムは、イソブチルゲルマン、アルキルゲルマニウムトリクロライド、およびジメチルアミノゲルマニウムトリクロライドなどの有機ゲルマニウム化合物を含むことによって、化学気相堆積によって、約300までの温度で堆積されてもよい。炭素でドープされたシリコンは、四塩化ケイ素およびメタンのような前駆体を使用するエピタキシャルリアクタの中で、熱プラズマ化学気相堆積によって堆積されてもよい。CVDまたはPECVDのための適切な炭素前駆体は、特に、メチルシラン、メタン、エタン、エチレンを含む。LPCVD堆積に対しては、メチルシランは、炭素およびシリコンの両方を提供するので特に好ましい前駆体である。PECVD堆積に対しては、好ましい前駆体は、シランおよびメタンを含む。

#### 【0035】

いくつかの具体例では、シリコン、ゲルマニウム、またはシリコンおよびゲルマニウムを含む半導体材料の層の堆積の後、選択的に、単結晶半導体ハンドル基板は、シリコン、ゲルマニウム、またはシリコンおよびゲルマニウムを含む半導体材料を少なくとも部分的に緩和しまたは完全に緩和するのに十分な温度および時間でアニールされてもよい。弾性ひずみは、高温で緩和し始める。緩和は、層と高抵抗率半導体ハンドル基板との間の界面にミスフィット転位を生成することによって実現される。アニールの後、高密度の、すなわち約 $1 \times 10^{-5}$ ～ $1 \times 10^{-10} / \text{cm}^2$ のミスフィット転位および貫通転位が存在する。緩和アニールは、600を超える温度、例えば約700～約900で生じてもよい。緩和アニールは、約1秒～約1時間の期間、例えば約10秒～約30分、例えば約1分～約30分の期間行われてもよい。

#### 【0036】

いくつかの具体例では、多結晶シリコン層は、シリコン、ゲルマニウム、またはシリコンおよびゲルマニウムを含む半導体材料の緩和層の上に堆積されてもよい。多結晶シリコン層は、適切なシリコン前駆体および条件を使用して、上記のように堆積されてもよい。シリコン、ゲルマニウム、またはシリコンおよびゲルマニウムを含む半導体材料の緩和層と多結晶シリコン層との組合せは、電荷トラップ層として機能する。有利には、SiGeを含むか、または本質的にGeから成る完全緩和層は、高抵抗率ハンドルウェハと多結晶シリコン層との間に形成され、SOI製造の中に含まれる高温プロセスステップの間、多

10

20

30

40

50

結晶シリコン電荷トラップ層の再結晶化を防止する転位ネットワークを提供する。多結晶シリコン層は、約0.5マイクロメートル～約3マイクロメートル、または約1マイクロメートル～約3マイクロメートルの厚さまで堆積されてもよい。

### 【0037】

いくつかの具体例では、シリコン、ゲルマニウム、またはシリコンとゲルマニウムの両方を含む半導体材料の層の堆積、および多結晶シリコン膜の選択的な堆積の後、選択的に、堆積された電荷トラップ層の上に酸化膜が形成される。これは、熱酸化（そこで堆積された半導体材料膜の一部が消費される）および／またはCVD酸化物堆積などの当該技術分野で公知の手段によって達成されてもよい。いくつかの具体例では、電荷トラップ層が熱酸化されてもよく（そこで堆積された半導体材料膜の一部が消費される）、または二酸化シリコン膜がCVD酸化物堆積によって成長してもよい。いくつかの具体例では、単結晶半導体ハンドル基板の表面上に堆積された電荷トラップ層は、ASM A400などの炉の中で熱酸化されてもよい。その温度は、酸化雰囲気中で750～1200の範囲であってもよい。酸化周囲雰囲気は、ArまたはN<sub>2</sub>、およびO<sub>2</sub>などの不活性気体の混合物であってもよい。酸素含有量は、1%から10%またはそれ以上まで変化してもよい。いくつかの具体例では、酸化周囲雰囲気は、100%に達してもよい（「ドライ酸化」）。例示的な具体例では、半導体ハンドルウエハは、垂直炉内に装填されてもよい。N<sub>2</sub>とO<sub>2</sub>の混合物を設けて温度を酸化温度まで上昇させる。所望の酸化物厚が得られた後、O<sub>2</sub>がオフにされ、炉の温度が下げられ、炉からウエハが取り出される。界面層の中に窒素を組み込んで窒化シリコンまたは酸窒化シリコンを堆積させるために、雰囲気は、窒素単体または酸素と窒素の組合せを含んでもよく、温度は、1100～1400まで上げられてもよい。代替的な窒素源は、アンモニアである。いくつかの具体例では、電荷トラップ層は、十分な時間にわたって酸化され、少なくとも約0.01マイクロメートルの厚さ、または少なくとも約0.05マイクロメートルの厚さ、例えば約0.05マイクロメートル～約4マイクロメートル、例えば約0.1マイクロメートル～約2マイクロメートル、または約0.2マイクロメートル～約0.4マイクロメートルの厚さの酸化物層を提供してもよい。シリコンゲルマニウムまたはゲルマニウムを含む膜の酸化は、酸化物層と単結晶シリコンハンドル基板の表面との界面でGeを濃縮させ得る。これにより、酸化物と基板との間のGe濃度が非常に高くなる。次に、Siの酸化は、Geリッチ層を通して拡散するSiによって進行する。このようにして、SOIウエハの所望の構造が形成される。酸化プロセスは、更に、単結晶半導体ハンドルウエハの裏面を酸化させ、有利には、シリコンと二酸化シリコンの異なる熱膨張係数によって潜在的に引き起こされる反りおよび湾曲を減少させる。

### 【0038】

電荷トラップ層の堆積、および選択的な酸化の後、ウエハ洗浄は選択的である。必要に応じて、ウエハは、例えば標準的なSC1/SC2溶液の中で洗浄可能である。さらに、ウエハは、特に、電荷トラップ層の上の二酸化シリコン層は、化学機械研磨（CMP）を受け、表面粗さを、好適にはRMS<sub>2x2 um<sup>2</sup></sub>が約5オングストローム以下であるレベルまで、減少させる。ここで、二乗平均平方根は、

$$R_g = \sqrt{\frac{1}{n} \sum_{i=1}^n y_i^2}$$

であり、粗さプロファイルは、トレースに沿って規則的に等間隔に配置された点を含み、y<sub>i</sub>は、平均線からデータポイントまでの垂直距離である。

### 【0039】

電荷トラップ層、および選択的に酸化膜を含む、本明細書に記載された方法によって製造された単結晶半導体ハンドルウエハは、次に、従来の層転写方法によって製造される単結晶半導体ドナー基板、例えば単結晶半導体ドナーウエハに接合される。すなわち、単結晶半導体ドナーウエハは、酸化、注入、および注入後の洗浄を含む標準的なプロセスス

10

20

30

40

50

ステップを受けてもよい。したがって、多層半導体構造の製造において従来から使用されている材料の単結晶半導体ウエハなどの単結晶半導体ドナー基板、例えば単結晶シリコンドナーウエハは、エッティングされ、研磨され、選択的に酸化されたものであるが、イオン注入されて、ドナー基板の中にダメージ層を形成する。

#### 【0040】

いくつかの具体例では、単結晶半導体ドナー基板の表面が熱酸化されてもよく（そこで半導体材料の一部が消費される）、または二酸化シリコン膜がCVD酸化物堆積によって成長してもよい。いくつかの具体例では、単結晶半導体ドナー基板、例えば単結晶シリコンドナーウエハは、ASM A400などの炉の中で熱酸化されてもよい。その温度は、酸化雰囲気中で750～1200の範囲であってもよい。<sup>10</sup> 酸化周囲雰囲気は、ArまたはN<sub>2</sub>、およびO<sub>2</sub>などの不活性気体の混合物であってもよい。酸素含有量は、1%から10%またはそれ以上まで変化してもよい。いくつかの具体例では、酸化周囲雰囲気は、100%に達してもよい（「ドライ酸化」）。例示的な具体例では、半導体ドナーウエハは、垂直炉内に装填されてもよい。N<sub>2</sub>とO<sub>2</sub>の混合物を設けて温度を酸化温度まで上昇させる。所望の酸化物厚が得られた後、O<sub>2</sub>がオフにされ、炉の温度が下げられ、炉からウエハが取り出される。いくつかの具体例では、ドナー基板は、酸化されて、表面層の上に少なくとも約1ナノメートル、例えば約0.01マイクロメートル～約10マイクロメートル、例えば約0.01マイクロメートル～約2マイクロメートル、または約0.1マイクロメートル～約1マイクロメートルの厚さの酸化物層を提供する。<sup>20</sup> 酸化プロセスは、更に、ドナー基板の裏面を酸化させ、有利には、シリコンと二酸化シリコンの異なる熱膨張係数によって潜在的に引き起こされる反りおよび湾曲を減少させる。

#### 【0041】

単結晶半導体ドナー基板のイオン注入は、Applied Materials Quantum Hなどの商業的に入手可能な機器によって実行されてもよい。注入されるイオンは、He、H、H<sub>2</sub>、またはそれらの組合せを含む。イオン注入は、半導体ドナー基板の中にダメージ層を形成するのに十分な密度および時間で実行される。注入密度は、約10<sup>12</sup> ions/cm<sup>2</sup>から約10<sup>17</sup> ions/cm<sup>2</sup>まで、例えば約10<sup>14</sup> ions/cm<sup>2</sup>から約10<sup>17</sup> ions/cm<sup>2</sup>まで変動してもよい。<sup>30</sup> 注入エネルギーは、約1keVから約3000keVまで、例えば約10keVから約3000keVまで変動してもよい。いくつかの具体例では、注入後に、単結晶半導体ドナーウエハ、例えば単結晶シリコンドナーウエハを清浄することが望ましい場合がある。いくつかの好適な具体例では、洗浄は、ピラニア洗浄とそれに続くDI水すすぎおよびSC1/SC2洗浄を含む。

#### 【0042】

本発明のいくつかの具体例では、ヘリウムイオンおよび/または水素イオンの注入によって形成されたイオン注入領域を有する単結晶半導体ドナー基板は、単結晶半導体ドナー基板内に熱的に活性化した劈開面を形成するのに十分な温度でアニールされる。適切なツールの例は、Blue Mモデルなどの単純なボックス炉である。いくつかの好適な具体例では、イオン注入単結晶半導体ドナー基板は、約200～約350、約225～約325、好適には約300の温度でアニールされる。熱アニールは、約2時間～約10時間、例えば約2時間～約8時間の期間行われてもよい。これらの温度範囲内での熱アニールは、熱的に活性化した劈開面を形成するのに十分である。劈開面を活性化させるための熱アニールの後、単結晶半導体ドナー基板表面は、好適には洗浄される。<sup>40</sup>

#### 【0043】

いくつかの具体例では、イオン注入され、および選択的に洗浄され、および選択的にアニールされた単結晶半導体ドナー基板は、酸素プラズマおよび/または窒素プラズマ表面活性化を受ける。いくつかの具体例では、酸素プラズマ表面活性化ツールは、EVG（登録商標）810LT低温プラズマ活性化システムなど、EVグループから入手可能なものなどの商業的に入手可能なツールである。イオン注入され、選択的に洗浄された単結晶半導体ドナーウエハは、チャンバに装填される。チャンバは排気され、および大気圧よりも低い圧力までO<sub>2</sub>で再充填され、それによってプラズマを生成する。単結晶半導体ドナー<sup>50</sup>

ウエハは、約1秒～約120秒の範囲の所望の時間、このプラズマに暴露される。酸素プラズマ表面酸化が行われ、単結晶半導体ドナー基板の表面を親水性にし、前述の方法によって製造された単結晶半導体ハンドル基板への接合を受けさせる。

#### 【0044】

単結晶半導体ドナー基板の親水性表面および単結晶半導体ハンドル基板の表面は、電荷トラップ層を含み、かつ更に選択的に酸化されてもよいものであるが、次に、密接に接触させられて、それによって接合構造を形成する。機械的接合は比較的弱いので、接合構造は、更にアニールされて、ドナーウエハとハンドルウエハとの間の接合を固める。本発明のいくつかの具体例では、接合構造は、単結晶半導体ドナー基板の中に熱的に活性化した劈開面を形成するのに十分な温度でアニールされる。適切なツールの例は、Blue Modelなどの単純なボックス炉である。いくつかの好適な具体例では、接合構造は、約200～約350、約225～約325、好適には約300の温度でアニールされる。熱アニールは、約0.5時間～約10時間の期間、好適には約2時間の期間行われてもよい。これらの温度範囲内での熱アニールは、熱的に活性化した劈開面を形成するのに十分である。劈開面を活性化させるための熱アニールの後、接合構造は、洗浄されてもよい。

#### 【0045】

熱アニールの後、単結晶半導体ドナー基板と単結晶半導体ハンドル基板との間の接合は、十分強く、劈開面で接合構造を劈開することによって層転写を開始する。劈開は、当該技術分野において公知の技術によって生じてもよい。いくつかの具体例では、接合構造は、一方の側に固定された吸着カップに取り付けられ、かつ他方の側のヒンジ付きアーム上の追加の吸着カップによって取り付けられた従来の劈開ステーションの中に配置されてもよい。亀裂は、吸着カップアタッチメントの近くで発生し、可動アームがヒンジを中心にして回してウエハを劈開する。劈開は、半導体ドナーウエハの一部を除去し、それによって半導体・オン・インシュレータ複合構造上に半導体デバイス層、好適にはシリコンデバイス層が残る。

#### 【0046】

劈開の後、劈開構造は、高温アニールを受け、転写デバイス層と単結晶半導体ハンドル基との間の接合を更に強化してもよい。適切なツールの例は、ASM A400などの垂直炉である。いくつかの好適な具体例では、接合構造は、約1000～約1200、好適には約1000の温度でアニールされる。熱アニールは、約0.5時間～約8時間の期間、好適には約4時間の期間行われる。これらの温度範囲内における熱アニールは、転写デバイス層と単結晶半導体ハンドル基との間の接合を強化するのに十分である。

#### 【0047】

劈開と高温アニールの後、接合構造は、表面から薄い熱酸化物を取り除き、微粒子を洗い流すように設計された洗浄プロセスを施されてもよい。いくつかの具体例では、H<sub>2</sub>をキャリアガスとして使用する水平流の枚葉式(single wafer)エピタキシャルリアクタの中で気相HC1エッチング処理を行うことによって、単結晶半導体ドナーウエハを所望の厚さおよび平滑さにすることができる。いくつかの具体例では、デバイス層の厚さは、約1ナノメートル～約100マイクロメートル、例えば約10ナノメートル～約50マイクロメートルであってもよい。いくつかの具体例では、エピタキシャル層は、転写デバイス層の上に堆積されてもよい。出来上がったSOIウエハは、半導体ハンドル基板、電荷トラップ層、誘電体層(例えば埋め込み酸化物層)、および半導体デバイス層を含み、そしてライン計測検査工程を受け、最終的に典型的なSC1-SC2プロセスを使用して洗浄されてもよい。

#### 【0048】

本発明によると、SOIウエハは、BOXの下に埋め込まれた堆積半導体材料電荷トラップ層と共に得られる。ここで図3を参照すると、いくつかの具体例における、本発明のいくつかの具体例に係る半導体・オン・インシュレータ構造100、例えばシリコン・オン・インシュレータウエハが図示されている。半導体・オン・インシュレータ構造100

、例えばシリコン・オン・インシユレータウエハは、高抵抗率半導体基板 102、例えば高抵抗率単結晶シリコン基板を含む。緩和 SiGe または Ge 層 104 は、高抵抗率半導体基板 102、例えば高抵抗率単結晶シリコン基板の表面に界面接触して形成される。多結晶シリコン層 106 は、緩和 SiGe または Ge 層 104 の表面に界面接触して形成される。埋め込み酸化物層 108 は、緩和 SiGe または Ge 層 104 と单結晶半導体デバイス層 110、例えばシリコンデバイス層との間に配置される。埋め込み酸化物層 108 は、緩和 SiGe または Ge 層 104 および单結晶半導体デバイス層 110、例えばシリコンデバイス層の酸化部分から形成されてもよい。

#### 【0049】

ここで図 4 を参照すると、いくつかの具体例における、本発明のいくつかの具体例に係る半導体・オン・インシユレータ構造 200、例えばシリコン・オン・インシユレータウエハが図示されている。半導体・オン・インシユレータ構造 200、例えばシリコン・オン・インシユレータウエハは、高抵抗率半導体基板 202、例えば高抵抗率単結晶シリコン基板を含む。Ge リッチ層 204 は、高抵抗率半導体基板 202、例えば高抵抗率単結晶シリコン基板の表面に界面接触して形成される。埋め込み酸化物層 208 は、Ge リッチ層 204 と单結晶半導体デバイス層 210、例えばシリコンデバイス層との間に配置される。埋め込み酸化物層 208 は、Ge リッチ層 204 および单結晶半導体デバイス層 210、例えばシリコンデバイス層の酸化部分から形成されてもよい。

#### 【0050】

本発明を詳細に説明したが、添付の特許請求の範囲に規定された本発明の範囲から逸脱することなく、変更および変形が可能であることは明らかであろう。

#### 【0051】

本発明の範囲から逸脱することなく、上記の組成物およびプロセスにおいて様々な変更を行うことができるから、上記の説明に含まれるすべての事項は、例示的なものであり限定的な意味ではないものとして解釈されることが意図されている。

#### 【0052】

本発明またはその好適な具体例の要素を紹介する場合に、「ある (a)」、「ある (an)」、「その (the)」、および「上記 (said)」の冠詞は、1 またはそれ以上の要素があることを意味することを意図する。「含む (comprising)」、「含む (including)」、および「有する (having)」の用語は、包括的であることを意図し、列挙された要素以外の追加の要素も存在し得ることを意味する。

10

20

30

【図1】

FIG. 1

【図3】

FIG. 3

【図2】

FIG. 2

【図4】

FIG. 4

---

フロントページの続き

(72)発明者 イゴール・ペイドウス

アメリカ合衆国 6 3 3 7 6 ミズーリ州セント・ピータース、パール・ドライブ 5 0 1 番

(72)発明者 ルー・フェイ

アメリカ合衆国 6 3 3 7 6 ミズーリ州セント・ピータース、パール・ドライブ 5 0 1 番

(72)発明者 ジェフリー・ルイス・リパート

アメリカ合衆国 6 3 3 7 6 ミズーリ州セント・ピータース、パール・ドライブ 5 0 1 番

(72)発明者 アンドリュー・エム・ジョーンズ

アメリカ合衆国 6 3 3 7 6 ミズーリ州セント・ピータース、パール・ドライブ 5 0 1 番

(72)発明者 アレックス・ユーセンコ

アメリカ合衆国 6 3 3 7 6 ミズーリ州セント・ピータース、パール・ドライブ 5 0 1 番

(72)発明者 ワン・ガン

アメリカ合衆国 6 3 3 7 6 ミズーリ州セント・ピータース、パール・ドライブ 5 0 1 番

(72)発明者 ショーン・ジー・トーマス

アメリカ合衆国 6 3 3 7 6 ミズーリ州セント・ピータース、パール・ドライブ 5 0 1 番

(72)発明者 スリカント・コンム

アメリカ合衆国 6 3 3 7 6 ミズーリ州セント・ピータース、パール・ドライブ 5 0 1 番

審査官 宇多川 勉

(56)参考文献 特表 2 0 1 3 - 5 1 3 2 3 4 ( J P , A )

特開 2 0 0 7 - 2 1 4 1 9 9 ( J P , A )

(58)調査した分野( Int.CI. , DB名)

H 0 1 L 2 1 / 0 2

H 0 1 L 2 7 / 1 2