US 20130134393A1

### (19) United States

# (12) Patent Application Publication BERTIN

## (54) NANOTUBE FIELD EFFECT DEVICES AND METHODS OF MAKING SAME

(75) Inventor: Claude L. BERTIN, Venice, FL (US)

(73) Assignee: Nantero Inc., Woburn, MA (US)

(21) Appl. No.: 13/446,941

(22) Filed: Apr. 13, 2012

### Related U.S. Application Data

(63) Continuation of application No. 11/527,127, filed on Sep. 26, 2006, now abandoned.

### **Publication Classification**

(51) **Int. Cl.** *H01L 29/78* (2006.01)

(10) Pub. No.: US 2013/0134393 A1

(43) **Pub. Date:** May 30, 2013

### (57) ABSTRACT

Methods of making non-volatile field effect devices and arrays of same. Under one embodiment, a method of making a non-volatile field effect device includes providing a substrate with a field effect device formed therein. The field effect device includes a source, drain and gate with a field-modulatable channel between the source and drain. An electromechanically-deflectable, nanotube switching element is formed over the field effect device. Terminals and corresponding interconnect are provided to correspond to each of the source, drain and gate such that the nanotube switching element is electrically positioned between one of the source, drain and gate and its corresponding terminal, and such that the others of said source, drain and gate are directly connected to their corresponding terminals.

# Column 2: SWITCH OPEN SMALL SIGNAL CIRCUIT OPERATION (FED Controllable Source) $\rm V_{\rm DD}$ $\rm V_{\rm DD}$ $\rm V_{\rm DD}$ $V_{\text{T2}} = V_{\text{OUT}}$ Figure 6 Column 1: SWITCH CLOSED $V_{T2} = V_{OUT}$ $V_{ m DD}$ $\circ$ $V_{ m DD}$

$V_{

m DD}$

$V_{

m DD}$

$V_{OUT} = V_{T2}$

0

$V_{OUT} = V_{T2} \,$

# CIRCUIT OPERATION (FULL VOLTAGE SWING)

365

Figure 12

Figure 30AX

Figure 54

Figure 56A

# NANOTUBE FIELD EFFECT DEVICES AND METHODS OF MAKING SAME

# CROSS REFERENCE TO RELATED APPLICATIONS

[0001] This application is a continuation of and claims priority under 35 U.S.C. §120 to U.S. patent application Ser. No. 11/527,127 filed Sep. 16, 2006 and entitled Method of Making Non-Volatile Field Effect Devices and Arrays of Same, the entire contents of which are incorporated herein by reference in their entirety, which claims priority under 35 U.S.C. §120 to U.S. patent application Ser. No. 10/864,751, filed Jun. 9, 2004 and entitled Method of Making Non-Volatile Field Effect Devices and Arrays of Same, the entire contents of which are incorporated herein by reference, which claims priority under 35 U.S.C. §119(e) to U.S. Provisional Patent Application No. 60/476,976, filed on Jun. 9, 2003, entitled Non-Volatile Electromechanical Field Effect Transistors and Methods of Forming Same, which is incorporated herein by reference in its entirety, and which is related to the following U.S. applications, the contents of which are incorporated herein in their entirety by reference:

[0002] U.S. patent application Ser. No. 10/810,962, filed Mar. 26, 2004, entitled NRAM Bit Selectable Two-Device Nanotube Array;

[0003] U.S. patent application Ser. No. 10/810,963, filed Mar. 26, 2004, entitled NRAM Byte/Block Released Bit Selectable One-Device Nanotube Array;

[0004] U.S. patent application Ser. No. 10/811,191, filed Mar. 26, 2004, entitled Single Transistor With Integrated Nanotube (NT-FET); and

[0005] U.S. patent application Ser. No. 10/811,373, filed Mar. 26, 2004, entitled Nanotube-On-Gate FET Structures and applications.

## **BACKGROUND**

[0006] 1. Technical Field

[0007] The present invention relates to field effect devices having non-volatile behavior as a result of control structures having nanotube components and to methods of forming such devices.

[0008] 2. Discussion of Related Art

[0009] Semiconductor MOSFET transistors are ubiquitous in modern electronics. These field effect devices possess the simultaneous qualities of bistability, high switching speed, low power dissipation, high-reliability, and scalability to very small dimensions. One feature not typical of such MOSFET-based circuits is the ability to retain a digital state (i.e. memory) in the absence of applied power; that is, the digital state is volatile.

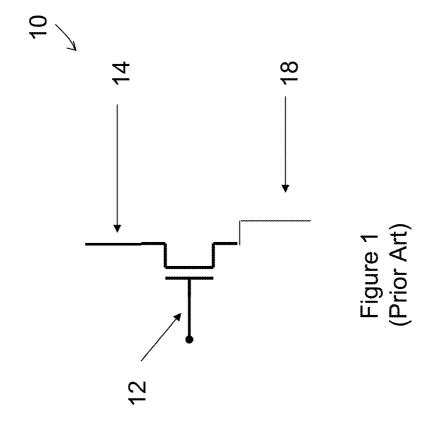

[0010] FIG. 1 depicts a prior art field effect transistor 10. The transistor 10 includes a gate node 12, a drain node 14, and a source node 18. Typically, the gate node 12 is used to control the device. Specifically, by applying an adequate voltage to the gate node 12 an electric field is caused that creates a conductive path between the drain 14 and source 18. In this sense, the transistor is referred to as switching on.

[0011] Currently, most memory storage devices utilize a wide variety of energy dissipating devices which employ the confinement of electric or magnetic fields within capacitors or inductors respectively. Examples of state of the art circuitry used in memory storage include FPGA, CPLD, ASIC, CMOS, ROM, PROM, EPROM, EPROM, DRAM, MRAM

and FRAM, as well as dissipationless trapped magnetic flux in a superconductor and actual mechanical switches, such as relays.

[0012] An FPGA (Field Programmable Gate Array) or a CPLD (Complex Programmable Logic Device) is a programmable logic device (PLD), a programmable logic array (PLA), or a programmable array logic (PAL) with a high density of gates, containing up to hundreds of thousands of gates with a wide variety of possible architectures. The ability to modulate (i.e. effectively to open and close) electrical circuit connections on an IC (i.e. to program and reprogram) is at the heart of the FPGA (Field programmable gate array) concept.

[0013] An ASIC (Application Specific Integrated Circuit) chip is custom designed (or semi-custom designed) for a specific application rather than a general-purpose chip such as a microprocessor. The use of ASICs can improve performance over general-purpose CPUs, because ASICs are "hardwired" to do a specific job and are not required to fetch and interpret stored instructions.

[0014] Important characteristics for a memory cell in electronic device are low cost, nonvolatility, high density, low power, and high speed. Conventional memory solutions include Read Only Memory (ROM), Programmable Read only Memory (PROM), Electrically Programmable Memory (EPROM), Electrically Programmable Read Only Memory (EEPROM), Dynamic Random Access Memory (DRAM) and Static Random Access Memory (SRAM).

[0015] ROM is relatively low cost but cannot be rewritten. PROM can be electrically programmed but with only a single write cycle. EPROM (Electrically-erasable programmable read-only memories) has read cycles that are fast relative to ROM and PROM read cycles, but has relatively long erase times and reliability only over a few iterative read/write cycles. EEPROM (or "Flash") is inexpensive, and has low power consumption but has long write cycles (ms) and low relative speed in comparison to DRAM or SRAM. Flash also has a finite number of read/write cycles leading to low long-term reliability. ROM, PROM, EPROM and EEPROM are all non-volatile, meaning that if power to the memory is interrupted the memory will retain the information stored in the memory cells.

[0016] DRAM (dynamic random access memory) stores charge on capacitors but must be electrically refreshed every few milliseconds complicating system design by requiring separate circuitry to "refresh" the memory contents before the capacitors discharge. SRAM does not need to be refreshed and is fast relative to DRAM, but has lower density and is more expensive relative to DRAM. Both SRAM and DRAM are volatile, meaning that if power to the memory is interrupted the memory will lose the information stored in the memory cells.

[0017] Consequently, existing technologies are either non-volatile but are not randomly accessible and have low density, high cost, and limited ability to allow multiple writes with high reliability of the circuit's function, or they are volatile and complicate system design or have low density. Some emerging technologies have attempted to address these short-comings.

[0018] For example, magnetic RAM (MRAM) or ferromagnetic RAM (FRAM) utilizes the orientation of magnetization or a ferromagnetic region to generate a nonvolatile memory cell. MRAM utilizes a magnetoresistive memory element involving the anisotropic magnetoresistance or giant

magnetoresistance of ferromagnetic materials yielding non-volatility. Both of these types of memory cells have relatively high resistance and low-density. A different memory cell based upon magnetic tunnel junctions has also been examined but has not led to large-scale commercialized MRAM devices. FRAM uses circuit architecture similar to DRAM but which uses a thin film ferroelectric capacitor. This capacitor is purported to retain its electrical polarization after an externally applied electric field is removed yielding a non-volatile memory. FRAM suffers from a large memory cell size, and it is difficult to manufacture as a large-scale integrated component. See U.S. Pat. Nos. 4,853,893; 4,888,630; 5,198,994, 6,048,740; and 6,044,008.

[0019] Another technology having non-volatile memory is phase change memory. This technology stores information via a structural phase change in thin-film alloys incorporating elements such as selenium or tellurium. These alloys are purported to remain stable in both crystalline and amorphous states allowing the formation of a bi-stable switch. While the nonvolatility condition is met, this technology appears to suffer from slow operations, difficulty of manufacture and poor reliability and has not reached a state of commercialization. See U.S. Pat. Nos. 3,448,302; 4,845,533; and 4,876,667.

[0020] Wire crossbar memory (MWCM) has also been proposed. See U.S. Pat. Nos. 6,128,214; 6,159,620; and 6,198, 655. These memory proposals envision molecules as bi-stable switches. Two wires (either a metal or semiconducting type) have a layer of molecules or molecule compounds sandwiched in between. Chemical assembly and electrochemical oxidation or reduction are used to generate an "ON" or "OFF" state. This form of memory requires highly specialized wire junctions and may not retain non-volatilely owing to the inherent instability found in redox processes.

[0021] Recently, memory devices have been proposed which use nanoscopic wires, such as single-walled carbon nanotubes, to form crossbar junctions to serve as memory cells. See WO 01/03208, Nanoscopic Wire-Based Devices, Arrays, and Methods of Their Manufacture; and Thomas Rueckes et al., "Carbon Nanotube-Based Nonvolatile Random Access Memory for Molecular Computing," Science, vol. 289, pp. 94-97, 7 Jul., 2000. Electrical signals are written to one or both wires to cause them to physically attract or repel relative to one another. Each physical state (i.e., attracted or repelled wires) corresponds to an electrical state. Repelled wires are an open circuit junction. Attracted wires are a closed state forming a rectified junction. When electrical power is removed from the junction, the wires retain their physical (and thus electrical) state thereby forming a nonvolatile memory cell.

[0022] The use of an electromechanical bi-stable device for digital information storage has also been suggested (c.f. U.S. Pat. No. 4,979,149: Non-volatile memory device including a micro-mechanical storage element).

[0023] The creation and operation of a bi-stable nano-electro-mechanical switches based on carbon nanotubes (including mono-layers constructed thereof) and metal electrodes has been detailed in a previous patent application of Nantero, Inc. (U.S. Pat. Nos. 6,574,130, 6,643,165, 6,706,402; U.S. patent application Ser. Nos. 09/915,093, 10/033,323, 10/033, 032, 10/128,117, 10/341,005, 10/341,055, 10/341,054, 10/341,130, 10/776,059, and 10/776,572, the contents of which are hereby incorporated by reference in their entireties).

#### **SUMMARY**

[0024] The invention provides methods of making non-volatile field effect devices and arrays of same.

[0025] Under one aspect of the invention, a method of making a non-volatile field effect device includes providing a substrate with a field effect device formed therein. The field effect device includes a source, drain and gate with a field-modulatable channel between the source and drain. An electromechanically-deflectable, nanotube switching element is formed over the field effect device. Terminals and corresponding interconnect are provided to correspond to each of the source, drain and gate such that the nanotube switching element is electrically positioned between one of the source, drain and gate and its corresponding terminal, and such that the others of said source, drain and gate are directly connected to their corresponding terminals.

[0026] Under another aspect of the invention, forming an electromechanically-deflectable, nanotube switching element includes forming an article from nanotube fabric.

[0027] Under another aspect of the invention, the nanotube fabric is a porous nanotube fabric.

[0028] Under another aspect of the invention, forming an electromechanically-deflectable, nanotube switching element includes forming a fourth terminal to control operation of said nanotube switching element.

[0029] Under another aspect of the invention, the fourth terminal is covered with a dielectric material on a surface facing the article of nanotube fabric.

[0030] Under another aspect of the invention, forming an electromechanically-deflectable, nanotube switching element includes forming an article of nanofabric that is positioned between the fourth terminal and the one of the source, drain and gate.

[0031] Under another aspect of the invention, forming an electromechanically-deflectable, nanotube switching element includes forming an article of nanofabric that is suspended between the fourth terminal and the one of the source, drain and gate.

[0032] Under another aspect of the invention, forming an electromechanically-deflectable, nanotube switching element includes forming an article of nanofabric that is positioned between the fourth terminal and the one of the source, drain and gate, and wherein there is a gap between the article and the fourth terminal.

[0033] Under another aspect of the invention, forming an electromechanically-deflectable, nanotube switching element includes forming an article of nanofabric that is positioned between the fourth terminal and the one of the source, drain and gate, and wherein there is a gap between the one of the source, drain and gate.

[0034] Under another aspect of the invention, forming an electromechanically-deflectable, nanotube switching element includes forming an article of nanofabric that is horizontally suspended relative to a horizontal substrate surface and wherein the article is electrically positioned between the fourth terminal and the one of the source, drain and gate.

[0035] Under another aspect of the invention, the article is formed to have a suspended length that is sub-lithographic.

[0036] Under another aspect of the invention, forming an electromechanically-deflectable, nanotube switching element includes forming an sacrificial layer and then forming a porous fabric of nanotubes thereover, said fabric subsequently being lithographically patterned and subsequent to

that said sacrificial material being removed to suspend the article with a gap existing where the sacrificial material previously existed.

[0037] Under another aspect of the invention, a second sacrificial layer is formed on a side of the patterned article opposite the side of the sacrificial layer, wherein both the sacrificial layer and the second sacrificial layer are removed to form gaps on either side of the article.

[0038] Under another aspect of the invention, the sacrificial material is anisotropically etchable.

[0039] Under another aspect of the invention, the sacrificial material is poly.

[0040] Under another aspect of the invention, a method of making a non-volatile field effect device includes providing a substrate with a field effect device formed therein. The field effect device includes a source, drain and gate with a field-modulatable channel between the source and drain. Terminals and corresponding interconnect are provided to correspond to each of the source, drain and gate. The drain and gate directly connected to their corresponding terminals. An electromechanically-deflectable, nanotube switching element is formed over the field effect device. The nanotube switching element is connected such that it is electrically positioned in series between the source and the terminal corresponding to the source.

[0041] Under another aspect of the invention, a method of making a non-volatile field effect device includes providing a substrate with a field effect device formed therein. The field effect device includes a source, drain and gate with a field-modulatable channel between the source and drain. Terminals and corresponding interconnect are provided to correspond to each of the source, drain and gate. The source and gate are directly connected to their corresponding terminals. An electromechanically-deflectable, nanotube switching element is formed over the field effect device. The nanotube switching element is connected such that it is electrically positioned in series between the drain and the terminal corresponding to the drain.

[0042] Under another aspect of the invention, a method of making a non-volatile field effect device includes providing a substrate with a field effect device formed therein. The field effect device includes a source, drain and gate with a field-modulatable channel between the source and drain. Terminals and corresponding interconnect are provided to correspond to each of the source, drain and gate. The source and drain are directly connected to their corresponding terminals. An electromechanically-deflectable, nanotube switching element is formed over the field effect device. The nanotube switching element is connected such that it is electrically positioned in series between the gate and the terminal corresponding to the gate.

#### BRIEF DESCRIPTION OF THE DRAWINGS

[0043] In the drawing,

[0044] FIG. 1 is a schematic of a prior art field effect transistor:

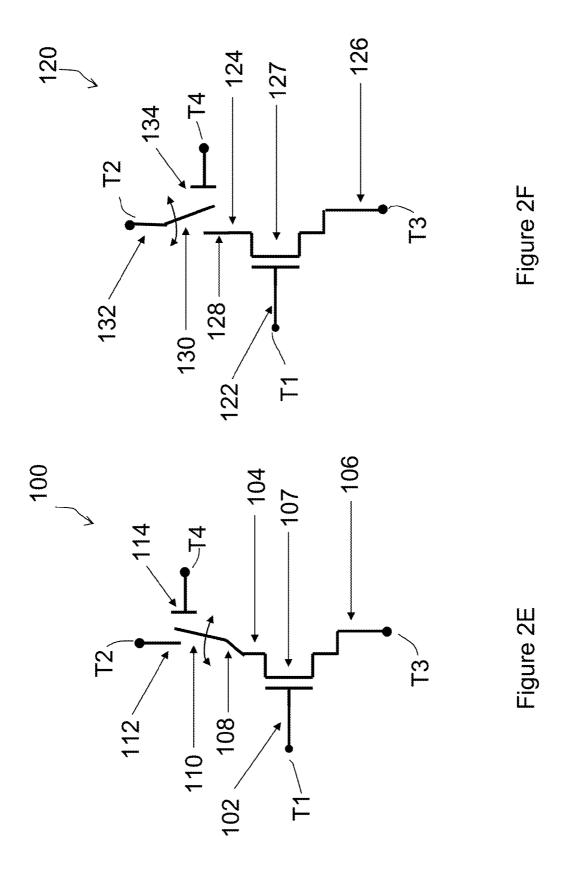

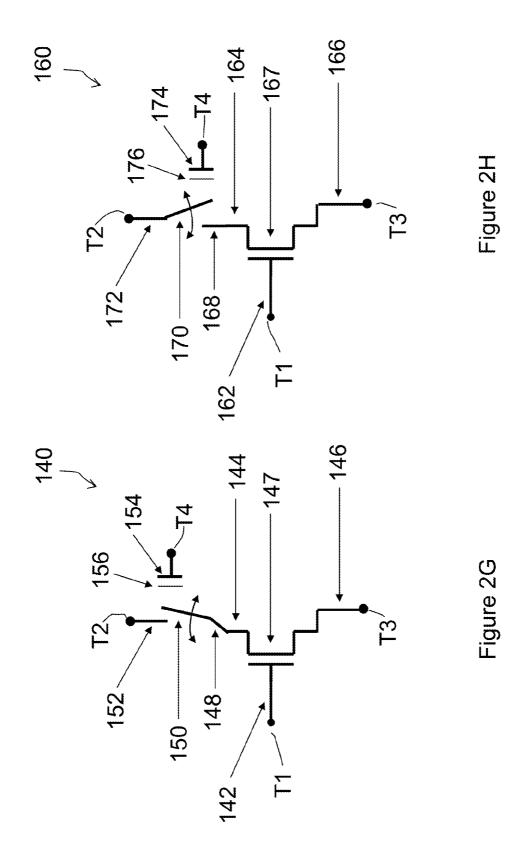

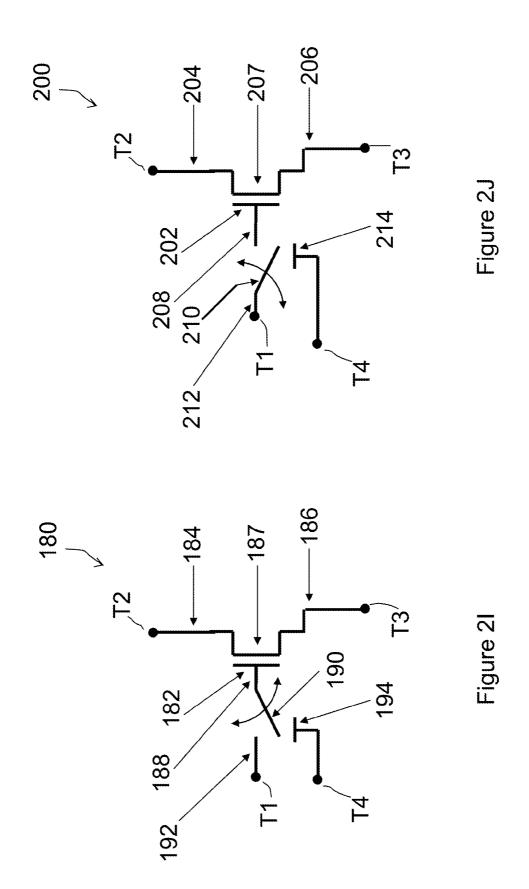

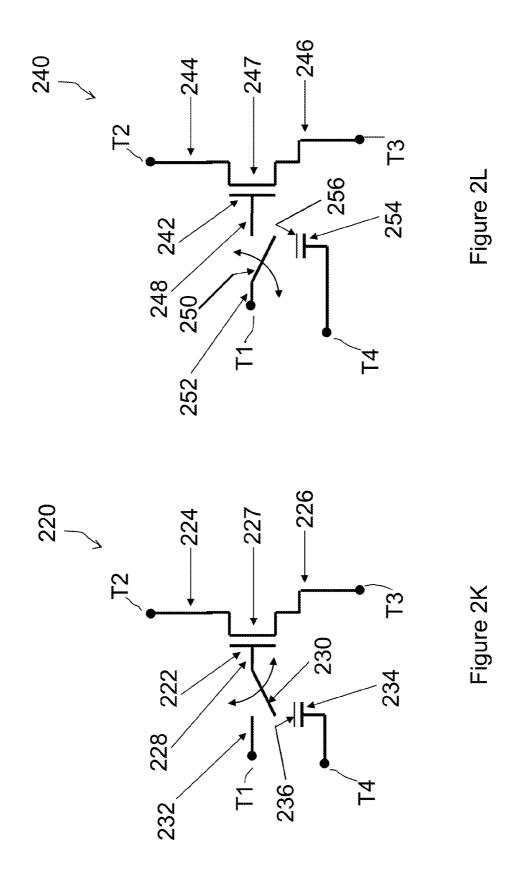

[0045] FIGS. 2A-L illustrate schematics of three models of preferred embodiments of the invention;

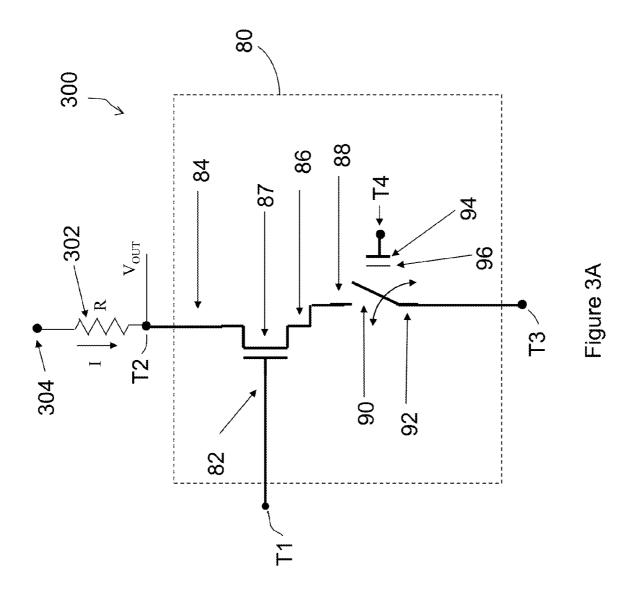

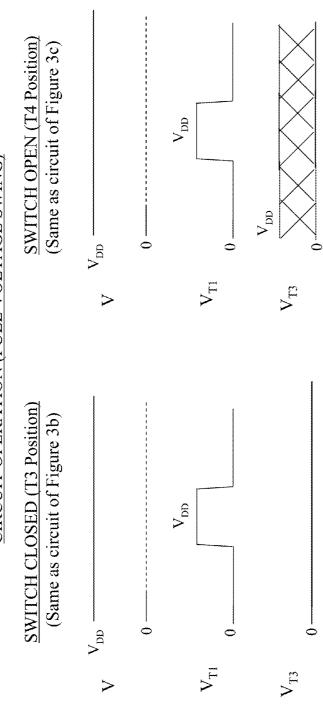

[0046] FIGS. 3A-C illustrate the operation of field effect devices with controllable sources for two of the FED configurations:

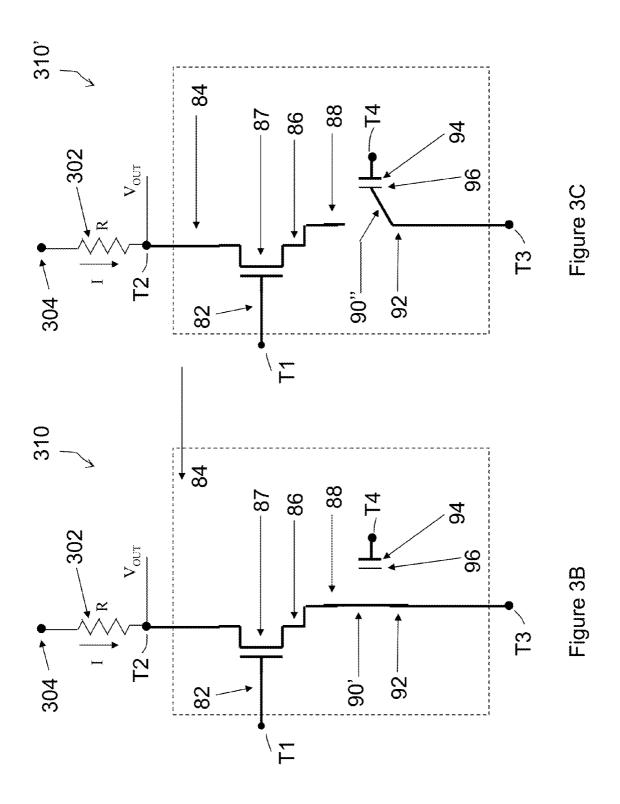

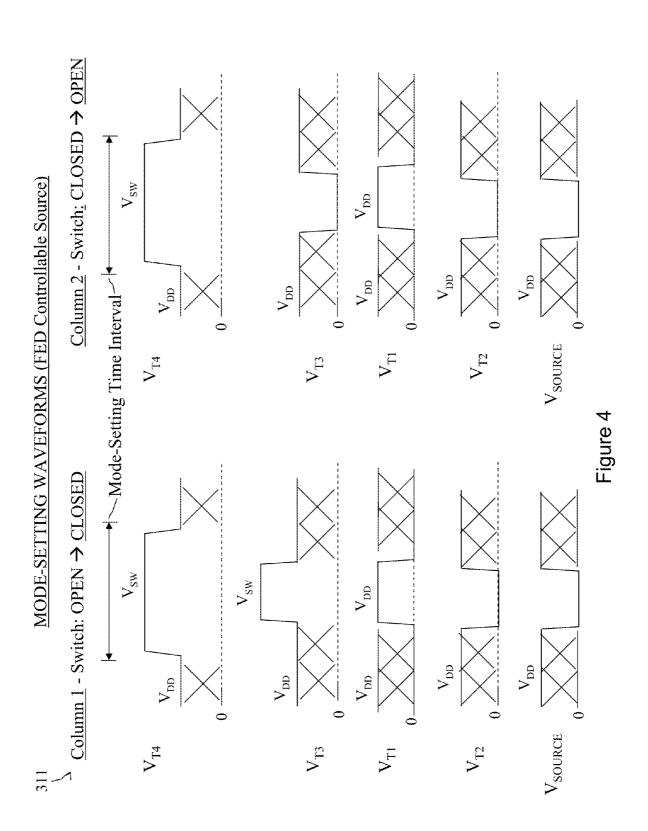

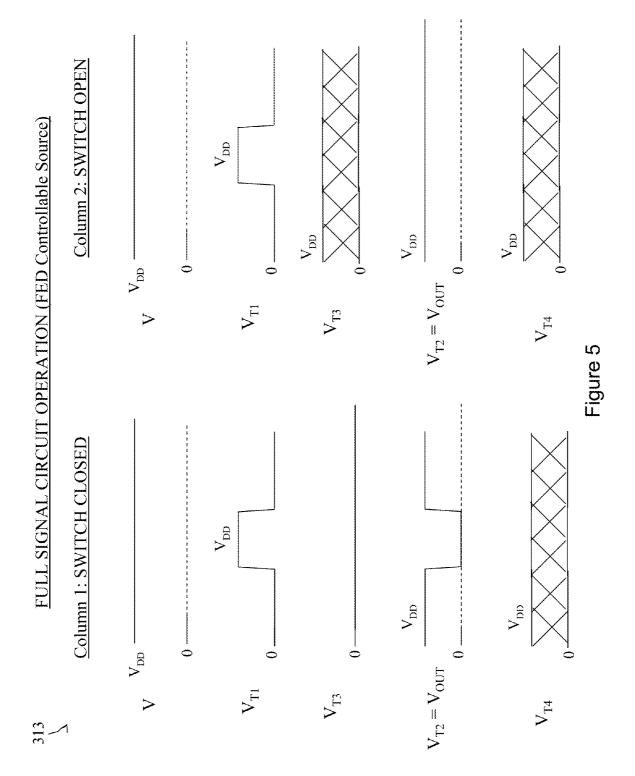

[0047] FIGS. 4-6 illustrate waveforms for exemplary operation of devices according to certain aspects of the invention:

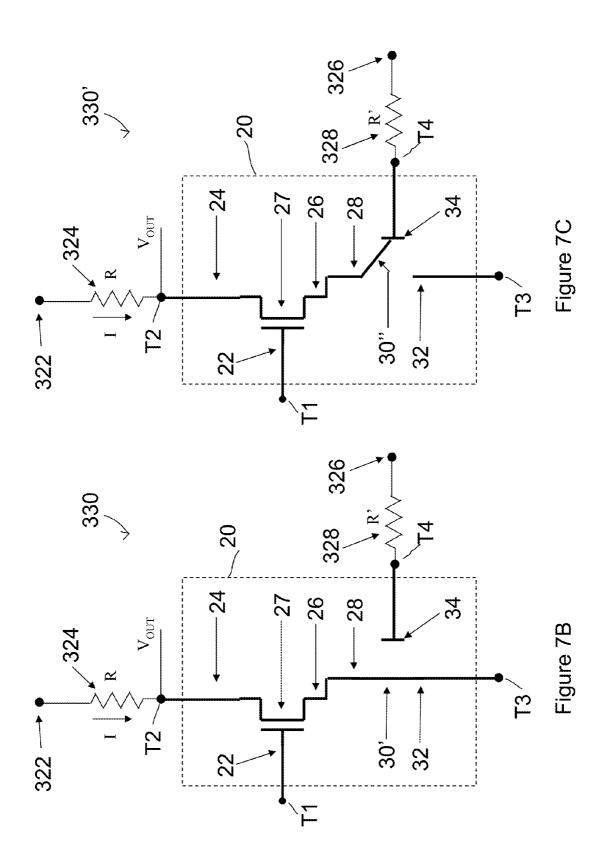

[0048] FIGS. 7A-C illustrate the operation of field effect devices according to certain aspects of the invention;

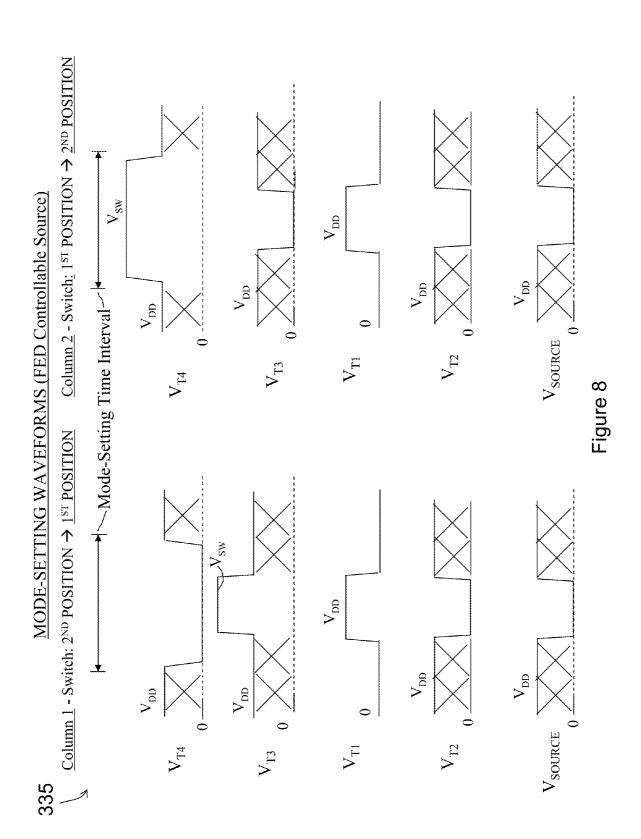

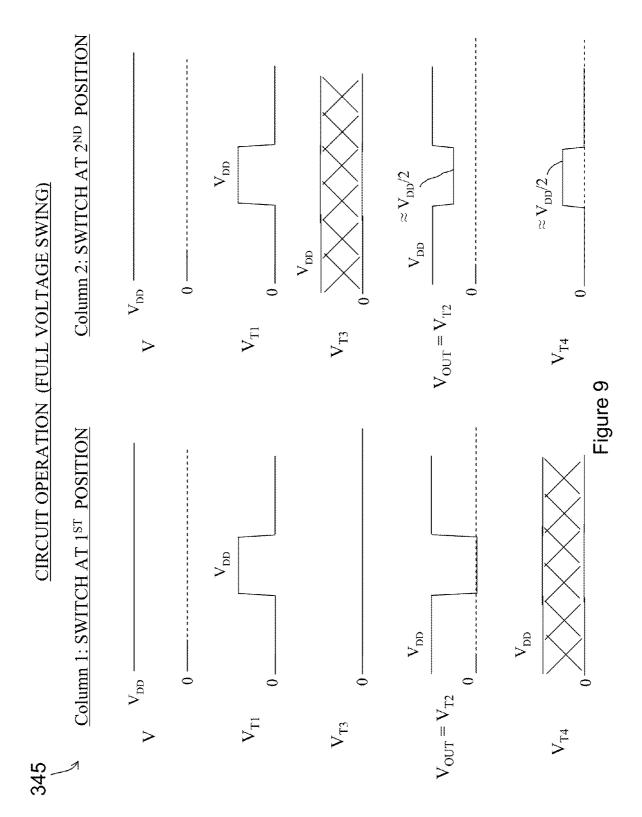

[0049] FIGS. 8 and 9 illustrate waveforms for exemplary operation of devices according to certain aspects of the invention:

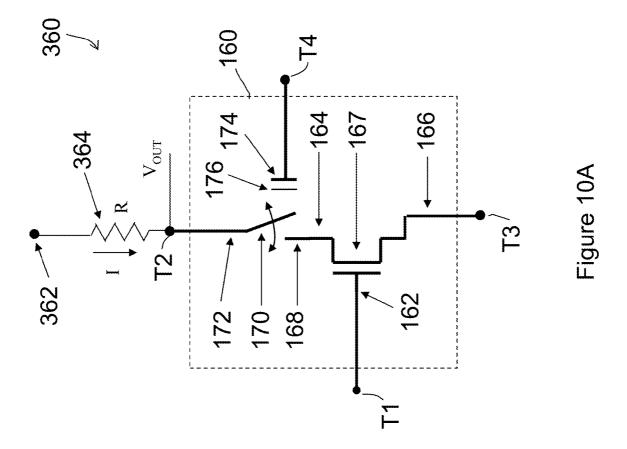

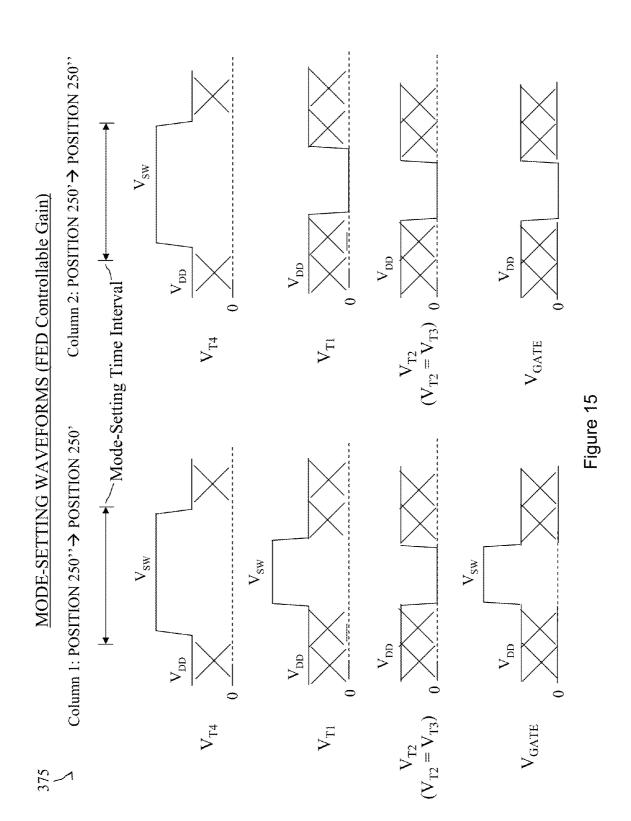

[0050] FIGS. 10A-12 illustrate the operational waveforms for field effect devices according to certain aspects of the invention;

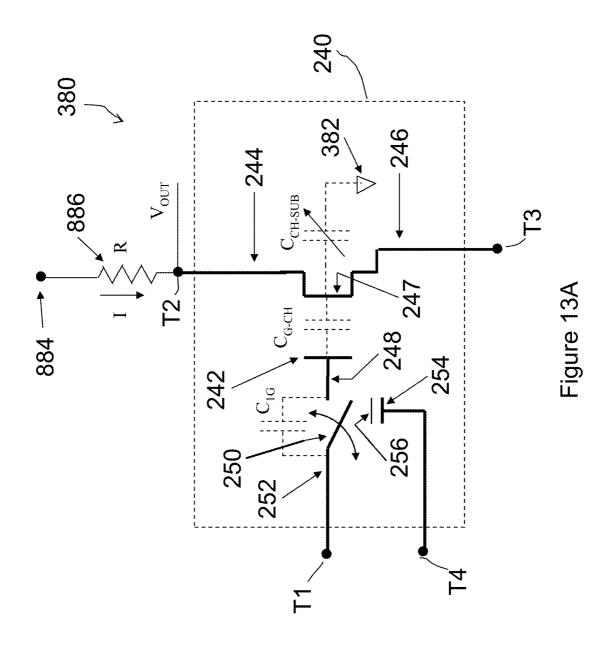

[0051] FIGS. 13A-C illustrate schematic representations of preferred embodiments of the invention;

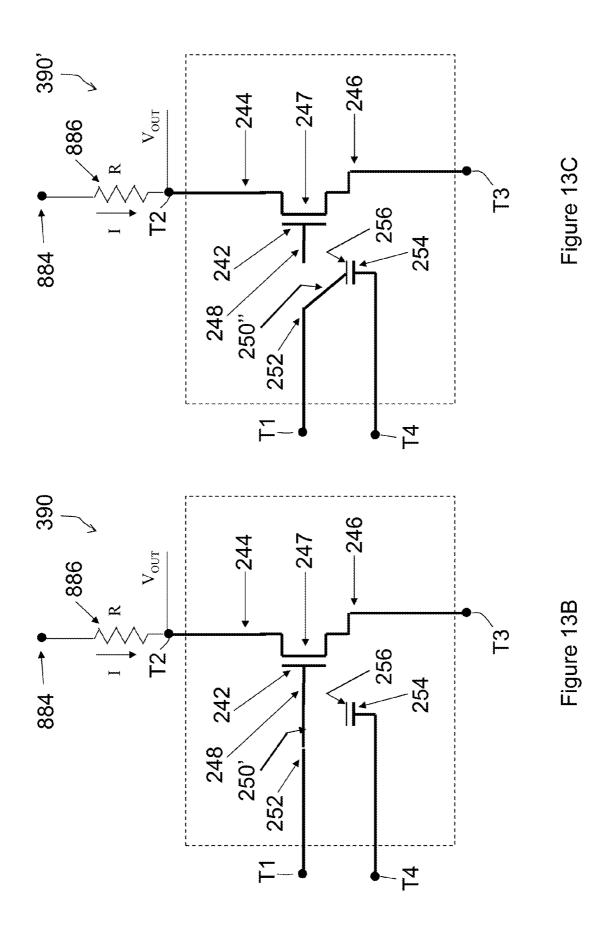

[0052] FIG. 14 illustrates a cross section of one embodiment of the invention;

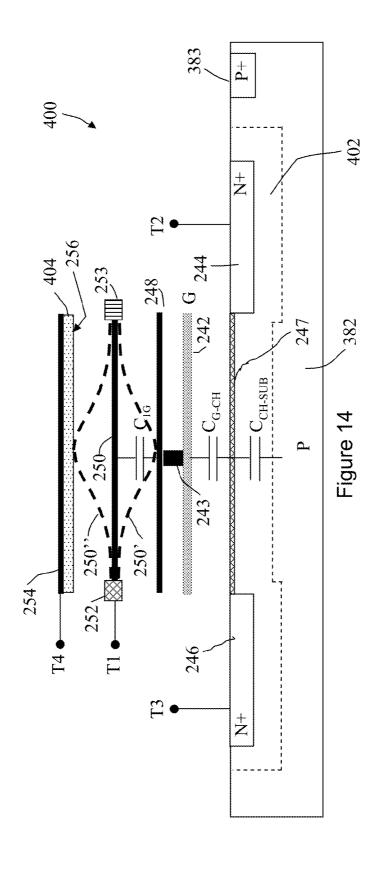

[0053] FIG. 15 illustrates operational waveforms for field effect devices according to certain aspects of the invention;

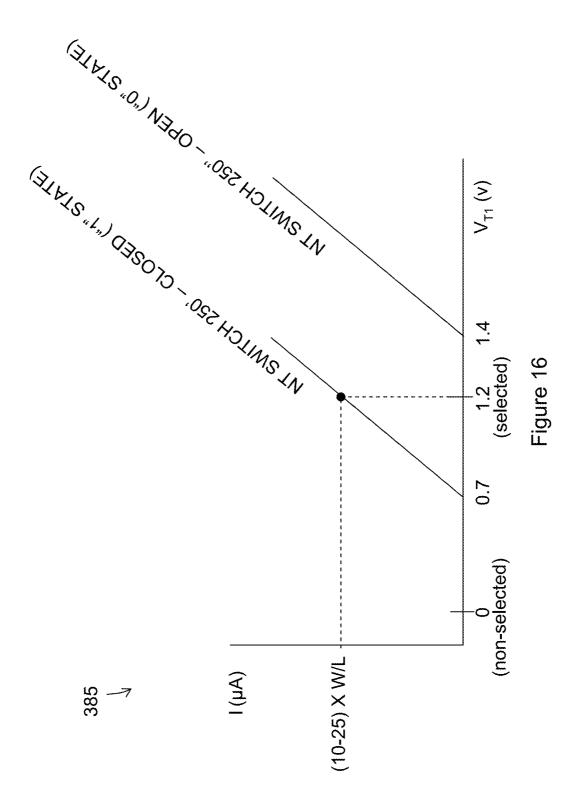

[0054] FIG. 16 illustrates electrical (IN) characteristics of devices according to one aspect of the invention;

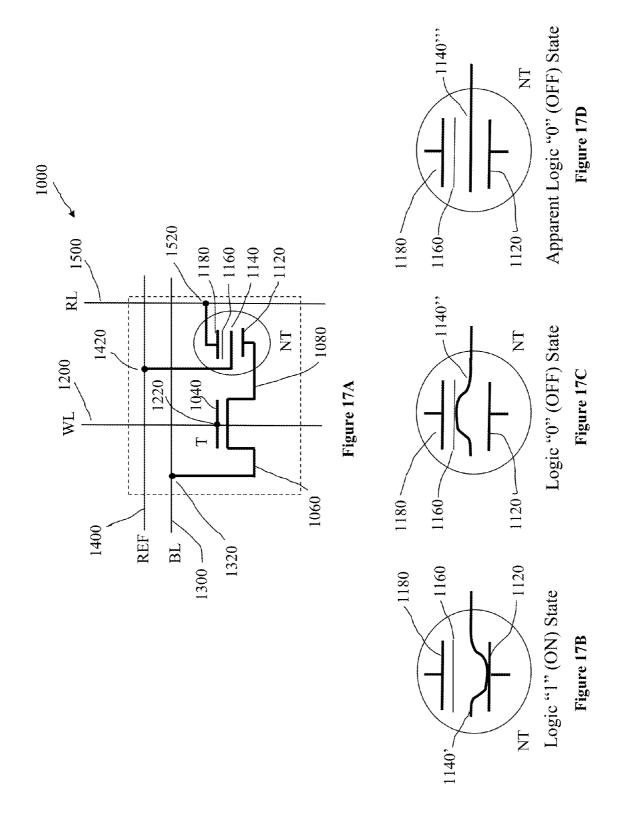

[0055] FIGS. 17A-D illustrate a schematic representation of devices according to one aspect of the invention along with depictions of memory states of such a device;

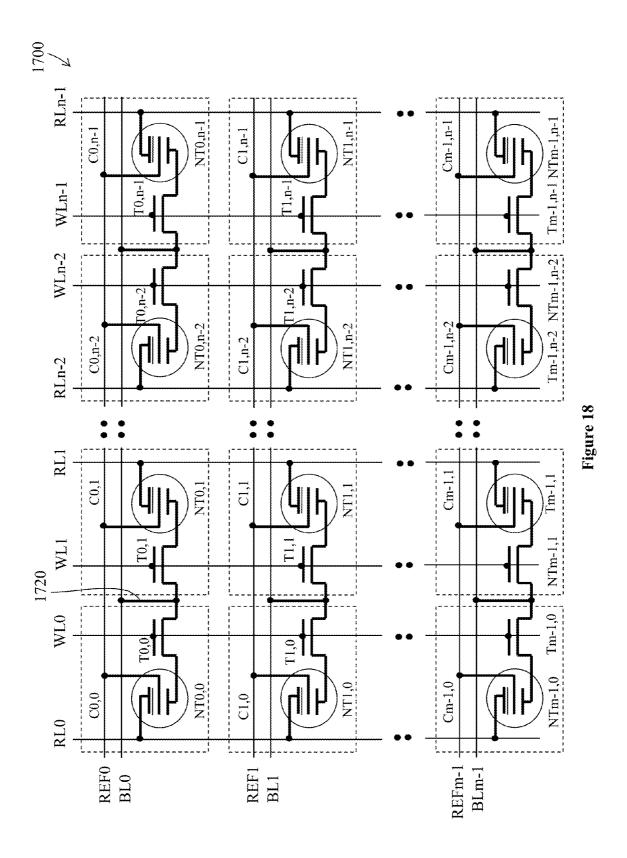

[0056] FIG. 18 illustrates schematics of an NRAM system according to preferred embodiments of the invention;

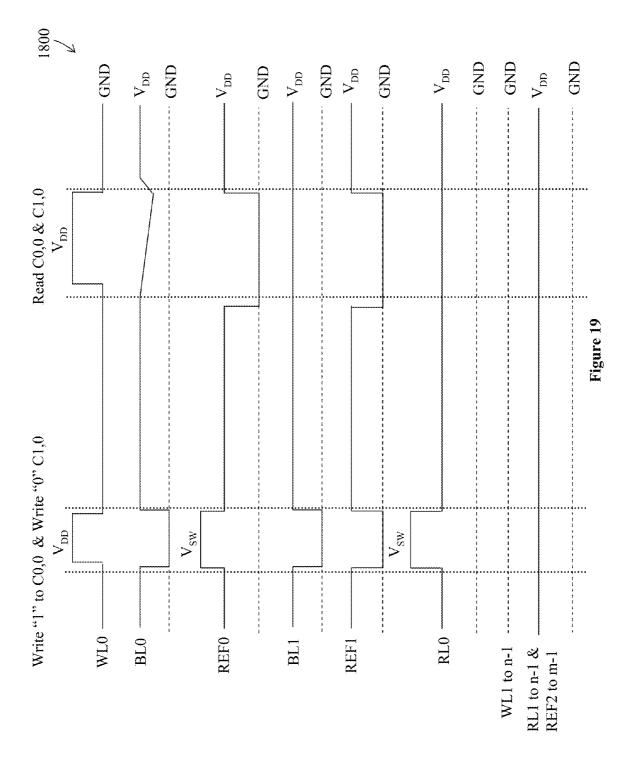

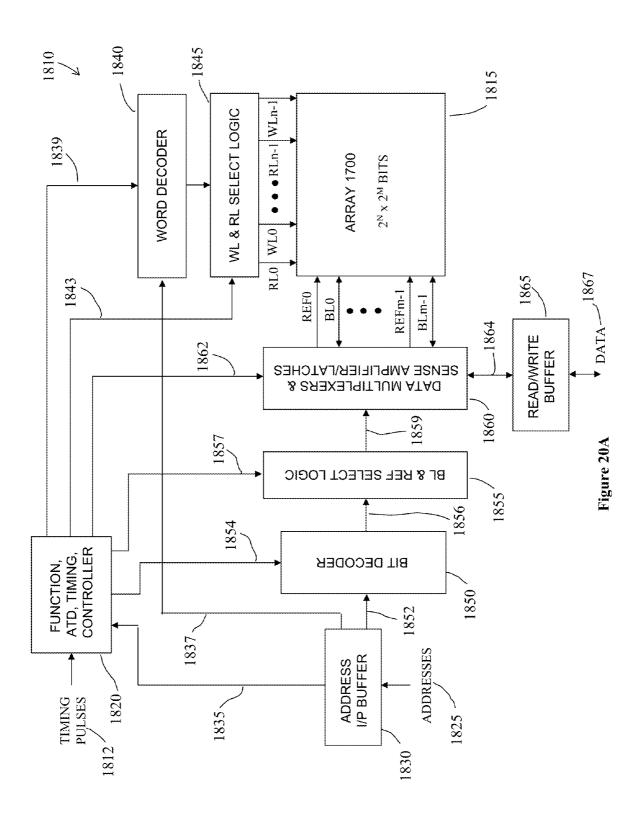

[0057] FIG. 19 illustrates operational waveforms for memory devices according to certain aspects of the invention; [0058] FIG. 20A illustrates a memory array flow chart according to one aspect of the invention;

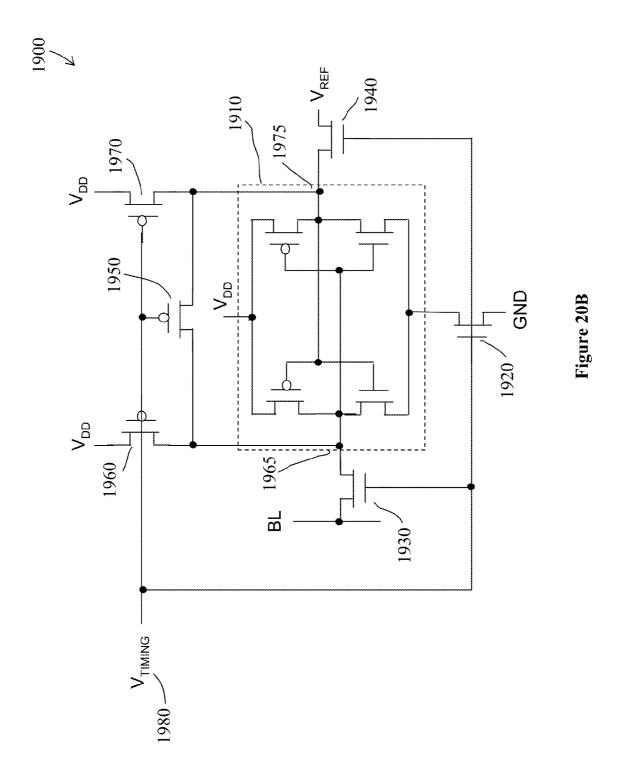

[0059] FIG. 20B illustrates a schematic of a switch amplifier/latch according to certain aspects of the invention;

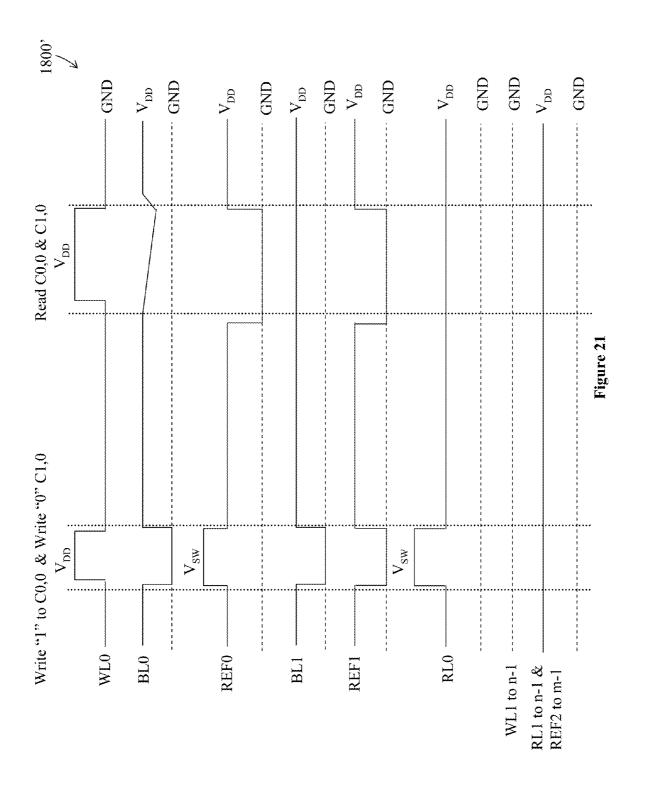

[0060] FIG. 21 illustrates waveforms for a memory system according to certain aspects of the invention;

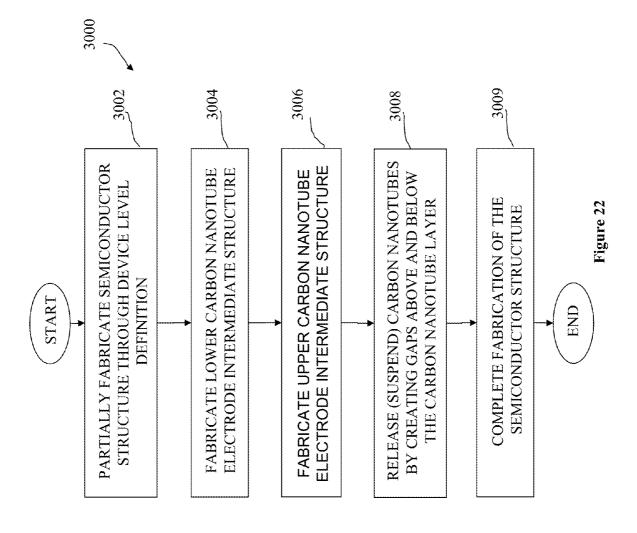

[0061] FIG. 22 is a flow chart of a method of manufacturing preferred embodiments of the invention;

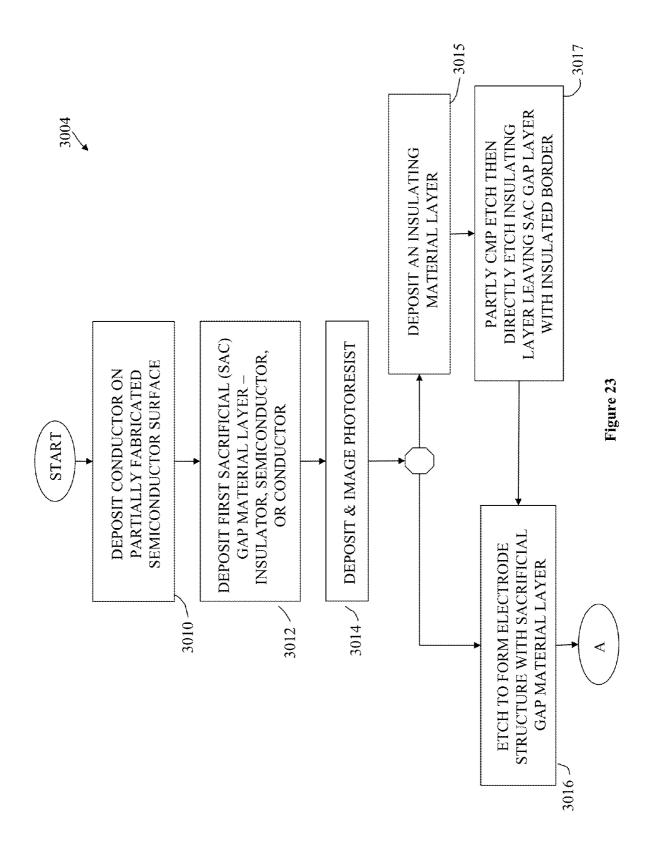

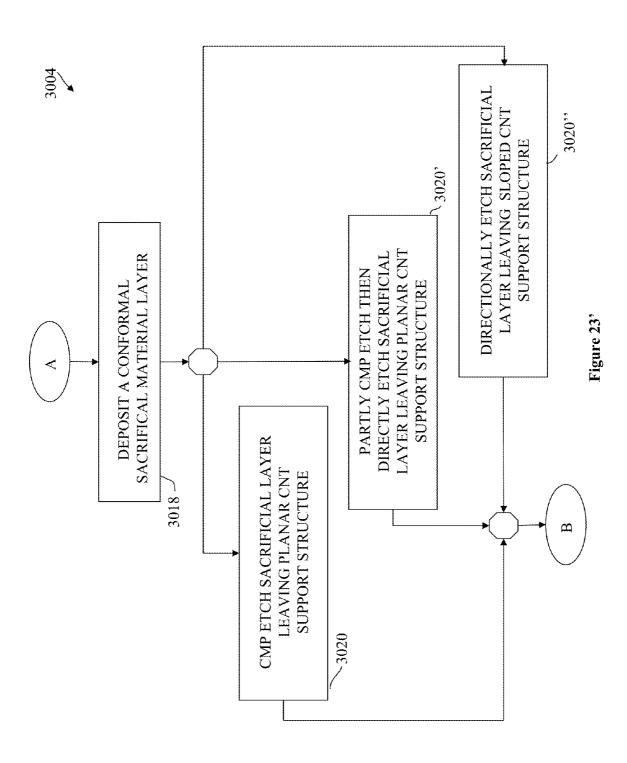

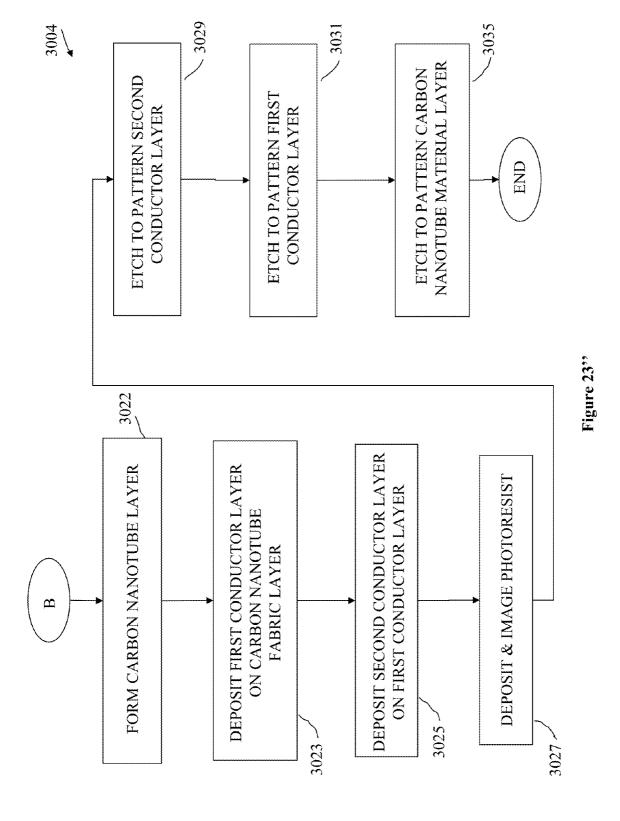

[0062] FIGS. 23, 23' and 23" are flow charts illustrating acts performed in preferred methods of the invention;

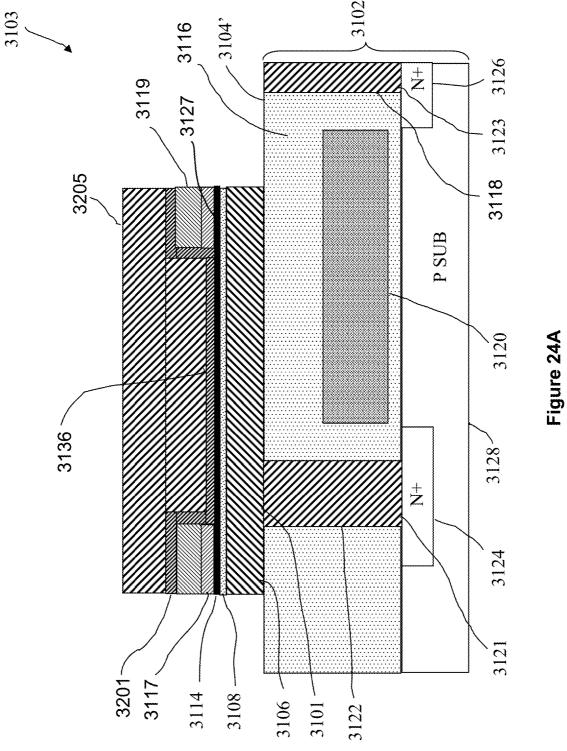

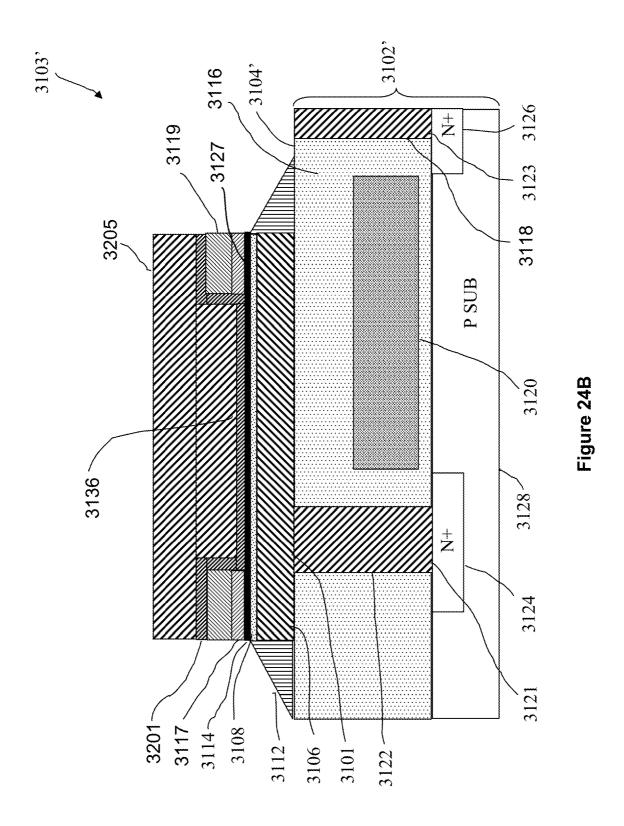

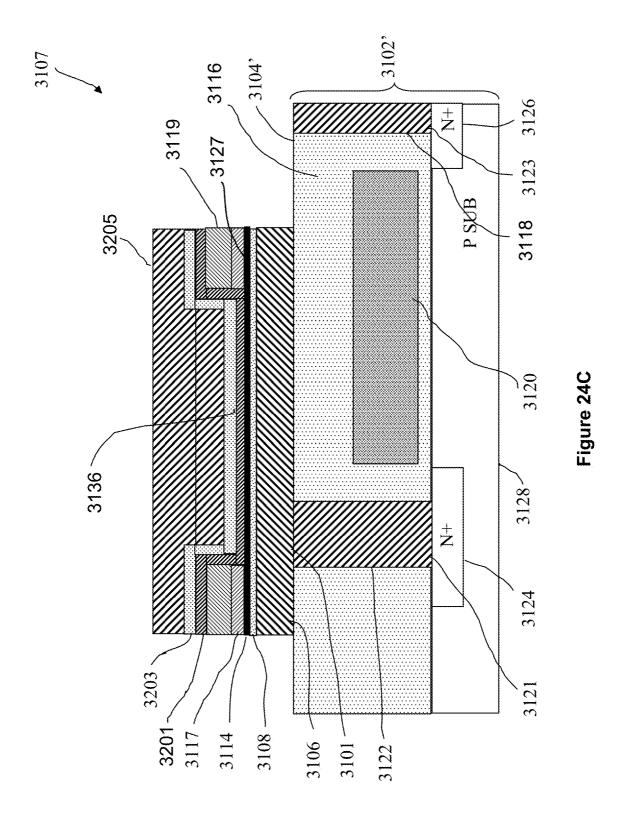

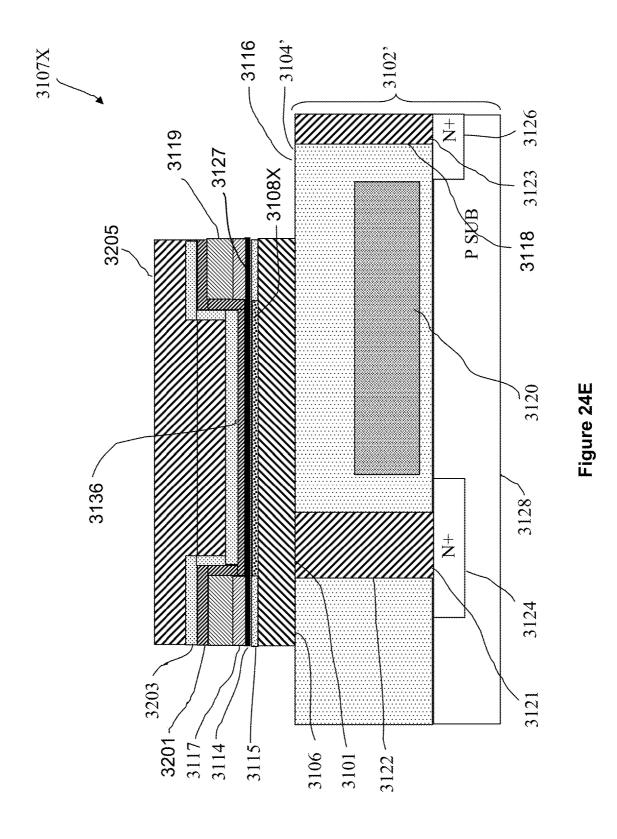

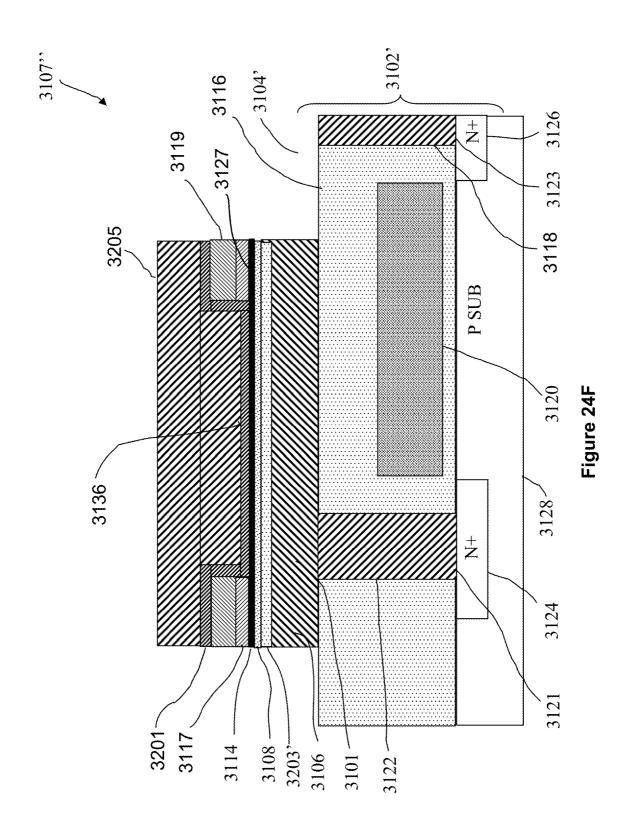

[0063] FIGS. 24A-F illustrate exemplary structures according to aspects of the invention;

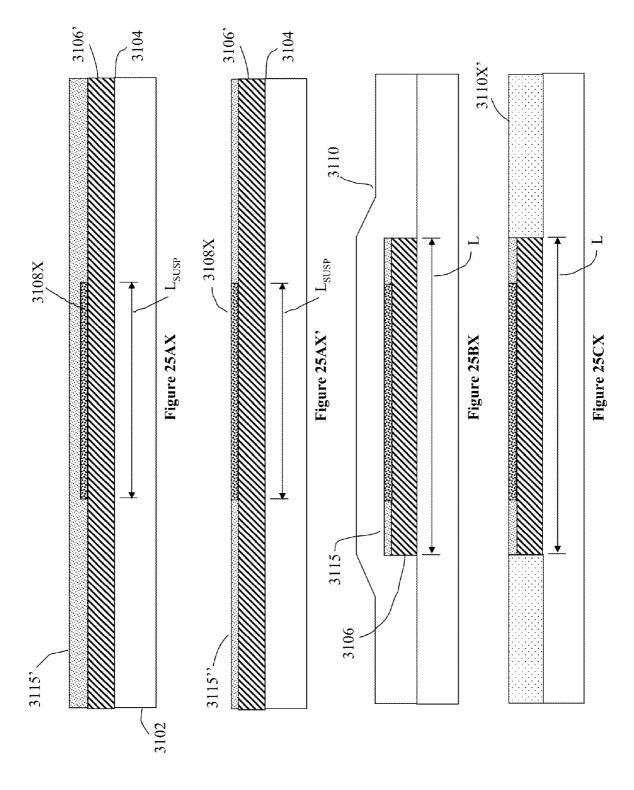

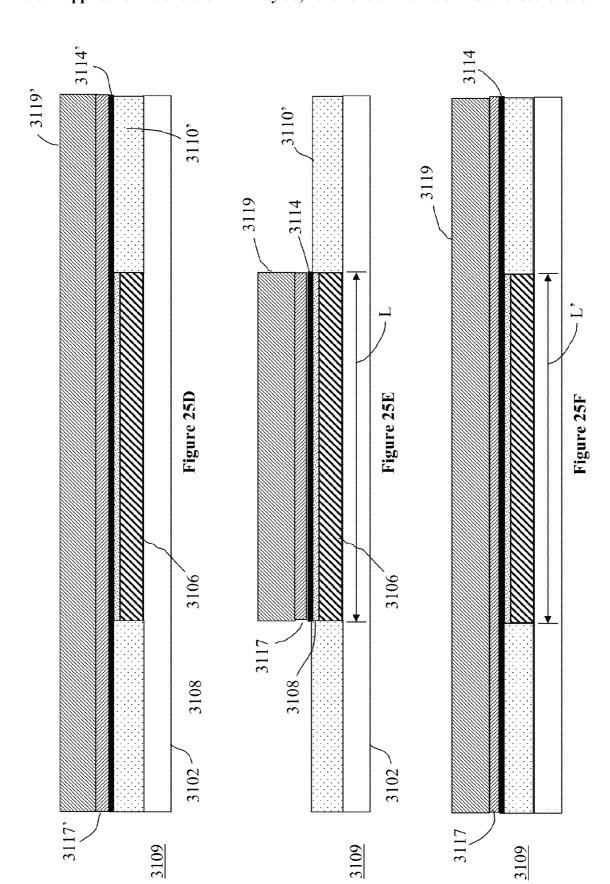

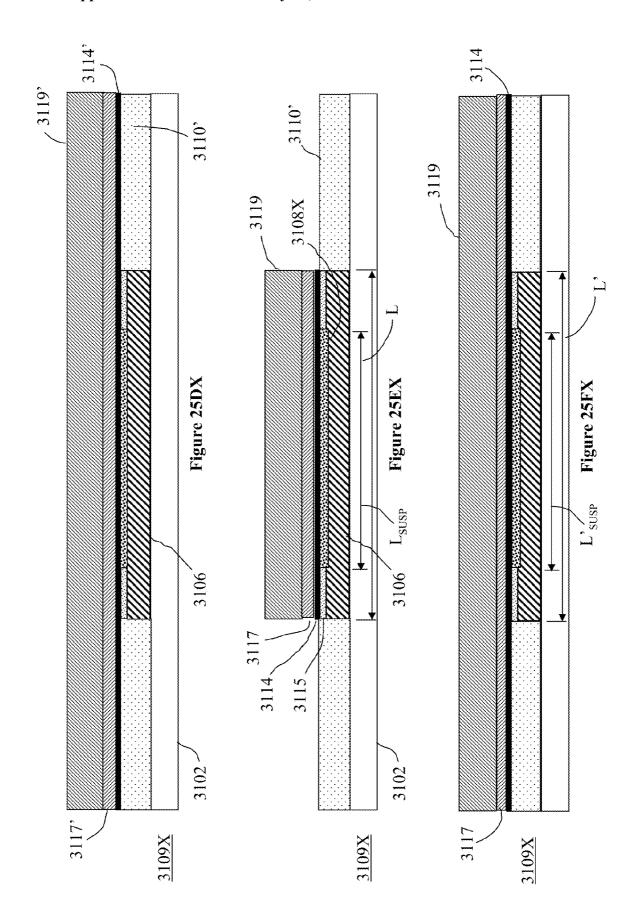

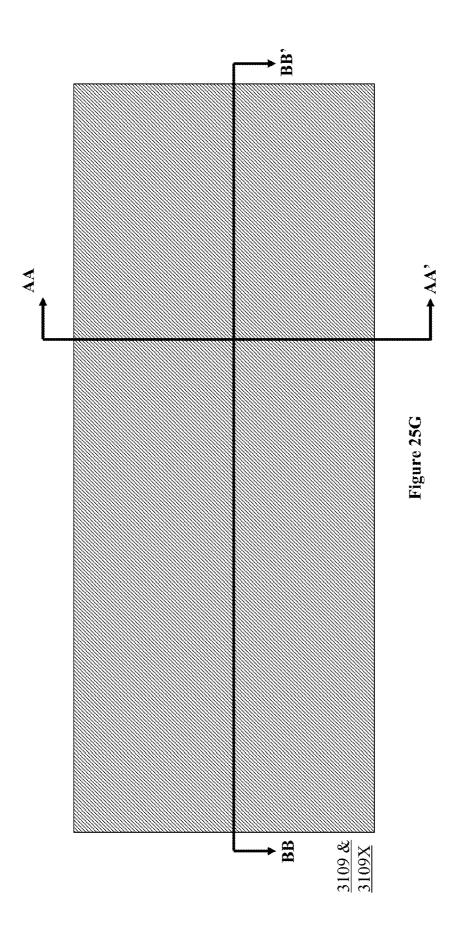

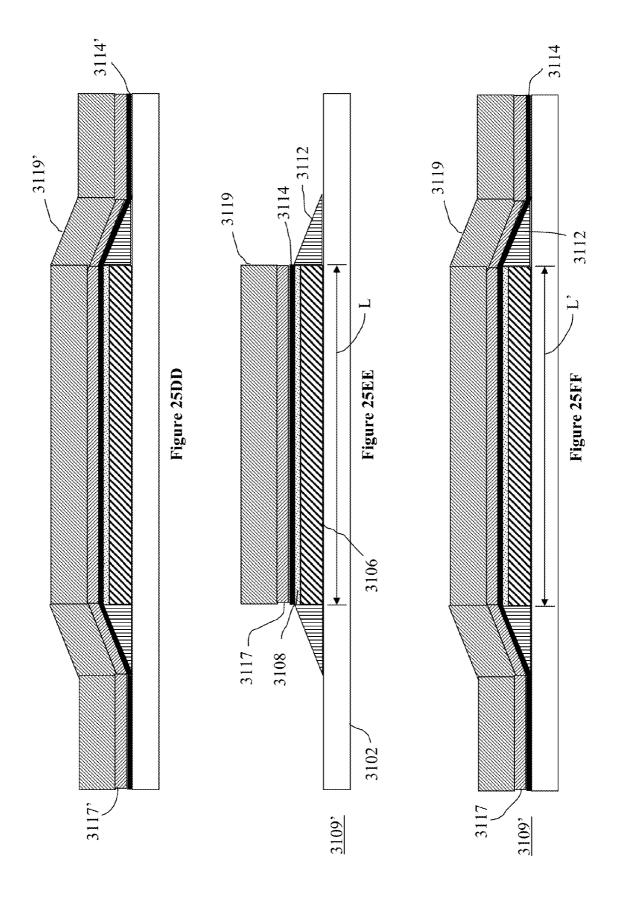

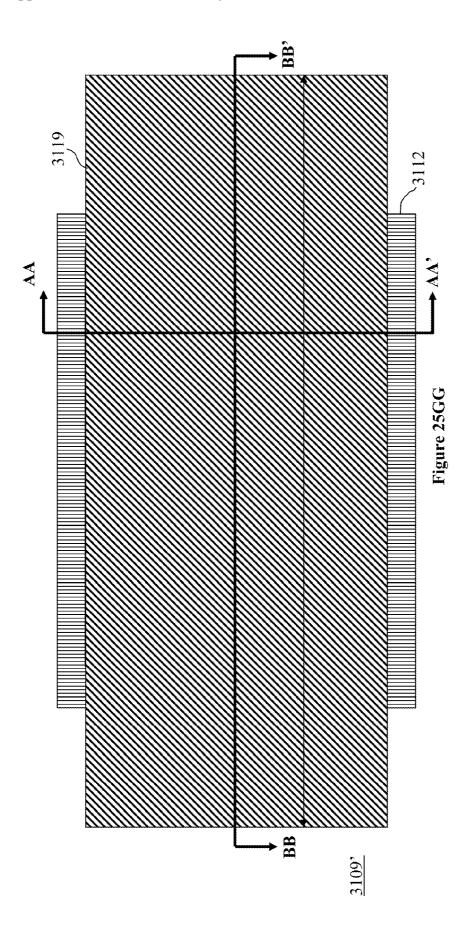

[0064] FIGS. 25A-GG illustrate exemplary intermediate structures according to certain aspects of the invention;

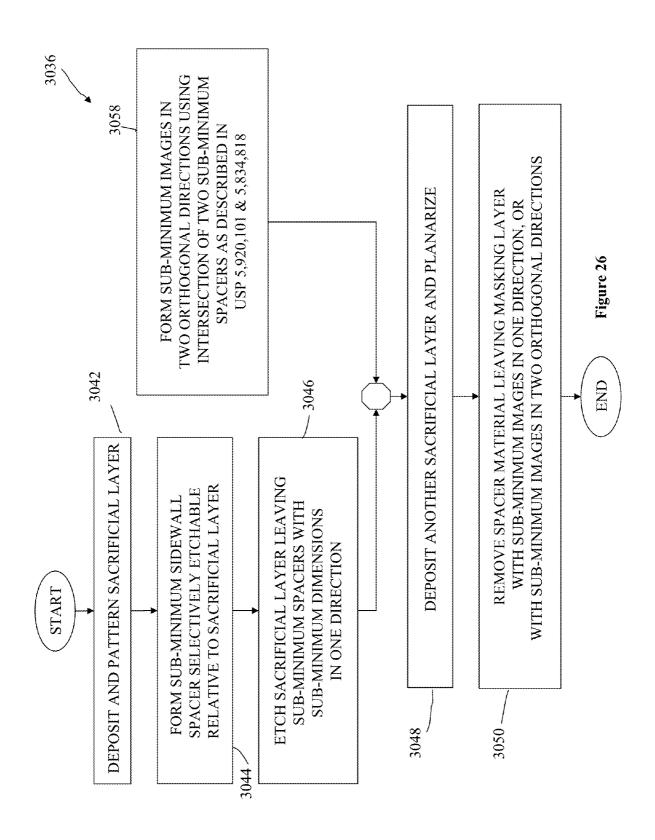

[0065] FIG. 26 is a flow chart of a method of manufacturing preferred embodiments of the invention;

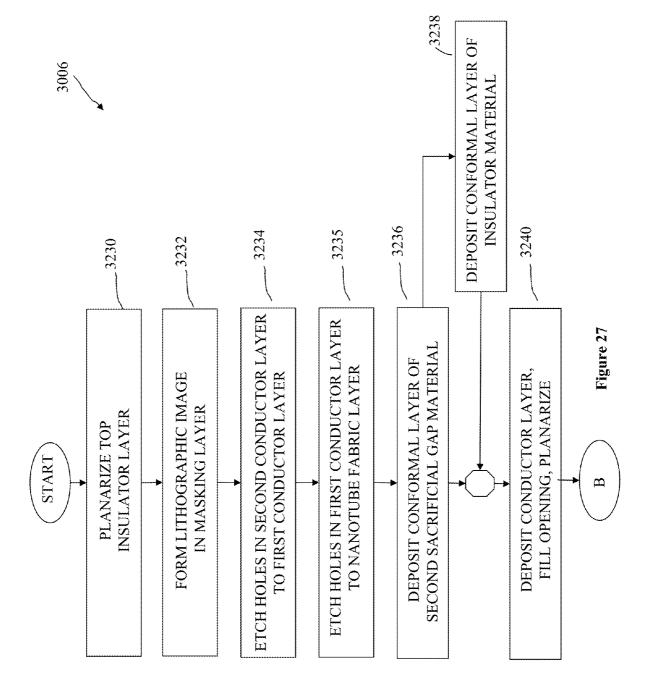

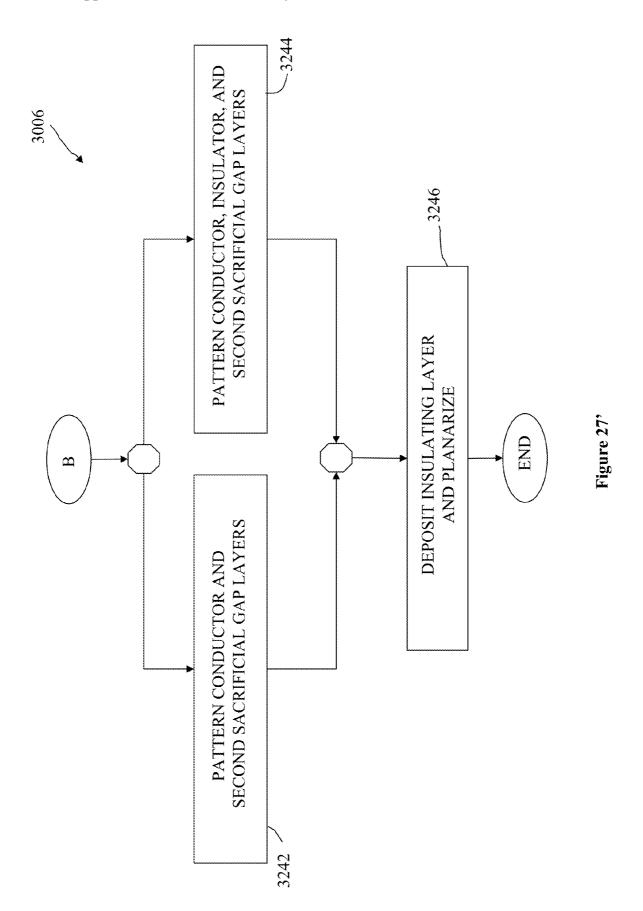

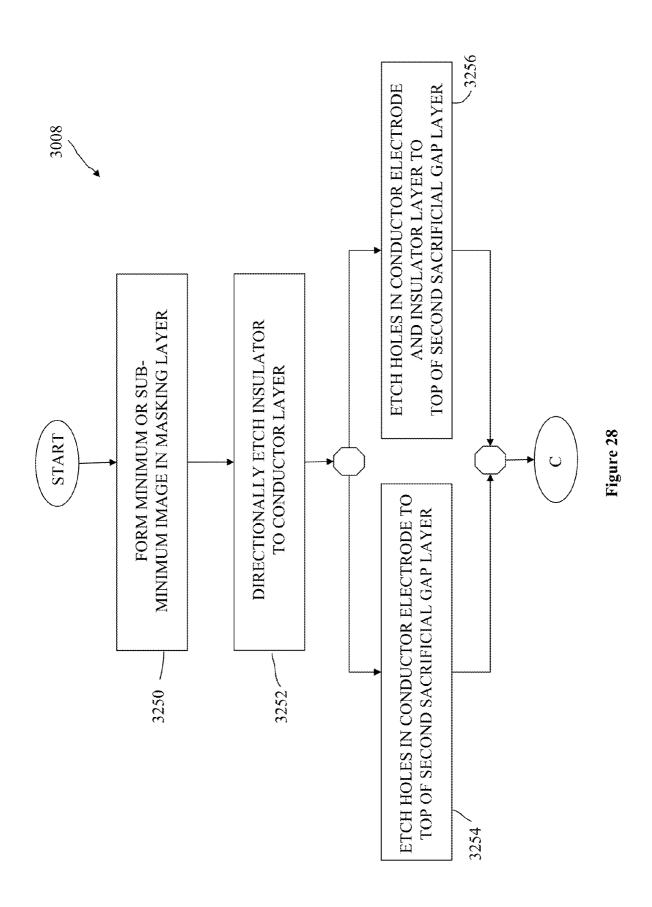

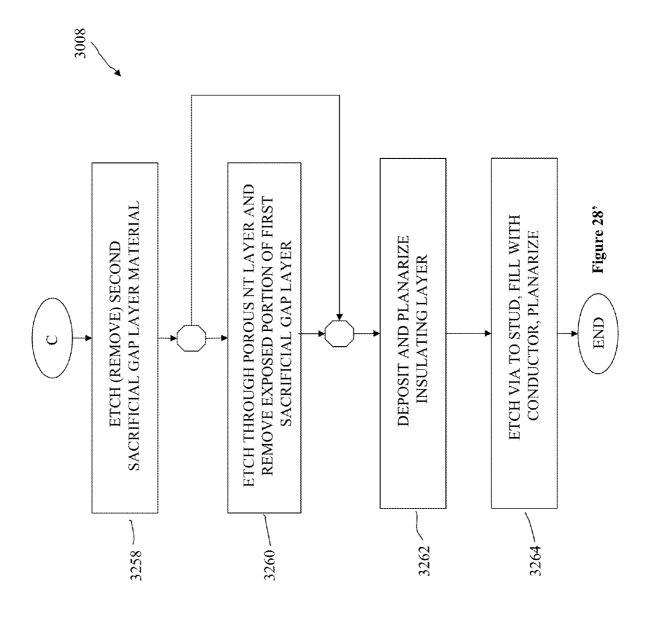

[0066] FIGS. 27, 27', 28 and 28' are flow charts of method of manufacturing preferred embodiments of the invention;

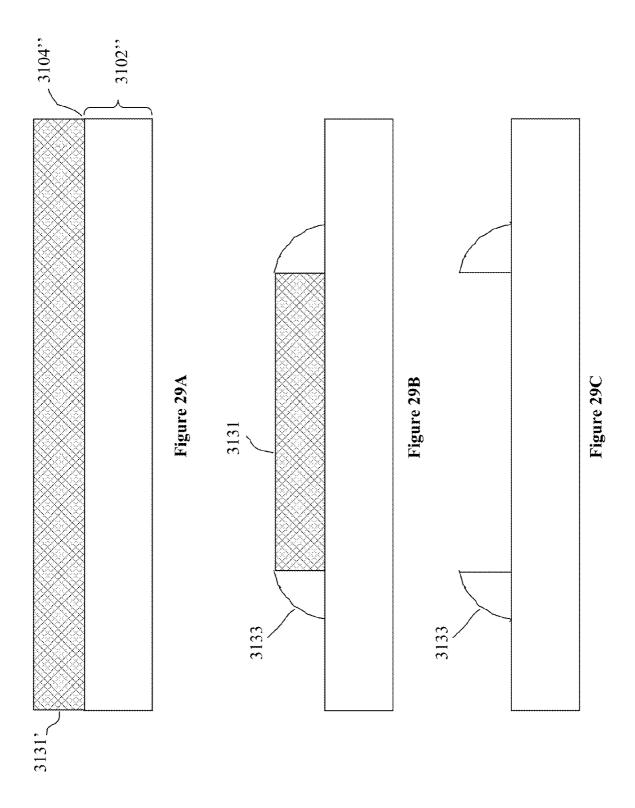

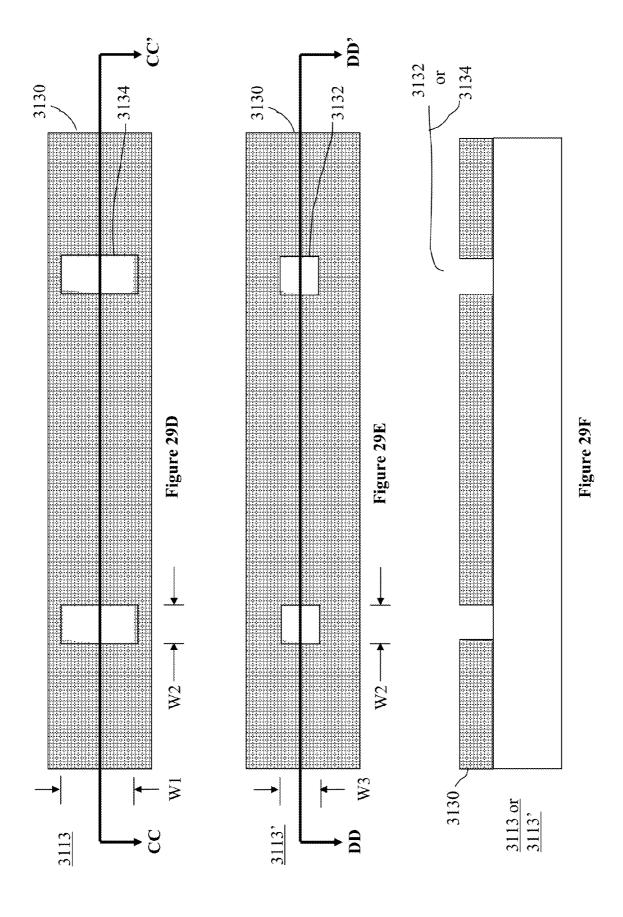

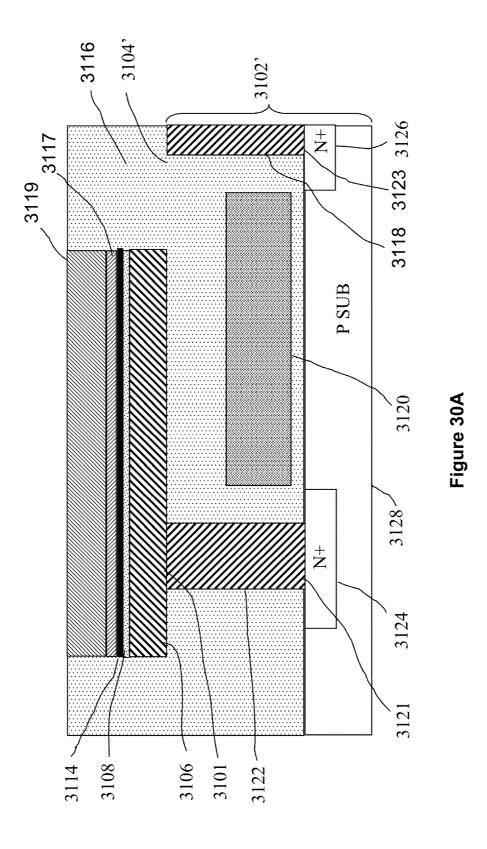

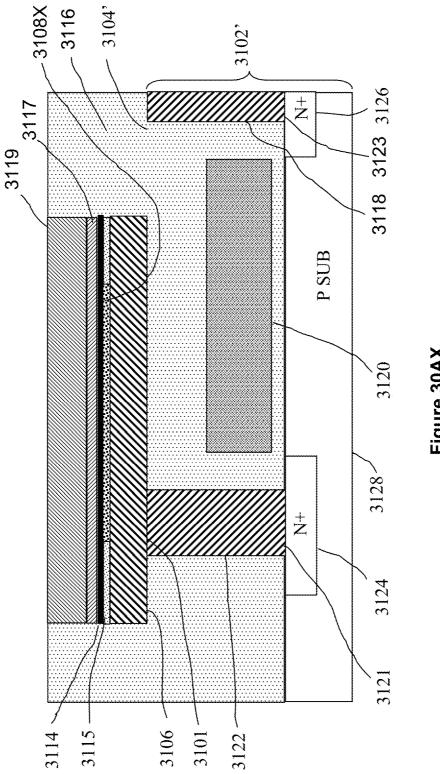

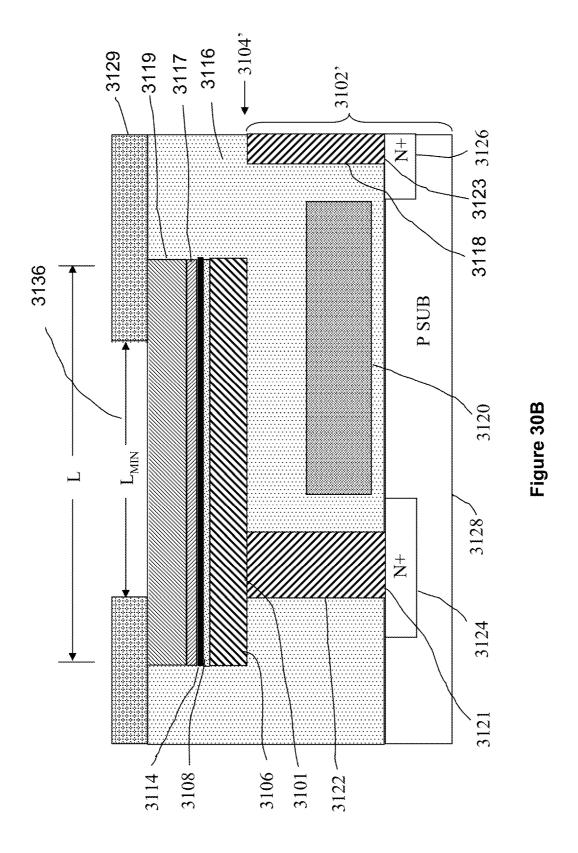

[0067] FIGS. 29A-F illustrate intermediate structures according to certain aspects of the invention;

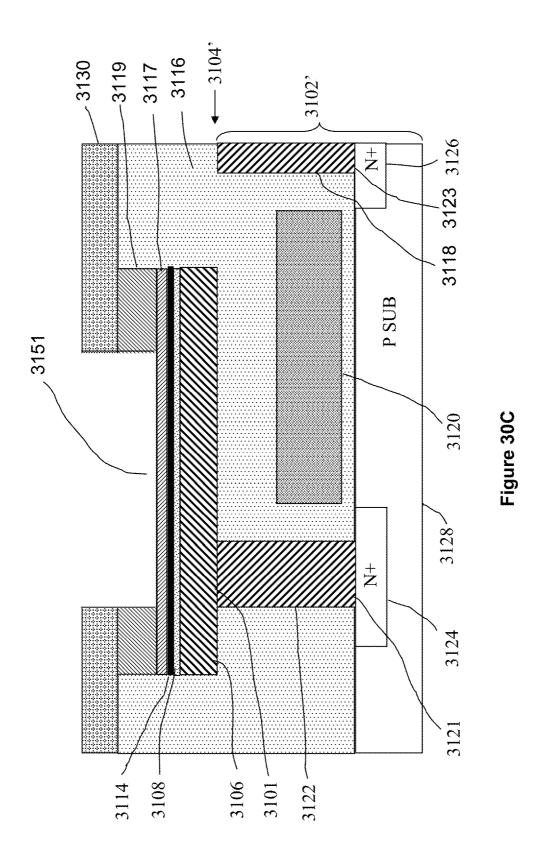

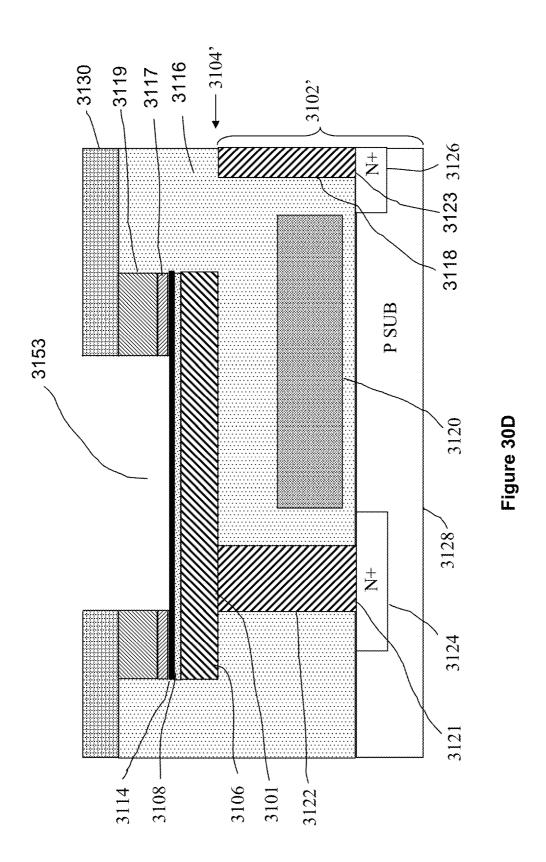

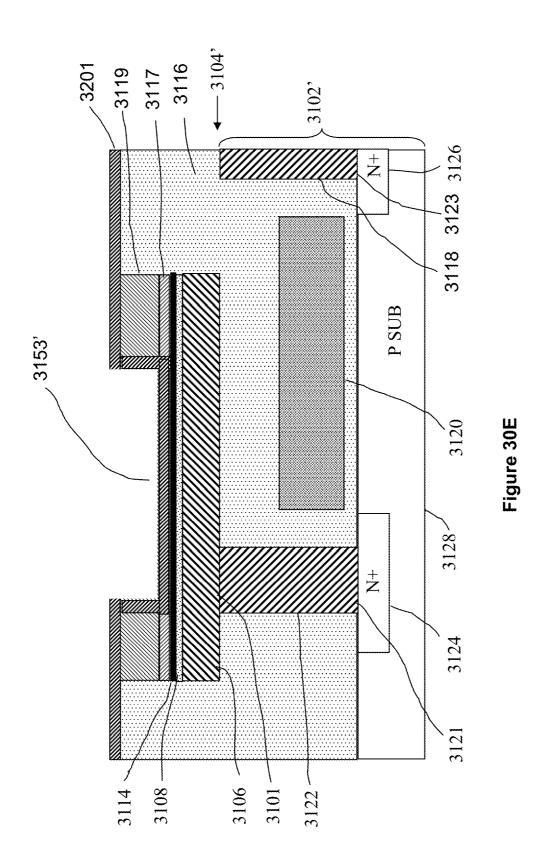

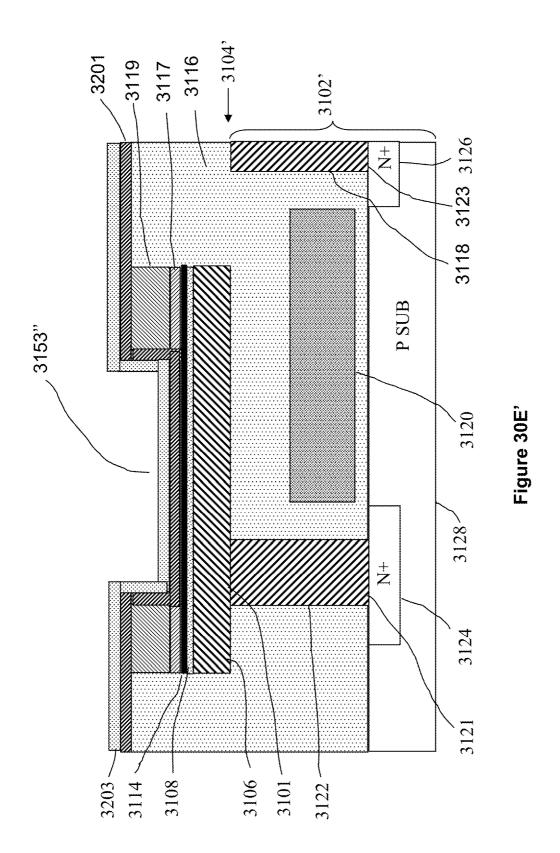

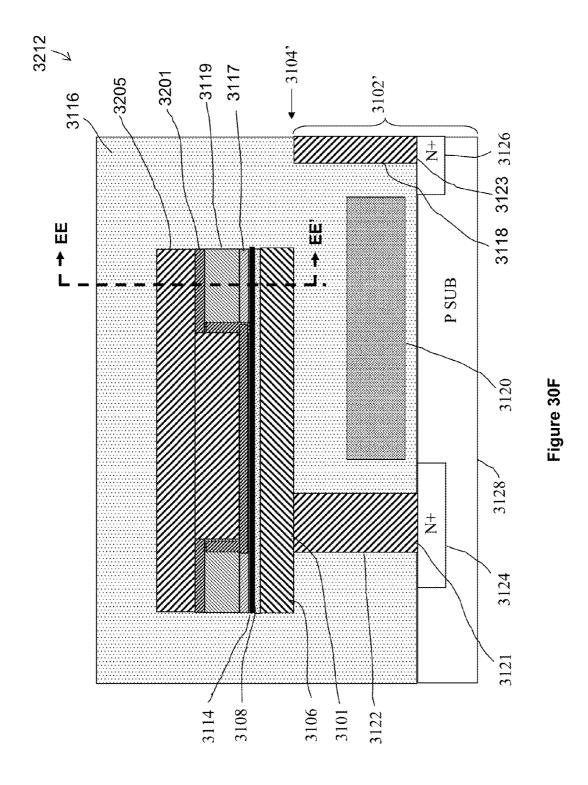

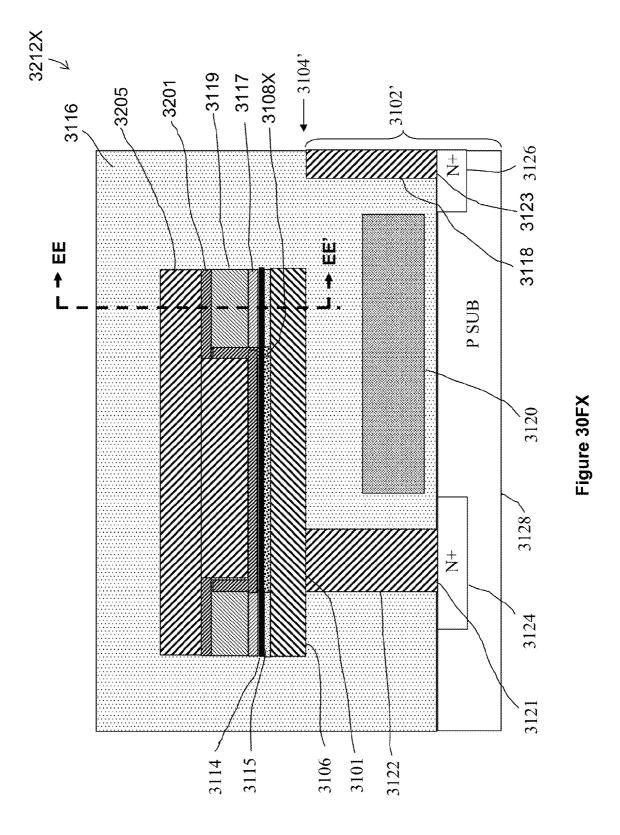

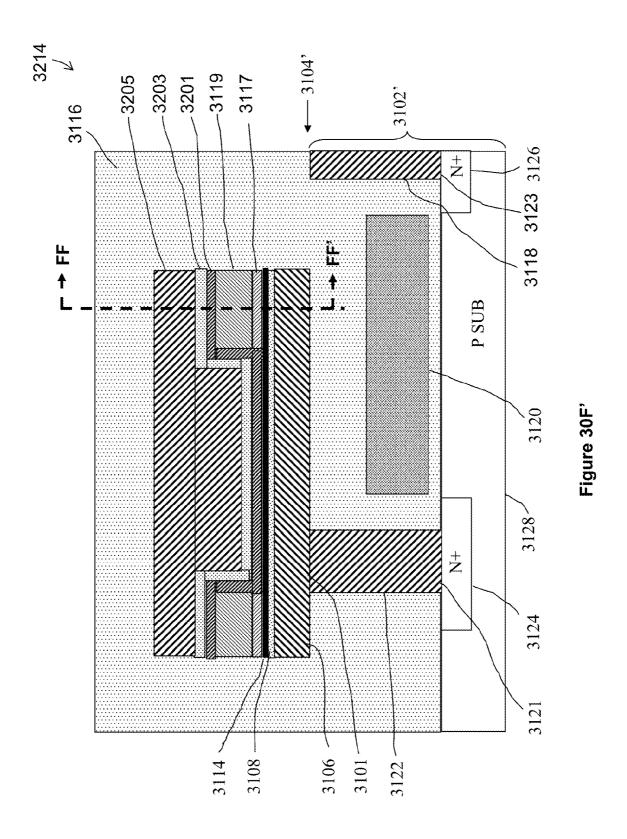

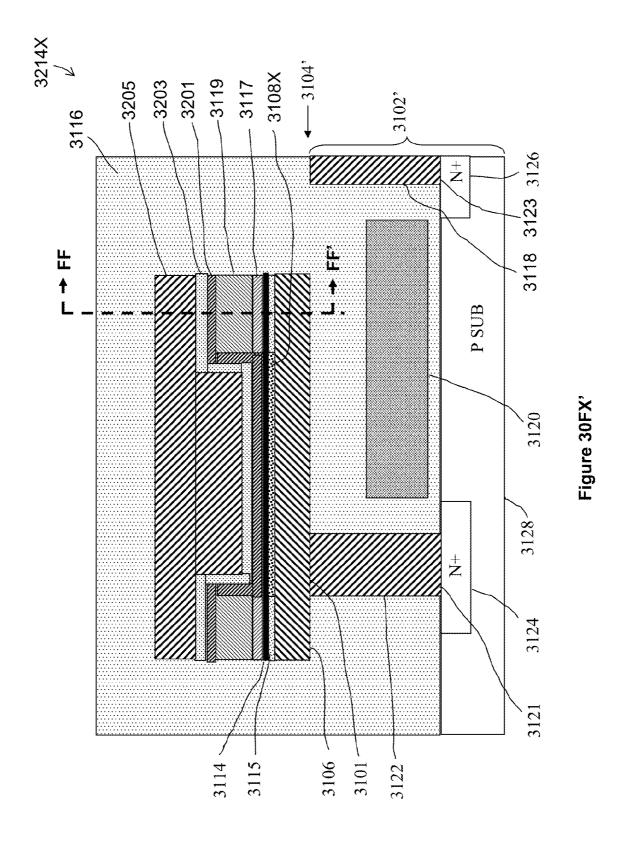

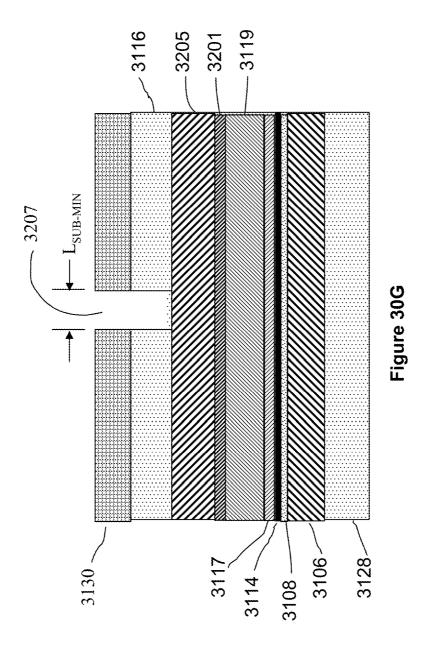

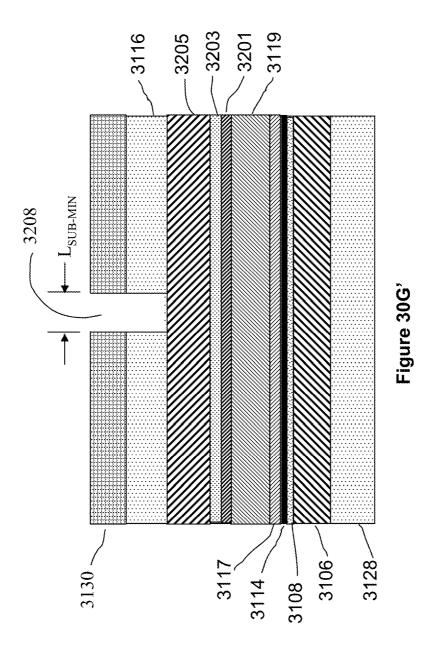

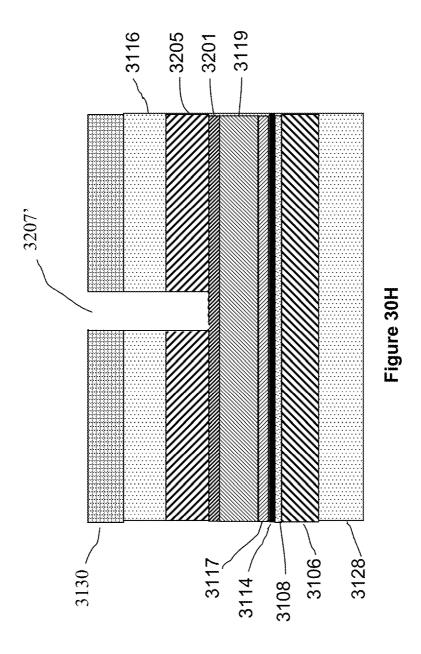

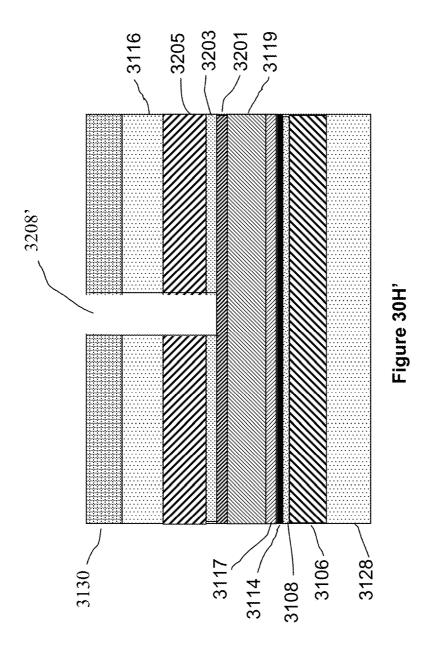

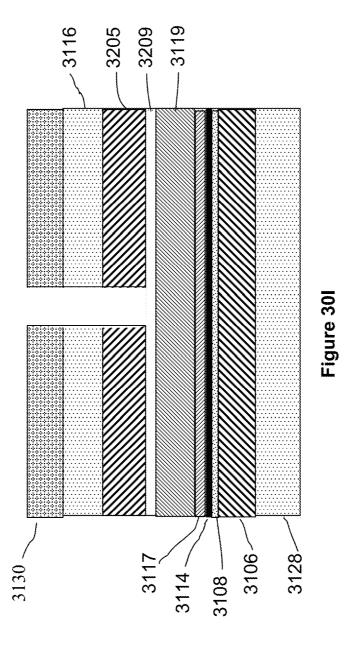

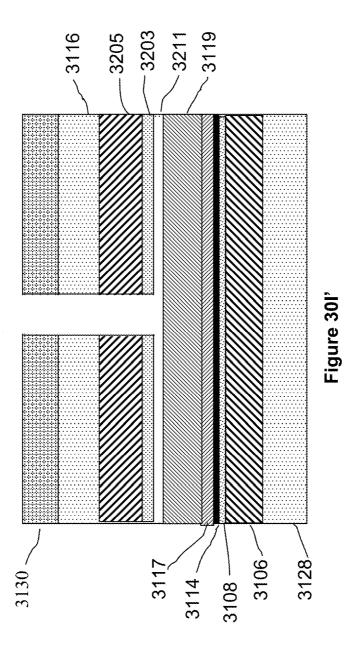

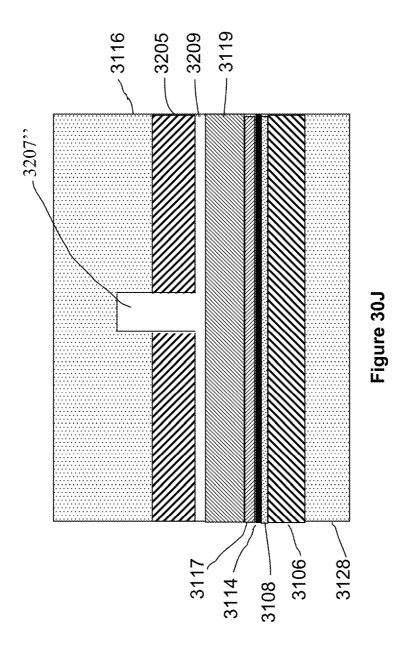

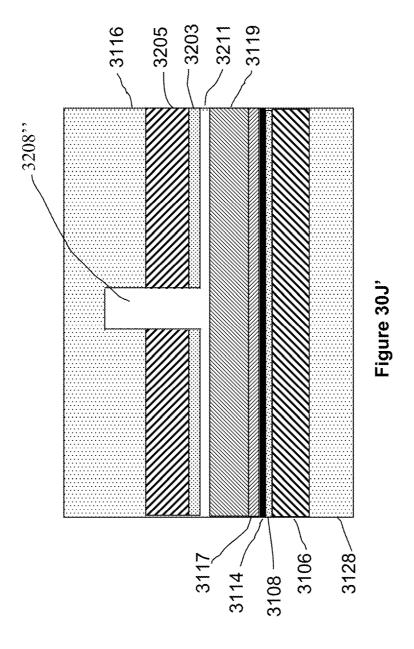

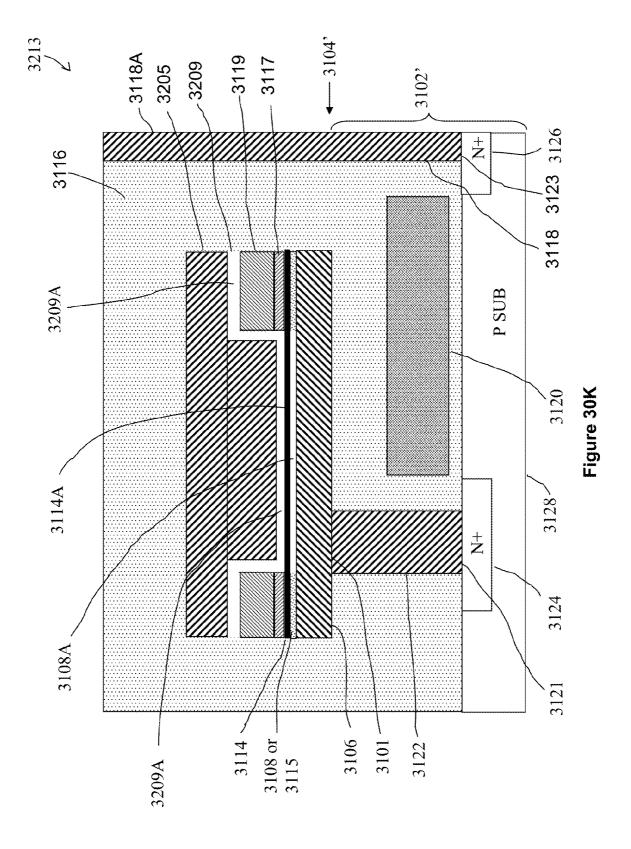

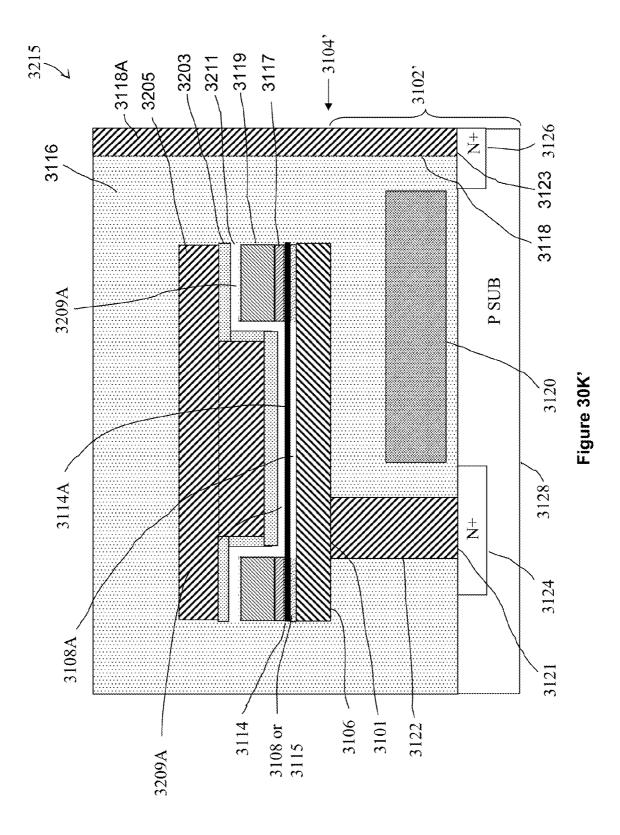

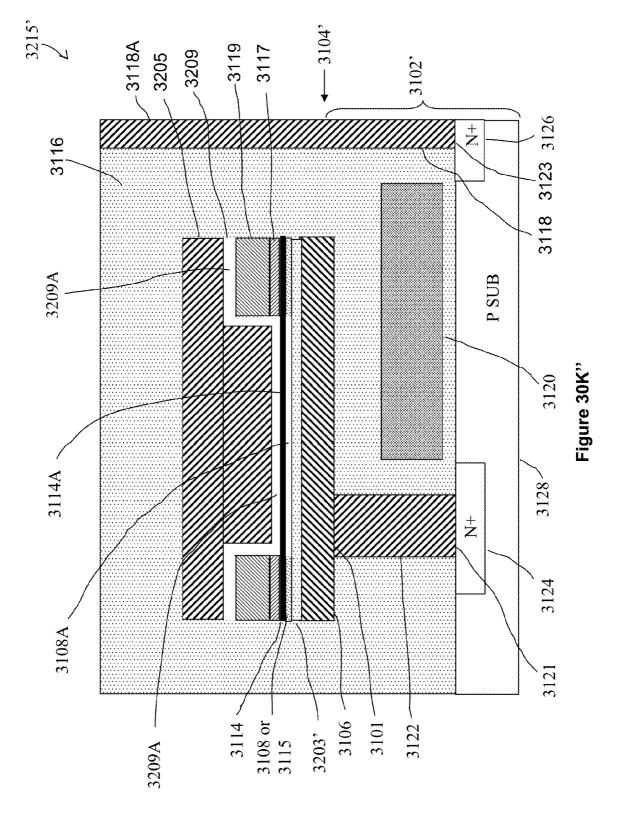

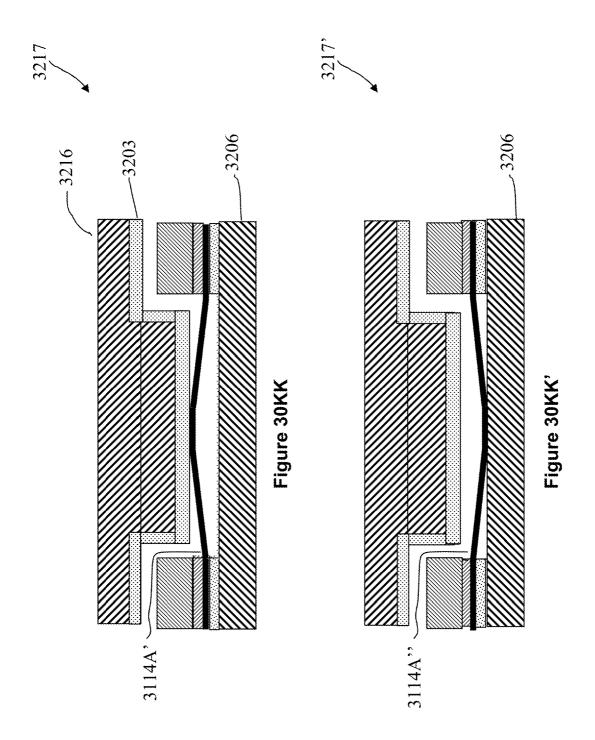

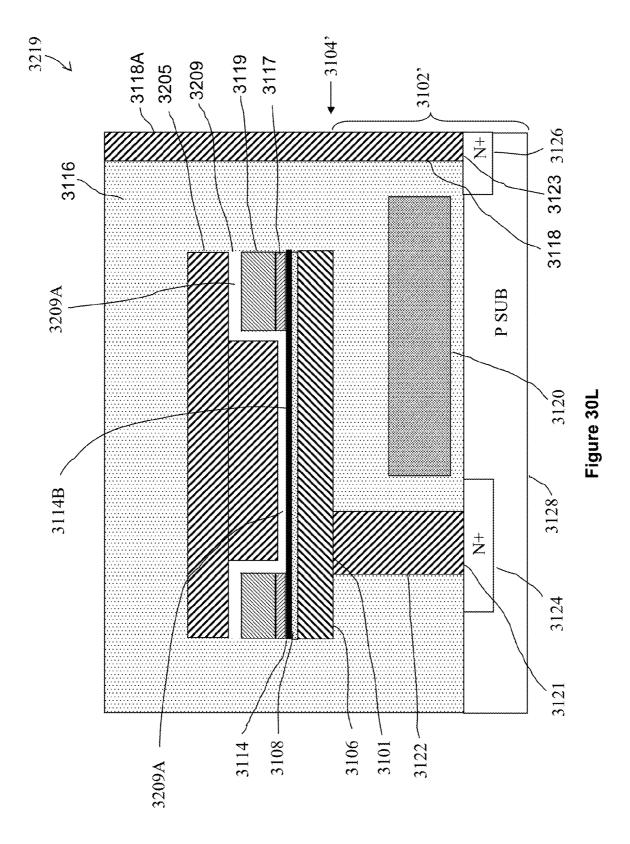

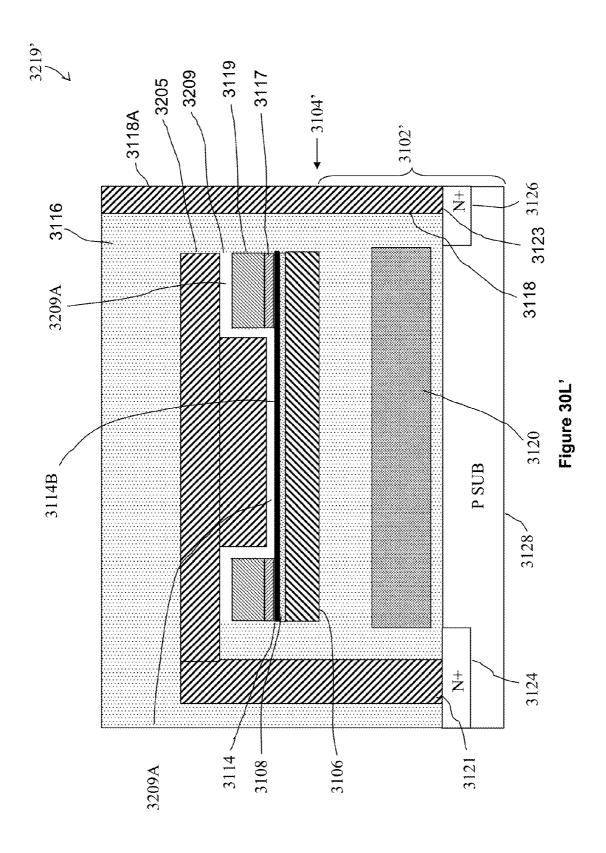

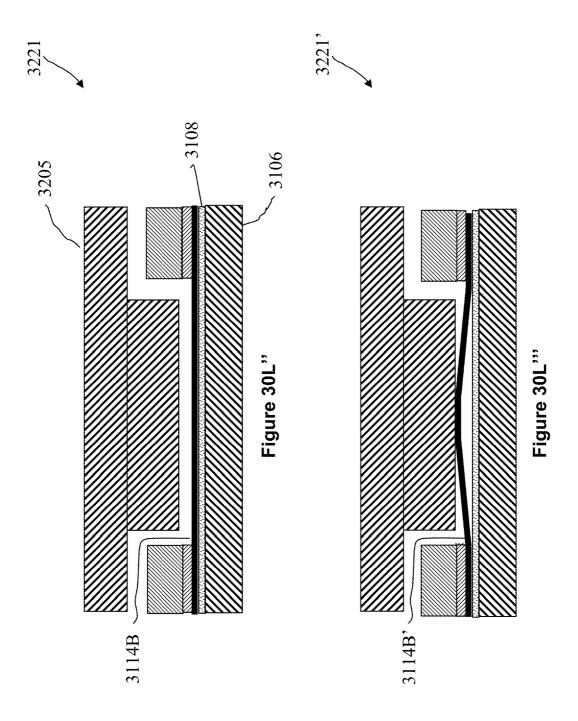

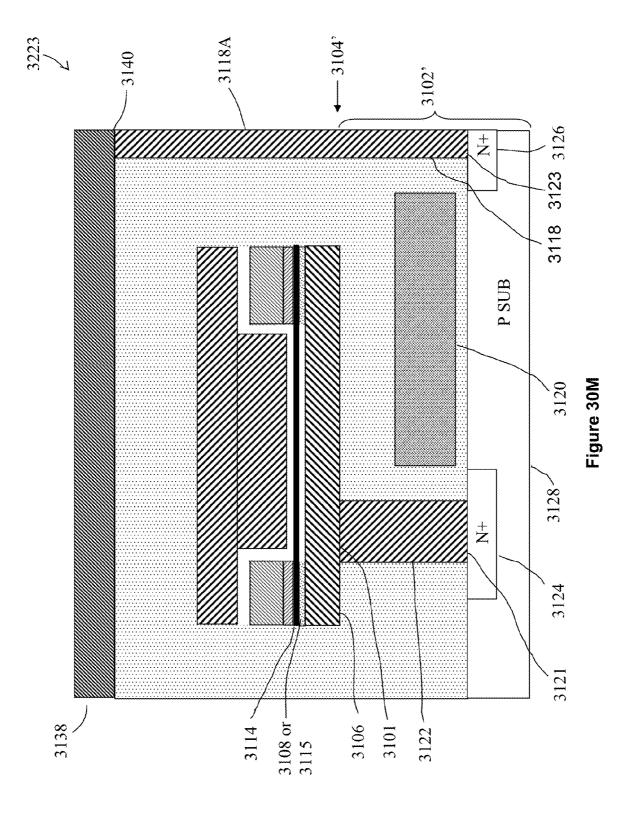

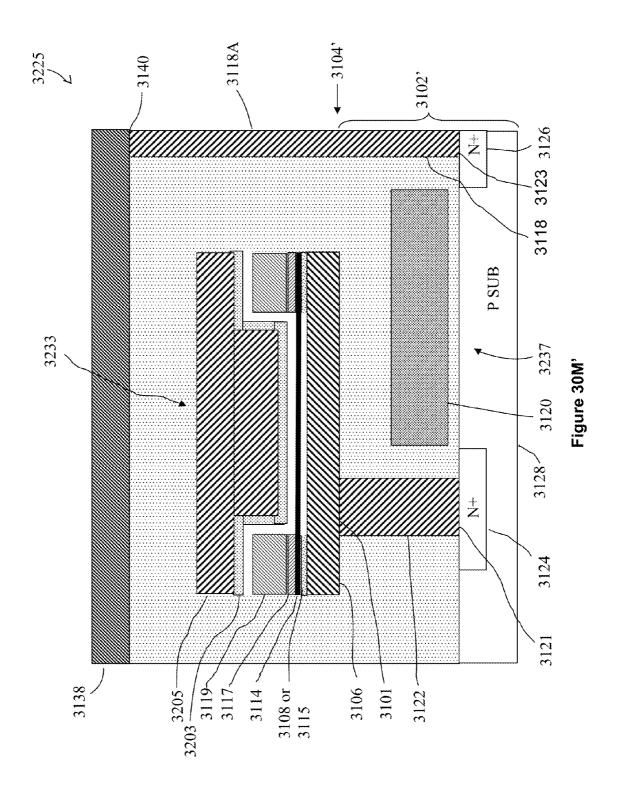

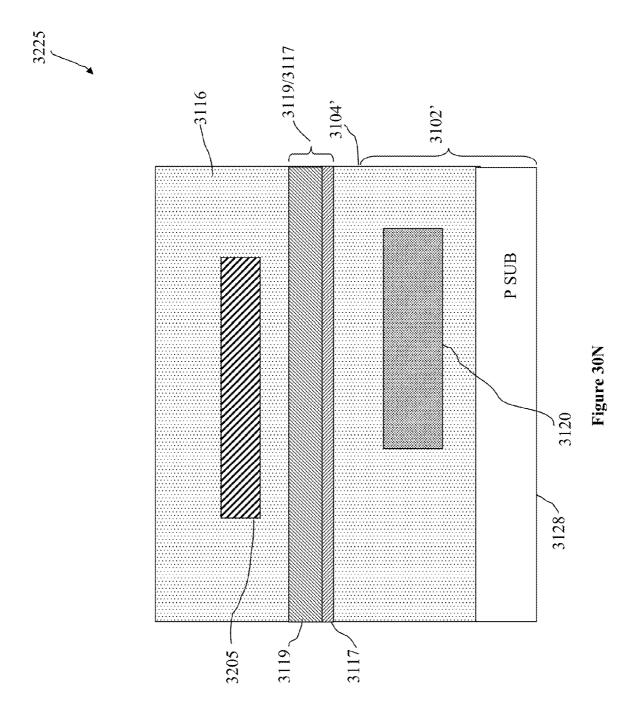

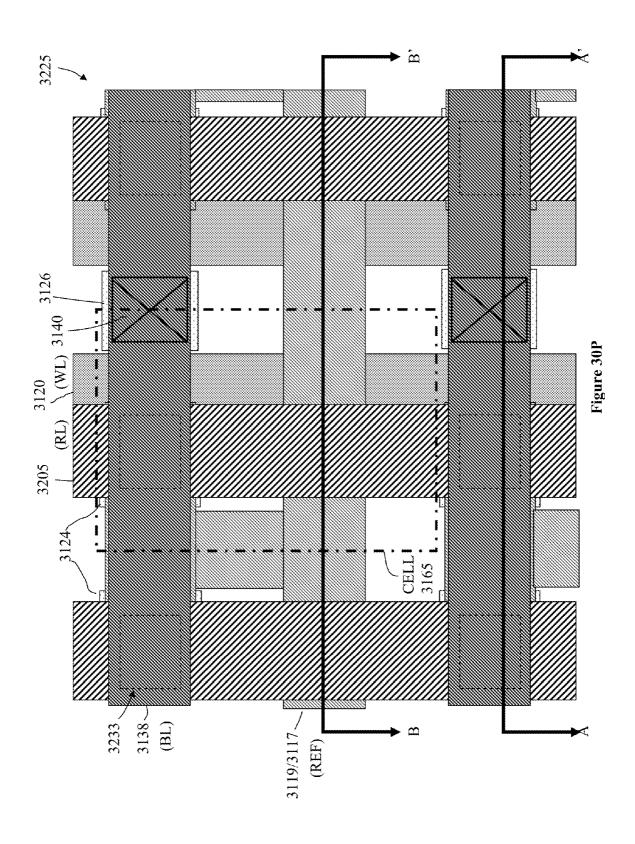

[0068] FIGS. 30A-P (exclusive of 0) illustrate intermediate structures according to certain aspects of the invention;

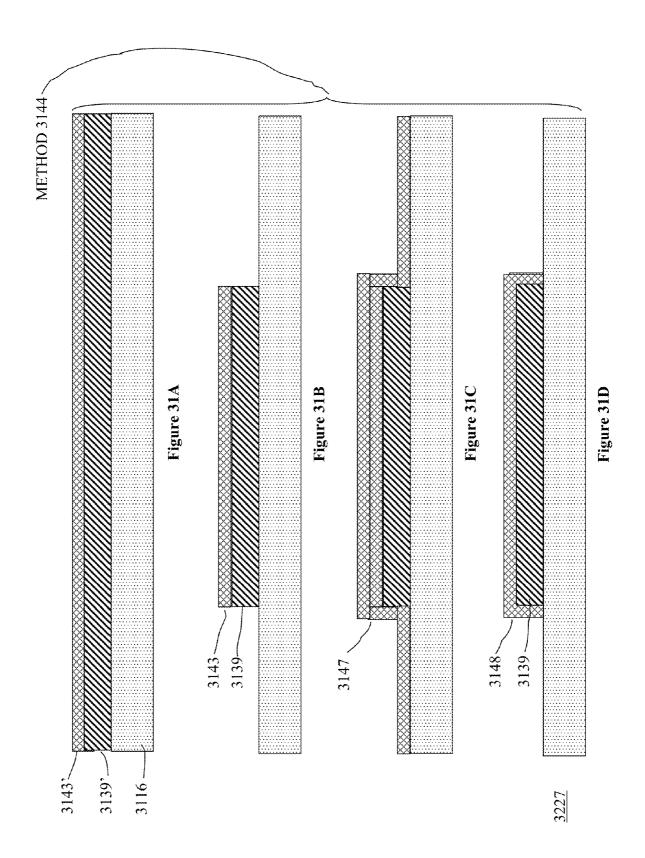

[0069] FIGS. 31A-D illustrate intermediate structures according to certain aspects of the invention;

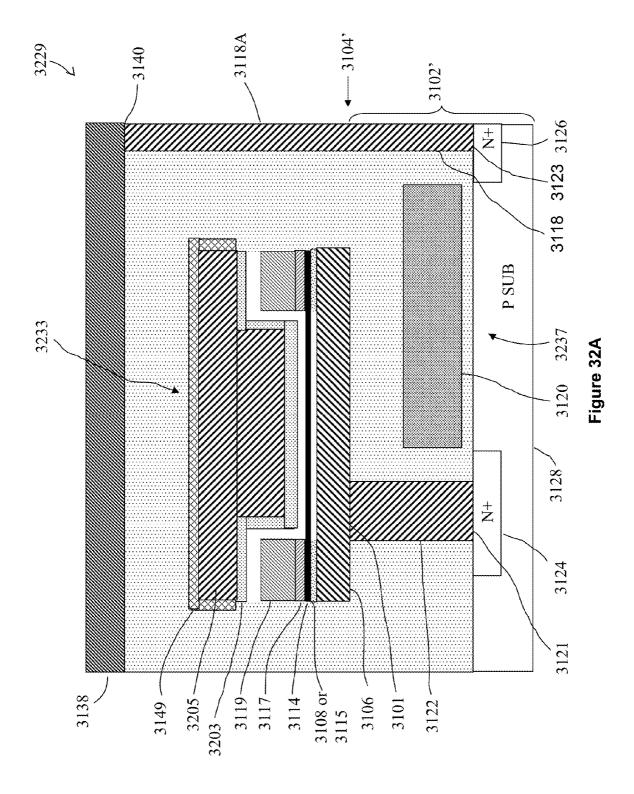

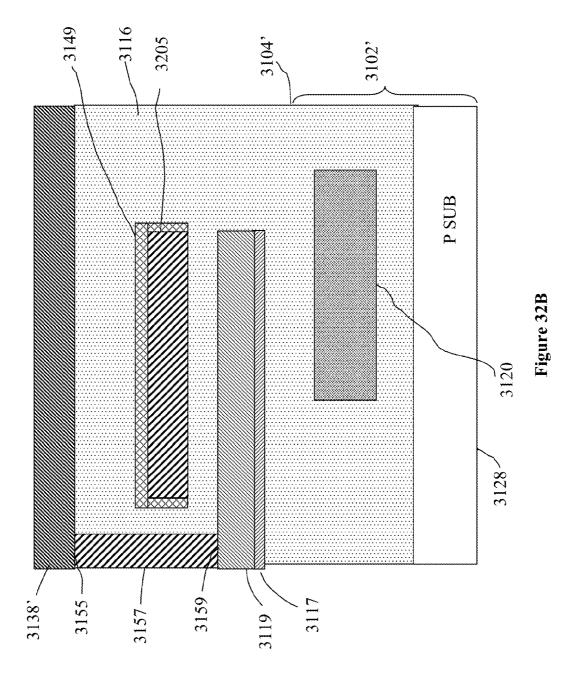

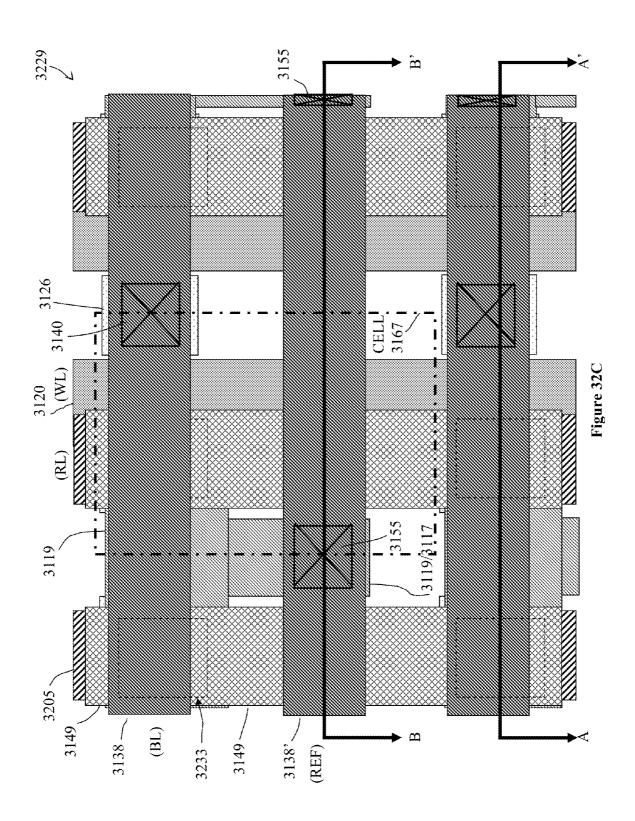

[0070] FIGS. 32A-B illustrate cross sections of an embodiment of the invention;

[0071] FIG. 32C illustrates a plan view of an embodiment of the invention;

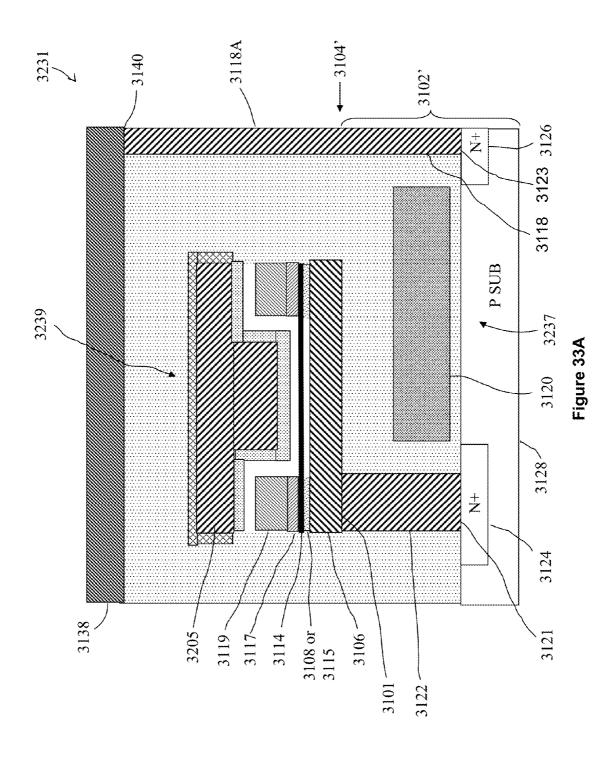

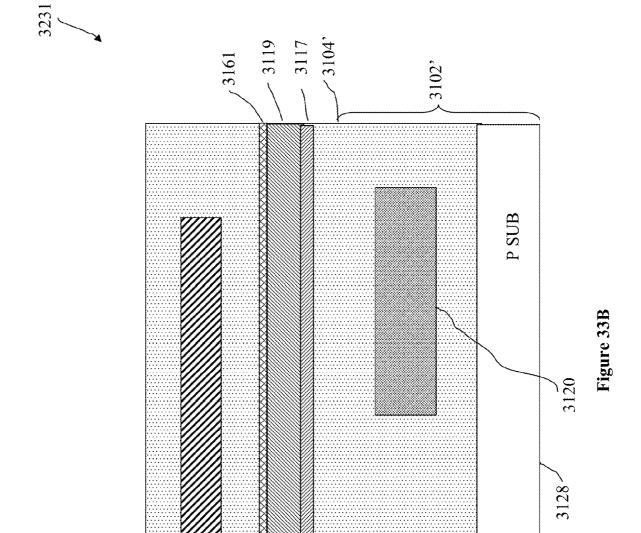

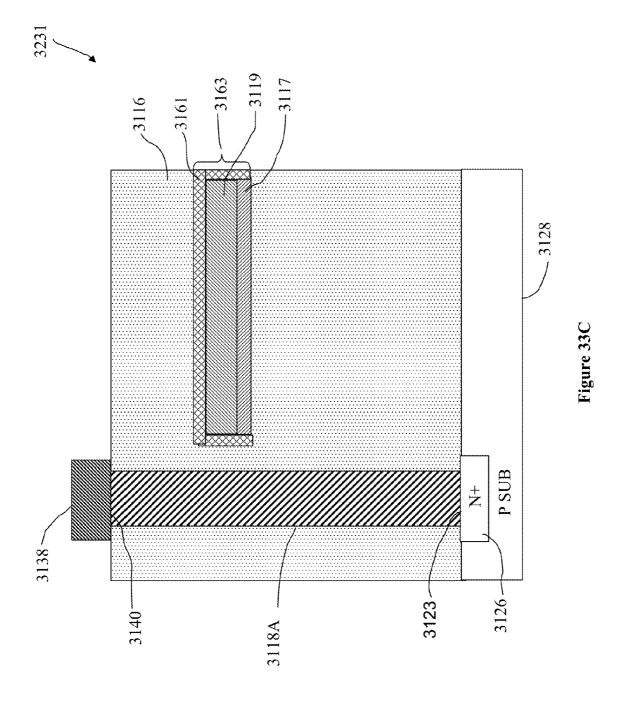

[0072] FIGS. 33A-C illustrate cross sections of an embodiment of the invention;

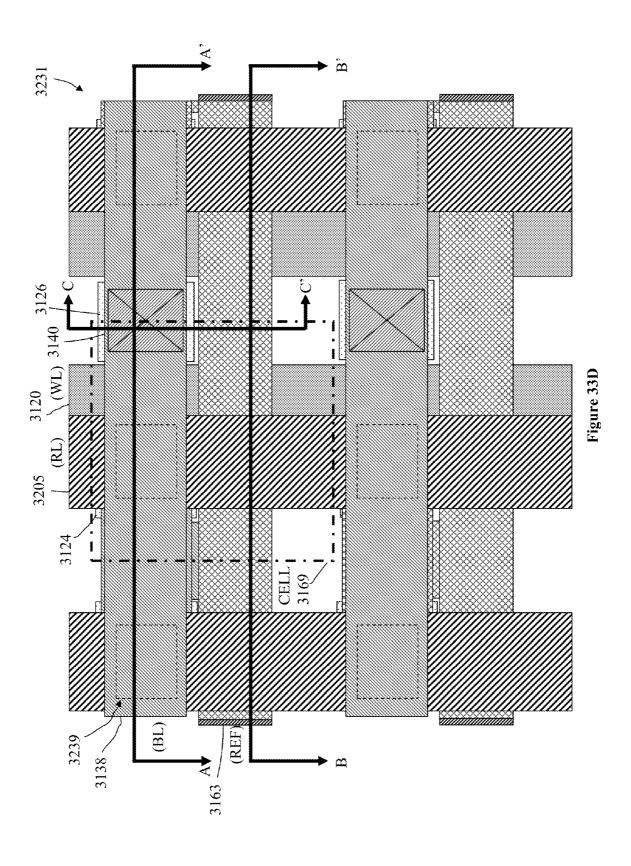

[0073] FIG. 33D illustrates a plan view of an embodiment of the invention:

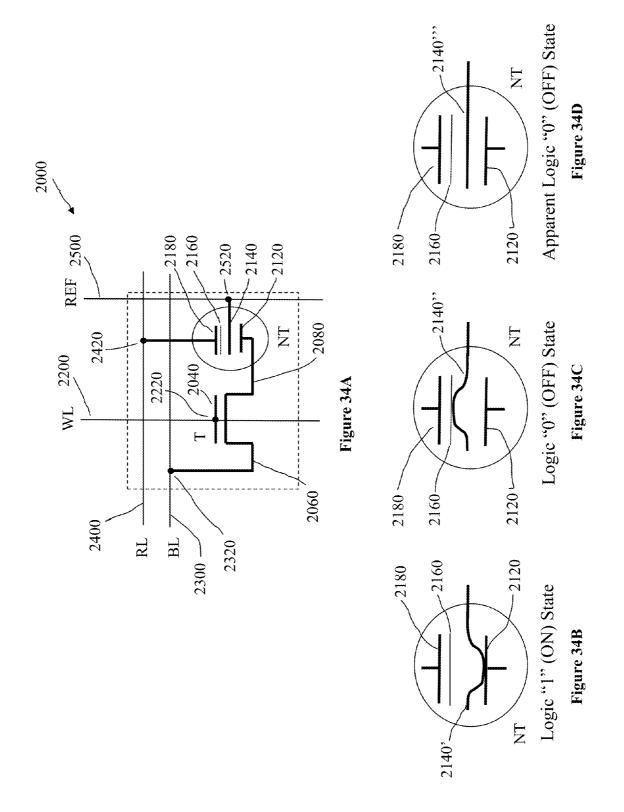

[0074] FIGS. 34A-D illustrate schematics of circuitry according to certain aspects of the invention;

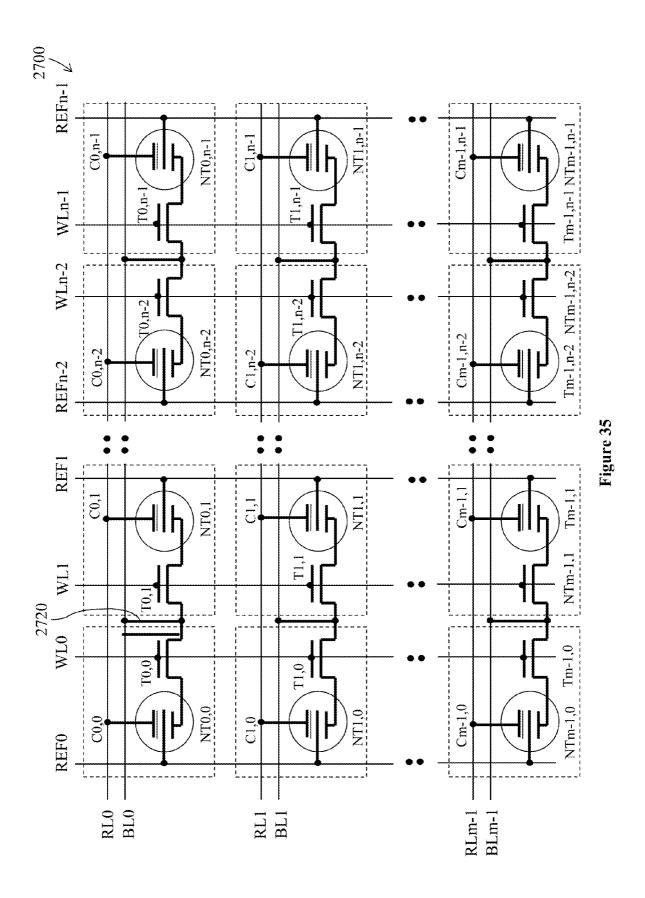

[0075] FIG. 35 illustrates schematics of memory arrays according to certain aspects of the invention;

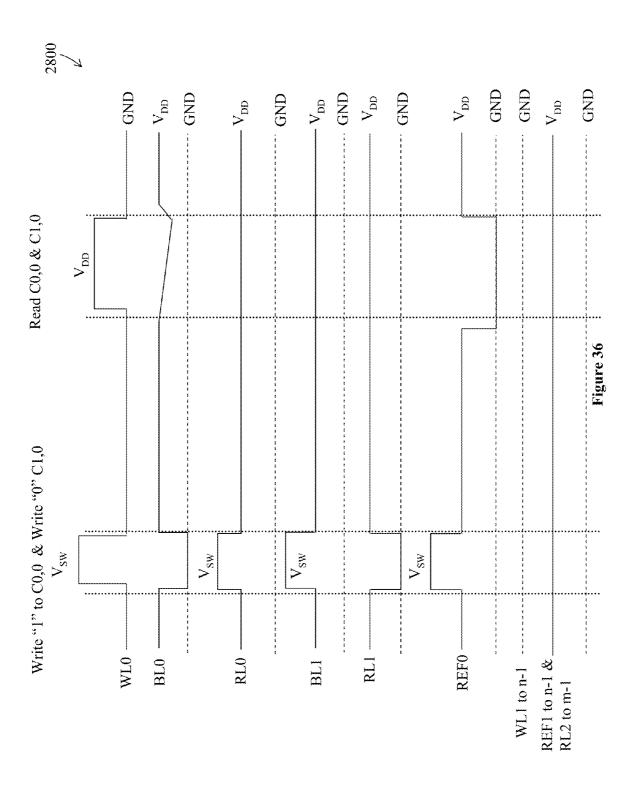

[0076] FIG. 36 illustrates operational waveforms of a memory array according to one aspect of the invention;

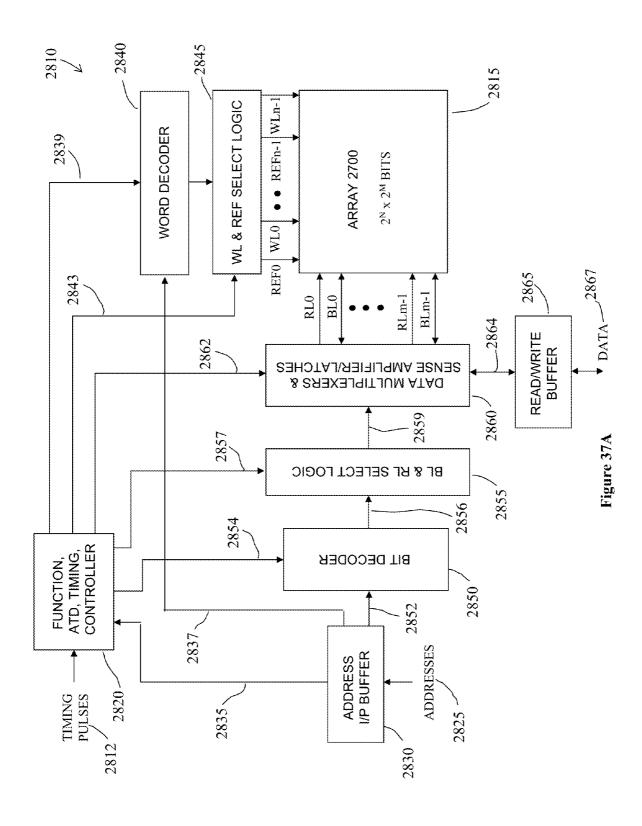

[0077] FIG. 37A illustrates a diagram outlining a memory array system according to one aspect of the invention;

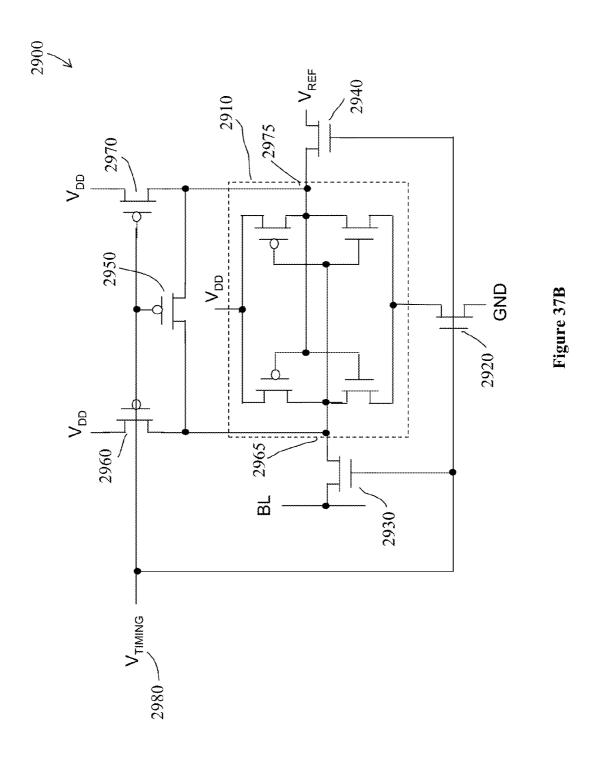

[0078] FIG. 37B is a schematic of a cell according to once aspect of the invention;

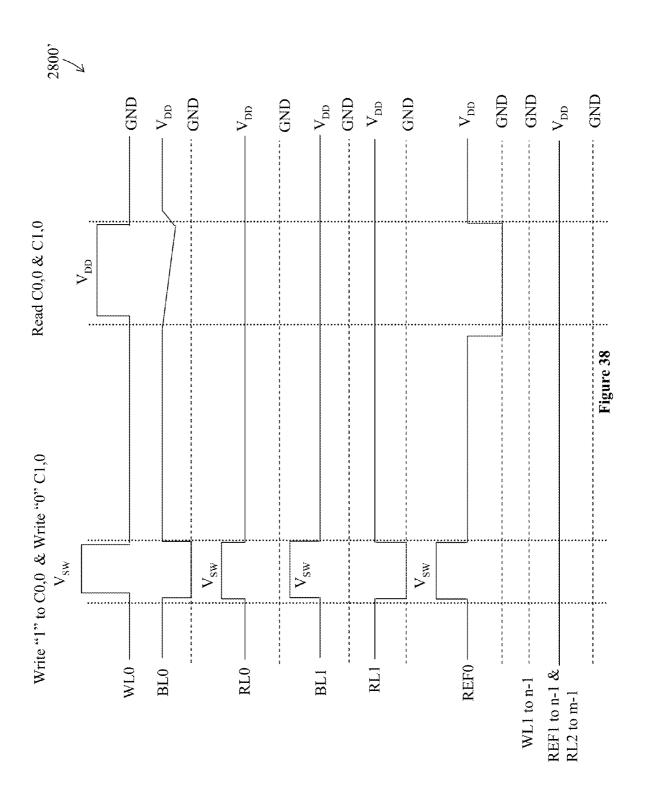

[0079] FIG. 38 illustrates operational waveforms of a memory array according to one aspect of the invention;

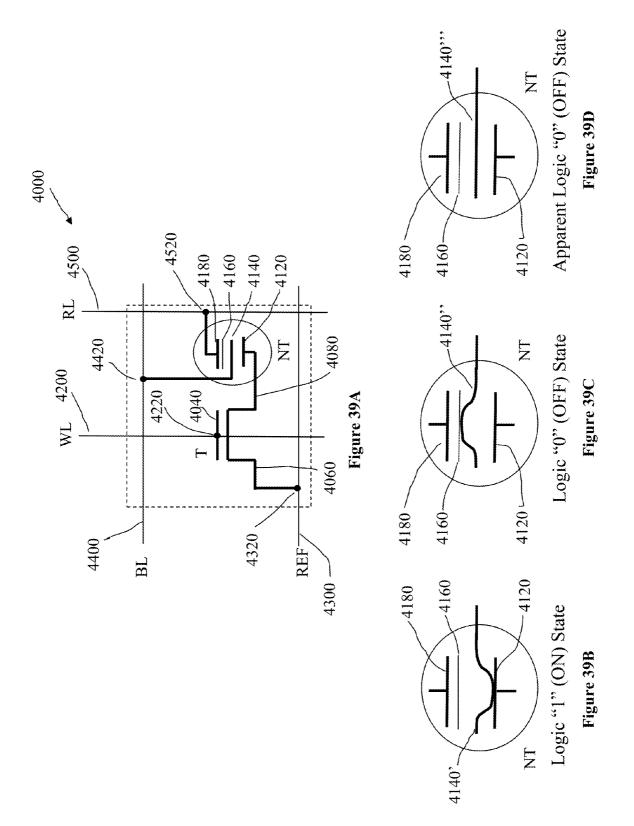

[0080] FIG. 39A-D illustrate schematics of circuitry according to certain aspects of the invention;

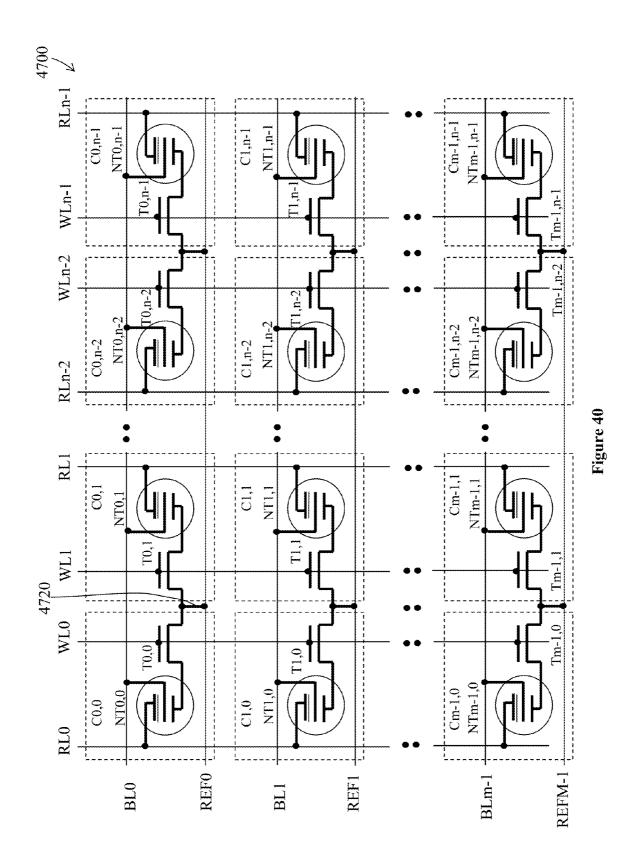

[0081] FIG. 40 illustrates a schematic of an NRAM system, according to one embodiment of the invention;

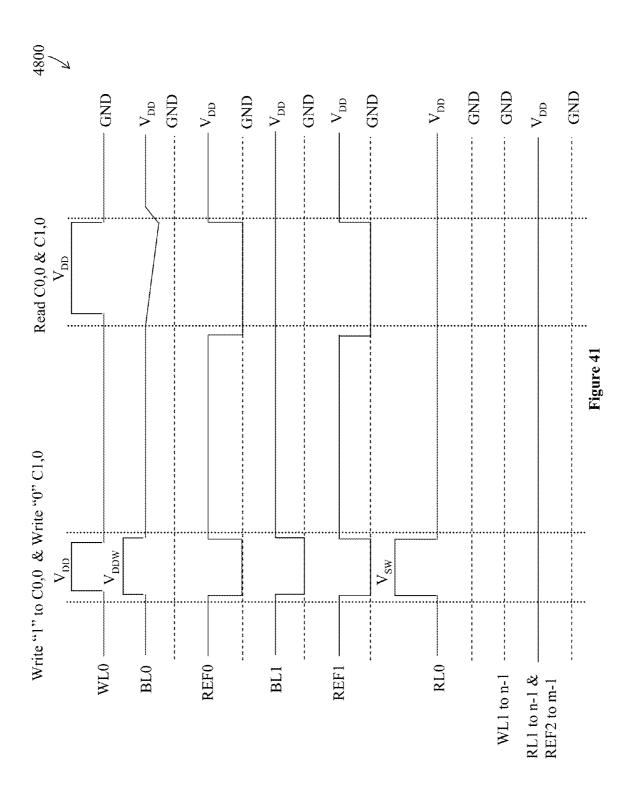

[0082] FIG. 41 illustrates the operational waveforms of a memory array according to one aspect of the invention;

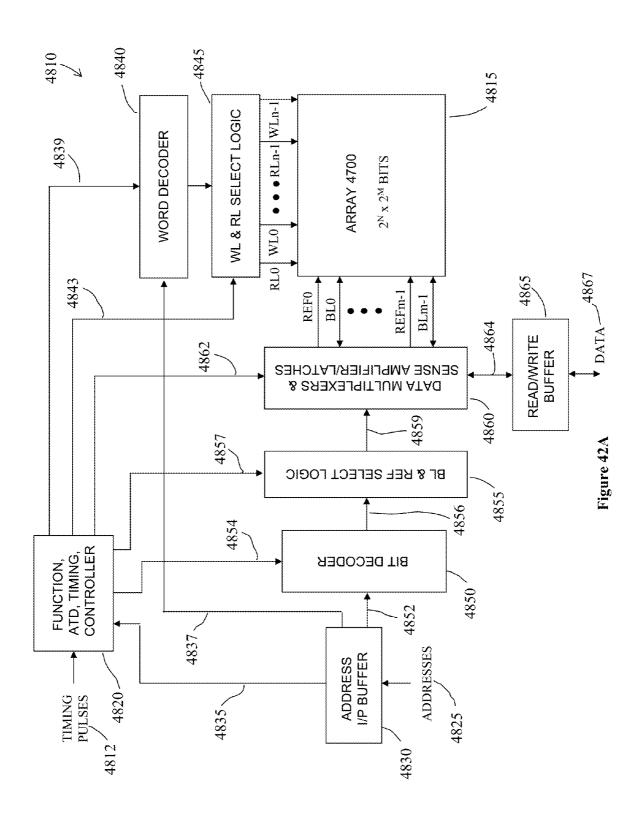

[0083] FIG. 42A illustrates a diagram outlining a memory array system according to one aspect of the invention;

[0084] FIG. 42B is a schematic of a cell according to once aspect of the invention;

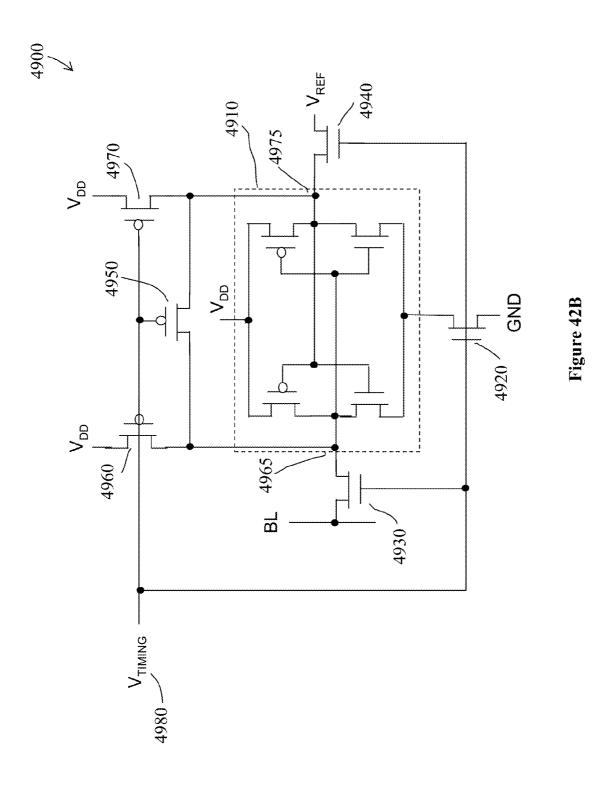

[0085] FIG. 43 illustrates the operational waveforms of a memory array according to one aspect of the invention;

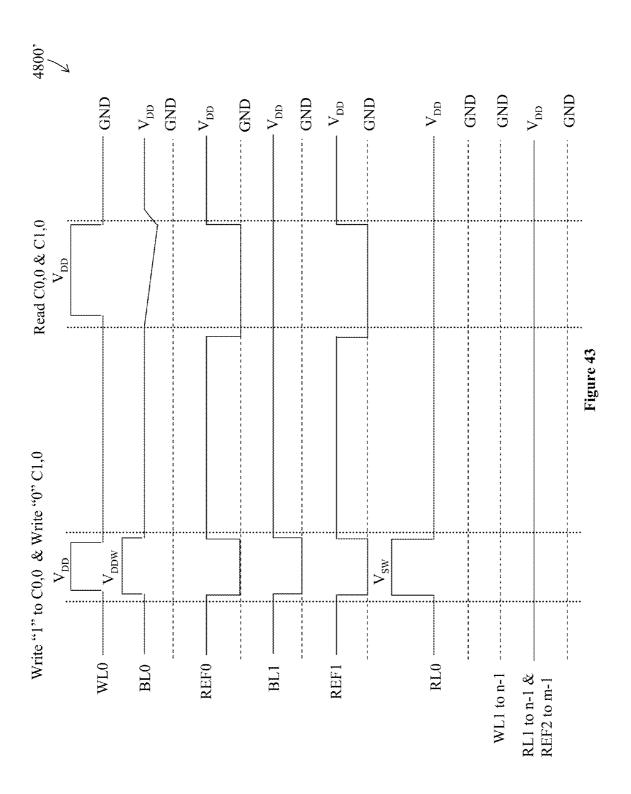

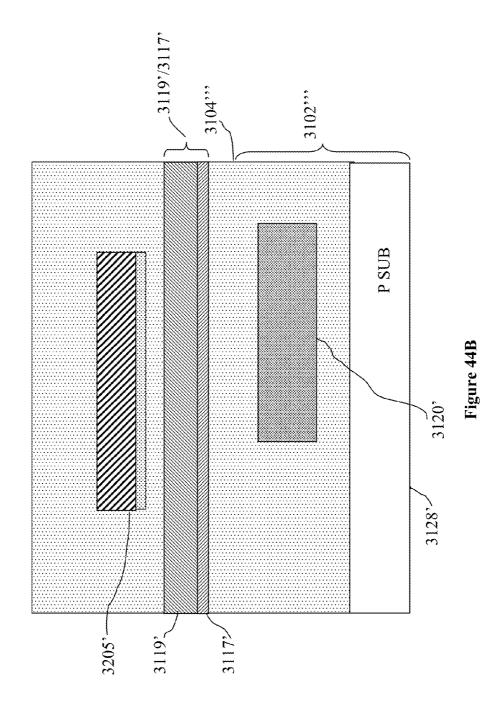

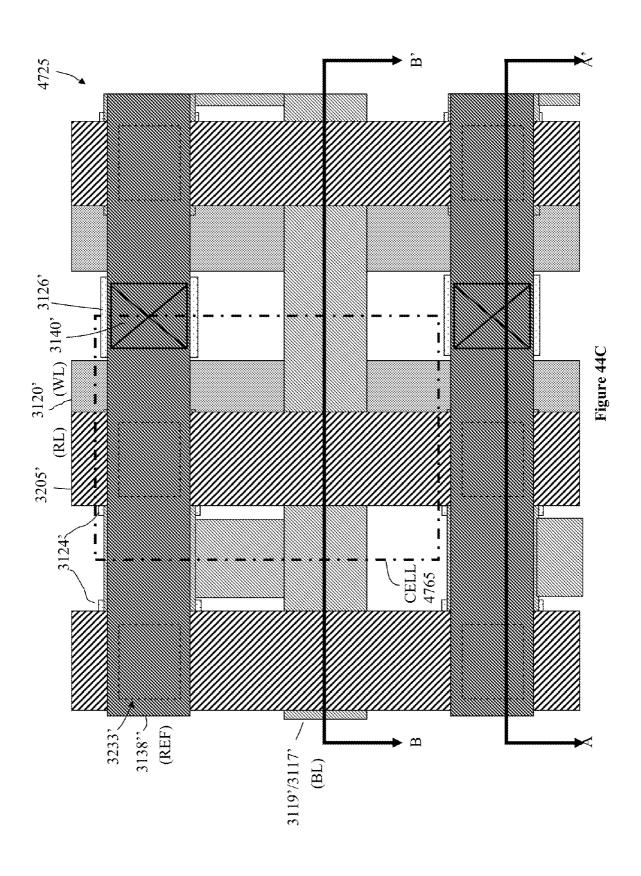

[0086] FIGS. 44A-B illustrate cross sections of memory arrays according to aspects of the invention;

[0087] FIG. 44C illustrates a plan view of a memory array structure according to one aspect of the invention;

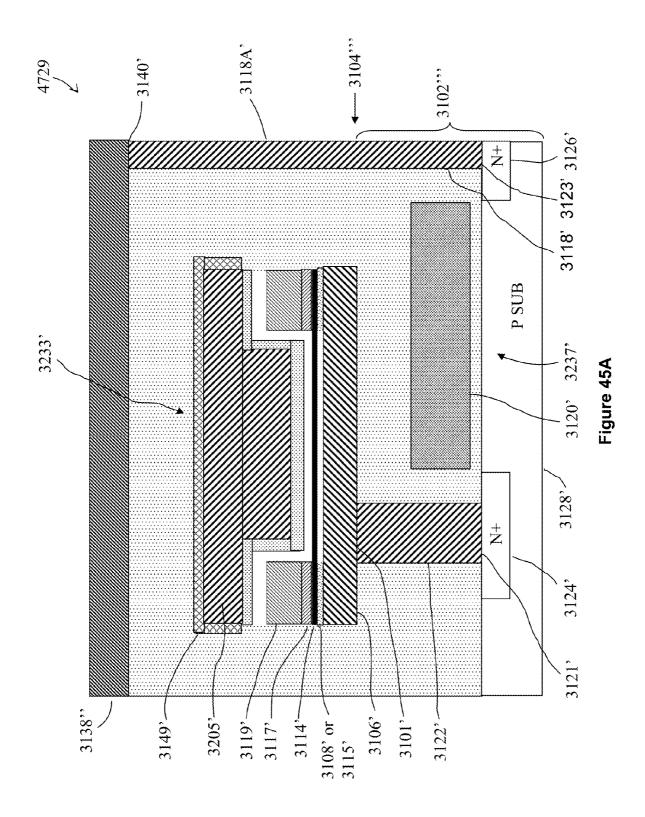

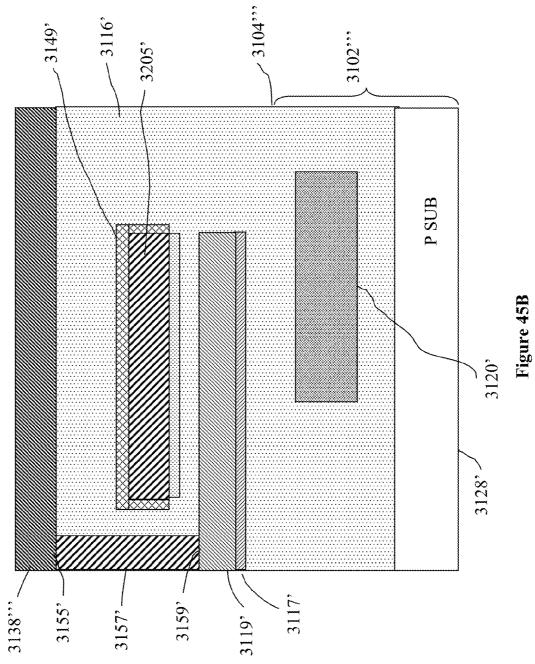

[0088] FIGS. 45A-B illustrate cross sections of memory arrays according to aspects of the invention;

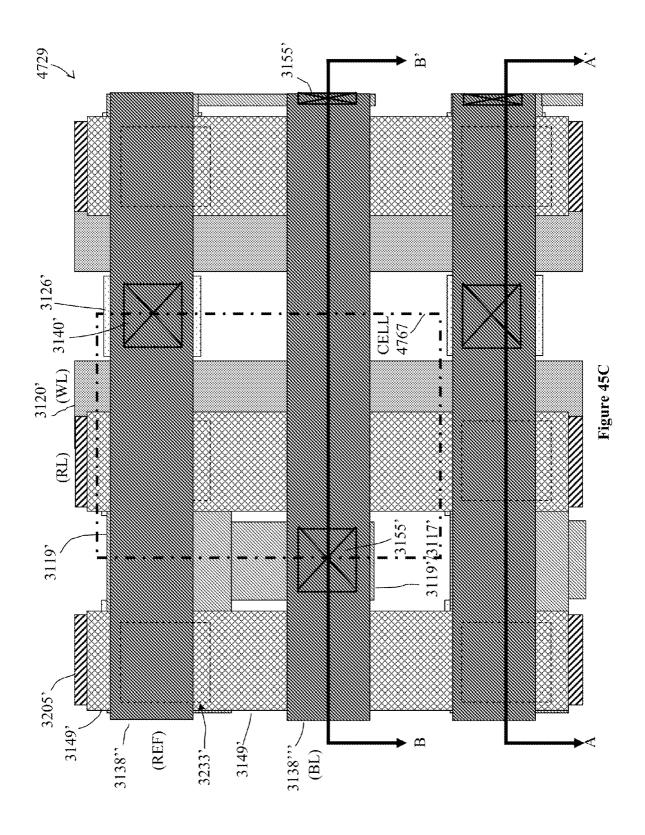

[0089] FIG. 45C illustrates a plan view of a memory array structure according to one aspect of the invention;

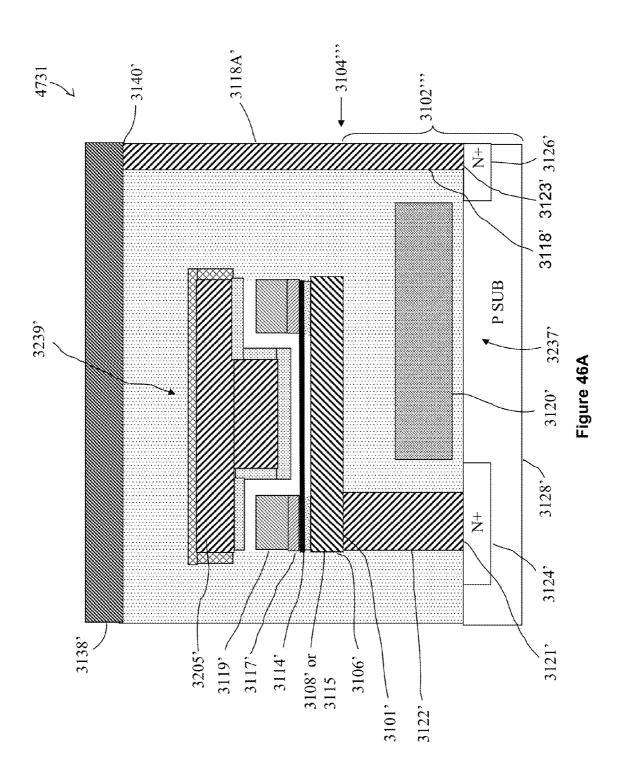

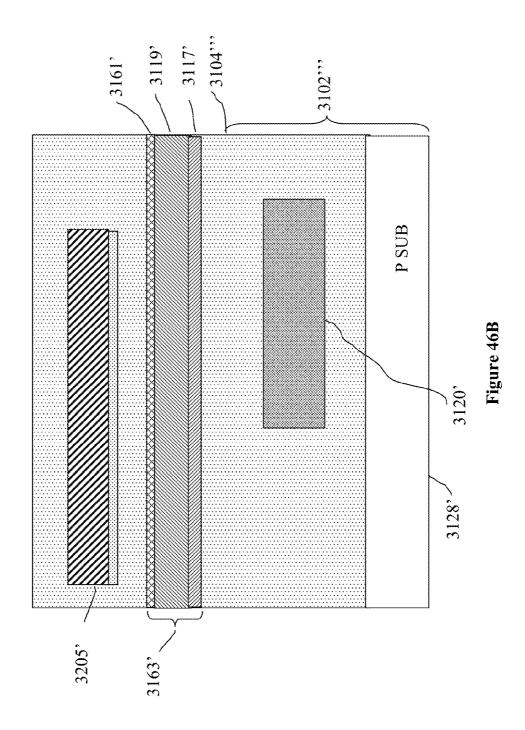

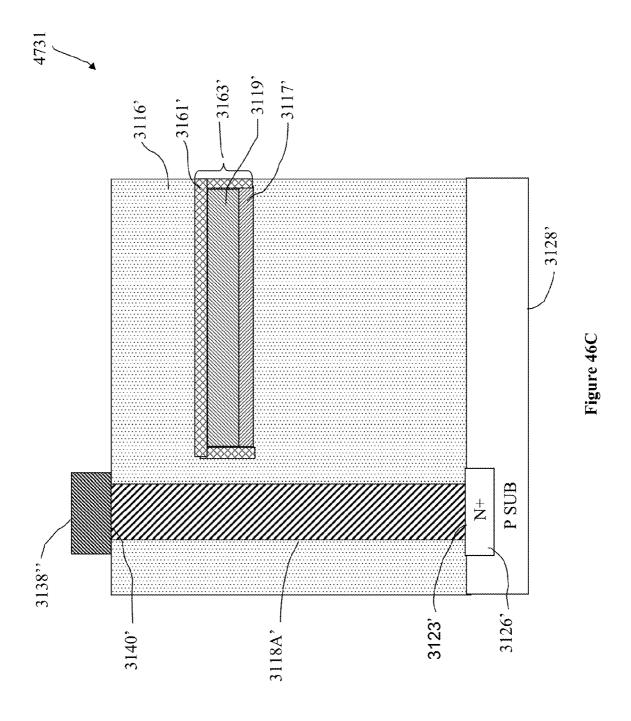

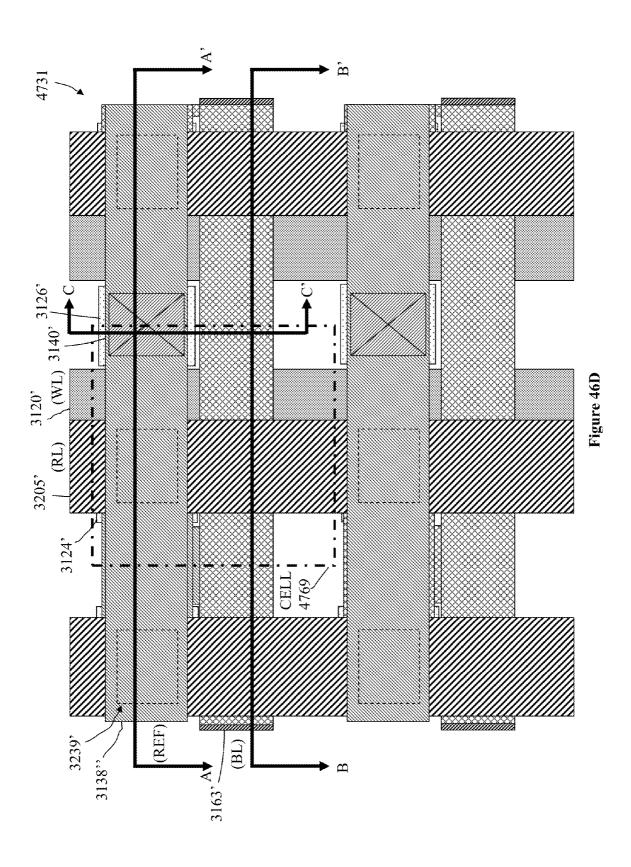

[0090] FIGS. 46A-C illustrate cross sections of structures according to certain aspects of the invention;

[0091] FIG. 46D illustrates a plan view of a memory array structure according to one aspect of the invention;

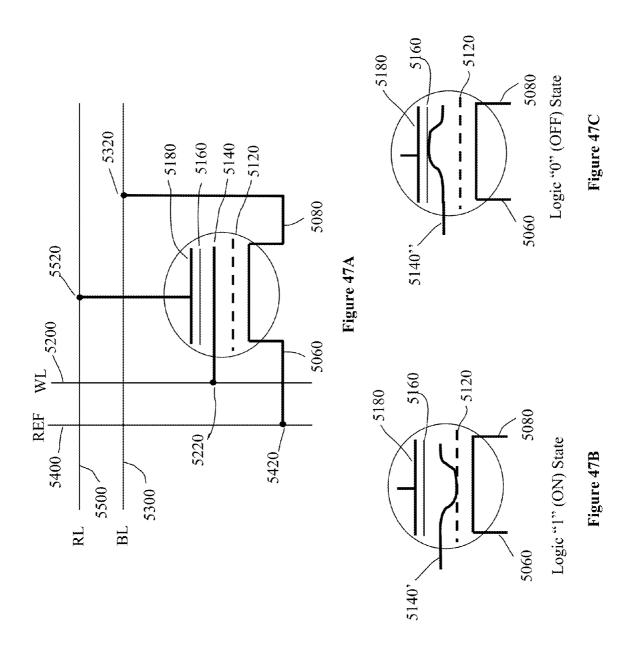

[0092] FIGS. 47A-C illustrate schematics of circuitry for a non-volatile field effect device according to aspects of the invention:

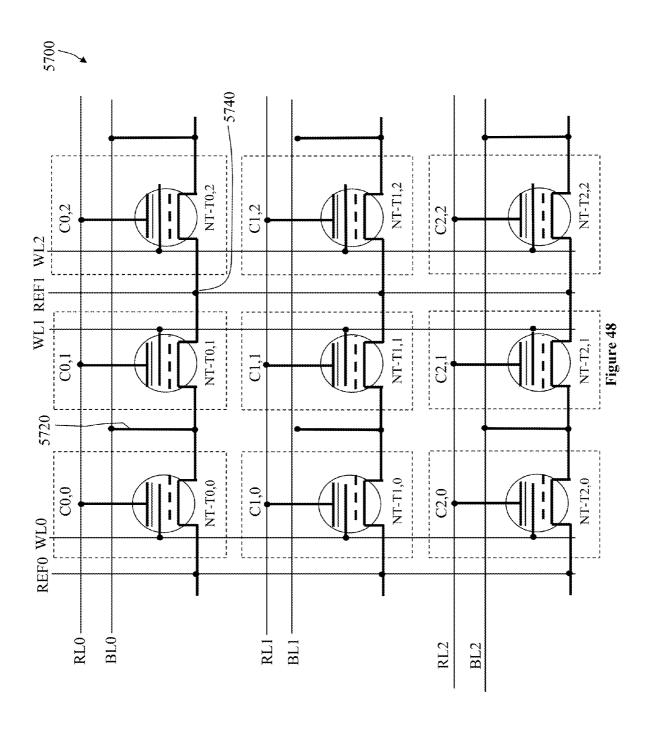

[0093] FIG. 48 illustrates a schematic of an NRAM system according to one aspect of the invention;

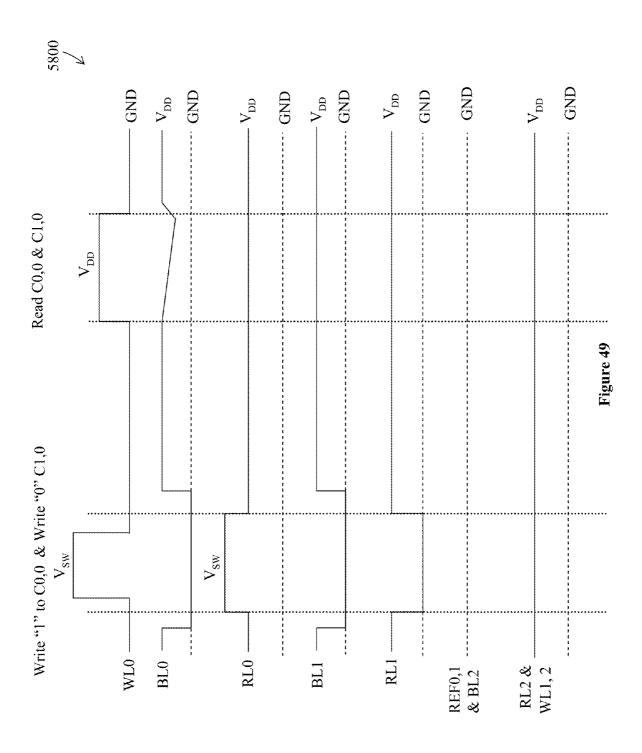

[0094] FIG. 49 illustrates operational waveforms of a memory array according to one aspect of the invention;

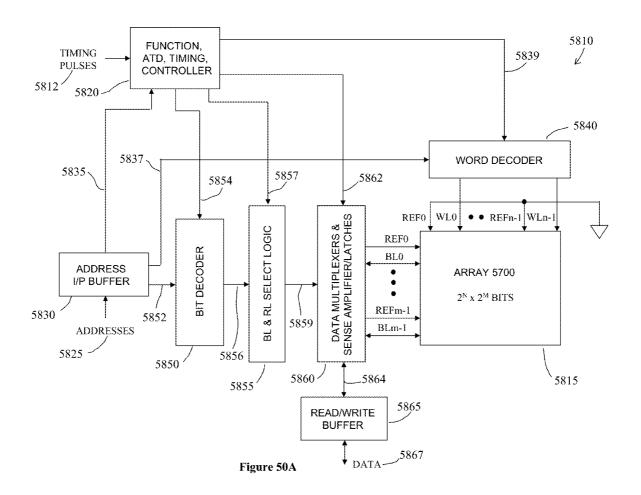

[0095] FIG. 50A illustrates a diagram outlining a memory array system according to one aspect of the invention;

[0096] FIG. 50B is a schematic of a cell according to once aspect of the invention;

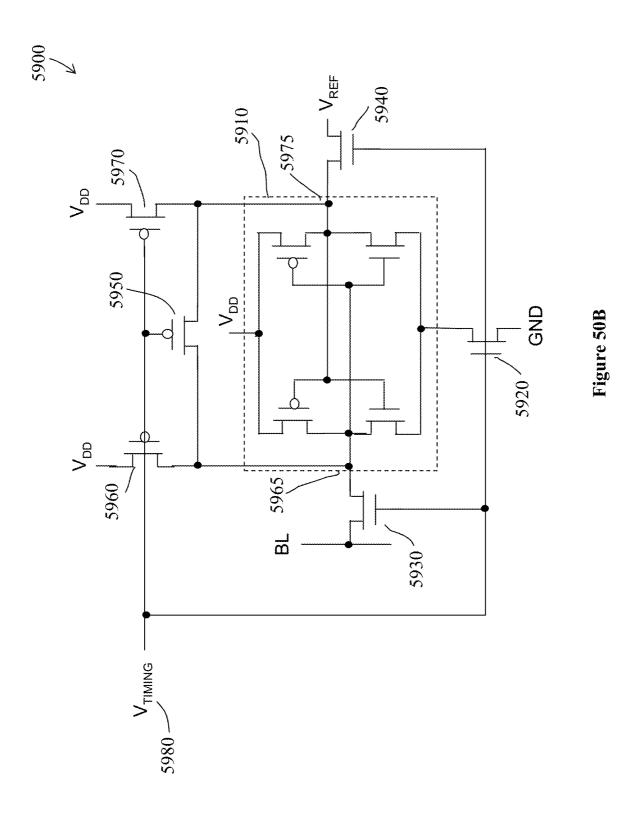

[0097] FIG. 51 illustrates operational waveforms of a memory array according to one aspect of the invention;

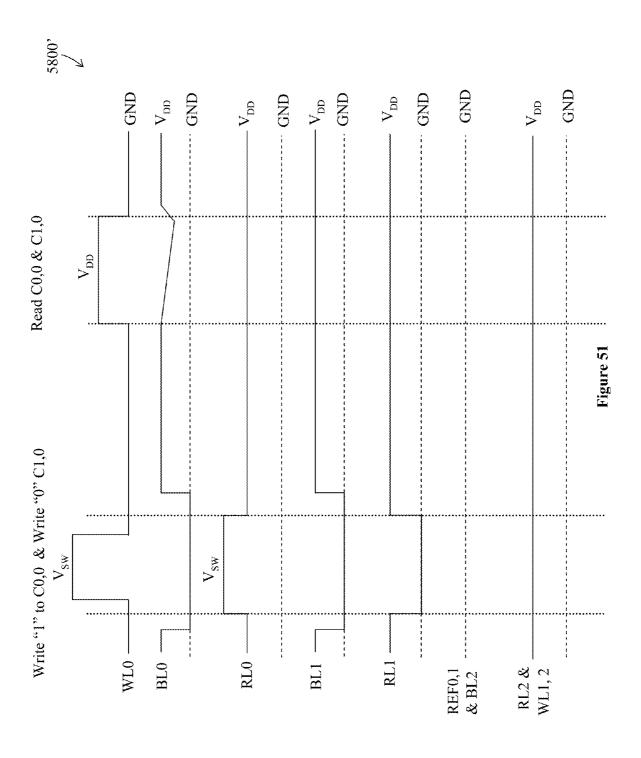

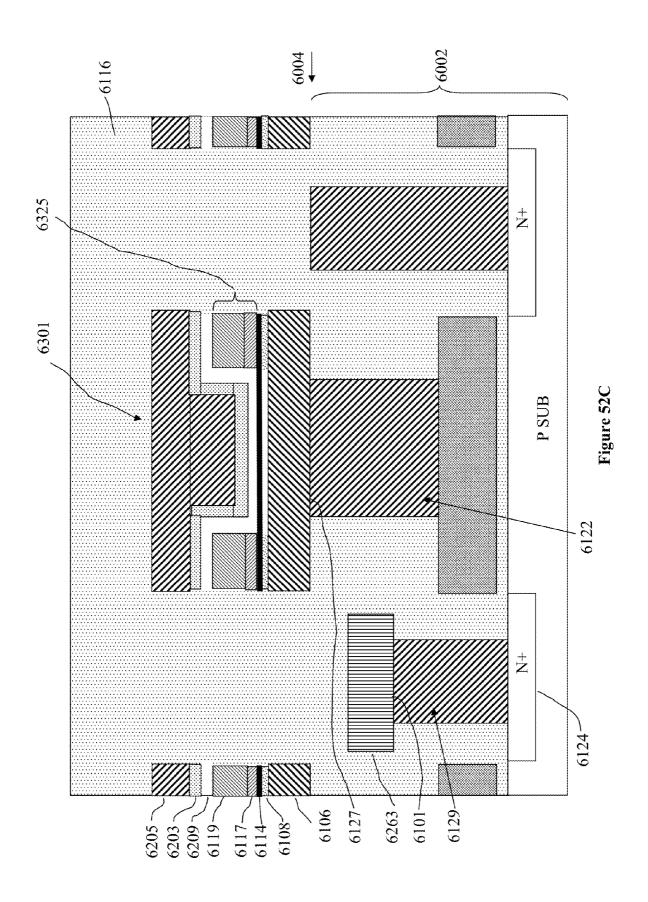

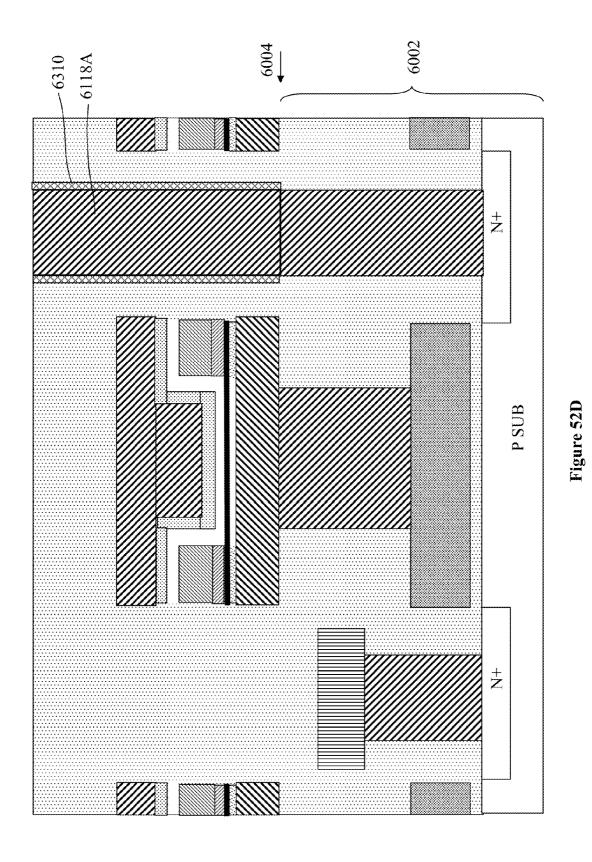

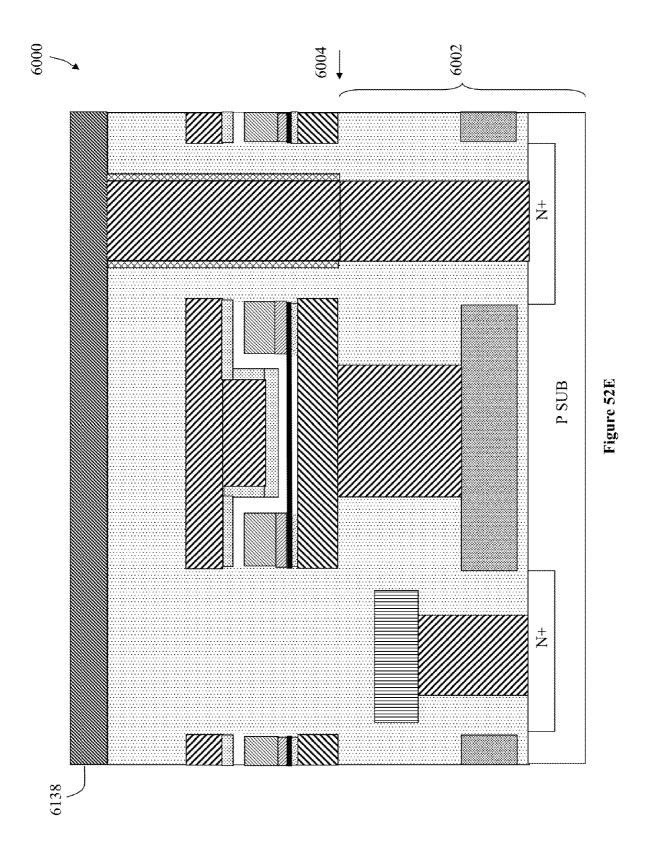

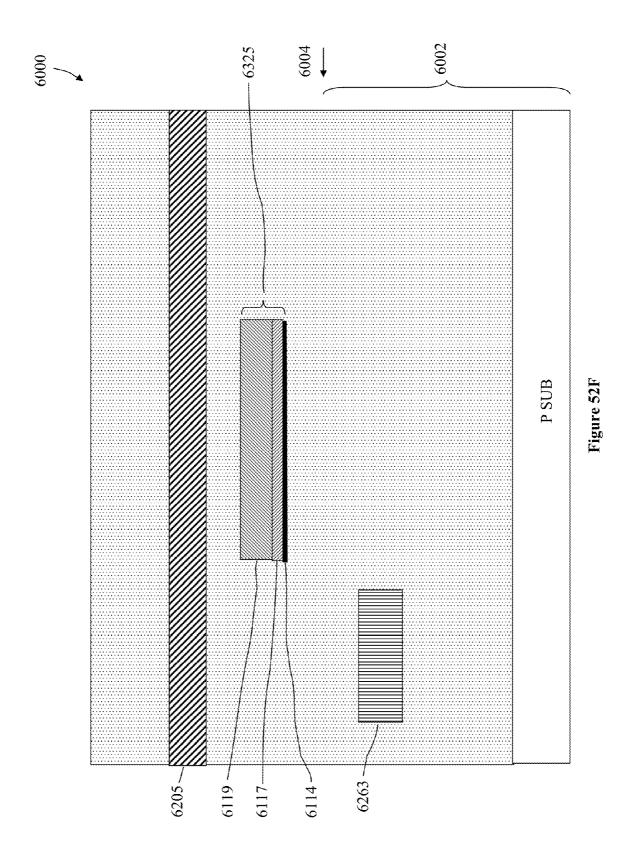

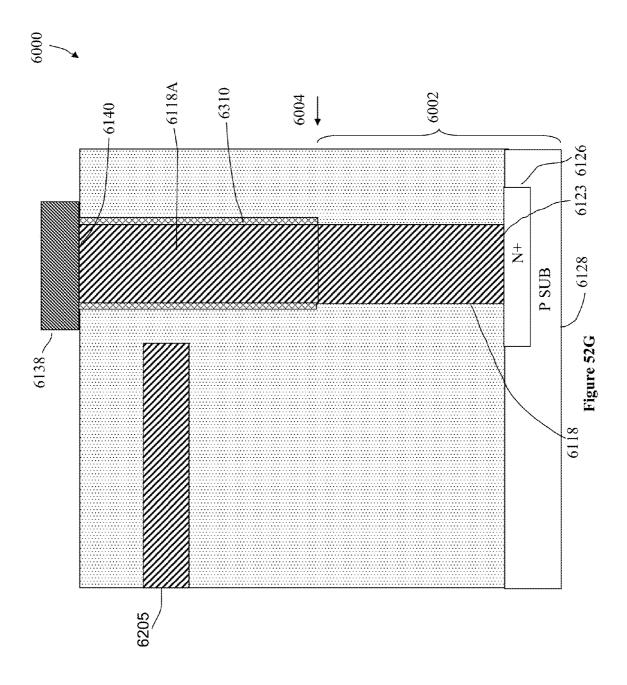

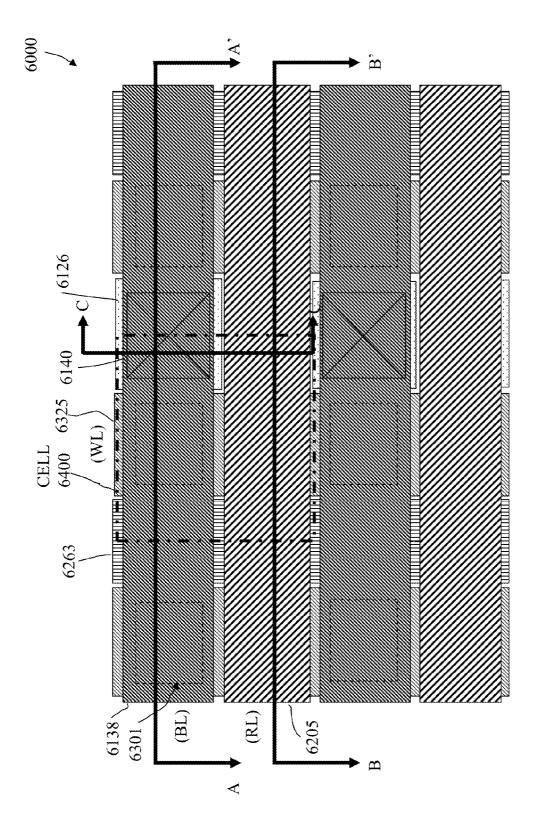

[0098] FIGS. 52A-G illustrate cross sections of exemplary structures according to aspects of the invention;

[0099] FIG. 52H illustrates a plan view of an exemplary structure according to one aspect of the invention;

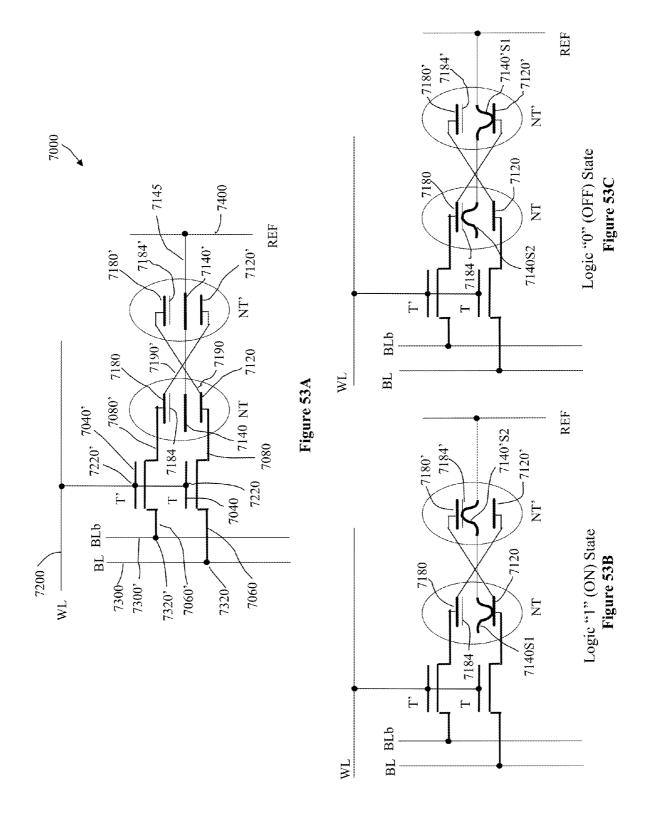

[0100] FIGS. 53A-C illustrate schematics of circuitry for two controlled source non-volatile field effect devices according to certain aspects of the invention;

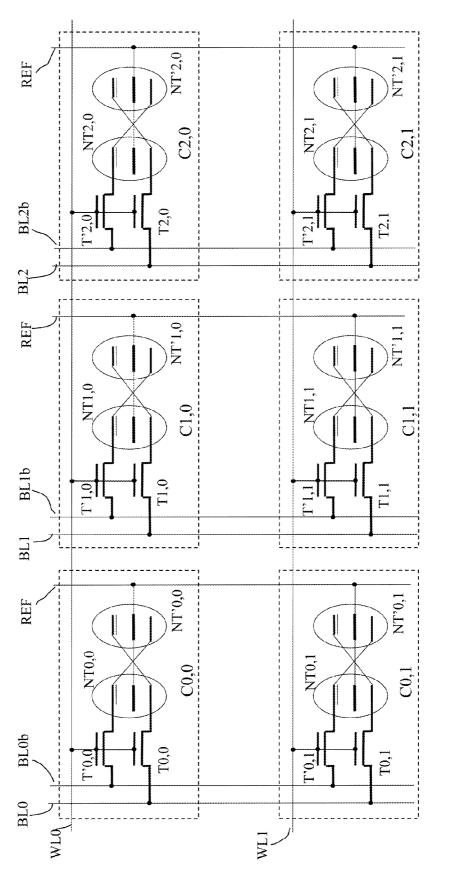

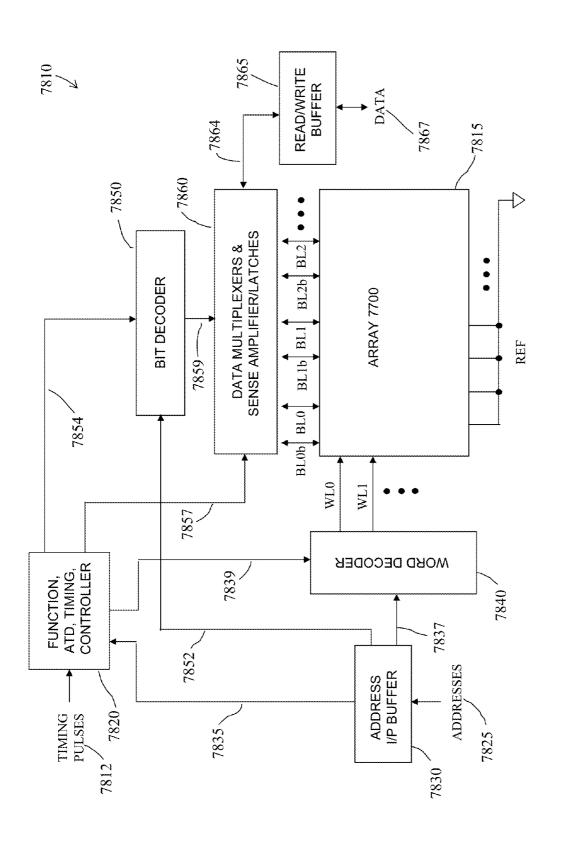

[0101] FIG. 54 illustrates a schematic of an NRAM system according to one aspect of the invention;

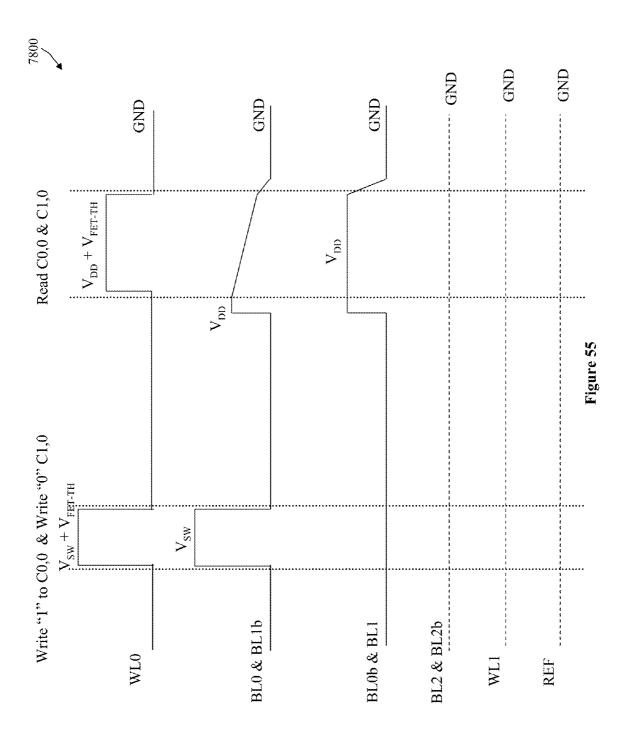

[0102] FIG. 55 illustrates the operational waveforms of a memory array according to one aspect of the invention;

[0103] FIG. 56A illustrates a diagram outlining a memory array system according to one aspect of the invention;

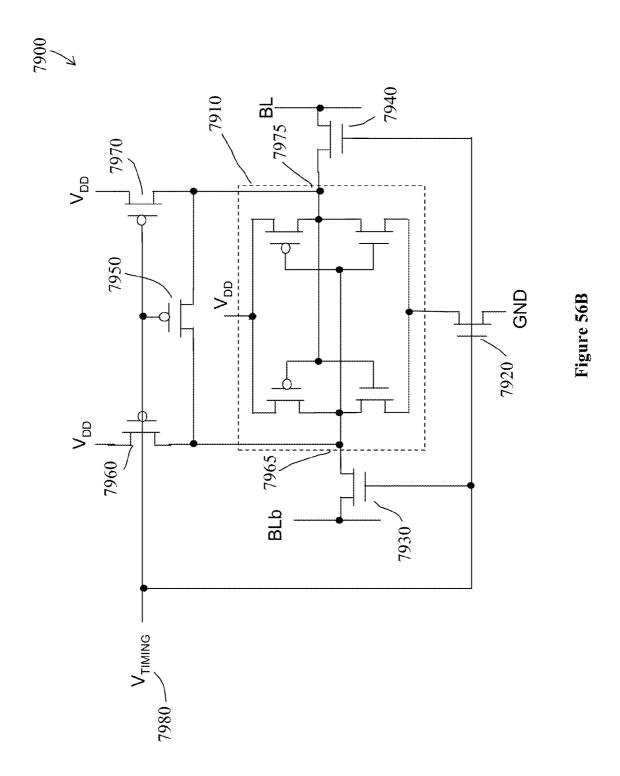

[0104] FIG. 56B is a schematic of a cell according to once aspect of the invention;

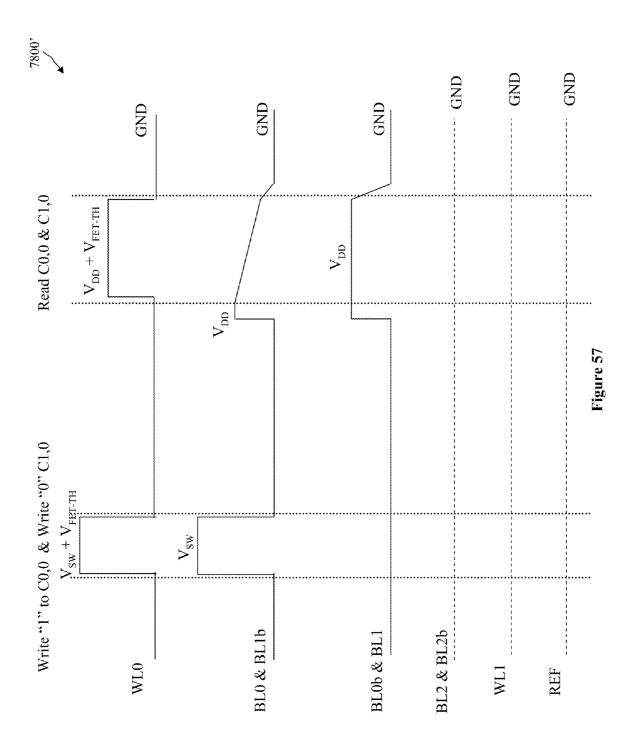

[0105] FIG. 57 illustrates the operational waveforms of a memory array according to one aspect of the invention;

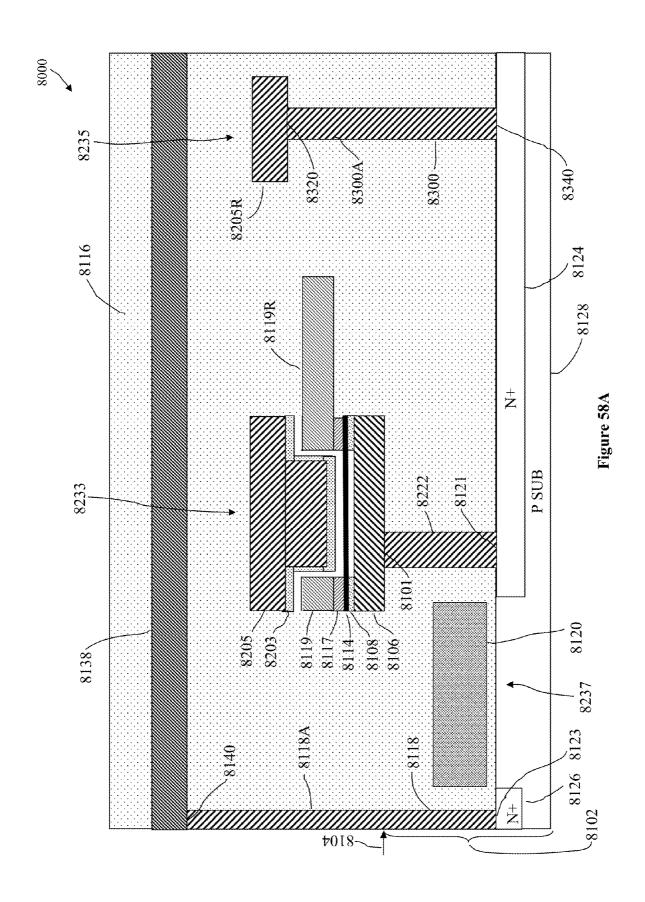

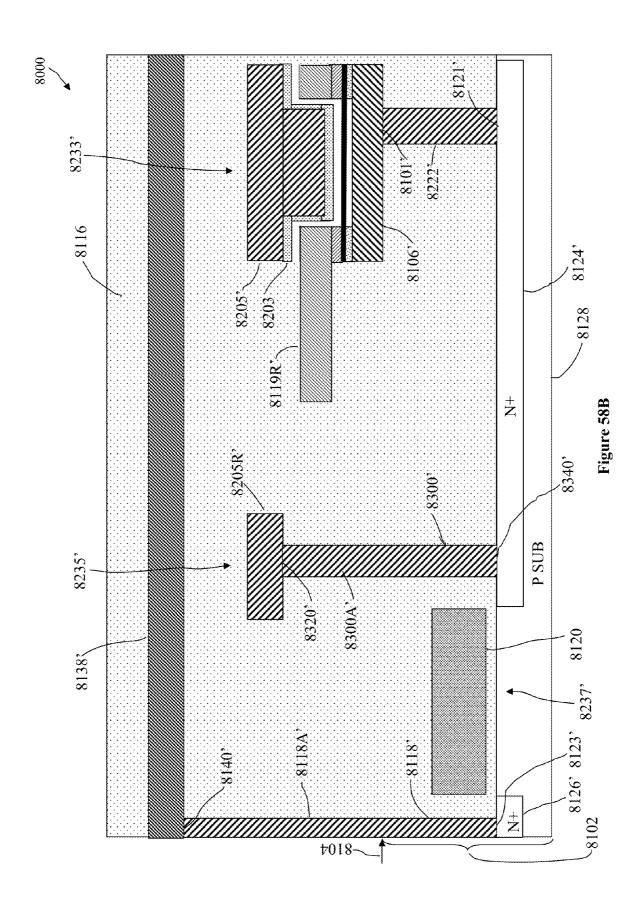

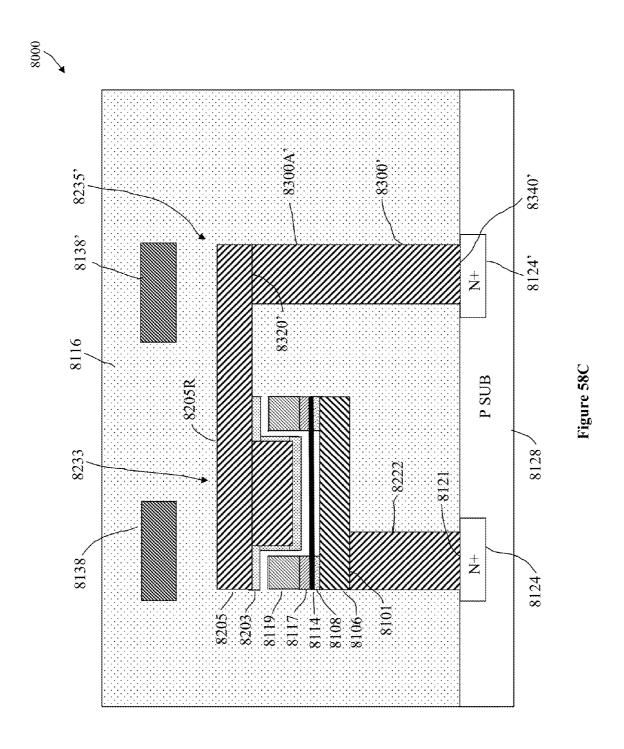

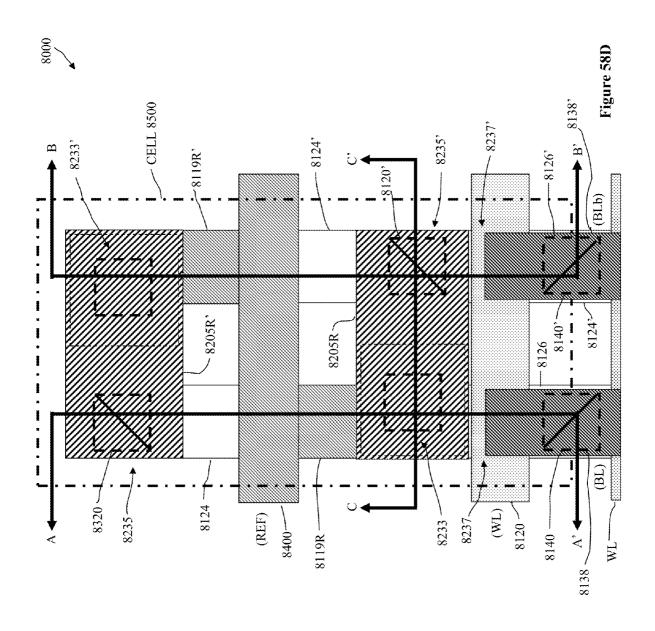

[0106] FIGS. 58A-C illustrate cross sections of exemplary structures according to aspects of the invention;

[0107] FIG. 58D illustrates a plan view of an exemplary structure according to one aspect of the invention.

### DETAILED DESCRIPTION

[0108] Preferred embodiments of the invention provide a field effect device that acts like a FET in its ability to create an electronic communication channel between a drain and a source node, under the control of a gate node. However, the preferred field effect devices further include a separate control structure to non-volatilely control the electrical capabilities of the field effect device. More specifically, the control structure uses carbon nanotubes to provide non-volatile switching capability that independently control the operation of the drain, source, or gate node of the field effect device. By doing so, the control structure provides non-volatile state behavior to the field effect device. Certain embodiments provide non-volatile RAM structures. Preferred embodiments are scalable to large memory array structures. Preferred embodiments use processes that are compatible with CMOS circuit manufacture. While the illustrations combine NMOS FETs with carbon nanotubes, it should be noted that based on the principle of duality in semiconductor devices, PMOS FETs may replace NMOS FETs, along with corresponding changes in the polarity of applied voltages

#### Overview

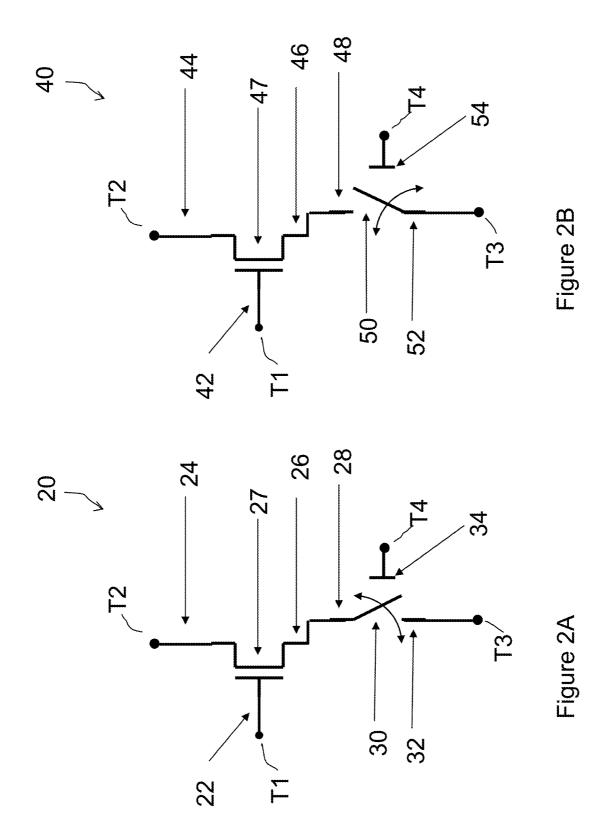

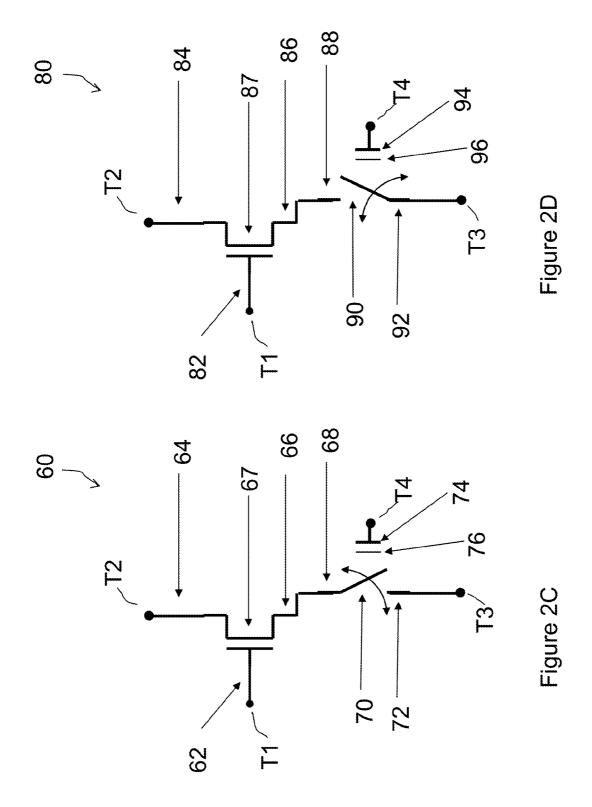

[0109] FIGS. 2A-L illustrate schematics of three models of preferred embodiments of the invention. As will be explained further, below, a preferred field effect device includes a control structure using nanotubes to provide non-volatile behavior as a result of the control structure.

Field Effect Devices (FEDs) with Controllable Sources

[0110] Field effect devices (FEDs) with controllable sources may also be referred to as nanotube (NT)-on-Source. FIG. 2A illustrates a schematic for field effect device (FED1) 20. The FED1 device 20 has a terminal T1 connected to gate 22, a terminal T2 connected to drain 24, and a controllable source 26. Like a typical field effect device (e.g., transistor 10 of FIG. 1) the gate node may be used to create a field to induce a conductive channel in channel region 27 between the drain 24 and a (controllable) source 26. In this case, the source 26 is controllable so that it may be in open or closed communication as illustrated with the switch 30. Switch 30, like all nanofabric articles referred to below, is fabricated using one or more carbon nanotubes (CNTs, or NTs) as described in incorporated references. Switch 30 is preferably physically and electrically connected to controllable source 26 by contact 28. Switch 30 may be displaced to contact switch-plate (switch-node) 32, which is connected to a terminal T3. Switch **30** may be displaced to contact release-plate (release-node) 34, which is connected to terminal T4. As will be explained below, the controllable gate utilizes nanotube components to create a non-volatile switching ability, meaning that the gate will retain its open or closed state even upon interruption of power to the circuit.

[0111] FIG. 2B illustrates a schematic for second field effect device (FED2) 40. The FED2 device 40 has a terminal T1 connected to gate 42, a terminal T2 connected to drain 44, and a controllable source 46. Like a typical field effect device (e.g., transistor 10 of FIG. 1) the gate node may be used to create a field to induce a conductive channel in channel region 47 between the drain 44 and a (controllable) source 46. In this case, the source 46 is controllable so that it may be in open or closed communication as illustrated with the depiction of switch 50. Switch 50 is fabricated using one or more carbon nanotubes (CNTs, or NTs). Switch 50 is preferably physi-

cally and electrically connected to contact 52, which is connected to a terminal T3. Switch 50 may be displaced to contact a switch-plate 48, which is connected to a controllable source 46. Switch 50 may be displaced to contact release-plate 54, which is connected to terminal T4. As will be explained below, the controllable gate utilizes nanotube components to create a non-volatile switching ability, meaning that the gate will retain its open or closed state even upon interruption of power to the circuit.

[0112] FIG. 2C illustrates a schematic of third field effect device (FED3) 60. The FED3 device 60 has a terminal T1 connected to gate 62, a terminal T2 connected to drain 64, and a controllable source 66. Like a typical field effect device (e.g., transistor 10 of FIG. 1) the gate node may be used to create a field to induce a conductive channel in channel region 67 between the drain 64 and a (controllable) source 66. In this case, the source 66 is controllable so that it may be in open or closed communication as illustrated with the depiction of switch 70. Switch 70 is fabricated using one or more carbon nanotubes (CNTs, or NTs). Switch 70 is preferably physically and electrically connected to controllable source 66 by contact 68. Switch 70 may be displaced to contact switchplate 72, which is connected to a terminal T3. Switch 70 may be displaced to contact dielectric surface of release-plate 76 on release-plate 74, which is connected to terminal T4. As will be explained below, the controllable gate utilizes nanotube components to create a non-volatile switching ability, meaning that the gate will retain its open or closed state even upon interruption of power to the circuit, such non-volatilely is more fully described in incorporated references and will not be repeated here for the sake of brevity.

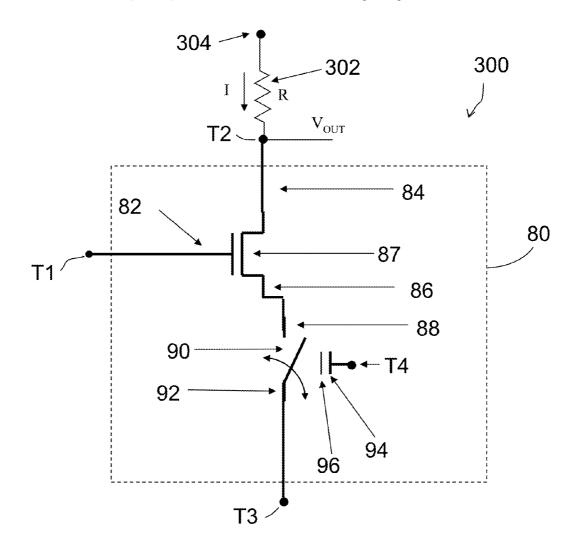

[0113] FIG. 2D illustrates a schematic of fourth field effect device (FED4) 80. The FED4 device 80 has a terminal T1 connected to gate 82, a terminal T2 connected to drain 84, and a controllable source 86. Like a typical field effect device (e.g., transistor 10 of FIG. 1) the gate node may be used to create a field to induce a conductive channel in channel region 87 between the drain 84 and a (controllable) source 86. In this case, the source 86 is controllable so that it may be in open or closed communication as illustrated with by the depiction of switch 90. Switch 90 is fabricated using one or more carbon nanotubes (CNTs, or NTs) as described in incorporated references. Switch 90 is preferably physically and electrically connected to contact 92, which is connected to a terminal T3. Switch 90 may be displaced to contact a switch-plate 88, which is connected to a controllable source 86. Switch 90 may be displaced to contact release-plate dielectric surface 96 on release-plate 94, which is connected to terminal T4. As will be explained below, the controllable gate utilizes nanotube components to create a non-volatile switching ability, meaning that the gate will retain its open or closed state even upon interruption of power to the circuit.

Field Effect Devices (FEDs) with Controllable Drains

[0114] Field effect devices (FEDs) with controllable drains may also be referred to as nanotube (NT)-on-Drain. FIG. 2E illustrates a schematic of fifth field effect device (FED5) 100. The FED5 device 100 has a terminal T1 connected to gate 102, a controllable drain 104, and a source 106 connected to a terminal T3. Like a typical field effect device (e.g., transistor 10 of FIG. 1) the gate node may be used to create a field to induce a conductive channel in channel region 107 between the (controllable) drain 104 and a source 106. In this case, the drain 104 is controllable so that it may be in open or closed communication as illustrated by the depiction of switch 110.

Switch 110 is fabricated using one or more carbon nanotubes (CNTs, or NTs). Switch 110 is preferably physically and electrically connected to controllable drain 104 by contact 108. Switch 110 may be displaced to contact switch-plate 112, which is connected to a terminal T2. Switch 110 may be displaced to contact release-plate 114, which is connected to terminal T4. As will be explained below, the controllable gate utilizes nanotube components to create a non-volatile switching ability, meaning that the gate will retain its open or closed state even upon interruption of power to the circuit.

[0115] FIG. 2F illustrates a schematic of sixth field effect device (FED6) 120. The FED6 device 120 has a terminal T1 connected to gate 122, a controllable drain 124, and a source 126 connected to a terminal T3. Like a typical field effect device (e.g., transistor 10 of FIG. 1) the gate node may be used to create a field to induce a conductive channel in channel region 127 between the drain 124 and a (controllable) source 126. In this case, the drain 124 is controllable so that it may be in open or closed communication as illustrated by the depiction of switch 130. Switch 130 is fabricated using one or more carbon nanotubes (CNTs, or NTs). Switch 130 is preferably physically and electrically connected to contact 132, which is connected to terminal T2. Switch 130 may be displaced to contact a switch-plate 128, which is connected to a controllable drain 124. Switch 130 may be displaced to contact release-plate 134, which is connected to terminal T4. As will be explained below, the controllable gate utilizes nanotube components to create a non-volatile switching ability, meaning that the gate will retain its open or closed state even upon interruption of power to the circuit.

[0116] FIG. 2G illustrates a schematic of seventh field effect device (FED7) 140. The FED7 device 140 has a terminal T1 connected to gate 142, a controllable drain 144, and a source 146 connected to a terminal T3. Like a typical field effect device (e.g., transistor 10 of FIG. 1) the gate node may be used to create a field to induce a conductive channel in channel region 147 between the (controllable) drain 144 and a source 146. In this case, the drain 144 is controllable so that it may be in open or closed communication as illustrated by the depiction of switch 150. Switch 150 is fabricated using one or more carbon nanotubes (CNTs, or NTs). Switch 150 is preferably physically and electrically connected to controllable drain 144 by contact 148. Switch 150 may be displaced to contact switch-plate 152, which is connected to a terminal T2. Switch 150 may be displaced to contact release-plate dielectric surface 156 on release-plate 154, which is connected to terminal T4. As will be explained below, the controllable gate utilizes nanotube components to create a nonvolatile switching ability, meaning that the gate will retain its open or closed state even upon interruption of power to the circuit.

[0117] FIG. 2H illustrates a schematic of eighth field effect device (FED8) 160. The FED8 device 160 has a terminal T1 connected to gate 162, a controllable drain 164, and a source 166 connected to a terminal T3. Like a typical field effect device (e.g., transistor 10 of FIG. 1) the gate node may be used to create a field to induce a conductive channel in channel region 167 between the (controllable) drain 164 and a source 166. In this case, the drain 164 is controllable so that it may be in open or closed communication as illustrated by the depiction of switch 170. Switch 170 is fabricated using one or more carbon nanotubes (CNTs, or NTs). Switch 170 is preferably physically and electrically connected to contact 172, which is connected to terminal T2. Switch 170 may be displaced to

contact a switch-plate 168, which is connected to a controllable drain 164. Switch 170 may be displaced to contact release-plate dielectric surface 176 on release-plate 174, which is connected to terminal T4. As will be explained below, the controllable gate utilizes nanotube components to create a non-volatile switching ability, meaning that the gate will retain its open or closed state even upon interruption of power to the circuit.

Field Effect Devices (FEDs) with Controllable Gates

[0118] Field effect devices (FEDs) with controllable gates may also be referred to as nanotube (NT)-on-Gate. FIG. 21 illustrates a schematic of ninth field effect device (FED9) 180. The device 180 has a controllable gate 182, a drain 184 connected to terminal T2, and a source 186 connected to a terminal T3. Like a typical field effect device (e.g., transistor 10 of FIG. 1) the gate node may be used to create a field to induce a conductive channel in channel region 187 between a drain 184 and a source 186. In this case, the gate 182 is controllable so that it may be in open or closed communication as illustrated by the depiction of switch 190. Switch 190 is fabricated using one or more carbon nanotubes (CNTs, or NTs). Switch 190 is preferably physically and electrically connected to controllable gate 182 by contact 188. Switch 190 may be displaced to contact switch-plate 192, which is connected to a terminal T1. Switch 190 may be displaced to contact release-plate 194, which is connected to terminal T4. As will be explained below, the controllable gate utilizes nanotube components to create a non-volatile switching ability, meaning that the gate will retain its open or closed state even upon interruption of power to the circuit.

[0119] FIG. 2J illustrates a schematic of tenth field effect device (FED10) 200. The FED10 device 200 has a terminal controllable gate 202, a drain 204 connected to a terminal T2, and a source 206 connected to a terminal T3. Like a typical field effect device (e.g., transistor 10 of FIG. 1) the gate node may be used to create a field to induce a conductive channel in channel region 207 between the drain 204 and source 206. In this case, the gate 202 is controllable so that it may be in open or closed communication as illustrated by the depiction of switch 210. Switch 210 is fabricated using one or more carbon nanotubes (CNTs, or NTs). Switch 210 is preferably physically and electrically connected to contact 212, which is connected to terminal T1. Switch 210 may be displaced to contact a switch-plate 208, which is connected to a controllable gate 202. Switch 210 may be displaced to contact release-plate 214, which is connected to terminal T4. As will be explained below, the controllable gate utilizes nanotube components to create a non-volatile switching ability, meaning that the gate will retain its open or closed state even upon interruption of power to the circuit.

[0120] FIG. 2K illustrates a schematic of eleventh field effect device (FED11) 220. The device 220 has a controllable gate 222, a drain 224 connected to a terminal T2, and a source 226 connected to a terminal T3. Like a typical field effect device (e.g., transistor 10 of FIG. 1) the gate node may be used to create a field to induce a conductive channel in channel region 227 between a drain 224 and a source 226. In this case, the gate 222 is controllable so that it may be in open or closed communication as illustrated by the depiction of switch 230. Switch 230 is fabricated using one or more carbon nanotubes (CNTs, or NTs). Switch 230 is preferably physically and electrically connected to controllable gate 222 by contact 228. Switch 230 may be displaced to contact switch-plate 232, which is connected to a terminal T1. Switch 230 may be

displaced to contact release-plate dielectric surface 236 on release-plate 234, which is connected to terminal T4. As will be explained below, the controllable gate utilizes nanotube components to create a non-volatile switching ability, meaning that the gate will retain its open or closed state even upon interruption of power to the circuit.

[0121] FIG. 2L illustrates a schematic of twelfth field effect device (FED12) 240. The FED12 device 240 has a controllable gate 242, a drain 244 connected to a terminal T2, and a source 246 connected to a terminal T3. Like a typical field effect device (e.g., transistor 10 of FIG. 1) the gate node may be used to create a field to induce a conductive channel in channel region 247 between the (controllable) drain 244 and a source 246. In this case, the gate 242 is controllable so that it may be in open or closed communication as illustrated by the depiction of switch 250. Switch 250 is fabricated using one or more carbon nanotubes (CNTs, or NTs). Switch 250 is preferably physically and electrically connected to contact 252, which is connected to terminal T1. Switch 250 may be displaced to contact a switch-plate 248, which is connected to a controllable gate 242. Switch 250 may be displaced to contact release-plate dielectric surface 256 on release-plate 254, which is connected to terminal T4. As will be explained below, the controllable gate utilizes nanotube components to create a non-volatile switching ability, meaning that the gate will retain its open or closed state even upon interruption of power to the circuit.

[0122] As will be explained below, the controllable structures are implemented using nanotube technology. More specifically, non-volatile switching elements are made of ribbons of matted fabric of carbon nanotubes. These elements may be electromechanically deflected into an open or closed state relative to a respective source, drain, or gate node using electrostatic forces. Under preferred embodiments, the construction of the control structures is such that once switched "ON" inherent van der Waals forces are sufficiently large (relative to a restoring force inherent in the device geometry) so that the switching element will retain its non-volatilized state; that is, the element will retain its state even in the event of power interruption.

Operation of Field Effect Devices with Controllable Sources

[0123] Four schematics of field effect devices (FEDs) with controllable sources have been described (FIGS. 2A-D). FIGS. 3A through FIG. 9 illustrate the operation of field effect devices with controllable sources for two of the FED configurations, device 80 (FIG. 2D) and device 20 (FIG. 2A). FED devices with controllable sources are also referred to as NT-on-Source devices. For each of these two FED configurations, at least one switch-mode setting operation is described, followed by an example of full voltage swing circuit operation (digital switching), and an example of small signal analog circuit operation.

[0124] FIG. 3A illustrates a first FED configuration; field effect device 80 is combined with resistor 302 of value R, such that one terminal of resistor 302 is attached to FED device 80 terminal T2, and the other side of resistor 302 is attached to power supply terminal 304 to form circuit schematic 300. FIG. 3B illustrates circuit schematic 310 in which switch 90 has been activated to position 90' to electrically connect switch-plate 88 with contact 92 as illustrated in FIG. 3B. Controllable source 86 is electrically connected to terminal T3 by means of the established continuous electrical path formed by source 86 connected to switch-plate 88, switch-

plate 88 connected to one side of switch 90', the opposite side of switch 90' connected to contact 92, and contact 92 connected to terminal T3.

[0125] FIG. 3C illustrates circuit schematic 310' in which switch 90 has been activated to position 90" to electrically release-plate dielectric surface 96. Controllable source 86 is an electrically open circuited, and has no continuous electrical path to any FED4 80 device terminals. The mode-setting electrical signals applied to the terminals T1, T2, T3, and T4 of schematics 300, 310, and 310' to cause switch 90 to switch to position 90' or position 90" are illustrated in FIG. 4.

[0126] FIG. 4 illustrates the operational mode-setting voltage waveforms 311 applied to terminals T1, T2, T3, and T4 to activate switch 90. Control signals are applied to terminals T1-T4 by a control circuit (not shown) using control lines (not shown). There is no electrical signal applied to electrical terminal 304 during mode-setting. Column 1 illustrates the electrical signals used to change switch 90 from position 90", (also referred to as the open (off) position), to position 90', (also referred to as the closed (on) position). Column 2 illustrates the electrical signals used to change switch 90 from position 90', (also referred to as the closed position), to position 90", (also referred to as the open position). The modesetting waveforms are valid within the mode-setting time interval illustrated under columns 1 and 2 in FIG. 4. Other time intervals contain cross-hatched lines between voltages 0 and  $V_{DD}$ , indicating that these waveforms can be anywhere within this voltage range, and represent the circuit operating range.  $V_{DD}$  is selected to be less than the voltage switching voltage  $V_{SW}$  to ensure that switch 90 is not activated (resulting in mode-change) during circuit operation.

[0127] Mode-setting is based on electromechanical switching of carbon nanotube (NT) switch using electrostatic forces. The behavior of a NT fabric is similar to that of a single NT, see U.S. Pat. No. 6,643,165, where the electrostatic attractive force is due to oppositely charged surfaces 1 and 2, and where the electrostatic  $F_E = K (V_1 - V_2)^2 / (R_{12})^2$ . For an applied voltage, an equilibrium position of the NT, or NT fabric, is defined by the balance of the elastic, electrostatic, and van der Waals forces. As the NT, or NT fabric deflects, the elastic forces change. When the applied potential (voltage) difference between the nanotube and a reference electrode exceeds a certain voltage, the NT or NT fabric becomes unstable and collapses onto the reference electrode. The voltage difference between a NT or NT fabric, and a reference electrode that causes the NT or NT fabric to collapse, may be referred to as the pull-in voltage, or the collapse voltage, or the nanotube threshold voltage  $\mathbf{V}_{\mathit{NT-TH}}$  . The reference electrode may be a switch-plate, or a release-plate, or a release-plate with a dielectric layer. Once the NT or NT fabric is in contact with, or in very close proximity to, the reference electrode (in a region of strong van der Waals force), the electrostatic force  $F_E$  may be reduced to zero by removing the voltage difference between NT or NT fabric and the reference electrode. Power may be removed, and the NT or NT fabric remains in contact, and thus stores information in a non-volatile mode.

[0128] Column 1 of FIG. 4 illustrates the voltage and timing waveforms applied to terminals T1-T4 of FED4 80 that force a transition of NT switch 90 from position 90", in contact with insulator surface 96 on release-plate 94 as illustrated in FIG. 3C, to position 90', in contact with switch-plate 88 as illustrated in FIG. 3B. Switch 90 transitions from open to closed. Voltage  $V_{T4}$ , applied to terminal T4, transitions to switching voltage  $V_{SW}$ . Voltage  $V_{T2}$  applied to terminal T2

transitions to zero (0) volts.  $V_{T3}$  applied to terminal T3 transitions to switching voltage  $\mathbf{V}_{\mathit{SW}}$  . Terminal T1 (connected to gate 82) transitions from zero to  $V_{DD}$  forming a channel in channel region 87, thereby driving controllable source 86 voltage  $V_{\ensuremath{\textit{SOURCE}}}$  to zero. The electrostatic force between switch 90 in position 90" and release-plate 94 is zero. The electrostatic force between switch 90 in position 90" and switch-plate 88 is  $F_E = K (V_{SW})^2 / (R_{12})^2$ , where  $R_{12}$  is the gap separating switch 90 from switch-plate 88. Typical  $V_{NT-TH}$ voltages may range from 2 to 3 volts, for example, any appropriate potential difference however, is within the scope of the invention.  $V_{NT-TH}$  is a function of the suspended length of NT switch 90 and the gap (separation) between NT switch 90 and the switch-plate and release-plate electrodes. Typical NT switch suspended length is 130 to 180 nm, with gaps of 10 to 20 nm, for example, but other geometries are possible so long as the switching properties work appropriately.

[0129] Column 2 of FIG. 4 illustrates the voltage and timing waveforms applied to terminals T1-T4 of FED4 80 that force a transition of NT switch 90 from position 90', in contact with switch-plate 88 as illustrated in FIG. 3B, to position 90", in contact with release-plate dielectric surface 96 on releaseplate 94 as illustrated in FIG. 3C. Switch 90 transitions from closed to open. Voltage  $V_{T4}$ , applied to terminal T4, transitions to switching voltage  $\mathbf{V}_{SW}$ . Voltage  $\mathbf{V}_{T2}$  applied to terminal T2 transitions to zero (0) volts.  $V_{T3}$  applied to terminal T3 transitions to zero volts. Terminal T1 (connected to gate 82) transitions from zero to  $V_{DD}$  forming a channel in channel region 87, thereby driving controllable source 86 voltage  $V_{SOURCE}$  to zero. The electrostatic force between switch 90 in position 90' and switch-plate 88 is zero. The electrostatic force between switch 90 in position 90' and release-plate 94 is  $F_E = K (V_{SW})^2 / (R_{12})^2$ , where  $R_{12}$  is the gap separating switch  ${\bf 90}$  from release-plate  ${\bf 94}$ . Typical  ${\bf V}_{NT\text{-}TH}$  voltages may range from 2 to 3 volts, for example. The threshold voltage for switch 90 transitions between open and closed, and closed and open positions may be different, without effecting the operation of the device. If  $V_{SW}$  exceeds  $V_{NT-TH}$ , then modesetting will take place. Circuit operating voltages range from 0 to  $V_{DD}$ . In order to avoid unwanted mode-setting during circuit operation,  $V_{DD}$  is less than  $V_{NT-TH}$ .

[0130] FIG. 5 illustrates the full signal (voltage) swing waveform 313 operation of circuit 300, with waveforms applied to terminals T1, T2, T3, and T4. Column 1 illustrates the electrical signals applied to terminal T1-T4 for circuit schematic 310 when switch 90 is in the closed position 90' as illustrated in FIG. 3B. Column 2 illustrates the electrical signals applied to terminals T1-T4 for circuit schematic 310' when switch 90 is in the open position 90" as illustrated in FIG. 3C. Circuit schematic 310 illustrates the FED used in a simple inverter configuration with load resistor 302 of value R connected to voltage terminal 304 at voltage  $V=V_{DD}$ . For  $V_{NT-TH}$  in the 2 to 3 volt range, for example,  $V_{DD}$  is selected as less than 2 volts, 1.0 to 1.8 volts, for example. The operation of circuit 310 is as illustrated in FIG. 5, column 1. With switch 90 in the 90' position, the voltage  $V_{T4}$  on terminal T4 can be any value. Voltage  $V_{T3}$  applied to terminal T3 is set to zero volts. A pulse  $V_{T1}$  of amplitude  $V_{DD}$  is applied to terminal T1. When  $V_{T1}=0$ , no FET conductive path is activated, the electrical path between terminals T2 and T3 of FED4 80 is open, current I=0, and  $V_{OUT}$ = $V_{DD}$ . When  $V_{T1}$ = $V_{DD}$ , FET 80 channel of resistance  $R_{FET}$  is formed, in series with  $R_{SWITCH}$ of switch 90', connecting terminals T2 and T3. The resistance of FED4 80 between terminals T2 and T3 is  $R_{FED}=R_{FET}+$

$R_{SWITCH}$ .  $R_{FET}$  is the FET channel resistance, and  $R_{SWITCH}$  is the resistance of NT switch 90'.  $R_{SWITCH}$  includes the resistance between switch-plate 88 and NT 90', the NT 90' resistance (typically much less than the contact resistances), and the contact resistance between contact 92 and NT 90'.  $R_{FET}$  is determined by the FET electrical parameters and the width to length ratio used in the FET design (Reference: Baker et al., "CMOS Circuit Design, Layout, and Simulation", IEEE Press, 1998, Chapter 5 "the MOSFET", pages 83-106). By selecting W/L ratio values,  $R_{\it FET}$  may range from less than 10 Ohms to more than 10,000 Ohms. The quantum contact resistance between metal electrodes and the NT fabric varies as a function of the fabric density (number of NTs per unit area) and the width of the contact. The contact resistance per fiber may vary from less than 100 Ohms to more than 100,000 Ohms. When  $V_{T1}=V_{DD}$ , current  $I=V_{DD}/(R+R_{FED})$ , and  $V_{T2}=V_{OUT}=V_{DD}\times(R_{FED})/(R+R_{FED})$ . If  $R_{FED}<< R$ , then  $V_{T2}=V_{OUT}\approx 0$  volts, illustrated in FIG. **5**, column 1.

[0131] Circuit schematic 310' illustrates FED4 80 used in a simple inverter configuration with load resistor 302 of value R connected to voltage terminal 304 at voltage  $V=V_{DD}$ . The full signal (voltage) swing operation of circuit 310' is as illustrated in FIG. 5, column 2. With switch 90 in position 90", the FED electrical path between terminals T2 and T3 is open, terminal T4 is insulated, therefore current I=0, and  $V_{T2}=V_{DU7}=V_{DD}$  for all applied voltages.

[0132] FIG. 6 illustrates the small signal (voltage) swing waveforms 315 operation of circuit 300, with waveforms applied to terminals T1, T2, T3, and T4. Column 1 illustrates the electrical signals applied to terminal T1-T4 for circuit schematic 310 when switch 90 is in the closed position 90' as illustrated in FIG. 3B. Circuit schematic 310 illustrates the FED used in a simple inverter configuration with load resistor 302 of value R connected to voltage terminal 304 at voltage  $V=V_{DD}$ . For  $V_{NT-TH}$  in the 2 to 3 volt range, for example,  $V_{DD}$ is selected as less than 2 volts, 1.0 to 1.8 volts, for example. The operation of circuit 310 for small signal (analog) amplification is as illustrated in FIG. 5, column 1. With switch 90 in position 90', the voltage  $V_{T4}$  on terminal T4 can be any value. Voltage  $V_{T3}$  applied to terminal T3 is set to zero volts. A signal  $V_{T1}$  of with amplitude exceeding FET threshold voltage  $V_{FET\text{-}TH}^{T}$  ( $V_{FET\text{-}TH}$ =0.3-0.7 volts, for example) is applied to terminal T1. Since  $V_{T1}$ > $V_{FET\text{-}TH}$ , a path between terminals T2 and T3 is maintained. If  $R_{SWTTCH}$  is less than  $R_{FET}$ , then the output  $V_{T2} = V_{OUT}$  of circuit 310 inverts the input signal and exhibits gain as illustrated in FIG. 6, column 1. Circuit gain can be calculated as described in Baker et al., "CMOS Circuit Design, Layout, and Simulation", IEEE Press, 1998, Chapter 9 "the MOSFET", pages 165-181.

[0133] Circuit schematic 310' illustrates FED4 80 used in a simple inverter configuration with load resistor 302 of value R connected to voltage terminal 304 at voltage  $V=V_{DD}$ . The small signal (voltage) swing operation of circuit 310' is as illustrated in FIG. 6, column 2. With switch 90 in position 90", the FED electrical path between terminals T2 and T3 is open, terminal T4 is insulated, therefore current I=0, and  $V_{T2}=V_{DUT}=V_{DD}$  for all applied voltages.

[0134] In the second FED configuration, field effect device 20 is combined with first resistor 324 of value R, such that one terminal of resistor 324 is attached to FED device 20 terminal T2, and the other side of resistor 324 is attached to power supply terminal 322 as illustrated in FIG. 7A. A second resistor 328 of value R' is attached to FED device 20 terminal T4, and the other side of resistor 328 is attached to power supply

**326** to form the circuit schematic illustrated in FIG. 7A. Such configurations are exemplary and other working configurations are within the scope of the invention.

[0135] FIG. 7B illustrates a schematic of circuit 330 in which switch 30 has been activated to first position 30' to electrically connect contact 28 to switch-plate 32. Controllable source 26 is electrically connected to terminal T3 by means of the established continuous electrical path formed by source 26 connected to contact 28; contact 28 connected to one side of switch 30'; the opposite side of switch 30' connected to switch-plate 32; switch-plate 32 connected to terminal T3. FIG. 7C illustrates a schematic of circuit 330' in which switch 30 has been activated to second position 30" and contacts release-plate 34. Controllable source 26 is electrically connected to FED1 20 device terminal T4. The modesetting electrical signals applied to the terminals T1, T2, T3, and T4 of schematics 320, 330, and 330' that cause switch 30 to switch to first position 30' or second position 30" are illustrated in FIG. 8.

[0136] FIG. 8 illustrates the operational mode-setting waveforms 335 applied to terminals T1, T2, T3, and T4 to activate switch 30. Control signals are applied to terminals T1-T4 by a control circuit (not shown) using control lines (not shown). There is no electrical signal applied to electrical terminals 322 and 326 during mode-setting. Column 1 illustrates the electrical signals used to change switch 30 from position 30", also referred to as the second position, to position 30', also referred to as the first position. Column 2 illustrates the electrical signals used to change switch 30 from position 30', also referred to as the first position, to position 30", also referred to as the second position. The mode-setting waveforms are valid within the mode-setting time interval illustrated under columns 1 and 2 in FIG. 8. Other time intervals contain cross-hatched lines between voltages 0 and  $V_{DD}$ , indicating that these waveforms can be anywhere within this voltage range, and represent the circuit operating range.  $V_{DD}$  is selected to be less than the voltage switching voltage  $V_{SW}$  to ensure that switch 30 is not activated (resulting in mode-resetting) during circuit operation.

[0137] Mode-setting is based on electromechanical switching of carbon nanotube (NT) switch using electrostatic forces. The behavior of a NT fabric is similar to that of a single NT, as stated above, where the electrostatic attractive force is due to oppositely charged surfaces. Column 1 of FIG. 8 illustrates the voltage and timing waveforms applied to terminals T1-T4 of FED1 20 that force a transition of NT switch 30 from second position 30", in contact with release-plate 94 as illustrated in FIG. 7C, to first position 30', in contact with switchplate 32 as illustrated in FIG. 7B. Voltage  $V_{T4}$ , applied to terminal T4, transitions to zero volts. Voltage  $\mathbf{V}_{T2}$  applied to terminal T2 transitions to zero (0) volts.  $\mathbf{V}_{T3}$  applied to terminal T3 transitions to switching voltage  $V_{\mathit{SW}}$ . Terminal T1 (connected to gate 22) transitions from zero to  $V_{DD}$  forming a channel in channel region 27, thereby driving controllable source 26 voltage  $V_{\it SOURCE}$  to zero. The electrostatic force between switch 30 in position 30" and release-plate 34 is zero. The electrostatic force between switch 30 in position 30" and switch-plate 32 is  $F_E = K (V_{SW})^2 / (R_{12})^2$ , where  $R_{12}$  is the gap separating switch 30 from switch-plate 32. Typical  $V_{NT-TH}$ voltages may range from 2 to 3 volts, for example. Typical NT switch suspended length is 130 to 180 nm, with gaps of 10 to 20 nm, for example.

[0138] Column 2 of FIG. 8 illustrates the voltage and timing waveforms applied to terminals T1-T4 of FED20 that

force a transition of NT switch 30 from first position 30', in contact with switch-plate 32 as illustrated in FIG. 7B, to second position 30", in contact with release-plate 34 as illustrated in FIG. 7C. Voltage  $V_{74}$ , applied to terminal T4, transitions to switching voltage  $V_{SW}$ . Voltage  $V_{T2}$  applied to terminal T2 transitions to zero (0) volts.  $V_{T3}$  applied to terminal T3 transitions to zero volts, terminal T1 (connected to gate 22) transitions from zero to  $V_{DD}$  forming a channel in channel region 27, thereby driving controllable source 26 voltage  ${

m V}_{\it SOURCE}$  to zero. The electrostatic force between switch 30 in position 30' and switch-plate 28 is zero. The electrostatic force between switch 30 in position 30' and release-plate 34 is  $F_E = K (V_{SW})^2 / (R_{12})^2$ , where  $R_{12}$  is the gap separating switch 30 from release-plate 34. Typical  $V_{NT-TH}$  voltages may range from 2 to 3 volts, for example. The threshold voltage for switch 30 transitions between second and first, and first and second positions may be different, without effecting the operation of the device. If  $\mathbf{V}_{\mathit{SW}}$  exceeds  $\mathbf{V}_{\mathit{NT-TH}}$  , then modesetting will take place. Circuit operating voltages range from  $0 \ \mathrm{to} \ \mathrm{V}_{D\!D}\!.$  In order to avoid unwanted mode-setting during circuit operation,  $V_{DD}$  is less than  $V_{NT\text{-}TH}$ .

[0139] FIG. 9 illustrates the full signal (voltage) swing waveforms 345 operation of circuit 320, with waveforms applied to terminals T1, T2, T3, and T4. Column 1 illustrates the electrical signals applied to terminal T1-T4 for circuit 330 when switch 30 is in the first position 30' as illustrated in FIG. 7B. Column 2 illustrates the electrical signals applied to terminals T1-T4 for circuit 330' when switch 30 is in the second position 30" as illustrated in FIG. 7C. Circuit 330 illustrates a FED used in a simple inverter configuration with load resistor 324 of value R connected to voltage terminal 322 at voltage  $V=V_{DD}$ . For  $V_{NT-TH}$  in the 2 to 3 volt range, for example,  $V_{DD}$  is selected as less than 2 volts, 1.0 to 1.8 volts, for example. The operation of circuit 330 is as illustrated in FIG. 9, column 1. With switch 30 in the 30' position, the voltage  $V_{T4}$  on terminal T4 can be any value. Voltage  $V_{T3}$ applied to terminal T3 is set to zero volts. A pulse  $V_{T1}$  of amplitude  $V_{DD}$  is applied to terminal T1. When  $V_{T1} = 0$ , no FET conductive path is activated, the electrical path between terminals T2 and T3 of FED20 is open, current I=0, and  $V_{T2}=V_{OUT}=V_{DD}$ . When  $V_{T1}=V_{DD}$ , FET channel 27 of resistance  $R_{FET}$  is formed, in series with  $R_{SWITCH}$  of switch 30', connecting terminals T2 and T3. The resistance of FED20 between terminals T2 and T3 is  $R_{FED} = R_{FET} + \frac{RSW}{ITCH} \cdot R_{FET}$ is the FET channel resistance, and  $\mathbf{R}_{\mathit{SWITCH}}$  is the resistance of NT switch 30'. R<sub>SWITCH</sub> includes the resistance between contact 28 and NT 30', the NT 30' resistance (typically much less than the contact resistances), and the resistance between switch-plate 32 and NT 30'.  $R_{FET}$  is determined by the FET electrical parameters and the width to length ratio used in the FET design (Reference: Baker et al., "CMOS Circuit Design, Layout, and Simulation", IEEE Press, 1998, Chapter 5 "the MOSFET", pages 83-106). By selecting W/L ratio values,  $R_{FET}$  may range from less than 10 Ohms to more than 10,000 Ohms. The quantum contact resistance between metal electrodes and the NT fabric varies as a function of the fabric density (number of NTs per unit area) and the width of the contact. The contact resistance may vary from less than 100 Ohms to more than 100,000 Ohms. When  $V_{T1} = V_{DD}$ , current

$$\begin{split} & \text{I=V}_{DD}/(\text{R+R}_{FED}), \text{ and V}_{T2} = & \text{V}_{OUT} = \text{V}_{DD} \times (\text{R}_{FED})/(\text{R+R}_{FED}). \\ & \text{If R}_{FED} < < \text{R, then V}_{T2} = & \text{V}_{OUT} \approx 0 \text{ volts, illustrated in FIG. 9,} \end{split}$$

[0140] The schematic of circuit 330' illustrates a FED used in a more complex circuit configuration with load resistor 324

of value R connected to voltage terminal 322 at voltage  $V=V_{DD}$ , and resistor 328 of value R' connected to voltage terminal 326 at voltage zero. For  $V_{\mathit{NT-TH}}$  in the 2 to 3 volt range, for example,  $V_{DD}$  is selected as less than 2 volts, 1.0 to 1.8 volts, for example. The operation of circuit 330' is as illustrated in FIG. 9, column 2. With switch 30 in the 30' position, the voltage  $V_{T3}$  on terminal T3 can be any value. A pulse  $V_{T}$  of amplitude  $V_{DD}$  is applied to terminal T1. When  $V_{T_1}$ =0, no FET conductive path is activated, the electrical path between terminals T2 and T4 of FED1 20 is open, current I=0, and  $V_{T2}=V_{OUT}=V_{DD}$ , and  $V_{T4}=0$ . When  $V_{T1}=V_{DD}$ , FET channel 27 of resistance  $R_{FET}$  is formed, in series with R<sub>SWITCH</sub> of switch 30", connecting terminals T2 and T4. The resistance of FED20 between terminals T2 and T4 is  $R_{FED} = R_{FET} + R_{SWITCH}$ .  $R_{FET}$  is the FET channel resistance, and  $R_{SWITCH}$  is the resistance of NT switch 30".  $R_{SWITCH}$ includes the resistance between contact 28 and NT 30", the NT 30" resistance (usually much less than the contact resistances), and the resistance between release-plate 34 and NT 30".  $R_{\it FET}$  is determined by the FET electrical parameters and the width to length ratio used in the FET design. By selecting W/L ratio values,  $R_{\it FET}$  may range from less than 10 Ohms to more than 10,000 Ohms. The quantum contact resistance between metal electrodes and the NT fabric varies as a function of the fabric density (number of NTs per unit area) and the width of the contact. The contact resistance may vary from less than 100 Ohms to more than 100,000 Ohms When  $V_{T1} = V_{DD}$ , current  $I = V_{DD} / (R + R' + R_{FED})$ ,  $V_{T2} = V_{OUT} = V_{DD} \times R' + R' + R_{FED}$  $\begin{array}{l} ({\rm R'+R_{\it FED}})/({\rm R+R'+R_{\it FED}}), \text{ and } {\rm V_{\it T4}} = {\rm V_{\it DD}} \times ({\rm R'})/({\rm R+R'+R_{\it FED}}). \\ {\rm If } \ \ {\rm R_{\it FED}} <<<{\rm R, } \ \ {\rm and } \ \ {\rm R'=R, } \ \ {\rm then} \ \ \ {\rm V_{\it T2}} = {\rm V_{\it DUT}} = {\rm V_{\it DD}}/2, \ \ {\rm and} \\ \end{array}$  $V_{T4}=V_{DD}/2$ , as illustrated in FIG. 9, column 2.

[0141] In the example of the operation of circuit 320 (FIG. 7A), circuit operation for two switch-mode settings were described, one for switch 30 in first position 30' as illustrated in FIG. 7B, and the other for switch 30 in the second position 30" as illustrated in FIG. 7C. The voltages on FED terminals T2 and T4 varied as a function of the switch-mode settings. FED1 20 may also be used in other applications. For example, a first network may be connected to terminal T2, a second network may be connected to terminal T3, and a third network may be connected to terminal T4. When FED1 20 switch 30 is in the first position 30' (FIG. 7B), a first network connected to terminal T2 is connected to a second network connected to terminal T3. When FED1 20 switch 30 is in the second position 30", a first network connected to terminal T2 is connected to a third network connected to terminal T4. Thus, in this application, FED1 20 is used to route signals from a first network to a second network, or instead, to a third network. The network configuration remains in place even if power is turned off because FED1 20 is a non-volatile device.

Operation of Field Effect Devices with Controllable Drains

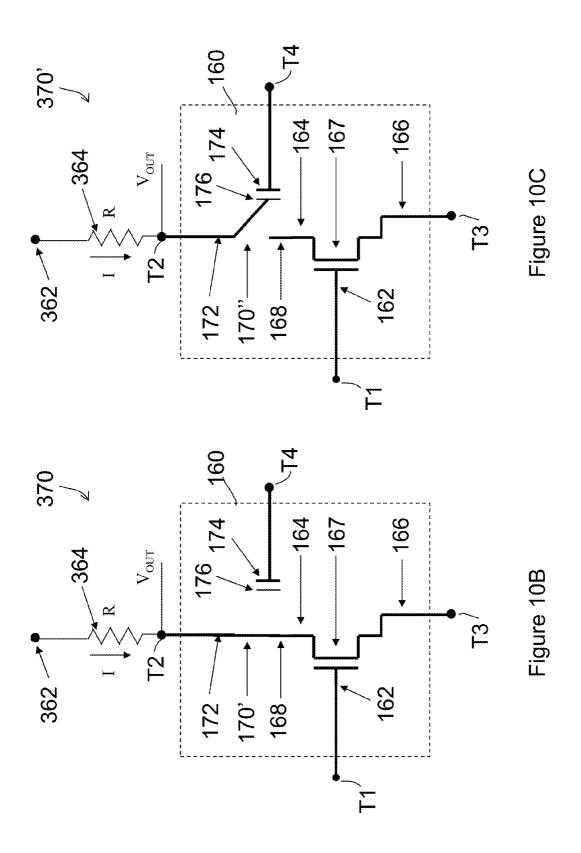

[0142] Four schematics of field effect devices (FEDs) with controllable drains have been described (FIGS. 2E-H). FIGS. 10A-12 illustrates the operation of field effect devices with controllable drains for one of the FED configurations, FED8 device 160 (FIG. 2H). As stated above, FED devices with controllable drains are also referred to as NT-on-Drain devices. A switch-mode setting operation is described, followed by an example of full voltage swing circuit operation (digital switching).

[0143] Field effect device FED8 160 is combined with resistor 364 of value R, such that one terminal of resistor 364 is attached to FED8 device 160 terminal T2, and the other side

of resistor 364 is attached to power supply terminal 362 to form circuit schematic 360 as illustrated in FIG. 10A.

[0144] FIG. 10B illustrates circuit schematic 370 in which switch 170 has been activated to position 170' to electrically connect switch-plate 168 to contact 172. Controllable drain 164 is electrically connected to terminal T2 by means of the established continuous electrical path formed by drain 164 connected to switch-plate 168; switch-plate 168 connected to one side of switch 170'; the opposite side of switch 170' connected to contact 172; contact 172 connected to terminal T2.

[0145] FIG. 10C illustrates circuit schematic 370' in which switch 170 has been activated to position 170" to contact release-plate dielectric surface 176. Controllable drain 164 is electrically open circuited, and has no continuous electrical path to any terminals of FED8 160 device. The mode-setting electrical signals applied to the terminals T1, T2, T3, and T4 of schematics 360, 370, and 370' to cause switch 170 to switch to position 170' or position 170" are illustrated in FIG. 11.

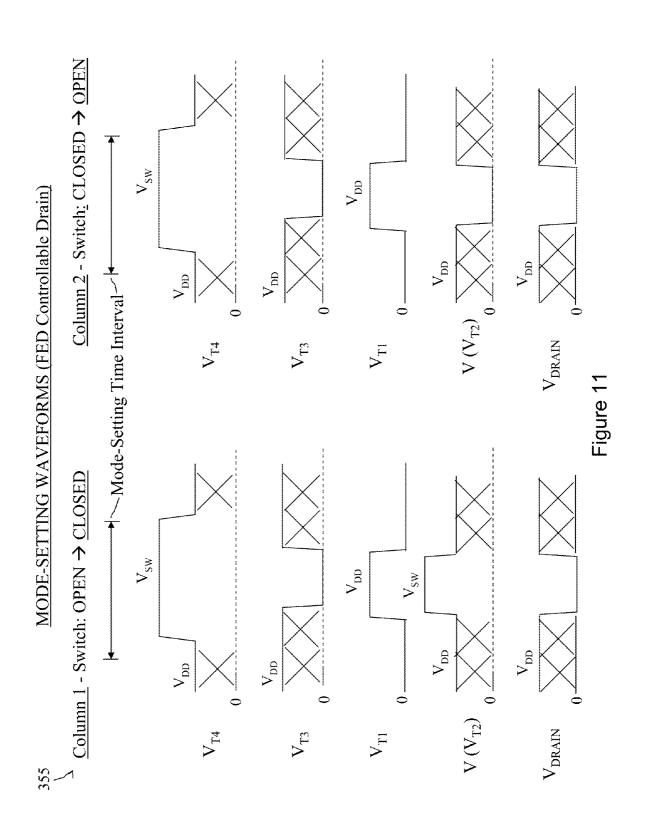

[0146] FIG. 11 illustrates the operational mode-setting waveforms 355 applied to terminals T1, T2, T3, and T4 to activate switch 170. Control signals are applied to terminals T1-T4 by a control circuit (not shown) using control lines (not shown). There is no electrical signal applied to electrical terminal 362. Column 1 illustrates the electrical signals used to change switch 170 from position 170", also referred to as the open position, to position 170', also referred to as the closed position. Column 2 illustrates the electrical signals used to change switch 170 from position 170', also referred to as the closed position, to position 170", also referred to as the open position. The mode-setting waveforms are valid within the mode-setting time interval illustrated under columns 1 and 2 in FIG. 11. Other time intervals contain cross-hatched lines between voltages 0 and  $V_{DD}$ , indicating that these waveforms can be anywhere within this voltage range, and represent the circuit operating range.  $\mathbf{V}_{DD}$  is selected to be less than the voltage switching voltage  $V_{SW}$  to ensure that switch 170 is not activated (resulting in mode-resetting) during circuit

Mode-setting is based on electromechanical switching of carbon nanotube (NT) switch using electrostatic forces. As stated above, the behavior of a NT fabric is similar to that of a single NT, where the electrostatic attractive force is due to oppositely charged surfaces. Column 1 of FIG. 11 illustrates the voltage and timing waveforms applied to terminals T1-T4 of FED8 160 that force a transition of NT switch 170 from position 170", in contact with insulator surface 176 on release-plate 174 as illustrated in FIG. 10C, to position 170', in contact with switch-plate 168 as illustrated in FIG. 10B. Switch 170 transitions from open to closed. Voltage  $V_{T4}$ , applied to terminal T4, transitions to switching voltage  $V_{SW}$ . Voltage  $V_{T2}$  applied to terminal T2 transitions switching voltage  $V_{W}$ .  $V_{T3}$  applied to terminal T3 transitions to zero volts. Terminal T1 (connected to gate 162) transitions from zero to  $V_{DD}$  forming a channel in channel region 167, thereby driving controllable drain 164 voltage  $V_{DRAIN}$  to zero. The electrostatic force between switch 170 in position 170" and releaseplate 174 is zero. The electrostatic force between switch 170 in position 170" and switch-plate 168 is  $F_E = K (V_{SW})^2 / (R_{12})^2$ , where  $R_{12}$  is the gap separating switch 170 from switch-plate 168. Typical  $V_{NT-TH}$  voltages may range from 2 to 3 volts, for example.  $V_{NT-TH}$  is a function of the suspended length of NT switch 170 and the gap (separation) between NT switch 170 and the switch-plate and release-plate electrodes. Typical, but non-exclusive exemplary ranges for NT switch suspended length is 130 to 180 nm, with gaps of 10 to 20 nm.

[0148] Column 2 of FIG. 11 illustrates the voltage and timing waveforms applied to terminals T1-T4 of FED8 160 that force a transition of NT switch 170 from position 170', in contact with switch-plate 168 as illustrated in FIG. 10B, to position 170", in contact with release-plate dielectric surface 176 on release-plate 174 as illustrated in FIG. 10C. Switch 170 transitions from closed to open. Voltage  $V_{T4}$ , applied to terminal T4, transitions to switching voltage  $V_{SW}$ . Voltage  $V_{T2}$  applied to terminal T2 transitions to zero (0) volts.  $V_{T3}$ applied to terminal T3 transitions to zero volts. Terminal T1 (connected to gate 162) transitions from zero to  $V_{DD}$  forming a channel in channel region 167, thereby driving controllable drain 164 voltage  $V_{DRAIN}$  to zero. The electrostatic force between switch 170 in position 170' and switch-plate 168 is zero. The electrostatic force between switch 170 in position 170' and release-plate 174 is  $F_E = K (V_{SW})^2 / (R_{12})^2$ , where  $R_{12}$ is the gap separating switch 170 from release-plate 174. Typical  $V_{NT-TH}$  voltages may range from 2 to 3 volts, for example. The threshold voltage for switch 170 transitions between open and closed, and closed and open positions may be different, without effecting the operation of the device. If  $V_{SW}$ exceeds  $V_{\mathit{NT-TH}}$ , then mode-setting will take place. Circuit operating voltages range from 0 to  $V_{DD}$ . In order to avoid unwanted mode-setting during circuit operation,  $V_{DD}$  is less than  $V_{NT-TH}$ .

[0149] FIG. 12 illustrates the full signal (voltage) swing waveforms 365 operation of circuit 360, with waveforms applied to terminals T1, T2, T3, and T4. Column 1 illustrates the electrical signals applied to terminal T1-T4 for circuit schematic 370 when switch 170 is in the closed position 170' as illustrated in FIG. 10B. Column 2 illustrates the electrical signals applied to terminals T1-T4 for circuit schematic 370' when switch 170 is in the open position 170" as illustrated in FIG. 10C. Circuit schematic 370 illustrates the FED used in a simple inverter configuration with load resistor 364 of value R connected to voltage terminal 362 at voltage  $V=V_{DD}$ . For  $V_{NT-TH}$  in the 2 to 3 volt range, for example,  $V_{DD}$  is selected as less than 2 volts, 1.0 to 1.8 volts, for example. The operation of circuit 370 is as illustrated in FIG. 12, column 1. With switch 170 in the 170' position, the voltage  $V_{T4}$  on terminal T4 can be any value. Voltage  $V_{T3}$  applied to terminal T3 is set to zero volts. A pulse  $\mathbf{V}_{T1}$  of amplitude  $\mathbf{V}_{DD}$  is applied to terminal T1. When  $V_{T1}$ =0, no FET conductive path is activated, the electrical path between terminals T2 and T3 of FED8 160 is open, current I=0, and  $V_{OUT}$ = $V_{DD}$ . When  $V_{T1}$ = $V_{DD}$ , FET 167 channel of resistance  $R_{FET}$  is formed, in series with  $R_{SWITCH}$ of switch 170', connecting terminals T2 and T3. The resistance of FED8 160 between terminals T2 and T3 is  $\mathbf{R}_{FET}\!\!=\!\!\mathbf{R}_{FET}\!\!+\!\!\mathbf{R}_{SWITCH}\!.$   $\mathbf{R}_{FET}$  is the FET channel resistance, and  $R_{SWITCH}$  is the resistance of NT switch 170'.  $R_{SWITCH}$ includes the resistance between switch-plate 168 and NT 170', the NT 170' resistance (typically much less than the contact resistances), and the contact resistance between contact 172 and NT 170'.  $R_{FET}$  is determined by the FET electrical parameters and the width to length ratio used in the FET design. By selecting W/L ratio values,  $\mathbf{R}_{FET}$  may range from less than 10 Ohms to more than 10,000 Ohms. The quantum contact resistance between metal electrodes and the NT fabric varies as a function of the fabric density (number of NTs per unit area) and the width of the contact. The contact resistance may vary from less than 100 Ohms to more than 100,000 Ohms. When  $V_{T1}=V_{DD}$ , current  $I=V_{DD}/(R+R_{FED})$ , and  $V_{T2}=V_{OUT}=V_{DD}\times(R_{FED})/(R+R_{FED})$ . If  $R_{FED}<< R$ , then  $V_{T2}=V_{OUT}=0$  volts, illustrated in FIG. **12**, column 1.

[0150] Circuit schematic 370' illustrates FED8 160 used in a simple inverter configuration with load resistor 364 of value R connected to voltage terminal 362 at voltage  $V=V_{DD}$ . The full signal (voltage) swing operation of circuit 370' is as illustrated in FIG. 12, column 2. With switch 90 in position 90", the FED electrical path between terminals T2 and T3 is open, terminal T4 is insulated, therefore current I=0, and  $V_{T2}=V_{OUT}=V_{DD}$  for all applied voltages.

Operation of Field Effect Devices with Controllable Gates [0151] Four schematics of field effect devices (FEDs) with controllable gates have been described (FIGS. 2I-L). FIGS. 13A-16 illustrates the operation of field effect devices with controllable gates for one of the FED configurations, FED11 device 240 (FIG. 2L). FED devices with controllable gates are also referred to as NT-on-Gate devices. A switch-mode setting operation is described, followed by an example of full voltage swing circuit operation (digital switching).

[0152] FIG. 13A illustrates FED11 240. FED11 240 is combined with resistor 886 of value R, such that one terminal of resistor 886 is attached to FED11 device 240 terminal T2, and the other side of resistor 886 is attached to power supply terminal 884 to form circuit schematic. FED11 240 terminal T2 is connected to FET drain 244; terminal T3 is connected to FET source 246; terminal T4 is connected to release plate 254. FIG. 13B illustrates circuit schematic 390 in which switch 250 has been activated to position 250' to electrically connect switch-plate 248 to contact 252. Controllable gate 242 is electrically connected to terminal T1 by means of the established continuous electrical path formed by gate 242 connected to switch-plate 248; switch-plate 248 connected to one side of switch 250; the opposite side of switch 250' connected to contact 252; contact 252 connected to terminal T1. The combination of contact 252 area and NT fabric layer switch 250 area may be referred to as the NT control gate, because the voltage applied to this control gate controls the FET channel region 247 electrical characteristics.

[0153] FIG. 13C illustrates circuit schematic 390' in which switch 250 has been activated to position 250" to contact release-plate dielectric surface 256. Controllable gate 242 is electrically open circuited, and has no continuous electrical path to any FED 249 device terminals.