(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6337026号

(P6337026)

(45) 発行日 平成30年6月6日(2018.6.6)

(24) 登録日 平成30年5月11日(2018.5.11)

|                   |                  |      |       |      |

|-------------------|------------------|------|-------|------|

| (51) Int.Cl.      | F 1              |      |       |      |

| <b>H04R 19/00</b> | <b>(2006.01)</b> | H04R | 19/00 | 330  |

| <b>B81B 3/00</b>  | <b>(2006.01)</b> | B81B | 3/00  |      |

| <b>B81C 3/00</b>  | <b>(2006.01)</b> | B81C | 3/00  |      |

| <b>H04R 31/00</b> | <b>(2006.01)</b> | H04R | 31/00 | 330  |

| <b>H01L 23/12</b> | <b>(2006.01)</b> | H01L | 23/12 | 501P |

請求項の数 20 (全 15 頁)

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2015-560307 (P2015-560307)  |

| (86) (22) 出願日 | 平成26年2月27日 (2014.2.27)        |

| (65) 公表番号     | 特表2016-511607 (P2016-511607A) |

| (43) 公表日      | 平成28年4月14日 (2016.4.14)        |

| (86) 国際出願番号   | PCT/US2014/019011             |

| (87) 国際公開番号   | W02014/134301                 |

| (87) 国際公開日    | 平成26年9月4日 (2014.9.4)          |

| 審査請求日         | 平成29年2月27日 (2017.2.27)        |

| (31) 優先権主張番号  | 13/779,376                    |

| (32) 優先日      | 平成25年2月27日 (2013.2.27)        |

| (33) 優先権主張国   | 米国(US)                        |

|               |                                                                                                                       |

|---------------|-----------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者     | 390020248<br>日本テキサス・インスツルメンツ株式会社<br>東京都新宿区西新宿六丁目24番1号                                                                 |

| (73) 特許権者     | 507107291<br>テキサス インスツルメンツ インコーポ<br>レイテッド<br>アメリカ合衆国 テキサス州 75265<br>-5474 ダラス メイル ステイショ<br>ン 3999 ピーオーボックス 655<br>474 |

| (74) 上記1名の代理人 | 100098497<br>弁理士 片寄 恒三                                                                                                |

最終頁に続く

(54) 【発明の名称】基板貫通ビア (T S V) を備えた容量性微細加工超音波トランステューサ (C M U T) デバイス

## (57) 【特許請求の範囲】

## 【請求項 1】

容量性微細加工超音波トランステューサ (C M U T) セルを含む C M U T デバイスであつて、

前記 C M U T セルが、

頂部側と底部側とを含む基板と、

前記基板の頂部側の上の誘電体層であつて、第1の領域と、前記第1の領域により横方向に囲まれて前記第1の領域よりも薄い第2の領域とを含み、前記第1及び第2の領域がキャビティを定める、前記誘電体層と、

前記誘電体層の第1の領域上に直接に接合され、前記誘電体層の第2の領域の上で前記キャビティを取り囲む薄膜層であつて、前記キャビティ内に可動薄膜を含む、前記薄膜層と、

前記基板と前記誘電体層と前記薄膜層とに入り込み、前記可動薄膜から横方向に離れて位置する基板貫通ビア (T S V) であつて、前記薄膜層と共に面になるように、前記基板の底部側から延在する導電性充填材を含む、前記基板貫通ビア (T S V) と、

前記基板の頂部側の上で前記導電性充填材に接する金属層であつて、前記薄膜層に沿つて横方向に延び、前記可動薄膜に接する、前記金属層と、

を含む、デバイス。

## 【請求項 2】

請求項 1 に記載の C M U T デバイスであつて、

10

前記金属層の上の誘電性パッセーション層を更に含む、デバイス。

【請求項 3】

請求項 1 に記載の C M U T デバイスであって、

第 2 の C M U T セルと、

前記基板の底部側の下の前記第 1 の C M U T セルの前記導電性充填材に接して前記第 1 の C M U T セルを前記第 2 の C M U T セルに接続する第 2 の金属層と、

を更に含む、デバイス。

【請求項 4】

請求項 1 に記載の C M U T デバイスであって、

前記薄膜層が単結晶シリコン材料を含む、デバイス。

10

【請求項 5】

請求項 1 に記載の C M U T デバイスであって、

前記導電性充填材が、銅を含み、前記基板の前記底部側から突出する、デバイス。

【請求項 6】

請求項 1 に記載の C M U T デバイスであって、

前記基板が、0.1 - cm より小さいか又はそれに等しい抵抗を有する、デバイス。

【請求項 7】

請求項 1 に記載の C M U T デバイスであって、

前記薄膜層が前記誘電体層に真空融解ボンディングされる、デバイス。

20

【請求項 8】

トランスデューサデバイスであって、

第 1 の側と第 1 の側の反対の第 2 の側とを有する基板と、

トランスデューサセルと、

を含み、

前記トランスデューサセルが、

前記基板の第 1 の側の上の誘電体層であって、第 1 の領域と、第 1 の領域よりも薄く、キャビティを定めるために前記第 1 の領域により横方向に囲まれる第 2 の領域とを有する、前記誘電体層と、

前記キャビティを取り囲み、前記誘電体層の第 2 の領域の上に可動薄膜を含む薄膜層と

、

前記基板と前記誘電体層と前記薄膜層とに入り込む貫通基板ビア (T S V) と、

を含む、デバイス。

30

【請求項 9】

請求項 8 に記載のトランスデューサデバイスであって、

前記薄膜層が前記誘電体層の第 1 の領域上に直接に接合される、デバイス。

【請求項 10】

請求項 8 に記載のトランスデューサデバイスであって、

前記 T S V が、前記可動薄膜に垂直に重なっていない、デバイス。

【請求項 11】

請求項 8 に記載のトランスデューサデバイスであって、

前記 T S V が、前記薄膜層と共に面になるように前記基板の第 2 の側から延びる導電性充填材を含む、デバイス。

40

【請求項 12】

請求項 8 に記載のトランスデューサデバイスであって、

前記基板の第 1 の側に隣接する前記 T S V に接する金属層であって、前記薄膜層に沿って横方向に延び、前記可動薄膜に接する、前記金属層を更に含む、デバイス。

【請求項 13】

請求項 8 に記載のトランスデューサデバイスであって、

前記薄膜層が単結晶シリコン材料を含む、デバイス。

【請求項 14】

50

請求項 8 に記載のトランスデューサデバイスであって、

第 2 のトランスデューサセルと、

前記第 2 のトランスデューサセルを前記基板の第 2 の側に隣接する前記トランスデューサセルの前記 TSV に接続する金属層と、

を更に含む、デバイス。

## 【請求項 15】

トランスデューサデバイスであって、

第 1 の側と前記第 1 の側の反対の第 2 の側とを有する基板と、

複数のトランスデューサセルであって、各トランスデューサセルが、

前記基板の第 1 の側の上の誘電体層であって、第 1 の領域と、前記第 1 の領域よりも薄く、キャビティを定めるように前記第 1 の領域により横方向に囲まれる第 2 の領域とを有する、前記誘電体層と、 10

前記キャビティを取り囲む薄膜層であって、前記誘電体層の第 2 の領域の上に可動薄膜を含む、前記薄膜層と、

前記基板と前記誘電体層と前記薄膜層とに入り込む貫通基板ビア (TSV) であって、

誘電体充填材を含む、前記 TSV と、

を含む、前記複数のトランスデューサセルと、

前記基板の第 2 の側に隣接する少なくとも 2 つの前記トランスデューサセルの導電性充填材に接続する相互接続金属層と、

を含む、デバイス。

20

## 【請求項 16】

請求項 15 に記載のトランスデューサデバイスであって、

前記薄膜層が前記誘電体層の第 1 の領域に直接に接合される、デバイス。

## 【請求項 17】

請求項 15 に記載のトランスデューサデバイスであって、

前記 TSV が、前記可動薄膜に垂直に重ならない、デバイス。

## 【請求項 18】

請求項 15 に記載のトランスデューサデバイスであって、

前記導電性充填材が、前記薄膜層と共に前記基板の第 2 の側から延びる、

デバイス。

30

## 【請求項 19】

請求項 15 に記載のトランスデューサデバイスであって、

前記基板の第 1 の側に隣接する前記 TSV に接する相互セル金属層であって、前記薄膜層に沿って横方向に延び、前記可動薄膜に接する、前記相互セル金属層を更に含む、デバイス。

## 【請求項 20】

請求項 15 に記載のトランスデューサデバイスであって、

前記薄膜層が単結晶シリコン材料を含む、デバイス。

## 【発明の詳細な説明】

## 【技術分野】

40

## 【0001】

開示される実施例は、容量性微細加工 (micromachined) 超音波トランスデューサ (CUMT) デバイス及びその製造のための方法に関する。

## 【背景技術】

## 【0002】

CUMT デバイスは、医療用途においてますます一般的になってきており、例えば、CUMT デバイスは、医療用超音波イメージングプローブを改善するために用いられており、CUMT デバイスはまた、医療において用いられる高密度焦点式超音波を提供するためにも用いられており、従来の CUMT デバイスは典型的にシリコン基板上 (即ち、シリコンウェハ上) に直接製造される。例えば、従来の CUMT デバイスは大抵、マイ

50

クロエレクトロメカニカルシステム（MEMS）製造手法を用いて製造され、この手法では、リリース層がエッティングで取り除かれて、独立した（フレキシブル）薄膜が残る。この薄膜の頂部が頂部（電極）プレートを提供するためにメタライズされ、その後、薄膜は超音波信号を送信及び受信するためトランステューサとして用いられる。

【0003】

従来のCUMTデバイスは、CUMTアレイに配される複数のCUMT要素を含むCUMTデバイスのための複数のボンドパッドなど、そのCUMTデバイスにおけるCUMT要素の各々に対する頂部プレートへの電気的コンタクトを提供するためにボンドパッドを用いる。ボンドワイヤはボンドパッドより上に高くされるため、ボンドパッドは、パッケージングを助けるためにCUMTアレイにおけるCUMT要素から離れて配置される。この制約は、相互接続配路ラインの必要性に起因してCUMTデバイスダイサイズを増大させるだけでなく、パッケージングプロセスを複雑にする。増大されたダイサイズ及び複雑化されたパッケージングプロセスは、いずれも、パッケージングされたCUMTダイのコストを増大させる。

10

【発明の概要】

【0004】

開示される実施例は、各CUMTセルの頂部プレートへの接続のためのボンドパッドの従来の利用に伴うCUMTデバイス問題に対する解決策を記載する。これらの問題は、実質的に設計を制約し、CUMT要素の2次元（2D）CUMTアレイを含むCUMTデバイスのサイズを増大させ、それらの性能も損ねると認識されている。ボンドパッドを従来の大きな2D CUMTアレイの各CUMT要素に接続することは、CUMTダイの頂部側の金属相互接続トレースを広範囲に利用することに關与し、それにより、ダイサイズが増大し、CUMT性能が低減される。多数のCUMT要素（例えば、10×10アレイより多いCUMT要素）を含むCUMTアレイでは、各要素へのコンタクトを提供するために金属相互接続トレースを利用することは概して、内部要素のために著しく複雑化され、代替の接続方式が必要とされている。このような接続方式の1つが基板貫通接続の利用である。

20

【0005】

開示される実施例は、ダイ2D CUMTアレイの製造を促進するため、底部側デバイス（ダイ）コンタクトが、CUMTセルの、又はダイを介する複数のCUMTセルを含むCUMT要素の、頂部プレート（頂部電極）への接続を成すことを可能にする基板貫通ビア（TSV）を有するCUMTデバイスを含む。複数のCUMT要素を有するCUMTデバイスでは、頂部電極は各CUMT要素に対して個別であり、そのため、各要素に対して単一TSVを用いるそれぞれの要素の個別アドレス指定が可能なり、また、概して、デバイス上の全てのCUMT要素に対し電気的に共通の底部側電極（例えば、Si基板の固体シート）がある。他の実施例において、CUMTデバイスは、全てのCUMT要素に対して電気的に共通の頂部電極と、それぞれの要素の個別アドレス指定を可能にするための各要素に対して個別の底部電極とを有し得る。

30

【図面の簡単な説明】

【0006】

40

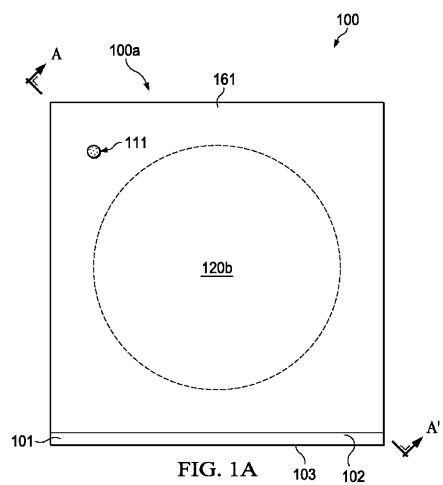

【図1A】例示の一実施例に従った、単一CUMTセルを備えたCUMT要素として示される例示のCUMTデバイスの上面図である。

【0007】

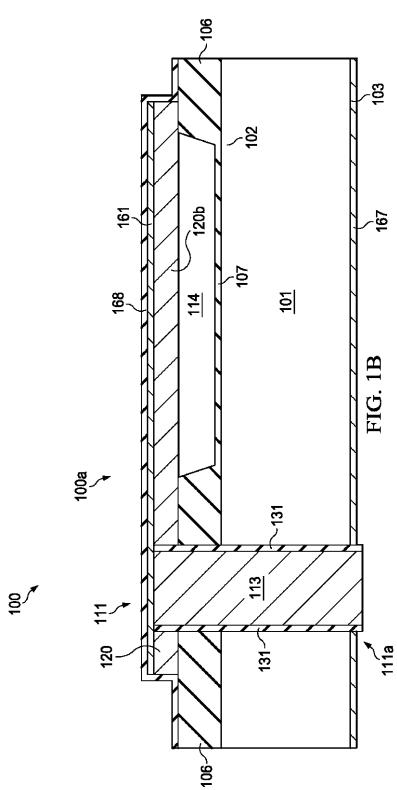

【図1B】図1Aに示す例示のCUMTデバイス／要素／セルの、図示する切断線A-A'に沿った断面図である。

【0008】

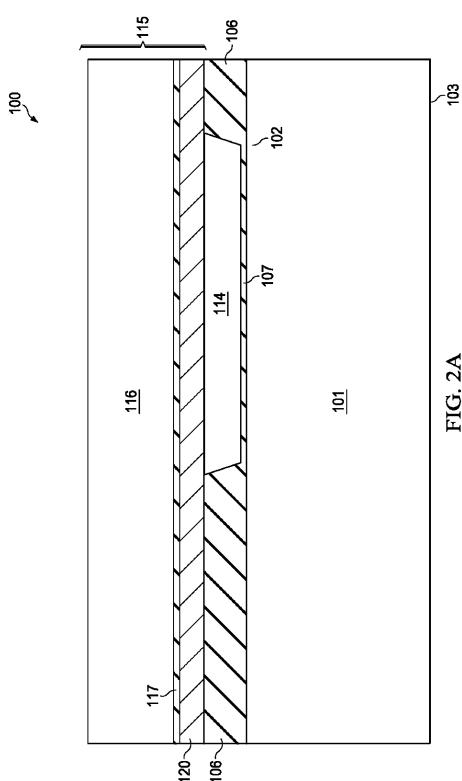

【図2A】例示の一実施例に従って、CUMTデバイスを形成する例示の方法のための処理進行を示す断面図である。

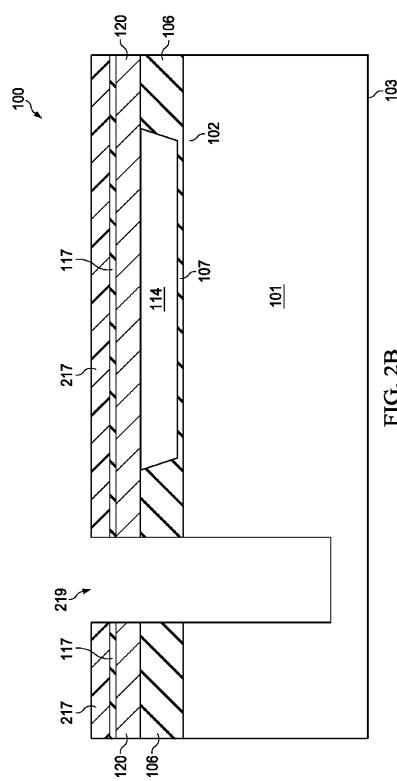

【図2B】例示の一実施例に従って、CUMTデバイスを形成する例示の方法のための処理進行を示す断面図である。

50

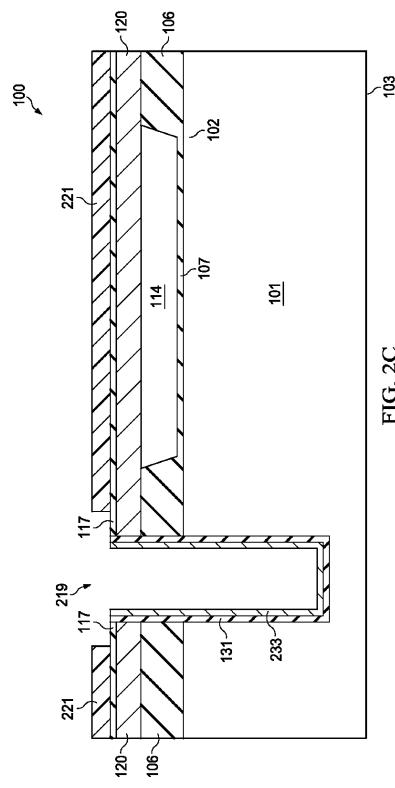

【図2C】例示の一実施例に従って、CUMTデバイスを形成する例示の方法のための処理進行を示す断面図である。

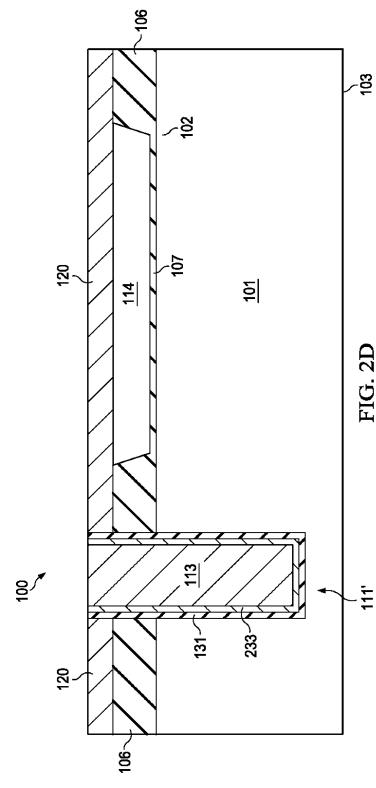

【図2D】例示の一実施例に従って、CUMTデバイスを形成する例示の方法のための処理進行を示す断面図である。

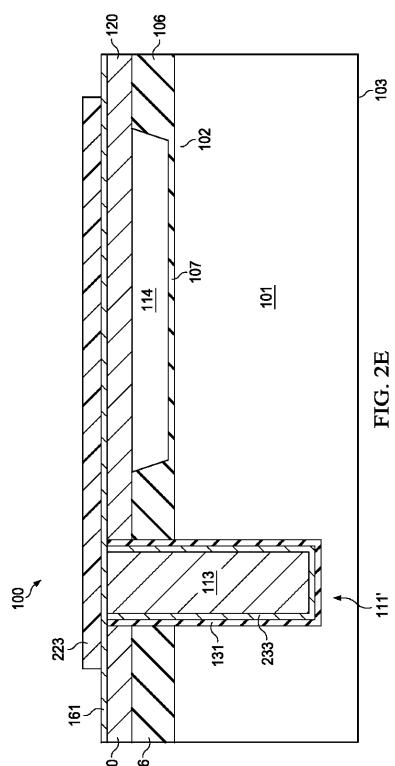

【図2E】例示の一実施例に従って、CUMTデバイスを形成する例示の方法のための処理進行を示す断面図である。

【図2F】例示の一実施例に従って、CUMTデバイスを形成する例示の方法のための処理進行を示す断面図である。

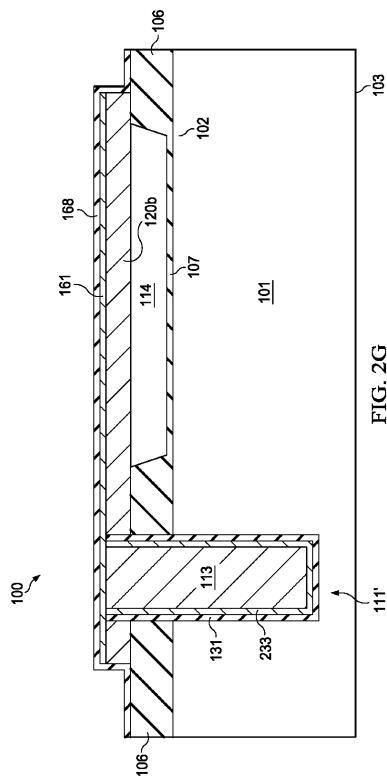

【図2G】例示の一実施例に従って、CUMTデバイスを形成する例示の方法のための処理進行を示す断面図である。

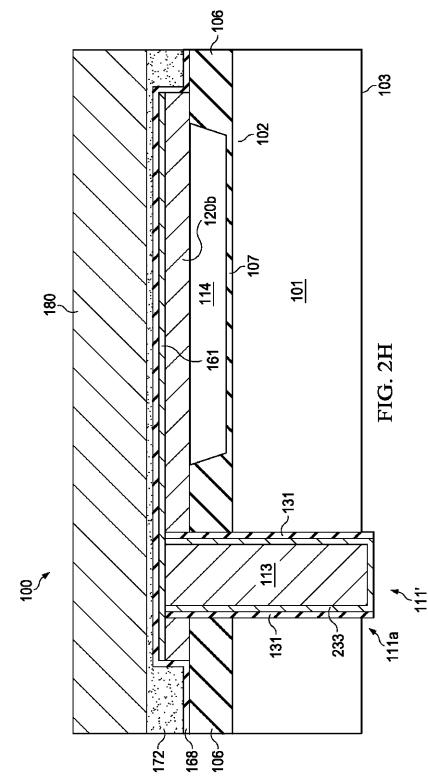

【図2H】例示の一実施例に従って、CUMTデバイスを形成する例示の方法のための処理進行を示す断面図である。

【0009】

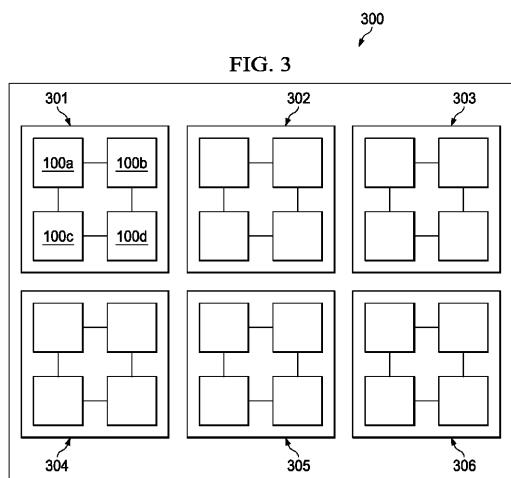

【図3】例示の一実施例に従った、各々図1A及び図1Bに示すCUMTセルを複数含む、複数のCUMT要素を含む例示のCUMTデバイスの上面図である。

【発明を実施するための形態】

【0010】

容量性微細加工超音波トランスデューサ(CUMT)センサユニット個体は、CUMTセンサセルである。CUMT要素を形成するために複数のCUMTセンサセルが(例えば、電気的に共通の可動薄膜120bを用いて)並列に接続され得る。CUMT要素は、任意の数(1)のCUMTセルを有し得る。典型的に、或る要素におけるCUMTセルが多いほど、所与の刺激に応答してその要素が生成し得る超音波出力圧力が大きい。CUMTアレイ(デバイス/ダイ)が任意の数のCUMT要素を有し得る。各CUMT要素が独立的にアドレス指定可能となるよう独立的に接続され得るように、それぞれのCUMT要素の電極の一方(例えば、頂部)が、他のCUMT要素の他方の電極(例えば、頂部)から電気的に絶縁され得る。本明細書に記載するように、或るCUMT要素における各CUMTセルのための可動薄膜120bを電気的に共通とすることで、単一TSVによるCUMT要素における全てのセルのアドレス指定が可能となる。

【0011】

図1Aは、例示の一実施例に従った、単一CUMTセル100aを備えたCUMT要素として示される、例示のCUMTデバイス100を図示する。後述の図1B及び他の図2A～図2Hに示す断面図のために切断線A-A'が提供されている。CUMTセル100aは、基板貫通ビア(TSV)111、及び頂部側102と底部側103とを有する単結晶材料(例えば、単結晶基板上のバルク単結晶シリコン又はシリコンエピタキシャル層)の第1の基板101を含む。

【0012】

図1Bに示すように、頂部側102はその上に、厚い誘電体領域106と薄い誘電体領域107とを含んで、パターニングされた誘電体層を含む。TSV111は、薄膜層120の頂部表面まで第1の基板101の全厚に延在する。TSV111は、誘電体ライナー131により、第1の基板101及び薄膜層120から電気的に絶縁される。誘電体ライナー131は、厚い誘電体領域106の側壁上を含むTSV111の全長に沿って示されているが、熱的に形成される誘電体ライナー131(例えば、シリコン酸化物)の場合は、堆積される誘電体ライナー131とは対照的に、誘電体ライナー131は、厚い誘電体領域106の側壁上に成長せず、そのため厚い誘電体領域106の側壁上にはない。TSV111は、一つの特定の実施例においてCuなど、TSV充填材料113を含む。TSV111はまた、第1の基板101の底部側103から突出する、任意選択の突出するTSVティップ111aを含んで図示される。

【0013】

SOI(silicon on insulator)基板115(図2Aで示す)として示される第2の基板の薄膜層120は、厚い誘電体領域106にボンディングされ、また、図示されるME

M S キャビティ 114 の上の可動薄膜 120b を提供するため第 1 の基板 101 の薄い誘電体領域 107 の上にある。このボンディングは、真空融解ボンディングなどの真空ボンディングを含み得る。パターニングされた頂部側金属層（例えば、AlCu 層）161 が、TSV111 の頂部の上、及び、TSV111 を可動薄膜 120b に結合する金属層部分を含む可動薄膜 120b の頂部の上にある。誘電体パッシベーション層 168 が CUMT セル 100a の頂部の上に示されている。

【0014】

第 1 の基板 101 は、単結晶シリコン、又は単結晶シリコン上のエピタキシャルシリコンを含み得る。第 1 の基板 101 は典型的に、0.1 cm より小さいか又はそれに等しい（）抵抗を有し、p 型又は n 型ドープされ得る。CUMT セル 100a は、第 1 の基板 101 の底部側 103 のパターニングされた金属層 167 を含んで示されており、これは、固定電極を実現するために CUMT セル 100a の底部側 103 の第 1 の電極コンタクトを提供する。上述のように、CUMT デバイスが、各々複数の CUMT セル 100a を含む複数の CUMT 要素を含む場合、パターニングされた金属層 167 により提供される固定電極コンタクトは、CUMT デバイス上の全ての CUMT 要素に対する共通底部側固定電極（例えば、Si シートなどの、第 1 の基板 101 の固体シート）のためのものである。

【0015】

TSV111 は、可動薄膜 120b への底部側接続を提供し、可動薄膜 120b は、CUMT デバイス 100 の CUMT セル 100a のための頂部プレートを提供する。上述のように、複数の CUMT 要素を有する CUMT デバイスでは、頂部電極は各 CUMT 要素に対して個別とされ得、各要素のためそれぞれの TSV111 を用いるそれぞれの要素の個別アドレス指定を可能にする。そのため、CUMT デバイス 100 により必要とされる頂部側コンタクト又はボンドパッドはない。

【0016】

CUMT デバイスの厚み及び寸法は特定の用途に合うように調節され得ることを留意されたい。例えば、180 kHz オペレーションでの空中（airborne）超音波用途のための典型的な例示の寸法は、直径が 1.12 mm の可動薄膜 120b、1.32 mm のプレート幅のパターニングされた頂部側金属層 161（CUMT セル 100a の側面上の頂部側金属層 161 の 100 μm プレート重なり）、及び 14 μm の厚みの可動薄膜 120b を有する CUMT セルである。

【0017】

図 2A～図 2H は、例示の一実施例に従って、異なる製造段階の間の CUMT デバイスを形成する例示の方法における工程を図示する。説明する CUMT デバイスは単一 CUMT センサセルを備えた単一要素を有して形成されるが、上述のように開示される CUMT デバイスが、複数の CUMT 要素を有する CUMT アレイを形成するように 1 つ又は複数の CUMT セルを各々が備えた、複数の CUMT 要素を有して形成されてもよい（後で説明する図 3 を参照されたい）。

【0018】

図 2A～図 2H は、単一 CUMT セル 100a を備えた単一 CUMT 要素を有する CUMT デバイスを形成する例示の方法のための処理における工程を図示する。複数の開示される CUMT 要素を含む CUMT デバイスを形成することを含み、開示される CUMT デバイスを形成するための他の手法を本開示の範囲から逸脱することなく用いることができる。CUMT 要素内の幾つかの CUMT セルが、所与のエリアにわたる出力圧力を増大させるためなど、所与の CUMT 要素における CUMT セルの可動薄膜 120b を共に結合することにより並列に接続され得る。CUMT セルを並列に接続することで、（駆動のための）インピーダンスが低減される。CUMT 要素は、ビームステアリングを独立的に促進するために用いるため又は大きなエリアにわたる改善された空間的解像度のため、互いに電気的に絶縁され得る。また、コモンモード信号を改善するため又は製造不均整を緩和するために、差動的に CUMT 要素を駆動 / 感知することもできる。

10

20

30

40

50

## 【0019】

シリコン酸化物層を含むなどの厚い誘電体領域106が、第1の基板101の頂部側102に提供される。第1の基板101は、概して、シリコンベースの基板又は他の基板を含む、任意の単結晶基板材料を含み得る。第1の基板101は、約0.01 cmなど、0.1 cmに等しいかそれより小さい低基板抵抗を提供する。

## 【0020】

一つの特定の実施例において、厚い誘電体領域106aを形成するため、厚いシリコン酸化物層が、高圧酸化(HiPOx)プロセスを用いて4.5 μm ~ 5.5 μmの厚みまで成長される。HiPOxの利用は、厚い熱的酸化物層の急速な成長を促進し、また概して、ダイにわたって典型的に±1%未満の良好な厚み制御を提供する。1つの特定の例示のセットのHiPOxプロセス条件には、最初の(virgin)第1の基板101(例えば、バルク単結晶シリコンウエハ)上で9.5時間の蒸気内の25気圧の1,000の温度が含まれ、フォトリソグラフィのための整合マークが後にこのプロセスにおいてエッチングされる。

10

## 【0021】

代替として、厚い誘電体領域106はまた、(例えば、概して酸化に対するマスクとしてシリコン窒化物を用いてシリコンウエハ上の選択されたエリア(ここでは厚い誘電体領域106)に二酸化シリコンが形成される、シリコンの局所酸化(LOCOS)プロセスを用いる)従来の熱的成長されたシリコン酸化物を含み得るか、又は、シリコン酸化物又は他の誘電性材料を含む堆積された誘電体層であり得る。しかし、従来の酸化を用いるLOCOSアプローチは概して5 μmの厚みの(又は一層厚い)酸化物層を生成せず、堆積される誘電体(例えば、酸化物)フィルムは、概してダイにわたって±1%未満の厚み制御を提供しない。

20

## 【0022】

最小の表面汚染又は粗さを確実にするために、一般に存在する基板ベンダーのレーザー・スクライプを用いることができ、これは後続のウエハボンディング工程の助けとなり得る。表側整合マークのマスキング及びエッチングがこれに続き得る。レジストストリップ及び事前洗浄プロセスが、厚い誘電体領域106のための滑らかな表面を確実にすることを助け得、厚い誘電体領域106は、SOI基板115又は標準的なバルクシリコン基板などの第2の基板の、それに対するボンディング薄膜層120のためのプロセスにおいて後に用いられる。

30

## 【0023】

第1の基板101(例えば、Siウエハ)上の各CUMTアレイ/ダイに対し少なくとも1つのエッチングされた単一セルCUMT要素を画定することをまず開始するため、第1のマスキングレベル「CELLETCH」が、厚い誘電体領域106(例えば、厚いシリコン酸化物層)を介する後続のエッチングをサポートするために厚いフォトレジストを用いる。厚い誘電体領域106がシリコン酸化物を含み且つ約5 μm ~ 5.3 μmの厚みを有するときに約4.65 μmのシリコン酸化物をエッチングするためなど、厚い誘電体領域106の第1の部分をエッチングするために、非重合であるプラズマエッチングを用いることができる。80度までの側壁傾斜が概して望ましく、これは自然レジスト浸食から達成され得る。プラズマエッチングの後、厚い誘電体領域106の残りの部分(例えば、0.5 μmのシリコン酸化物)は、第1の基板101の頂部側102を損傷させることを避けるために、基板材料(例えば、Si)に対してエッチング選択性を提供するウェットエッチングによって取り除かれ得る。

40

## 【0024】

第1の基板101(例えば、ウエハ)の頂部側102の約50%が、厚い誘電体領域106のエッチングの間、概して開かれ(露出され)得る。レジストはその後剥がされる(例えば、湿式ストリッププロセス)。適切な事前酸化洗浄に続いて、酸化工程において、薄い誘電体領域107を形成するように、薄い(例えば、0.3 μmの)CUMTセル酸化物が成長され得る。

50

## 【0025】

図2Aは、SOI基板（例えば、SOIウエハ）115の真空融解ボンディング後の製造過程のCUMTデバイスの断面図を示し、SOI基板115は、ハンドル（例えば、ウエハ）116、埋め込み誘電体層117（概して当業界で「埋め込み酸化物層」又は「(BOX)層」と称される）、及び薄膜層120（例えば、概してSOIの分野において「アクティブ層」と称される）を含む。薄膜層120は、第1の基板101の厚い誘電体領域106にボンディングされる。

## 【0026】

犠牲のハンドル116は、ドープされていない又は軽くドープされた（n又はp型ドープされた）シリコンなどの任意の適切な材料から形成される、任意の適切な半導体ウエハを表し得る。同じく犠牲の埋め込み誘電体層117は、シリコン酸化物層などの電気的に絶縁性の（誘電体）材料の任意の適切な層であり得る。薄膜層120は、ドープされた単一結晶シリコンなどの基板材料の任意の適切な層を表す。特定の実施例において、ハンドル116は、約5～10 cmの抵抗のシリコンウエハを含み、埋め込み誘電体層117は、約1.5 μm～2.5 μmの厚みであるシリコン酸化物層を表し、薄膜層120は、約5 cmの抵抗のドープされたシリコンが約14 μm±5 μmの厚みであることを表す。セル間又は要素間の電気的相互接続の目的のため、薄膜層120は、その上に金属層を含み得、これは、経路に低抵抗経路を提供させる。

## 【0027】

しかし、上述のように、コストを低減するためSOI基板の代替として、標準的なシリコンバルク基板材料（例えば、バルクSiウエハ）を含む第2の基板が、第1の基板101（CUMT基板／ウエハ）の厚い誘電体領域106にボンディングされ得る。この実施例において、ボンディング後、第2の基板材料は、14 μm±5 μmの厚みなど所望のターゲット薄膜厚みまでバックグラウンド及び研磨によって薄化され得る。

## 【0028】

CUMTデバイス／ダイが複数のCUMT要素（CUMTアレイ）を含む実施例では、薄膜層120は、各CUMT要素における全てのCUMTセルに対し電気的に共通であり得る。各CUMT要素が、要素内のセルに対する複数の電気的に接続される可動薄膜120bを含む個別の／特有の頂部プレートを有し得、これらは、第1の基板101の底部側103からアクセス可能な専用TSVを介して電気的に接続され得る。各CUMT要素の頂部プレートの低抵抗は、可動薄膜120b上の後続の金属堆積によって及びこれ以後に説明するようなパターニング処理工程によって提供され得る。洗浄及びプラズマ事前処理を含む適切な既知のボンディング手法を用いることができる。

## 【0029】

真空融解ウエハボンディングでは、当業界で通常既知であるように、良好なウエハボンディングを確実にする属性には、典型的に3A未満の表面粗さの滑らかなボンディング面が含まれる。成長された熱的酸化物及びシリコン基板は概してこの要件を満たす。ボンディング前に、表面は、典型的に10分間、75又は80でNH<sub>4</sub>OH（水酸化アンモニウム）+H<sub>2</sub>O<sub>2</sub>（過酸化水素）+H<sub>2</sub>O（水）の1:1:5溶液で、RCA洗浄（SC-1、ここで、SCは標準的な洗浄（Standard Clean）を表す）で処理され得る。第2のRCA洗浄工程は、薄い酸化物層及びいくらかのイオン性汚染物質を取り除くために、25のHF+H<sub>2</sub>Oの1:50溶液における短時間浸漬である。第3及び最後の工程のRCA洗浄（SC-2と称される）は、75又は80のHCl+H<sub>2</sub>O<sub>2</sub>+H<sub>2</sub>Oの1:1:6溶液で実施される。この処理は、金属性（イオン性）汚染物質の残ったトレースを効率的に取り除く。N<sub>2</sub>プラズマアクティベーション及びDI水リーンスがこれに続き得る。真空ボンディングは典型的に、8×10<sup>-5</sup> mbar未満の圧力で実施される。最終的な工程として、ボンディングされた表面は、4時間の1050 N<sub>2</sub>アニールなど、数時間N<sub>2</sub>内でアニーリングされる。

## 【0030】

ハンドル116はその後、約150 μmのポストバックグラウンドターゲットまでハン

10

20

30

40

50

ドル 116 をバックグラインドすること、バックグラインド後、バックグラインド後に残ったハンドルのウェットエッティング前に、第 2 の 4 時間 1050 アニールを実施すること、及びその後、残ったハンドルをウェットエッティングすることによるなど、ボンディング後に取り除かれる。ハンドル 116 がシリコンを含むとき、バックグラインド後に残ったハンドルは、水酸化物（例えば、KOH 又は TMAH）を用いるなど、埋め込み誘電体層 117 で止まる、ウェットシリコンエッティングにおいてエッティングされ得る。可動薄膜（例えば、シリコンプレート）120b をマスキング及びエッティングすることで、整合マークを再び開けるため及び後続の処理工程のための適切な整合を可能にするために、整合マークの上の薄膜層 120 が取り除かれる。薄膜層 120 はエッティングのため概して比較的厚い層である（例えば、約 14 μm の厚み）ため、Bosch エッティングが、薄膜層 120 のエッティングの間、レジスト浸食を補償し得る。当業界で既知であるように、パルスされた又は時間多重化されたエッティングとしても知られている Bosch プロセスは、ほぼ垂直のエッティングされた構造を得るために 2 つのモード / 位相間で反復的に交替する。

#### 【0031】

図 2B は、マスキングレベル Mask 「TSVHOLE」（マスク #2）後の製造過程の CUMT デバイスを図示する。一つの特定の実施例において、TSV ホール（埋め込みビア）219 は、直径が 30 μm で 150 μm の深さ（総深さ）である。レジスト 217 は、1.1 μm の埋め込み誘電体層 117、及び 14 μm の薄膜層 120、及び 5.1 μm の厚い誘電体領域 106、及び第 1 の基板 101 内に 130 μm など、提供されるスタッカを介するエッティングをサポートするために充分な厚みであるべきである。その後、TSV ホール 219 はエッティングされる。埋め込み誘電体層 117（例えばシリコン酸化物）をエッティングするため及びシリコンの場合に第 1 の基板 101 をエッティングするための Bosch エッティングに、個別のエッティングツールを用いることができる。

#### 【0032】

その後、レジスト 217 は剥がされ、誘電体ライナー 131（例えば、0.5 μm の誘電体酸化物）が、埋め込みビア / TSV ホール 219 内の半導体表面上に堆積されるか又は熱成長される。誘電体ライナー 131 上に形成される拡散障壁金属層が、TSV をフレーミングし、Cu などの高度に可動性の金属 TSV 充填材料の場合に半導体への TSV 充填材（又はコア）材料 113 の流出（escape）から保護する。例えば、一つの特定の実施例において、0.0875 μm の Ta / TaN 拡散障壁金属層及び 1.5 μm の Cu シード層 233（図 2C 参照）が、銅 TSV 充填材料 113 の実施例のために誘電体ライナー 131 上に堆積される。代替として、シード層 233 は、例えば、チタンの上の銅を含み得る。

#### 【0033】

図 2C は、レジスト 221 を用いるマスキングレベル Mask 「CUMOLD」（マスク #3）後の製造過程の CUMT デバイスを図示する。このマスクは、CUMT セルの一部の上のめっきから Cu などの金属を排除するために用いられ得る。マスキング後 TSV にレジストがないことを確実にするためにネガティブレジストが用いられ得る。可動薄膜 120b（例えば、Si プレート）が数ミクロン撓み得、また、銅充填された TSV の場合の後続の Cu 化学機械研磨（CMP）工程が CUMT セルの上の銅を完全には取り除かれない可能性があるため、このマスクは有効である。

#### 【0034】

その後、充填された TSV ホール 219 を TSV 充填材料 113 で画定するための後続の CMP で（例えば、約 15 μm の Cu が用いられる）、TSV 充填材料 113 を電気めっきすることなどで、金属層が堆積される。レジスト 221 はその後剥がされる。図 2D は、埋め込み TSV 111' の上の及びその横のシード層 233 上の TSV 充填材料 113 から金属ネールヘッドが取り除かれて示されるような、TSV 充填材料 113 の CMP、及びフィールドエリアの上の埋め込み誘電体層 117 と共に誘電体ライナー 131 が除去された後の、TSV 充填材料 113 堆積（例えば、Cu）後の製造過程の CUMT デバイスの断面図を示す。アニール工程がこれに続き得る。存在する場合に全ての残りの障壁

10

20

30

40

50

金属（例えばCu + TaN）を取り除くために、第2のTSV CMPが用いられる。CUMTセルの上の残留物を取り除くためにウェットストリップが用いられる。その後、誘電体ライナー131は埋め込み誘電体層117と共に取り除かれ、薄膜層120（例えば、Si）上で止まる。

【0035】

図2Eは、0.5 μmの厚みのAlCu金属層など、頂部側金属層161の堆積後の製造過程のCUMTデバイスを図示する。頂部側金属層161は、薄膜層120プレートメタライゼーションを提供し、薄膜層120を埋め込みTSV111'の頂部側に接続する。レジスト223を用いるマスキングレベル「ALTOP」（マスク#4）が示されており、これにより、CUMT要素の上の頂部側金属層161（例えば、AlCu層）を画定するためのエッチングが可能となる。ALTOP CDは、最終的なプレート寸法より小さく（例えば、1 μm / 辺小さく）され得る。可動薄膜120（例えば、Siプレート）をパターニングする前に頂部側金属層161をパターニングすることで、頂部側金属層161及びレジストステップカバレッジ問題両方が避けられる。頂部側金属層161は、レジスト223における開口を用いてフィールドエリアからウェットエッチングされ得る。レジスト223はその後剥がされる。

【0036】

図2Fは、マスクレベル「PLATESI」（マスク#5）を用いるレジスト225のパターニング後の製造過程のCUMTデバイスを図示する。レジスト225は、パターニングされた頂部側金属層161（例えば、AlCu層）を完全に封止し得る。このマスクは、上述のAlCu（ALTOP）マスクより大きく（例えば、1 μm / 辺大きく）され得る。

【0037】

その後、薄膜層120は、複数のCUMT要素を有するCUMTデバイスのためにCUMT要素を分けるため、及び図示される可動薄膜120bを形成するために、レジスト225を用いてエッチングされる。薄膜層120のエッチングは、厚い誘電体領域106上で止まる。側壁スカラップ（scalloping）を最小化するために、短いサイクルのBoschエッチングが用いられる。このエッチングは、凹まないように構成されるべきである。レジスト225はその後剥がされる。

【0038】

図2Gは、一つの特定の実施例において、約0.2 μmのプラズマオルトケイ酸テトラエチル（TEOS）由来のシリコン酸化物層、及びその後の、0.2 μmのプラズマ窒化物パッシベーション層など、誘電体パッシベーション層168を堆積した後の製造過程のCUMTデバイスを図示する。誘電体パッシベーション層168は、可動薄膜120bの側壁を覆って示されている。CUMT用途に応じて、一層厚いパッシベーションスタックを用いることができる。最終的な合金が、N<sub>2</sub> + H<sub>2</sub>（形成ガス）内の400などで実施され得る。

【0039】

図2Hは、任意選択で、接着剤172を用いて一時キャリアウエハ180に製造過程CUMT基板（例えば、ウエハ）をボンディングし、第1の基板101の底部側103のTSVをバックグラウンドして露出させ、突出するTSVティップ111aを形成した後の、製造過程のCUMTデバイスを図示する。バックグラウンドは、埋め込みTSV近くの製造過程CUMT基板（例えば、ウエハ）を薄化し得、また、全ての底部側フィルムを取り除き得、一つの特定の実施例において、第1の基板101のための725 μmの厚みのSi基板のうちの約550 μmを取り除き、約175 μmを残す。第1の基板101の底部側103は、約1000 μmの厚みとなるように第1の基板101を残して、TSVティップ111aを露出するようにエッチングされ得る。TSV111のための露出されたTSV充填材料113を有するTSVティップ111aを形成するために誘電体ライナー131及び障壁金属（存在する場合）が取り除かれるように、XeFプラズマエッチング又はウェットSiエッチングを用いることができる。誘電体ライナー131及び障壁金属の

10

20

30

40

50

プラズマエッティングが、T S V 1 1 1 及び 1 1 2 の側壁上に誘電体（例えば、酸化物）スペーサを概して残す。

#### 【 0 0 4 0 】

その後、1つの特定の実施例において T i / N i / A g 層（例えば、1 0 0 0 の T i + 2 8 0 0 の N i + 1 5 0 0 の A g）など、第1の基板の底部側 1 0 3 上に金属層が堆積される。第1の基板 1 0 1 の底部側 1 0 3 は、金属層 1 6 7 堆積前に洗浄され得る。約 3 0 0 の事前スパッタエッティングが用いられ得る。その後、マスキングレベル「T S V E X P」（マスク # 6）が、金属層 1 6 7 のエリアを保護するために用いられ得、一方、それは T S V ティップ 1 1 1 a から剥がされる。第1の基板 1 0 1 の底部側 1 0 3 のパターニングされた金属層 1 6 7 を形成するためのパターニング、及びマスク 6 レジストのストリップの後、上述で図 1 B に示す C U M T デバイス 1 0 0 が生じる（図 1 B には Cu シード層 2 3 3 が示されていない）。ダイシング（シンギュレーション）に続いて、結果の C U M T ダイは、制御ダイの頂部上にボンディングされるなど、パッケージングされ得る。

10

#### 【 0 0 4 1 】

図 3 は、複数の C U M T 要素 3 0 1 ~ 3 0 6 を含む、例示の C U M T デバイス（ダイ）3 0 0 を示す。例示の一実施例に従って、各容量性 C U M T 要素は、要素内で共に接続される C U M T セル 1 0 0 a ~ 1 0 0 d として示される 4 つの図 1 A 及び図 1 B における C U M T セル 1 0 0 a を含む。上述のように、頂部電極は、各 C U M T 要素に対して個別であり得、そのため、各要素に対して単一 T S V を用いるそれぞれの要素の個別アドレス指定が可能となり、この場合、デバイス上の全ての C U M T 要素のための共通底部側電極（例えば、S i の固体シート）がある。他の実施例において、C U M T デバイスは、各要素のための共通頂部電極、及びそれぞれの要素の個別のアドレス指定を可能にするための各要素のための個別の底部電極を有する。

20

#### 【 0 0 4 2 】

各 C U M T 要素が 4 つの C U M T セル 1 0 0 a ~ 1 0 0 d を含む、6 つの C U M T 要素 3 0 1 ~ 3 0 6 を有する C U M T デバイス 3 0 0 が示されているが、開示される C U M T デバイスは、各々が任意の数の C U M T セルを有する任意の数の C U M T 要素を有していてよい。C U M T 要素 3 0 1 ~ 3 0 6 は、互いに電気的に絶縁され得、（駆動のため）インピーダンスを低減するために（例えば、それらのそれぞれの T S V 1 1 1 を共通ソースに接続することにより）ダイに接して又はダイから離れて並列に接続され得、又は（感知のため）インピーダンスを増大させるために（ダイに接して又はダイから離れて）直列に接続され得る。それぞれの C U M T 要素は、コモンモード信号を差動的に改善するため又は製造不均整を緩和するために駆動 / 感知され得る。

30

#### 【 0 0 4 3 】

開示される C U M T デバイスの利点には、4 度に少ないマスクレベルを用いるフルプロセスが含まれる。他の利点には、C U M T デバイスの頂部側の超音波伝送表面（可動薄膜 1 2 0 b）に結合するためにダイサイズを増大させ且つワイヤボンディングを必要とする従来のボンドパッドを必要とすることなく、一層小さなダイサイズが可能となることが含まれる。開示される C U M T デバイスはまた、パッケージングオペレーションを単純化し、その結果、伝送媒体への結合が容易となり、これによりパッケージングコストが低減される。両電極が C U M T デバイスの底部側から接触されるため、開示される C U M T デバイスはまた、制御ダイ上に C U M T ダイをスタックするオプションを促進する。

40

#### 【 0 0 4 4 】

開示される実施例は、種々の異なるデバイス及び関連する製品を形成するために種々のアッセンブリフローに統合され得る半導体ダイを形成するために用いることができる。当業者であれば、本発明の特許請求の範囲内で、説明した例示の実施例に変形が成され得ること、及び多くの他の実施例が可能であることが分かるであろう。

【図 1 A】

FIG. 1A

【図 1 B】

FIG. 1B

【図 2 A】

FIG. 2A

【図 2 B】

FIG. 2B

【図2C】

FIG. 2C

【図2D】

FIG. 2D

【図2E】

FIG. 2E

【図2F】

FIG. 2F

【図 2 G】

FIG. 2G

【図 2 H】

FIG. 2H

【図 3】

FIG. 3

---

フロントページの続き

(72)発明者 ピーター ビー ジョンソン

アメリカ合衆国 94087 カリフォルニア州 サニーヴェール, オンフルール ドライブ

1614

(72)発明者 アイラ オークトゥリー ワイガント

アメリカ合衆国 94301 カリフォルニア州 パロ アルト 906, アルマ ストリート

101

審査官 大石 剛

(56)参考文献 国際公開第2005/120130 (WO, A1)

国際公開第2005/120360 (WO, A1)

特開2009-050560 (JP, A)

特開2011-109358 (JP, A)

(58)調査した分野(Int.Cl., DB名)

B81B 3/00

B81C 3/00

H01L 23/12

H04R 19/00

H04R 31/00