(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5972473号

(P5972473)

(45) 発行日 平成28年8月17日(2016.8.17)

(24) 登録日 平成28年7月22日(2016.7.22)

|                          |                |

|--------------------------|----------------|

| (51) Int.Cl.             | F 1            |

| HO 1 L 21/822 (2006.01)  | HO 1 L 27/04 H |

| HO 1 L 27/04 (2006.01)   | HO 1 L 21/82 F |

| HO 1 L 21/82 (2006.01)   | HO 1 L 21/88 J |

| HO 1 L 21/3205 (2006.01) | HO 1 L 25/08 C |

| HO 1 L 21/768 (2006.01)  |                |

請求項の数 30 (全 21 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2015-535786 (P2015-535786)  |

| (86) (22) 出願日 | 平成25年10月3日 (2013.10.3)        |

| (65) 公表番号     | 特表2015-532534 (P2015-532534A) |

| (43) 公表日      | 平成27年11月9日 (2015.11.9)        |

| (86) 國際出願番号   | PCT/US2013/063297             |

| (87) 國際公開番号   | W02014/055777                 |

| (87) 國際公開日    | 平成26年4月10日 (2014.4.10)        |

| 審査請求日         | 平成28年1月12日 (2016.1.12)        |

| (31) 優先権主張番号  | 13/646,109                    |

| (32) 優先日      | 平成24年10月5日 (2012.10.5)        |

| (33) 優先権主張国   | 米国(US)                        |

早期審査対象出願

|           |                                                                                    |

|-----------|------------------------------------------------------------------------------------|

| (73) 特許権者 | 507364838<br>クアルコム、インコーポレイテッド<br>アメリカ合衆国 カリフォルニア 921<br>21 サン・ディエゴ モアハウス・ドライブ 5775 |

| (74) 代理人  | 100108453<br>弁理士 村山 靖彦                                                             |

| (74) 代理人  | 100163522<br>弁理士 黒田 晋平                                                             |

| (72) 発明者  | ブライアン・エム・ヘンダーソン<br>アメリカ合衆国・カリフォルニア・921<br>21・サン・ディエゴ・モアハウス・ドライブ・5775               |

最終頁に続く

(54) 【発明の名称】スタック型マルチチップ集積回路の静電気保護

## (57) 【特許請求の範囲】

## 【請求項 1】

第1の集積回路(I C)ダイと、

前記第1のI Cダイに対してスタック型配置にある第2のI Cダイであって、前記第2のI Cダイにおける基板貫通ビア(T S V)によって前記第1のI Cダイに電気的に結合するように構成された入力/出力(I / O)ノードを有する第2のI Cダイと、

前記I / Oノードに電気的に結合するように構成された前記第2のI Cダイのアクティブ表面上のヒューズと、

を含み、

前記ヒューズは、静電放電(E S D)電流サージがグランドに直接行き、前記第2のダイの増幅器回路をバイパスすることを可能にし、前記E S D電流サージによって生じるダメージから前記増幅器回路を保護するように構成されており、

前記増幅器回路は、前記I / Oノードをグランドから電気的に切断し、前記ヒューズを閉状態から開状態に遷移させるためのヒューズ破断電流を生成し、且つ前記I / Oノードで出力信号を提供及び/または入力信号を受け取るように構成されている、マルチチップモジュール。

## 【請求項 2】

前記ヒューズは、前記第1のI Cダイを前記第2のI Cダイに電気的に結合することに応答して起こる前記E S Dによって生じるダメージから前記第2のI Cダイを保護するように構成される、請求項1に記載のマルチチップモジュール。

**【請求項 3】**

前記ヒューズは、前記 I / O ノードに結合された第 1 の端子と、グランドに結合された第 2 の端子とを含む、請求項 1 に記載のマルチチップモジュール。

**【請求項 4】**

前記ヒューズは、閉状態である場合、前記 I / O ノードからグランドへの短絡回路バスを提供する、請求項 1 に記載のマルチチップモジュール。

**【請求項 5】**

前記増幅器回路は、増幅器入力端子および / または増幅器出力端子を含み、前記増幅器出力端子および前記増幅器入力端子のうちの 1 つは、前記 I / O ノードに電気的に結合するように構成される、請求項 1 に記載のマルチチップモジュール。 10

**【請求項 6】**

前記ヒューズは、50マイクロ秒 (μs) ~ 200 μs 続く 1 ミリアンペア (mA) ~ 100 mA のパラメータ、10 μs ~ 200 μs 続く 5 mA ~ 100 mA のパラメータ、または 10 μs ~ 200 μs 続く 10 mA ~ 100 mA のパラメータを有する前記ヒューズ破断電流に応答して前記閉状態から前記開状態に遷移する、請求項 1 に記載のマルチチップモジュール。

**【請求項 7】**

前記ヒューズは、前記 ESD によって生成された、前記 I / O ノードにおける前記電流サージに応答して閉状態のままであり、前記第 2 の IC ダイの前記増幅器回路によって生成されたヒューズ破断電流に応答して開状態に遷移する、請求項 1 に記載のマルチチップモジュール。 20

**【請求項 8】**

前記ヒューズは、ダイオードが無い ESD 保護回路の一部である、請求項 1 に記載のマルチチップモジュール。

**【請求項 9】**

前記ヒューズは、金属ヒューズまたはポリシリコンヒューズである、請求項 1 に記載のマルチチップモジュール。

**【請求項 10】**

前記ヒューズは、開状態である場合、前記 I / O ノードとグランドとの間に 10 メガオームよりも大きいかまたはそれに等しい抵抗値を提供する、請求項 1 に記載のマルチチップモジュール。 30

**【請求項 11】**

前記マルチチップモジュールは、音楽プレーヤ、ビデオプレーヤ、娯楽ユニット、ナビゲーションデバイス、通信デバイス、モバイルフォン、スマートフォン、携帯情報端末、固定位置端末、タブレットコンピュータ、および / またはラップトップコンピュータのうちの少なくとも 1 つに組み込まれる、請求項 1 に記載のマルチチップモジュール。

**【請求項 12】**

前記ヒューズが開状態になり、前記 I / O ノードがグランドから電気的に切断されるとき、前記 I / O ノードに電気的に結合された I / O バッファは、前記 I / O ノードを経て前記出力信号を提供および / または前記入力信号を受け取る、請求項 1 に記載のマルチチップモジュール。 40

**【請求項 13】**

前記第 1 の IC ダイが前記第 2 の IC ダイに電気的且つ物理的に結合されるとき、前記 ESD 電流サージが起こらず、且つ前記ヒューズが前記閉状態のままである場合、前記 I / O バッファは前記ヒューズを前記閉状態から前記開状態へ遷移させる電流の流れを生成する、請求項 12 に記載のマルチチップモジュール。

**【請求項 14】**

マルチチップモジュールを製造する方法であって、

第 1 の集積回路 (IC) ダイを提供するステップと、

前記第 1 の IC ダイに対してスタック型配置にある第 2 の集積回路ダイを提供するステ 50

ップと、

前記第2のICダイに基板貫通ビア(TSV)を提供し、前記TSVを経て、前記第2のICダイの入力/出力(I/O)ノードから前記第1のICダイへの電気的パスを提供するステップと、

前記第2のICダイのアクティブ表面上にヒューズを形成するステップとを含み、

前記ヒューズは、前記I/Oノードに電気的に結合されており、静電放電(ESD)電流サージがグランドに直接行き、前記第2のダイの増幅器回路をバイパスすることを可能にし、前記ESD電流サージによって生じるダメージから前記増幅器回路を保護しており、

前記増幅器回路は、前記I/Oノードをグランドから電気的に切断し、前記ヒューズを閉状態から開状態に遷移させるためのヒューズ破断電流を生成し、且つ前記I/Oノードで出力信号を提供および/または入力信号を受け取るように構成されている、方法。

#### 【請求項15】

前記ヒューズは、前記第1のICダイを前記第2のICダイに電気的に結合することに応答して起こる前記ESDによって生じるダメージから前記第2のICダイを保護する、請求項14に記載の方法。

#### 【請求項16】

前記ヒューズの第1の端子を前記I/Oノードに結合するステップと、

前記ヒューズの第2の端子をグランドに結合するステップと

をさらに含む、請求項14に記載の方法。

#### 【請求項17】

前記ヒューズが閉状態である間、前記I/Oノードからグランドへの短絡回路パスを提供するステップ

をさらに含む、請求項14に記載の方法。

#### 【請求項18】

前記増幅器回路は、増幅器出力端子および/または増幅器入力端子を含み、前記増幅器出力端子および前記増幅器入力端子のうちの1つは、前記I/Oノードに電気的に結合されている、請求項14に記載の方法。

#### 【請求項19】

前記ヒューズ破断電流は、50マイクロ秒(μs)～200μs続く1ミリアンペア(mA)～100mAのパラメータ、10μs～200μs続く5mA～100mAのパラメータ、または10μs～200μs続く10mA～100mAのパラメータを有する、請求項14に記載の方法。

#### 【請求項20】

前記ヒューズは、前記ESDによって生成された、前記I/Oノードにおける電流サージに応答して閉状態であり、前記第2のICダイの増幅器回路によって生成されたヒューズ破断電流に応答して開状態である、請求項14に記載の方法。

#### 【請求項21】

前記マルチチップモジュールは、音楽プレーヤ、ビデオプレーヤ、娛樂ユニット、ナビゲーションデバイス、通信デバイス、モバイルフォン、スマートフォン、携帯情報端末、固定位置端末、タブレットコンピュータ、および/またはラップトップコンピュータのうちの少なくとも1つに組み込まれる、請求項14に記載の方法。

#### 【請求項22】

前記ヒューズが開状態になり、前記I/Oノードがグランドから電気的に切断されるとき、前記I/Oノードに電気的に結合されたI/Oバッファは、前記I/Oノードを経て前記出力信号を提供および/または前記入力信号を受け取る、請求項14に記載の方法。

#### 【請求項23】

前記第1のICダイが前記第2のICダイに電気的且つ物理的に結合されるとき、前記

10

20

30

40

50

E S D 電流サージが起こらず、且つ前記ヒューズが前記閉状態のままである場合、前記 I / O バッファは前記ヒューズを前記閉状態から前記開状態へ遷移させる電流の流れを生成する、請求項 2 2 に記載の方法。

**【請求項 2 4】**

第 1 の集積回路 ( I C ) ダイと、

前記第 1 の I C ダイに対してスタック型配置にあり、入力 / 出力 ( I / O ) ノードを有する第 2 の I C ダイと、

前記第 1 の I C ダイに電気的に結合するように前記第 2 の I C ダイの前記 I / O ノードを構成するための手段と、

静電放電 ( E S D ) 電流サージがグランドへ直接行き、前記第 2 の I C ダイの増幅器回路をバイパスすることを可能にすることによって、前記 E S D 電流サージによって生じるダメージから前記増幅器回路を保護するための手段であって、前記第 2 の I C ダイのアクティプ表面上に配置された保護するための手段と、を含み、10

前記増幅器回路は、前記 I / O ノードをグランドから電気的に切断し、保護するための前記手段を有効状態から無効状態に遷移させるためのヒューズ破断電流を生成するよう、且つ前記 I / O ノードで出力信号を提供及び / または入力信号を受け取るように構成されている、マルチチップモジュール。

**【請求項 2 5】**

保護するための前記手段は、前記第 1 の I C ダイを前記第 2 の I C ダイに電気的に結合することに応答して起こる前記 E S D によって生じるダメージから前記第 2 の I C ダイの前記増幅器回路を保護するように構成されている、請求項 2 4 に記載のマルチチップモジュール。20

**【請求項 2 6】**

前記第 2 の I C ダイの前記増幅器回路を保護するための前記手段は、前記 I / O ノードに結合された第 1 の端子と、グランドに結合された第 2 の端子とを有するヒューズである、請求項 2 4 に記載のマルチチップモジュール。

**【請求項 2 7】**

前記ヒューズは、閉状態である場合、前記 I / O ノードからグランドへの短絡回路バスを提供する、請求項 2 6 に記載のマルチチップモジュール。

**【請求項 2 8】**

前記ヒューズは、前記 E S D によって生成された、前記 I / O ノードにおける電流サージに応答して閉状態のままであり、前記増幅器回路によって生成されたヒューズ破断電流に応答して開状態に遷移する、請求項 2 6 に記載のマルチチップモジュール。30

**【請求項 2 9】**

保護するための前記手段が無効状態になり、前記 I / O ノードがグランドから電気的に切断されるとき、前記 I / O ノードに電気的に結合された I / O バッファは、前記 I / O ノードを経て前記出力信号を提供および / または前記入力信号を受け取る、請求項 2 4 に記載のマルチチップモジュール。

**【請求項 3 0】**

前記第 1 の I C ダイが前記第 2 の I C ダイに電気的且つ物理的に結合されるとき、前記 E S D 電流サージが起こらず、且つ保護するための前記手段が前記有効状態のままである場合、前記 I / O バッファは保護するための前記手段を前記有効状態から前記無効状態へ遷移させる電流の流れを生成する、請求項 2 9 に記載のマルチチップモジュール。40

**【発明の詳細な説明】**

**【技術分野】**

**【0 0 0 1】**

様々な特徴は、集積回路 ( I C ) に関し、より詳細には、スタック型マルチチップ集積回路の静電保護に関する。

**【背景技術】**

**【0 0 0 2】**

10

20

30

40

50

携帯電話およびラップトップコンピュータなどの、より小さく、より軽く、より高速のポータブル電子デバイスを求める、常に増大する需要によって、電子産業は、より大きい容量、より高い性能、およびより小さい寸法を有する回路構成要素を作り出すように助長されてきた。たとえば、現在、ポータブルデバイスは、垂直にスタッキングされ、集積回路（I C）パッケージの同じ成形コンパウンド内に収容された2つ以上の半導体ダイを有するI Cパッケージを含み得る。そのようなマルチチップI Cパッケージは、一般に、「チップスタックマルチチップモジュール」（M C M）と呼ばれる場合がある。「シリコン貫通スタッキング」（T S S）と呼ばれる1つの技法によると、垂直にスタッキングされた複数の半導体ダイは、基板貫通ビア（T S V）を使用して互いに電気的に結合される。T S Vは、一方の端部がダイ基板の裏側表面で露出され、他方の反対端部がダイのアクティブ表面（active surface）に電気的に結合されるように、ダイ基板の厚さを垂直に貫通する、典型的には金属から作製された電気導体である。10

#### 【0003】

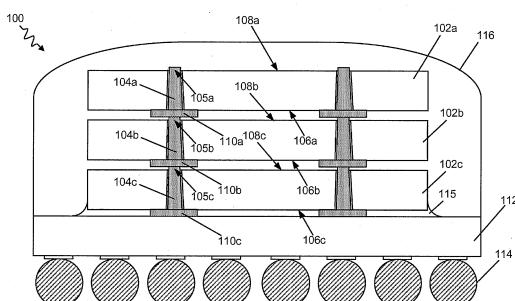

図1は、従来技術で見られるT S S M C M 1 0 0 の側面断面概略図を示す。M C M 1 0 0 は、T S V 1 0 4 a、1 0 4 b、1 0 4 cを使用して互いに電気的に結合された複数の半導体ダイ1 0 2 a、1 0 2 b、1 0 2 cを含む。上部ダイ1 0 2 aは、複数の集積回路構成要素（たとえば、トランジスタ、キャパシタ、インダクタ、抵抗器など）を含むアクティブ表面1 0 6 aと、裏側表面1 0 8 aとを有する。T S V 1 0 4 aは、アクティブ表面1 0 6 aに電気的に結合され、ダイ1 0 2 aの基板の厚さを貫通する。同様に、中間部および下部のダイ1 0 2 b、1 0 2 cは各々、アクティブ表面1 0 6 b、1 0 6 cおよび裏側表面1 0 8 b、1 0 8 cを有する。中間部ダイのT S V 1 0 4 bは、中間部ダイのアクティブ表面1 0 6 bに電気的に結合され、下部ダイのT S V 1 0 4 cは、下部ダイのアクティブ表面1 0 6 cに電気的に結合される。20

#### 【0004】

T S V 1 0 4 a、1 0 4 b、1 0 4 cは、一方の端部にコンタクトパッド1 1 0 a、1 1 0 b、1 1 0 cを有し、反対の端部にコンタクトパッド受容部1 0 5 a、1 0 5 b、1 0 5 cを有する。各ダイのアクティブ表面1 0 6 a、1 0 6 b、1 0 6 cは、そのそれぞれのT S V 1 0 4 a、1 0 4 b、1 0 4 cに電気的に結合され得る。コンタクトパッド1 1 0 a、1 1 0 b、1 1 0 cは、ダイの前側アクティブ表面1 0 6 a、1 0 6 b、1 0 6 cに露出され、コンタクトパッド受容部1 0 5 a、1 0 5 b、1 0 5 cは、ダイの裏側表面1 0 8 a、1 0 8 b、1 0 8 cに露出される。コンタクトパッド1 1 0 a、1 1 0 b、1 1 0 cは、金属「マイクロバンプ」であり、コンタクトパッド受容部1 0 5 a、1 0 5 b、1 0 5 cは、マイクロバンプ1 1 0 a、1 1 0 b、1 1 0 cを受容し、それらに嵌合するための対応する湾曲部を有する、ダイ上の金属凹部であり得る。30

#### 【0005】

上部ダイのコンタクトパッド1 1 0 aは、中間部ダイのコンタクトパッド受容部1 0 5 bに物理的かつ電気的に結合され、中間部ダイのコンタクトパッド1 1 0 bは、下部ダイのコンタクトパッド受容部1 0 5 cに物理的かつ電気的に結合される。このようにして、ダイのアクティブ表面1 0 6 a、1 0 6 b、1 0 6 cは、ビア1 0 4 a、1 0 4 b、1 0 4 cを介して互いに電気的に結合される。40

#### 【0006】

下部ダイ1 0 2 cは、アンダーフィルおよび／またはエポキシ1 1 5 により、フリップチップ形式でパッケージ基板1 1 2（たとえば、積層基板、銅ベースの基板などの金属ベースの基板など）に物理的かつ電気的に結合される。パッケージ基板1 1 2は、間に複数の相互接続部（図示せず）を有する多重レイヤを含み得る。相互接続部は、次に、M C M 1 0 0 がプリント回路基板（図示せず）に電気的に結合するために使用するボールグリッドアレイ（B G A）を形成する複数のはんだボール1 1 4に電気的に結合され得る。ダイ1 0 2 a、1 0 2 b、1 0 2 cと、T S V 1 0 4 a、1 0 4 b、1 0 4 cと、基板1 1 2の少なくとも一部とを含むM C M 1 0 0 の構成要素は、成形コンパウンド1 1 6に収容され得る。50

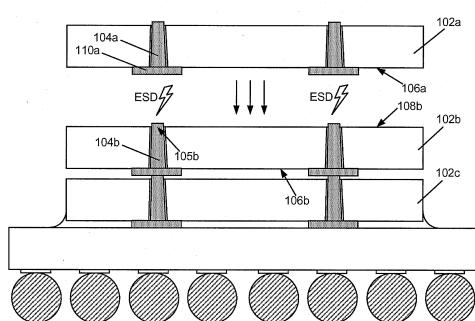

### 【0007】

図2は、MCM100の製造中に上部ダイ102aを中間部ダイ102bに電気的かつ物理的に結合するプロセスを示す。図示の例では、成形コンパウンド116(図1参照)は、上部ダイ102aが中間部ダイ102b上にどのように配置されているかを示すために除かれている(図2の方向を示す3つの矢印は、上部ダイ102aの中間部ダイ102bに向かう動きを示す)。このプロセス中、上部ダイ102aは、中間部ダイ102bに近づくように動かされ、上部ダイ102aのコンタクトパッド110aが中間部ダイ102bのコンタクトパッド受容部105bに嵌合するように上にスタッキングされる。しかしながら、場合によっては、上部ダイ102aは、中間部ダイ102bとは大幅に異なる(たとえば、かなり大きいか、またはかなり小さい)静電電位を有する可能性があり、接地され得る。2つのダイ102a、102bが十分近づく(たとえば、接触する)とき、静電放電(ESD)事象(すなわち、静電気)がトリガされ得、その結果、比較的大量の電流が中間部ダイ102bのTSV104bを瞬間に貫流する。適切なESD保護回路が無い場合、TSV104bに電気的に結合される、中間部ダイのアクティブ表面106b上に配置された(バッファ回路トランジスタなどの)高感度のIC構成要素が、ESD事象によりダメージを受ける場合がある。場合によっては、上部ダイ102aのアクティブ表面106a上に配置された回路もダメージを受ける可能性がある。同様に、中間部ダイ102bが下部ダイ102cに電気的かつ物理的に結合されているときの下部ダイ102cを含めて、MCM100内の他のダイも、そのようなESD障害を受けやすい。

### 【0008】

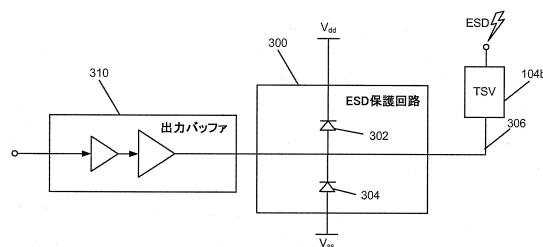

図3は、ESD障害から中間部ダイ102bの回路310を保護するために中間部ダイのTSV104bに結合され得る、従来技術で見られるESD保護回路300の概略図を示す。ESD保護回路300は、たとえば、出力信号バッファであり得る、高感度回路310から離れる方向にESD電流をバイパスする分流器を形成するダイオード302、304を採用する。

### 【0009】

ESD保護回路300は、ESD障害から出力信号バッファ310を保護する際に有効であり得るが、著しい欠点を有する。たとえば、ダイオード302、304は、大きいESD電流の流れを調整するのに必要とされる、比較的大きいサイズに起因する大きいシリコン/ダイ面積を占める可能性がある。さらに、ダイオード302、304は、寄生容量および/またはインダクタンスを含む、TSV104bの出力ノード306における寄生効果を作り出す。これらの寄生効果を補償するために、バッファ310のサイズは、出力ノード306における出力信号を十分に駆動することができるよう、より大きくする必要がある場合がある。より大きいバッファ310は、より多くの電力を消費し、また、より大きいアクティブシリコン/ダイ面積を占める。したがって、ESD保護回路300専用のシリコン/ダイ面積は、通常ならば他のIC構成要素に使用され得るアクティブ表面面積を、直接的(たとえば、ダイオード302、304構成要素面積)にかつ間接的(たとえば、より大きいバッファ310)に使用する。

### 【発明の概要】

#### 【発明が解決しようとする課題】

### 【0010】

このように、上述のサイズおよび電力消費量の問題に見舞われることなく、MCMのダイを十分に保護する高度なESD保護回路が必要になる。

### 【課題を解決するための手段】

### 【0011】

1つの特徴は、第1の集積回路(IC)ダイと、基板貫通ビア(TSV)によって第1のICダイに電気的に結合された入力/出力(I/O)ノードを有する第2のICダイと、I/Oノードに電気的に結合された第2のICダイのアクティブ表面上のヒューズであって、静電放電(ESD)によって生じるダメージから第2のICダイを保護するように構成されるヒューズとを含むマルチチップモジュールを提供する。一態様によれば、ヒュ

10

20

30

40

50

ーズは、第1のICダイを第2のICダイに電気的に結合することに応答して起こるESDによって生じるダメージから第2のICダイを保護するように構成される。別の態様によれば、ヒューズは、I/Oノードに結合された第1の端子と、グランドに結合された第2の端子とを含む。さらに別の態様によれば、ヒューズは、閉状態である場合、I/Oノードからグランドへの短絡回路バスを提供し、開状態である場合、I/Oノードをグランドから電気的に切断する。

#### 【0012】

一態様によれば、マルチチップモジュールは、I/Oノードに電気的に結合された増幅器入力端子および／または増幅器出力端子のうちの少なくとも1つを有する増幅器回路をさらに含む。ヒューズは、ESDによって生じるダメージから増幅器回路を保護するように構成され得る。一態様によれば、増幅器回路は、ヒューズを閉状態から開状態に遷移させるヒューズ破断電流を生成する。別の態様によれば、ヒューズは、50マイクロ秒(μs)～200μs続く1ミリアンペア(mA)～100mAのパラメータ、10μs～200μs続く10mA～100mAのパラメータ、または10μs～200μs続く10mA～100mAのパラメータを有するヒューズ破断電流に応答して閉状態から開状態に遷移する。一態様によれば、ヒューズ破断回路はI/Oノードに電気的に結合され、ヒューズを閉状態から開状態に遷移させるヒューズ破断電流を生成する。別の態様によれば、ヒューズは、ESDによって生成された、I/Oノードにおける電流サージに応答して閉状態のままであり、増幅器回路またはヒューズ破断回路によって生成されたヒューズ破断電流に応答して開状態に遷移する。

10

20

#### 【0013】

一態様によれば、ヒューズは、ダイオードが無いESD保護回路の一部である。別の態様によれば、ヒューズは、金属ヒューズまたはポリシリコンヒューズである。ヒューズは、開状態である場合、I/Oノードとグランドとの間に10メガオームよりも大きいかまたはそれに等しい抵抗値を提供することができる。一例によれば、マルチチップモジュールは、音楽プレーヤ、ビデオプレーヤ、娛樂ユニット、ナビゲーションデバイス、通信デバイス、モバイルフォン、スマートフォン、携帯情報端末、固定位置端末、タブレットコンピュータ、および／またはラップトップコンピュータのうちの少なくとも1つに組み込まれ得る。

30

#### 【0014】

別の特徴は、第1のICダイを提供するステップと、第2のICダイを提供するステップと、第1のICダイに第2のICダイのI/Oノードを電気的に結合する基板貫通ビア(TSV)を提供するステップと、第2のICダイのアクティプ表面上にヒューズを形成するステップと、ESDによって生じるダメージから第2のICダイを保護するように構成されるヒューズをI/Oノードに電気的に結合するステップとを含む、マルチチップモジュールを製造する方法を提供する。一態様によれば、本方法は、ヒューズの第1の端子をI/Oノードに結合するステップと、ヒューズの第2の端子をグランドに結合するステップとをさらに含む。別の態様によれば、本方法は、ヒューズを閉状態に維持することによってI/Oノードからグランドへの短絡回路バスを提供するステップをさらに含む。さらに別の態様によれば、本方法は、ヒューズを閉状態から開状態に遷移させることによってI/Oノードをグランドから電気的に切断するステップをさらに含む。さらに別の態様によれば、本方法は、I/Oノードに増幅器回路の増幅器出力端子および／または増幅器入力端子のうちの少なくとも1つを電気的に結合するステップをさらに含む。さらに別の態様によれば、本方法は、増幅器回路において、ヒューズを閉状態から開状態に遷移させるヒューズ破断電流を生成するステップをさらに含む。さらに別の態様によれば、本方法は、ESDによって生成された、I/Oノードにおける電流サージに応答してヒューズを閉状態に維持するステップと、増幅器回路またはヒューズ破断回路によって生成されたヒューズ破断電流に応答してヒューズを開状態に遷移させるステップとをさらに含む。

40

#### 【0015】

別の特徴は、第1のICダイと、I/Oノードを有する第2のICダイと、第1のIC

50

ダイに第2のICダイのI/Oノードを電気的に結合するための手段と、第2のICダイのアクティブ表面上に配置された、静電放電(ESD)によって生じるダメージから第2のICダイを保護するための手段とを含む、マルチチップモジュールを提供する。一態様によれば、第2のICダイを保護するための手段は、第1のICダイを第2のICダイに電気的に結合することに応答して起こるESDによって生じるダメージから第2のICダイを保護するように構成される。別の態様によれば、第2のICダイを保護するための手段は、I/Oノードに結合された第1の端子と、グランドに結合された第2の端子とを有するヒューズである。さらに別の態様によれば、ヒューズは、ESDによって生成された、I/Oノードにおける電流サージに応答して閉状態のままであり、増幅器回路またはヒューズ破断回路によって生成されたヒューズ破断電流に応答して開状態に遷移する。さらに別の態様によれば、ヒューズは、ESDによって生じるダメージからESD高感度回路を保護するように構成される。ESD高感度回路は、ヒューズを閉状態から開状態に遷移させるヒューズ破断電流を生成し得る。10

**【図面の簡単な説明】**

**【0016】**

【図1】従来技術で見られるシリコン貫通スタッキング(TSS)マルチチップモジュール(MCM)の側面断面概略図である。

【図2】従来技術で見られる、MCMの製造中に上部ダイを中間部ダイに電気的かつ物理的に結合するプロセスを示す図である。

【図3】ESD障害から中間部ダイの回路を保護するために中間部ダイの基板貫通ビア(TSV)に結合され得る、従来技術で見られる静電放電(ESD)保護回路の概略図である。20

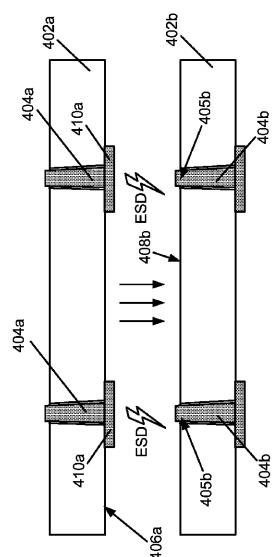

【図4】ESD保護回路を採用するスタック型MCMの側面断面概略図である。

【図5】MCMの製造中に第1のダイを第2のダイに(方向を示す矢印参照)電気的かつ物理的に結合するプロセスを示す図である。

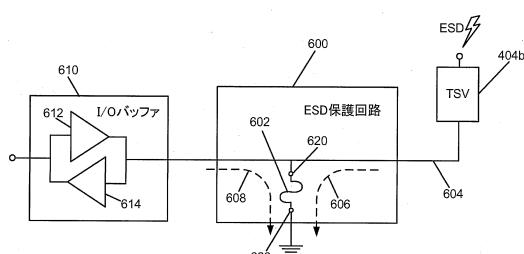

【図6】MCMのダイをESD障害から保護するESD保護回路の概略図である。

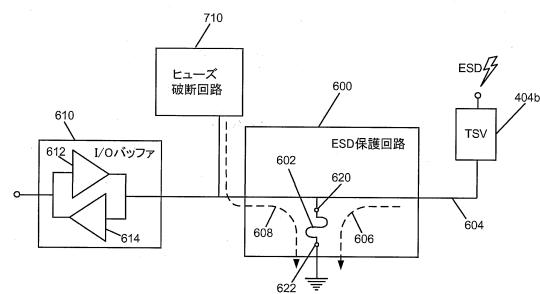

【図7】ヒューズ破断回路にも電気的に結合されたESD保護回路の概略図である。

【図8】様々な時間期間の間に様々な量の電流の流れがあると仮定して、ヒューズを開状態から開状態に遷移させることに関連付けられた特性を有するヒューズの表である。

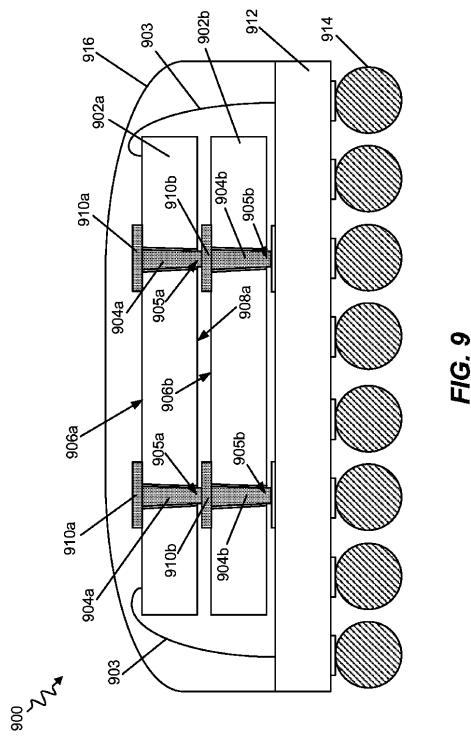

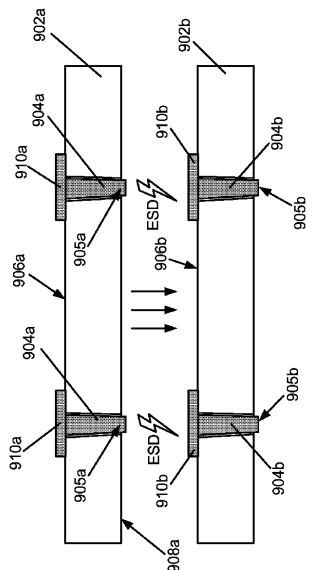

【図9】第1のダイがパッケージ基板にワイヤボンディングされ、第2のダイがフリップチップ形式でパッケージ基板に結合されない、2つのダイを含むMCMを示す図である。30

【図10】MCMの製造中に第1のダイを第2のダイに電気的かつ物理的に結合するプロセスを示す図である。

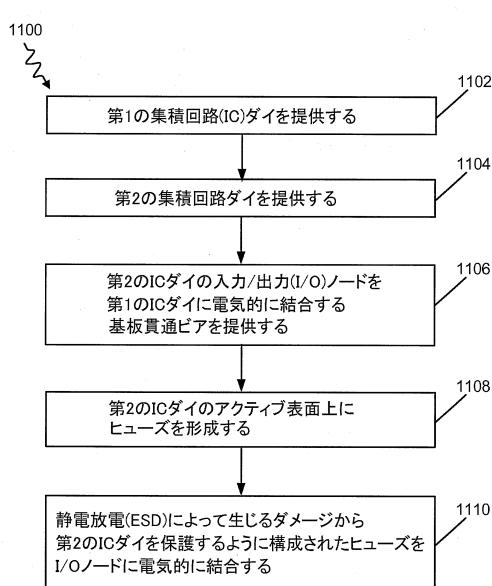

【図11】マルチチップモジュールを製造する方法のフローチャートである。

【図12】MCMと統合され得る様々な電子デバイスを示す図である。

**【発明を実施するための形態】**

**【0017】**

以下の説明では、本開示の様々な態様の完全な理解を提供するために具体的な詳細が与えられる。ただし、態様はこれらの具体的な詳細なしに実施され得ることを当業者は理解されよう。たとえば、態様が不要な詳細で不明瞭になるのを避けるために、回路をブロック図で示すことがある。他の場合には、本開示の態様を不明瞭にしないように、よく知られている回路、構造および技法を詳細に示さないことがある。40

**【0018】**

「例示的な」という言葉は、「例、事例、または例示として機能すること」を意味するように本明細書で使用される。「例示的」として本明細書で説明するいかなる実装形態または態様も、必ずしも本開示の他の態様よりも好ましいまたは有利なものと解釈すべきではない。同様に、「態様」という用語は、本開示のすべての態様が、論じられた特徴、利点または動作モードを含むことを必要とするとは限らない。本明細書で使用する「電気的に結合された」という用語は、2つの物体間に起こる電流の流れを可能にする、2つの物体間の直接的または間接的な結合を指すために本明細書で使用される。たとえば、物体A50

が物体Bに物理的に接触し、物体Bが物体Cに物理的に接触する場合、物体AおよびCは、互いに直接物理的に接触していなくとも、物体Bが物体Aから物体Cまでおよび/または物体Cから物体Aまで電流の流れが生じることを可能にする導体であれば、互いに電気的に結合されているとさらに見なすことができる。本明細書で使用する「入力/出力ノード」および「I/Oノード」という用語は、回路および/またはダイの入力回路端子および/または出力回路端子を指す。このように、I/Oノードは、出力端子もしくは入力端子のいずれかとして、または回路および/またはダイの入力端子と出力端子の両方として機能し得る。本明細書で使用する「ビア」という用語は、物理的な電子回路内の導体の異なるレイヤ間の垂直な電気接続部であり、MCM内の異なるICダイ間の垂直な電気接続部でもあり得る「垂直相互接続アクセス部」である。

10

### 【0019】

#### 概要

ESD事象からマルチチップモジュール(MCM)ダイ上のESD高感度回路を保護するための方法および装置が提供される。たとえば、1つの特徴は、第1のICダイおよび第2のICダイを含むマルチチップモジュールに関する。第2のICダイは、基板貫通ビアによって第1のICダイに電気的に結合されたI/Oノードを有する。第2のダイのアクティブ表面は、I/Oノードに電気的に結合され、ESD事象によって生じるダメージから第2のICダイを保護するように構成されたヒューズも含む。詳細には、ヒューズは、マルチチップモジュールの製造中に第1のダイを第2のダイに電気的に結合する結果として生成され得るESD事象から第2のICダイを保護する。第1のダイを第2のダイに結合すると、ヒューズは、ESDによって生成されたESD電流をグランドにバイパスすることができる。マルチチップモジュールのパッケージングが完了した後、ヒューズを破断させて開放することができる。

20

### 【0020】

本明細書で説明するヒューズを有するESD保護回路を利用することは、特に、従来技術の解決策と比較してESD保護回路がESDからダイを保護するのに必要なアクティブ表面面積を大幅に低減させ得るので、有利である。たとえば、ヒューズは、従来技術のESD保護回路に関連するダイオードよりも小さい、ダイ上のアクティブ表面面積を占め得る。さらに、本明細書で説明するESD保護回路を代わりに使用することによって大きいダイオードベースのESD保護回路の必要性をなくすことは、アクティブ表面面積をさらに節約することができるが、それは、新規のESD保護回路に結合された、I/Oノードを駆動するのに使用されるか、またはI/Oノードによって駆動される任意の入力バッファ回路および/または出力バッファ回路自体がより小さく設計され得るからである。たとえば、ダイオードよりも小さい面積を占めるヒューズは、I/Oノードにおける寄生効果を低減させることができ、次に、より小さいI/Oバッファ回路がI/Oノードを駆動することを可能にする。

30

### 【0021】

#### ESD保護回路

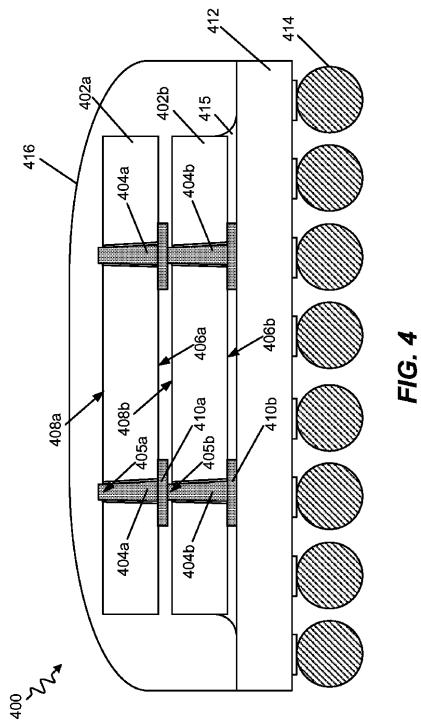

図4は、本開示の一態様による、ESD保護回路を採用するスタック型マルチチップモジュール(MCM)400の側面断面概略図を示す。MCM400は、1つまたは複数の導電性のTSV404a、404bを使用して両方が互いに電気的に結合された、第1の半導体ダイ402aおよび第2の半導体ダイ402bを含む。第1のダイ402aは、複数の集積回路構成要素(たとえば、トランジスタ、キャパシタ、インダクタ、抵抗器など)を含むアクティブ表面406aと、裏側表面408aとを有する。TSV404aは、第1のダイのアクティブ表面406aに電気的に結合され、第1のダイ402aの厚さ(たとえば、第1のダイ402aの基板の厚さ)を貫通する。同様に、第2の半導体ダイ402bは、アクティブ表面406bおよび裏側表面408bを有する。第2のダイのTSV404bは、第2のダイのアクティブ表面406bに電気的に結合され、第2のダイ402bの基板の厚さを貫通する。たとえば、第1のダイのTSV404aは、第1のダイ402aに関連付けられた入力/出力ノードに電気的に結合することができ、第2のダイ

40

50

の T S V 4 0 4 b は、第 2 のダイ 4 0 2 b に関連付けられた入力 / 出力ノードに電気的に結合することができる。これらの入力 / 出力ノードは、ダイ 4 0 2 a、4 0 2 b の入力端子および / または出力端子として機能する。

#### 【 0 0 2 2 】

T S V 4 0 4 a、4 0 4 b は、一方の端部にコンタクトパッド 4 1 0 a、4 1 0 b を有し、反対の端部にコンタクトパッド受容部 4 0 5 a、4 0 5 b を有する。各ダイのアクティブ表面 4 0 6 a、4 0 6 b は、そのそれぞれの T S V 4 0 4 a、4 0 4 b に電気的に結合され得る。コンタクトパッド 4 1 0 a、4 1 0 b は、ダイの前側アクティブ表面 4 0 6 a、4 0 6 b に露出され、コンタクトパッド受容部 4 0 5 a、4 0 5 b は、ダイの裏側表面 4 0 8 a、4 0 8 b に露出される。一態様では、コンタクトパッド 4 1 0 a、4 1 0 b は、金属「マイクロバンプ」であり得、コンタクトパッド受容部 4 0 5 a、4 0 5 b は、マイクロバンプを受容し、それらに嵌合するための対応する湾曲部を有する、ダイ上の金属凹部であり得る。しかしながら、概して、コンタクトパッド 4 1 0 a、4 1 0 b および対応するコンタクトパッド受容部 4 0 5 a、4 0 5 b は、互いに嵌合し、互いにダイ 4 0 2 a、4 0 2 b に電気的に結合するように構成された電気導体である。10

#### 【 0 0 2 3 】

第 1 のダイのコンタクトパッド 4 1 0 a は、第 2 のダイのコンタクトパッド受容部 4 0 5 b に物理的かつ電気的に結合される。このようにして、ダイのアクティブ表面 4 0 6 a、4 0 6 b は、T S V 4 0 4 a、4 0 4 b を介して互いに電気的に結合される。20

#### 【 0 0 2 4 】

第 2 のダイ 4 0 2 b は、アンダーフィルおよび / またはエポキシ 4 1 5 により、フリップチップ形式でパッケージ基板 4 1 2 (たとえば、積層基板、銅ベースの基板などの金属ベースの基板など) に物理的かつ電気的に結合される。パッケージ基板 4 1 2 は、間に複数の相互接続部 (図示せず) を有する多重レイヤを含み得る。相互接続部は、次に、M C M 4 0 0 をプリント回路基板 (図示せず) に電気的に結合するために使用されるボールグリッドアレイ (B G A) を形成する複数のはんだボール 4 1 4 に電気的に結合され得る。ダイ 4 0 2 a、4 0 2 b と、T S V 4 0 4 a、4 0 4 b と、基板 4 1 2 の少なくとも一部とを含む M C M 4 0 0 の構成要素は、成形コンパウンド 4 1 6 に収容され得る。図示された M C M 4 0 0 は 2 つのダイ 4 0 2 a、4 0 2 b を有するが、M C M 4 0 0 は、第 1 および第 2 のダイ 4 0 2 a、4 0 2 b に関して上述したものと同様のコンタクトパッドおよびコンタクトパッド受容部を有する T S V を使用して互いの上にスタッキングされ互いに電気的に結合される、2 つに等しいかまたはそれよりも大きい任意の数のダイを有し得る。30

#### 【 0 0 2 5 】

図 5 は、M C M 4 0 0 の製造中に第 1 のダイ 4 0 2 a を第 2 のダイ 4 0 2 b に (方向を示す矢印参照) 電気的かつ物理的に結合するプロセスを示す。(パッケージ基板 4 1 2、はんだボール 4 1 4、および成形コンパウンド 4 1 6 は、明快のために省略された。) このプロセス中、第 1 のダイ 4 0 2 a は、第 2 のダイ 4 0 2 b により近づくように動かされ、第 1 のダイ 4 0 2 a のコンタクトパッド 4 1 0 a が第 2 のダイ 4 0 2 b のコンタクトパッド受容部 4 0 5 b に物理的かつ電気的に結合するように上にスタッキングされる。場合によっては、第 1 のダイ 4 0 2 a は、第 2 のダイ 4 0 2 b とは大幅に異なる (たとえば、かなり大きいか、またはかなり小さい) 静電電位を有する可能性があり、接地され得る。2 つのダイ 4 0 2 a、4 0 2 b が十分近づく (たとえば、接触する) とき、静電放電 (E S D) 事象 (たとえば、静電気) が生じる可能性があり、比較的大量の電流が第 2 のダイ 4 0 2 b の T S V 4 0 4 b を瞬間的に貫流する。後述のように、E S D 保護回路は、第 2 のダイ 4 0 2 b の入力 / 出力ノードにおける高感度回路を E S D 事象から保護するために T S V 4 0 4 b に電気的に結合される。40

#### 【 0 0 2 6 】

図 6 は、本開示の一態様による、M C M のダイを E S D 障害から保護する E S D 保護回路 6 0 0 の概略図を示す。図 4 ~ 図 6 を参照すると、E S D 回路 6 0 0 は、第 2 のダイの T S V 4 0 4 b のうちの 1 つに電気的に結合される。第 2 のダイ 4 0 2 b の各 T S V 4 050

4 b は、第 2 のダイ 4 0 2 b に関連付けられた 1 つまたは複数の入力 / 出力 (I / O) ノード 6 0 4 に電気的に結合され得る。各 I / O ノード 6 0 4 は、ダイ 4 0 2 b の入力端子および / または出力端子として機能する。I / O ノード 6 0 4 は、E S D 回路 6 0 0 に電気的に結合され、I / O 信号バッファ回路 6 1 0 (本明細書では「増幅器回路」とも呼ぶ) にも電気的に結合され得る。

#### 【0027】

I / O 信号バッファ回路 6 1 0 は、出力信号を処理 (たとえば、増幅) し、出力信号を I / O ノード 6 0 4 に提供することができる 1 つまたは複数の出力増幅器 6 1 2 を含み得る。次いで、これらの出力信号は、第 1 のダイ 4 0 2 a の入力ノードを含む、M C M 4 0 0 内の他の点に提供され得る。代替的に、または追加として、I / O 信号バッファ回路 6 1 0 は、I / O ノード 6 0 4 から入力信号を受け取る 1 つまたは複数の入力増幅器 6 1 4 を含み得る。次いで、これらの入力信号は、処理 (たとえば、増幅) され、I / O 信号バッファ回路 6 1 0 によって第 2 のダイ 4 0 2 b の他の回路構成要素に提供され得る。このように、増幅器回路 6 1 0 は、I / O ノード 6 0 4 に電気的に結合された増幅器入力端子および / または増幅器出力端子のうちの少なくとも 1 つを有し得る。

#### 【0028】

使用される増幅器 6 1 2、6 1 4 の特有の構造は、M C M 4 0 0 の用途に依存しており、当業者によって選択され得る。しかしながら、I / O バッファ回路 6 1 0 の特有の構造にもかかわらず、回路 6 1 0 は、限定はしないが、入力増幅器および / または出力増幅器 6 1 2、6 1 4 などの、I / O ノード 6 0 4 において E S D 事象によって容易にダメージを受け得る高感度の回路構成要素を含み得る。さらに、I / O バッファ回路 6 1 0 に加えて、またはその代わりに、他の E S D 高感度回路は、同様に E S D 障害を受けやすい I / O ノード 6 0 4 に電気的に結合され得る。E S D 事象は、図 5 に関して上記で説明したプロセスによって生じ得る。すなわち、別の半導体ダイ (たとえば、第 1 のダイ 4 0 2 a) を第 2 のダイ 4 0 2 b に電気的に結合することにより、T S V 4 0 4 b を介して I / O ノード 6 0 4 において E S D 事象が生じ得る。

#### 【0029】

E S D 保護回路 6 0 0 は、ヒューズ 6 0 2 を含む。ヒューズは、通常、「閉状態」(本明細書では「破断していない状態」および「短絡回路状態」と呼ぶこともある) で動作しているとき、理想的にはゼロ抵抗値を有し、端子間で短絡回路のように機能する二端子要素である。対照的に、ヒューズは、「開状態」(本明細書では「破断状態」および「開回路状態」と呼ぶもある) で動作しているとき、理想的には無限の抵抗値を有し、端子間で開回路のように機能する。ヒューズは、所定の時間期間の間に所定の量よりも多い電荷がその 2 つの端子を通過するとき、閉状態から開状態に遷移する (すなわち、ヒューズが破断されて開放される)。たとえば、ヒューズは、20 ミリ秒を超える間に 1 アンペアを超える電流がヒューズを通過する場合、閉状態から開状態に遷移するように設計され得る。

#### 【0030】

図 6 に示すヒューズ 6 0 2 は、第 2 のダイ 4 0 2 b のアクティブ表面 4 0 6 b 上に形成された集積回路構成要素である。ヒューズ 6 0 2 の第 1 の端子 6 2 0 は、I / O ノード 6 0 4 に結合されているが、ヒューズ 6 0 2 の第 2 の端子 6 2 2 は、グランドに結合されている。ヒューズ 6 0 2 は、その初期状態では、閉短絡回路状態であり、その結果、I / O ノード 6 0 4 とグランドとの間に低抵抗短絡回路バスが存在する。次いで、サージ電流 (方向を示す曲がった破線の矢印 6 0 6 で示す) が T S V 4 0 4 b および I / O ノード 6 0 4 を通過するように、第 1 のダイ 4 0 2 a を第 2 のダイ 4 0 2 b に電気的に結合して、E S D 事象がトリガされる場合、ヒューズ 6 0 2 は、E S D 電流 6 0 6 のサージがグランドに直接行き、それによって、I / O ノード 6 0 4 に電気的に結合された、I / O バッファ回路 6 1 0 および / または他の高感度回路をバイパスすることを可能にする。このように、ヒューズ 6 0 2 の閉状態 (すなわち、短絡回路状態) は、第 1 のダイ 4 0 2 a が第 2 のダイ 4 0 2 b に電気的に結合される場合に生じ得る E S D 障害から、I / O ノード 6 0 4

に電気的に結合された、I/Oバッファ回路610および/または他の高感度回路を保護する。

#### 【0031】

ヒューズ602は、銅、アルミニウム、金属合金、または他の金属材料などの金属ヒューズであり得る。ヒューズ602は、ポリシリコンヒューズ（すなわち、ポリヒューズ）であってもよい。当然、ヒューズ602は、これらの材料から構成されることに限定されず、ヒューズ602を構築するのに、他の材料またはそれらの組合せも使用し得る。本開示の一態様では、MCMの複数のダイ上の複数のTSVは各々、図6に示す方法で別のESD保護回路600に電気的に結合することができ、その結果、ダイの各I/Oノードは、MCMの製造中にESD障害から保護される。このESD障害は、限定はしないが、MCMの2つのダイを互いに電気的に結合することを含む製造ステップから生じ得るESD障害を含む。10

#### 【0032】

第1のダイ402aは、第2のダイ402bに電気的かつ物理的に結合されると、MCM400は、成形コンパウンド416によってカプセル化され得る。しかしながら、ヒューズ602は、閉状態のままである場合、不必要に、I/Oバッファ回路610の動作を変更する可能性がある。たとえば、そのような場合、I/Oノード604は、グランドに電気的に結合されたままであり、したがって、提供される出力信号および/またはI/Oバッファ回路610によって受け取られる入力信号にかかわらず、I/Oノード604における信号レベルは、グランドである。それゆえ、MCM400の通常動作が開始し得る前に、ヒューズ602は、「ヒューズ破断状態」を経るべきであり、ヒューズ602は、ESD事象自体によって未だ破断されて開放されていない場合、故意に破断されて開放される。一態様によると、MCM400がヒューズ破断状態に入るとき、I/Oバッファ回路610は、ヒューズ602を破断させるのに十分大きく十分長く維持された、ヒューズ602を通る電流の流れ（方向を示す曲がった破線の矢印608で示す）を生成する。ヒューズ602が破断されて開回路状態になると、MCM400の通常動作（すなわち、I/Oバッファ回路610は、I/Oノード604において出力信号を提供し、および/または入力信号を受け取ることができる）が開始することができるが、それは、I/Oノード604がこれ以上グランドに電気的に結合されないからである。20

#### 【0033】

図7は、本開示の一態様による、ヒューズ破断回路710にも電気的に結合されたESD保護回路600の概略図を示す。ヒューズ破断回路710は、ヒューズ破断電流608を生成するように構成された増幅器回路（たとえば、トランジスタ）を含み得る。図示の例では、ヒューズ破断回路710は、I/Oバッファ回路610とは別の回路として示される。したがって、図6のI/Oバッファ回路610は、I/Oノード604用の出力信号発生器、およびさらにヒューズ602を破断させるのに十分な電流608を生成するように構成されたヒューズ破断回路を兼ねる可能性があるが、図7のヒューズ破断回路710は、バッファ610とは別の異なる回路であり得る。30

#### 【0034】

本開示の一態様によれば、ヒューズ602は、典型的なESD事象（たとえば、第1のダイ402aを第2のダイ402bに電気的に結合する）によって生成される電流606がヒューズ602を破断させないように設計および選択されるが、ヒューズ602は、バッファ回路および/またはヒューズ破断回路710によって生成されたヒューズ破断電流608に応答して破断する。典型的には、ESD事象は、極めて短い持続時間の間に比較的高い電流レベルを生成し、ヒューズ602を破断させるのに必要なしきい値未満の総電荷流（total charge flow）をもたらし得る。対照的に、バッファ回路610および/またはヒューズ破断回路710によって生成されたヒューズ破断電流608は、比較的長い時間期間の間、維持される比較的適度な電流の流れである可能性があり、ヒューズ602を破断させるのに十分な総電荷流をもたらす。たとえば、ヒューズ破断電流608によって生成された総電荷流は、ESD事象によって生成された総電荷流より4050

も大きい桁数であり得る。

#### 【0035】

図8は、様々な時間期間の間に様々な量の電流の流れがあると仮定して、ヒューズ602を閉状態から開状態に遷移させることに関連付けられた特性を有するヒューズの表800を示す。図6および図7に示すヒューズ602は、表800に示すヒューズA、B、C、D、E、F、G、H、およびIの特性のうちのいずれか1つを有し得る。図8を参照すると、ヒューズAは、1ピコ秒(p s)～10ナノ秒(n s)続く1マイクロアンペア(μ A)～1アンペア(A)の範囲にあるESD事象電流に応答して閉じたままである可能性がある。これらの値は、ヒューズAを貫流する1アトクーロン(a C)～10ナノクーロン(n C)の範囲の総電荷量をもたらす。対称的に、ヒューズAは、50マイクロ秒(μ s)～10ミリ秒(m s)続く1ミリアンペア(m A)～500mAの範囲にある、I/Oバッファ回路610および/またはヒューズ破断回路710によって生成されたヒューズ破断電流に応答して、破断して開放する(すなわち、開状態に遷移する)ことができる。これらの値は、ヒューズAを貫流する50nC～5ミリクーロン(m C)の範囲の総電荷量をもたらす。ヒューズBおよびCも、1 p s ~ 10 n s 続く 1 μ A ~ 1 A の範囲にある ESD 事象電流に応答して閉じたままである可能性があり、これらの値は、1 a C ~ 10 n C の範囲の総電荷流をもたらす。しかしながら、ヒューズBは、10 μ s ~ 10 m s 続く 5 mA ~ 500 mA の範囲にあるヒューズ破断電流に応答して破断して開放することができるが、ヒューズCは、5 μ s ~ 10 m s 続く 10 mA ~ 500 mA の範囲にあるヒューズ破断電流に応答して破断して開放することができる。これらの値は、ヒューズBおよびCを貫流する50nC～5mCの範囲の総電荷量をもたらす。

10

20

#### 【0036】

ヒューズD、E、およびFは、1 p s ~ 1 n s 続く 1 μ A ~ 10 A の範囲にある ESD 事象電流に応答して閉じたままであり、これらの値は、1 a C ~ 10 n C の範囲の総電荷流をもたらす。しかしながら、ヒューズD、E、およびFは、それぞれ、50 μ s ~ 10 m s 続く 1 mA ~ 500 mA の範囲、10 μ s ~ 10 m s 続く 5 mA ~ 500 mA の範囲、および 5 μ s ~ 10 m s 続く 10 mA ~ 500 mA の範囲にあるヒューズ破断電流に応答して破断して開放することができます。これらの値は、ヒューズD、E、およびFを貫流する50nC～5mCの範囲の総電荷量をもたらす。ヒューズG、H、およびIは、1 p s ~ 100 n s 続く 1 μ A ~ 0.1 A の範囲にある ESD 事象電流に応答して閉じたままであり、これらの値は、1 a C ~ 10 n C の範囲の総電荷流をもたらす。しかしながら、ヒューズG、H、およびIは、それぞれ、50 μ s ~ 10 m s 続く 1 mA ~ 500 mA の範囲、10 μ s ~ 10 m s 続く 5 mA ~ 500 mA の範囲、および 5 μ s ~ 10 m s 続く 10 mA ~ 500 mA の範囲にあるヒューズ破断電流に応答して破断して開放することができます。これらの値は、ヒューズG、H、およびIを貫流する50nC～5mCの範囲の総電荷量をもたらす。

30

#### 【0037】

上記に与えた例では、ヒューズ602は、ESD事象の間に破断して開放しない可能性があるが、I/Oバッファ回路610および/またはヒューズ破断回路710によって生成されたヒューズ破断電流が、ヒューズ602を閉状態から開状態に遷移させるのに十分な電流の流れの状態を生成した後、破断して開放することができる。このように、ヒューズ602は、MCM400の第1のダイ402aを第2のダイ402bに電気的に結合するときトリガされ得るESD事象などのESD事象の典型であり得る電流サージに耐えることができるよう設計され得る。

40

#### 【0038】

しかしながら、場合によっては、ESD電流サージ自体は、それでも、ESD事象の間にヒューズ602を破断させて開放することができる。この場合、MCM400は、依然としてESD事象から保護され、標準動作中に正常に機能することもできる。たとえば、ESD電流サージは、ヒューズ602を破断させて開放することができるが、十分な量の電流は、I/Oバッファ回路610などのESD高感度回路をすでにバイパスしている可

50

能性があり、その結果、これらの高感度回路は、依然として、E S D事象によって損傷されない。さらに、M C M 4 0 0の製造が完了した（すなわち、M C M 4 0 0が成形コンパウンド4 1 6によってカプセル化された、など）後、M C M 4 0 0は、M C M内の1つまたは複数のヒューズ6 0 2が開状態であるか、または閉状態であるかを確かめるためにテストされ得る。すなわち、M C M 4 0 0の製造が完了すると、I / Oノード6 0 4は、それらがグランドに短絡されている（すなわち、ヒューズ6 0 2が依然として閉状態である）かどうかを確かめるために直接的または間接的にテストされ得る。依然として閉状態であるこれらのヒューズ6 0 2は、上述のI / Oバッファ回路6 1 0および／またはヒューズ破断回路7 1 0を使用してヒューズ6 0 2を通してヒューズ破断電流を流すことによって開放にプログラムされる必要がある可能性がある。しかしながら、E S D事象自体によりすでに破断して開放したこれらのヒューズ6 0 2は、すでに開状態であるので、I / Oバッファ回路6 1 0および／またはヒューズ破断回路7 1 0を使用して開放にプログラムされる必要がない。ヒューズ6 0 2が開状態に遷移すると、E S D事象自体であろうが、またはヒューズ破断電流プログラミングであろうが、I / Oバッファ回路6 1 0は、正常に動作する（すなわち、出力信号を提供するか、またはI / Oノード6 0 4から入力信号を受け取る）ことができる。10

#### 【0039】

ヒューズ6 0 2は、破断されて開放された後、それに関連する、有限であるが、極めて高い抵抗値を有する。一様によれば、ヒューズ6 0 2は、その開状態では、I / Oノード6 0 4とグランドとの間に1メガオームに等しいかまたはそれよりも大きい抵抗値を作り出す。別の様によれば、ヒューズ6 0 2は、その開状態では、10メガオームに等しいかまたはそれよりも大きい抵抗値を作り出す。さらに別の実施形態では、抵抗値は、100メガオームに等しいかまたはそれよりも大きい。これらの有限の抵抗値は、少量の漏れ電流にヒューズ6 0 2を貫流させる。しかしながら、ダイ4 0 2 bの供給電圧に応じて、この漏れ電流は、比較的小さく、1nA～1μAの範囲にあり得る。20

#### 【0040】

本明細書で説明するヒューズ6 0 2を有するE S D保護回路6 0 0を利用することは、特に、（図3を参照して述べた）従来技術の解決策と比較してE S D保護回路がE S Dからダイ4 0 2 bを保護するのに必要なアクティブ表面面積を大幅に低減させ得るので、有利である。たとえば、ヒューズ6 0 2は、従来技術のE S D保護回路3 0 0に関連するダイオード3 0 2、3 0 4よりも小さい、ダイ6 0 2 b上のアクティブ表面面積を占め得る。さらに、大きいダイオード3 0 2、3 0 4ベースのE S D保護回路3 0 0の必要性をなくし、本明細書で説明するE S D保護回路6 0 0を代わりに使用することは、ダイ4 0 2 b上のアクティブ表面面積をさらに節約することができるが、それは、I / Oノード6 0 4に結合されたI / Oバッファ回路6 1 0自身がより小さく設計され得るからである。たとえば、ダイオード3 0 2、3 0 4よりも小さい面積を占めるヒューズ6 0 2は、I / Oノード6 0 4における寄生効果を低減させることができ、次に、より小さいI / Oバッファ回路6 1 0がI / Oノード6 0 4を駆動することを可能にする。30

#### 【0041】

上述のE S D保護回路6 0 0は、フリップチップ形式でパッケージ基板4 1 2にマウントされる4 0 2 bなどのダイを伴う使用（図4参照）に限定されない。加えて、E S D保護回路6 0 0は、そのようなフリップチップ形式でパッケージ基板に結合されないM C Mダイの回路構成要素を保護するために使用することができ、ダイのアクティブ表面は、パッケージ基板から離れた方向を向く。40

#### 【0042】

たとえば、図9は、第1のダイ9 0 2 aがパッケージ基板9 1 2にワイヤボンディング9 0 3され、第2のダイ9 0 2 bがフリップチップ形式でパッケージ基板9 1 2に結合されない、2つのダイ9 0 2 a、9 0 2 bを含むM C M 9 0 0を示す。第1のダイ9 0 2 aおよび第2のダイ9 0 2 bは、1つまたは複数の導電性のT S V 9 0 4 a、9 0 4 bを使用して両方が互いに電気的に結合される。第1のダイ9 0 2 aは、パッケージ基板9 1 250

から離れた方向を向く、複数の集積回路構成要素（たとえば、トランジスタ、キャパシタ、インダクタ、抵抗器など）を含むアクティブ表面 906a と、パッケージ基板 912 の方向を向く裏側表面 908a とを有する。TSV904a は、第1のダイのアクティブ表面 906a に電気的に結合され、第1のダイ 902a の基板の厚さを貫通する。同様に、第2の半導体ダイ 902b は、アクティブ表面 906b および裏側表面 908b を有する。第2のダイの TSV904b は、第2のダイのアクティブ表面 906b に電気的に結合され、第2のダイ 902b の基板の厚さを貫通する。たとえば、第1のダイの TSV904a は、第1のダイ 902a に関連付けられた入力／出力ノードに電気的に結合することができ、第2のダイの TSV904b は、第2のダイ 902b に関連付けられた入力／出力ノードに電気的に結合することができる。これらの入力／出力ノードは、ダイ 902a 10 、902b の入力端子および／または出力端子として機能する。

#### 【0043】

TSV904a、904b は、一方の端部にコンタクトパッド 910a、910b を有し、反対の端部にコンタクトパッド受容部 905a、905b を有する。各ダイのアクティブ表面 906a、906b は、そのそれぞれの TSV904a、904b に電気的に結合され得る。コンタクトパッド 910a、910b は、ダイの前側アクティブ表面 906a、906b に露出され、コンタクトパッド受容部 905a、905b は、ダイの裏側表面 908a、908b に露出される。

#### 【0044】

第1のダイのコンタクトパッド受容部 905a は、第2のダイのコンタクトパッド 910b に物理的かつ電気的に結合される。このようにして、ダイのアクティブ表面 906a、906b は、ビア 904a、904b を介して互いに電気的に結合される。第2のダイ 902b は、パッケージ基板 912 に物理的かつ電気的に結合される。たとえば、第2のダイ 902b は、ワイヤボンディング（図示せず）を使用して直接的に、および／またはパッケージ基板 912 にワイヤボンディング 903 される第1のダイ 902a を介して間接的にパッケージ基板 912 に電気的に結合され得る。パッケージ基板 912 は、間に複数の相互接続部（図示せず）を有する多重レイヤを含み得る。相互接続部は、次に、MCM900 をプリント回路基板（図示せず）に電気的に結合するために使用されるボールグリッドアレイ（BGA）を形成する複数のはんだボール 914 に電気的に結合され得る。ダイ 902a、902b と、TSV904a、904b と、基板 912 の少なくとも一部とを含む MCM900 の構成要素は、成形コンパウンド 916 に収容され得る。図示された MCM900 は 2つのダイ 902a、902b を有するが、MCM900 は、第1および第2のダイ 902a、902b に関して上述したものと同様のコンタクトパッドおよびコンタクトパッド受容部を有する TSV を使用して互いの上にスタッキングされ互いに電気的に結合される、2つに等しいかまたはそれよりも大きい任意の数のダイを有し得る。

#### 【0045】

図 10 は、MCM900 の製造中に第1のダイ 902a を第2のダイ 902b に（方向を示す矢印参照）電気的かつ物理的に結合するプロセスを示す。（ワイヤボンディング 903、パッケージ基板 912、はんだボール 914、および成形コンパウンド 916 は、明快のために省略された。）このプロセス中、第1のダイ 902a は、第2のダイ 902b により近づくように動かされ、第1のダイ 902a のコンタクトパッド受容部 905a が第2のダイ 902b のコンタクトパッド 910b に物理的かつ電気的に結合するように上にスタッキングされる。図 4 および図 5 に関して上記で説明した MCM400 と同様に、図 10 の第1のダイ 902a は、第2のダイ 902b とは大幅に異なる（たとえば、かなり大きいか、またはかなり小さい）静電電位を有する可能性があり、接地され得る。2つのダイ 902a、902b が十分近づく（たとえば、接触する）とき、ESD 事象が生じる可能性があり、比較的大量の電流が第2のダイ 902b の TSV904b を瞬間的に貫流する。

#### 【0046】

ESD 回路 600 は、その上に配置された高感度回路へのダメージを防ぐために第2の

10

20

30

40

50

ダイのアクティブ表面 906b に関連付けられた I/O ノードに結合され得る。したがって、ESD 回路 600、そのヒューズ 602 の動作モード、ならびに I/O バッファ回路および／またはヒューズ破断回路 710 を使用してヒューズ 602 を破断させる技法はすべて、図 6～図 8 に関して上記で説明したものと同じ方法で図 9 および図 10 に示す MCM900とともに使用され得る。

#### 【0047】

図 11 は、本開示の一態様による、マルチチップモジュールを製造する方法のフローチャート 1100 を示す。ステップ 1102 では、第 1 の集積回路 (IC) ダイが提供される。ステップ 1104 では、第 2 の集積回路ダイが提供される。一例では、第 1 および第 2 の IC ダイは、スタッキングされ得る。ステップ 1106 では、第 2 の IC ダイの入力／出力 (I/O) ノードを第 1 の IC ダイに電気的に結合する基板貫通ビア (TSV) が提供される。ステップ 1108 では、第 2 の IC ダイのアクティブ表面上にヒューズが形成される。ステップ 1110 では、ヒューズは、I/O ノードに電気的に結合され、静電放電 (ESD) によって生じるダメージから第 2 の IC ダイを保護するように構成される。

10

#### 【0048】

図 12 は、マルチチップモジュール (MCM) 1200 と統合され得る様々な電子デバイスを示す。MCM1200 は、図 4 および／または図 9 に関して上記で説明した MCM400 および／または MCM900 のうちのいずれか 1 つであり得る。たとえば、携帯電話 1202、ラップトップコンピュータ 1204、および固定位置端末 1206 は、MCM1200 を含み得る。図 12 に示すデバイス 1202、1204、1206 は、例にすぎない。他の電子デバイスは、限定しないが、ハンドヘルドパーソナル通信システム (PCS) ユニット、携帯情報端末などのポータブルデータユニット、GPS 対応デバイス、ナビゲーションデバイス、セットトップボックス、音楽プレーヤ、ビデオプレーヤ、娛樂ユニット、メタ読取り機器などの固定位置データユニット、またはデータもしくはコンピュータ命令の記憶もしくは取り出しを行う任意の他のデバイス、またはそれらの任意の組合せを含む MCM1200 を採用することもできる。

20

#### 【0049】

また、本開示の態様は、フローチャート、流れ図、構造図またはブロック図として示されるプロセスとして説明され得ることに留意されたい。フローチャートは動作を逐次プロセスとして説明し得るが、動作の多くは並行してまたは同時に実行され得る。加えて、動作の順序は並び替えられ得る。プロセスは、その動作が完了したときに終了する。プロセスは、方法、関数、手順、サブルーチン、サブプログラムなどに対応し得る。

30

#### 【0050】

本明細書で説明する本発明の様々な特徴は、本発明から逸脱することなく様々なシステムで実装され得る。上記の本開示の態様は例にすぎず、本発明を限定するものと解釈すべきではないことに留意されたい。本開示の態様の説明は、例示的なものであり、特許請求の範囲を限定するものではない。したがって、本教示は、他のタイプの装置、ならびに多くの代替形態、変更形態、および変形形態に容易に適用され得ることが当業者には明らかであろう。

40

#### 【符号の説明】

#### 【0051】

- 100 マルチチップモジュール (MCM)

- 102a 上部ダイ

- 102b 中間部ダイ

- 102c 下部ダイ

- 104a 基板貫通ビア (TSV)

- 104b 基板貫通ビア (TSV)

- 104c 基板貫通ビア (TSV)

- 105a コンタクトパッド受容部

10

20

30

40

50

|         |                       |    |

|---------|-----------------------|----|

| 1 0 5 b | コンタクトパッド受容部           |    |

| 1 0 5 c | コンタクトパッド受容部           |    |

| 1 0 6 a | アクティブ表面               |    |

| 1 0 6 b | アクティブ表面               |    |

| 1 0 6 c | アクティブ表面               |    |

| 1 0 8 a | 裏側表面                  |    |

| 1 0 8 b | 裏側表面                  |    |

| 1 0 8 c | 裏側表面                  |    |

| 1 1 0 a | コンタクトパッド              | 10 |

| 1 1 0 b | コンタクトパッド              |    |

| 1 1 0 c | コンタクトパッド              |    |

| 1 1 2   | パッケージ基板               |    |

| 1 1 4   | はんだボール                |    |

| 1 1 5   | アンダーフィルまたはエポキシ        |    |

| 1 1 6   | 成形コンパウンド              |    |

| 3 0 0   | E S D 保護回路            |    |

| 3 0 2   | ダイオード                 |    |

| 3 0 4   | ダイオード                 |    |

| 3 0 6   | 出力ノード                 |    |

| 3 1 0   | 出力バッファ                | 20 |

| 4 0 0   | マルチチップモジュール ( M C M ) |    |

| 4 0 2 a | 第 1 の半導体ダイ            |    |

| 4 0 2 b | 第 2 の半導体ダイ            |    |

| 4 0 4 a | 基板貫通ビア ( T S V )      |    |

| 4 0 4 b | 基板貫通ビア ( T S V )      |    |

| 4 0 5 a | コンタクトパッド受容部           |    |

| 4 0 5 b | コンタクトパッド受容部           |    |

| 4 0 6 a | アクティブ表面               |    |

| 4 0 6 b | アクティブ表面               |    |

| 4 0 8 a | 裏側表面                  | 30 |

| 4 0 8 b | 裏側表面                  |    |

| 4 1 0 a | コンタクトパッド              |    |

| 4 1 0 b | コンタクトパッド              |    |

| 4 1 2   | パッケージ基板               |    |

| 4 1 4   | はんだボール                |    |

| 4 1 5   | アンダーフィルまたはエポキシ        |    |

| 4 1 6   | 成形コンパウンド              |    |

| 6 0 0   | E S D 保護回路            |    |

| 6 0 2   | ヒューズ                  |    |

| 6 0 4   | 入力 / 出力 ( I / O ) ノード | 40 |

| 6 0 6   | E S D 電流              |    |

| 6 0 8   | ヒューズ破断電流              |    |

| 6 1 0   | I / O バッファ回路          |    |

| 6 1 2   | 出力増幅器                 |    |

| 6 1 4   | 入力増幅器                 |    |

| 6 2 0   | 第 1 の端子               |    |

| 6 2 2   | 第 2 の端子               |    |

| 7 1 0   | ヒューズ破断回路              |    |

| 9 0 0   | マルチチップモジュール ( M C M ) |    |

| 9 0 2 a | 第 1 のダイ               | 50 |

- 902b 第2のダイ

903 ワイヤボンディング

904a 基板貫通ビア (TSV)

904b 基板貫通ビア (TSV)

905a コンタクトパッド受容部

905b コンタクトパッド受容部

906a アクティブ表面

906b アクティブ表面

908a 裏側表面

908b 裏側表面

910a コンタクトパッド

910b コンタクトパッド

912 パッケージ基板

914 はんだボール

916 成形コンパウンド

1200 マルチチップモジュール (MCM)

1202 携帯電話

1204 ラップトップコンピュータ

1206 固定位置端末

10

【図1】

FIG. 1 (従来技術)

【図3】

FIG. 3 (従来技術)

【図2】

FIG. 2 (従来技術)

【図4】

FIG. 4

【図5】

FIG. 5

【図6】

FIG. 6

【図8】

| ヒューズ番号 | ESD事象: 閉じたままである |               |              | ヒューズ破断状態: 破断され開放する |               |              |

|--------|-----------------|---------------|--------------|--------------------|---------------|--------------|

|        | 電流              | 時間            | 総Q           | 電流                 | 時間            | 総Q           |

| ヒューズA  | 1 μA - 1 A      | 1 ps - 10 ns  | 1 aC - 10 nC | 1 mA - 500 mA      | 50 μs - 10 ms | 50 nC - 5 mC |

| ヒューズB  | 1 μA - 1 A      | 1 ps - 10 ns  | 1 aC - 10 nC | 5 mA - 500 mA      | 10 μs - 10 ms | 50 nC - 5 mC |

| ヒューズC  | 1 μA - 1 A      | 1 ps - 10 ns  | 1 aC - 10 nC | 10 mA - 500 mA     | 3 μs - 10 ms  | 50 nC - 5 mC |

| ヒューズD  | 1 μA - 10 A     | 1 ps - 1 ns   | 1 aC - 10 nC | 1 mA - 500 mA      | 50 μs - 10 ms | 50 nC - 5 mC |

| ヒューズE  | 1 μA - 10 A     | 1 ps - 1 ns   | 1 aC - 10 nC | 5 mA - 500 mA      | 10 μs - 10 ms | 50 nC - 5 mC |

| ヒューズF  | 1 μA - 10 A     | 1 ps - 1 ns   | 1 aC - 10 nC | 10 mA - 500 mA     | 3 μs - 10 ms  | 50 nC - 5 mC |

| ヒューズG  | 1 μA - 0.1A     | 1 ps - 100 ns | 1 aC - 10 nC | 1 mA - 500 mA      | 50 μs - 10 ms | 50 nC - 5 mC |

| ヒューズH  | 1 μA - 0.1A     | 1 ps - 100 ns | 1 aC - 10 nC | 5 mA - 500 mA      | 10 μs - 10 ms | 50 nC - 5 mC |

| ヒューズI  | 1 μA - 0.1A     | 1 ps - 100 ns | 1 aC - 10 nC | 10 mA - 500 mA     | 5 μs - 10 ms  | 50 nC - 5 mC |

FIG. 8

【図7】

FIG. 7

【図9】

FIG. 9

【図10】

FIG. 10

【図11】

FIG. 11

【図12】

FIG. 12

---

フロントページの続き

(51)Int.Cl. F I

H 01 L 23/522 (2006.01)

H 01 L 25/065 (2006.01)

H 01 L 25/07 (2006.01)

H 01 L 25/18 (2006.01)

(72)発明者 チュウ - グアン・タン

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 グレゴリー・エー・ウヴィエガーラ

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

(72)発明者 レザ・ジャリリゼインアリ

アメリカ合衆国・カリフォルニア・92121・サン・ディエゴ・モアハウス・ドライブ・577

5

審査官 市川 武宣

(56)参考文献 特開2002-124577(JP, A)

特開平02-146762(JP, A)

特開昭59-013354(JP, A)

特開昭59-134863(JP, A)

特開2010-129958(JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 21 / 822

H 01 L 21 / 3205

H 01 L 21 / 768

H 01 L 21 / 82

H 01 L 23 / 522

H 01 L 25 / 065

H 01 L 25 / 07

H 01 L 25 / 18

H 01 L 27 / 04