(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5185062号

(P5185062)

(45) 発行日 平成25年4月17日(2013.4.17)

(24) 登録日 平成25年1月25日(2013.1.25)

(51) Int.Cl.

H01L 25/10 (2006.01)

H01L 25/11 (2006.01)

H01L 25/18 (2006.01)

F 1

H01L 25/14

Z

請求項の数 5 (全 9 頁)

(21) 出願番号 特願2008-270414 (P2008-270414)

(22) 出願日 平成20年10月21日 (2008.10.21)

(65) 公開番号 特開2010-103129 (P2010-103129A)

(43) 公開日 平成22年5月6日 (2010.5.6)

審査請求日 平成22年2月5日 (2010.2.5)

(73) 特許権者 000005821

パナソニック株式会社

大阪府門真市大字門真1006番地

(74) 代理人 110001427

特許業務法人前田特許事務所

(74) 代理人 100077931

弁理士 前田 弘

(74) 代理人 100110939

弁理士 竹内 宏

(74) 代理人 100110940

弁理士 嶋田 高久

(74) 代理人 100113262

弁理士 竹内 祐二

(74) 代理人 100115059

弁理士 今江 克実

最終頁に続く

(54) 【発明の名称】積層型半導体装置及び電子機器

## (57) 【特許請求の範囲】

## 【請求項 1】

上面に第1の電極ランドと接続端子とが設けられた配線基板と、

回路形成面を前記配線基板に向かた状態で前記配線基板の上面上に搭載された半導体チップと、

前記第1の電極ランドと前記半導体チップの回路形成面とを接続する第1の接続部材と、

前記接続端子上であって、前記配線基板の上面のうち平面的に見て前記半導体チップの外側の領域上に設けられた第1の金属ポストと、

少なくとも前記配線基板と前記半導体チップとの隙間に充填された第1の封止樹脂と、

一方の主面に第2の電極ランドが設けられた半導体装置と、

前記第1の金属ポストと前記第2の電極ランドとを電気的に接続する第2の接続部材とを備え、

前記第1の封止樹脂は、前記配線基板と前記半導体チップとの隙間から前記第1の金属ポスト間の領域に亘って設けられており、前記第1の金属ポストの側面の一部は前記第1の封止樹脂より露出し、前記第1の金属ポストの側面の他部は前記第1の封止樹脂により覆われることを特徴とする積層型半導体装置。

## 【請求項 2】

前記第2の接続部材と前記第2の電極ランドとの間に設けられた第2の金属ポストをさらに備え、前記第2の金属ポストの側面は第1の封止樹脂より露出していることを特徴と

10

20

する請求項 1 に記載の積層型半導体装置。

**【請求項 3】**

前記第 1 の封止樹脂上及び前記半導体チップの回路形成面と対向する面上に設けられ、前記第 1 の金属ポストの上面を露出させる第 2 の封止樹脂をさらに備えていることを特徴とする請求項 1 または 2 に記載の積層型半導体装置。

**【請求項 4】**

前記半導体チップと前記第 1 の金属ポストとの距離は 0.1 mm 以上であることを特徴とする請求項 1 ~ 3 のうちいずれか 1 つに記載の積層型半導体装置。

**【請求項 5】**

請求項 1 ~ 4 のうちいずれか 1 つに記載の積層型半導体装置を備えた電子機器。 10

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、半導体チップを内包したパッケージが積層接続されてなる積層型半導体装置に関する。

**【背景技術】**

**【0002】**

近年、情報通信機器や事務用電子機器の小型化および高機能化が進展するのに伴って、これらの機器に搭載される半導体集積回路装置等を有する半導体装置についても、小型化とともに、入出力のための外部端子の数を増加することが要求されている。しかし、複数の半導体装置を同じ平面上に実装する方式では、小型化、薄型化が特に要求される携帯機器用の半導体装置を製造するのが困難になってきている。 20

**【0003】**

これらの要求を実現させる技術として、集積度の高いパッケージ積層構造である P o P (Package on Package) 構造が採用されるようになってきた。以下、図 5 を用いて従来の半導体装置について説明する。

**【0004】**

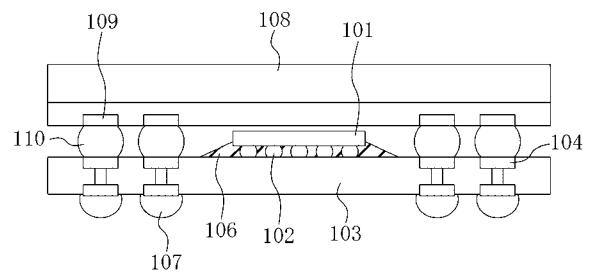

図 5 は、P o P 構造を有する従来の積層型半導体装置を示す断面図である。同図に示すように、半導体チップ 101 上には、半導体チップ 101 上の電極端子に機械的および電気的に接続されたはんだからなる金属バンプ 102 が形成されている。半導体チップ 101 は、配線基板 103 にこの金属バンプ 102 を介してフリップチップ搭載され、機械的および電気的に接続されている。そして、半導体チップ 101 と配線基板 103 との隙間には、金属バンプ 102 を封止するアンダーフィル樹脂 106 が充填されている。また、配線基板 103 の半導体チップ搭載面（以下、「上面」と称する）に対向する面（以下、「下面」と称する）には、はんだからなる外部接続端子 107 が形成されている。また、配線基板 103 の上面上のうち、半導体チップ 101 が搭載されていない、平面的に見て半導体チップ 101 を囲む領域上には接続端子 104 が配置されている。以上より形成された下側パッケージの上に、電極ランド 109 が下面に形成された積層パッケージ 108 がはんだからなる金属ボール 110 を介して機械的及び電気的に接続されている。金属ボール 110 は、接続端子 104 と電極ランド 109 を機械的、電気的に接続しており、外部接続端子 107 に電気的に接続されている。 30

**【0005】**

前述したフリップチップ実装方式による積層型半導体装置の製造方法について説明する。

**【0006】**

まず、電気めっき法や印刷法やボール搭載法などの方法で金属バンプ 102 を形成した半導体チップ 101 と、金属バンプ 102 に対応する位置に電極ランドが形成された配線基板 103 とを用意する。そして、半導体チップ 101 を配線基板 103 上にフリップチップ接続する。

**【0007】**

10

20

30

40

50

次に、半導体チップ101の金属バンプ102をリフローすることにより、はんだを溶融し、金属バンプ102により半導体チップ101と配線基板103とを接続する。

#### 【0008】

その後、半導体チップ101と配線基板103との隙間を清浄化し、ディスペンサを用いてその隙間にアンダーフィル樹脂106を注入する。注入は半導体チップ101の周辺部から行うが、液状の樹脂は毛細管現象により半導体チップ101と配線基板103との隙間の全体に浸入し、半導体チップ101と配線基板103との隙間にアンダーフィル樹脂106が充填される。

#### 【0009】

その後、熱処理を行い、アンダーフィル樹脂106を硬化することによって半導体チップ101の回路形成面及び金属バンプ102による接続部分を封止する。10

#### 【0010】

最後に、配線基板103の上面（チップ搭載面）と反対側の面（下面）に引き出された金属パッドに外部接続端子107を形成し、リフローする。

#### 【0011】

以上により、BGA型の積層型半導体装置が完成する。

【特許文献1】特開2007-287906号公報

#### 【発明の開示】

##### 【発明が解決しようとする課題】

#### 【0012】

20

前述したような従来のPOP構造では、下側パッケージに搭載された半導体チップ101の厚さおよび金属バンプ102の高さが接続後の金属ボール110の高さによりに制限される。また、積層パッケージ108が搭載される際に下側パッケージ上の接続端子104が露出している必要があり、そのため半導体チップ101と配線基板103との隙間に充填されているアンダーフィル樹脂106のフィレットが接続端子104の一部または全部を覆うことが許されず、結果として半導体チップ101の外形サイズが制限される。

#### 【0013】

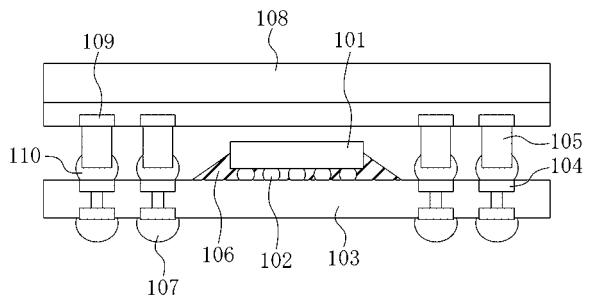

両パッケージ間のスタンドオフ（積層パッケージ108と配線基板103との隙間）を確保する方法として、図6に示すように、積層パッケージ108の電極ランド109に金属ポスト105を形成する方法がある（例えば、特許文献1参照）。この構成によれば、金属ポスト105を追加する分、図5に示す構造よりもスタンドオフを広げができる可能性がある。しかし、積層パッケージ108が搭載される際に下側パッケージ上の接続端子104が完全に露出している必要があることは解消されず、そのため半導体チップ101の外形サイズが制限されることは解決できない。30

#### 【0014】

本発明は、このような事情に鑑み、複数のパッケージが積層されてなる積層型半導体装置において、パッケージ間のスタンドオフを十分に確保しつつ、チップサイズの制限を緩和することを目的とする。

#### 【課題を解決するための手段】

#### 【0015】

40

上記目的を達成するために、本発明の積層型半導体装置は、上面に第1の電極ランドと接続端子とが設けられた配線基板と、回路形成面を前記配線基板に向かた状態で前記配線基板の上面に搭載された半導体チップと、前記第1の電極ランドと前記半導体チップの回路形成面とを接続する第1の接続部材と、前記接続端子上であって、前記配線基板の上面のうち平面的に見て前記半導体チップの外側の領域上に設けられた第1の金属ポストと、少なくとも前記配線基板と前記半導体チップとの隙間に充填された封止樹脂と、一方の主面に第2の電極ランドが設けられた半導体装置と、前記第1の金属ポストと前記第2の電極ランドとを電気的に接続する第2の接続部材とを備えている。

#### 【0016】

この構成によれば、第1の金属ポストが接続端子上に設けられていることにより、配線

50

基板と半導体装置間のスタンドオフを十分に確保することができる。このため、第1の接続部材の高さや半導体チップの厚みの制限が緩和され、半導体チップの破損等を防ぐことができる。また、封止樹脂が配線基板と半導体チップとの隙間から第1の金属ポスト間の領域にはみ出しても第1の金属ポストと第2の接続部材との電気的接続は確保できるので、半導体チップと第1の金属ポストとの距離を従来の積層型半導体装置に比べて縮小することができ、積層型半導体装置のサイズが同じである場合でも、半導体チップのサイズを従来よりも大きくすることができます。

#### 【0017】

また、本発明の積層型半導体装置は、携帯電話等の通信機器やデジタルカメラ等種々の電子機器に用いられる。

10

#### 【発明の効果】

#### 【0018】

以上のように、PnP構造をとる場合に、配線基板と半導体装置との間のスタンドオフを十分に確保しつつ、チップサイズの制限を大幅に緩和することができる。

#### 【発明を実施するための最良の形態】

#### 【0019】

以下、本発明に係る積層型半導体装置の実施形態について図面を用いて詳細に説明する。

#### 【0020】

##### (第1の実施形態)

20

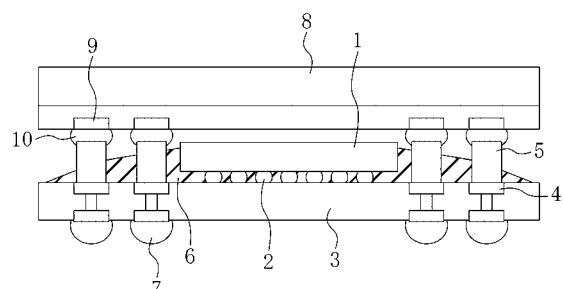

図1は、本発明の第1の実施形態に係る積層型半導体装置を示す断面図である。同図に示すように、本実施形態の積層型半導体装置は、上面及び下面に複数の接続端子4が形成された配線基板3と、配線基板3の上面上に回路形成面を配線基板3に向けて搭載された半導体チップ1と、配線基板3の上面に設けられた接続端子4上に設けられ、平面的に見て半導体チップ1の外側の位置に形成された金属ポスト5と、一方の主面に電極ランド9が形成され、金属ポスト5上にはんだ等からなる金属ボール(第2の接続部材)10を介して機械的、電気的に接続された積層パッケージ(半導体装置)8と、配線基板3の下面に形成された接続端子4上に設けられたはんだ等からなる外部接続端子7と、半導体チップ1と配線基板3との隙間に充填され、金属バンプ2を封止するアンダーフィル樹脂(封止樹脂)6とを備えている。配線基板3の上面に形成されたランドは、はんだ等からなる金属バンプ(第1の接続部材)2を介して半導体チップ1の回路形成面に接続されている。積層パッケージ8は、半導体チップ1とは別の半導体チップ(図示せず)を有している。

30

#### 【0021】

半導体チップ1の回路形成面にはアルミニウム(A1)からなる複数の電極パッドが形成されている。その電極パッド上に、例えばスパッタ法によって形成されたチタン(Ti)からなるバリアメタルと銅(Cu)からなる下部金属膜と、その上方に電気めっき法によって形成されたニッケル(Ni)からなる上部金属膜とによって構成された金属膜が形成されている。バリアメタルにはTiWやCr等を用いてもよい。または、金属膜は、無電解めっき法によって形成されたニッケル(Ni/Au)で構成されていてもよい。さらに、この金属膜上に上述の金属バンプ2が形成される。

40

#### 【0022】

配線基板3の配線は銅(Cu)からなり、電極ランドは配線基板3上面に形成されたソルダーレジストを開口させて形成している。その表面は、無電解めっき法によって形成されたニッケル(Ni/Au)からなる金属膜によって構成されている。または、OSP(Organic Solder Preservative)が配線基板3の上面に塗布されていてもよい。さらに、印刷法もしくは搭載法によりはんだからなるSOP(Solder on Pad)が配線基板3の上面に形成されていてもよい。配線基板3の上面のうち、上記の電極ランドが形成されていない外側の領域に、積層パッケージ8の電極ランド9上に形成された金属ボール10に対応する接続端子4が形成されている。また、金属ポスト5は、例えば銅等の金属で構成さ

50

れており、金属ポスト 5 の上面位置は少なくとも金属バンプ 2 の上端よりも高いことが好ましく、搭載後の半導体チップ 1 の裏面（回路形成面に対向する面）と同等以上であることが特に好ましい。

#### 【 0 0 2 3 】

本実施形態の積層型半導体装置を作成する際には、まず半導体チップ 1 の回路形成面（正面）を下に向かた状態で金属バンプ 2 の先端にフラックスを転写する。あるいは、配線基板 3 の上面にフラックスを塗布してもよい。この後、半導体チップ 1 を配線基板 3 の上面に搭載し、リフロー炉で加熱することで金属バンプ 2 を溶融させ、半導体チップ 1 と配線基板 3 とを接続する。次いで、半導体チップ 1 の回路形成面及び金属バンプ 2 による接続部分を保護するため、半導体チップ 1 と配線基板 3 との隙間にアンダーフィル樹脂 6 を半導体チップ 1 の外周部からディスペンサで塗布・充填する。この際に、アンダーフィル樹脂 6 が金属ポスト 5 の上面を覆うことなく、金属ポスト 5 の周辺部に充填される。なお、全ての金属ポスト 5 間の隙間がアンダーフィル樹脂 6 に周辺部を充填される必要はなく、アンダーフィル樹脂 6 と接触しない金属ポスト 5 があってもよい。10

#### 【 0 0 2 4 】

次に、積層パッケージ 8 の電極ランド 9 を下側パッケージ上に搭載する。ここで、「下側パッケージ」とは、配線基板 3、半導体チップ 1 及び金属ポスト 5 を含むパッケージのことを指す。この工程では、電極ランド 9 上に設けられた金属ボール 10 と金属ポスト 5 とを位置を合わせて接触させた状態でリフロー炉内で加熱し、金属ボール 10 を溶解させ、金属ボール 10 と金属ポスト 5 とを接続させる。以上のようにして本実施形態の積層型半導体装置が作製される。なお、金属ボール 10 は積層パッケージ 8 側ではなく下側パッケージ側にあらかじめ設けられていてもよい。20

#### 【 0 0 2 5 】

本実施形態の積層型半導体装置の特徴は、配線基板 3 の上面側の接続端子 4 上に金属ポスト 5 が設けられていることにある。これにより、下側パッケージと積層パッケージ 8 との間隔（スタンドオフ）を十分に広く確保することができるので、金属バンプ 2 の高さや半導体チップ 1 の厚みの制限がなくなり、設計の自由度が向上する。これに伴って、半導体チップ 1 の割れや金属バンプ 2 の破壊も抑制することができる。また、金属ポスト 5 が設けられていることにより、半導体チップ 1 のサイズを大きくしても、配線基板 3 と半導体チップ 1 との隙間から漏れだしたアンダーフィル樹脂 6 が金属ポスト 5 の上面を覆うことがなくなる。このため、半導体チップ 1 を金属ポスト 5 に近接して配置することができる、積層型半導体装置の平面サイズに対して半導体チップ 1 の平面サイズが占める割合を大きくすることができる。よって、同じサイズの半導体チップ 1 を用いた場合でも積層型半導体装置の外形サイズを従来よりも小さくすることが可能となる。金属ポスト 5 と半導体チップ 1 との距離は従来の積層型半導体装置に比べて小さくすることができるが、製造の都合上 0.1 mm 以上であることが好ましい。30

#### 【 0 0 2 6 】

##### （第 2 の実施形態）

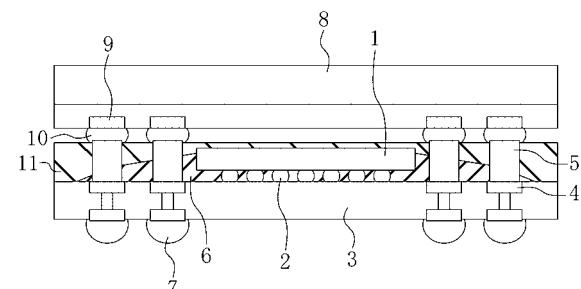

図 2 は、本発明の第 2 の実施形態に係る積層型半導体装置を示す断面図である。同図において、図 1 に示す部材と同じ部材については同一の符号を付して説明を省略または簡略化する。40

#### 【 0 0 2 7 】

本実施形態の積層型半導体装置では、第 1 の実施形態に係る積層型半導体装置において、金属ボール 10 と電極ランド 9 との間に第 2 の金属ポスト 15 が設けられた構成をとっている。第 2 の金属ポスト 15 及び金属ボール 10 は、積層パッケージ 8 の搭載工程の前にあらかじめ積層パッケージ 8 に設けておく。その他の構成は第 1 の実施形態の積層型半導体装置と同様であるので、説明を省略する。

#### 【 0 0 2 8 】

本実施形態の積層型半導体装置においては、積層パッケージ 8 と下側パッケージとのスタンドオフを第 1 の実施形態の積層型半導体装置よりもさらに広く確保できる。その結果50

として、半導体チップ1の厚さおよび金属バンプ2の高さの制限が小さくなり、半導体チップ1の割れや金属バンプ2の破壊をより効果的に抑制することができる。また、第1の実施形態の積層型半導体装置と同様に金属ポスト5が設けられていることにより、半導体チップ1のサイズを従来よりも大きくすることができる。

#### 【0029】

##### (第3の実施形態)

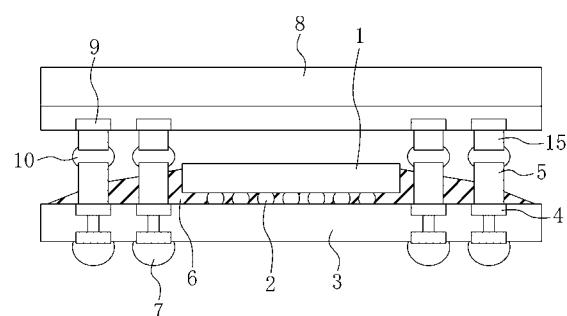

図3は、本発明の第3の実施形態に係る積層型半導体装置を示す断面図である。同図において、図1に示す部材と同じ部材については同一の符号を付して説明を省略または簡略化する。

#### 【0030】

本実施形態の積層型半導体装置の特徴は、下側パッケージの上面部、すなわちアンダーフィル樹脂6及び半導体チップ1の裏面上にモールド樹脂11が形成されていることにある。モールド樹脂11は金属ポスト5を埋め込むとともに、金属ポスト5の上面(頭頂部)を露出させる。その他の構成は第1の実施形態の積層型半導体装置と同様であるので、説明を省略する。

#### 【0031】

本実施形態の積層型半導体装置は、アンダーフィル樹脂6の注入及び硬化を行った後、金属ポスト5の上面に密着して下側パッケージの上面全体を覆うテープなどを設けた状態でモールド樹脂11を注入する。次いで、モールド樹脂11を硬化させた後、テープをはがすことによって積層型半導体装置が作製できる。

#### 【0032】

本実施形態の積層型半導体装置においては、金属ポスト5の周辺部を強固に保護できる。その結果として、積層パッケージ8と下側パッケージとの接続部の破壊を抑えることができる。また、第1の実施形態の積層型半導体装置と同様に金属ポスト5が設けられることにより、半導体チップ1のサイズを従来よりも大きくすることができる。

#### 【0033】

##### (第4の実施形態)

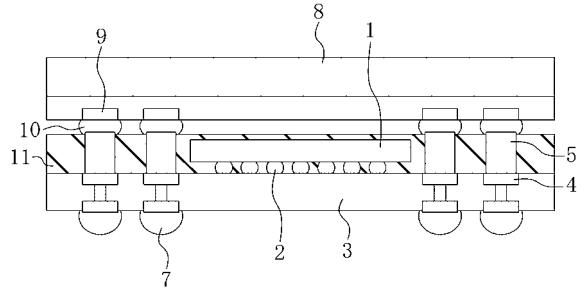

図4は、本発明の第4の実施形態に係る積層型半導体装置を示す断面図である。同図において、図1に示す部材と同じ部材については同一の符号を付して説明を省略または簡略化する。

#### 【0034】

本実施形態の積層型半導体装置は、第3の実施形態に係る積層型半導体装置において、アンダーフィル樹脂6を形成せず、モールド樹脂11が半導体チップ1と配線基板3との隙間にも充填された構成となっている。すなわち、モールド樹脂11は、配線基板3と半導体チップ1との隙間に充填されるとともに第1の金属ポスト5間の領域及び半導体チップ1を埋め込み、金属ポストの上5面を露出させる均一な樹脂で構成されている。

#### 【0035】

本実施形態の積層型半導体装置においては、アンダーフィル樹脂6を形成するプロセスを省略することができる。また、モールド樹脂11とアンダーフィル樹脂6との界面に剥離が生じる問題を解消することができる。その結果として、下側パッケージの信頼性を向上することができる。また、第1の実施形態の積層型半導体装置と同様に金属ポスト5が設けられることにより、半導体チップ1のサイズを従来よりも大きくすることができる。

#### 【0036】

なお、以上で説明した各実施形態の積層型半導体装置は、多段構成の例えば撮像ユニットとして携帯電話等の通信機器、デジタルカメラ等の電子機器などに搭載することができる。

#### 【産業上の利用可能性】

#### 【0037】

本発明は、PnP構造を有する積層型半導体装置に適用され、種々の電子機器に用いら

10

20

30

40

50

れる。

**【図面の簡単な説明】**

**【0038】**

【図1】本発明の第1の実施形態に係る積層型半導体装置を示す断面図である。

【図2】本発明の第2の実施形態に係る積層型半導体装置を示す断面図である。

【図3】本発明の第3の実施形態に係る積層型半導体装置を示す断面図である。

【図4】本発明の第4の実施形態に係る積層型半導体装置を示す断面図である。

【図5】P o P構造を有する従来の積層型半導体装置を示す断面図である。

【図6】従来の積層型半導体装置の一例を示す断面図である。

**【符号の説明】**

**【0039】**

- |    |           |

|----|-----------|

| 1  | 半導体チップ    |

| 2  | 金属バンプ     |

| 3  | 配線基板      |

| 4  | 接続端子      |

| 5  | 金属ポスト     |

| 6  | アンダーフィル樹脂 |

| 7  | 外部接続端子    |

| 8  | 積層パッケージ   |

| 9  | 電極ランド     |

| 10 | 金属ボール     |

| 11 | モールド樹脂    |

| 15 | 第2の金属ポスト  |

10

20

**【図1】**

**【図3】**

**【図2】**

**【図4】**

【図5】

【図6】

---

フロントページの続き

(74)代理人 100115691

弁理士 藤田 篤史

(74)代理人 100117581

弁理士 二宮 克也

(74)代理人 100117710

弁理士 原田 智雄

(74)代理人 100121728

弁理士 井関 勝守

(74)代理人 100124671

弁理士 関 啓

(74)代理人 100131060

弁理士 杉浦 靖也

(72)発明者 大隅 貴寿

大阪府門真市大字門真1006番地 パナソニック株式会社内

審査官 關根 崇

(56)参考文献 特開2007-287762(JP, A)

国際公開第2007/069606(WO, A1)

特開2007-281129(JP, A)

特開2007-123520(JP, A)

特開2007-287906(JP, A)

(58)調査した分野(Int.Cl., DB名)

H 01 L 25 / 10

H 01 L 25 / 11

H 01 L 25 / 18

H 01 L 21 / 56