(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6349855号

(P6349855)

(45) 発行日 平成30年7月4日(2018.7.4)

(24) 登録日 平成30年6月15日(2018.6.15)

(51) Int.Cl.

F 1

H02M 1/08 (2006.01)

H03K 17/08 (2006.01)H02M 1/08

H03K 17/08A

C

請求項の数 7 (全 13 頁)

(21) 出願番号 特願2014-66596 (P2014-66596)

(22) 出願日 平成26年3月27日 (2014.3.27)

(65) 公開番号 特開2015-192490 (P2015-192490A)

(43) 公開日 平成27年11月2日 (2015.11.2)

審査請求日 平成29年2月15日 (2017.2.15)

(73) 特許権者 000004260

株式会社デンソー

愛知県刈谷市昭和町1丁目1番地

(74) 代理人 100106149

弁理士 矢作 和行

(74) 代理人 100121991

弁理士 野々部 泰平

(74) 代理人 100145595

弁理士 久保 貴則

(72) 発明者 長瀬 拓生

愛知県刈谷市昭和町1丁目1番地 株式会社デンソー内

審査官 坂東 博司

最終頁に続く

(54) 【発明の名称】 駆動装置

## (57) 【特許請求の範囲】

## 【請求項 1】

パワースイッチング素子(200)のオンオフを制御する駆動装置であって、前記パワースイッチング素子のゲート電流を制御してオフ動作を行うオフ側回路(120)を備え、

前記オフ側回路は、

出力トランジスタとしてのメインMOSトランジスタ(Tr1)と、

前記メインMOSトランジスタとゲートが共通し、前記メインMOSトランジスタに対してカレントミラーを構成することによって、前記メインMOSトランジスタのドレイン電流を規定するセンスMOSトランジスタ(Tr2)と、

前記センスMOSトランジスタのドレイン電流を一定に制御するセンス電流制御回路と、を有し、

前記センス電流制御回路は、参照電位を発生させる参照電源(123)と、前記センスMOSトランジスタに直列接続された基準抵抗(122)と、前記基準抵抗と前記センスMOSトランジスタとの間の電位が前記参照電位に近づくように前記センスMOSトランジスタのゲートに出力を発生させるオペアンプ(121)と、を有して、前記センスMOSトランジスタのドレイン電流として前記基準抵抗の抵抗値と前記参照電位とによって決まる電流を流すように構成され、

前記オフ側回路は、前記センスMOSトランジスタのゲートに対して、前記オペアンプと並列に接続され、前記オペアンプの出力と異なる電位を発生させるドライブ能力切替電

10

20

源(125)と、

前記メインMOSトランジスタのゲートに印加される電圧を、前記オペアンプと前記ドライブ能力切替電源との間で切り替え可能なドライブ能力切替スイッチ(SW1, SW2)と、を有することを特徴とする駆動装置。

【請求項2】

前記ドライブ能力切替電源の少なくとも一つは、前記オペアンプの出力よりも高い電位を発生させるものであり、

前記パワースイッチング素子のゲート電圧が所定の閾値を下回ることにより、前記メインMOSトランジスタのゲートに印加される電圧が、前記オペアンプの出力よりも高くなることを特徴とする請求項1に記載の駆動装置。

10

【請求項3】

パワースイッチング素子(200)のオンオフを制御する駆動装置であって、

前記パワースイッチング素子のゲート電流を制御してオフ動作を行うオフ側回路(120)を備え、

前記オフ側回路は、

出力トランジスタとしてのメインMOSトランジスタ(Tr1)と、

前記メインMOSトランジスタとゲートが共通し、前記メインMOSトランジスタに対してカレントミラーを構成することによって、前記メインMOSトランジスタのドレイン電流を規定するセンスMOSトランジスタ(Tr2)と、

前記センスMOSトランジスタのドレイン電流を一定に制御するセンス電流制御回路と、を有し、

20

前記センス電流制御回路は、参照電位を発生させる参照電源(123)と、前記センスMOSトランジスタに直列接続された基準抵抗(122)と、前記基準抵抗と前記センスMOSトランジスタとの間の電位が前記参照電位に近づくように前記センスMOSトランジスタのゲートに出力を発生させるオペアンプ(121)と、を有して、前記センスMOSトランジスタのドレイン電流として前記基準抵抗の抵抗値と前記参照電位とによって決まる電流を流すように構成され、

前記メインMOSトランジスタのゲートに接続され、前記パワースイッチング素子のコレクタ電流の電流値に基づいて動作する保護回路(130)を備え、

該保護回路は、

30

前記メインMOSトランジスタとカレントミラーを構成する保護用MOSトランジスタ(Tr3)と、

前記保護用MOSトランジスタに一定のドレイン電流を供給する定電流回路(P1, P2)と、

前記定電流回路と前記保護用MOSトランジスタの間に設けられ、前記保護用MOSトランジスタへの電流供給を制御する保護スイッチ(SW3, SW4)と、

前記パワースイッチング素子のコレクタ電流の電流値が所定の閾値を上回ったことを検出するコレクタ電流検出部(140)と、を有し、

該コレクタ電流検出部は、前記パワースイッチング素子のコレクタ電流の電流値が所定の閾値を上回ることにより、前記保護スイッチをオンすることを特徴とする駆動装置。

40

【請求項4】

前記オフ側回路は、前記センスMOSトランジスタのゲートに対して、前記オペアンプと並列に接続され、前記オペアンプの出力と異なる電位を発生させるドライブ能力切替電源(125)と、

前記メインMOSトランジスタのゲートに印加される電圧を、前記オペアンプと前記ドライブ能力切替電源との間で切り替え可能なドライブ能力切替スイッチ(SW1, SW2)と、を有することを特徴とする請求項3に記載の駆動装置。

【請求項5】

前記ドライブ能力切替電源の少なくとも一つは、前記オペアンプの出力よりも高い電位を発生させるものあり、

50

前記パワースイッチング素子のゲート電圧が所定の閾値を下回ることにより、前記メインMOSトランジスタのゲートに印加される電圧が、前記オペアンプの出力よりも高くなることを特徴とする請求項4に記載の駆動装置。

【請求項6】

前記パワースイッチング素子のコレクタ電流の閾値は、過電流検出用の閾値、および、過電流検出用の閾値よりも高い電流値に設定された短絡検出用の閾値、の少なくとも一方が設定されることを特徴とする請求項3～5のいずれか1項に記載の駆動装置。

【請求項7】

前記参照電位は、予め測定された前記パワースイッチング素子のゲート容量に対応した値に設定されることを特徴とする請求項1～6のいずれか1項に記載の駆動装置。

10

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、パワースイッチング素子のオンオフ制御および異常時の保護を行う駆動装置に関する。

【背景技術】

【0002】

インバータやコンバータ等の半導体電力変換装置を構成するパワースイッチング素子について、スイッチング動作時のサージ電圧とスイッチング損失とのトレードオフを向上する技術として、ゲート電圧あるいはゲート電流を動的に制御するアクティブゲートコントロール(AGC)が用いられている。

20

【0003】

また、特許文献1のように、パワースイッチング素子に過大な電流が流れた場合にゲート電圧を抑制してコレクタ電流を抑制し、パワースイッチング素子が破壊しないように保護する駆動回路が提案されている。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特開2010-34701号公報

30

【発明の概要】

【発明が解決しようとする課題】

【0005】

しかしながら、特許文献1では、パワースイッチング素子のゲート電流を制御するためには多くのMOSFETや抵抗器等が必要となる。このため、回路規模、すなわちレイアウト面積が大きくなってしまう。

【0006】

また、特許文献1の技術は、パワースイッチング素子のゲートに接続された抵抗器の抵抗値に基づいて、ゲート電流を制御する方式であるため、パワースイッチング素子の製造ばらつきに起因する閾値電圧のばらつきによって、スイッチング速度がばらつき、スイッチング損失にばらつきが生じてしまう。つまり、スイッチング損失が仕様書等に規定された規格から外れ、歩留まりが低下する等の問題がある。

40

【0007】

本発明は、上記問題点を鑑みてなされたものであり、パワースイッチング素子のターンオフ動作を行う駆動装置において、回路規模を抑制しつつ出力電流を高精度に制御してスイッチング損失を低減することを目的とする。

【課題を解決するための手段】

【0008】

ここに開示される発明は、上記目的を達成するために以下の技術的手段を採用する。なお、特許請求の範囲およびこの項に記載した括弧内の符号は、ひとつの態様として後述する実施形態に記載の具体的手段との対応関係を示すものであって、発明の技術的範囲を限

50

定するものではない。

【0009】

上記目的を達成するために、本発明のひとつは、パワースイッチング素子(200)のオンオフを制御する駆動装置であって、パワースイッチング素子のゲート電流を制御してオフ動作を行うオフ側回路(120)を備え、オフ側回路は、出力トランジスタとしてのメインMOSトランジスタ(Tr1)と、メインMOSトランジスタとゲートが共通し、メインMOSトランジスタに対してカレントミラーを構成することによって、メインMOSトランジスタのドレイン電流を規定するセンスMOSトランジスタ(Tr2)と、センスMOSトランジスタのドレイン電流を一定に制御するセンス電流制御回路と、を有し、センス電流制御回路は、参照電位を発生させる参照電源(123)と、センスMOSトランジスタに直列接続された基準抵抗(122)と、基準抵抗とセンスMOSトランジスタとの間の電位が参照電位に近づくようにセンスMOSトランジスタのゲートに出力を発生させるオペアンプ(121)と、を有して、センスMOSトランジスタのドレイン電流として基準抵抗の抵抗値と参照電位とによって決まる電流を流すように構成され、オフ側回路は、センスMOSトランジスタのゲートに対して、オペアンプと並列に接続され、オペアンプの出力と異なる電位を発生させるドライブ能力切替電源(125)と、メインMOSトランジスタのゲートに印加される電圧を、オペアンプとドライブ能力切替電源との間で切り替え可能なドライブ能力切替スイッチ(SW1, SW2)と、を有することを特徴としている。

【0010】

これによれば、カレントミラーによってメインMOSトランジスタのドレイン電流を規定するセンスMOSトランジスタのドレイン電流が、参照電位と基準抵抗の抵抗値によって規定される。このため、本発明に係る駆動装置に電力を供給する電源電圧や、オフ側回路の出力電流の電流値に依らず、出力電流を高精度に制御することができる。したがって、パワースイッチング素子のゲート電流のばらつきを小さくでき、スイッチング損失を低減することができる。

【0011】

また、特許文献1のような従来技術に較べて、抵抗器等の受動素子の部品点数を削減できるため、レイアウト面積を小さくすることができる。例えば、本発明に係る駆動装置とパワースイッチング素子とを同一のパッケージに実装することが可能になり、集積化することができる。

【0012】

また、特許文献1では、パワースイッチング素子のゲートを駆動するゲート電流が大きく、なおかつ精度が必要なためにディスクリート部品の抵抗器が必要であった。これに対して、本発明の回路構成では、パワースイッチング素子のゲートの直列経路に抵抗器が不要であるため、ディスクリート部品を削減でき、集積化が容易である。

【図面の簡単な説明】

【0013】

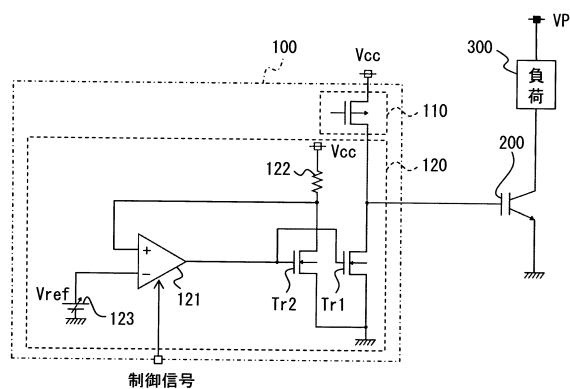

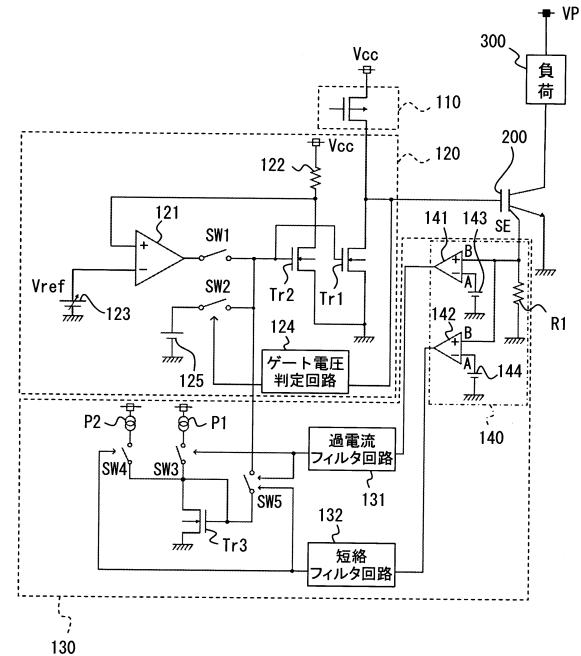

【図1】第1実施形態に係る駆動装置の概略構成を示す回路図である。

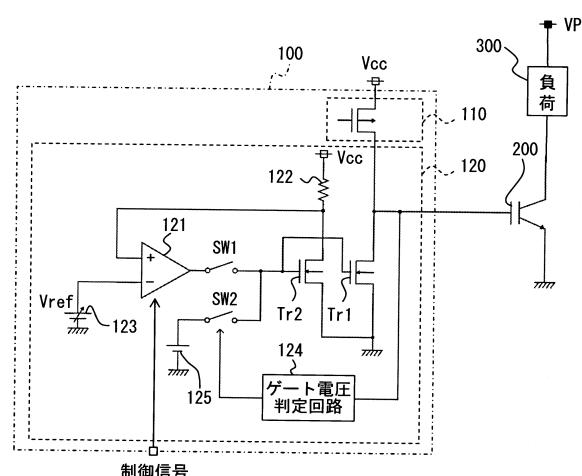

【図2】駆動装置およびパワースイッチング素子の概略構成を示す上面図である。

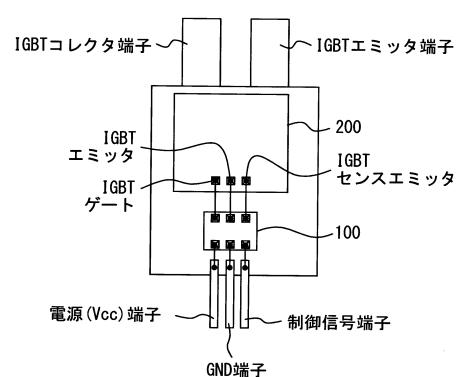

【図3】第2実施形態に係る駆動装置の概略構成を示す回路図である。

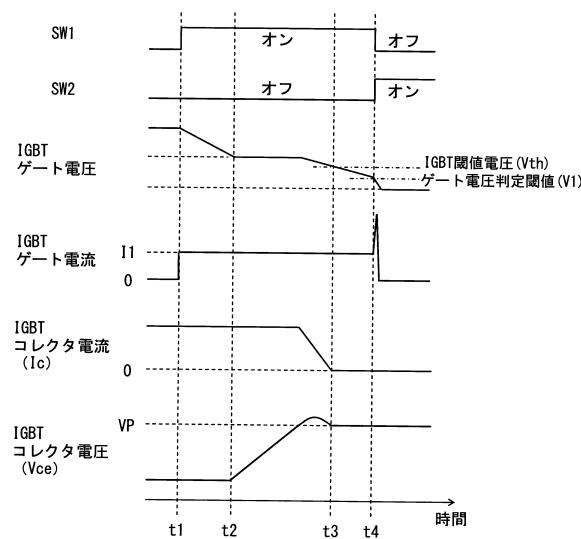

【図4】駆動装置による駆動を示すタイミングチャートである。

【図5】第3実施形態に係る駆動装置の概略構成を示す回路図である。

【発明を実施するための形態】

【0014】

以下、本発明の実施の形態を図面に基づいて説明する。なお、以下の各図相互において、互いに同一もしくは均等である部分に、同一符号を付与する。

【0015】

(第1実施形態)

最初に、図1を参照して、本実施形態に係る駆動装置について説明する。

10

20

30

40

50

## 【0016】

図1に示すように、この駆動装置100は、負荷300を駆動するパワースイッチング素子としての絶縁ゲートバイポーラトランジスタ(IGBT)200の駆動を制御するものである。

## 【0017】

この駆動装置100は、オン側回路110と、オフ側回路120と、を備えている。

## 【0018】

オン側回路110およびオフ側回路120は電源とGNDとの間で直列に接続され、その中間点にIGBT200のゲートが接続されている。オン側回路110は、PMOSトランジスタにより構成され、このPMOSトランジスタがオン状態のときにはIGBT200のゲートに電源電圧Vccが印加される。これによりIGBT200がオン状態になり、IGBT200のコレクタ-エミッタ間に電流が流れ、負荷300に電力が供給される。

10

## 【0019】

オフ側回路120は、2つのNMOSトランジスタ(Tr1, Tr2)を有している。これらNMOSトランジスタは、出力トランジスタとしてのメインMOSトランジスタTr1と、メインMOSトランジスタTr1のドレイン電流を規定するセンスMOSトランジスタTr2とから構成されている。本実施形態では、メインMOSトランジスタTr1が、センスMOSトランジスタTr2に対してカレントミラーを構成するようになっている。具体的には、メインMOSトランジスタTr1のゲートはセンスMOSトランジスタTr2のゲートと共に通とされ、ソースが共通してGNDに接続されている。メインMOSトランジスタTr1のドレインはIGBT200のゲート接続されている。

20

## 【0020】

このような構成では、メインMOSトランジスタTr1には、センスMOSトランジスタTr2とのサイズ比と同一の電流比でドレイン電流が流れる。

## 【0021】

また、オフ側回路120は、センスMOSトランジスタTr2のドレイン電流を制御するためのオペアンプ121と、該オペアンプ121の出力を規定するための基準抵抗122と、該オペアンプ121の一つの入力端子に参照電位Vrefを与える参照電源123と、を有している。オペアンプ121は、図示しないマイコンなどからIGBT200をオフさせることを示す制御信号が入力されると、センスMOSトランジスタTr2のゲートに電圧を印加することで、IGBT200のゲートから一定の電流が引き抜かれるようになっている。

30

## 【0022】

基準抵抗122は、シャント抵抗であり、センスMOSトランジスタTr2のドレイン電流の電流値を規定する。ひいては、IGBT200のゲートから引き抜かれる電流の電流値を規定する。IGBT200のゲートから引き抜かれる電流は、メインMOSトランジスタTr1に流れるドレイン電流である。そして、メインMOSトランジスタTr1はセンスMOSトランジスタTr2とともにカレントミラーを構成しているので、IGBT200のゲートから引き抜かれる電流はセンスMOSトランジスタTr2のドレイン電流に依存する。

40

## 【0023】

このような構成では、IGBT200をオフさせることを示す制御信号が入力されると、オペアンプ121が駆動されてセンスMOSトランジスタTr2にゲート電圧が印加される。このときのドレイン電流は基準抵抗122の抵抗値Rにより規定される。そして、その電流値は、基準抵抗122とセンスMOSトランジスタTr2との間の接続点の電位が、参照電位Vrefに近づくように、オペアンプ121の出力が調整されることによりフィードバック制御される。これにより、センスMOSトランジスタTr2のドレイン電流が高精度に一定の値( $= (V_{cc} - V_{ref}) / R$ )に制御される。よって、IGBT200のゲートから引き抜かれる電流も、高精度に一定電流とされる。なお、本実施形態

50

において、特許請求の範囲に記載のセンス電流制御回路は、オペアンプ121と基準抵抗122および参照電源123とにより構成される回路に相当する。

【0024】

次に、本実施形態に係る駆動装置100の作用効果について説明する。

【0025】

カレントミラーによってメインMOSトランジスタTr1のドレイン電流を規定するセンスMOSトランジスタTr2のドレイン電流が、参照電位Vrefと基準抵抗の抵抗値Rによって規定される。このため、駆動装置100に電力を供給する電源電圧Vccや、オフ側回路の出力電流の電流値に依らず、出力電流を高精度に制御することができる。したがって、IGBT200のゲート電流のばらつきを小さくでき、スイッチング損失を低減することができる。

【0026】

また、従来技術に較べて、抵抗器等の受動素子の部品点数を削減できるため、駆動装置100のレイアウト面積を小さくすることができる。例えば、図2に示すように、駆動装置100とIGBT200とを同一のパッケージに実装することが可能になり、集積化することができる。

【0027】

また、例えば特許文献1では、パワースイッチング素子のゲートを駆動するゲート電流が大きく、なおかつ精度が必要なためにディスクリート部品の抵抗器が必要であった。これに対して、本発明の回路構成では、パワースイッチング素子のゲートの直列経路に抵抗器が不要であるため、ディスクリート部品を削減でき、集積化が容易である。

【0028】

(第2実施形態)

本実施形態に係る駆動装置100は、図3に示すように、オフ側回路120の構成要素として、第1実施形態における要素に加えて、ゲート電圧判定回路124と、ドライブ能力切替電源125と、ドライブ能力切替スイッチSW1, SW2とを有している。

【0029】

まず、図3を参照して、本実施形態に係る駆動装置100の構成要素について説明する。

【0030】

ゲート電圧判定回路124は、IGBT200のゲート電圧と所定の閾値(以降、ゲート電圧判定閾値V1という)とを比較し、これらの大小関係に基づいて、後述するドライブ能力切替スイッチSW1, SW2のオンオフを切り替える。

【0031】

ドライブ能力切替電源125は、センスMOSトランジスタTr2のゲートに対して、オペアンプ121と並列に接続されている。本実施形態におけるドライブ能力切替電源125は、センスMOSトランジスタTr2のゲートに印加する電圧がオペアンプ121により印加される電圧よりも高く設定されている。

【0032】

ドライブ能力切替スイッチSW1, SW2は、センスMOSトランジスタTr2のゲートに印加される電圧について、オペアンプ121から印加されるか、あるいはドライブ能力切替電源125から印加されるか、を切り替えるスイッチである。具体的には、スイッチSW1は、センスMOSトランジスタTr2のゲートとオペアンプ121の出力端子との間に接続されている。スイッチSW2は、センスMOSトランジスタTr2のゲートとドライブ能力切替電源125との間に接続されている。

【0033】

次に、図4を参照して、本実施形態に係る駆動装置100の動作および作用効果について説明する。

【0034】

時刻t1において、オペアンプ121にIGBT200をオフさせることを示す制御信

10

20

30

40

50

号が入力される。時刻  $t_1$ においては、出力電流を高精度に制御するため、オペアンプ 121 によるセンスMOSトランジスタTr2の駆動を行う。つまり、ドライブ能力切替スイッチSW1がオン状態とされ、ドライブ能力切替スイッチSW2はオフ状態とされる。これにより、図4に示すように、オペアンプ121が駆動してIGBT200のゲート電流が流れる。

【0035】

IGBT200のゲートから電荷の引き抜きが行われ始めると、ゲート電圧は低下していく。そして、時刻  $t_2$ において、ゲート電圧が所定の電位（ミラー電圧）まで低下して所定時間が経過するとコレクタ電圧  $V_{ce}$  が上昇を始める。そして、コレクタ電圧が電源電圧  $V_P$  に達した時点からコレクタ電流  $I_c$  が減少を開始する。

10

【0036】

そして、時刻  $t_3$ において、IGBT200のゲート電圧が閾値電圧（いわゆる  $V_{th}$ ）を下回るとコレクタ電流  $I_c$  はゼロに収束し、コレクタ電圧  $V_{ce}$  は電源電圧  $V_P$  に収束する。

【0037】

その後もドライブ能力切替スイッチSW1がオン状態であるから、オフ側回路120によるIGBT200のゲート電荷の引き抜きは継続される。これにより、IGBT200のゲート電圧は低下を続ける。そして、時刻  $t_4$ において、ゲート電圧がゲート電圧判定回路124において設定されたゲート電圧判定閾値  $V_1$  を下回ると、ゲート電圧判定回路124は、ドライブ能力切替スイッチSW1をオンからオフに遷移させ、ドライブ能力切替スイッチSW2をオフからオンに遷移させる。つまり、メインMOSトランジスタTr1のゲートには、オペアンプ121からの出力ではなく、ドライブ能力切替電源125の電圧が印加された状態となる。

20

【0038】

ドライブ能力切替電源125は、メインMOSトランジスタTr1のゲートに印加する電圧がオペアンプ121により印加される電圧よりも高く設定されているので、メインMOSトランジスタTr1のドレイン電流は大きくなる。このため、時刻  $t_4$ において、IGBT200のゲート電流は急激に上昇する。すなわち、オフ側回路120のドライブ能力が大きくなる。これによって、IGBT200のゲート電荷が急速に引き抜かれてゲート電圧はゼロとなる。すなわち、IGBT200のオフ動作が完了する。なお、次にIGBT200をオンする場合には、ドライブ能力切替スイッチSW2をオンからオフに遷移させてから、オン側回路110を駆動させる。

30

【0039】

時刻  $t_4$ 以降も、ドライブ能力切替スイッチSW2はオン状態を維持しているので、IGBT200のゲート-エミッタ間を低インピーダンスで短絡し続けることができる。したがって、IGBT200がオフ状態において、ノイズ等によって誤ってオンすることを抑制することができる。すなわち、確実なオフ保持が可能となる。

【0040】

なお、オペアンプ121に接続された参照電源123の参照電位  $V_{ref}$  を小さくすることによってセンスMOSトランジスタTr2のドレイン電流を大きくし、オフ側回路120のドライブ能力を向上させることでもオフ保持は可能である。しかしながら、オフ保持にはオフ側回路120の出力電流の精度が求められることと、ドライブ能力切替スイッチSW1, SW2の切り替えによるドライブ能力の切り替えのほうが、切り替えの応答速度を早くすることができる。

40

【0041】

また、オフ保持に用いられるドライブ能力切替電源125の電圧としては、IGBT200をオフするために十分な電圧が設定されるので、オペアンプ121の出力に比べて十分大きな電圧となる。この電圧は精度よく制御される必要がないため、複雑な回路を必要としない。よって、本実施形態における駆動装置100は、第1実施形態に較べて回路規模をさほど大きくすることなく実現することができる。

50

## 【0042】

## (第3実施形態)

本実施形態に係る駆動装置100は、図5に示すように、第2実施形態における要素に加えて保護回路130を備えている。

## 【0043】

まず、図5を参照して、本実施形態に係る駆動装置100の構成要素について説明する。

## 【0044】

保護回路130は、保護用MOSトランジスタTr3と、保護用MOSトランジスタTr3にドレイン電流を供給する定電流回路P1, P2と、定電流回路P1, P2から保護用MOSトランジスタTr3への電流供給を制御する保護スイッチSW3, SW4と、IGBT200のコレクタ電流をセンスエミッタ端子SEの電流により検出するコレクタ電流検出部140と、を有している。

10

## 【0045】

保護用MOSトランジスタTr3のゲートは、スイッチSW5を介して、オフ側回路120のメインMOSトランジスタTr1のゲートに接続されており、メインMOSトランジスタTr1に対してカレントミラーを構成している。このため、保護用MOSトランジスタTr3のドレイン電流を制御することにより、センスMOSトランジスタTr2の駆動を介さず、メインMOSトランジスタTr1のドレイン電流を制御することができる。換言すれば、オフ側回路120に構成されたセンス電流制御回路(オペアンプ121、基準抵抗122および参照電源123から構成される回路)に依らず、IGBT200のゲート電流を制御することができる。

20

## 【0046】

定電流回路P1は、保護スイッチSW3を介して保護用MOSトランジスタのドレインに接続されている。また、定電流回路P2は、保護スイッチSW4を介して、保護用MOSトランジスタTr3のドレインに対して定電流回路P1と並列に接続されている。定電流回路P1およびP2の供給する電流は、それぞれ異なる電流値に設定され、保護スイッチSW3, SW4を切り替えることによって保護用MOSトランジスタTr3に異なるドレイン電流を供給できるようになっている。また、定電流回路P1およびP2の供給する電流は、センスMOSトランジスタTr2に通常流れるドレイン電流よりも小さい値が設定されている。なお、本実施形態では、定電流回路P2の電流値が定電流回路P1の電流値よりも小さく設定されている。

30

## 【0047】

コレクタ電流検出部140は、IGBT200のコレクタ電流を検出して、過電流あるいは負荷300の短絡からIGBT200を保護する回路である。この電流検出部140は、コンパレータ141, 142と、コンパレータ141, 142の入力端子Aに閾値となる電圧を与える電圧源143, 144と、IGBT200のコレクタ電流を電圧に変換するための抵抗器R1とを有している。

## 【0048】

より詳しく説明する。図5に示すように、コンパレータ141の一方の入力端子Aには電圧源143が接続されている。そして、他方の入力端子Bは、IGBT200のセンスエミッタ端子SEとGNDとの間に接続された抵抗器R1との中間点に接続されている。すなわち、コンパレータ141における入力端子Bには、IGBT200のセンスエミッタ端子SEからGNDに向かって流れる電流と抵抗器R1の抵抗値に対応した電圧が印加されている。入力端子Bに印加される電圧は、センスエミッタ端子SEからGNDに向かって流れる電流に比例する。つまり、この電圧はIGBT200のコレクタ電流が大きくなるほど高電圧となる。

40

## 【0049】

コンパレータ141は、センスエミッタ端子SEを流れる電流に対応した電圧が、電圧源143の電圧を超えた場合、すなわち、コレクタ電流が所定の閾値(過電流検出用の閾

50

値)を超えた場合に、過電流フィルタ回路131を介して保護スイッチSW3およびスイッチSW5をオンするように信号を出力する。

【0050】

コンパレータ142についても、コンパレータ141と同様の構成である。すなわち、コンパレータ142の一方の入力端子Aには電圧源144が接続されている。そして、他方の入力端子Bは、IGBT200のセンスエミッタ端子SEとGNDとの間に接続された抵抗器R1との中間点に接続されている。

【0051】

そして、コンパレータ142は、センスエミッタ端子SEを流れる電流に対応した電圧が、電圧源144の電圧を超えた場合、すなわち、コレクタ電流が所定の閾値(短絡検出用の閾値)を超えた場合に、短絡フィルタ回路132を介して保護スイッチSW4およびスイッチSW5をオンするように信号を出力する。

【0052】

電圧源143はIGBT200にとって過電流と判断されるような電圧が設定されている。また、電圧源144は負荷300が短絡したと判断されるような電圧が設定されている。つまり、電圧源144の電圧は、電圧源143の電圧よりも高く設定されている。

【0053】

なお、フィルタ回路(131, 132)とは、予め設定されたフィルタ時間内において、入力された情報がある状態を維持した場合に、入力に対応した信号を出力する回路である。例えば、コレクタ電流検出部140によって、過電流検出用の閾値を超えたコレクタ電流が、過電流フィルタ回路131に設定された所定のフィルタ時間以上検出された場合に、保護スイッチSW3とスイッチSW5をオンする。また、例えば、コレクタ電流検出部140によって、短絡検出用の閾値を超えたコレクタ電流が、短絡フィルタ回路132に設定された所定のフィルタ時間以上検出された場合に、保護スイッチSW4とスイッチSW5をオンする。

【0054】

このフィルタ回路(131, 132)は、IGBT200のコレクタ電流におけるパルスノイズ等によって、保護回路130が動作することを防止するために設けられている。

【0055】

次に、本実施形態に係る駆動装置100の動作および作用効果について説明する。

【0056】

例えば、IGBT200に通常よりも過大なコレクタ電流(過電流)が流れているとする。過電流のため、コレクタ電流検出部140のコンパレータ141の入力端子Bの電位は入力端子Aの電位よりも高くなり、コンパレータ141はその旨を過電流フィルタ回路131に出力する。過電流の状態が、過電流フィルタ回路131に予め設定されたフィルタ時間だけ継続すると、過電流フィルタ回路131は、ドライブ能力切替スイッチSW1, SW2をオフにしつつ、保護スイッチSW3とスイッチSW5をオンする。

【0057】

これにより、保護用MOSトランジスタTr3には、定電流回路P1により規定されたドレイン電流が流れる。そして、保護用MOSトランジスタTr3とカレントミラーを構成するメインMOSトランジスタTr1にもミラーされたドレイン電流が流れる。定電流回路P1の電流値は、センスMOSトランジスタTr2に通常流れるドレイン電流よりも小さい値が設定されているため、オフ側回路120の出力電流がセンスMOSトランジスタTr2のドレイン電流により制御される場合に較べて、ドライブ能力を低下させることができる。

【0058】

IGBT200のコレクタ電流が過電流の状態では、ターンオフ時にコレクタ電圧Vceに大きなサージが発生し、IGBT200の破壊の可能性が高まる。そこで、オフ側回路120のドライブ能力を低下させておくことによってサージ電圧を小さくし、IGBT200を安全に遮断して保護することができる。

10

20

30

40

50

## 【0059】

一方、負荷300が短絡し、IGBT200に過電流よりも大きなコレクタ電流が流れているとする。短絡のため、コレクタ電流検出部140のコンパレータ142の入力端子Bの電位は入力端子Aの電位よりも高くなり、コンパレータ142はその旨を短絡フィルタ回路132に出力する。短絡の状態が、短絡フィルタ回路132に予め設定されたフィルタ時間だけ継続すると、短絡フィルタ回路132は、ドライブ能力切替スイッチSW1, SW2をオフにしつつ、保護スイッチSW4とスイッチSW5をオンする。

## 【0060】

これにより、保護用MOSトランジスタTr3には、定電流回路P2により規定されたドレイン電流が流れる。定電流回路P2の電流値は定電流回路P1の電流値よりも小さく設定されているから、過電流の場合よりもさらにドライブ能力を低下させることができ、サージ電圧を抑制することができる。

10

## 【0061】

なお、短絡フィルタ回路132に予め設定されたフィルタ時間は、過電流フィルタ回路に設定されたフィルタ時間よりも短く設定しておくことが好ましい。これによれば、短絡時のコレクタ電流は、過電流時よりもその電流値が大きいため、IGBT200を短い時間でオフすることによって、IGBT200のストレスを軽減することができるためである。また、通常動作時に、スイッチング時のノイズ等で、誤って過電流や短絡保護がかからないよう、最低限のフィルタ時間は必要である。

## 【0062】

20

## (その他の実施形態)

以上、本発明の好ましい実施形態について説明したが、本発明は上記した実施形態になんら制限されることなく、本発明の主旨を逸脱しない範囲において、種々変形して実施することが可能である。

## 【0063】

上記した各実施形態では、パワースイッチング素子としてIGBT200を例示したが、この例に限定されない。例えば、パワースイッチング素子として、パワーMOSトランジスタ等についても本発明を適用することができる。

## 【0064】

また、参照電位Vrefは、予め測定されたパワースイッチング素子のゲート容量に対応した値に設定されることが好ましい。図示しないが、駆動装置100にメモリ回路を設け、駆動装置100の出荷前検査（製造後に行われる特性検査）において測定されたゲート容量に対応した参照電位をメモリに記憶するようにする。具体的には、ゲート容量が大きいほど参照電位Vrefの値を小さく設定し、オフ側回路120のドライブ能力を大きくさせておくことにより、IGBT200のゲート容量の製造ばらつきを抑制することができる。したがって、IGBT200のスイッチング損失のばらつきを低減することができる。

30

## 【0065】

また、第2実施形態において、ドライブ能力切替電源125の電圧が、オペアンプ121から出力される電圧よりも高く設定された例、すなわち、ドライブ能力切替電源125とドライブ能力切替スイッチSW2がオフ保持回路を構成する例について示した。これに対して、ドライブ能力切替電源125の電圧をオペアンプ121から出力される電圧よりも低く設定することもできる。この場合、ドライブ能力切替電源125とドライブ能力切替スイッチSW2は、オフ側回路120のドライブ能力を抑制する回路として機能する。

40

## 【符号の説明】

## 【0066】

100・・・駆動装置

110・・・オン側回路

120・・・オフ側回路

130・・・保護回路

50

1 4 0 . . . コレクタ電流検出部

2 0 0 . . . パワースイッチング素子 ( I G B T )

T r 1 . . . メインM O Sトランジスタ

T r 2 . . . センスM O Sトランジスタ

S W 1 , S W 2 . . . ドライブ能力切替スイッチ

【図 1】

【図 3】

【図 2】

【図4】

【図5】

---

フロントページの続き

(56)参考文献 特開2014-54019(JP, A)

特許第4954290(JP, B2)

特開2000-228868(JP, A)

特開2012-129978(JP, A)

(58)調査した分野(Int.Cl., DB名)

H02M 1/08

H03K 17/08