(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2006-121088

(P2006-121088A)

(43) 公開日 平成18年5月11日(2006.5.11)

(51) Int.C1.

HO5K 1/16 (2006.01)

F 1

HO5K 1/16

HO5K 1/16

テーマコード(参考)

B

4 E 3 5 1

E

審査請求 未請求 請求項の数 15 O L (全 11 頁)

(21) 出願番号 特願2005-303552 (P2005-303552)

(22) 出願日 平成17年10月18日 (2005.10.18)

(31) 優先権主張番号 10/967,569

(32) 優先日 平成16年10月18日 (2004.10.18)

(33) 優先権主張国 米国(US)

(71) 出願人 390023674

イー・アイ・デュポン・ドウ・ヌムール・

アンド・カンパニー

E. I. DU PONT DE NEMO

URS AND COMPANY

アメリカ合衆国、デラウェア州、ウイルミ

ントン、マーケット・ストリート 100

7

(74) 代理人 100077481

弁理士 谷 義一

(74) 代理人 100088915

弁理士 阿部 和夫

最終頁に続く

(54) 【発明の名称】容量性/抵抗性デバイスおよびそのようなデバイスを組み込むプリント配線板、ならびにその作製の方法

## (57) 【要約】

【課題】抵抗性機能と容量性機能を共に提供する容量性/抵抗性デバイスを提供すること。

【解決手段】この容量性/抵抗性デバイスは、プリント配線板の層内に埋め込むことができる。容量性/抵抗性デバイスを埋め込むことにより、基板表面積が保存され、はんだ接続の数が低減され、それによって信頼性が高まる。

【選択図】図3

## 【特許請求の範囲】

## 【請求項 1】

第 1 の電極と、

前記第 1 の電極を覆って配置された誘電体と、

前記誘電体上で、前記誘電体に隣接して形成された抵抗要素と、

導電性トレースと、

前記誘電体を覆って配置された、前記抵抗要素と電気接觸する第 2 の電極とを備えた容量性／抵抗性デバイスであって、前記誘電体が、前記第 1 の電極と前記第 2 の電極の間に配置されることを特徴とするデバイス。

## 【請求項 2】

前記抵抗要素は、前記第 2 の電極と前記導電性トレースとの間に、それらを部分的に覆って延びることを特徴とする請求項 1 に記載の容量性／抵抗性デバイス。

## 【請求項 3】

前記抵抗要素は、前記第 2 の電極と前記導電性トレースとの間に間隙を跨いで延び、前記誘電体と当接することを特徴とする請求項 2 に記載の容量性／抵抗性デバイス。

## 【請求項 4】

前記誘電体は、フィラーなしのポリマーを含むことを特徴とする請求項 1 に記載の容量性／抵抗性デバイス。

## 【請求項 5】

前記誘電体は、誘電機能相で充填されたポリマーを含むことを特徴とする請求項 1 に記載の容量性／抵抗性デバイス。

## 【請求項 6】

少なくとも 2 つの有機誘電ラミネート層内に埋め込まれ、前記ラミネート層および前記容量性／抵抗性デバイスは、ラミネート構造を形成することを特徴とする請求項 1 に記載の容量性／抵抗性デバイス。

## 【請求項 7】

少なくとも 1 つの請求項 6 に記載のラミネート構造と、

プリント配線板の上面に配置された少なくとも 1 つの I C デバイスであって、前記容量性／抵抗性デバイスに電気的に結合される I C デバイスと

を備えたことを特徴とするプリント配線板。

## 【請求項 8】

第 1 の金属箔および第 2 の金属箔を設けるステップと、

前記第 1 と第 2 の金属箔との間で誘電体を形成するステップと、

前記第 1 の金属箔から第 1 の電極を形成するステップと、

前記第 2 の金属箔から第 2 の電極および導電性トレースを形成するステップと、

前記誘電体に隣接する、かつ前記第 2 の電極および前記導電性トレースと電気接觸する抵抗要素を形成するステップと

を備えたことを特徴とする容量性／抵抗性デバイスを作製する方法。

## 【請求項 9】

第 1 の金属箔および第 2 の金属箔を設けるステップと、

前記第 1 の金属箔および前記第 2 の金属箔をエッティングし、前記第 1 および第 2 の電極を形成するステップと

をさらに備えたことを特徴とする請求項 8 に記載の方法。

## 【請求項 10】

前記抵抗要素を形成するステップは、前記誘電体を覆って、前記第 2 の電極に当接して抵抗材料を堆積するステップを含むことを特徴とする請求項 9 に記載の方法。

## 【請求項 11】

前記誘電体を形成するステップは、フィラー入り、またはフィラーなしのポリマー溶液のうち少なくとも 1 つで、前記第 1 または第 2 の金属箔のうち少なくとも 1 つを覆ってキャスティングするステップを含むことを特徴とする請求項 10 に記載の方法。

10

20

30

40

50

## 【請求項 1 2】

前記誘電体を形成するステップは、フィラー入り、またはフィラーなしのポリマーの別個の膜を形成するステップと、前記膜を前記第1および第2の金属箔に積層するステップとを含むことを特徴とする請求項11に記載の方法。

## 【請求項 1 3】

請求項8に記載の方法によって形成された少なくとも1つの容量性／抵抗性デバイスを、少なくとも2つの有機誘電ラミネート層間に埋め込むステップを備えたことを特徴とするラミネート構造を作製する方法。

## 【請求項 1 4】

少なくとも1つの請求項13に記載のラミネート構造を設けるステップと、

プリント配線板の上面に配置された、前記容量性／抵抗性デバイスに電気的に結合される少なくとも1つのICデバイスを設けるステップと

を備えたことを特徴とするプリント配線板を作製する方法。

## 【請求項 1 5】

第1の金属箔および第2の金属箔を設けるステップと、

前記第1の金属箔を覆ってポリイミド誘電体を形成するステップと、

前記第1の金属箔から第1の電極を形成するステップと、

第1の誘電層を前記第1の電極の側部に積層するステップと、

前記第2の金属箔から第2の電極および導電性トレースを形成するステップであって、

前記第2の電極および前記導電性トレースが、前記誘電体を覆って配置されるステップと

、

前記ポリイミド誘電体を覆って、前記第2の電極と電気接觸する抵抗要素をプリントするステップであって、前記誘電体が、前記第1の電極と前記第2の電極との間に配置されるステップと、

第2の誘電層を前記第2の電極および前記抵抗要素に積層するステップと

を備えたことを特徴とするラミネート構造を作製する方法。

## 【発明の詳細な説明】

## 【技術分野】

## 【0001】

本技術分野は、容量性機能および抵抗性機能を共に有するデバイスと、そのようなデバイスを有機誘電ラミネートおよびプリント配線板内に組み込む方法とに関する。

## 【背景技術】

## 【0002】

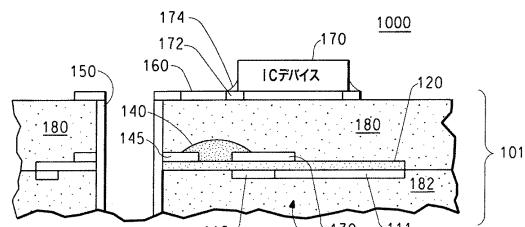

コンデンサおよび抵抗は、集積回路( IC )デバイス間に延びる信号トレースの伝送ライン終端用として直列で使用することができる。コンデンサおよび抵抗は、ICデバイスのインピーダンスをラインに対して整合させるために、または信号反射を低減する、もしくはなくすために使用される。いくつかの回路は連続負荷であり、抵抗をラインと並列で使用する。非連続負荷回路は、抵抗およびコンデンサが直列に接続され、低電力ICに有用である。図1は、従来技術を形成するICデバイス10および20の非連続負荷終端の概略図である。

## 【0003】

図1では、aからbの距離は、一般に短い。抵抗Rの値は、ラインインピーダンスに整合するように選ばれ、一般に約45～80オームである。コンデンサCの値は、直列の抵抗RとコンデンサCとのRC時定数が、信号の立ち上り時間より大きく、信号パルスの合計時間より小さくなるように選ばれる。典型的な静電容量値は、30ピコファラド程度である。

## 【発明の開示】

## 【発明が解決しようとする課題】

## 【0004】

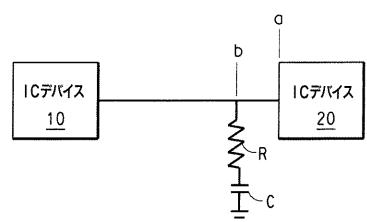

従来のRC終端は、一般に表面実装技術(SMT)抵抗／コンデンサで構築される。図

2は、I Cデバイス30に接続されたS M T抵抗40およびS M Tコンデンサ50を有し、I C30用に従来のS M T R C伝送ライン終端を形成するプリント回路板25の一部分の横断面図である。I C30に信号を搬送する信号ラインは、I Cデバイス30を抵抗40に接続する回路トレース60に接続される。コンデンサ50は、1対のはんだパッド52および1対のはんだ継手58の一方によって回路トレース70に結合される。抵抗40は、はんだパッド42とはんだ継手48によって回路トレース70に結合される。コンデンサ50は、他方のはんだパッド58と回路トレース59によってバイアホール80に結合される。この構成は、信号ラインと直列で、めっきスルーホールバイア80を介して接地された抵抗40とコンデンサ50を配置する。この従来の表面実装手法は、貴重な表面積の使用を必要とする。さらに、はんだ継手に対する要件により、信頼性が低下し、作製コストが増大する。

10

【課題を解決するための手段】

【0 0 0 5】

第1の実施態様によれば、容量性/抵抗性デバイスが、第1の電極と、第1の電極を覆って配置された誘電体と、誘電体上で、誘電体に隣接して形成された抵抗要素と、導電性トレースと、誘電体を覆って配置された、抵抗要素と電気接触する第2の電極とを備える。容量性/抵抗性デバイスは、有機誘電ラミネート内に埋め込み、プリント配線板内に組み込むことができる。

【0 0 0 6】

上記の実施態様によれば、抵抗機能とコンデンサ機能とを共に单一の埋込みラミネート内に一体化し、抵抗機能およびコンデンサ機能を生み出す際にコストと難点を低減することができる。容量性/抵抗性デバイスがプリント配線板内に組み込まれるとき、容量性/抵抗性デバイスを埋め込むことによって貴重な表面積もまた解放される。さらに、S M Tデバイスに関連するはんだ継手をなくし、それによって信頼性を改善することができる。この容量性/抵抗性デバイスは、従来のエッチングプロセスを使用して処理し、さらに生産コストを削減することができる。

20

【0 0 0 7】

当業者なら、諸実施態様の以下の詳細な説明を読めば、上述の利点、ならびに本発明の様々な追加の実施態様の他の利点および利益を理解するであろう。

【0 0 0 8】

30

詳細な説明は、同様の数字が同様の要素を指す以下の図面を参照することになる。

【発明を実施するための最良の形態】

【0 0 0 9】

本発明の諸実施形態は、プリント配線板(P W B)の基板内に埋めることができる容量性/抵抗性デバイスを対象とする。P W B基板内に容量性機能および抵抗性機能を設けることにより、プリント配線板上の貴重な表面積が保存される。また、本発明の諸実施形態は、従来のS M T終端構成ほどはんだ継手を必要としない。

【0 0 1 0】

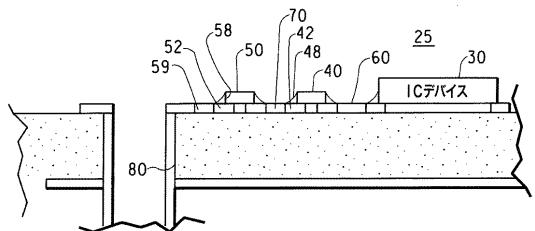

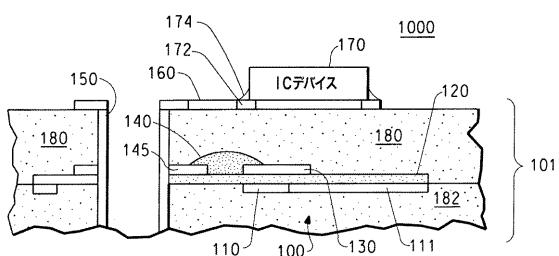

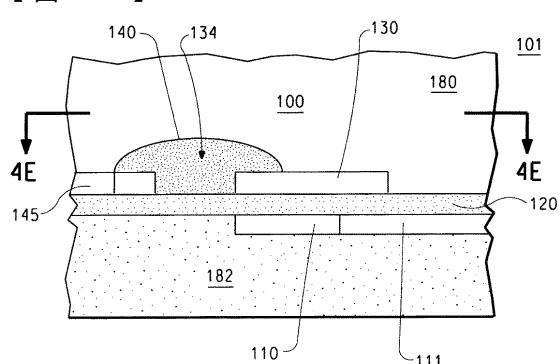

図3は、プリント配線板1000の一部分の第1の実施形態の断面図である。プリント配線板断面1000は、抵抗機能およびコンデンサ機能が単一の容量性/抵抗性デバイス100内に統合されているR C伝送ライン終端を含む。デバイス100は、プリント配線板断面1000内に埋め込まれる。デバイス100は、底部電極110、誘電体120、頂部電極または頂部プレート130、抵抗要素140、導電性トレース145を備える。デバイス100は、中括弧101によって全体的に示される単一のラミネート構造内に抵抗性機能および容量性機能を設ける。

40

【0 0 1 1】

デバイス100は、誘電層180、182を介して延びるめっきスルーホールバイア150と、導電性回路トレース160とによって、I Cデバイス170に結合される。I Cデバイス170は、はんだパッド172とはんだ継手174によって導電性回路トレース160に接続される。しかし、他の接続技術を使用することもできる。底部電極110は

50

、プリント配線板内の導電性グランドプレーンとしても働くことができ、他の回路に接続する導電性回路トレース 111 に結合することができる。

【0012】

図 4 A ~ 4 F は、デバイス 100 を含めて、コンデンサラミネートを作製する方法を示す。

【0013】

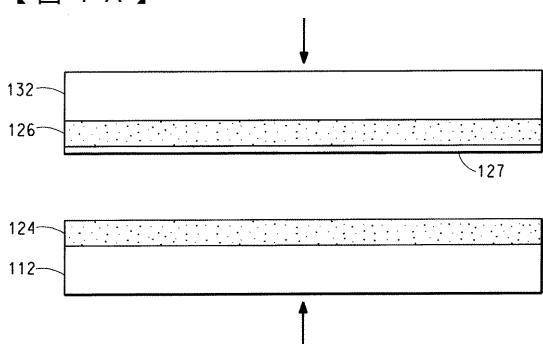

図 4 A は、第 1 および第 2 の金属箔 112、132 が設けられる製造の第 1 段階の正面断面図である。箔 112、132 は、たとえば、銅、銅を主成分とする材料、および他の金属から作ることができる。スラリー材料または溶液を第 1 の箔 112 上にキャスティングまたは被覆し、乾燥および硬化させ、第 1 の誘電層 124 を形成することができる。硬化は、スラリーが熱可塑性のものである場合、たとえば 150 °C で乾燥することによって行うことができる。スラリーが熱硬化性材料である場合、より高い硬化温度を使用することができる。同様の第 2 の誘電層 126 が、第 2 の箔 132 上で同様の形で形成される。

【0014】

誘電層 124、126 を形成するために使用される溶液は、たとえば、溶媒内で溶解されたポリマーを含むことができる。スラリー材料は、高誘電率 (ハイ K) フィラーまたは機能相を有するポリマー溶媒溶液を含むことができる。スラリーまたは溶液として好適なポリマーは、たとえば、エポキシ樹脂またはポリイミド樹脂を含むことができる。ハイ K 機能相は、500 を超える誘電率を有する材料として定義されることができ、一般式  $A B O_3$  のペロブスカイトを含むことができる。好適なフィラーには、たとえば、結晶性チタン酸バリウム (BT)、チタン酸バリウム・ストロンチウム (BST)、チタン酸ジルコン酸鉛 (PZT)、チタン酸ランタン鉛、チタン酸ジルコン酸ランタン鉛 (PLZT)、ニオブ酸マグネシウム鉛 (PMN)、チタン酸カルシウム銅が含まれる。フィラーは、粉末形態とすることができます。

【0015】

(図 4 A では誘電層 126 上で示されている) 一方または両方の誘電層 124、126 の表面に、薄い接着層 127 を被着させることができる。接着層 127 は、熱可塑性ポリマーから形成することができ、誘電率が薄まるのを回避するために高誘電相で充填することができる。次いで、2 つの構造は、図 4 A で矢印によって示されている方向で熱と圧力を受けて、共に積層される。

【0016】

図 4 B を参照すると、積層により、層 124、126、127 から単一の誘電体 120 が形成される。接着層 127 は、積層プロセス中に誘電層 124 および 126 の接合を容易にする。しかし、接着層 127 は、誘電層 124 および 126 が積層前に部分的に硬化されるにすぎず、あるいは熱可塑性のものであり、それにより、積層したとき適切な温度と圧力により樹脂が十分軟化し、その結果、層 124 および 126 が接着剤なしで接着する場合、省略することができる。得られる誘電体 120 は、たとえば、積層後 4 ~ 25 ミクロン程度の薄い層とすることができます。

【0017】

誘電体 120 を形成する代替の方法は、フィラー入り (filled)、またはフィラーなしの (unfilled) 热可塑性ポリマーを箔 112、132 の一方上にキャスティングすること、および他方の箔をフィラー入り熱可塑性ポリマーに直接積層することとすることができる。この方法は、接着層を不要にする。他の代替の製造方法は、誘電層 120 を単一の膜として別々に形成し、熱と圧力を使用して、第 1 の箔 112 および第 2 の箔 132 に積層することを含む。

【0018】

たとえば (デラウェア州ウィルミントンの DuPont Electronic Technologies より入手可能な) ポリイミド誘電体 INTEGRA (商標) HK04 など、フィラーなしのポリマーを使用し、誘電体 120 を形成することができる。

【0019】

10

20

30

40

50

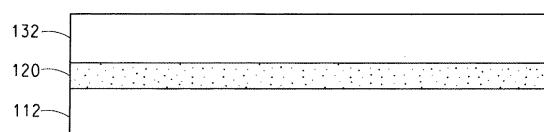

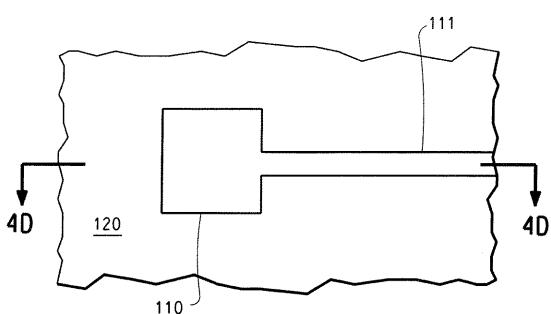

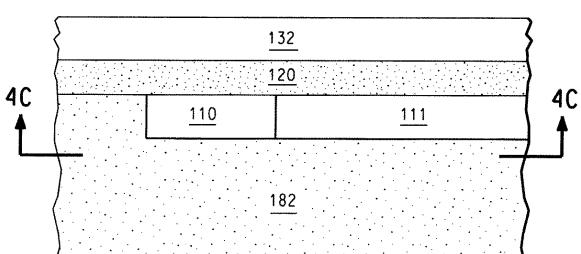

積層後、標準的な配線板プリント処理条件を使用して、(図4Bには示されていない)フォトレジストが箔112に被着され、箔112がイメージングおよびエッチングされ、残りのフォトレジストが剥離される。図4Cは、図4Dの線4C-4C上で取られた、エッティング後の得られるものの底部断面図である。図4Cを参照すると、エッティングにより、デバイス100の底部電極110ができる。底部電極110を接地または他の回路に接続するために、導電性回路トレース111もまた箔112から形成することができる。

#### 【0020】

図4Dは、図4Cの線4D-4D上で取られた正面断面図である。図4Dを参照すると、得られる物品の底部電極110側は、誘電ラミネート材料182に積層される。積層は、標準的な配線板プリントプロセスにおいて、たとえば、FR4プリプレグまたは他のプリプレグを使用して行うことができる。

10

#### 【0021】

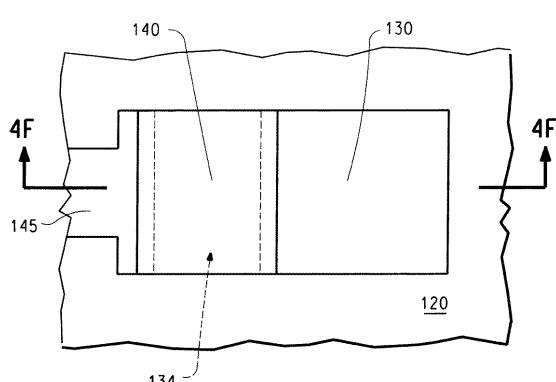

(図4Dには示されていない)フォトレジストが箔132に被着され、箔132がイメージングおよびエッチングされ、残りのフォトレジストが剥離される。図4Eは、図4Fの線4E-4E上で取られた、エッティング後の得られる物品の頂部断面図である。図4Fは、図4Eの線4F-4F上で取られた、得られる物品の正面断面図である。図4Eを参照すると、エッティングにより、デバイス100の頂部電極130、間隙134、導電性回路トレース145ができる。

20

#### 【0022】

図4Fを参照すると、誘電体120を覆って間隙134内に抵抗材料を堆積することによって、抵抗要素140が形成される。抵抗要素140は、たとえば、ポリマー厚膜抵抗ペーストを堆積し、その抵抗ペーストを硬化させることによって形成することができる。頂部電極130および導電性回路トレース145は、抵抗要素140用の終端として働く。ポリマー厚膜抵抗ペーストは、たとえば、スクリーン印刷用溶剤内に分散された炭素粉末など、諸材料から作ることができる。スクリーン印刷用溶剤は、たとえば、適切な溶媒内で溶解されたエポキシ樹脂を含むことができる。界面活性剤など他の添加剤を追加し、得られる抵抗要素140の誘電特性を修正することができる。

20

#### 【0023】

抵抗要素140を硬化させた後で、誘電層180が誘電層182の構成部品側に積層され、ラミネート構造101を形成する。次いで、上記のプロセスから得られるラミネート構造101は、たとえば、従来の積層を使用して、また形成プロセスを介して、図3に示されているプリント配線板内に組み込むことができる。

30

#### 【0024】

##### (実施例1)

デバイス100のこの実施例は、図3を参照して論じられる。この実施例では、電極110、130は銅箔から形成され、誘電体120は、誘電率(Dk)3.5を有する厚さ25ミクロンのフィラーなしのポリイミド誘電体であり、それによって1平方インチ(6.4516 cm<sup>2</sup>)当たり800ピコファラドの静電容量密度を生み出す(デラウェア州ウィルミントンのDuPont Electronic Technologiesより入手可能なINTERRA(商標)HK04)。

40

#### 【0025】

30ピコファラドの伝送ライン終端に必要とされるコンデンサのサイズは、(平面図で見たとき)24.2 mm<sup>2</sup>であり、これは5 mm × 5 mmよりわずかに小さいものに対応する。堆積される抵抗材料は、(DuPont Electronicsより入手可能な)スクリーン印刷可能な100 / sqポリマー厚膜抵抗ペーストである。

40

#### 【0026】

抵抗公称60オーム用の、この実施例における抵抗のサイズは、好ましくは長さ対幅比を約0.6~1.0の範囲内で維持して変えることができる。上記のコンデンササイズは、ICに必要とされる終端抵抗が比較的少ない場合、許容される。大量の終端が必要とされる場合には、より高い静電容量密度を有するラミネートのほうが、コンデンサをより小

50

さくすることができるため、より望ましい。

【0027】

(実施例2)

デバイス100の実施例2は、図3を参照して論じられる。この実施例2では、チタン酸バリウムで充填された熱可塑性ポリイミドを銅箔上でキャスティングし、第2の銅箔を、チタン酸バリウムで充填された熱可塑性ポリイミド被覆の表面上に積層することによって、ラミネートが形成される。チタン酸バリウムは、容易に入手可能であり、無鉛であるため、フィラーとして有利である。

【0028】

積層は、別個の接着材料を使用することなしに物品同士が接着するように、適切な温度と圧力で行われる。電極110、130は銅箔から形成され、誘電体120は、誘電率(Dk)1.1を有する厚さ14ミクロンのフィラー入りポリイミド誘電体であり、それによって1平方インチ(6.4516cm<sup>2</sup>)当たり4.5ナノファラドの静電容量密度を生み出す(DuPont Electronic Technologiesより入手可能なINTERRA(商標)HK11)。

【0029】

上述の伝送ライン終端に必要とされるコンデンサのサイズは、4.3mm<sup>2</sup>、または約2mm×2mmである。堆積される抵抗は、(DuPont Electronicsより入手可能な)スクリーン印刷型100/sqポリマー厚膜抵抗ペーストである。

【0030】

抵抗公称60オーム用の、この実施例2における抵抗の好ましいサイズは、長さ対幅縦横比0.6対1.0を有して、長さ1.2mm、幅2mmである。

【0031】

(実施例3)

デバイス100のこの実施例3は、図3を参照して論じられる。この実施例3では、ラミネートは、(DuPont Electronic Technologiesより入手可能な)チタン酸バリウムで充填された熱可塑性ポリイミドを2枚の銅箔上でキャスティングし、適切な温度と圧力でそれらを共に積層し共に接着することによって作られる。別個の接着材料は使用されない。電極110、130は、銅箔から形成される。得られる誘電体120は、1平方インチ(6.4516cm<sup>2</sup>)当たり6.2ナノファラドの静電容量密度を有する厚さ8ミクロンの、チタン酸バリウムで充填されたポリイミド誘電体である。

【0032】

上述の伝送ライン終端に必要とされるコンデンサのサイズは、3.1mm<sup>2</sup>、または約1.77mm×1.77mmである。堆積される抵抗は、(DuPont Electronicsより入手可能な)スクリーン印刷型100/sqポリマー厚膜抵抗ペーストから形成することができる。

【0033】

この実施例における抵抗公称60オーム用の抵抗の好ましいサイズは、長さ対幅縦横比0.6対1.0を有して、長さ1.06mm、幅1.77mmとなることになる。

【0034】

上記の諸実施形態によれば、抵抗と組み合わせた薄いコンデンサラミネート構造を使用し、埋込みコンデンサ機能のサイズを削減する、またSMT伝送ライン終端をより効果的に埋めることができる。コンデンサ機能および抵抗機能を埋め込むことにより、貴重な基板表面積が解放され、SMTデバイスに関連するはんだ継手がなくなり、それによって信頼性が改善される。さらに、ラミネート内で抵抗と静電容量を組み合わせるラミネートは、従来のエッチングプロセスを使用して処理することができ、これにより生産コストが削減される。

【0035】

また、上記の諸実施形態は、回路設計者およびPWB作製者に他のオプションを提供す

10

20

30

40

50

る。たとえば、1枚のラミネートを使用し、ディスクリート抵抗およびディスクリートコンデンサを埋め込むことができ、これにより、抵抗とコンデンサとを接続することに関連するインダクタンスが低減される。

【0036】

上記の諸実施形態によれば、抵抗と組み合わせた薄いコンデンサラミネート構造を使用して、埋込みコンデンサ機能のサイズを削減し、かつRC伝送ライン終端をより効果的に埋めることができる。コンデンサ機能および抵抗機能を埋め込むことにより、貴重な基板表面積が解放され、SMTデバイスに関連するはんだ継手がなくなり、それによって信頼性が改善される。さらに、ラミネート内で抵抗と静電容量を組み合わせるラミネートは、従来のエッティングプロセスを使用して処理することができ、これにより生産コストが削減される。

【0037】

また、上記の諸実施形態は、回路設計者およびPWB作製者に他のオプションを提供する。たとえば、1枚のラミネートを使用し、多数のディスクリート抵抗および多数のディスクリートコンデンサを埋め込むことができ、これにより、抵抗とコンデンサとを接続することに関連するインダクタンスが低減される。

【0038】

平面図におけるコンデンサ実施形態の形状は、概して矩形である。しかし、コンデンサ電極、誘電体、ならびに他の構成部品および層は、たとえば円形、細長いもの（oblong）、楕円（oval）、または多角形など、他の規則的または不規則な表面領域形状を有することができる。

【0039】

単一の容量性／抵抗性デバイス100が上述のラミネート構造101内で形成される。しかし、パネル構造およびプリント配線板は、種類および構成の異なる多数の個々の容量性／抵抗性デバイスを含むことができる。

【0040】

上記の実施形態では、抵抗、静電容量、インダクタンスが組み合わさって、一般に大文字Zによって識別される固有回路インピーダンスを生み出す。抵抗と静電容量とは、ある固有インピーダンスを達成するように構造化することができる。抵抗、静電容量、または両方を変更することにより、インダクタンスが変更されることになる。3つの変更すべてを制御し、最終的なインピーダンスを規定することができる。換言すれば、ラミネートのインピーダンスは「調整可能」である。

【0041】

本発明の前述の説明は、本発明について例示し、述べている。さらに、本開示は、本発明の選択された好ましい実施形態について述べているに過ぎず、本発明は、様々な他の組合せ、修正、環境で使用することができる、上記の教示に対応する、本明細書で述べられている発明性のある概念の範囲内で、かつ／または関連技術の技量または知識内で、変更または修正が可能であることを理解されたい。

【0042】

さらに、上述の諸実施形態は、本発明を実施することについて知られている最良の形態について述べること、また、そのような、または他の実施形態で、また特定の応用例または本発明の使用によって必要とされる様々な修正と共に、当業者が本発明を利用することを可能にすることが意図されている。したがって、本説明は、本発明を本明細書で開示されている形態に限定しないものとする。また、添付の特許請求の範囲は、詳細な説明において明示的に定義されていない代替の諸実施形態を含むように解釈するべきであるものとする。

【図面の簡単な説明】

【0043】

【図1】抵抗およびコンデンサを直列で有する従来（従来技術）の非連続負荷終端の概略図である。

10

20

30

40

50

【図2】集積回路デバイス用の従来（従来技術）のSMT RC伝送ライン終端を有するプリント配線板の横断面図である。

【図3】第1の実施形態による埋込み型容量性／抵抗性デバイスを有するプリント回路板の一部分の断面図である。

【図4A】図3に示されている容量性／抵抗性デバイスを作製する方法を示す図である。

【図4B】図3に示されている容量性／抵抗性デバイスを作製する方法を示す図である。

【図4C】図3に示されている容量性／抵抗性デバイスを作製する方法を示す図である。

【図4D】図3に示されている容量性／抵抗性デバイスを作製する方法を示す図である。

【図4E】図3に示されている容量性／抵抗性デバイスを作製する方法を示す図である。

【図4F】図3に示されている容量性／抵抗性デバイスを作製する方法を示す図である。

10

【符号の説明】

【0044】

|           |               |

|-----------|---------------|

| 25        | プリント回路板       |

| 40        | SMT 抵抗        |

| 42、52、172 | はんだパット        |

| 48、58、174 | はんだ継手         |

| 50        | SMT コンデンサ     |

| 59、60、70  | 回路トレース        |

| 100       | 容量性／抵抗性デバイス   |

| 110       | 底部電極          |

| 111、160   | 導電性回路トレース     |

| 112、132   | 金属箔           |

| 120       | 誘電体           |

| 130       | 頂部電極または頂部プレート |

| 140       | 抵抗要素          |

| 145       | 導電性トレース       |

| 150       | めっきスルーホールバイア  |

| 180、182   | 誘電層           |

20

【図1】

【図2】

【図3】

【図4 A】

【図4 B】

【図4 C】

【図4 E】

【図4 D】

【図4 F】

---

フロントページの続き

(72)発明者 デビッド ロス マクグレゴール

アメリカ合衆国 27539 ノースカロライナ州 アペックス チョッププリンシパー ウェイ

3618

F ターム(参考) 4E351 AA03 AA04 BB01 BB03 BB05 BB30 BB31 CC11 DD04 DD29

DD42 GG20