(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-5556

(P2011-5556A)

(43) 公開日 平成23年1月13日(2011.1.13)

(51) Int.Cl.

**B81B 7/02** (2006.01)

**B81C 1/00** (2006.01)

**H01L 25/00** (2006.01)

**B81C 3/00** (2006.01)

F 1

B 81 B 7/02

B 81 C 1/00

H 01 L 25/00

B 81 C 3/00

テーマコード(参考)

3C081

Z

審査請求 未請求 請求項の数 4 O L (全 18 頁)

(21) 出願番号

特願2009-148670 (P2009-148670)

(22) 出願日

平成21年6月23日 (2009. 6. 23)

(71) 出願人 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 泉 小波

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

(72) 発明者 齋藤 祐美子

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内F ターム(参考) 3C081 AA11 BA22 BA32 BA43 CA03

CA32 EA01

(54) 【発明の名称】半導体装置及びその作製方法

## (57) 【要約】

【課題】厚さの薄い半導体装置を得ることを課題とする。

【解決手段】フレキシブル基板上に、無線通信の機能を有する半導体素子層と、センサの機能を有する微小構造体と、半導体素子層及び微小構造体を電気的に接続する配線とを有する半導体装置、及び、第1の基板上に、互いに密着性の弱い第1の層及び第2の層を形成し、第2の層上に無線通信の機能を有する半導体素子層及び絶縁層を形成し、絶縁層上に半導体素子層と電気的に接続される第1の配線、犠牲層、第2の配線を形成し、第1の層と第2の層とを分離することにより、基板から半導体素子層、絶縁層、第1の配線、犠牲層、第2の配線を分離した後、第2のフレキシブル基板に貼り合わせ、犠牲層を除去して、第1の配線、第2の配線、第1の配線と第2の配線との間に空間を有し、センサの機能を有する微小構造体を作製する半導体装置の作製方法に関する。

【選択図】図2

## 【特許請求の範囲】

## 【請求項 1】

フレキシブル基板上に、

無線通信の機能を有する半導体素子層と、

センサの機能を有する微小構造体と、

前記半導体素子層及び微小構造体を電気的に接続する配線と、

を有することを特徴とする半導体装置。

## 【請求項 2】

フレキシブル基板上に、

無線通信の機能を有する半導体素子層と、

前記半導体素子層上に絶縁層と、

前記絶縁層上に、前記半導体素子層と電気的に接続される配線と、

前記絶縁層及び配線上に、導電性を有する接着材と、

前記導電性を有する接着材上に、センサの機能を有する微小構造体と、

を有し、

前記微小構造体は、前記導電性を有する接着材を介して、前記半導体素子層に電気的に

接続されていることを特徴とする半導体装置。

## 【請求項 3】

第1の基板上に、互いに密着性の弱い第1の層及び第2の層を形成し、

前記第2の層上に、無線通信の機能を有する半導体素子層を形成し、

前記半導体素子層上に、絶縁層を形成し、

前記絶縁層上に、前記半導体素子層と電気的に接続される第1の配線と、犠牲層、第2

の配線を形成し、

前記第1の層と第2の層とを分離することにより、前記基板から、前記半導体素子層、

前記絶縁層、前記第1の配線、前記犠牲層、前記第2の配線を分離し、

前記分離した半導体素子層、絶縁層、第1の配線、犠牲層、第2の配線を、第2のフレ

キシブル基板に貼り合わせ、

前記犠牲層を除去することにより、前記第1の配線、前記第2の配線、前記第1の配線

と第2の配線との間に空間を有し、センサの機能を有する微小構造体を作製することを特

徴とする半導体装置の作製方法。

## 【請求項 4】

第1の基板上に、互いに密着性の弱い第1の層及び第2の層を形成し、

前記第2の層上に、無線通信の機能を有する半導体素子層を形成し、

前記半導体素子層上に、第1の絶縁層を形成し、

前記第1の絶縁層上に、前記半導体素子層と電気的に接続される第1の配線を形成し、

第2の基板上に、互いに密着性の弱い第3の層及び第4の層を形成し、

前記第3の層上に、第2の配線、犠牲層、第3の配線を形成し、

前記第3の層と第4の層とを分離することにより、前記第2の基板から、前記第2の配

線、前記犠牲層、前記第3の配線を分離し、

前記分離された第3の層、第2の配線、犠牲層、第3の配線を、導電性を有する接着材

により、前記第1の配線及び半導体素子層上に貼り合わせ、

前記第1の層と第2の層とを分離することにより、前記第1の基板から、前記半導体素

子層、前記第1の配線、前記導電性を有する接着材、前記第2の配線、前記犠牲層、前記

第3の配線を分離し、

前記分離した半導体素子層、第1の配線、導電性を有する接着材、第2の配線、犠牲層

、第3の配線を、第3のフレキシブル基板に貼り合わせ、

前記犠牲層を除去することにより、前記第2の配線、前記第3の配線、前記第2の配線

と第3の配線との間に空間を有し、センサの機能を有する微小構造体を作製することを特

徴とする半導体装置の作製方法。

## 【発明の詳細な説明】

10

20

30

40

50

**【技術分野】****【0001】**

本明細書に開示される発明は、MEMS (Micro Electro Mechanical System) 技術を用いて形成されるマイクロマシン、そのようなマイクロマシンを有する電気機器に関する。

**【背景技術】****【0002】**

近年、MEMS (Micro Electro Mechanical System) 技術を利用したMEMSスイッチ、またはこれらを備えたセンサ、共振器、通信用デバイスなどが注目されている。なお、これらは、マイクロマシンとも呼ばれている。

10

**【0003】**

またMEMSセンサにより検知した情報を、外部の検出器に送るために、MEMSセンサとRF回路を有する検出装置が開発されている（特許文献1及び特許文献2参照）。

**【先行技術文献】****【特許文献】****【0004】**

【特許文献1】特開2005-353333号公報

【特許文献2】特開2006-29931号公報

**【発明の概要】****【発明が解決しようとする課題】**

20

**【0005】**

しかし、MEMSセンサはシリコン基板を用いて形成することが多いので、薄いMEMSセンサを作るのは難しい。さらに、MEMSセンサとRF回路を別々に形成し、それらを電気的に配線すると、検出装置の厚さが厚くなってしまう恐れがある。

**【課題を解決するための手段】****【0006】**

基板上にMEMSセンサを形成して、基板から剥離し、別にRFID (IDタグ、ICタグ、電子タグともいう) を基板上に形成して剥離し、それらをフレキシブル基板上に貼り合わせることによって、厚さが薄いMEMSセンサ及びRFIDを有する半導体装置を作製する。

30

**【0007】**

フレキシブル基板上に、無線通信の機能を有する半導体素子層と、センサの機能を有する微小構造体と、前記半導体素子層及び微小構造体を電気的に接続する配線とを有することを特徴とする半導体装置に関する。

**【0008】**

フレキシブル基板上に、無線通信の機能を有する半導体素子層と、前記半導体素子層上に絶縁層と、前記絶縁層上に、前記半導体素子層と電気的に接続される配線と、前記絶縁層及び配線上に、導電性を有する接着材と、前記導電性を有する接着材上に、センサの機能を有する微小構造体とを有し、前記微小構造体は、前記導電性を有する接着材を介して、前記半導体素子層に電気的に接続されていることを特徴とする半導体装置に関する。

40

**【0009】**

第1の基板上に、互いに密着性の弱い第1の層及び第2の層を形成し、前記第2の層上に、無線通信の機能を有する半導体素子層を形成し、前記半導体素子層上に、絶縁層を形成し、前記絶縁層上に、前記半導体素子層と電気的に接続される第1の配線と、犠牲層、第2の配線を形成し、前記第1の層と第2の層とを分離することにより、前記基板から、前記半導体素子層、前記絶縁層、前記第1の配線、前記犠牲層、前記第2の配線を分離する。前記分離した半導体素子層、絶縁層、第1の配線、犠牲層、第2の配線を、第2のフレキシブル基板に貼り合わせ、前記犠牲層を除去することにより、前記第1の配線、前記第2の配線、前記第1の配線と第2の配線との間に空間を有し、センサの機能を有する微小構造体を作製することを特徴とする半導体装置の作製方法に関する。

50

## 【0010】

第1の基板上に、互いに密着性の弱い第1の層及び第2の層を形成し、前記第2の層上に、無線通信の機能を有する半導体素子層を形成し、前記半導体素子層上に、第1の絶縁層を形成し、前記第1の絶縁層上に、前記半導体素子層と電気的に接続される第1の配線を形成し、第2の基板上に、互いに密着性の弱い第3の層及び第4の層を形成し、前記第3の層上に、第2の配線、犠牲層、第3の配線を形成し、前記第3の層と第4の層とを分離することにより、前記第2の基板から、前記第2の配線、前記犠牲層、前記第3の配線を分離する。前記分離された第3の層、第2の配線、犠牲層、第3の配線を、導電性を有する接着材により、前記第1の配線及び半導体素子層上に貼り合わせ、前記第1の層と第2の層とを分離することにより、前記第1の基板から、前記半導体素子層、前記第1の配線、前記導電性を有する接着材、前記第2の配線、前記犠牲層、前記第3の配線を分離する。前記分離した半導体素子層、第1の配線、導電性を有する接着材、第2の配線、犠牲層、第3の配線を、第3のフレキシブル基板に貼り合わせ、前記犠牲層を除去することにより、前記第2の配線、前記第3の配線、前記第2の配線と第3の配線との間に空間を有し、センサの機能を有する微小構造体を作製することを特徴とする半導体装置の作製方法に関する。

10

## 【発明の効果】

## 【0011】

フレキシブル基板上に、MEMSセンサ及びRFIDを有する半導体装置を作製することができ、かつ、半導体装置全体の厚さを薄くすることができる。

20

## 【図面の簡単な説明】

## 【0012】

【図1】半導体装置の構成を示す図。

【図2】半導体装置の断面図。

【図3】半導体装置の作製工程を示す断面図。

【図4】半導体装置の作製工程を示す断面図。

【図5】半導体装置の作製工程を示す断面図。

【図6】半導体装置の作製工程を示す断面図。

【図7】半導体装置の構成を示す図。

【図8】半導体装置を示す断面図。

30

【図9】半導体装置を示す上面図。

【図10】半導体装置を示す断面図。

## 【発明を実施するための形態】

## 【0013】

以下、本明細書に開示された発明の実施の態様について、図面を参照して説明する。但し、本明細書に開示された発明は多くの異なる態様で実施することが可能であり、本明細書に開示された発明の趣旨及びその範囲から逸脱することなくその形態及び詳細を様々に変更し得ることは当業者であれば容易に理解される。従って、本実施の形態の記載内容に限定して解釈されるものではない。なお、以下に示す図面において、同一部分又は同様な機能を有する部分には同一の符号を付し、その繰り返しの説明は省略する。

40

## 【0014】

なお本明細書において、半導体装置とは、半導体を利用して機能する素子及び装置全般を指し、電子回路、液晶表示装置、発光装置等を含む電気装置およびその電気装置を搭載した電子機器をその範疇とする。

## 【0015】

## [実施の形態1]

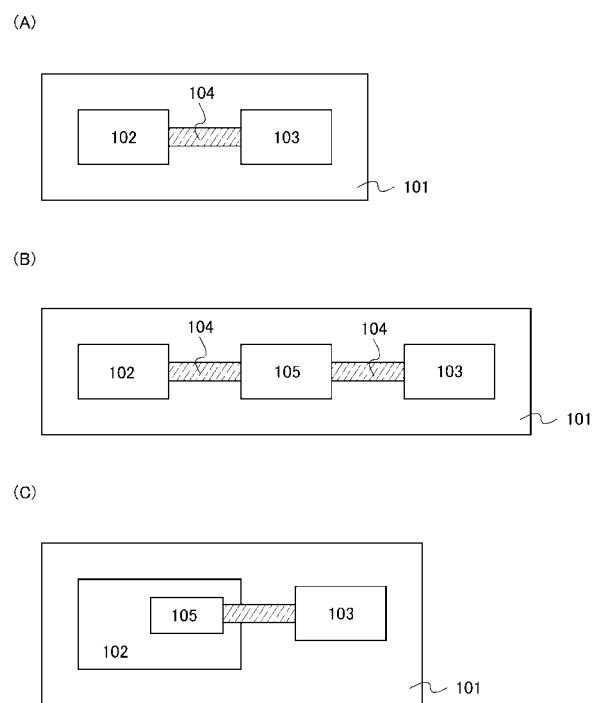

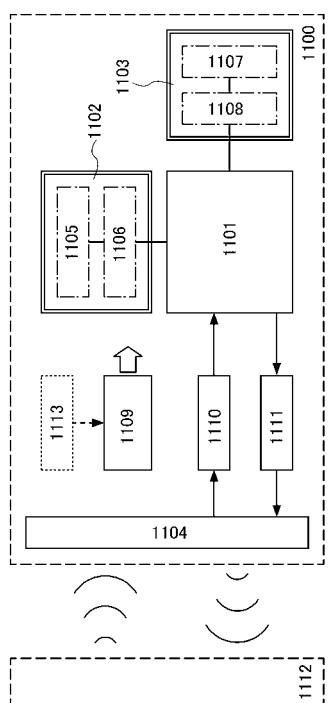

本実施の形態の半導体装置について、図1(A)～図1(C)及び図2を用いて説明する。

## 【0016】

まず、本実施の半導体装置の構成例を図1(A)に示す。本実施の形態の半導体装置 1

50

01は、半導体素子によって形成され無線通信の機能を有するRFID回路102（本明細書では「無線通信の機能を有する半導体回路」ともいう）、及び、センサの機能を有するMEMS構造体（本明細書では、「微小構造体」ともいう）103を有する。RFID回路102及びMEMS構造体103は、配線104によって電気的に接続されている。そして、この半導体装置101はフレキシブル基板（「可とう性を有する基板」ともいう）上に形成されており、全体として湾曲させることが可能である。

#### 【0017】

10 このように構成された半導体装置101は、MEMS構造体103によりセンシングした物理量の情報を、RFID回路102からリーダライタに送信する。このような半導体装置101を用いた固体管理システムでは、その情報を上位機器であるコンピュータで管理することができる。

#### 【0018】

次に、上述の半導体装置101を用いた構成を図1（B）及び図1（C）に示す。本実施の形態の半導体装置101は、図1（B）に示すようにインターフェース回路105を有し、RFID回路102とMEMS構造体103とはそのインターフェース回路105を介して接続することができる。

#### 【0019】

これは、MEMS構造体103がアナログ的な動作をする、すなわち出力がアナログ信号である場合が多いことに対し、RFID回路102はデジタル回路で構成されることが多いためである。従って、出力がアナログ信号であるアナログ回路とデジタル回路との間で、A/D変換等のインターフェースを設ける必要がある。

#### 【0020】

また、本実施の形態の半導体装置101は、図1（C）に示すように、インターフェース回路105を有するRFID回路102とMEMS構造体103とが配線104を介して接続する構成を用いることも可能である。このように、RFID回路102の内部にインターフェース回路105を組み込むことで、回路設計及びレイアウト等の最適化により全体として回路規模を縮小できることが可能である。

#### 【0021】

以上のように本実施の形態の半導体装置101は、半導体素子によって形成されるRFID回路102、及び、MEMS構造体103を有し、RFID回路102及びMEMS構造体103は、配線104によって直接、あるいは、間接的に電気的な接続がなされている。なお本明細書では、半導体素子によって形成されるRFID回路を半導体回路ともいう。

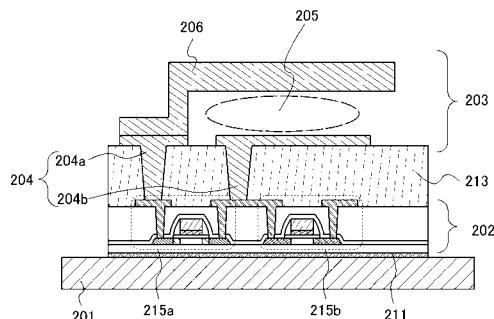

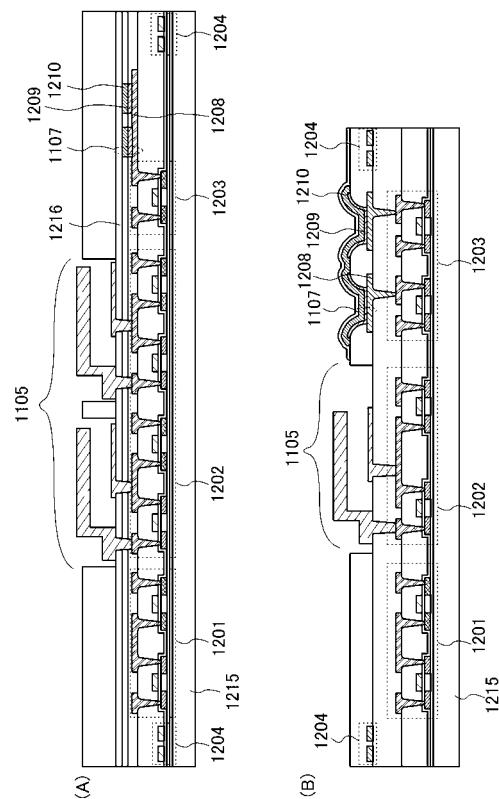

#### 【0022】

次に、本実施の形態の半導体装置の断面構造の例を、図2を用いて説明する。本実施の形態の半導体装置101は、フレキシブル基板201上に、RFID回路102を形成する半導体素子層202、及び、MEMS構造体203を有する。なお図1（A）～図1（C）におけるMEMS構造体103と、図2におけるMEMS構造体203は同じものを見示す。

#### 【0023】

半導体素子層202及びMEMS構造体103は、絶縁層213を介し、配線204（配線204a及び配線204b）によって電気的に接続されている。またフレキシブル基板201と半導体素子層202は、接着層211を用いて貼り合わせられている。

#### 【0024】

図2において、半導体素子層202として、薄膜トランジスタ（Thin Film Transistor（TFT））215a及びTFT215bを形成するが、半導体素子層202はこれに限定されない。半導体素子層202を用いて形成されるRFID回路102は様々な半導体素子（例えば、電界効果トランジスタ、容量素子、抵抗素子、ダイオード等）を用いて形成すればよい。

#### 【0025】

10

20

30

40

50

MEMS構造体には、平行に向かい合い、2つの異なるノードに接続された導電層を有し、2つの導電層間には空間が存在する。ただし本明細書では、空間とは固体の物が何も存在していない状態を指す。

#### 【0026】

また図2においては、半導体素子層202に電気的に接続されている配線204aと、MEMS構造体203の上側の導電層206が別々に分かれているが、同じ材料と及び同じ工程で作製してもよい。図2においては、半導体素子層202に電気的に接続されている配線204bは、MEMS構造体203の一部であると言え、配線204aと導電層206が同じ材料と及び同じ工程で形成された導電物である場合、このような導電物は、半導体素子層202に電気的に接続されており、かつ、MEMS構造体203の一部であると言える。10

#### 【0027】

図2に示すMEMS構造体203、フレキシブル基板201に平行に2つの導電層である配線204bと導電層206が設けられており、上側の導電層206は片側が基板に固定されている片持ち梁構造である。これはMEMS構造体の一例を示しており、この例に限定されることはない。MEMS構造体203は、片持ち梁構造の他、両側が基板に固定されている両持ち梁構造や、その他のMEMSと呼ばれる構造であればよい。

#### 【0028】

また、図2では、半導体素子層202、配線204、及び、MEMS構造体203を積層構造としたが、本実施の形態の半導体装置101はこの構造に限定されない。すなわち、半導体素子層202とMEMS構造体203とがフレキシブル基板201上において、重ならない領域に設けられ、かつ、半導体素子層202及びMEMS構造体203が配線204で電気的に接続されていてもよい。20

#### 【0029】

#### [実施の形態2]

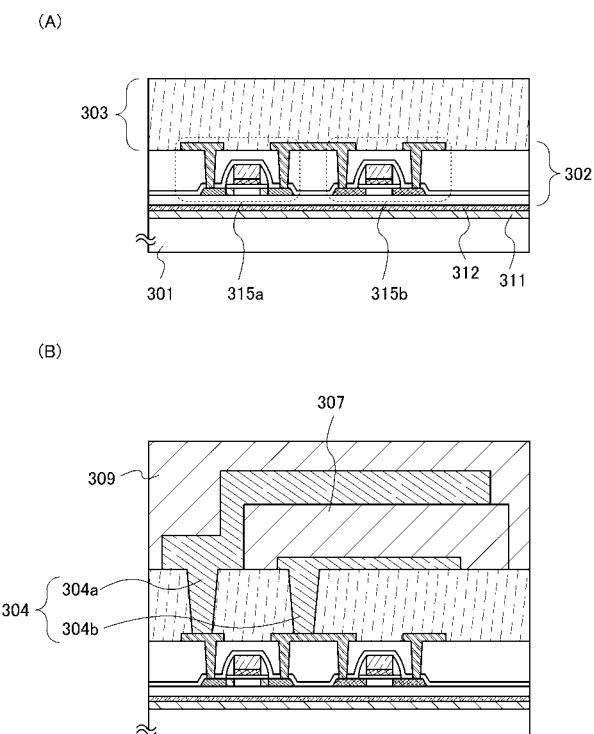

本実施の形態では、図3(A)～図3(B)及び図4(A)～図4(B)を用いて、実施の形態1で述べた半導体装置101の作製方法の例について説明する。本実施の形態では、RFID回路102を形成する半導体素子層302の上にMEMS構造体305を作製する例を示す。

#### 【0030】

まず、基板301上にRFID回路102を形成する半導体素子層302を作製する。半導体素子層302の作製工程の中で、加熱工程が存在するため、半導体素子層302を形成するために用いる基板301は、加熱工程時の温度に耐えられる材料を用いた基板である必要がある。30

#### 【0031】

基板301には、絶縁表面を有するガラス基板、石英基板、プラスチック基板等を用いることができる。その他、金属等の導電性基板や、シリコン等の半導体性基板上に絶縁膜を形成した基板を用いることもできる。

#### 【0032】

また基板301と半導体素子層302との間には、互いに密着性の弱い第1の層311及び第2の層312が設けられている。40

#### 【0033】

互いに密着性の弱い第1の層311及び第2の層312の界面が分離できることで、基板301及び第1の層311、並びに、第2の層312より上に設けられている積層構造を分離させることができる。

#### 【0034】

互いに密着性の弱い第1の層311及び第2の層312として、例えば金属膜とシリコン酸化膜などが挙げられる。具体的には、第1の層311としてタンゲステン膜を形成し、第1の層311上に、スパッタリング法により酸化珪素膜等の第2の層312を形成すればよい。50

## 【0035】

また第1の層311及び第2の層312として、成膜時にはそれぞれ密着性が低くなくとも、成膜後に処理を加えることにより密着性が低下する膜の組み合わせを用いてもよい。例えば、第1の層311として非晶質珪素膜、及び、第2の層312として酸化珪素膜を積層し、成膜後に加熱または基板裏面からレーザビームを照射すると、非晶質珪素膜が結晶化され、第1の層311と第2の層312との密着性が低下する。

## 【0036】

また、半導体素子層302は公知の技術を用いて作製すればよい。本実施の形態では、例えば半導体素子層302として薄膜トランジスタを作製する(図3(A)参照)。ただし図3(A)では、半導体素子層302として2つの薄膜トランジスタが描かれているが、これに限定されない。RFID回路102は様々な半導体素子(例えば、電界効果トランジスタ、容量素子、抵抗素子、ダイオード等)を用いて形成すればよい。

10

## 【0037】

次に、半導体素子層302の上に絶縁層303を形成する。次いで絶縁層303上に、半導体素子層302とMEMS構造体305とを接続する配線304のうち配線304bを形成する。さらに絶縁層303及び配線304b上に、後の工程で除去される層である犠牲層307を形成する。絶縁層303及び犠牲層307上に、半導体素子層302とMEMS構造体305とを接続する配線304のうち配線304aを形成する。

## 【0038】

犠牲層307は、後の工程で第1の導電層である配線304bと第2の導電層である配線304aとの間に、空間405を形成するために設けられる。

20

## 【0039】

次に、絶縁層303、犠牲層307、配線304a上に、上に平坦化膜309を形成する(図3(B)参照)。

## 【0040】

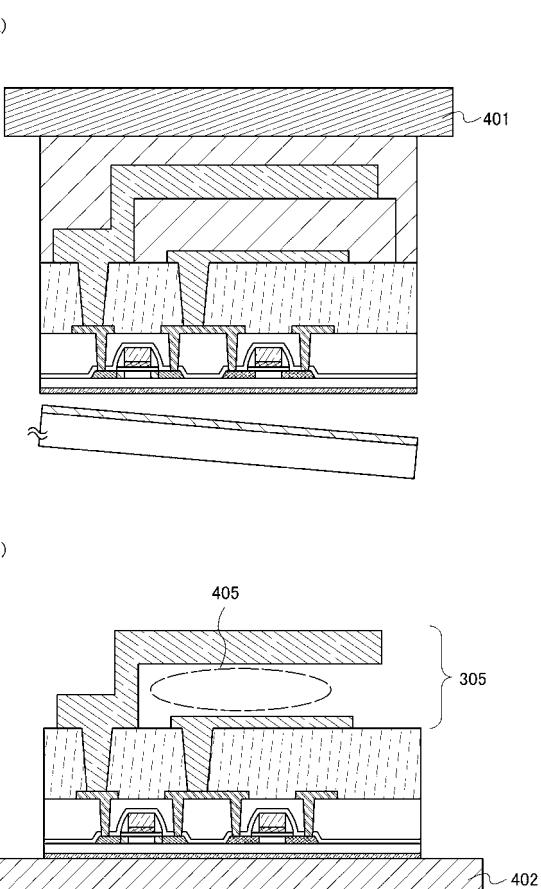

そして、平坦化膜309上に、後で除去できる支持基板401を貼り合わせる。次いで、半導体素子層302、配線304、犠牲層306、及び、平坦化膜309を、基板301から分離させる(図4(A)参照)。なおこの分離工程は、互いに密着性の弱い第1の層311と第2の層312の界面を分離することにより行われる。

30

## 【0041】

また、支持基板401としては、熱可塑性樹脂や光可塑性樹脂を粘着剤として塗布した基板を用いることができる。また、この支持基板401自体も柔軟性のあるフレキシブルな基板であったほうが、基板から半導体素子等を分離するときに半導体素子等を傷つけることない。

## 【0042】

次いで、フレキシブル基板402を貼り合わせ、支持基板401を除去する(図4(B)参照)。なお第2の層312と支持基板401との間に、接着層を設けてもよい。

## 【0043】

次いで、平坦化膜309及び犠牲層307を除去することにより、MEMS構造体305が作製される(図4(B)参照)。

40

## 【0044】

MEMS構造体305は、平行に設けられた第1の導電層(下部電極)である配線304b及び第2の導電層(上部電極)である配線304aを有し、配線304b及び配線304aの間には空間405が存在する。

## 【0045】

半導体素子層302に電気的に接続されている配線304a及び配線304bは、MEMS構造体203上部電極と下部電極であり、MEMS構造体203の一部であると言える。

## 【0046】

半導体素子層302及びMEMS構造体203が配線204によって電気的に接続され

50

、全体として湾曲させることができるようなフレキシブルな半導体装置を形成することができる。

#### 【0047】

##### [実施の形態3]

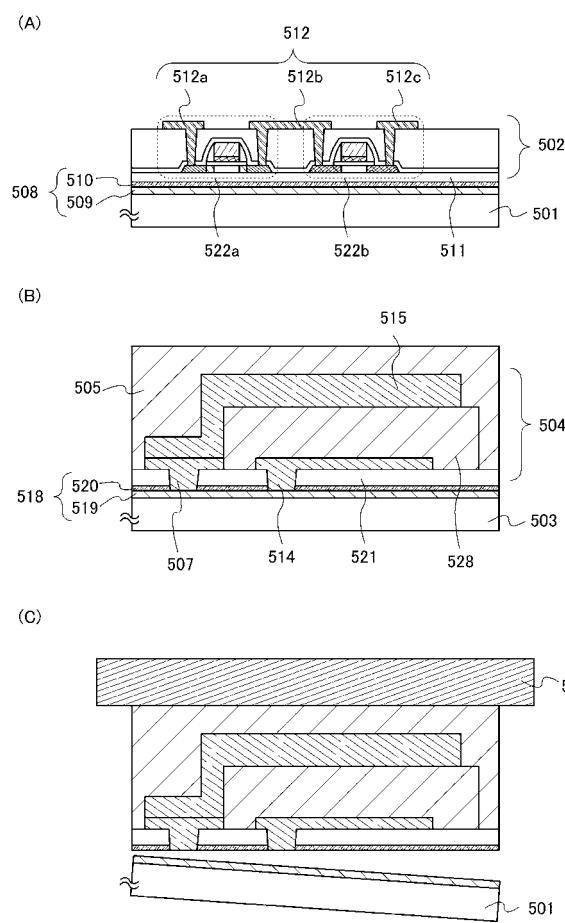

本実施の形態では、実施の形態2とは異なる半導体装置及びその作製方法を、図5(A)～図5(C)及び図6(A)～図6(B)を用いて説明する。

#### 【0048】

まず基板501上に、互いに密着性の弱い第1の層509及び第2の層509を含む積層膜508を形成する。次いで積層膜508上に、RFID回路102を形成する半導体素子層502を作製する(図5(A)参照)。

10

#### 【0049】

基板501、第1の層509、第2の層510は、それぞれ実施の形態2で述べた、基板301、第1の層311、第2の層312と同様の材料を用いればよい。

#### 【0050】

図5(A)において、半導体素子層502には、下地層511、TFT522a、TFT522bが設けられている。TFT522aには、配線512a及び配線512b、並びに、TFT522bには配線512b及び配線512cが含まれる。また本実施の形態では、配線512a、配線512b、配線512cを総して配線512と呼ぶことにする。

20

#### 【0051】

後述する工程で、前駆体504を基板503から分離する際、基板503と接していた面には配線507が露出していることになる。これを、例えば異方性の導電性を有する接着材603で、半導体素子層502上に貼り合わせれば、MEMS構造体602と半導体素子層502とを電気的に接続することができる。そのため、基板501上に半導体素子層502を作製する際に、最表面にはMEMS構造体602と接続される配線512が露出するように形成しておくとよい。

20

#### 【0052】

また、基板503上に、互いに密着性の弱い第1の層519及び第2の層520を含む積層膜518を形成する。次いで積層膜518上に、MEMS構造体の前駆体504を形成する。

30

#### 【0053】

前駆体504には、絶縁層521、配線507、配線514、犠牲層528、導電層515が含まれる。

#### 【0054】

基板503、第1の層519、第2の層520、配線514、犠牲層528は、それぞれ実施の形態2で述べた、基板301、第1の層311、第2の層312、配線304b、犠牲層307と同様の材料を用いればよい。また配線507と導電層515は、配線514と同様の材料を用いて形成すればよい。配線507と導電層515は、実施の形態1の配線204a及び導電層206と同様に別々に分かれてもよいし、実施の形態2の配線304aと同様に同じ材料及び同じ工程で形成してもよい。

40

#### 【0055】

また前駆体504を作製する際に、下地層511及び第2の層510にコンタクトホールを形成し、配線507及び配線514を形成する。次いで絶縁層521、配線507、配線514上に、犠牲層528を形成する。さらに犠牲層528上に、配線507と電気的に接続する導電層515を形成する。

#### 【0056】

あるいは、下地層511及び第2の層510にコンタクトホールを形成し、配線514を形成する。次いで絶縁層521、配線514上に、犠牲層528を形成する。さらに、犠牲層528上に、配線507及び導電層515として機能する導電層を形成してもよい。すなわち、実施の形態2における配線304aと同様にして、配線507及び導電層515

50

15として機能する導電層を形成してもよい。

【0057】

次いで、前駆体504上に、平坦化膜505を形成する(図5(B)参照)。

【0058】

次いで平坦化膜505上に、後で除去できる支持基板506を貼り合わせ、前駆体504を基板503から分離させる(図5(C)参照)。

【0059】

前駆体504を基板503から分離させる工程は、実施の形態2と同様に第1の層519と第2の層520との間の界面から行われる。

【0060】

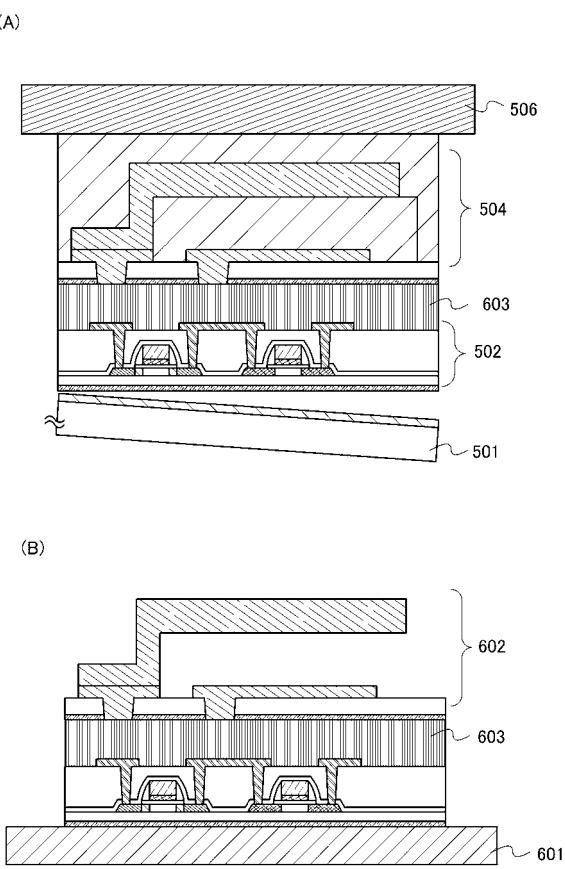

次いで、基板501上に形成された半導体素子層502上に、第2の層520、前駆体504、平坦化膜505、支持基板506を貼り合わせる。

【0061】

このとき、半導体素子層502及び前駆体504とが電気的に接続するように貼り合わせる。また、貼り合わせた後に電気的接続がなされるように加工を加えても良い。異方性の導電性を有する接着材603を用いて、半導体素子層502及び前駆体504を貼り合わせる。

【0062】

次に、基板501上に設けられた半導体素子層502及びの前駆体504の積層体を、基板501から分離する(図6(A)参照)。半導体素子層502及びの前駆体504の積層体を、基板501から分離する工程は、実施の形態2と同様に第1の層509と第2の層510との間の界面から行われる。

【0063】

次いで、半導体素子層502及びの前駆体504の積層体を、フレキシブル基板601に貼り合わせ、支持基板506を除去する。

【0064】

次いで、犠牲層528を除去することにより、MEMS構造体602を形成する。以上により、半導体素子層502及びMEMS構造体602が導電性を有する接着材603によって電気的に接続され、全体として湾曲させることができるようなフレキシブルな半導体装置を形成することができる(図6(B)参照)。

【0065】

[実施の形態4]

本実施の形態では、図1(A)～図1(C)とは異なる半導体装置の構成の例を示し、図2、図3(A)～図3(B)、図4(A)～図4(B)、図5(A)～図5(C)、図6(A)～図6(B)に示すMEMS構造体を検出素子1105として用いる。

【0066】

本実施の形態の半導体装置の構成について、図7を用いて説明する。半導体装置1100は、演算処理回路1101、検出部1102、記憶部1103、アンテナ1104、電源回路1109、復調回路1110及び変調回路1111を有する。また、半導体装置1100は、その用途に応じて、バッテリ1113を有する。

【0067】

検出部1102は、検出素子1105と検出制御回路1106を有する。記憶部1103は、記憶素子1107と記憶制御回路1108を有する。半導体装置1100は、アンテナ1104を介して、外部の機器とデータの送受信を行う。外部の機器とは、例えば、リーダ/ライタ1112である。

【0068】

演算処理回路1101は、リーダ/ライタ1112から入力される信号に基づき、動作する。演算処理回路1101の動作とは、例えば、検出部1102で検出されたデータの増幅、データの変換、データの記憶部1103への書き込み、記憶部1103に書き込まれたデータの読み出し、必要な情報をリーダ/ライタ1112へ出力する動作等に相当す

10

20

30

40

50

る。

**【0069】**

検出部1102は、図2、図3(A)～図3(B)、図4(A)～図4(B)、図5(A)～図5(C)、図6(A)～図6(B)に示すMEMS構造体を用いて形成される検出素子1105と、検出素子1105の動作を制御する検出制御回路1106を有する。

**【0070】**

検出素子1105が検出する情報は、電気信号として外部に出力される。より具体的には、具体的には、検出素子1105により検出された電気信号は検出制御回路1106に出力され、検出制御回路1106で増幅、A/D変換等の処理がされ、演算処理回路1101に入力される。

10

**【0071】**

記憶部1103は、データを記憶する機能を有し、記憶素子1107と、記憶素子1107に対するデータの書き込みや記憶素子1107に記憶されたデータの読み出しを制御する記憶制御回路1108を有する。記憶部1103は、半導体装置自体の識別番号や、検出部1102の検出結果等のデータを記憶する。半導体装置の識別番号は、検出部1102の検出結果を外部に送信する際に、他の半導体装置と区別するために用いられる番号である。

**【0072】**

記憶部1103には、有機メモリ、DRAM(Dynamic Random Access Memory)、SRAM(Static Random Access Memory)、FeRAM(Ferroelectric Random Access Memory)、マスクROM(Read Only Memory)、PROM(Programmable Read Only Memory)、EPROM(Electrically Programmable Read Only Memory)、EEPROM(Electrically Erasable Programmable Read Only Memory)及びフラッシュメモリから選択された一つ又は複数が用いられる。

20

**【0073】**

有機メモリは、一対の導電層間に有機化合物を含む層が挟まれた積層体を含む。このような積層体は、構造が単純であるため、作製工程を簡略化することができ、低コスト化を実現することができる。また、構造が単純であるために、積層体の面積を小型化することが容易であり、大容量化を実現することができる。また、不揮発性であり、かつ、追記が可能であるという長所がある。

30

**【0074】**

次に、半導体装置1100とリーダ/ライタ1112のデータの送受信に関する動作について説明する。

**【0075】**

まず、リーダ/ライタ1112から電磁波として、半導体装置1100に送信された信号は、アンテナ1104において交流の電圧に変換される。電源回路1109では、交流の電圧を用いて電源電圧を生成し、各回路へ電源電圧を供給する。復調回路1110では、交流の電圧に含まれる電気信号を復調し、演算処理回路1101に供給する。演算処理回路1101では、入力された信号に従って各種演算処理を行って、検出部1102や記憶部1103等に信号を出力する。

40

**【0076】**

そして、演算処理回路1101から変調回路1111に、検出部1102で検出されたデータが送られ、変調回路1111から、当該データに従ってアンテナ1104に負荷変調を加える。リーダ/ライタ1112は、アンテナ1104に加えられた負荷変調を、電磁波として、受信することにより、データを読み取ることができる。

**【0077】**

上記の構成では、各回路への電源電圧の供給を電磁波により行うタイプとしているが、

50

バッテリ 1113 を用いて各回路に電源電圧を供給するタイプとしてもよい。また、バッテリ 1113 を用いて電磁波とバッテリ 1113 により各回路に電源電圧を供給するタイプとしてもよい。半導体装置 1100 にバッテリを設けない場合、低コスト化、薄型化、軽量化、小型化を実現することができる。

#### 【0078】

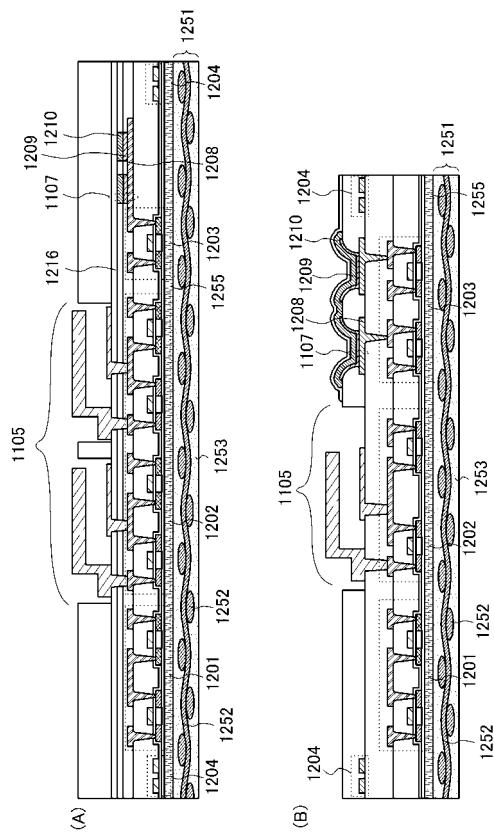

次に、演算処理回路 1101、検出部 1102、記憶部 1103 及びアンテナ 1104 を含むの半導体装置 1100 の断面構造について、図 8 (A) を用いて説明する。

#### 【0079】

検出部 1102 は検出素子 1105 と検出制御回路 1106 を含み、記憶部 1103 は記憶素子 1107 と記憶制御回路 1108 を含む。10

#### 【0080】

図 8 (A) に示す半導体装置 1100 は、演算処理回路 1101 を構成する素子 1201、検出素子 1105、検出制御回路 1106 を構成する素子 1202、記憶素子 1107、記憶制御回路 1108 を構成する素子 1203、アンテナ 1104 として機能する導電層 1204 を有する。

#### 【0081】

素子 1201、素子 1202、素子 1203 は、トランジスタ、容量素子及び抵抗素子等を含み、図示する構造では、素子 1201、素子 1202、素子 1203 として、複数のトランジスタを示す。トランジスタは、薄膜トランジスタ (TFT) でもよいし、半導体基板にチャネル層を設ける電界効果トランジスタ (FET) でもよい。20

#### 【0082】

記憶素子 1107 は、導電層 1208、有機化合物を含む層 1209 及び導電層 1210 の積層体に相当する。この構成では、1つのメモリセルに1つの記憶素子 1107 が設けられたパッシブマトリクス型の記憶部 1103 を示す。

#### 【0083】

記憶素子 1107 が含む導電層 1208 及び導電層 1210 は、金 (Au)、銀 (Ag)、白金 (Pt)、ニッケル (Ni)、タングステン (W)、クロム (Cr)、モリブデン (Mo)、鉄 (Fe)、コバルト (Co)、銅 (Cu)、パラジウム (Pd)、炭素 (C)、アルミニウム (Al)、マンガン (Mn)、チタン (Ti)、タンタル (Ta) 等から選ばれた一種の元素または当該元素を複数含む合金からなる単層または積層構造に相当する。合金としては、Al と Ti が含まれた合金等が挙げられる。また、他にも、酸化インジウムスズ (ITO)、酸化亜鉛 (ZnO)、酸化インジウム亜鉛 (IZO)、ガリウムを添加した酸化亜鉛 (GZO) などその他の透光性酸化物導電材料を用いることが可能である。30

#### 【0084】

また、記憶素子 1107 が含む有機化合物を含む層 1209 は、4,4'-ビス [N-(1-ナフチル)-N-フェニル-アミノ]-ビフェニル (略称: -NPD) や 4,4'-ビス [N-(3-メチルフェニル)-N-フェニル-アミノ]-ビフェニル (略称: TPD) 等の低分子化合物の単層または積層構造、ポリ (p-フェニレンビニレン) (PPV)、[メトキシ-5-(2-エチル)ヘキシロキシ]-p-フェニレンビニレン (MEH-PPV)、ポリ (9,9-ジアルキルフルオレン) (PAF)、ポリ (9-ビニルカルバゾール) (PVK)、ポリピロール類、ポリチオフェン類、ポリアセチレン類、ポリピレン類、ポリカルバゾール類等の高分子化合物の単層または積層構造に相当する。また、低分子化合物または高分子化合物からなる層に加えて、前記低分子または高分子化合物と無機化合物とを混合してなる層を積層して設けることもできる。40

#### 【0085】

アンテナとして機能する導電層 1204 は、トランジスタのゲート電極と同じ層に設かれている。しかし、トランジスタのソース配線やドレイン配線、記憶素子 1107 を構成する一対の導電層、検出素子 1105 を構成する導電層と同じ層に設けてもよい。このように、アンテナとして機能する導電層を、他の素子が含む導電層と同じ層に設けること50

により、アンテナとして機能する導電層を形成する工程を独立して設ける必要がなくなる。そのため、アンテナとして機能する導電層を形成する工程と、他の素子の導電層を形成する工程を同時にを行うことができる。従って、作製工程を簡略化し、作成費用の削減や歩留まりの向上を実現することができる。

#### 【0086】

また、アンテナとして機能する導電層を、他の素子が含む導電層とは別に設ける場合には、スクリーン印刷等の印刷法や液滴吐出法を用いて形成することによって作製工程の簡略化および材料の利用効率の向上を実現することができる。上記の構成では、アンテナとして機能する導電層1204は他の素子が含む導電層と同じ層に設ける場合を示すが、アンテナとして機能する導電層を別途作製し、後の工程で貼り合わせて設けた構成を用いることも可能である。10

#### 【0087】

検出素子1105と素子1201、素子1202、素子1203の間の絶縁層（例えば絶縁層1216）や、素子1201、素子1202、素子1203を覆う絶縁層として、バリア性の高い絶縁層を形成するとよい。バリア性の高い絶縁層とは、例えば、窒化物からなる絶縁層、酸化物からなる絶縁層、酸化窒化物からなる絶縁層、炭化物からなる絶縁層である。具体的には、酸化珪素、窒化珪素、酸化窒化珪素、ダイヤモンドライカーボン（DLC）又は窒化炭素等からなる絶縁層である。

#### 【0088】

次に、図8（A）に示す構成とは異なる半導体装置の断面構造について、図8（B）を用いて説明する。図8（B）に示す半導体装置1100は、検出素子1105、記憶素子1107、素子1201、素子1202、素子1203、導電層1204を有する。この構成では、1つのメモリセルに、1つのスイッチング用トランジスタと記憶素子1107が設けられたアクティブマトリクス型の記憶部1103を示す。20

#### 【0089】

図8（A）及び図8（B）において、基板1215上に、演算処理回路1101、検出部1102、記憶部1103及びアンテナ1104を設けている。基板1215は、ガラス基板、石英基板、金属基板の一表面に絶縁層を形成したもの、ステンレス基板の一表面に絶縁層を形成したもの、有機樹脂からなる基板（例えばプラスチック基板）、フィルム（例えば、ポリプロピレン、ポリエステル、ビニル、ポリフッ化ビニル、塩化ビニル等からなる）、繊維質な材料からなる紙、基材フィルム（例えば、ポリエステル、ポリアミド、無機蒸着フィルム、紙類等からなる）と接着性合成樹脂フィルム（アクリル系合成樹脂、エポキシ系合成樹脂等）の積層フィルム等に相当する。30

#### 【0090】

また、図8（A）及び図8（B）に示す構造では、基板1215上に、演算処理回路1101、検出部1102、記憶部1103及びアンテナ1104を設けているが、この構造に制約されない。基板1215上から、演算処理回路1101等を構成する複数の素子を分離してもよい。基板1215から複数の素子を分離することにより、小型化、薄型化、軽量化を実現することができる。

#### 【0091】

また、基板1215として、有機樹脂からなる基板などの耐熱性の低い基板を用いる場合がある。そのような場合、耐熱性の高いガラス基板上に素子を形成した後、基板から素子を分離し、続いて、分離した素子を、耐熱性の低い基板に貼るとよい。40

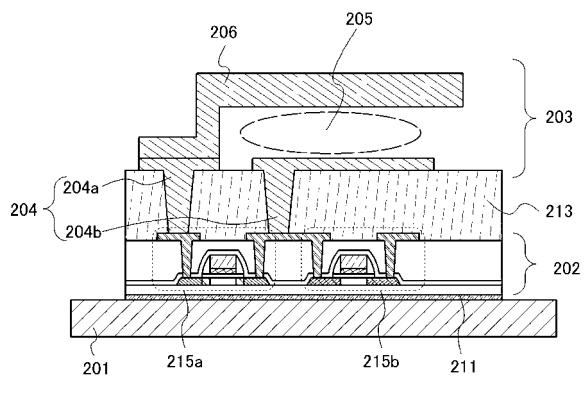

#### 【0092】

ここで分離した素子を、シート状繊維体1252及び有機樹脂1253を有する構造体（「プリプレグ」ともいう）1251に貼り合わせた例を、図10（A）及び図10（B）を用いて説明する。また素子の構造は図8（A）及び図8（B）に示す構造に基づくものとする。

#### 【0093】

シート状繊維体1252は、有機化合物または無機化合物の織布または不織布である。

10

20

30

40

50

またシート状纖維体1252として、有機化合物または無機化合物の高強度纖維を用いてもよい。

【0094】

また、シート状纖維体1252は、纖維（単糸）の束（以下、糸束という）を経糸及び緯糸に使って製織した織布、または複数種の纖維の糸束をランダムまたは一方向に堆積させた不織布で構成されてもよい。織布の場合、平織り、綾織り、縞子織り等適宜用いることができる。

【0095】

糸束の断面は、円形でも橢円形でもよい。糸束として、高压水流、液体を媒体とした高周波の振動、連続超音波の振動、ロールによる押圧等によって、開纖加工をした糸束を用いてもよい。開纖加工をした糸束は、糸束幅が広くなり、厚み方向の单糸数を削減することが可能であり、糸束の断面が橢円形または平板状となる。また、糸束として低撚糸を用いることで、糸束が扁平化しやすく、糸束の断面形状が橢円形状または平板形状となる。このように、断面が橢円形または平板状の糸束を用いることで、シート状纖維体1252の厚さを薄くすることが可能である。このため、構造体1251の厚さを薄くすることが可能であり、薄型の半導体装置を作製することができる。

10

【0096】

シート状纖維体1252は、一定間隔をあけた経糸及び一定間隔をあけた緯糸が織られている。また、糸束内部への有機樹脂1253の浸透率を高めるため、糸束に表面処理が施されても良い。例えば、糸束表面を活性化させるためのコロナ放電処理、プラズマ放電処理等がある。また、シランカップリング材、チタネートカップリング材を用いた表面処理がある。

20

【0097】

また高強度纖維とは、具体的には引張弾性率が高い纖維である。または、ヤング率が高い纖維である。高強度纖維の代表例としては、ポリビニルアルコール系纖維、ポリエステル系纖維、ポリアミド系纖維、ポリエチレン系纖維、アラミド系纖維、ポリパラフェニレンベンゾピスオキサゾール纖維、ガラス纖維、または炭素纖維である。ガラス纖維としては、Eガラス、Sガラス、Dガラス、Qガラス等を用いたガラス纖維を用いることができる。なお、シート状纖維体113は、一種類の上記高強度纖維で形成されてもよい。また、複数種類の上記高強度纖維で形成されてもよい。

30

【0098】

シート状纖維体1252に含浸される有機樹脂1253は、エポキシ樹脂、不飽和ポリエステル樹脂、ポリイミド樹脂、ビスマレイミドトリアジン樹脂、またはシアネット樹脂等の熱硬化性樹脂を用いることができる。また、ポリフェニレンオキシド樹脂、ポリエーテルイミド樹脂、またはフッ素樹脂等の熱可塑性樹脂を用いることができる。また、上記熱可塑性樹脂及び上記熱硬化性樹脂の複数を用いてもよい。上記有機樹脂を用いることで、熱処理によりシート状纖維体を半導体素子層に固着することができる。なお、有機樹脂1253はガラス転移温度が高いほど、局所的押圧に対して破壊しにくいため好ましい。

40

【0099】

有機樹脂1253またはまたは纖維の糸束内に高熱伝導性フィラーを分散させてもよい。高熱伝導性フィラーとしては、窒化アルミニウム、窒化ホウ素、窒化珪素、アルミナ等がある。また、高熱伝導性フィラーとしては、銀、銅等の金属粒子がある。高熱伝導性フィラーが有機樹脂または糸束内に含まれることにより素子層での発熱を外部に放出しやすくなるため、半導体装置の蓄熱を抑制することが可能であり、半導体装置の破壊を低減することができる。

【0100】

なお、経糸及び緯糸をそれぞれ1本ずつ編んで形成したシート状纖維体を示しているが、経糸及び緯糸の数はこれに限定されるものではない。経糸及び緯糸の数はそれぞれ必要に応じて決めればよい。

50

## 【0101】

素子と構造体1251は、接着層1255により接着されていてもよいし、構造体1251に含まれる有機樹脂1253によって接着されていてもよい。接着層1255としては、反応硬化型接着剤、熱硬化型接着剤、紫外線硬化型接着剤等の光硬化型接着剤、嫌気型接着剤などの各種硬化型接着剤を用いることができる。

## 【0102】

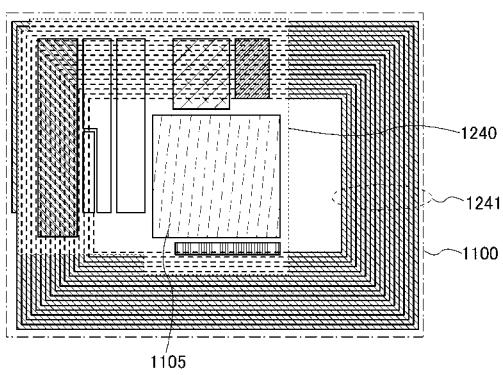

次に、本実施の形態の半導体装置の上面構造の一例について、図9を参照して説明する。

## 【0103】

半導体装置1100は、検出部1102などの複数の回路を構成する複数の素子が設けられた薄膜集積回路1240と、アンテナ1104として機能する導電層1241を含む。アンテナ1104として機能する導電層1241は、薄膜集積回路1240に電気的に接続されている。また、検出部1102は露出された状態にある。

## 【0104】

図9に示す構成では、アンテナ1104として機能する導電層1241をコイル状に設け、電磁誘導方式を適用する例を示すが、本実施の形態の半導体装置はこれに限定されない。マイクロ波方式を適用することも可能である。マイクロ波方式の場合は、用いる電磁波の波長によりアンテナ1104として機能する導電層1241の形状が適宜決定される。

## 【符号の説明】

## 【0105】

|       |             |

|-------|-------------|

| 101   | 半導体装置       |

| 102   | R F I D 回路  |

| 103   | M E M S 構造体 |

| 104   | 配線          |

| 105   | インターフェース回路  |

| 201   | フレキシブル基板    |

| 202   | 半導体素子層      |

| 203   | M E M S 構造体 |

| 204   | 配線          |

| 204 a | 配線          |

| 204 b | 配線          |

| 206   | 導電層         |

| 211   | 接着層         |

| 213   | 絶縁層         |

| 215 a | T F T       |

| 215 b | T F T       |

| 301   | 基板          |

| 302   | 半導体素子層      |

| 303   | 絶縁層         |

| 304   | 配線          |

| 304 a | 配線          |

| 304 b | 配線          |

| 305   | M E M S 構造体 |

| 306   | 犠牲層         |

| 307   | 犠牲層         |

| 309   | 平坦化膜        |

| 311   | 層           |

| 312   | 層           |

| 401   | 支持基板        |

10

20

30

40

50

|         |             |    |

|---------|-------------|----|

| 4 0 2   | フレキシブル基板    |    |

| 4 0 5   | 空間          |    |

| 5 0 1   | 基板          |    |

| 5 0 2   | 半導体素子層      |    |

| 5 0 3   | 基板          |    |

| 5 0 4   | 前駆体         |    |

| 5 0 5   | 平坦化膜        |    |

| 5 0 6   | 支持基板        |    |

| 5 0 7   | 配線          | 10 |

| 5 0 8   | 積層膜         |    |

| 5 0 9   | 層           |    |

| 5 1 0   | 層           |    |

| 5 1 1   | 下地層         |    |

| 5 1 2   | 配線          |    |

| 5 1 2 a | 配線          |    |

| 5 1 2 b | 配線          |    |

| 5 1 2 c | 配線          |    |

| 5 1 4   | 配線          |    |

| 5 1 5   | 導電層         |    |

| 5 1 8   | 積層膜         | 20 |

| 5 1 9   | 層           |    |

| 5 2 0   | 層           |    |

| 5 2 1   | 絶縁層         |    |

| 5 2 2 a | T F T       |    |

| 5 2 2 b | T F T       |    |

| 5 2 8   | 犠牲層         |    |

| 6 0 1   | フレキシブル基板    |    |

| 6 0 2   | M E M S 構造体 |    |

| 6 0 3   | 接着材         |    |

| 1 1 0 0 | 半導体装置       | 30 |

| 1 1 0 1 | 演算処理回路      |    |

| 1 1 0 2 | 検出部         |    |

| 1 1 0 3 | 記憶部         |    |

| 1 1 0 4 | アンテナ        |    |

| 1 1 0 5 | 検出素子        |    |

| 1 1 0 6 | 検出制御回路      |    |

| 1 1 0 7 | 記憶素子        |    |

| 1 1 0 8 | 記憶制御回路      |    |

| 1 1 0 9 | 電源回路        |    |

| 1 1 1 0 | 復調回路        | 40 |

| 1 1 1 1 | 変調回路        |    |

| 1 1 1 2 | リーダ／ライタ     |    |

| 1 1 1 3 | バッテリ        |    |

| 1 2 0 1 | 素子          |    |

| 1 2 0 2 | 素子          |    |

| 1 2 0 3 | 素子          |    |

| 1 2 0 4 | 導電層         |    |

| 1 2 0 8 | 導電層         |    |

| 1 2 0 9 | 層           |    |

| 1 2 1 0 | 導電層         | 50 |

|         |        |

|---------|--------|

| 1 2 1 5 | 基板     |

| 1 2 1 6 | 絶縁層    |

| 1 2 4 0 | 薄膜集積回路 |

| 1 2 4 1 | 導電層    |

| 1 2 5 1 | 構造体    |

| 1 2 5 2 | 繊維体    |

| 1 2 5 3 | 有機樹脂   |

| 1 2 5 5 | 接着層    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図 7】

【図 8】

【図 9】

【図 10】