US 20020180008A1

# (19) United States (12) Patent Application Publication (10) Pub. No.: US 2002/0180008 A1 Corisis

## (54) LEADS UNDER CHIP IN CONVENTIONAL **IC PACKAGE**

(76) Inventor: David J. Corisis, Meridian, ID (US)

> Correspondence Address: **TRASK BRITT** P.O. BOX 2550 SALT LAKE CITY, UT 84110 (US)

- (21) Appl. No.: 10/200,847

- (22)Filed: Jul. 22, 2002

#### **Related U.S. Application Data**

(60) Continuation of application No. 09/852,868, filed on May 10, 2001, now Pat. No. 6,445,061, which is a continuation of application No. 09/301,710, filed on Apr. 29, 1999, now Pat. No. 6,271,580, which is a division of application No. 08/774,609, filed on Dec. 30, 1996, now Pat. No. 5,907,769.

# Dec. 5, 2002 (43) **Pub. Date:**

# **Publication Classification**

- (51) Int. Cl.<sup>7</sup> ..... H01L 23/495

- (52)

#### (57) ABSTRACT

A semiconductor device assembly including a semiconductor device having a plurality of bond pads on the active surface thereof and a lead frame having a portion of the plurality of lead fingers of the lead frame located below the semiconductor device in a substantially horizontal plane and another portion of the plurality of lead fingers of the lead frame located substantially in the same horizontal plane as the active surface of the semiconductor device. Both pluralities of lead fingers of the lead frame having their ends being located substantially adjacent the peripheral sides of the semiconductor device, rather than at the ends thereof.

Fig. 1

Fig. 3

Fig. 4

#### LEADS UNDER CHIP IN CONVENTIONAL IC PACKAGE

#### CROSS-REFERENCE TO RELATED APPLICATIONS

[0001] This application is a continuation of application Ser. No. 09/852,868, filed May 10, 2001, pending, which is continuation of application Ser. No. 09/301,710, filed Apr. 29, 1999, now U.S. Pat. No. 6,271,580 B1, issued Aug. 7, 2001, which is a divisional of application Ser. No. 08/774,609, filed Dec. 30, 1996, now U.S. Pat. No. 5,907,769, issued May 25, 1999.

#### BACKGROUND OF THE INVENTION

[0002] 1. Field of the Invention

**[0003]** The present invention is related to a semiconductor device assembly including a semiconductor device having a plurality of bond pads on the active surface thereof and a lead frame having a first portion of the plurality of lead fingers of the lead frame located below the inactive surface of the semiconductor device in a substantially horizontal plane and another portion of the plurality of lead fingers of the lead frame located substantially in the same horizontal plane as the active surface of the semiconductor device. Both plurality of lead fingers of the lead fingers of the lead frame having their ends being located substantially adjacent the peripheral sides of the semiconductor device, rather than at the ends thereof.

**[0004]** 2. State of the Art

[0005] High performance, low cost, increased miniaturization of components, and greater packaging density of integrated circuits have been and are goals in the electronics industry. Greater integrated circuit package density for a given level of component and internal conductor density is primarily limited by the space available for semiconductor device mounting and packaging. For lead frame mounted semiconductor devices, this limitation is a result of the conventional lead frame design, such conventional lead frame design inherently limits potential single-die package density because the die-attach paddle of the lead frame must be as large or larger than the semiconductor device secured thereto. The larger the semiconductor device, the less space (relative to size of the semiconductor device) that remains around the periphery of the die-attach paddle for bond pads for attendant wire bonding. Furthermore, the inner ends of the lead fingers of a lead frame provide anchor points for the lead fingers when the lead fingers and the die are encapsulated in plastic. These anchor points may be emphasized later as flanges or bends or kinks in the lead. Therefore, as the die size is increased in relation to the package size in ever decreasing size semiconductor packages, there is a corresponding reduction in the space along the sides of the package for the encapsulating plastic which joins the top and bottom portions of the molded plastic body at the mold part line and anchors to the leads. As the leads are subjected to the normal stresses of forming and assembly operations, the encapsulating plastic may crack, which may destroy the package seal and substantially increase the probability of premature semiconductor device failure.

**[0006]** One method of increasing integrated circuit density is to stack semiconductor dice vertically. U.S. Pat. No. 5,012,323 to Farnworth illustrates combining a pair of semiconductor devices mounted on opposing sides of a lead frame. An upper semiconductor device is back-bonded to the upper surface of the leads of the lead frame by a first adhesively coated, insulated film layer. The lower semiconductor device is face-bonded to the lower lead frame diebonding region via a second, adhesively coated, insulative, film layer. The wirebonding pads on both upper and lower semiconductor devices are interconnected with the ends of their associated lead extensions with gold or aluminum wires. The lower device needs to be sightly larger than the upper device in order that the lower die bonding pads are accessible from above through an aperture in the lead frame such that gold wire connections can be made to the lead extensions. However, this arrangement has a major disadvantage from a production standpoint, since the different size semiconductor devices require that different separate equipment produce the different dice or that the same equipment be switched over in different production runs to produce the different semiconductor devices. Moreover, the lead frame design employed by Farnworth employs long conductor runs between the die and the exterior of the package. Also, the lead frame configuration is specialized and rather complex.

[0007] U.S. Pat. No. 5,291,061 to Ball illustrates a multiple stacked semiconductor device that contains up to four such devices which does not exceed the height of current single semiconductor device packages. The low profile of the semiconductor device is achieved by close-tolerance stacking which is made possible by a low-loop-profile wirebonding operation and thin adhesive layers between the stacked semiconductor devices. However, Ball secures all of the semiconductor devices to the same side of the lead frame, thereby increasing wire length. Moreover, Ball employs a die paddle to support the semiconductor device stack.

**[0008]** U.S. Pat. No. 4,862,245 to Pashby illustrates a "leads-over-chip" (LOC) configuration, wherein the inner lead ends of a standard dual-in-line package (DIP) lead frame configuration extend over and are secured to the active (upper) of the semiconductor device through a dielectric layer. The bond wire length is shortened by placing the inner lead ends in closer proximity to a central row of die bond pads, and the lead extensions purportedly enhance heat transfer from the semiconductor device. However, the Pashby LOC configuration, as disclosed, relates to mounting and bonding a single semiconductor device with the inner lead ends of the lead fingers to the surface of the semiconductor device.

**[0009]** U.S. Pat. No. 4,943,843 illustrates a semiconductor device having improved packaging adhesion of the lead fingers within the packaging resin by spreading leads on or near the non-circuit forming face of the semiconductor device thereby extending the lengths of the inner portions of the lead fingers on or under the semiconductor device. As illustrated in the '843 patent, the semiconductor device is of the type having bond pads located only on the ends thereof, not the peripheral sides of the semiconductor device.

**[0010]** U.S. Pat. No. 4,595,945 illustrates a lead frame to distribute power off a semiconductor device using a lead frame having the support paddle of the lead frame being split electrically to provide at least two conductor members that

cross under the inactive surface of the semiconductor device. As illustrated, the semiconductor device is of the configuration type having bond pads located only on the ends thereof, not about the peripheral sides of the semiconductor chip or the periphery of the semiconductor device.

**[0011]** U.S. Pat. No. 5,554,886 illustrates a lead frame used to support a semiconductor device having a portion of the peripheral lead fingers of the lead frame extending along the peripheral sides of the semiconductor device and locally supporting the semiconductor chip therealong. However, no lead fingers are used which extend under the length of the inactive surface of the semiconductor chip to support the semiconductor device and are connected by wire bonding to the bond pads of the semiconductor device.

**[0012]** U.S. Pat. No. 5,557,143 illustrates a packaged semiconductor device assembly utilizing a plurality of leads. Such leads are arranged in an up and down staggered manner, an interval between ends of low stage leads in the package being narrower than a width of upper stage leads and ends of the lower stage leads in the package are positioned nearer to the semiconductor device pad than ends of the upper stage leads. However, none of the leads extend below the semiconductor device which is solely supported by the die paddle (pad).

#### SUMMARY OF THE INVENTION

**[0013]** The present invention is related to a semiconductor device assembly including a semiconductor device having a plurality of bond pads on the active surface thereof and a lead frame having a first portion of the plurality of lead fingers of the lead frame located below the inactive surface of the semiconductor device in a substantially horizontal plane and another portion of the plurality of lead fingers of the lead frame located substantially in the same horizontal plane as the active surface of the semiconductor device. Both plurality of lead fingers of the lead frame located substantially adjacent the peripheral sides of the semiconductor device, rather than at the ends thereof.

#### BRIEF DESCRIPTION OF THE SEVERAL VIEWS OF THE DRAWINGS

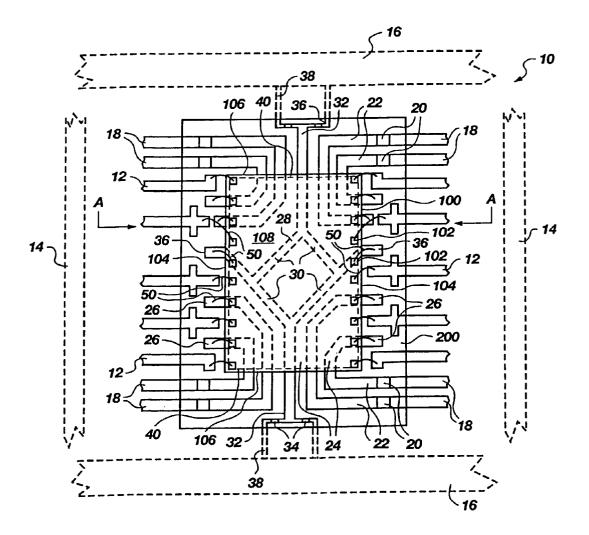

**[0014] FIG. 1** is a top view of a portion of the first embodiment of the present invention of the semiconductor assembly including a semiconductor device and lead frame;

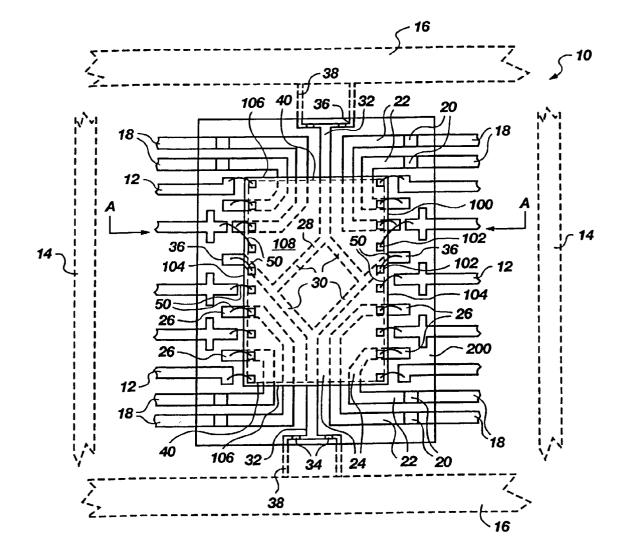

**[0015] FIG. 2** is a cross sectional view taken along line A-A of **FIG. 1** of a portion of the semiconductor assembly of the first embodiment of the present invention;

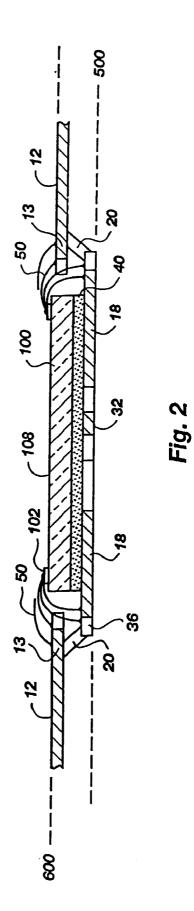

**[0016] FIG. 3** is a top view of a second embodiment of the present invention of the semiconductor assembly including a semiconductor device and lead frame; and

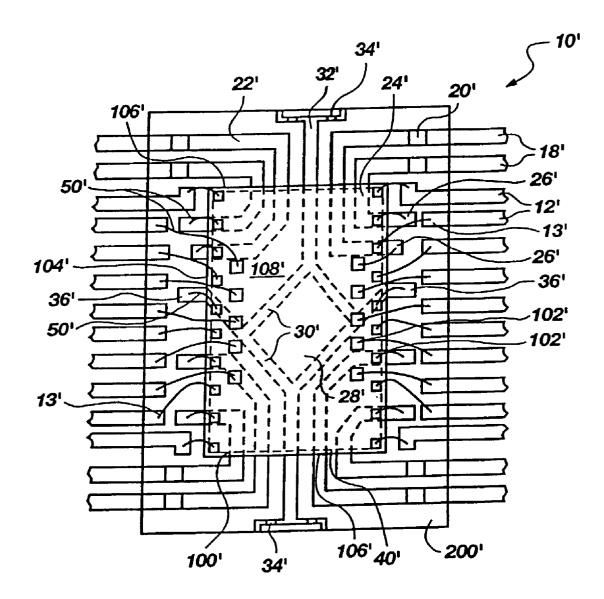

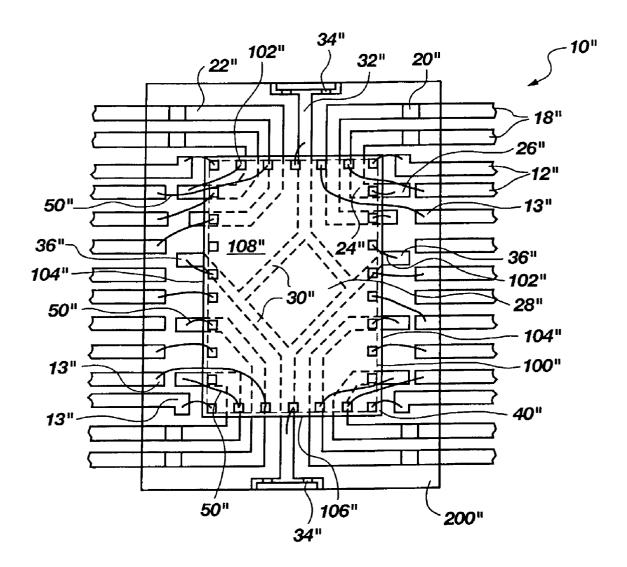

**[0017] FIG. 4** is a top view of a third embodiment of the present invention of the semiconductor assembly including a semiconductor device and lead frame.

**[0018]** The present invention will be better understood when the drawings are taken in conjunction with the description of the invention hereinafter.

### DETAILED DESCRIPTION OF THE INVENTION

[0019] Referring to drawing FIG. 1, a semiconductor assembly of a first embodiment of the present invention

including a portion of the lead frame **10** is shown in relation to a semiconductor device **100** in an encapsulated package **200**.

[0020] As illustrated, the semiconductor device 100 includes a plurality of bond pads 102 located on the longer peripheral sides 104 thereon, rather than on the ends 106 of the semiconductor device 100. The semiconductor device 100 may be of any type, such as a memory device, a microprocessor, etc. The lead frame 10 of the present invention is illustrated having a first plurality of lead fingers 12 which at one time were connected to tie bars 14 before being separated therefrom during the packaging process of the semiconductor device 100. The first plurality of lead fingers 12 extends substantially inwardly in a substantially parallel manner with respect to adjacent individual lead fingers 12 from the tie bars 14 to terminate at ends 13 thereof which are located substantially adjacent the longer peripheral sides 104 of the semiconductor device 100 in substantially the same horizontal plane as the active surface 108 of the semiconductor device 100.

[0021] As further illustrated, the lead frame 10 of the present invention further includes a second plurality of lead fingers 18, each lead finger 18 extending substantially inwardly in a substantially parallel manner with respect to individual adjacent lead fingers 18 from the tie bars 14 and is downset at portions 20 thereon to have portions 22 thereof lying in a horizontal plane which is substantially slightly lower than the bottom inactive surface of the semiconductor device 100, the portions 22 of each lead finger 18 having a first portion which extends substantially parallel to the end 106 of the semiconductor device 100 and a second portion which extends substantially perpendicular to the end 106 of the semiconductor device 100 and extending thereto, and lead finger portions 24 which extend under the bottom inactive surface of the semiconductor device 100, which help support the semiconductor device 100, and terminate at ends 26 outside the semiconductor device 100 substantially adjacent a longer peripheral side 104 of the semiconductor device 100. Each portion 24 of a lead finger 18 has a first portion extending substantially parallel to a side 104 of the semiconductor device 100 and a second portion terminating in an end 26 extending substantially perpendicular to the side 104 of the semiconductor device 100 and a third transition portion which may contain one or more angled portions therein to transition the lead finger 18 from extending in a first direction from perpendicular to an end 106 of the semiconductor device 100 to perpendicular to a side 104 of the semiconductor device 100.

[0022] The lead frame 10 of the present invention further includes die paddle 28 formed by die paddle members 30 in any desired geometric shape, having an opening therein or formed as a unitary piece, which are, in turn, connected to die paddle supports 32, each of which contain downsets 34 therein so that the die paddle 28 is located in a horizontal plane below the semiconductor device 100. The die paddle supports 32 each further include ends 36 thereon which terminate outside the semiconductor device 100 substantially adjacent a longer peripheral side 104 of the semiconductor device 100. Outer portions 38 of the die paddle supports 32 extended to frame rails 16 of the lead frame 10 before being severed therefrom after packaging of the semiconductor device 100.

[0023] The first plurality of lead fingers 12, second plurality of lead fingers 18, and die paddle supports 32 have their ends 13, 26, and 36, respectively, connected to bond pads 102 of the semiconductor device 100 by means of wire bonds 50 formed during suitable wire bond processes well known in the art.

[0024] As illustrated, after the wire bonds 50 are made connecting the ends 13, 26, and 36 of the first plurality of lead fingers 12, second plurality of lead fingers 18, and die paddle supports 32, respectively, the semiconductor device 100 is encapsulated in suitable well known epoxy plastic material to form the package 200 in a well known standard die molding process.

[0025] As illustrated, a piece of suitable tape 40, such as Kapton tape, is adhesively secured, using any suitable thermo-setting adhesive, to the portions 24 of the first plurality of lead fingers 18, the die paddle members 30, and die paddle supports 32. Preferably, a silver filled epoxy paste adhesive material is used to adhesively attach the semiconductor device 100 to the tape 40.

[0026] Referring to drawing FIG. 2, the semiconductor device 100 is adhesively attached to tape 40 which is, in turn, adhesively attached using a suitable thermosetting adhesive to the die paddle supports 32 and portions 24 of the second plurality of lead fingers 18. As illustrated, the ends 13 of the first plurality of lead fingers 12 and ends 36 of the second plurality of lead fingers 18 are connected to the bond pads 102 of the active surface 108 of the semiconductor device 100 by wire bonds 50.

[0027] Since the first plurality of lead fingers 12 is located in substantially the same horizontal plane 600 as the active surface 108 of the semiconductor device 100 having bond pads 102 thereon and the second plurality of lead fingers 18 is located in substantially the same horizontal plane 500 below the inactive bottom surface of the semiconductor device 100, a large number of lead fingers 12 and 18 may be used to form connections between the bond pads 102 and the first plurality of lead fingers 12 and second plurality of lead fingers 18 because the lead fingers 12 and 18 are located in different horizontal planes with respect to the semiconductor device 100. Furthermore, the second plurality of lead fingers 18 may be used to support the semiconductor device 100 in the package 200 and may be used to conduct heat away from the semiconductor device 200 during operation. In this manner, greater flexibility is created in the design of the circuitry of the semiconductor device 100 and the location of the bond pads 102 thereon. Additionally, since the lead frame 10 of the present invention has the location of the first plurality of lead fingers 12 adjacent the peripheral sides 104 of the semiconductor device 100 in substantially the same horizontal plane as the active surface 108 of the semiconductor device 100 while the second plurality of lead fingers 18 is located in substantially the same horizontal plane as the die paddle members 30 supporting the semiconductor device 100, the assembly of the semiconductor device 100 and lead frame 10 of the present invention may be wire bonded in conventional wire bonding equipment and encapsulated in conventional die molding equipment without substantial modification thereof. In this manner, the present invention of the lead frame 10 and semiconductor device 100 saves the expenditure of capital investment in new wire bonding and die molding equipment.

[0028] Referring to drawing FIG. 3, a semiconductor assembly of a second embodiment of the present invention including a portion of the lead frame 10' is shown in relation to a semiconductor device 100' in an encapsulated package 200'.

[0029] As illustrated, the semiconductor device 100' includes a plurality of bond pads 102' located in multiple rows or columns on the longer peripheral sides 104' thereon, rather than on the ends 106' of the semiconductor device 100'. The semiconductor device 100' may be of any type, such as a memory device, a microprocessor, etc.

[0030] The lead frame 10' of the present invention is illustrated having a first plurality of lead fingers 12' extending substantially inwardly, terminating at ends 13' thereof which are located substantially adjacent the longer peripheral sides 104' of the semiconductor device 100' in substantially the same horizontal plane as the active surface 108' of the semiconductor device 100'.

[0031] As further illustrated, the lead frame 10' of the present invention further includes a second plurality of lead fingers 18' which extends substantially inwardly and is downset at portions 20' thereon to have portions 22' thereof lying in a horizontal plane which is substantially slightly lower than the inactive bottom surface of the semiconductor device 100', the portions 22' of the lead fingers 18' extending to the ends 106' of the semiconductor device 100', and lead finger portions 24' which extend under the semiconductor device 100', and terminate at ends 26' outside the semiconductor device 100' substantially adjacent a longer peripheral side 104' of the semiconductor device 100'.

[0032] The lead frame 10' of the present invention further includes die paddle 28' formed by die paddle members 30' in any desired geometric shape or as a solid, one piece member which are, in turn, connected to die paddle supports 32', each of which contain downsets 34' therein so that the die paddle 28' is substantially located in a horizontal plane below the inactive bottom surface of the semiconductor device 100'. The die paddle supports 32' each further include ends 36' thereon which terminate outside the semiconductor device 100' substantially adjacent a longer peripheral side 104' of the semiconductor device 100'.

[0033] The first plurality of lead fingers 12', second plurality of lead fingers 18', and die paddle supports 32' have the ends 13', 26', and 36' thereof, respectively, connected to bond pads 102' of the semiconductor device 100' by means of wire bonds 50' formed during suitable wire bond processes well known in the art.

[0034] As illustrated, after the wire bonds 50' are made connecting the ends 13', 26', and 36' of the first plurality of lead fingers 12', second plurality of lead fingers 18', and die paddle supports 32', respectively, the semiconductor device 100' is encapsulated in suitable well known epoxy plastic material to form the package 200' in a well known standard transfer die molding process.

[0035] As illustrated, a piece of suitable tape 40', such as Kapton tape, is adhesively secured, using any suitable thermo- setting adhesive, to the portions 24' of the first plurality of lead fingers 18', the die paddle members 30', and die paddle supports 32'. Preferably, a silver filled epoxy

paste adhesive material is used to adhesively attach the semiconductor device 100' to the tape 40'.

[0036] The second plurality of lead fingers 18' may be used to support the semiconductor device 100' in the package 200' and may be used to conduct heat away from the semiconductor device 100' during operation. In this manner, greater flexibility is created in the design of the circuitry of the semiconductor device 100' and the location of the bond pads 102' thereon. Additionally, since the lead frame 10' of the present invention has the location of the first plurality of lead fingers 12' adjacent the peripheral sides 104' of the semiconductor device 100' in substantially the same horizontal plane as the active surface 108' of the semiconductor device 100' while the second plurality of lead fingers 18' is located in substantially the same horizontal plane as the die paddle members 30' supporting the semiconductor device 100', the assembly of the semiconductor device 100' and lead frame 10' of the present invention may be wire bonded in conventional wire bonding equipment and encapsulated in conventional die molding equipment without substantial modification thereof. In this manner, the present invention of the lead frame 10' and semiconductor device 100' saves the expenditure of capital investment in new wire bonding and die molding equipment.

[0037] Referring to drawing FIG. 4, a semiconductor assembly of a third embodiment of the present invention including a portion of the lead frame 10" is shown in relation to a semiconductor device 100" in an encapsulated package 200". As illustrated, the semiconductor device 100" includes a plurality of bond pads 102" located on the longer peripheral sides 104" and the ends 106" thereon. The semiconductor device 100" may be of any type, such as a memory device, a microprocessor, etc.

[0038] The lead frame 10" of the present invention is illustrated having a first plurality of lead fingers 12" extending substantially inwardly terminating at ends 13" thereof which are located substantially adjacent the longer peripheral sides 104" of the semiconductor device 100" in substantially the same horizontal plane as the active surface 108" of the semiconductor device 100".

[0039] As further illustrated, the lead frame 10" of the present invention further includes a second plurality of lead fingers 18" which extends substantially inwardly and is downset at portions 20" thereon to have portions 22" thereof lying in a horizontal plane which is substantially slightly lower than the inactive bottom surface of the semiconductor device 100", the portions 22" of the lead fingers 18" extending to the ends 106" of the semiconductor device 100", and lead finger portions 24" which extend under the semiconductor device 100", which help support the semiconductor device 100", and terminate at ends 26" outside the semiconductor device 100" substantially adjacent a longer peripheral side 104" of the semiconductor device 100".

[0040] The lead frame 10" of the present invention further includes die paddle 28" formed by die paddle members 30" in any desired geometric shape or as a solid one piece member which are, in turn, connected to die paddle supports 32", each of which contain downsets 34" therein so that the die paddle 28" is substantially located in a horizontal plane below the inactive bottom surface of the semiconductor device 100". The die paddle supports 32" each further include ends 36" thereon which terminate outside the semi-

conductor device 100" substantially adjacent a longer peripheral side 104" of the semiconductor device 100".

[0041] The first plurality of lead fingers 12", second plurality of lead fingers 18", and die paddle supports 32" have the ends 13", 26", and 36" thereof, respectively, connected to bond pads 102" of the semiconductor device 100" by means of wire bonds 50" formed during suitable wire bond processes well known in the art.

[0042] As illustrated, after the wire bonds 50" are made connecting the ends 13", 26", and 36" of the first plurality of lead fingers 12", second plurality of lead fingers 18", and die paddle supports 32", respectively, the semiconductor device 100" is encapsulated in suitable well known epoxy plastic material to form the package 200" in a well known standard transfer die molding process.

[0043] As illustrated, a piece of suitable tape 40", such as Kapton tape, is adhesively secured, using any suitable thermo- setting adhesive, to the portions 24" of the first plurality of lead fingers 18", the die paddle members 30", and die paddle supports 32". Preferably, a silver filled epoxy paste adhesive material is used to adhesively attach the semiconductor device 100" to the tape 40".

[0044] Also, bond pads 102" are located on the ends 106" of semiconductor device 100" and interconnected with the second plurality of lead fingers 18" or the die paddle supports 32", if desired. In this manner, greater flexibility is created in the design of the circuitry of the semiconductor device 100" and the location of the bond pads 102" thereon. Additionally, since the lead frame 10" of the present invention has the location of the first plurality of lead fingers 12" adjacent the peripheral sides 104" of the semiconductor device 100" in substantially the same horizontal plane as the active surface 108" of the semiconductor device 100" while the second plurality of lead fingers 18" is located in substantially the same horizontal plane as the die paddle members 30" supporting the semiconductor device 100", the assembly of the semiconductor device 100" and lead frame 10" of the present invention may be wire bonded in conventional wire bonding equipment and encapsulated in conventional die molding equipment without substantial modification thereof. In this manner, the present invention of the lead frame 10" and semiconductor device 100" saves the expenditure of capital investment in new wire bonding and die molding equipment.

[0045] As is readily apparent from the foregoing, the semiconductor assembly of the present invention including a semiconductor device and lead frame having a portion of the lead fingers supporting the semiconductor device offers the advantages of having a portion of the lead fingers supporting the semiconductor device thereby allowing a smaller die paddle to be used and a less substantial die paddle to be required, a wide variety of sizes of semiconductor devices may be used with the lead frame, a wide variety of bond pad layouts may be used on the semiconductor devices with the same lead frame, conventional wire bonding equipment may be used to form the connections between the bond pads on the semiconductor device and the lead frame, conventional transfer molding equipment may be used to encapsulate the assembly, and a higher lead finger density may be used in the same available area depending upon lead frame and semiconductor device design.

**[0046]** It is contemplated that changes, additions, modifications and deletions may be made to the semiconductor

assembly of the present invention which fall within the scope of the claimed invention. For instance, although the semiconductor device of the present invention is illustrated with longer peripheral sides and opposed ends, the semiconductor device may be substantially square in configuration thereby having opposed peripheral sides and opposed ends of substantially the same length. The lead frame may be formed with any number of lead fingers as space allows. Any number of lead fingers may be used to support the semiconductor device in addition to/or without a die paddle support of the semiconductor device. The ends of the lead fingers extending along the peripheral sides of the semiconductor device may extend past the ends of adjacent lead fingers. The lead fingers extending below the semiconductor device may be spaced any desired distance below the bottom inactive surface of the semiconductor device.

#### What is claimed is:

1. A semiconductor assembly for a semiconductor device having opposed longer peripheral sides and opposed ends, an active surface in substantially a first horizontal plane, an inactive bottom surface in substantially a second horizontal plane, and a plurality of bonds pads located on the active surface of the semiconductor device, a first portion of the plurality of bond pads located adjacent one of the opposed longer peripheral sides and a second portion of the plurality of bond pads located adjacent another of the opposed longer peripheral sides, said assembly including:

- a lead frame comprising:

- a first plurality of lead fingers extending substantially in the first horizontal plane of the active surface of the semiconductor device, each lead finger of the first plurality of lead fingers terminating in an end located adjacent a longer peripheral side of the opposed longer peripheral sides of the semiconductor device; and

- a second plurality of lead fingers extending below the inactive bottom surface of the semiconductor device, each lead finger of the second plurality of lead fingers having a portion thereof extending adjacent an end of the opposed ends of the semiconductor device and terminating in an end located adjacent a longer peripheral side of the opposed longer peripheral sides of the semiconductor device, some of the second plurality of lead fingers forming a die paddle for locating the semiconductor device thereon, a plurality of lead fingers of the second plurality of lead fingers each having a portion thereof extending adjacent a portion of a lead finger of the first plurality of lead fingers, a portion thereof extending substantially adjacent an end of the opposed ends of the semiconductor device, a portion extending substantially opposed to an end of the opposed ends of the semiconductor device and extending adjacent a portion of the die paddle, and having a portion extending beyond a side of the opposed longer peripheral sides of the semiconductor device.

**2**. The assembly of claim 1, wherein the die paddle of the lead frame further includes:

a die paddle located below the inactive bottom surface of the semiconductor device formed by a plurality of the second plurality of lead fingers. **3**. The assembly of claim 1, wherein the ends of the first plurality of lead fingers extend past the ends of adjacent lead fingers of the second plurality of lead fingers.

4. The assembly of claim 1, wherein the ends of the second plurality of lead fingers extend past the ends of adjacent lead fingers of the first plurality of lead fingers.

- 5. The assembly of claim 1, further including:

- tape located between the second plurality of lead fingers and the inactive bottom surface of the semiconductor device.

- 6. The assembly of claim 2, further including:

tape located between the die paddle and the inactive bottom surface of the semiconductor device.

- 7. The assembly of claim 2, further including:

- tape located between the die paddle and the second plurality of lead fingers and the inactive bottom surface of the semiconductor device.

**8**. The assembly of claim 5, wherein the second plurality of lead fingers are adhesively attached to the tape.

**9**. The assembly of claim 8, wherein the second plurality of lead fingers are adhesively attached to the tape using thermosetting adhesive.

**10**. The assembly of claim 5, wherein the semiconductor device is adhesively attached to the tape.

**11**. The assembly of claim 10, wherein the semiconductor device is adhesively attached to the tape using silver epoxy paste.

- 12. The assembly of claim 1, further including:

- at least one wire bond extending between at least one bond pad of the plurality bond pads located on the active surface of the semiconductor device and at least one lead finger of the first plurality of lead fingers and second plurality of lead fingers of the lead frame.

**13**. The assembly of claim 2, wherein the die paddle includes at least one portion thereon extending beyond a longer peripheral side of the opposed longer peripheral sides and at least another portion extending beyond an end of the opposed ends of the semiconductor device.

14. The assembly of claim 1, wherein the opposed longer peripheral sides of the semiconductor device and the opposed ends of the semiconductor device are substantially a same length.

15. The assembly of claim 13, further including:

- at least one wire bond connecting the at least one portion of the die paddle extending beyond the longer peripheral side of the opposed longer peripheral sides and a bond pad of the plurality of bond pads on the active surface of the semiconductor device.

- 16. The assembly of claim 13, further including:

- at least one wire bond connecting the at least one portion of the die paddle extending beyond the end of the opposed ends of the semiconductor device and a bond pad of the plurality of bonds pads on the active surface of the semiconductor device.

- 17. The assembly of claim 1, further including:

- a plastic material encapsulating the semiconductor device and the lead frame.

**18**. The assembly of claim 1, wherein at least one lead fingers of the second plurality of lead fingers includes an offset therein.

**19**. The assembly of claim 1, wherein the second plurality of lead fingers includes:

at least one lead finger having a portion thereof extending adjacent a portion of a lead finger of the first plurality of lead fingers, a portion thereof extending substantially adjacent an end of the opposed ends of the semiconductor device, a portion extending substantially opposed to an end of the opposed ends of the semiconductor device, and having a portion extending beyond a side of the opposed longer peripheral sides of the semiconductor device.

**20**. A lead frame for a semiconductor assembly having a semiconductor device having opposed longer peripheral sides, opposed ends, an active surface in substantially a first horizontal plane, an inactive bottom surface in substantially a second horizontal plane, and a plurality of bonds pads located on the active surface of the semiconductor device, a first portion of the plurality of bond pads located adjacent one of the opposed longer peripheral sides and a second portion of the plurality of bond pads located adjacent another of the opposed longer peripheral sides, said lead frame comprising:

- a first plurality of lead fingers extending substantially in the first horizontal plane of the active surface of the semiconductor device, each lead finger of the first plurality of lead fingers terminating in an end located adjacent a longer peripheral side of the opposed longer peripheral sides of the semiconductor device; and

- a second plurality of lead fingers extending below the inactive bottom surface of the semiconductor device, each lead finger of the second plurality of lead fingers having a portion thereof extending adjacent an end of the opposed ends of the semiconductor device and terminating in an end located adjacent the longer peripheral side of the opposed longer peripheral sides of the semiconductor device, at least one lead finger having a portion thereof extending adjacent a portion of a lead finger of the first plurality of lead fingers, a portion thereof extending substantially adjacent an end of the opposed ends of the semiconductor device, a portion extending substantially opposed to an end of the opposed ends of the semiconductor device, and having a portion extending beyond a side of the opposed longer peripheral sides of the semiconductor device; and

a die paddle.

**21**. The lead frame of claim 20, wherein the ends of the first plurality of lead fingers extend past the ends of adjacent lead fingers of the second plurality of lead fingers.

**22.** The lead frame of claim 20, wherein the ends of the second plurality of lead fingers extend past the ends of adjacent lead fingers of the first plurality of lead fingers.

23. The lead frame of claim 20, further including:

tape located on the second plurality of lead fingers.

- 24. The lead frame of claim 20, further including:

- tape located between the die paddle and the inactive bottom surface of the semiconductor device.

- 25. The lead frame of claim 20, further including:

- tape located between the die paddle and the second plurality of lead fingers and the inactive bottom surface of the semiconductor device.

26. The lead frame of claim 23, wherein the second plurality of lead fingers are adhesively attached to the tape.

**27**. The lead frame of claim 26, wherein the second plurality of lead fingers are adhesively attached to the tape using thermosetting adhesive.

**28**. The lead frame of claim 20, wherein the die paddle includes at least one portion thereon extending beyond a longer peripheral side of the opposed longer peripheral sides and at least another portion extending beyond an end of the opposed ends of the semiconductor device.

**29**. The lead frame of claim 20, wherein at least one lead fingers of the second plurality of lead fingers includes an offset therein.

**30**. A lead frame for a semiconductor assembly having a semiconductor device having opposed longer peripheral sides, opposed ends, an active surface in substantially a first horizontal plane, an inactive bottom surface in substantially a second horizontal plane, and a plurality of bonds pads located on the active surface of the semiconductor device, a first portion of the plurality of bond pads located adjacent one of the opposed longer peripheral sides and a second portion of the plurality of bond pads located adjacent another of the opposed longer peripheral sides, said lead frame comprising:

- a first plurality of lead fingers extending over at least a portion of the active surface of the semiconductor device, each lead finger of the first plurality of lead fingers terminating in an end located adjacent a longer peripheral side of the opposed longer peripheral sides of the semiconductor device; and

- a second plurality of lead fingers extending below the inactive bottom surface of the semiconductor device, some of the second plurality of lead fingers forming a die paddle, a plurality of lead fingers of the second plurality of lead fingers each having a portion thereof extending adjacent a portion of a lead finger of the first plurality of lead fingers, a portion thereof extending substantially adjacent an end of the opposed ends of the semiconductor device, a portion extending substantially opposed to an end of the opposed ends of the semiconductor device and extending adjacent a portion of the die paddle, and having a portion extending beyond a side of the opposed longer peripheral sides of the semiconductor device.

\* \* \* \* \*