## (12) 发明专利

(10) 授权公告号 CN 108352324 B

(45) 授权公告日 2022.08.09

(21) 申请号 201680064897.1

(22) 申请日 2016.12.28

(65) 同一申请的已公布的文献号

申请公布号 CN 108352324 A

(43) 申请公布日 2018.07.31

(30) 优先权数据

14/981,348 2015.12.28 US

(85) PCT国际申请进入国家阶段日

2018.05.07

(86) PCT国际申请的申请数据

PCT/US2016/069051 2016.12.28

(87) PCT国际申请的公布数据

W02017/117315 EN 2017.07.06

(73) 专利权人 德州仪器公司

地址 美国德克萨斯州

(72) 发明人 A·M·海德尔 Q·法里德

(74) 专利代理机构 北京律盟知识产权代理有限公司 11287

专利代理人 林斯凯

(51) Int.CI.

H01L 21/335 (2006.01)

H01L 21/20 (2006.01)

H01L 29/772 (2006.01)

(56) 对比文件

US 2013001586 A1, 2013.01.03

JP 2005340762 A, 2005.12.08

US 2006138446 A1, 2006.06.29

CN 104716241 A, 2015.06.17

CN 102956773 A, 2013.03.06

JP 2002164571 A, 2002.06.07

CN 102460739 A, 2012.05.16

JP 2007189028 A, 2007.07.26

JP 2002175994 A, 2002.06.21

US 5990495 A, 1999.11.23

邓旭光.蓝宝石, Si 和 SiC 衬底上GaN 和 AlGaN 的外延研究.《硕士学位论文电子期刊》.2014, (第03期),

审查员 王艳

权利要求书2页 说明书5页 附图3页

(54) 发明名称

用于族IIIA-N装置的非蚀刻性气体冷却外延堆叠

(57) 摘要

在所描述实例中，一种制造用于族IIIA-N晶体管的外延堆叠的方法(100)包含在沉积系统的沉积腔室中在衬底上沉积(102)至少一个族IIIA-N缓冲层。随后将至少一个族IIIA-N顶盖层沉积(103)于第一族IIIA-N缓冲层上。在从所述顶盖层沉积的沉积温度的冷却期间，供应到所述沉积腔室的气体混合物包含NH<sub>3</sub>和至少一种其它气体。所述气体混合物在所述沉积腔室中提供相对于所述顶盖层为非蚀刻性的环境，以使得在所述顶盖层的表面处：(a) 均方根 rms 粗糙度<10 Å；且(b) 大于(>)2nm深的凹点的凹点密度小于(<)每平方 μ m 10个凹点，其中平均凹点直径小于(<)

0.05 μ m。

CN 108352324 B

1.一种制造族IIIA-N晶体管的方法,其包括:

在沉积系统的沉积腔室中在衬底上以第一温度沉积至少第一族IIIA-N缓冲层,以及

在所述沉积系统的所述沉积腔室中在所述第一族IIIA-N缓冲层上以小于或等于所述第一温度的第二温度沉积至少一个族IIIA-N表面顶盖层,接着使用冷却工艺冷却所述衬底,所述冷却工艺将气体混合物提供到所述沉积腔室,直到冷却温度,在所述冷却温度处所述沉积腔室被排放,所述气体混合物包含NH<sub>3</sub>及至少一种其它气体,所述至少一种其它气体包含按体积计至多40%的H<sub>2</sub>,其中所述气体混合物在所述沉积腔室中提供相对于所述顶盖层为非蚀刻性的环境,以使得在所述顶盖层的表面处:(i)均方根rms粗糙度<10 Å;且(ii)大于2nm深的凹点的凹点密度小于每平方μm10个凹点,其中平均凹点直径小于0.05μm;

在所述族IIIA-N表面顶盖层上形成栅极介电层;

在所述栅极介电层上形成金属栅极电极;以及

形成具有到所述族IIIA-N表面顶盖层的源极触点的源极以及具有到所述族IIIA-N表面顶盖层的漏极触点的漏极。

2.根据权利要求1所述的方法,其进一步包括在沉积所述第一族IIIA-N缓冲层后,在沉积所述族IIIA-N顶盖层之前,使用所述冷却工艺将所述衬底从所述第一温度冷却到顶盖层沉积温度。

3.根据权利要求1所述的方法,其中所述沉积系统包括金属有机化学气相沉积MOCVD系统、分子束外延MBE系统,或氢化物气相外延HVPE系统。

4.根据权利要求1所述的方法,其中所述族IIIA-N顶盖层的厚度范围为3nm至50nm之间。

5.根据权利要求1所述的方法,其中所述第一族IIIA-N缓冲层和所述族IIIA-N表面顶盖层均包括GaN或AlGaN。

6.根据权利要求1所述的方法,其中所述衬底包括蓝宝石、硅或碳化硅SiC。

7.根据权利要求1所述的方法,其中所述气体混合物由N<sub>2</sub>和NH<sub>3</sub>构成。

8.根据权利要求1所述的方法,其中所述气体混合物不包括H<sub>2</sub>。

9.一种制造族IIIA-N晶体管的方法,其包括:

在沉积系统的沉积腔室中在衬底上以第一温度沉积族IIIA-N缓冲层,以及

使用包含NH<sub>3</sub>以及至少一种其它气体的气体混合物将所述衬底冷却到小于或等于所述第一温度的温度,使得所述沉积腔室中的环境相对于所述族IIIA-N缓冲层是非蚀刻性的;以及

在所述沉积系统的所述沉积腔室中在所述族IIIA-N缓冲层上沉积族IIIA-N顶盖层,接着使用冷却工艺冷却到小于或等于550°C,直到所述沉积腔室被排放,所述冷却工艺利用供应到所述沉积腔室的包含N<sub>2</sub>和NH<sub>3</sub>的气体混合物;

在所述族IIIA-N表面顶盖层上形成栅极介电层;

在所述栅极介电层上形成金属栅极电极;以及

形成具有到所述族IIIA-N表面顶盖层的源极触点的源极以及具有到所述族IIIA-N表面顶盖层的漏极触点的漏极。

10.根据权利要求9所述的方法,其中所述沉积系统包括金属有机化学气相沉积MOCVD系统、分子束外延MBE系统,或氢化物气相外延HVPE系统。

11. 根据权利要求9所述的方法,其中所述族IIIA-N顶盖层的厚度为3nm至50nm。

12. 根据权利要求9所述的方法,其中所述衬底是硅衬底。

13. 一种制造族IIIA-N晶体管的方法,其包括:

在沉积系统的沉积腔室中在衬底上以第一温度沉积至少第一族IIIA-N缓冲层;

在所述沉积系统的所述沉积腔室中在所述第一族IIIA-N缓冲层上以小于或等于所述第一温度的第二温度沉积至少一个族IIIA-N表面顶盖层,接着使用冷却工艺冷却所述衬底到550°C或小于550°C,所述冷却工艺将气体混合物提供到所述沉积腔室,直到冷却温度,在所述冷却温度处所述沉积腔室被排放,所述气体混合物包含NH<sub>3</sub>及至少一种其它气体,所述至少一种其它气体包含按体积计至多40%的H<sub>2</sub>;

在所述族IIIA-N表面顶盖层上形成栅极介电层;

在所述栅极介电层上形成金属栅极电极;以及

形成具有到所述族IIIA-N表面顶盖层的源极触点的源极以及具有到所述族IIIA-N表面顶盖层的漏极触点的漏极。

14. 根据权利要求13所述的方法,其中所述气体混合物在所述沉积腔室中提供相对于所述顶盖层为非蚀刻性的环境,以使得在所述顶盖层的表面处: (i) 均方根rms粗糙度小于1nm;且 (ii) 大于2nm深的凹点的凹点密度小于每平方μm 10个凹点,其中平均凹点直径小于0.05μm。

15. 根据权利要求13所述的方法,其中所述气体混合物不包括H<sub>2</sub>。

## 用于族IIIA-N装置的非蚀刻性气体冷却外延堆叠

### 技术领域

[0001] 本公开涉及族IIIA-N(例如,GaN)场效应晶体管(FET),且更具体地说涉及用于此类FET的缓冲层。

### 背景技术

[0002] 氮化镓(GaN)为常用的族IIIA-N材料,其中族IIIA元素(例如Ga、硼、铝、铟和铊)有时也被称作族13元素。GaN为具有纤维锌矿(Wurtzite)晶体结构的二元IIIA/V直接带隙半导体。其在室温下的3.4eV的相对较宽带隙(对比硅的1.1eV)使其具有用于光学电子、大功率装置和高频电子装置中的广泛多种应用的具体特性。

[0003] 由于GaN和硅具有显著的热膨胀系数失配,因此缓冲层常用于硅衬底与GaN层之间以用于应变管理。此缓冲技术形成通常用于高电子迁移率晶体管(HEMT)(也被称作异质结构FET(HFET))或掺杂调变的FET(MODFET)装置的大部分硅上GaN(GaN-on-Si)的基础,所述掺杂调变的FET装置为场效应晶体管,并入有具有不同带隙的两种材料之间的接合点(即异质结)作为代替掺杂区域的沟道(对于MOSFET通常为此情况)。用于此类装置的一些缓冲布置使用超晶格结构或递变缓冲结构。

[0004] GaN顶盖层沉积在沉积至少一个缓冲层之后。常规的缓冲层和顶盖层沉积工艺在其对应的沉积温度的冷却期间使用NH<sub>3</sub>和H<sub>2</sub>。H<sub>2</sub>体积流率大体上为NH<sub>3</sub>体积流率的若干倍。

### 发明内容

[0005] 在所描述实例中,一种制造用于族IIIA-N晶体管的外延堆叠的方法包含在沉积系统的沉积腔室中在衬底上沉积至少一个族IIIA-N缓冲层。随后将至少一个族IIIA-N顶盖层沉积于第一族IIIA-N缓冲层上。在从所述顶盖层沉积的沉积温度的冷却期间,供应到所述沉积腔室的气体混合物包含NH<sub>3</sub>和至少一种其它气体。所述气体混合物在所述沉积腔室中提供相对于所述顶盖层为非蚀刻性的环境,以使得在所述顶盖层的表面处:(a)

均方根(rms)粗糙度<10 Å;且(b)大于(>)2nm深的凹点的凹点密度小于(<)每平方μm 10个凹点,其中平均凹点直径小于(<)0.05μm。

### 附图说明

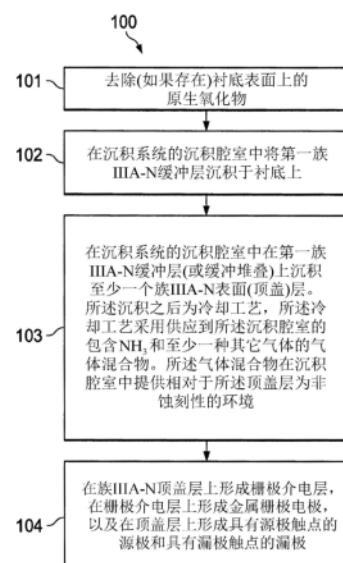

[0006] 图1是根据实例实施例的制造包含用于功率族IIIA-N晶体管的至少一个低疵点密度顶盖层的外延层堆叠的实例方法中的步骤的流程图。

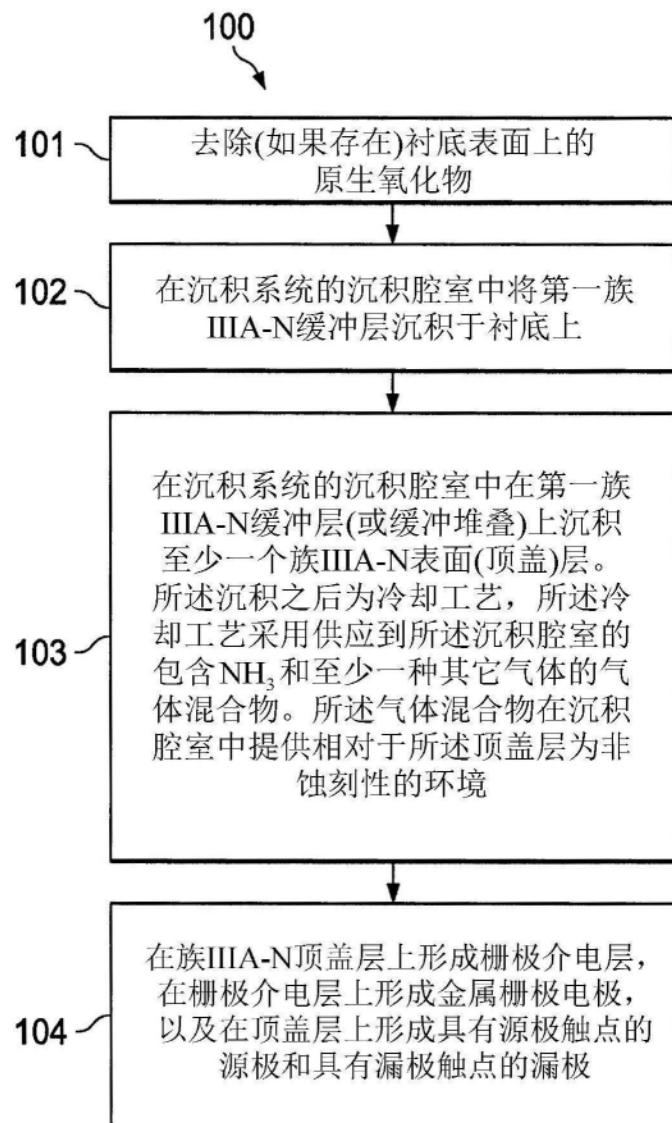

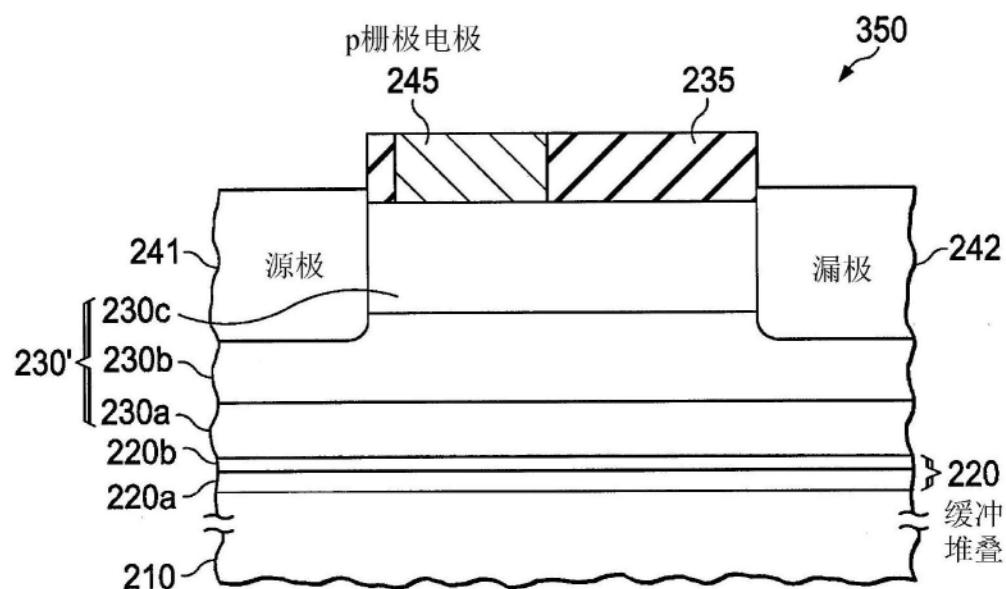

[0007] 图2是根据实例实施例的包含在其上具有低疵点密度顶盖层的族IIIA-N缓冲层的实例装置堆叠的截面绘图。

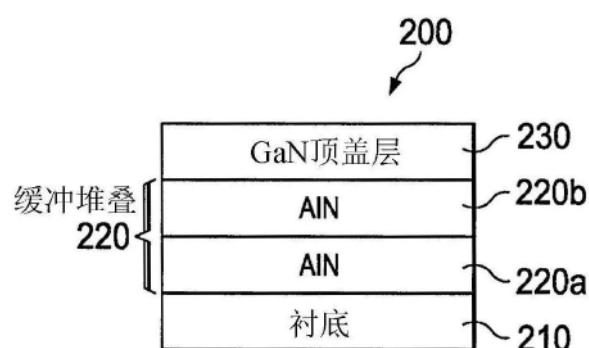

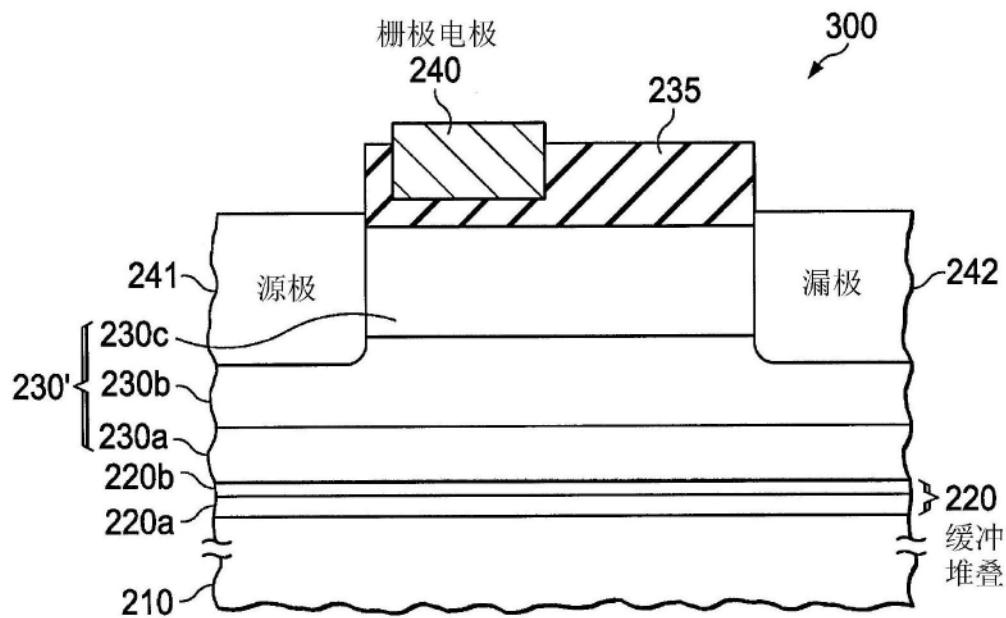

[0008] 图3A是根据实例实施例的外延层堆叠具有低疵点密度顶盖层的实例耗尽型高电子迁移率晶体管(HEMT)的截面视图。

[0009] 图3B是根据实例实施例的外延层堆叠具有低疵点密度顶盖层的具有常闭栅极的实例增强型HEMT的截面视图。

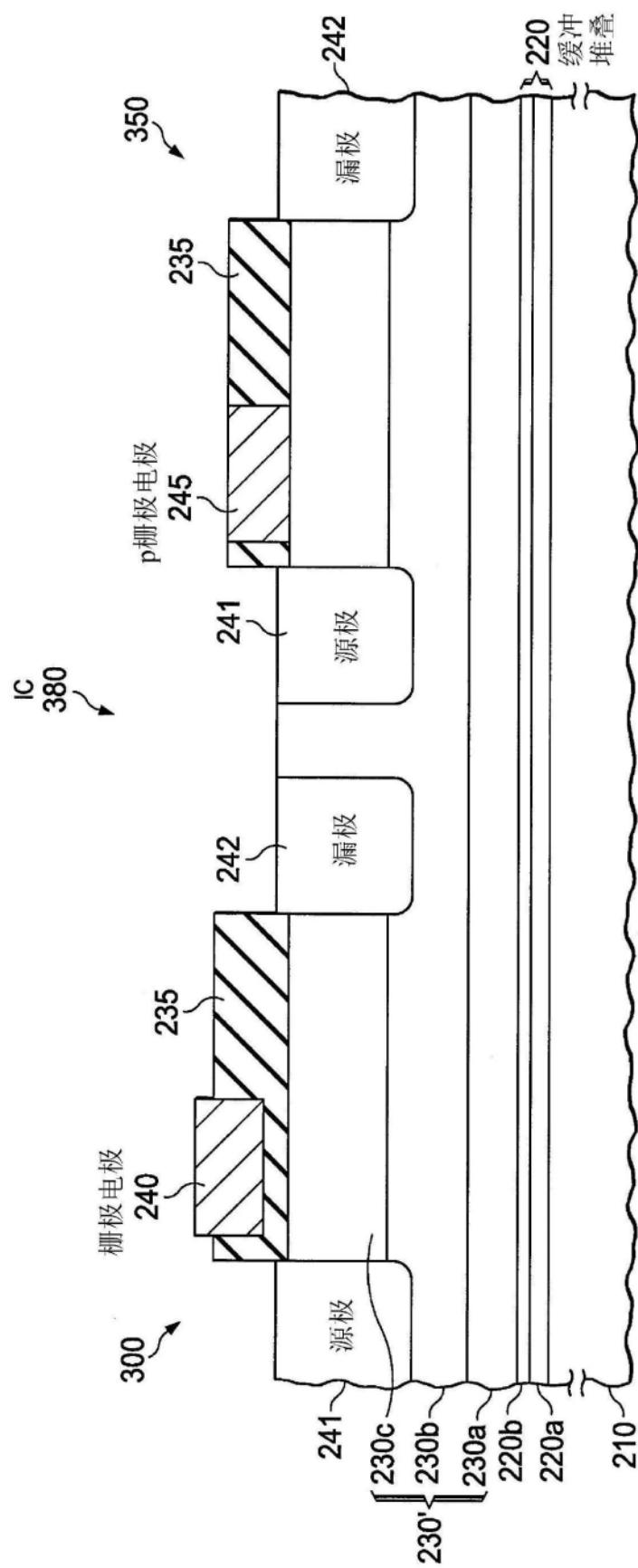

[0010] 图3C是包含均在缓冲堆叠上的相同低疵点密度顶盖层上的图3A中所示的耗尽型HEMT功率装置和图3B中所示的增强型HEMT的实例IC的截面视图。

## 具体实施方式

[0011] 图式未必按比例绘制。在图式中，相同参考编号表示类似或等效元件。一些图解说明的动作或事件可与其它动作或事件以不同顺序和/或同时发生。此外，实施根据本说明书的方法可能不需要一些图解说明的动作或事件。

[0012] 实例实施例认识到，在族IIIA-N装置的外延族IIIA-N顶盖层之后的冷却期间供应到沉积腔室的常规的NH<sub>3</sub>和H<sub>2</sub>气体混合物在冷却之后在顶盖层中产生凹点，在可能在发生优先蚀刻的后续蚀刻/清洁之后可能恶化。H<sub>2</sub>可能侵蚀族IIIA-N顶盖层（例如GaN或AlGaN），从而产生凹点。顶盖层中的疵点（例如凹点）使在功率晶体管中产生疵点，且如果其以足够高密度存在，则可能导致装置故障。

[0013] 在所描述实例中，顶盖层沉积在于衬底上沉积至少一个缓冲层之后，使用冷却工艺，所述冷却工艺使用包含NH<sub>3</sub>和至少一种其它气体的供应的气体混合物，其中所述气体混合物在沉积腔室中提供相对于第一族IIIA-N层为非蚀刻性的环境。如本文所使用，“非蚀刻性”是指顶盖层的所得表面具有：(a)<10 Å的均方根(rms)粗糙度；以及(b)小于(%)每平方μm 10个凹点的大于(%)2nm深的凹点层的凹点密度，其中平均凹点直径小于(%)0.05μm。一个实例使用在冷却期间仅含有NH<sub>3</sub>和N<sub>2</sub>的气体混合物。

[0014] 图1是根据实例实施例的制造包含用于族IIIA-N功率晶体管的低疵点密度顶盖层的外延层堆叠的实例方法100中的步骤的流程图。可使用金属有机化学气相沉积(MOCVD)系统、分子束外延(MBE)系统或氢化物气相外延(HVPE)系统在单次程序中外延沉积所有对应的缓冲和族IIIA-N顶盖层。

[0015] 步骤101包括去除（如果存在）衬底（例如，晶片）表面上的原生氧化物。所述衬底可包括蓝宝石、硅或碳化硅(SiC)。

[0016] 步骤102包括在沉积系统的沉积腔室中使用大体上为1050°C到1300°C的沉积温度将至少第一族IIIA-N缓冲层沉积于衬底上。缓冲层可为1微米至10微米厚。本文中所描述的族IIIA-N缓冲层和顶盖层可由通式Al<sub>x</sub>Ga<sub>y</sub>In<sub>1-x-y</sub>N表示，其中0<x≤1,0≤y≤1,0<x+y≤1。举例来说，族IIIA-N层可包括AlN、AlGaN、AlInN和AlInGaN中的至少一种。可包含如硼(B)的其它族IIIA元素，且N可部分地被磷(P)、砷(As)或锑(Sb)替代。族IIIA氮化物化合物半导体中的每一个可含有选自Si、C、Ge、Se、O、Fe、Mn、Mg、Ca、Be、Cd以及Zn的任选掺杂剂。

[0017] 缓冲层沉积可任选地后续接着从较高缓冲层沉积温度（例如，1250°C）冷却到顶盖层沉积的较低沉积温度（例如，900°C到1050°C）的冷却工艺，所述冷却工艺使用供应到沉积腔室的包含NH<sub>3</sub>和至少一种其它气体的气体混合物，其中所述气体混合物在沉积腔室中提供相对于第一族IIIA-N缓冲层为非蚀刻性的环境。此冷却工艺期间的减速率大体上为5°C/min到40°C/min。其它气体可为N<sub>2</sub>、Ar、He、Ne、Kr及或此类气体的组合。在一个特定实施例中，以2至20升/分钟来供应NH<sub>3</sub>，且以50至150升/分钟来供应N<sub>2</sub>。在混合物保持非蚀刻性的情况下，氢气(H<sub>2</sub>)可提供按体积计至多约40%的H<sub>2</sub>。

[0018] 在步骤102之后，所述方法可包括在第一族IIIA-N缓冲层上沉积至少第二族IIIA-N缓冲层以形成缓冲堆叠。其它缓冲层沉积步骤可使用与上文所描述的步骤102相同的低疵

点密度沉积工艺,包含所描述的冷却工艺。

[0019] 步骤103包括在第一族IIIA-N缓冲层(或缓冲堆叠)上沉积至少一个族IIIA-N顶盖层。如上文所描述,顶盖层沉积温度大体上为900°C至1050°C。

[0020] 顶盖层沉积之后为从沉积温度到大体上300°C至550°C的温度的冷却工艺,所述冷却工艺使用包含NH<sub>3</sub>和至少一种其它气体的气体混合物,其中所述气体混合物在沉积腔室中提供相对于所述顶盖层为非蚀刻性的环境。如上文所描述,本文中的“非蚀刻性”是指所得顶盖层具有:(a)<10 Å的均方根(rms)粗糙度;以及(b)小于(<)每平方μm 10个凹点的大于(>)2nm深的凹点层的凹点密度,其中平均凹点直径小于(<)0.05μm。表面粗糙度可由原子力显微镜(AFM)系统来测量,而凹点密度可由疵点分析工具来测量,例如KLA-Tencor CANDELA® 8620检测系统。

[0021] 其它气体可为N<sub>2</sub>、Ar、He、Ne、Kr及或此类气体的组合。在一个特定实施例中,以2至20升/分钟来供应NH<sub>3</sub>,且以50至150升/分钟来供应N<sub>2</sub>。在混合物保持非蚀刻性的情况下,氢气(H<sub>2</sub>)可提供按体积计至多约40%的H<sub>2</sub>。此冷却工艺期间的减速率大体上为5°C/min至40°C/min,且如上文所描述可冷却至300°C至550°C的温度,其中沉积腔室排放到大气,且随后大体上从沉积腔室去除晶舟。

[0022] 步骤104包括在顶盖层上形成栅极介电层(例如,SiN、SiON、Al2O3、AlN、氧化硅或任何这些层的组合),在栅极介电层上形成金属栅极电极,以及在顶盖层上形成具有源极触点的源极和具有漏极触点的漏极。在一个实施例中,栅极电极可包括TiW掺合物。在一个特定实施例中,可通过溅镀例如Ti/A1/TiN的金属堆叠来形成源极和漏极。

[0023] 图2是根据实例实施例的包含包括在衬底(例如,硅)210上均展示为AlN层的第一族IIIA-N缓冲层220a和第二族IIIA-N缓冲层220b的多层缓冲堆叠(缓冲层堆叠)220的实例装置堆叠200的截面绘图。展示为GaN层的族IIIA-N顶盖层230位于第二族IIIA-N缓冲层220b上,其中族IIIA-N顶盖层230具有使用顶盖层冷却工艺形成的低疵点密度,所述冷却工艺在冷却期间使用沉积腔室中相对于顶盖层为非蚀刻性的环境。在另一布置中,第一族IIIA-N缓冲层220a包括AlN,第二族IIIA-N缓冲层220b包括GaN,且族IIIA-N顶盖层230包括AlGaN。可用作HEMT层的族IIIA-N顶盖层230的实例厚度范围可为5Å至300Å,第二族IIIA-N缓冲层220b为50Å至300Å,且第一族IIIA-N缓冲层220a为0.1μm至5μm。

[0024] 实例实施例的优点包含沉积包含基本上空的且无裂纹的顶盖层的基本上空的且无裂纹的外延GaN膜堆叠的能力,以使得能够获得更高的晶体管击穿电压、更低泄漏电流以及减少的衬底弓曲/翘曲。举例来说,功率晶体管可提供在每mm<sup>2</sup>为1μamp的泄漏电流密度下至少100V的击穿电压。

[0025] 可使用所描述外延堆叠的功率半导体装置的实例包含HEMT、双异质结构场效应晶体管(DHFET)、异质结双极晶体管(HBT)以及双极结晶体管(BJT)。HEMT(也被称作异质结构FET(HFET)或掺杂调变的FET(MODFET))为场效应晶体管,并入有具有不同带隙的两种半导体材料之间的接合点(即异质结)作为代替掺杂区域的二维电子气(2DEG)沟道层(对于金属氧化物半导体场效应晶体管(MOSFET)通常为此情况)。HEMT包含具有例如GaN和AlGaN的宽带隙的化合物半导体。由于GaN和IIIA-N材料系统中的高电子饱和度速率,GaN HEMT中的电子迁移率高于其它一般晶体管(例如,金属氧化物半导体场效应晶体管(MOSFET))的电子迁

移率。

[0026] 图3A是根据实例实施例的实例耗尽型HEMT功率装置300的截面视图,其中展示了所描述的外延层堆叠,其在衬底210的缓冲层堆叠220上包含族IIIA-N顶盖层230'。展示HEMT装置300具有栅极介电层235,例如包括氮化硅或氮氧化硅。族IIIA-N顶盖层230'为低疵点密度顶盖层,其中族IIIA-N顶盖层230'的表面具有:(a)<10 Å的均方根(rms)粗糙度;以及(b)小于(<)每平方 $\mu\text{m}$  10个凹点的大于(>)2nm深的凹点层的凹点密度,其中平均凹点直径小于(<)0.05 $\mu\text{m}$ 。在此实施例中,族IIIA-N顶盖层230'可包括夹在最顶部(第一)GaN层230c与位于第二族IIIA-N缓冲层220b上的最底部(第二)GaN层230a之间的AlGaN层230b。最顶部GaN层230c和最底部GaN层230a大体上各自具有 $1\times 10^{15}\text{cm}^{-3}$ 与 $1\times 10^{18}\text{cm}^{-3}$ 之间的掺杂浓度。掺杂剂可包含碳、镁、硅或锌,或此类掺杂剂的组合。

[0027] HEMT功率装置300可为离散装置,或IC上的许多装置中的一个。更一般地说,族IIIA-N顶盖层230'可包含GaN、InN、AlN、AlGaN、AlInN、InGaN以及AlInGaN中的一或多个。如上文所描述,族IIIA-N层可包含其它族IIIA元素,例如B,且N可部分地由P、As或Sb替代,且还可含有任选掺杂剂。在另一特定实例中,族IIIA-N顶盖层230'可包括 $\text{Al}_x\text{Ga}_y\text{N}$ 层或 $\text{In}_x\text{Al}_y\text{N}$ 层顶部上的GaN层。另一具体实例为族IIIA-N顶盖层230',三层堆叠可包括AlGaN上的InAlN上的GaN。

[0028] HEMT功率装置300包含源极241、漏极242以及栅极电极240。栅极电极240位于源极241与漏极242之间,比漏极242更接近源极241。源极241、漏极242和栅极电极240可由金属和/或金属氮化物形成,但实例实施例不限于此。

[0029] 图3B是根据实例实施例的具有常闭栅极的实例增强型HEMT功率装置350的截面视图,其具有在展示为衬底210上的缓冲层堆叠220的缓冲层上的族IIIA-N顶盖层230'。族IIIA-N顶盖层230'为低疵点密度顶盖层,其中族IIIA-N顶盖层230'的表面具有:(a)<10 Å的均方根(rms)粗糙度;以及(b)小于(<)每平方 $\mu\text{m}$  10个凹点的大于(>)2nm深的凹点层的凹点密度,其中平均凹点直径小于(<)0.05 $\mu\text{m}$ 。在此实施例中,栅极电极为与族IIIA-N顶盖层230c(例如,GaN层)直接接触的p掺杂栅极电极245(展示为p-GATE ELECTRODE)。图3C是包含均使用相同顶盖层和缓冲堆叠的图3A中所示的耗尽型HEMT功率装置300和图3B中所示的增强型HEMT的实例IC 380的截面视图。

[0030] 实例实施例进一步由以下实例说明。

[0031] 针对使用 $\text{NH}_3/\text{N}_2$ 顶盖层冷却形成的Si衬底上的顶盖层相较针对顶盖层冷却的使用 $\text{NH}_3/\text{H}_2$ 气体混合物形成的已知顶盖层来采集AFM数据。在一个实例中, $\text{NH}_3/\text{N}_2$ 流量比为1:10, $\text{NH}_3$ 的流量范围为2至20升/分钟,且 $\text{N}_2$ 的范围为50至150升/分钟。根据来自若干不同程序的晶片的数据,沉积时,使用所描述的 $\text{NH}_3/\text{N}_2$ 顶盖层冷却处理的晶片一致地未表现出表面凹点。相比之下,依据来自若干不同程序的晶片的数据,使用已知 $\text{NH}_3/\text{H}_2$ 顶盖层冷却处理的晶片一致地表现出大小在10nm到200nm范围内的每 $\text{cm}^2$ 的表面凹点 $1\times 10^{10}$ 。

[0032] 还发现在后续蚀刻/清洁之后顶盖层中的凹点可能恶化,其中在疵点部位发现发生优先蚀刻。具有来自 $\text{NH}_3/\text{N}_2$ 冷却顶盖层工艺的顶盖层以及使用针对顶盖层冷却的 $\text{N}_2/\text{H}_2$ 气体混合物形成的已知顶盖层的晶片经提交用于两组清洁工艺。针对两种顶盖层工艺对晶片执行AFM分析。针对具有来自 $\text{NH}_3/\text{N}_2$ 冷却顶盖层的顶盖层的晶片,凹点的深度在沉积时为约0.7nm至1nm,其在两组清洁工艺之后保持在约0.7nm至1nm。针对具有来自已知 $\text{NH}_3/\text{N}_2$ 冷却工

艺的顶盖层的晶片,凹点的深度在沉积时为约1nm至3nm,其在两组清洁工艺之后增加到6nm至10nm。

[0033] 获得高温反向偏压 (HTRB) HEMT装置数据,其中顶盖层包括GaN,且缓冲层包括使用N<sub>2</sub>/NH<sub>3</sub>顶盖层冷却形成的AlGaN以及使用已知NH<sub>3</sub>/H<sub>2</sub>顶盖层冷却形成的控制GaN顶盖层。

[0034] 由于GaN顶盖层凹点,HTRB故障与安全性故障相关联。具有使用已知N<sub>2</sub>/H<sub>2</sub>顶盖层冷却形成的控制GaN顶盖层的HEMT具有5%至10%的老化故障率,而具有使用NH<sub>3</sub>/N<sub>2</sub>顶盖层冷却形成的GaN顶盖层的HEMT具有<2%HTRB故障的故障率。

[0035] 实例实施例可用于形成半导体管芯,所述半导体裸片可集成到多种组件流中以形成多种不同装置和相关产品。半导体裸片中可包含各种元件和/或其上可包含各种层,包含势垒层、介电层、装置结构、有源元件和无源元件,包含源极区域、漏极区域、位线、基极、发射级、集极、导电线路和导电通孔。此外,半导体裸片可由多种工艺形成,包含双极、绝缘栅双极晶体管 (IGBT)、CMOS、BiCMOS 和 MEMS。

[0036] 在所描述的实施例中可能进行修改,且其它实施例在权利要求的范围内为可能的。

图1

图2

图3A

图3B

图3C