(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6736871号

(P6736871)

(45) 発行日 令和2年8月5日(2020.8.5)

(24) 登録日 令和2年7月20日(2020.7.20)

|                     |           |

|---------------------|-----------|

| (51) Int.Cl.        | F 1       |

| HO3M 1/38 (2006.01) | HO3M 1/38 |

| HO3M 1/12 (2006.01) | HO3M 1/12 |

| HO3M 1/06 (2006.01) | HO3M 1/06 |

| HO3B 5/32 (2006.01) | HO3B 5/32 |

| HO3M 1/46 (2006.01) | HO3M 1/46 |

請求項の数 13 (全 42 頁)

(21) 出願番号 特願2015-236404 (P2015-236404)

(22) 出願日 平成27年12月3日 (2015.12.3)

(65) 公開番号 特開2017-103661 (P2017-103661A)

(43) 公開日 平成29年6月8日 (2017.6.8)

審査請求日 平成30年11月29日 (2018.11.29)

(73) 特許権者 000002369

セイコーエプソン株式会社

東京都新宿区新宿四丁目1番6号

(74) 代理人 100104710

弁理士 竹腰 昇

(74) 代理人 100090479

弁理士 井上 一

(74) 代理人 100124682

弁理士 黒田 泰

(72) 発明者 加納 新之助

長野県諏訪市大和3丁目3番5号 セイコーエプソン株式会社内

審査官 及川 尚人

最終頁に続く

(54) 【発明の名称】回路装置、発振器、電子機器及び移動体

## (57) 【特許請求の範囲】

## 【請求項 1】

結果データを記憶するレジスター部と、

前記結果データをD/A変換してD/A変換電圧を出力するD/A変換器と、

入力電圧と、前記D/A変換器からの前記D/A変換電圧との比較を行う比較部と、

前記比較部の比較結果に基づいて判定処理を行い、前記判定処理に基づいて前記結果データの更新処理を行って、前記入力電圧のA/D変換結果データを求める処理部と、

を含み、

前記処理部は、

前記A/D変換結果データのMSB側の前記判定処理を、第1の判定期間で行い、前記A/D変換結果データのLSB側の前記判定処理を、前記第1の判定期間よりも長い期間である第2の判定期間で行い、前記A/D変換結果データの前記MSB側と前記LSB側の間のビット範囲における前記判定処理を、前記第1の判定期間よりも長く、且つ、前記第2の判定期間よりも短い第3の判定期間で行い、

前記処理部は、

前記比較部での比較期間の長さと、前記入力電圧に対応する電荷を蓄積するサンプル期間の長さを設定することで、前記第1の判定期間、前記第2の判定期間及び前記第3の判定期間の長さを設定し、

前記第3の判定期間は、前記第1の判定期間に比べて少なくとも前記比較期間の長さが長く、

10

20

前記第2の判定期間は、前記第1の判定期間に比べて前記比較期間及び前記サンプル期間の長さが長いことを特徴とする回路装置。

【請求項2】

請求項1に記載の回路装置において、

前記処理部は、

前記回路装置の起動期間の前半期間において、前記A/D変換結果データの前記MSB側の前記判定処理を行い、

前記回路装置の前記起動期間の後半期間において、前記A/D変換結果データの前記LSB側の前記判定処理を行うことを特徴とする回路装置。

【請求項3】

請求項2に記載の回路装置において、

前記処理部は、

前記起動期間において、前記MSB側の前記判定処理を前記第1の判定期間で行い、前記LSB側の前記判定処理を前記第2の判定期間で行う第1のA/D変換方式で、前記A/D変換結果データを求め、

前記起動期間の後の通常動作期間において、前記起動期間における前記A/D変換結果データを初期値として、前記第1のA/D変換方式とは異なる第2のA/D変換方式で前記A/D変換結果データを求める特徴とする回路装置。

【請求項4】

請求項3に記載の回路装置において、

A/D変換でのデータの最小分解能を LSBとしたとき、

前記処理部は、

前記第2のA/D変換方式として、

第1の出力タイミングの前記A/D変換結果データを第1のA/D変換結果データとし、前記第1の出力タイミングの次の第2の出力タイミングの前記A/D変換結果データを第2のA/D変換結果データとしたとき、前記第1のA/D変換結果データに対する前記第2のA/D変換結果データの変化が  $k \times LSB$  ( $k$  は  $k < j$  を満たす整数、 $j$  は A/D変換の分解能を表す整数) 以下となるように、前記A/D変換結果データを求める処理を行うことを特徴とする回路装置。

【請求項5】

請求項4に記載の回路装置において、

前記比較部は、

前記第1の出力タイミングでの前記A/D変換結果データに対応する前回の最終結果データを前記D/A変換器で変換した前記D/A変換電圧と、前記入力電圧とを比較して第1の比較結果を出力し、

前記第1の出力タイミングでの前記A/D変換結果データを  $k \times LSB$  以下の範囲で更新し、更新後のデータを前記D/A変換器で変換した前記D/A変換電圧と、前記入力電圧とを比較して第2の比較結果を出力し、

前記処理部は、

前記第1の比較結果及び前記第2の比較結果に基づく前記判定処理を行い、前記判定処理に基づいて、前記第1の出力タイミングでの前記A/D変換結果データを  $k \times LSB$  以下の範囲で更新して、前記第2の出力タイミングでの前記A/D変換結果データとして決定する前記更新処理を行うことを特徴とする回路装置。

【請求項6】

請求項1乃至5のいずれか一項に記載の回路装置において、

前記処理部は、

前記A/D変換結果データを、所与のビット幅で複数のビット範囲に区画し、区画された各ビット範囲においてMSB側からLSB側にビット値を決定していくことを特徴とする回路装置。

【請求項7】

10

20

30

40

50

請求項6に記載の回路装置において、

前記A/D変換結果データが第1～第N（Nは2以上の整数）のビット範囲に区画される場合に、

前記A/D変換結果データのMSB側の前記判定処理は、第1～第p（pは1以上の整数）のビット範囲に対する判定処理を含み、

前記A/D変換結果データのLSB側の前記判定処理は、第q（qはp < q < Nを満たす整数）～第Nのビット範囲に対する判定処理を含むことを特徴とする回路装置。

#### 【請求項8】

請求項7に記載の回路装置において、

前記処理部は、

10

前記第1～第Nのビット範囲のうちの、第r（rは2 < r < Nを満たす整数）のビット範囲での前記判定処理の結果に基づいて、前記第rのビット範囲のMSB側の第r-1のビット範囲での前記判定処理の結果を変更することを特徴とする回路装置。

#### 【請求項9】

請求項1乃至8のいずれか一項に記載の回路装置において、

前記入力電圧は、温度センサー部からの温度検出電圧であり、

前記A/D変換結果データは、前記温度検出電圧のA/D変換結果である温度検出データであることを特徴とする回路装置。

#### 【請求項10】

請求項9に記載の回路装置において、

20

前記D/A変換器と、前記比較部と、前記処理部とを含むA/D変換回路と、

前記温度検出データに基づく周波数制御データを出力するデジタル信号処理部と、

前記デジタル信号処理部からの前記周波数制御データと振動子を用いて、前記周波数制御データにより設定される発振周波数の発振信号を生成する発振信号生成回路と、

を含むことを特徴とする回路装置。

#### 【請求項11】

請求項10に記載の回路装置と、

前記振動子と、

を含むことを特徴とする発振器。

#### 【請求項12】

30

請求項1乃至10のいずれか一項に記載の回路装置を含むことを特徴とする電子機器。

#### 【請求項13】

請求項1乃至10のいずれか一項に記載の回路装置を含むことを特徴とする移動体。

#### 【発明の詳細な説明】

##### 【技術分野】

##### 【0001】

本発明は、回路装置、発振器、電子機器及び移動体等に関する。

##### 【背景技術】

##### 【0002】

従来、アナログ信号をデジタルデータに変換するアナログデジタル変換（以下A/D変換）、及びA/D変換を行う回路であるA/D変換回路が広く知られている。A/D変換回路の方式としては、フラッシュ型、逐次比較型、逐次積分型等、種々の方式が知られている。例えば特許文献1には、逐次比較型のA/D変換を実行する一手法が開示されている。

40

##### 【0003】

また、温度センサー部からの温度検出信号（アナログ信号）をA/D変換した結果である温度検出データを用いる種々の回路が知られている。例えば、従来より、TCXO（temperature compensated crystal oscillator）と呼ばれる温度補償型発振器が知られている。このTCXOは、例えば携帯通信端末、GPS関連機器、ウェアラブル機器、又は車載機器などにおける基準信号源等として用いられている。デジタル方式の温度補償型発振器であるDTCXOの従来技術としては特許文献2に開示される技術が知られている。

50

**【先行技術文献】****【特許文献】****【0004】****【特許文献1】特開2011-223404号公報****【特許文献2】特開昭64-82809号公報****【発明の概要】****【発明が解決しようとする課題】****【0005】**

A / D 変換の結果である A / D 変換結果データを高速で（短い A / D 変換期間の間に）出力することに対する要求がある。例えば、D T C X O 等のデジタル方式の発振器では、

出力である発振周波数を短時間で安定させるという要求が生じる場合があり、その際には

、温度補償処理に用いる温度検出データを高速で出力できなくてはならない。10

**【0006】**

しかし、特許文献1では A / D 変換の速度については触れられていない。また、特許文献2は、冗長変換アルゴリズムを用いる A / D 変換器、特にその効率的な試験方法を開示するものであって、具体的な高速化手法を開示するものではない。

**【0007】**

本発明の幾つかの態様によれば、逐次比較型に準ずる構成において、高速且つ高精度での A / D 変換を実現する回路装置、発振器、電子機器及び移動体等を提供できる。

**【課題を解決するための手段】****【0008】**

本発明の一態様は、途中結果データ又は最終結果データである結果データを記憶するレジスター部と、前記結果データを D / A 変換して D / A 変換電圧を出力する D / A 変換器と、入力電圧と、前記 D / A 変換器からの前記 D / A 変換電圧との比較を行う比較部と、前記比較部の比較結果に基づいて判定処理を行い、前記判定処理に基づいて前記結果データの更新処理を行って、前記入力電圧の A / D 変換結果データを求める処理部と、を含み、前記処理部は、前記 A / D 変換結果データの M S B 側の前記判定処理を、第1の判定期間で行い、前記 A / D 変換結果データの L S B 側の前記判定処理を、前記第1の判定期間よりも長い期間である第2の判定期間で行う回路装置に関係する。20

**【0009】**

本発明の一態様では、D / A 変換電圧と入力電圧との比較結果に基づく判定処理を行って結果データの更新処理を行うことで、入力電圧の A / D 変換結果データを求める構成の回路装置において、M S B 側と L S B 側とで判定期間の長さに差を設ける。このようにすれば、各ビット（ビット範囲）に適した判定期間を設定することができるため、精度のよい A / D 変換を高速で実現することなどが可能になる。30

**【0010】**

また、本発明の一態様では、前記処理部は、前記回路装置の起動期間の前半期間において、前記 A / D 変換結果データの前記 M S B 側の前記判定処理を行い、前記回路装置の前記起動期間の後半期間において、前記 A / D 変換結果データの前記 L S B 側の前記判定処理を行ってもよい。40

**【0011】**

このようにすれば、回路装置の起動期間において本実施形態の A / D 変換を行うことなどが可能になる。

**【0012】**

また、本発明の一態様では、前記処理部は、前記起動期間において、前記 M S B 側の前記判定処理を前記第1の判定期間で行い、前記 L S B 側の前記判定処理を前記第2の判定期間で行う第1の A / D 変換方式で、前記 A / D 変換結果データを求め、前記起動期間の後の通常動作期間において、前記起動期間における前記 A / D 変換結果データを初期値として、前記第1の A / D 変換方式とは異なる第2の A / D 変換方式で前記 A / D 変換結果データを求めてよい。50

**【 0 0 1 3 】**

このようにすれば、起動期間と、起動期間の後の通常動作期間とで、A / D 変換の方式を切り替えること等が可能になる。

**【 0 0 1 4 】**

また、本発明の一態様では、A / D 変換でのデータの最小分解能を L S B とした場合に、前記処理部は、前記第2のA / D 変換方式として、第1の出力タイミングの前記A / D 変換結果データを第1のA / D 変換結果データとし、前記第1の出力タイミングの次の第2の出力タイミングの前記A / D 変換結果データを第2のA / D 変換結果データとした場合に、前記第1のA / D 変換結果データに対する前記第2のA / D 変換結果データの変化が  $k \times L S B$  ( $k$  は  $k < j$  を満たす整数、 $j$  は A / D 変換の分解能を表す整数) 以下となるように、前記A / D 変換結果データを求める処理を行ってもよい。10

**【 0 0 1 5 】**

このようにすれば、A / D 変換結果データの急激な変化を抑制し、当該変化に起因する不具合を抑止すること等が可能になる。

**【 0 0 1 6 】**

また、本発明の一態様では、前記第1の出力タイミングでの前記A / D 変換結果データに対応する前回の前記最終結果データを前記D / A 変換器で変換した前記D / A 変換電圧と、前記入力電圧とを比較して第1の比較結果を出力し、前記第1の出力タイミングでの前記A / D 変換結果データを  $k \times L S B$  以下の範囲で更新し、更新後のデータを前記D / A 変換器で変換した前記D / A 変換電圧と、前記入力電圧とを比較して第2の比較結果を出力し、前記処理部は、前記第1の比較結果及び前記第2の比較結果に基づく前記判定処理を行い、前記判定処理に基づいて、前記第1の出力タイミングでの前記A / D 変換結果データを  $k \times L S B$  以下の範囲で更新して、第2の出力タイミングでの前記A / D 変換結果データとして決定する前記更新処理を行ってもよい。20

**【 0 0 1 7 】**

このようにすれば、複数回の比較の結果に基づいて、前回の最終結果データから  $k \times L S B$  以下の範囲で変化した値を、今回の最終結果データ(温度検出データ)として決定することが可能になる。

**【 0 0 1 8 】**

また、本発明の一態様では、前記処理部は、前記比較部での比較期間の長さを設定することで、前記第1の判定期間及び前記第2の判定期間の長さを設定してもよい。30

**【 0 0 1 9 】**

このようにすれば、比較部の比較期間の設定により、判定間に差を設けることが可能になる。

**【 0 0 2 0 】**

また、本発明の一態様では、前記処理部は、前記A / D 変換結果データを、所与のビット幅で複数のビット範囲に区画し、区画された各ビット範囲において M S B 側から L S B 側にビット値を決定しててもよい。

**【 0 0 2 1 】**

このようにすれば、ビット範囲単位でA / D 変換を行うこと等が可能になる。40

**【 0 0 2 2 】**

また、本発明の一態様では、前記A / D 変換結果データが第1～第N( $N$ は2以上の整数)のビット範囲に区画される場合に、前記A / D 変換結果データのM S B 側の前記判定処理は、第1～第p( $p$ は1以上の整数)のビット範囲に対する判定処理を含み、前記A / D 変換結果データのL S B 側の前記判定処理は、第q( $q$ は

$p < q < N$ を満たす整数)～第Nのビット範囲に対する判定処理を含んでもよい。

**【 0 0 2 3 】**

このようにすれば、デジタルデータを複数のビット範囲に区画し、そのうちのM S B を含む1又は複数のビット範囲をM S B 側とし、L S B を含む1又は複数のビット範囲をL S B 側としてA / D 変換を実行すること等が可能になる。50

**【0024】**

また、本発明の一態様では、前記処理部は、前記第1～第Nのビット範囲のうちの、第r( $r$ は2～Nを満たす整数)のビット範囲での前記判定結果に基づいて、前記第rのビット範囲のMSB側の第 $r-1$ のビット範囲の結果を変更してもよい。

**【0025】**

これにより、LSB側の判定結果によりMSB側の判定結果を変更できるため、A/D変換の精度を高めること等が可能になる。

**【0026】**

また、本発明の一態様では、前記入力電圧は、温度センサー部からの温度検出電圧であり、前記A/D変換結果データは、前記温度検出電圧のA/D変換結果である温度検出データであってもよい。10

**【0027】**

これにより、温度検出電圧をA/D変換して温度検出データを求めることが可能になる。。

**【0028】**

また、本発明の一態様では、前記D/A変換器と、前記比較部と、前記処理部とを含むA/D変換回路と、前記温度検出データに基づいて発振周波数の温度補償処理を行い、前記発振周波数の周波数制御データを出力するデジタル信号処理部と、前記デジタル信号処理部からの前記周波数制御データと振動子を用いて、前記周波数制御データにより設定される前記発振周波数の発振信号を生成する発振信号生成回路と、を含んでもよい。20

**【0029】**

このようにすれば、DTCXO等の、温度検出電圧に基づく温度補償処理を行って発振信号を出力する回路を実現すること等が可能になる。

**【0030】**

また本発明の他の態様は、上記のいずれかに記載の回路装置と、前記振動子と、を含む発振器に関係する。

**【0031】**

また本発明の他の態様は、上記のいずれかに記載の回路装置を含む電子機器に関係する。。

**【0032】**

また本発明の他の態様は、上記のいずれかに記載の回路装置を含む移動体に関係する。30

**【図面の簡単な説明】****【0033】**

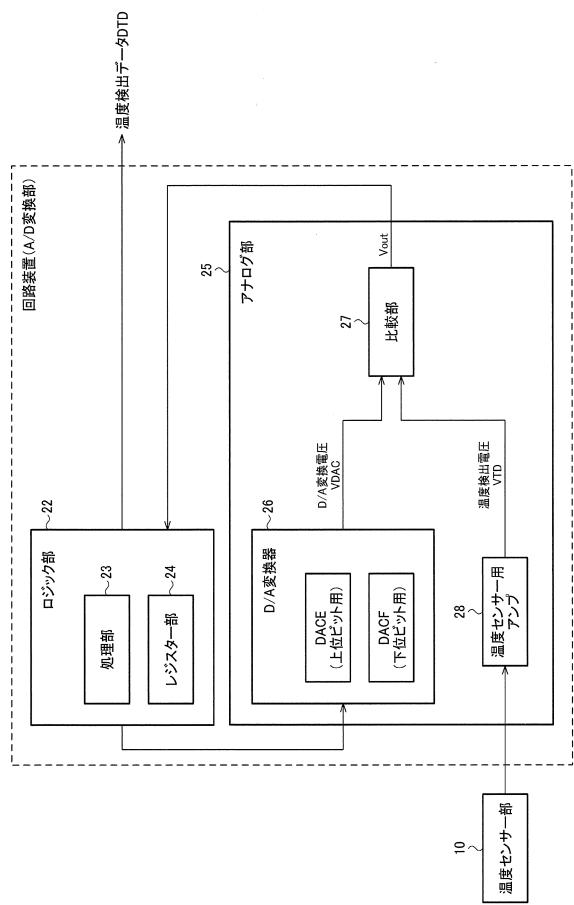

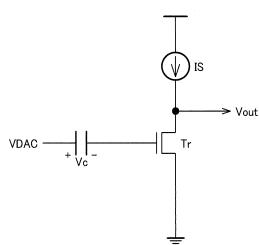

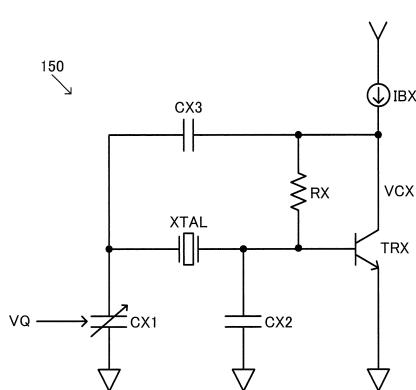

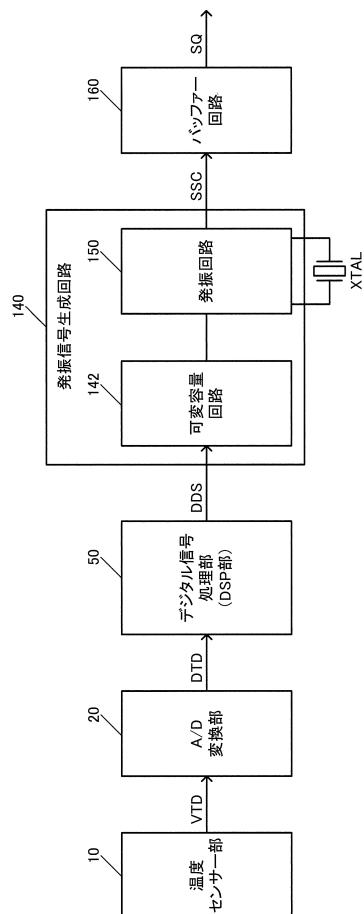

**【図1】**本実施形態の回路装置の基本的な構成例。

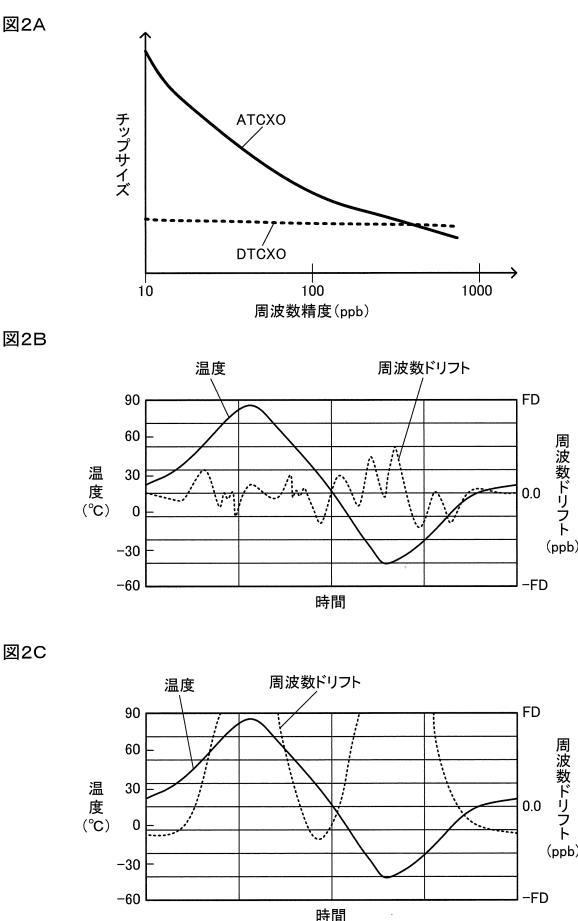

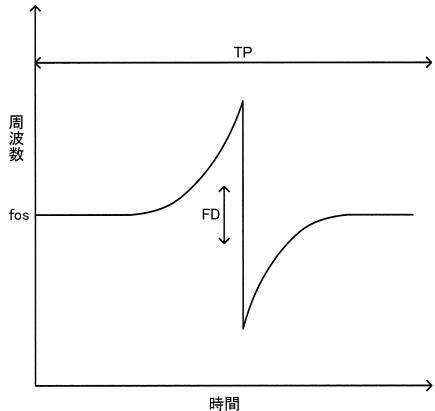

**【図2】**図2A、図2B、図2CはDTCXOの利点や問題点についての説明図。

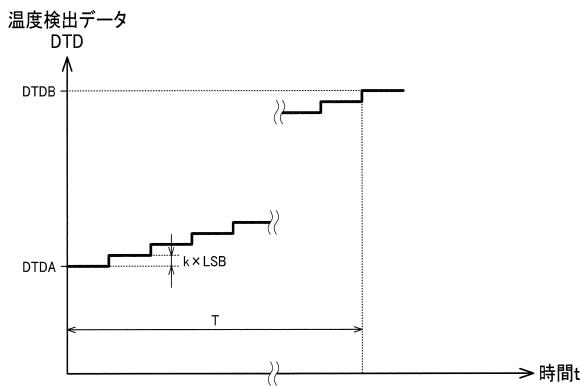

**【図3】** $k \times L$ SB以下の更新によって生じる課題を説明する図。

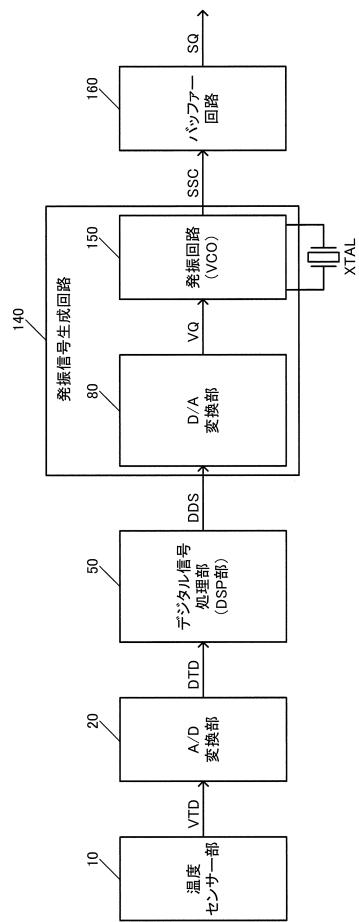

**【図4】**本実施形態の回路装置の構成例。

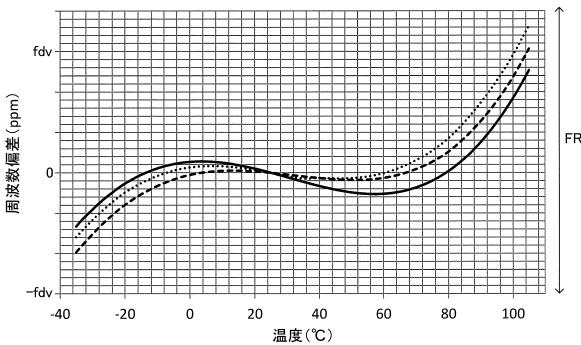

**【図5】**振動子の温度特性やそのバラツキの例を示す図。

**【図6】**温度補償処理の説明図。

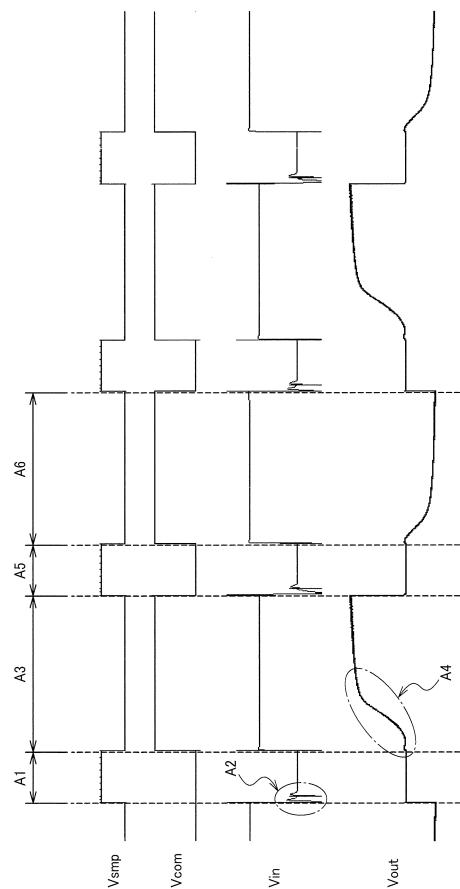

**【図7】**図7A、図7B、図7Cは比較部の構成例。40

**【図8】**比較部の波形図の例。

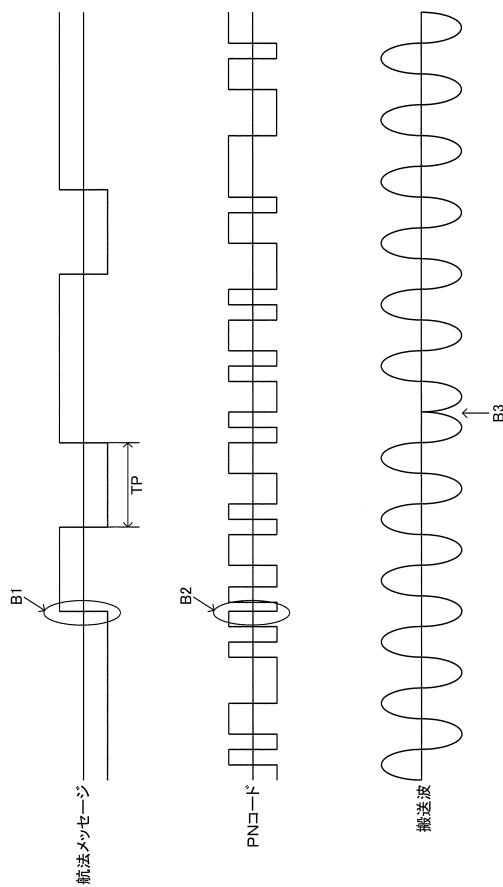

**【図9】**周波数ドリフトが原因で発生する通信エラーの説明図。

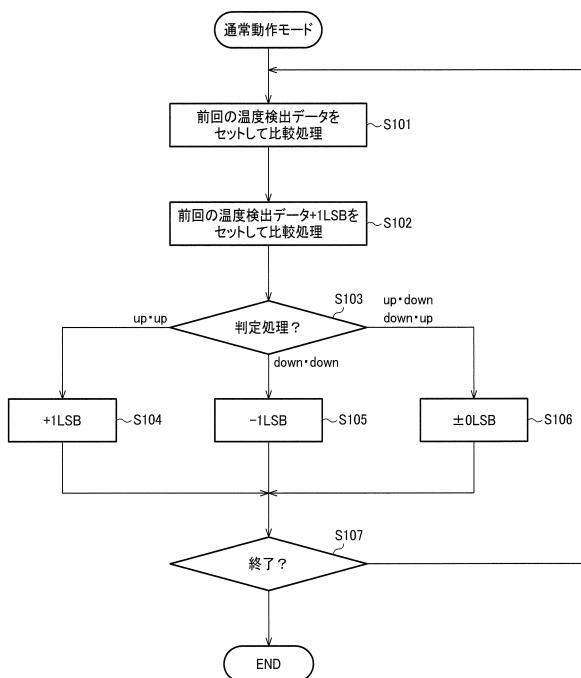

**【図10】**通常動作モードの処理を説明するフローチャート。

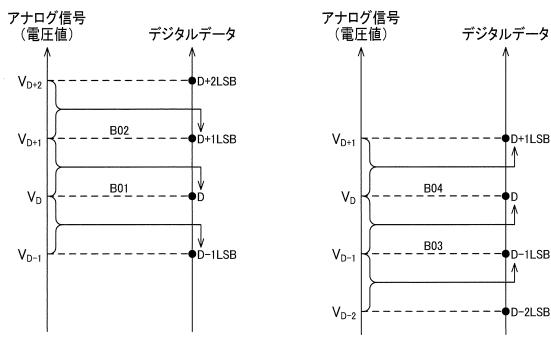

**【図11】**図11A、図11Bはアナログ信号とデジタルデータの関係例。

**【図12】**比較部の他の構成例。

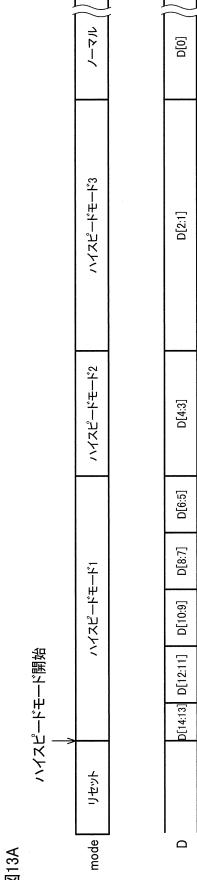

**【図13】**図13A、図13Bはハイスピードモードにおける判定期間の設定例。

**【図14】**図14Aはハイスピードモードの処理を説明するフローチャート、図14B、図14Cは判定処理の具体例。

**【図15】**ハイスピードモードでの結果データの遷移の具体例。

**【図16】**A/D変換部以外の構成で周波数ホッピング等を抑止する手法の説明図。50

【図17】図17A、図17BはA/D変換部以外の構成で周波数ホッピング等を抑止する手法の説明図。

【図18】周波数ホッピングについての説明図。

【図19】図19A、図19B、図19Cは温度センサー部の詳細な構成例及びその説明図。

【図20】発振回路の詳細な構成例。

【図21】本実施形態の変形例の回路装置の構成例。

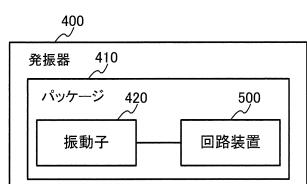

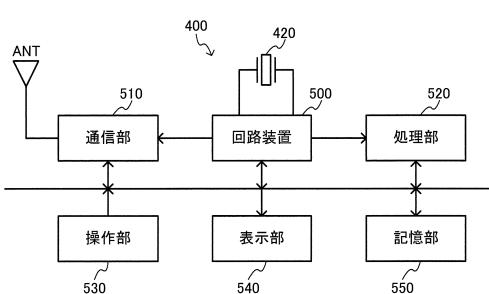

【図22】図22A、図22B、図22Cは発振器、電子機器、移動体の構成例。

【発明を実施するための形態】

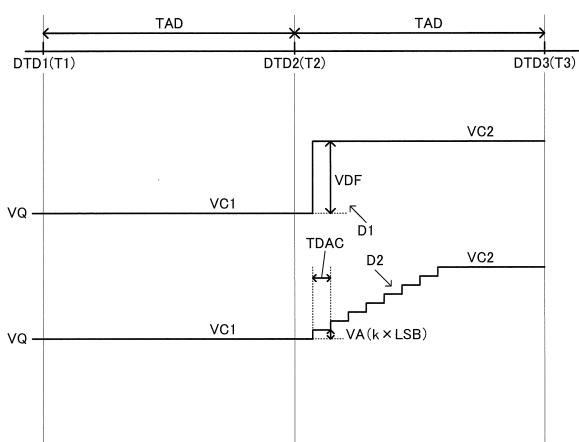

【0034】

10

以下、本発明の好適な実施の形態について詳細に説明する。なお以下に説明する本実施形態は特許請求の範囲に記載された本発明の内容を不当に限定するものではなく、本実施形態で説明される構成の全てが本発明の解決手段として必須であるとは限らない。

【0035】

1. 本実施形態の手法

1.1 ハイスピードモードの概要

まず本実施形態の手法について説明する。所与のアナログ信号をA/D変換してデジタルデータを取得する回路装置、特に、当該デジタルデータに基づいてデジタル信号処理部（例えばDSP, digital signal processor）において種々の処理を行う回路装置が知られている。一例としては、温度センサー部からの温度検出電圧のA/D変換結果である温度検出データに基づいて、デジタル処理により周波数の温度補償処理を行うDTCXOが知られている。

20

【0036】

このような回路装置におけるA/D変換に対しては種々の要求がある。例えば、A/D変換のレートを高くすること（A/D変換期間を短くすること）に対する要求がある。A/D変換結果データを高速で取得することができれば、当該A/D変換結果データを用いた処理等での利点が大きいためである。

【0037】

30

例えば、A/D変換が高速であればそれだけ早くA/D変換結果データを用いた処理を行うことが可能になる。逆に言えば、A/D変換結果データの取得までに時間がかかる、それ以降の処理に待ちが生じる等の問題が発生しうる。例えば、A/D変換結果データとして温度検出データDTDを取得し、当該温度検出データDTDにより発振周波数に対する温度補償処理を行うDTCXOの場合、温度検出データDTDが出力されるまでは温度補償処理を実行できないおそれもある。

【0038】

特に問題となるのが回路装置の起動時である。回路装置の起動時では、それ以前に温度検出データDTDが取得されていない。そのため、初期値として何らかの値、例えば15ビットであれば”1000000000000000”といった中間的な値が設定され、当該初期値は実際の温度とは何ら関係ない値となる。つまり起動後、最初の温度検出データDTDの出力までの期間（起動期間）は、実際の温度に対応した温度補償処理を実行することができず、結果として出力となる発振周波数を適切な値に安定させることができない。

40

【0039】

例えば、DTCXOを携帯電話の通信で利用する場合、起動から2 msec以内に出力周波数を安定させるという要求がある。そのためには、最悪でも2 msecよりも短い時間で温度補償用の温度検出データDTDを精度のよい値としておかなくてはならず、A/D変換の高速化は重要である。

【0040】

なお、A/D変換結果データ、特に温度検出電圧VTDをA/D変換した温度検出データDTDを利用する回路装置は、DTCXOに限定されるものではない。例えば、ジャイ

50

ロセンサーの出力は温度特性を有し、当該温度特性に起因して出力データに誤差が生じることが知られている。そのため、温度検出データ D T D に基づいて、ジャイロセンサーの出力の温度特性を補償する処理（例えばゼロ点補正処理）が行われることがあり、本実施形態における回路装置はそのようなジャイロセンサーに利用されてもよい。

#### 【 0 0 4 1 】

A / D 変換には種々の方式が知られており、逐次比較型、

型、フラッシュ型等がある。このうち、

型は積分回路を通すことになるため、高速での出力が難しい。またフラッシュ型は高速ではあるがビット数が増えるほど回路規模が増大するため、例えば 10 ビットを超えるような A / D 変換には適していない。逐次比較型もビット数に相当する回数の比較処理が必要であるため、例えば 2 K サンプル / sec で 15 回の比較をすると、出力まで 7 . 5 msec を要することになり上記の 2 msec といった要求を満たせない。

10

#### 【 0 0 4 2 】

逐次比較型の場合、1 ビット当たりの比較処理にかける時間を短くすれば、出力までに要する時間を短縮することができる。しかし、比較処理を行う時間が短くなれば判定精度が低くなることが知られている。図 7 A 等を用いて後述するチョッパー回路を用いた比較部 27 の例であれば、スイッチ S 1 をオフ、S 2 , S 3 をオンにして温度検出電圧 V T D に対応する電荷をキャパシター C に蓄積する時間（サンプルモード、図 8 の A 1 や A 5 ）、及びスイッチ S 1 をオン、S 2 , S 3 をオフにして、蓄積された電荷に対する D / A 変換電圧 V D A C の関係を出力するための時間（コンパレーターモード、図 8 の A 2 や A 6 ）、のそれぞれが短くなるため、回路状態が充分安定する前に比較処理の結果が出力され、精度が低下してしまう。

20

#### 【 0 0 4 3 】

以上を踏まえ、本出願人は逐次比較型に準じた方式であって、速度と精度とを両立させた A / D 変換手法を提案する。具体的には、本実施形態に係る回路装置は図 1 に示したように、途中結果データ又は最終結果データである結果データを記憶するレジスター部 24 と、結果データを D / A 変換して D / A 変換電圧を出力する D / A 変換器 26 と、入力電圧と、D / A 変換器 26 からの D / A 変換電圧 V D A C との比較を行なう比較部 27 と、比較部 27 の比較結果に基づいて判定処理を行い、判定処理に基づいて結果データの更新処理を行なって、入力電圧の A / D 変換結果データを求める処理部 23 を含む。そして処理部 23 は、A / D 変換結果データの M S B (most significant bit) 側の判定処理を第 1 の判定期間で行い、A / D 変換結果データの L S B (least significant bit) 側の判定処理を第 1 の判定期間よりも長い期間である第 2 の判定期間で行う。

30

#### 【 0 0 4 4 】

ここで、途中結果データ及び最終結果データは、レジスター部 24 に記憶されるデジタルデータである。最終結果データとは、1 つの A / D 変換結果（温度の場合は温度検出データ D T D ）に対応するものであり、途中結果データとは最終結果データを求める過程で求められるデータである。例えば、図 15 を用いて後述する例では、D B , D O の両方が結果データに含まれるが、D B については途中結果データに対応する。また D O については、図 15 の処理の終了時の値は最終結果データであるが、図 15 の処理中の値は途中結果データに対応する。また、後述する通常動作モードの場合、前回の最終結果データに 1 L S B を加算（減算）したデータは途中結果データに対応し、判定処理により求められるデータが最終結果データに対応する。

40

#### 【 0 0 4 5 】

また、「M S B 側」、「L S B 側」の定義は種々考えられるが、例えば M S B 側とはより M S B (最上位ビット) に近い位置の 1 又は複数のビットから構成されるビット範囲であり、L S B 側とは、M S B 側に比べて L S B (最下位ビット) に近い位置の 1 又は複数のビットから構成されるビット範囲であってもよい。狭義には、M S B 側とは M S B を含む 1 又は複数のビットであり、L S B 側とは L S B を含む 1 又は複数のビットであってもよい。

50

**【0046】**

M S B 側のデータは大きい値を表すものであるため、当該ビットが 0 である場合に対応するアナログ信号（電圧値）と、1 である場合に対応するアナログ信号との差異が比較的大きい。逆に、L S B 側のデータは小さい値を表すものであるため、当該ビットが 0 である場合に対応するアナログ信号と、1 である場合に対応するアナログ信号との差異が比較的小さい。

**【0047】**

つまり、M S B 側は L S B 側に比べて、粗い比較処理を行ったとしても誤判定の可能性を低くすることができる。この点を考慮し、M S B 側の判定処理の期間を相対的に短くすることで、1 回の A / D 変換に要する時間を短縮することが可能になる。具体的な数値例は種々考えられるが、例えば図 13A、図 13B を用いて後述する例であれば、1.5 ms e c 程度の所要時間で A / D 変換結果データの出力が可能である。10

**【0048】**

なお、より A / D 変換の精度を向上させるために、L S B 側の判定結果に基づいて M S B 側の判定結果を更新（修正）する手法を用いてもよい。本実施形態では、L S B 側の方が判定時間が相対的に長いため、判定精度も高いことが期待される。つまり、精度が高い判定結果により、相対的に精度に低い判定結果を更新することで、A / D 変換全体としての精度を向上させることができると可能になる。具体的な手法については後述する。

**【0049】**

以下、後述する通常動作モードと区別するため、上記の A / D 変換を行うモードをハイスピードモードと表記する。20

**【0050】**

なお、処理部 23 は、回路装置の起動期間の前半期間において、A / D 変換結果データの M S B 側の判定処理を行い、回路装置の起動期間の後半期間において、A / D 変換結果データの L S B 側の判定処理を行ってもよい。

**【0051】**

上述したように、回路装置を起動してから最初の A / D 変換結果データの出力までの時間を短くすることに対する要求があるため、起動期間でハイスピードモードを用いることの利点は大きい。その際、先に M S B 側を判定し、その後に L S B 側を判定するようすれば、一般的な逐次比較型と同様の手法により A / D 変換が可能である。さらに言えば、L S B 側の結果により M S B 側の結果を変更する手法を用いる場合、M S B 側の判定を L S B 側よりも先に行つておくことが必要となる。30

**【0052】**

また、以上からわかるように、M S B 側の判定と L S B 側の判定の順序が重要であり、具体的な判定期間の長さや、開始タイミング終了タイミング等は種々の変形実施が可能である。そのため、M S B 側を起動期間の「前半期間」、L S B 側を起動期間の「後半期間」と表記したが、それぞれの期間が同じ長さである必要はない。前半期間とは、起動期間の開始タイミングを含む所与の長さの期間であり、後半期間とは起動期間の終了タイミングを含む所与の長さの期間であってもよい。

**【0053】****1.2 通常動作モードの概要**

なお、必須の構成ではないが、本実施形態では上述したハイスピードモードとは異なる方式の A / D 変換を行ってもよい。具体的には、処理部 23 は、起動期間において、M S B 側の判定処理を第 1 の判定期間で行い、L S B 側の判定処理を第 2 の判定期間で行う第 1 の A / D 変換方式（ハイスピードモード）で、A / D 変換結果データを求め、起動期間の後の通常動作期間において、起動期間における A / D 変換結果データを初期値として、第 1 の A / D 変換方式とは異なる第 2 の A / D 変換方式（通常動作モード）で A / D 変換結果データを求めてよい。

**【0054】**

上述したハイスピードモードは、精度を確保しつつ、一般的な逐次比較型に比べて高速40

50

な A / D 変換を実現可能である。しかし、ハイスピードモードは過去の温度検出データ D T D 等を利用するものではないため、毎回全ビット（例えば 15 ビット）の値を一から求めることになる。起動期間（ここでは回路装置の起動後、最初の A / D 変換結果データの出力までの期間）のように、それ以前の温度検出データ D T D の利用がそもそも想定されないケースでは、ハイスピードモードを用いるとよい。しかしハイスピードモードでは上述したように全ビットを一から求める関係上、A / D 変換結果データが短期間で大きく変動する可能性がある。

#### 【 0 0 5 5 】

A / D 変換結果データの値が短期間に大きく変化してしまう場合、例えば所与の出力タイミングでの A / D 変換結果データと、次の出力タイミングの A / D 変換結果データとの間での値の変動が大きすぎる場合、当該変動に起因して不具合が発生する可能性が生じるためである。10

#### 【 0 0 5 6 】

例えば、D T C X O 等のデジタル方式の発振器では、その発振周波数の周波数ドリフトが原因で、発振器が組み込まれた通信装置において通信エラー等が発生してしまうという問題がある。デジタル方式の発振器では、温度センサー部からの温度検出電圧を A / D 変換し、得られた温度検出データに基づいて周波数制御データの温度補償処理を行い、当該周波数制御データに基づいて発振信号を生成する。この場合に、温度変化により周波数制御データの値が大きく変化すると、これが原因で周波数ホッピングの問題が生じることが判明した。このような周波数ホッピングが生じると、G P S 関連の通信装置を例にとれば、G P S のロックが外れてしまうなどの問題が発生してしまう。このような問題の発生を抑止するには、温度補償処理に用いる温度検出データの変動を抑えることが必要となる。なお、後述するように A / D 変換以外の部分（例えばデジタル信号処理部の処理）で周波数ホッピングを抑止することも可能であり、本実施形態の回路装置ではそれらの手法を組み合わせて用いてもよい。20

#### 【 0 0 5 7 】

以下、T C X O としてデジタル方式の D T C X O を採用した場合に生じうる周波数ドリフトの問題について簡単に説明する。温度補償型発振器である T C X O では、周波数精度の向上と低消費電力化への要求がある。例えば G P S 内蔵の時計や脈波等の生体情報の測定機器などのウェアラブル機器では、バッテリーによる動作継続時間を長くする必要がある。このため、基準信号源となる T C X O に対しては、周波数精度を確保しながら、より低消費電力であることが要求される。30

#### 【 0 0 5 8 】

また通信端末と基地局との通信方式としては種々の方式が提案されている。例えば T D D (Time Division Duplex) 方式では、各機器は割り当てられたタイムスロットにおいてデータを送信する。そしてタイムスロット（上がり回線スロット、下り回線スロット）の間にガードタイムが設定されることで、タイムスロットが重なることが防止される。次世代の通信システムでは、例えば 1 つの周波数帯域（例えば 5 0 G H z ）を用いて、T D D 方式でデータ通信することが提案されている。40

#### 【 0 0 5 9 】

しかしながら、このような T D D 方式を採用した場合には、各機器において時刻同期を行う必要があり、正確な絶対時刻の計時が要求される。このような要求を実現するために、例えば各機器に、基準信号源として原子時計（原子発振器）を設ける手法も考えられるが、機器の高コスト化を招いたり、機器が大型化するなどの問題が生じる。

#### 【 0 0 6 0 】

そして基準信号源として A T C X O （アナログ方式の T C X O ）を用いた場合に、周波数精度を高精度化しようとすると、図 2 A に示すように回路装置のチップサイズが増加してしまい、低コスト化や低消費電力化の実現が難しくなる。一方、D T C X O では、図 2 A に示すように、回路装置のチップサイズをそれほど大きくすることなく、周波数精度の高精度化を実現できるという利点がある。50

**【 0 0 6 1 】**

しかしながら、上述したような周波数ドリフトの問題があるため、D T C X O等のデジタル方式の発振器では、様々な回路方式が提案されているものの、このような通信エラーが問題となる実際の製品の基準信号源としては、デジタル方式の発振器は殆ど採用されず、A T C X O等のアナログ方式の発振器が採用されているのが現状であった。

**【 0 0 6 2 】**

例えば図2BはA T C X Oの周波数ドリフトを示す図である。A T C X Oでは、図2Bに示すように時間経過に伴い温度が変化した場合にも、その周波数ドリフトは、許容周波数ドリフト（許容周波数エラー）の範囲内（ $\pm F D$ ）に収まる。図2Bでは、周波数ドリフト（周波数エラー）は、公称発振周波数（例えば16MHz程度）に対する割合（周波数確度。p p b）で示されている。例えば通信エラーが生じないようにするためにには、所定期間T P（例えば20mssec）内において、周波数ドリフトを許容周波数ドリフトの範囲内（ $\pm F D$ ）に収める必要がある。ここでF Dは、例えば数p p b程度である。

10

**【 0 0 6 3 】**

一方、図2Cは、従来のD T C X Oを用いた場合の周波数ドリフトを示す図である。図2Cに示すように、従来のD T C X Oでは、その周波数ドリフトが許容周波数ドリフトの範囲内に収まっておらず、当該範囲を超えてしまう周波数ホッピングが発生している。このため、この周波数ホッピングを原因とする通信エラー（G P Sのロック外れ等）が発生してしまい、実際の製品の基準信号源としてD T C X Oを採用することの妨げとなっていた。

20

**【 0 0 6 4 】**

よって、第2のA / D変換方式としては、例えばA / D変換結果データの変動を抑制する手法を用いるとよい。具体的には、A / D変換でのデータの最小分解能をL S Bとした場合に、処理部23は、第2のA / D変換方式として、第1の出力タイミングのA / D変換結果データを第1のA / D変換結果データとし、第1の出力タイミングの次の第2の出力タイミングのA / D変換結果データを第2のA / D変換結果データとした場合に、第1のA / D変換結果データに対する第2のA / D変換結果データの変化が $k \times L S B$ （kは $k < j$ を満たす整数、jはA / D変換の分解能を表す整数）以下となるように、A / D変換結果データを求める処理を行う。

**【 0 0 6 5 】**

30

なお、ここでの出力タイミングとは、1つのA / D変換結果データが出力されるタイミングを表すものであり、例えばA / D変換が15ビットで行われる場合であれば15ビット精度のA / D変換結果データが出力されるタイミングを表す。本実施形態では暫定的な値（途中結果データ）による比較処理を複数回行い、当該複数回の比較処理の結果に基づいて15ビット精度のA / D変換結果データ（最終結果データ）を求めるという、逐次比較型に準じた方式によりA / D変換を行う。つまり、1回のA / D変換結果データを出力するにあたっては、複数回の比較処理の結果として1又は複数の途中結果データが出力される。途中結果データも広義にはA / D変換処理における出力ということになるが、ここでの「出力タイミング」とは、あくまで最終的なA / D変換結果データ（15ビット精度のデータ）の出力を表すものであり、途中結果データの出力タイミングではない。

40

**【 0 0 6 6 】**

また、A / D変換の分解能を表す整数jは、A / D変換結果データのビット数に依存する値であり、ビット数をpとした場合に、 $j = 2^p$ であってもよい。

**【 0 0 6 7 】**

本実施形態の手法によれば、隣り合う2タイミング間でのA / D変換結果データ（狭義には温度検出データD T D）の変動が $k \times L S B$ 以下に抑えられる。なお、ここでのL S BはA / D変換でのデータの最小分解能であるため、例えば、温度検出データとして、T1からT2（ $> T 1$ ）の温度範囲をpビットのデジタルデータで表現する場合、1LSBの変動は $(T 2 - T 1) / 2^p$ に対応する温度の変動を表すことになる。このような条件を設けない場合、A / D変換結果データは最大で $2^p$ （=j）LSBだけ変化しう

50

る。2<sup>P</sup>LSBの変化とは第1のタイミングでのA/D変換結果データが想定される最小値（最大値）であり、第2のタイミングでのA/D変換結果データが想定される最大値（最小値）となった場合に相当する。

#### 【0068】

これにより、上記のDTCXOの例であれば、温度検出データの変動が抑えられることにより、周波数ホッピングについても許容周波数ドリフトの範囲内に収められる可能性が向上する。また、DTCXO以外の例においても、A/D変換結果データの変動を抑止することで、不具合の発生を抑止することが可能になる。

#### 【0069】

また、本実施形態における入力電圧は、温度センサー部10からの温度検出電圧VTDであり、A/D変換結果データは、温度検出電圧VTDのA/D変換結果である温度検出データDTDであってもよい。10

#### 【0070】

この場合、通常動作モードは温度検出データDTDの変動を抑制する手法となり、当該手法を採用することには合理的な理由が存在する。自然条件下での温度変動（環境温度の変動）はさほど大きくないことが知られており、例えば最大でも0.28 / sec程度の温度変動を考慮すればよい。そのため、A/D変換のレートを2Kサンプル/secであるとすれば、1A/D変換期間当たりの温度変動、すなわち所与の出力タイミングと、その次の出力タイミングとの間での温度検出データの想定最大変化量は、0.14m / サンプルとなる。20

#### 【0071】

ここで、回路装置で考慮すべき温度範囲を125（例えば上述のT1 = -40、T2 = 85）とし、p = 15とすれば、1 LSB当たりの温度変化は125 / 2<sup>15</sup> 4m / LSBとなる。つまり、上述の0.14m / サンプルと、4m / LSBとを比較すればわかるように、自然条件下では30回のA/D変換結果データの出力が行われる間に、1 LSBの値の変化が生じるかどうかといった程度の温度変化を想定すれば充分である。

#### 【0072】

本実施形態の手法のように、出力である温度検出データDTDの変動を抑制した場合、実際の温度と温度検出データDTDとの乖離が生じてしまうと問題となる。例えば、アナログ信号である温度検出電圧VTDが大きく変化している（具体的にはk × LSBに対応する電圧値よりも大きく変化している）場合には、出力のデジタルデータである温度検出データDTDがその変化に追随できず（k × LSBまでしか変化せず）、実際の温度と温度検出データDTDとの乖離が生じてしまう。しかし自然条件下、且つA/D変換の変換レート及びビット数を上述の値に設定した例では、隣接出力タイミング間での実際の温度変化は1 LSBよりも小さい程度である。そのため、前の出力タイミングでの温度検出データDTDに対する変動をk × LSB（この例ではk = 1）に限定したとしても、実際の温度と温度検出データDTDとの乖離は生じないと考えてよく、適切なA/D変換が可能となる。

#### 【0073】

なお、自然条件下での環境温度の変動は、上述したように単位時間当たり（例えば1秒や10秒）の変動として定義される。そのため、隣り合う出力タイミング間で想定される温度変動は、当該隣り合う出力タイミング間の長さ、すなわちA/D変換期間に応じて変化することになる。A/D変換期間が長ければ想定される温度変動は大きくなるし、A/D変換期間が短ければ想定される温度変動は小さくなる。40

#### 【0074】

よって本実施形態では、1回のA/D変換期間での温度検出電圧VTDの電圧変化量が、k × LSBに対応する電圧以下となるように、A/D変換期間が設定されてもよい。このような設定をしておけば、温度変動（実際には当該変動に起因する温度検出電圧VTDの変化量）が、k × LSB以下（実際にはk × LSBに対応するD/A変換電圧以下）と50

なるため、温度検出データ D T D の変動を  $k \times L S B$  以下に抑制したとしても、実際の温度との乖離を抑止できる。

#### 【 0 0 7 5 】

ここで、上述したように温度変動は（或いはケルビン）等で定義されるため、 $1 L S B$  が何に対応するかも重要となる。例えば、A / D 変換のビット数（上述した p）を減らした場合、或いは回路装置で考慮する温度範囲（上述の例では 125）を広くした場合、デジタルデータが  $1 L S B$  変動した場合に、当該デジタルデータにより表される温度の変動は大きくなる。

#### 【 0 0 7 6 】

自然条件下での環境温度の変動  $< k \times L S B$  に対応する温度変動、という条件を満たすことだけを考慮すると、 $1 L S B$  当たりの温度を大きくする（p を小さくする、温度範囲を広くする）とよいように見える。しかし、そもそもその課題は A / D 変換結果データの変動を抑止し、周波数ホッピング等に起因する不具合を抑止することである。つまり、A / D 変換結果データの変動を  $k \times L S B$  以下に抑えたとしても、当該  $k \times L S B$  に対応する温度が大きければ結局大きな温度変動を許容してしまっていることになり、不適切である。

#### 【 0 0 7 7 】

よって本実施形態では、例えば回路装置で想定する温度範囲や、A / D 変換のビット数は、周波数ホッピングを抑止するという観点から設定し、設定された条件に基づいて、自然条件下での温度変動  $< k \times L S B$  に対応する温度変動となるように、A / D 変換期間を設定するとよい。

#### 【 0 0 7 8 】

値の変動を  $k \times L S B$  以下に限定できることで、効率的に（高速に）A / D 変換を実行することも可能になる。通常の p ビットの A / D 変換であれば、各出力タイミングでは、 $2^p$  通りの値のすべてが候補となるため、当該  $2^p$  通りの全てが出力可能な変換を実行しなくてはならない。例えば、一般的な逐次比較型の A / D 変換であれば、p ビットの各ビットの値を 1つ1つ決定するため、p 回の比較処理が必要となる。その点、本実施形態の手法であれば、前回の出力タイミングでの温度検出データ D T D に対して、そのままの値（変化 0）、 $\pm 1 L S B$ 、 $\pm 2 L S B$ 、 $\dots$   $\pm k \times L S B$  の値のみを候補とすればよい。特に、 $k = 1$  であれば、値の候補は変化が 0 或いは  $\pm 1 L S B$  の 3 通りのみを考慮すればよいため、A / D 変換に要する処理を簡略化することができる。具体的には比較部 27 での比較処理や、当該比較処理に用いるアナログ信号の生成処理（D / A 変換処理）の回数を減らすことができる。

#### 【 0 0 7 9 】

つまり本実施形態の手法によれば、周波数ホッピング等の A / D 変換結果データの急激な変動による不具合を抑止する、効率的な A / D 変換処理を実現するという 2 つの効果を奏しつつ、当該 A / D 変換を実行しても実温度と温度検出データ D T D との乖離を抑止可能となる。

#### 【 0 0 8 0 】

さらに、このような  $k \times L S B$  以下に変動を抑える通常動作モードと、上述したハイスペードモードを組み合わせることにも合理的な理由がある。上述したように、自然条件下での温度変化を考慮すれば、温度検出データ D T D の変動が  $k \times L S B$  以下に抑制される通常動作モードは合理的な方式と言える。しかしこれは、所与の出力タイミングで実際の温度（温度検出電圧 V T D）に合致した適切な温度検出データ D T D が求められていることが前提となる。

#### 【 0 0 8 1 】

そのため、起動時の初期値のように、実際の温度を反映していない値から通常動作モードを開始してしまうと、実際の温度が初期値と大きく異なる場合であっても、出力である温度検出データ D T D は、1 回の出力当たり  $k \times L S B$  しか変化できないため、出力が安定するまでに多大な時間を要してしまう。

10

20

30

40

50

## 【0082】

図3にこの場合の温度検出データD TDの時間変化例を示す。図3の縦軸が温度検出データD TDを表し、横軸が時間を表す。D T D Aが温度検出データD TDの初期値であり、D T D Bが実際の温度に対応するデジタル値を表す。ハイスピードモードや一般的な逐次比較型のA/D変換のように、pビットの値を全てその都度求める方式であれば、初期値と実際の温度との差が大きかったとしても、次の出力タイミングにおいて、実際の温度に対応した温度検出データを求めることができる。しかし本実施形態の通常動作モードでは、前回の出力に対する変動が $k \times L S B$ 以下に抑制されるため、図3に示したように、D T D AとD T D Bの差が大きかったとしても、温度検出データD TDは $k \times L S B$ ずつ段階的にしか変化させられない。その結果、温度検出データD TDが実際の温度に追従するまでに長い時間が必要となる。例えば、上記のような中間的な値を初期値とし、実際の温度に対応するデータが”1111111111111111”或いは”0000000000000000”といった値に対応する場合、 $k = 1$ であれば $2^{p-1}$ 回の出力を経てようやく実際の温度と温度検出データD TDとが合致することになる。10

## 【0083】

具体的に安定するまでの時間Tは、初期値の設定やA/D変換期間の長さにもよるが、最悪の場合には10秒以上を要することになる。この間は、温度検出データD TDは正確な温度を反映するものではないため、その後の処理、例えばD T C X Oにおける温度補償処理も正確に行うことができず問題となる。特に、起動後に高速で出力を安定させることに対する要求も多いためこの問題は重要となる。つまり、A/D変換結果データとして温度検出データD TDを出力する場合において、通常動作モードが適した手法であることは確かにあるとしても、起動期間から通常動作モードで動作することはできない。20

## 【0084】

その点、本実施形態では、まずハイスピードモードにより温度検出データD TDを求めておき、その後に当該温度検出データD TDを初期値として通常動作モードを開始する。ハイスピードモードでは、以前の出力に対する変化幅に制約はないため、実際の温度に合致した温度検出データD TDを初期値として出力可能である。そして、実際の温度に合致した初期値が決定できれば、その後に通常動作モードを用いても問題がないことは上述したとおりである。

## 【0085】

以下、本実施形態について詳細に説明していく。まず、本実施形態に係る回路装置の構成例を説明する。図4等を用いて後述するように、D T C X O等を想定したデジタル方式の発振器に用いられる回路装置の構成例を説明するが、本実施形態に係る回路装置はこれに限定されるものではない。その後、図4の各部の詳細について説明する。具体的には、A/D変換の具体的な手法を通常動作モード、ハイスピードモードのそれぞれについて説明する。さらに、デジタル信号処理部(DSP)やD/A変換回路、温度センサー部、発振回路等についても説明する。なお、デジタル信号処理部の処理により、D T C X Oの周波数ホッピングを抑止する手法についても説明する。その後、いくつかの変形例を説明し、さらに本実施形態の回路装置を含む電子機器等の例について説明する。30

## 【0086】

## 2. 構成

図4に本実施形態の回路装置の構成例を示す。この回路装置は、D T C X OやO C X O等のデジタル方式の発振器を実現する回路装置(半導体チップ)である。例えばこの回路装置と振動子X T A Lをパッケージに収納することで、デジタル方式の発振器が実現される。

## 【0087】

図4の回路装置は、A/D変換部20、デジタル信号処理部50、発振信号生成回路140を含む。なお、図1に示した回路装置の各部の構成は、例えばA/D変換部20に含まれる。また回路装置は温度センサー部10、バッファー回路160を含むことができる。なお回路装置の構成は図4の構成には限定されず、その一部の構成要素(例えば温度セ40

50

ンサー部、バッファー回路等)を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

#### 【0088】

振動子X T A Lは、例えば水晶振動子等の圧電振動子である。振動子X T A Lは恒温槽内に設けられるオープン型振動子(O C X O)であってもよい。振動子X T A Lは共振器(電気機械的な共振子又は電気的な共振回路)であってもよい。振動子X T A Lとしては、圧電振動子、S A W(Surface Acoustic Wave)共振子、M E M S(Micro Electro Mechanical Systems)振動子等を採用できる。振動子X T A Lの基板材料としては、水晶、タンタル酸リチウム、ニオブ酸リチウム等の圧電単結晶や、ジルコン酸チタン酸鉛等の圧電セラミックス等の圧電材料、又はシリコン半導体材料等を用いることができる。振動子X T A Lの励振手段としては、圧電効果によるもの用いてもよいし、クーロン力による静電駆動を用いてもよい。10

#### 【0089】

温度センサー部10は、温度検出電圧V T Dを出力する。具体的には、環境(回路装置)の温度に応じて変化する温度依存電圧を、温度検出電圧V T Dとして出力する。温度センサー部10の具体的な構成例については後述する。

#### 【0090】

A / D変換部20は、温度センサー部10からの温度検出電圧V T DのA / D変換を行って、温度検出データD T Dを出力する。例えば温度検出電圧V T DのA / D変換結果に対応するデジタルの温度検出データD T D(A / D変換結果データ)を出力する。A / D変換部20のA / D変換方式は例えば上述したように通常動作モードとハイスピードモードを切り替えて用いてもよく、詳細については後述する。20

#### 【0091】

デジタル信号処理部50(D S P部)は種々の信号処理を行う。例えばデジタル信号処理部50(温度補償部)は、温度検出データD T Dに基づいて発振周波数(発振信号の周波数)の温度補償処理を行う。そして発振周波数の周波数制御データD D Sを出力する。具体的にはデジタル信号処理部50は、温度に応じて変化する温度検出データD T D(温度依存データ)と、温度補償処理用の係数データ(近似関数の係数のデータ)などに基づいて、温度変化があった場合にも発振周波数を一定にするための温度補償処理を行う。このデジタル信号処理部50は、ゲートアレイ等のA S I C回路により実現してもよいし、プロセッサーとプロセッサー上で動作するプログラムにより実現してもよい。30

#### 【0092】

発振信号生成回路140は発振信号S S Cを生成する。例えば発振信号生成回路140は、デジタル信号処理部50からの周波数制御データD D Sと振動子X T A Lを用いて、周波数制御データD D Sにより設定される発振周波数の発振信号S S Cを生成する。一例としては、発振信号生成回路140は、周波数制御データD D Sにより設定される発振周波数で振動子X T A Lを発振させて、発振信号S S Cを生成する。

#### 【0093】

なお発振信号生成回路140は、ダイレクト・デジタル・シンセサイザー方式で発振信号S S Cを生成する回路であってもよい。例えば振動子X T A L(固定発振周波数の発振源)の発振信号をリファレンス信号として、周波数制御データD D Sで設定される発振周波数の発振信号S S Cをデジタル的に生成してもよい。40

#### 【0094】

発振信号生成回路140は、D / A変換部80と発振回路150を含むことができる。但し発振信号生成回路140は、このような構成には限定されず、その一部の構成要素を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。

#### 【0095】

D / A変換部80は、デジタル信号処理部50からの周波数制御データD D S(処理部の出力データ)のD / A変換を行う。D / A変換部80に入力される周波数制御データD D Sは、デジタル信号処理部50による温度補償処理後の周波数制御データ(周波数制御50

コード)である。D/A変換部80のD/A変換方式としては例えば抵抗ストリング型(抵抗分割型)を採用できる。但し、D/A変換方式はこれには限定されず、抵抗ラダー型(R-2Rラダー型等)、容量アレイ型、又はパルス幅変調型などの種々の方式を採用できる。またD/A変換部80は、D/A変換器以外にも、その制御回路や変調回路やフィルター回路などを含むことができる。

#### 【0096】

発振回路150は、D/A変換部80の出力電圧VQと振動子XTALを用いて、発振信号SSCを生成する。発振回路150は、第1、第2の振動子用端子(振動子用パッド)を介して振動子XTALに接続される。例えば発振回路150は、振動子XTAL(圧電振動子、共振子等)を発振させることで、発振信号SSCを生成する。具体的には発振回路150は、D/A変換部80の出力電圧VQを周波数制御電圧(発振制御電圧)とした発振周波数で、振動子XTALを発振させる。例えば発振回路150が、電圧制御により振動子XTALの発振を制御する回路(VCO)である場合には、発振回路150は、周波数制御電圧に応じて容量値が変化する可変容量キャパシター(バリキャップ等)を含むことができる。

#### 【0097】

なお、前述のように発振回路150はダイレクト・デジタル・シンセサイザー方式により実現してもよく、この場合には振動子XTALの発振周波数はリファレンス周波数となり、発振信号SSCの発振周波数とは異なる周波数になる。

#### 【0098】

バッファー回路160は、発振信号生成回路140(発振回路150)で生成された発振信号SSCのバッファリングを行って、バッファリング後の信号SQを出力する。即ち、外部の負荷を十分に駆動できるようにするためのバッファリングを行う。信号SQは例えばクリップドサイン波信号である。但し信号SQは矩形波信号であってもよい。或いはバッファー回路160は、信号SQとしてクリップドサイン波信号と矩形波信号の両方の出力が可能な回路であってもよい。

#### 【0099】

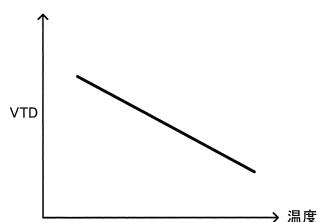

図5は振動子XTAL(AT振動子等)の温度による発振周波数の周波数偏差の一例を示す図である。デジタル信号処理部50は、図5のような温度特性を有する振動子XTALの発振周波数を、温度に依存せずに一定にするための温度補償処理を行う。

#### 【0100】

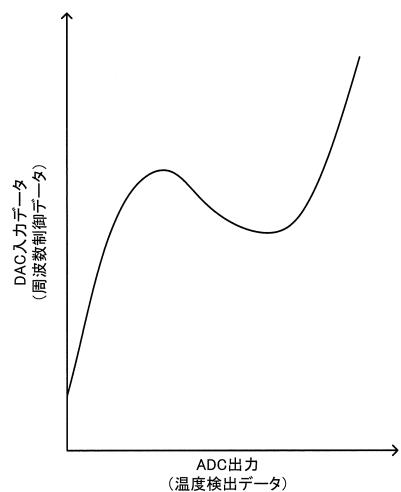

具体的にはデジタル信号処理部50は、A/D変換部20の出力データ(温度検出データDTD)とD/A変換部80の入力データ(周波数制御データ)とが図6に示すような対応関係になるような温度補償処理を実行する。図6の対応関係(周波数補正テーブル)は、例えば回路装置が組み込まれた発振器を恒温槽に入れ、各温度でのD/A変換部80の入力データ(DDS)とA/D変換部20の出力データ(DTD)をモニターするなどの手法により取得できる。

#### 【0101】

そして図6の対応関係を実現するための温度補償用の近似関数の係数データを、回路装置のメモリー部(不揮発性メモリー)に記憶しておく。そしてデジタル信号処理部50が、メモリー部から読み出された係数データと、A/D変換部20からの温度検出データDTDとに基づいて、演算処理を行うことで、振動子XTALの発振周波数を温度に依らずに一定にするための温度補償処理を実現する。

#### 【0102】

なお温度センサー部10の温度検出電圧VTDは、後述するように例えば負の温度特性を有している。従って、図6のような温度補償特性で、図5の振動子XTALの発振周波数の温度依存性を相殺して補償できるようになる。

#### 【0103】

##### 3. A/D変換部

次に、A/D変換部20の詳細について説明する。具体的には、A/D変換部20の構

10

20

30

40

50

成例を説明した後、通常動作モード、ハイスピードモードのそれぞれの手法を説明する。

#### 【0104】

##### 3.1 構成例

A/D変換部20の構成例は図1に示したとおりである。図1に示したようにA/D変換部20は、処理部23、レジスター部24、D/A変換器26(DACE、DACF)、比較部27を含む。また温度センサー部用アンプ28を含むことができる。処理部23、レジスター部24は、ロジック部22として設けられ、D/A変換器26、比較部27、温度センサー部用アンプ28は、アナログ部25として設けられる。

#### 【0105】

レジスター部24は、A/D変換の途中結果データや最終結果データなどの結果データを記憶する。このレジスター部24は、例えば逐次比較方式における逐次比較結果レジスターに相当する。D/A変換器26(DACE、DACF)は、レジスター部24の結果データをD/A変換する。これらのDACE、DACFとしては広く知られた種々のD/A変換器を採用できる。比較部27は、D/A変換器26の出力電圧(D/A変換電圧V<sub>DAC</sub>)と、温度検出電圧V<sub>TD</sub>(温度センサー部用アンプ28による增幅後の電圧、広義には入力電圧)との比較を行う。比較部27は例えばチョッパー型比較器などにより実現できる。処理部23は、比較部27の比較結果に基づいて判定処理を行い、レジスター部24の結果データの更新処理を行う。そして、当該更新処理により求められた最終的な温度検出データD<sub>TD</sub>が、温度検出電圧V<sub>TD</sub>のA/D変換結果として、A/D変換部20から出力される。このような構成により、通常動作モードやハイスピードモード、或いは一般的な逐次比較方式等のA/D変換を実現できる。

10

#### 【0106】

また、D/A変換器26は、処理部23における更新処理後の結果データのD/A変換を行う。これにより、更新処理後の結果データは、次の比較処理において温度検出電圧V<sub>TD</sub>との比較対象として用いることができる。

#### 【0107】

つまり、比較結果に基づき判定処理を行い、判定処理により結果データの更新処理を行い、更新処理後の結果データを、さらに次の比較処理に利用する、というサイクルを繰り返すことで、温度検出データD<sub>TD</sub>を適切に更新していくことが可能になる。

#### 【0108】

具体的には、比較部27は、前回の結果データをD/A変換器26で変換したD/A変換電圧V<sub>DAC</sub>と、温度検出電圧V<sub>TD</sub>とを比較し、処理部23は、比較結果に基づいて判定処理を行い、結果データをk×LSB以下の範囲で更新する更新処理を行ってもよい。これは後述する通常動作モードに対応する。更新処理後の結果データは、さらに次のタイミングを基準とした場合に「前回の温度検出データD<sub>TD</sub>」として扱われるため、D/A変換器26では、当該結果データのD/A変換を行って比較部27に出力する処理が行われる。このサイクルを繰り返すことで、通常動作モードでは、温度検出データD<sub>TD</sub>(最終結果データ)をk×LSB以下の範囲で更新していくことが可能になる。

30

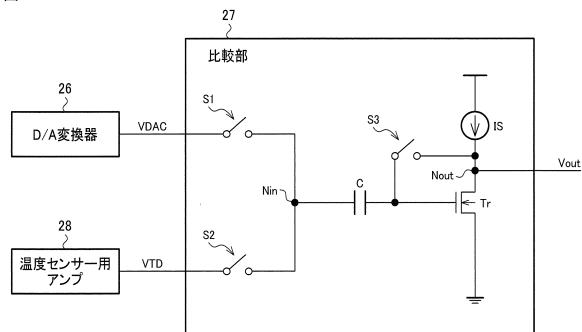

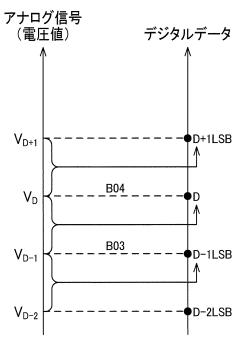

#### 【0109】

図7Aに比較部27の構成例を示す。比較部27は、レジスター部24の結果データがD/A変換器26でD/A変換された結果であるD/A変換電圧が入力される第1のスイッチS1と、温度検出電圧V<sub>TD</sub>が入力される第2のスイッチS2と、S1及びS2に一端(ここを入力端子N<sub>in</sub>とする)が接続されるキャパシターCと、キャパシターCの他端にゲート端子が接続されるトランジスターTrと、トランジスターTrのゲート端子とドレイン端子との間に設けられる第3のスイッチS3と、トランジスターTrのドレイン端子と高電位側電源端子との間に設けられる電流源ISとを含む。トランジスターTrのソース端子は低電位側電源端子(グラウンド)に接続される。また、トランジスターTrのドレイン端子に出力端子N<sub>out</sub>が接続され、N<sub>out</sub>からは出力電圧V<sub>out</sub>が出力される。

40

#### 【0110】

50

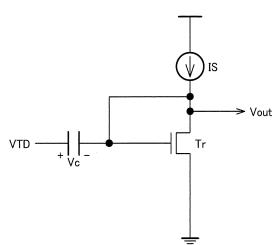

比較部27は、サンプルモードとコンパレーターモードの2つのモードを有する。サンプルモードでは、スイッチS1がオフに設定されるとともに、S2及びS3がオンに設定される。図7Bがサンプルモードの状態を表す模式図である。この場合、電流源ISとトランジスターTrにより構成されるインバーターのゲインが1となるため、サンプルモードでの出力電圧Vout1は下式(1)により求められる。下式(1)において、VcはキャパシターCの両端の電位差を表し、VthはトランジスターTrの閾値電圧を表す。

$$V_{out1} = V_{th} = (V_{TD} + V_c) \quad (1)$$

#### 【0111】

サンプルモードの実行後に、比較部27はコンパレーターモードに移行する。コンパレーターモードでは、S1がオンに設定されるとともに、S2及びS3がオフに設定される。図7Cがコンパレーターモードの状態を表す模式図である。コンパレーターモードでの出力電圧Vout2は、インバーターのゲインを-Gxとした場合、下式(2)により求められる。

$$\begin{aligned} V_{out2} &= -Gx \times \{ (V_{DAC} + V_c) - V_{th} \} \\ &= -Gx (V_{DAC} - V_{TD}) \quad (2) \end{aligned}$$

#### 【0112】

このように、VTDとVdacとの大小関係に応じて、トランジスターTrのオンオフが決まることになる。具体的には、温度検出電圧VTDよりもD/A変換電圧Vdacが大きければ、トランジスターTrはオンとなるため、出力電圧Voutは低電位側電源電圧(例えばグラウンド)となる。逆に、温度検出電圧VTDよりもD/A変換電圧Vdacが小さければ、トランジスターTrはオフとなるため、出力電圧Voutは高電位側電源電圧(例えばVDD)となる。このように、コンパレーターモードにおける出力電圧に基づいて、温度検出電圧VTDとD/A変換電圧Vdacの比較が可能となる。

#### 【0113】

図8が比較部27における具体的な波形図である。Vcomは第1のスイッチS1を制御する制御電圧であり、Vsmplは第2のスイッチS2及び第3のスイッチS3を制御する制御電圧である。VcomとVsmplは、Highの時に対応するスイッチがオンになり、Lowの時に対応するスイッチがオフとなる。また、Vinがチョッパー回路の入力電圧(入力端子Ninの電圧)、Voutが出力電圧である。

#### 【0114】

図8のA1はサンプルモードに対応する期間であり、VsmplがHighであり、VcomがLowであるため、S1がオフ、S2及びS3がオンに設定される。この状態では、温度検出電圧VTDが入力され、徐々にキャパシターCに電荷が蓄積されていき、安定した状態ではVinはVTD及びVcに対応する電圧となる。図8のA2からわかるように、キャパシターCのチャージは即座に行われるわけではないため、サンプルモードの期間を過剰に短くしてしまうと、Vcが温度検出電圧VTDに対応した値とならず、精度が低下することになる。

#### 【0115】

図8のA3がコンパレーターモードであり、VcomがHighであり、VsmplがLowであるため、S1がオン、S2及びS3がオフに設定される。この状態では、VinはD/A変換電圧Vdacとなる。図8の例では、Vdac < VTDであったため、Voutは徐々に大きくなり、安定した状態では高電位側電源電圧となる。

#### 【0116】

処理部23では、Voutが高電位側電源電圧(或いはそれに近い電圧)であると判定された場合には、温度検出電圧VTDがD/A変換電圧Vdacよりも大きいとしてアップ判定を行う。

#### 【0117】

図8のA4からわかるように、Voutの高電位側電源電圧への変化は即座に行われるわけではないため、コンパレーターモードの期間を過剰に短くしてしまうと、Voutが

10

20

30

40

50

温度検出電圧 V T D と D / A 変換電圧 V D A C の関係に対応した値とならず、精度が低下することになる。例えば、V D A C > V T D である場合（後述する A 6 の場合）の V o u t と明確に区別可能な程度まで V o u t が変化する長さの期間を設けなければ判定精度は低下してしまう。また、図 8 の A 2 と A 4 の比較からわかるように、コンパレーター モードでは回路状態が安定するまでに要する時間がサンプルモードよりも長い。そのため、コンパレーター モードに設定される期間は、サンプルモードに設定される期間よりも長くすることが望ましい。

#### 【 0 1 1 8 】

また、本実施形態の手法では、所与のタイミングでの温度検出電圧 V T D に対して、少なくとも 2 つの D / A 変換電圧 V D A C を用いた比較処理を行う。A 1 及び A 3 は 1 つめの D / A 変換電圧 V D A C を用いた比較処理に相当する。A 3 の終了後、温度検出電圧 V T D と 2 つめの D / A 変換電圧 V D A C を用いた比較処理を行う。この 2 回目の比較処理が A 5、A 6 に対応する。10

#### 【 0 1 1 9 】

A 5 は、A 1 と同様に温度検出電圧 V T D に対応する電荷を蓄積するサンプルモードである。なお、A 1 と A 5 では同じ温度検出電圧 V T D を対象としており、理想的にはキャパシター C のチャージ電圧 V c はコンパレーター モードの期間でも一定に保たれることから、A 5 のサンプルモードは不要であるとも考えられ、実際に A 5 を省略してもよい。しかし、サンプルモードとコンパレーター モードとの切り替えの際には、アナログスイッチ（S 1 ~ S 3）のオンオフが行われるため、電荷漏れが生じうる。図 8 の例では、この電荷漏れの可能性を考慮して、2 回目の比較処理の際にも再度サンプルモードで動作する期間 A 5 を設けている。20

#### 【 0 1 2 0 】

A 6 は、A 3 と同様に V c o m が H i g h、V s m p が L o w となり、D / A 変換電圧 V D A C が入力される。ただし、入力される D / A 変換電圧 V D A C は、A 3 とは異なるデジタルデータ（通常動作モードであれば後述するように 1 L S B 加算した値）を D / A 変換した電圧となり、それにより A 3 と A 6 では V i n の値が異なっている。

#### 【 0 1 2 1 】

図 8 の例では、A 6 では V D A C > V T D であったため、V o u t は徐々に小さくなり、安定した状態では低電位側電源電圧となる。処理部 2 3 では、V o u t が低電位側電源電圧（或いはそれに近い電圧）であると判定された場合には、温度検出電圧 V T D が D / A 変換電圧 V D A C よりも小さいとしてダウン判定を行う。30

#### 【 0 1 2 2 】

処理部 2 3 では、このようなアップ判定、ダウン判定の組み合わせに応じて、出力である温度検出データ D T D の値を決定すればよい。D / A 変換電圧 V D A C の生成に用いる具体的なデジタル値や、温度検出データ D T D の具体的な決定手法については、通常動作モード、ハイスピードモードのそれぞれについて後述する。

#### 【 0 1 2 3 】

##### 3.2 通常動作モード

通常動作モードは、上述したように A / D 変換結果データの急激な変化に起因する不具合、例えば周波数ホッピングによる不具合等を抑止する手法である。まず図 9 を用いて、周波数ホッピングが原因で発生する G P S (Global Positioning System) の通信エラーについて説明する。40

#### 【 0 1 2 4 】

G P S 衛星は、衛星軌道や時刻等に関する情報を図 9 の航法メッセージに含めて、G P S 衛星信号として、5 0 b p s のデータレートで送信している。このため 1 ビットの長さは 2 0 m s e c (P N コードの 2 0 周期) になる。1 つの航法メッセージは 1 つのマスター フレームで構成されており、1 つのマスター フレームは 1 5 0 0 ビットからなる 2 5 個のフレームで構成される。

#### 【 0 1 2 5 】

10

20

30

40

50

G P S衛星信号は、図9に示すように航法メッセージのビット値に応じてB P S K変調方式で変調されている。具体的には、航法メッセージに対してP Nコード（疑似ランダム符号）が乗算されてスペクトラム拡散が行われ、スペクトラム拡散後の信号に搬送波（1575.42MHz）が乗算されることで、B P S K変調が行われる。図9では、航法メッセージのB 1の部分のP Nコードが示され、P NコードのB 2の部分の搬送波が示されている。P Nコードの論理レベルが変化するタイミングで、B 3に示すように搬送波が位相反転する。搬送波の1波長の期間は0.635ns程度である。G P S受信機は、B P S K変調方式で変調された航法メッセージの搬送波を受信し、搬送波の受信信号の復調処理を行うことで、航法メッセージを取得する。

## 【0126】

10

このような受信信号の復調処理の際に、搬送波の周波数（1575.42MHz）との残差周波数を4Hz/20ms内に收めないと、復調処理において誤判定が生じてしまう。即ち、G P S航法メッセージの1ビット長の期間（G P S航法メッセージの周期）であるT P = 20msにおいて、搬送波の周波数との残差周波数を4Hz内に收めないと、周波数ホッピングによる通信エラーが生じてしまう。

## 【0127】

そして搬送波の周波数である1575.42MHzに対する上記の4Hzの割合が数p p b程度であるため、図2B、図2Cに示す許容ドリフト周波数であるF Dも数p p b程度になる。

## 【0128】

20

例えはG P Sの受信機では、本実施形態の回路装置（発振器）により生成される発振信号により、復調処理における搬送波の周波数が設定される。このため、発振信号の発振周波数の周波数ドリフトを、T P = 20msにおいて±F D内に收めることが必要になる。こうすることで、G P S衛星信号の受信信号の復調処理において誤判定の発生を防止でき、通信エラー（受信エラー）が生じるのを回避できる。

## 【0129】

しかしながら、従来のD T C X O等のデジタル方式の発振器では、期間T P（20ms）において周波数ドリフトを±F D（数p p b程度）内に抑えることは行ていなかった。このため図2Cに示すような周波数ホッピングが原因で、復調処理の誤判定による通信エラーが発生するという問題点があった。

30

## 【0130】

これに対して、通常動作モードでは隣り合う出力タイミング間での温度検出データD T Dの変化がk × L S B以下となるため、周波数ホッピング等を抑止可能である。

## 【0131】

図10は通常動作モードにおける処理を説明するフローチャートである。なお、ここではまずk = 1の場合を例にとって説明を行う。通常動作モードが開始されると、まず前回の温度検出データD T DのコードをD / A変換器26でD / A変換してD / A変換電圧V D A Cとする（S101）。そして、図8を用いて上述したように、サンプルモード（例えはA1）、コンパレーターモード（例えはA3）により温度検出電圧V T Dとの比較処理を行い、アップ判定とダウン判定のいずれかであるかの結果を取得する。

40

## 【0132】

次に、レジスター部の値、すなわち前回の温度検出データD T Dの値そのものに対して、1L S Bだけ加算し、加算後のデータをD / A変換器26でD / A変換してD / A変換電圧V D A Cとする（S102）。そして、図8を用いて上述したように、サンプルモード（例えはA5）、コンパレーターモード（例えはA6）により温度検出電圧V T Dとの比較処理を行い、アップ判定とダウン判定のいずれかであるかの結果を取得する。

## 【0133】

S101とS102により、比較部27は、前回の出力タイミングでの温度検出データD T D（前回の最終結果データ）をD / A変換器26で変換したD / A変換電圧V D A Cと、温度検出電圧V T Dを比較する第1の比較結果の出力、及び前回の最終結果データに

50

1 LSB を加算した第 2 のデータを D / A 変換器 26 で変換した D / A 変換電圧 VDAC と、温度検出電圧 VTD を比較する第 2 の比較結果の出力を行ったことになる。

#### 【0134】

処理部 23 は、この 2 つの比較処理の結果に基づいて、今回の温度検出データ DTD を決定する判定処理を行う（S103）。

#### 【0135】

まず、第 1 の比較結果に基づく判定処理により、温度検出電圧 VTD が D / A 変換電圧 VDAC よりも大きいと判定された場合、すなわちアップ判定であり、第 2 の比較結果に基づく判定処理の結果もアップ判定である場合は、今回の前記最終結果データを、第 2 のデータ、すなわち前回の温度検出データ DTD に 1 LSB を加算した値に決定する（ステップ S104）。 10

#### 【0136】

2 つの比較処理の両方がアップ判定である場合とは、現在の温度が前回の出力タイミングでの温度よりも充分大きくなっている状態に対応する。そのため、今回の温度検出データ DTD は前回の温度検出データ DTD よりも大きくするとよく、ここでは変化幅を 1 LSB 以下としているため、1 LSB だけ加算した値を出力すればよい。

#### 【0137】

また、第 1 の比較結果に基づく判定処理により、温度検出電圧 VTD が D / A 変換電圧 VDAC よりも小さいと判定された場合、すなわちダウン判定であり、第 2 の比較結果に基づく判定処理の結果もダウン判定である場合は、今回の最終結果データを、前回の最終結果データから 1 LSB を減算したデータに決定する（ステップ S105）。 20

#### 【0138】

2 つの比較処理の両方がダウン判定である場合とは、現在の温度が前回の出力タイミングでの温度よりも充分小さくなっている状態に対応する。そのため、今回の温度検出データ DTD は前回の温度検出データ DTD よりも小さくするとよく、ここでは変化幅を 1 LSB 以下としているため、1 LSB だけ減算した値を出力すればよい。

#### 【0139】

また、第 1 の比較結果に基づく判定処理の結果がアップ判定であり、第 2 の比較結果に基づく判定処理の結果がダウン判定である場合とは、温度の変化が大きくなない状態に対応する。そのため、今回の温度検出データ DTD は前回の温度検出データ DTD の値を維持すればよい（ステップ S106）。 30

#### 【0140】

また、第 1 の比較結果に基づく判定処理の結果がダウン判定であり、第 2 の比較結果に基づく判定処理の結果がアップ判定である場合とは、通常起こりえない状態である。なぜなら、この場合の温度検出電圧 VTD は、所与の電圧に比べて小さく、且つ当該所与の電圧よりも大きい電圧に比べて大きいことになり、そのような電圧値は存在しないためである。この状態では第 1 , 第 2 の比較処理の少なくとも一方が適切に行えていないおそれがあるため、そのような不適切な判定により出力する温度検出データ DTD の値を変動させることは好ましくない。よって本実施形態では、第 1 の比較結果がダウン判定であり、第 2 の比較結果がアップ判定である場合には、今回の温度検出データ DTD は前回の温度検出データ DTD の値を維持する（ステップ S106）。 40

#### 【0141】

ここでは k = 1 としたため比較処理が 2 回となったが、k が 2 以上の場合も処理の簡略化が可能な点は同様である。すなわち、 $\pm k \times \text{LSB}$  を超えるような MSB 側のビットについては、既に求められている前回の温度検出データ DTD の値をそのまま流用可能であるため、当該ビットを決定するための比較処理を省略できるという効果がある。

#### 【0142】

例えば、比較部 27 は、前回の出力タイミングでの温度検出データ DTD に対応する前回の最終結果データを D / A 変換器 26 で変換した D / A 変換電圧 VDAC と、温度検出電圧 VTD とを比較して第 1 の比較結果を出力し、前回の最終結果データが  $k \times \text{LSB}$  以 50

下の範囲で更新されたデータをD/A変換器26で変換したD/A変換電圧V<sub>DAC</sub>と、温度検出電圧V<sub>TD</sub>とを比較して第2の比較結果を出力する。そして処理部23は、第1の比較結果及び第2の比較結果に基づく判定処理を行い、判定処理に基づいて、前回の最終結果データをk×LSB以下の範囲で更新して、今回の最終結果データとして決定する更新処理を行えばよい。

#### 【0143】

ステップS104～S106のいずれかの処理後は、通常動作モードを終了するか否か、例えばディスエーブル信号が入力されたか否かを判定し(ステップS107)、S107でYesの場合には通常動作モードを終了し、Noの場合にはステップS101に戻り処理を継続する。

10

#### 【0144】

なお、以上では所与のデジタルデータと、当該デジタルデータに対応するアナログ信号(D/A変換電圧)との関係として図11Aに示した関係を想定していた。具体的には、デジタルデータとして所与の値Dと、D+1LSB、D-1LSBを設定し、各デジタルデータに対応するアナログ信号(電圧値)をV<sub>D</sub>、V<sub>D+1</sub>、V<sub>D-1</sub>とした場合に、電圧値がV<sub>D-1</sub>～V<sub>D</sub>の場合に対応するデジタルデータをD-1LSBとし、電圧値がV<sub>D</sub>～V<sub>D+1</sub>の場合に対応するデジタルデータをDとし、電圧値がV<sub>D+1</sub>～V<sub>D+2</sub>の場合に対応するデジタルデータをD+1LSBとする関係である。この例であれば、出力であるデジタルデータをDにするかD±1LSBにするかの境界は、BO1とBO2すなわちV<sub>D</sub>とV<sub>D+1</sub>である。そのため、S101、S102を用いて上述したように、D/A変換器26に入力するデータ(コード)は、前回の温度検出データDTD、及びそれに1LSBを加算した値を用いれば、今回の温度検出データDTDを前回の値そのままとするか±1LSBするかを適切に判定可能である。

20

#### 【0145】

しかし、アナログ信号とデジタルデータとの関係は図11Aに限定されるものではなく、例えば図11Bを用いてもよい。図11Bでは、電圧値がV<sub>D-2</sub>～V<sub>D-1</sub>の場合に対応するデジタルデータをD-1LSBとし、電圧値がV<sub>D-1</sub>～V<sub>D</sub>の場合に対応するデジタルデータをDとし、電圧値がV<sub>D</sub>～V<sub>D+1</sub>の場合に対応するデジタルデータをD+1LSBとしている。図11Bの例であれば、出力であるデジタルデータをDにするかD±1LSBにするかの境界は、BO3とBO4すなわちV<sub>D-1</sub>とV<sub>D</sub>である。そのため、D/A変換器26に入力するデータ(コード)は、前回の温度検出データDTD、及びそれから1LSBを減算した値を用いるとよいことになる。

30

#### 【0146】

この場合、比較部27は、前回の出力タイミングでの温度検出データDTDに対応する前回の最終結果データをD/A変換器26で変換したD/A変換電圧V<sub>DAC</sub>と、温度検出電圧V<sub>TD</sub>を比較する第1の比較結果の出力、及び前回の最終結果データから1LSBが減算された第2のデータをD/A変換器26で変換したD/A変換電圧V<sub>DAC</sub>と、温度検出電圧V<sub>TD</sub>を比較する第2の比較結果の出力を行えばよい。

#### 【0147】

この場合も処理部23での判定は同様に行えばよい。処理部23は、第1の比較結果に基づく判定処理の結果がアップ判定であり、第2の比較結果に基づく判定処理の結果もアップ判定である場合は、今回の最終結果データを、前回の最終結果データに1LSBを加算したデータに決定する。また、第1の比較結果に基づく判定処理の結果がダウン判定であり、第2の比較結果に基づく判定処理の結果もダウン判定である場合は、今回の最終結果データを第2のデータ(-1LSBしたデータ)に決定する。

40

#### 【0148】

また、処理部23は、第1の比較結果に基づく判定処理の結果、及び第2の比較結果に基づく判定処理の結果の一方がアップ判定であり、且つ他方がダウン判定である場合は、今回の最終結果データ(温度検出データDTD)を、前回の最終結果データに決定すればよい。

50

**【0149】**

なお、図7Aでは比較部27への入力は、D/A変換電圧V<sub>DAC</sub>と温度検出電圧V<sub>TD</sub>の2つであるものとしたがこれには限定されない。上述したように、通常動作モードでは温度検出電圧V<sub>TD</sub>との比較対象となる電圧は、前回の温度検出データD<sub>TD</sub>をD/A変換した第1のD/A変換電圧V<sub>DAC\_A</sub>と、前回の温度検出データD<sub>TD</sub>にLSBを加算（減算）したデータをD/A変換した第2のD/A変換電圧V<sub>DAC\_B</sub>との2つである。つまり、比較部27に対してV<sub>DAC\_A</sub>とV<sub>DAC\_B</sub>とが入力できればよいため、図7A～図7Cに示したように1つの入力経路を時分割的に利用して、V<sub>DAC\_A</sub>を入力する期間とV<sub>DAC\_B</sub>を入力する期間を設けてもよいし、V<sub>DAC\_A</sub>を入力する経路とV<sub>DAC\_B</sub>を入力する経路を別途設けてもよい。

10

**【0150】**

図12が経路を別途設ける場合の比較部27の構成例である。図12に示したように、比較部27はD/A変換器26とキャパシターCの一端との間に設けられる第4のスイッチS4を含み、S4に対してはD/A変換器26から第2のD/A変換電圧V<sub>DAC\_B</sub>が入力される。この例では、V<sub>DAC\_A</sub>とV<sub>TD</sub>を比較するコンパレーターモード（図8のA3）では、S1をオン、S2～S4をオフに設定し、V<sub>DAC\_B</sub>とV<sub>TD</sub>を比較するコンパレーターモード（図8のA5）では、S1～S3をオフ、S4をオンに設定すればよい。

20

**【0151】****3.3 ハイスピードモード**

次に第1のA/D変換方式の具体例としてハイスピードモードについて説明する。ハイスピードモードは上述したように、MSB側とLSB側とで判定期間に差を設ける手法であるため、まず具体的な判定期間について説明する。

**【0152】**

上述したように、MSB側のビットは大きな値に対応するため、当該ビットを0にするか1にするかに応じて値（D/A変換をした場合にはアナログ信号である電圧値）が大きく変化する。そのため、比較部27における比較処理の誤判定の可能性がLSB側に比べて低い。しかし、そうは言っても誤判定の可能性は残るし、本実施形態ではMSB側の判定期間が短いため誤判定の可能性も高まる。さらに、上述してきたようにMSB側は値に対する寄与度が高いため、誤判定が生じた場合の影響が非常に大きい。

30

**【0153】**

本実施形態では、その点を考慮して、LSB側の判定結果に基づいてMSB側の判定結果を修正する。 LSB側は判定期間が相対的に長いため、判定精度も高くできる。つまり、判定精度が高いLSB側の結果により、判定精度が相対的に低いMSB側の結果を修正することで、温度検出データD<sub>TD</sub>の精度を高くすることが可能になる。よって以下では、この修正手法についても説明する。

**【0154】**

なお、ハイスピードモードは逐次比較型に準ずる手法であり、温度検出データD<sub>TD</sub>の値をMSB側から1ビットずつ決定していくことは妨げられない。ただし、後述するように、LSB側の結果によるMSB側の結果の修正を、下位ビットからの繰り上がり又は繰り下がりにより実現しようとした場合、1ビットずつの処理では全ビットについて繰り上がり、繰り下がりの可能性を考慮しなくてはならず比較処理の回数が増えてしまう。例えばA/D変換を15ビットで行う場合、最上位ビットを除く14ビットの処理において、毎回繰り上がり繰り下がりの有無を判定しなくてはならない。その場合、1回当たりの比較処理の時間を短くしたとしても、高速化の効果が薄れるおそれがある。

40

**【0155】**

よって、下位ビットからの繰り上がり又は繰り下がりを行いつつ、効率的に高速化を行うためには、繰り上がり（繰り下がり）の発生を判定する回数を少なくするとよい。例えば、2ビットを1単位として処理を行った場合、15ビットは後述するように8つのビット範囲に区画され、最上位2ビット以外の7つのビット範囲において繰り上がり繰り下が

50

りの判定をすればよいことになる。

#### 【0156】

よって以下では、A / D 変換結果データを、所与のビット幅で複数のビット範囲に区画し、区画された各ビット範囲において M S B 側から L S B 側にビット値を決定していく場合を例にとって説明する。特に後述の例では、所与のビット幅とは 2 ビットである。もちろん、ここでの所与のビット幅を 3 ビット以上としてもよいし、上述したように 1 ビット単位で処理を行ってもよい。また、図 13 A や図 13 B では最下位ビットが 1 ビットを単位としていることからわかるように、全ビット範囲を同一のビット幅に設定する必要はなく、例えば M S B 側と L S B 側とで異なるビット幅を設定するといった変形実施も可能である。

10

#### 【0157】

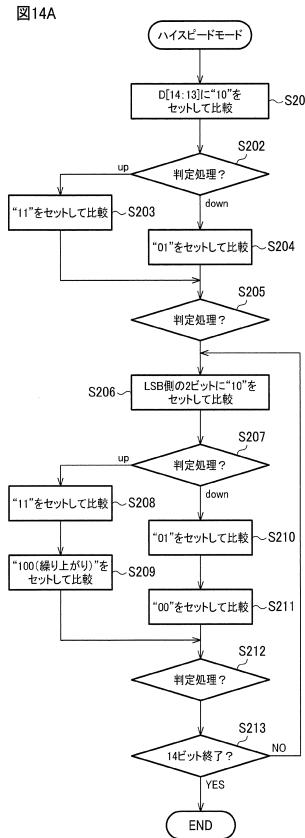

##### 3.3.1 M S B 側と L S B 側での判定期間の差

図 13 A、図 13 B にハイスピードモードにおける判定期間の設定例を示す。図 13 A の横軸は時間を表す。図 13 A の上段はモードを表し、ここではハイスピードモードの中でも判定期間の長さが異なる 3 つのモード（モード 1 ~ モード 3）が設定されている。図 13 A の下段は、15 ビットの A / D 変換結果データのうち、どのビットが判定対象となっているかを表すものである。D [ x : y ]との表記は、A / D 変換結果データのうち、最下位ビット（L S B）から数えて y ビット目から x ビット目までの x - y + 1 ビットの幅を持つデータを表す。最下位ビットを D [ 0 ] としているため、例えば D [ 14 : 13 ] であれば最も M S B 側の 2 ビットを表す。

20

#### 【0158】

図 13 A からわかるように、D [ 14 : 13 ] ~ D [ 6 : 5 ] の 5 区画では最も判定期間の短い（最も高速の）モード 1 に設定される。なお、図 13 A では D [ 14 : 13 ] とそれ以外とで判定期間の長さが異なるが、これは最上位のビットでは繰り上がり繰り下がりを考慮しなくてもよいという観点から生じたものであって、1 回の比較処理に要する時間に差はない。

#### 【0159】

そして、D [ 4 : 3 ] では、モード 1 に比べて判定期間の長いモード 2 に設定され、D [ 2 : 1 ] ではさらに判定期間の長いモード 3 に設定される。また、最下位ビットである D [ 0 ] については、モード 3 よりもさらに判定期間が長く設定される。詳細については後述するが、例えば D [ 0 ] の判定は上述した通常動作モードと同様の処理により実現されてもよい。

30

#### 【0160】

図 13 B が具体的な判定期間の設定例である。図 13 B の例では最も高速であるモード 1 では、サンプルモード及びコンパレーターモードのいずれについても、A / D 変換に用いるクロックに換算して 2 クロック分の期間を設定している。クロックは種々の設定が可能であるが、例えば 128 kHz である。

#### 【0161】

D [ 14 : 13 ] については、図 14 A のステップ S 201、ステップ S 203（或いはステップ S 204）を用いて後述するように、当該 2 ビットのデータの決定には 2 回の比較処理を行えばよい。つまり、D [ 14 : 13 ] は、1 回目のサンプルモード、1 回目のコンパレーターモード、2 回目のサンプルモード、2 回目のコンパレーターモードのそれぞれについて 2 クロック分の期間を要するため、合計で 8 クロック分の期間が判定期間として設定される。クロックが 128 kHz であれば、D [ 14 : 13 ] の判定期間は 62.5 μsec となる。

40

#### 【0162】

D [ 12 : 11 ] ~ D [ 6 : 5 ] の 4 区画については、図 14 A のステップ S 206、ステップ S 208 及びステップ S 209（或いはステップ S 210 及びステップ S 211）を用いて後述するように、当該 2 ビットのデータの決定及び繰り上がり繰り下がりの有無の決定に 3 回の比較処理が必要となる。よって、サンプルモード、コンパレーターモー

50

ドはそれぞれ3回ずつ実行され、各期間が2クロック分であるため、合計で12クロック分の期間が判定期間として設定される。クロックが128kHzであれば、D[12:1]～D[6:5]の各区画の判定期間は93.75μsecとなる。

#### 【0163】

D[4:3]では、それよりもMSB側に比べて判定精度を高くするために、比較的長い判定時間を設定する。その際、図8の波形図を用いて説明したように、コンパレーターモードの期間を長くする方が、サンプルモードの期間を長くする場合に比べて精度に対する寄与が大きい。よって図13Bの例では、モード2では、サンプルモードに2クロック分、コンパレーターモードに6クロック分の期間を割り当てる。D[4:3]でも、行われる比較処理は3回であるため、(2+6)×3の合計24クロック分の期間が判定期間として設定される。クロックが128kHzであれば、D[4:3]の判定期間は187.5μsecとなる。

#### 【0164】

D[2:1]では、さらに長い判定時間を設定する。図13Bの例では、モード3では、コンパレーターモードに12クロック分の期間を割り当てている。また、図8を用いて上述したようにサンプルモードも長い方が精度が期待できるため、ここではサンプルモードの期間も4クロック分に拡張している。D[2:1]でも、行われる比較処理は3回であるため、(4+12)×3の合計48クロック分の期間が判定期間として設定される。クロックが128kHzであれば、D[2:1]の判定期間は375μsecとなる。

#### 【0165】

D[0]では、さらに長い判定時間を設定する。図13Bの例では、コンパレーターモードに24クロック分、サンプルモードに8クロック分の期間を割り当てている。なお、後述するようにD[0]では通常動作モードと同様の処理を行ってもよい。この場合、比較処理は2回となるため、(8+24)×2の合計64クロック分の期間が判定期間として設定される。クロックが128kHzであれば、D[0]の判定期間は500μsecとなる。

#### 【0166】

なお、通常動作モードの説明では具体的な判定期間について触れなかったが、一例としてはD[0]と同様に、コンパレーターモードに24クロック分、サンプルモードに8クロック分の期間を割り当ればよい。もちろん、D[0]の処理内容や判定期間は通常動作モードと同一にする必要はなく、種々の変形実施が可能である。

#### 【0167】

また、図14Aのフローチャートを用いて後述するように、ハイスピードモード自体はD[14:1]までを決定するモードであると考え、ハイスピードモード内でD[0]を決定しないものとしてもよい。この場合、ハイスピードモードで決定したD[14:1]と、初期状態（後述の例では0）のままであるD[0]とから構成される15ビットのデータを初期値として、通常動作モードに移行することになる。最下位ビットやその近傍のビットについては実際の温度と誤差が生じている可能性があるが、その誤差は充分小さく、通常動作モードにおいてk×LSBずつ値を近づけていく処理でも大きな問題は生じない。

#### 【0168】

図13Bの変換時間の積算を見ればわかるように、15ビット精度のA/D変換の実行を例えれば1.5msで実現することができ、上述した2ms以内といった要求を満足することが可能になる。

#### 【0169】

なお、図13A、図13Bはハイスピードモードにおける判定期間の設定の一例であり、種々の変形実施が可能である。例えば、サンプルモードとコンパレーターモードに割り当てるクロック数を図13Bとは異なる値に設定してもよいし、上述したように2回目3回目のサンプルモード自体を省略してもよい。或いは、 LSB側の判定結果に基づくMSB側の判定結果の修正、例えは繰り上がりや繰り下がりを考慮しない場合であれば、D[

10

20

30

40

50

$[12:11] \sim [2:1]$  の各区間についても比較処理の回数を減らせるため、より高速化を実現することが可能である。また、ここではハイスピードモードのモード1～3及びノーマルモードの4段階で判定期間を変更する設定例を示したが、少なくともMSB側とLSB側とで判定期間が異なればよいため、判定期間の長さは2段階や3段階で変化させてもよいし、5段階以上で変化させることも可能である。

#### 【0170】

以上のように、処理部23は、比較部27での比較期間の長さを設定することで、第1の判定期間(MSB側の判定期間)及び第2の判定期間(LSB側の判定期間)の長さを設定してもよい。

#### 【0171】

ここで比較期間は、具体的にはサンプルモードを実行する期間及びコンパレーターモードを実行する期間の両方を表すものであってもよいし、コンパレーターモードを実行する期間を比較期間と考えてもよい。上述したように、コンパレーターモードを実行する期間を長くすることで、効率的にA/D変換の精度を向上させることが可能になる。

#### 【0172】

また、A/D変換結果データが第1～第N(Nは2以上の整数)のビット範囲に区画される場合に、A/D変換結果データのMSB側の判定処理は、第1～第p(pは1以上の整数)のビット範囲に対する判定処理を含み、A/D変換結果データのLSB側の判定処理は、第q(qは $p < q \leq N$ を満たす整数)～第Nのビット範囲に対する判定処理を含んでもよい。

#### 【0173】

図13A、図13Bの例では、 $N = 8$ であり、 $p = 5$ 、 $q = 8$ である。すなわち、 $D[14:13] \sim D[6:5]$ の第1～第5のビット範囲がMSB側であり、当該5範囲については最も短い判定期間により判定処理を行う。また、 $D[0]$ である第8のビット範囲がLSB側であり、当該1範囲については最も長い判定期間により判定処理を行う。また、図13A、図13Bの例では、判定期間は4段階で変更しており、中間的な長さの判定期間が設定されるビット範囲が存在する。具体的には第6のビット範囲である $D[4:3]$ は第1～第5のビット範囲より長く、第8のビット範囲より短い判定期間が設定され、第7のビット範囲である $D[2:1]$ は第6のビット範囲より長く、第8のビット範囲より短い判定期間が設定される。

#### 【0174】

##### 3.3.2 LSB側の判定結果に基づくMSB側の判定結果の修正

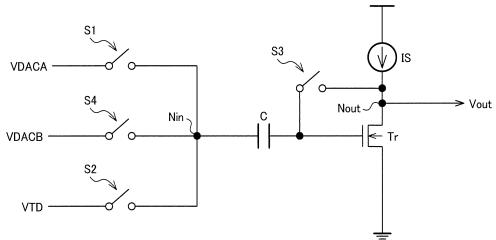

図14Aは、ハイスピードモードにおける具体的な処理の流れを説明するフローチャートである。ハイスピードモードは、大きく $D[14:13]$ を判定する部分(ステップS201～S205)と、 $D[12:1]$ を判定する部分(ステップS206～S213)とに分けられる。両者の差異は、MSB側への繰り上がり繰り下がりの有無である。以下詳細に説明する。

#### 【0175】

ハイスピードモードの開始時には、A/D変換結果データとして中間的な値が設定されている。例えば”1000000000000000”といったデータである。まず、 $D[14:13]$ の判定では、当該2ビットに”10”をセットしたデータをD/A変換してD/A変換電圧V<sub>DAC</sub>を生成し、温度検出電圧V<sub>TD</sub>との比較処理を行い(ステップS201)、処理部23でその結果に基づく判定処理を行う(ステップS202)。なお、判定対象とされていない他の13ビットについては、既に判定済みの値、或いは初期値をセットしておけばよい。 $D[14:13]$ の場合、 $D[12:0]$ は未判定、且つ初期値は全て0であるため、 $D[14:13]$ に”10”をセットした場合のデータは、”10000000000000”となる。

#### 【0176】

ステップS202で $V_{TD} > V_{DAC}$ である、すなわちアップ判定であるとされた場合には、 $D[14:13]$ に”11”をセットしたデータをD/A変換してD/A変換電圧

10

20

30

40

50

V D A Cを生成し、温度検出電圧V T Dとの比較処理を行う（ステップS 2 0 3）。一方、ステップS 2 0 2でV T D < V D A Cである、すなわちダウン判定であるとされた場合には、D [ 1 4 : 1 3 ]に”0 1”をセットしたデータをD / A変換してD / A変換電圧V D A Cを生成し、温度検出電圧V T Dとの比較処理を行う（ステップS 2 0 4）。

#### 【0 1 7 7】

そして処理部2 3は、ステップS 2 0 3或いはS 2 0 4の結果を判定する（ステップS 2 0 5）。図14Bは、具体的な判定内容を示す図である。”1 0”でアップ判定且つ”1 1”でもアップ判定の場合（ステップS 2 0 3に移行しそこでもアップ判定の場合）、D [ 1 4 : 1 3 ] = ”1 1”とする。”1 0”でアップ判定且つ”1 1”でダウン判定の場合（ステップS 2 0 3に移行しそこでダウン判定の場合）、D [ 1 4 : 1 3 ] = ”1 0”とする。”1 0”でダウン判定且つ”0 1”でアップ判定の場合（ステップS 2 0 4に移行しそこでアップ判定の場合）、D [ 1 4 : 1 3 ] = ”0 1”とする。”1 0”でダウン判定且つ”0 1”でもダウン判定の場合（ステップS 2 0 4に移行しそこでもダウン判定の場合）、D [ 1 4 : 1 3 ] = ”0 0”とする。

10

#### 【0 1 7 8】

以上の処理は一般的な比較処理と同様であり、特に繰り上がり繰り下がりは考慮しなくてよい。

#### 【0 1 7 9】

次に、2ビットL S B側の判定処理に移行する。まずはD [ 1 2 : 1 1 ]の2ビットについて”1 0”をセットしたデータをD / A変換してD / A変換電圧V D A Cを生成し、温度検出電圧V T Dとの比較処理を行い（ステップS 2 0 6）、処理部2 3でその結果に基づく判定処理を行う（ステップS 2 0 7）。この場合、D [ 1 4 : 1 3 ]には、ステップS 2 0 5で決定された値をセットし、D [ 1 0 : 0 ]には初期値（ここでは”0”）をセットする。例えば、D [ 1 4 : 1 3 ] = ”1 1”と決定された場合であれば、ステップS 2 0 6でセットするデータは”1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0”となる。

20

#### 【0 1 8 0】

ステップS 2 0 7でアップ判定の場合、D [ 1 2 : 1 1 ]に”1 1”をセットしたデータをD / A変換してD / A変換電圧V D A Cを生成し、温度検出電圧V T Dとの比較処理を行う（ステップS 2 0 8）。しかし、”1 1”をセットした場合にV T D > V D A Cとなつたとしても、ステップS 2 0 5で上述したように、D [ 1 2 : 1 1 ]が”1 1”と判定されるのみで、よりM S B側のビット（ここではD [ 1 4 : 1 3 ]）に対する修正ができるない。よって、繰り上がりを考慮するためには、D [ 1 2 : 1 1 ]に”1 1”をセットするよりもさらに大きい値をセットする必要がある。

30

#### 【0 1 8 1】

具体的には、繰り上がりが生じた状態のデータをセットしたデータをD / A変換してD / A変換電圧V D A Cを生成し、温度検出電圧V T Dとの比較処理を行う（ステップS 2 0 9）。この例ではD [ 1 2 : 1 1 ] = ”0 0”とし、D [ 1 3 ]の値を1大きくすればよい。例えば、D [ 1 4 : 1 3 ] = ”0 1”と判定されていた場合であれば、D [ 1 4 : 1 1 ] = ”1 0 0 0”をセットする。つまりステップS 2 0 8でD [ 1 4 : 1 1 ] = ”0 1 1 1”をセットし、ステップS 2 0 9ではさらにそれよりも大きい”1 0 0 0”をセットする。

40

#### 【0 1 8 2】

また、ステップS 2 0 7でダウン判定の場合、D [ 1 2 : 1 1 ]に”0 1”をセットしたデータをD / A変換してD / A変換電圧V D A Cを生成し、温度検出電圧V T Dとの比較処理を行う（ステップS 2 1 0）。しかし、”0 1”をセットした場合にV T D < V D A Cとなつたとしても、ステップS 2 0 5で上述したように、D [ 1 2 : 1 1 ]が”0 0”と判定されるのみで、よりM S B側のビットに対する修正（具体的には小さくする修正）ができるない。よって、繰り下がりを考慮するためには、D [ 1 2 : 1 1 ]に”0 1”をセットするよりもさらに小さい値をセットする必要がある。具体的には、D [ 1 2 : 1 1 ]に”0 0”をセットしたデータをD / A変換してD / A変換電圧V D A Cを生成し、温

50

度検出電圧VTDとの比較処理を行う(ステップS211)。

**【0183】**

そして処理部23は、ステップS208、S209の比較結果、或いはステップS210、S211の比較結果に基づく判定を行う。図14Cは、具体的な判定内容を示す図である。まず207でアップ判定である場合について説明する。この場合、ステップS208、S209の比較処理を行い、それぞれについてアップ判定、ダウン判定があり得るため合計4通りのパターンがあり得る。

**【0184】**

ステップS208及びS209の両方でアップ判定の場合、温度検出電圧VTDは繰り上がりが必要な程度に大きいことがわかる。よって、判定対象としている2ビットの値は”00”に決定し、その1つMSB側のビットに1を加算する。また、ステップS208及びS209の両方でダウン判定の場合、温度検出電圧VTDは”10”をセットした場合と”11”をセットした場合の間にあることがわかるため、判定対象としている2ビットは”10”に決定する。10

**【0185】**

また、ステップS208でアップ判定であり、ステップS209でダウン判定の場合、温度検出電圧VTDは、”11”をセットした場合と繰り上がりが生じる場合との間にあることがわかるため、判定対象としている2ビットは”11”に決定する。

**【0186】**

また、ステップS208でダウン判定であり、ステップS209でアップ判定の場合、通常ではあり得ないエラー状態であることがわかる。エラー状態である場合の処理は種々考えられるが、ここでは”11”という値を設定するものとしている。つまり、ステップS208、209については(1)両方アップ判定の場合(2)両方ダウン判定の場合(3)一方がアップ判定で他方がダウン判定の場合、の3パターンを考慮して値を決定する。20

**【0187】**

次に、207でダウン判定である場合について説明する。この場合、ステップS210、S211の比較処理を行い、それぞれについてアップ判定、ダウン判定があり得るため合計4通りのパターンがあり得る。

**【0188】**

ステップS210及びS211の両方でアップ判定の場合、温度検出電圧VTDは”01”をセットした場合と”10”をセットした場合の間にあることがわかるため、判定対象としている2ビットは”01”に決定する。ステップS210及びS211の両方でダウン判定の場合、温度検出電圧VTDは繰り下がりが必要な程度に小さいことがわかる。よって、判定対象としている2ビットの値は”11”に決定し、その1つMSB側のビットから1を減算する。例えば、D[14:13] = ”10”である場合であって、D[12:11]で繰り下がりが必要と判定された場合には、D[14:11] = ”0111”に決定すればよい。

**【0189】**

また、ステップS210でダウン判定であり、ステップS211でアップ判定の場合、温度検出電圧VTDは、”00”をセットした場合と”01”をセットした場合との間にあることがわかるため、判定対象としている2ビットは”00”に決定する。40

**【0190】**

また、ステップS210でアップ判定であり、ステップS211でダウン判定の場合、通常ではあり得ないエラー状態であることがわかる。エラー状態である場合の処理は種々考えられるが、ここでは”00”という値を設定するものとしている。つまり、ステップS210、S211についても(1)両方アップ判定の場合(2)両方ダウン判定の場合(3)一方がアップ判定で他方がダウン判定の場合、の3パターンを考慮して値を決定する。

**【0191】**

図15にハイスピードモードでの具体的な数値の決定例を示す。縦軸が時間を表し、表の上から下へ向かって処理が進んでいく。DB[14:0]はD/A変換器26でのD/A変換の対象となるデータ(D/A変換電圧V<sub>DAC</sub>のもととなるデータ)を表し、DO[14:0]がハイスピードモードの出力となる15ビット精度のA/D変換結果データを表す。DBの値を種々変更しながら比較処理、判定処理を行い、その結果によりDOを更新していく。そしてLSB側のビットまで処理が終わったタイミングでのDOがA/D変換結果データに対応することになる。なお、上述したように、MSB側とLSB側とで実際には判定期間が異なることになるが、図15では便宜上縦軸での長さには差を設けていない。また、DB, DOのうち、網掛けで示された部分は値が更新されたビットを表す。C8を用いて後述するように、繰り上がり繰り下がりが生じる場合には、処理対象でないビットについても更新対象となる可能性がある。

10

#### 【0192】

まず、最もMSB側の2ビットの”10”がセットされ(C1、ステップS201に対応)、判定処理が行われる。ここではアップ判定であったため、次に当該2ビットに”11”がセットされ(C2、ステップS203に対応)、判定処理が行われる。ここでもアップ判定であったため、DO[14:13]が”11”に決定され(C3)、D[12:11]の判定に移行する。

#### 【0193】

D[12:11]では、まず”10”がセットされ(C4、ステップS206に対応)、判定処理が行われる。ここではダウン判定であったため、”01”、“00”がセットされる(C5、C6、ステップS210, 211に対応)。図15の例では、C5, C6の両方がアップ判定であったため、DO[12:11]が”01”に決定され(C7)、D[10:9]の判定に移行する。

20

#### 【0194】

以下、説明を簡略化する。D[10:9]では、”10”でアップ判定、且つ”11”、“100(繰り上がり)”の一方がアップ、他方がダウン判定となり、DO[10:9]は”11”に決定されている。なお、”100”をセットする際には、繰り上がりが生じるためDB[12:11]が”10”となっている(C8)。

#### 【0195】

D[8:7]では、”10”でダウン判定、且つ”01”、“00”の両方がダウン判定となり、繰り下がりが生じている。具体的には、DO[8:7]は”11”に決定されるとともに、”11”に決定されてたD[10:9]に対して減算が行われ、D[10:9]が”10”に修正されている。

30

#### 【0196】

D[6:5]では、”10”でアップ判定、且つ”11”、“100(繰り上がり)”の両方がアップ判定となり、繰り上がりが生じている。具体的には、DO[6:5]は”00”に決定されるとともに、”11”に決定されてたDO[8:7]に対して加算が行われる。この場合、さらにMSB側のビットまで繰り上がりが波及し、D[10:7]=”1011”であったものが、”1100”に修正されている。

40

#### 【0197】

D[4:3]では、”10”でアップ判定、且つ”11”、“100(繰り上がり)”の両方がダウン判定となり、DO[4:3]は”10”に決定されている。

#### 【0198】

D[2:1]では、”10”でダウン判定、且つ”01”、“00”的一方がアップ、他方がダウン判定となり、DO[2:1]は”00”に決定されている。

#### 【0199】

D[0]では、通常動作モードと同様であるため、それまでに決定されたDO[14:0]をセットした場合の比較処理と、DO[14:0]に1 LSBを加算した値をセットした場合の比較処理を行い、1 LSB以下の範囲で値を更新すればよい。この例では、D[0]の初期値が0であるため、1 LSB減算した場合に繰り下がりが生じる。繰り上

50

がりを生じさせたいのであれば初期値を 1 にセットすればよい。

#### 【0200】

或いは、通常動作モードとは動作を変更し、まず”1”をセットし、アップ判定の場合に”10(繰り上がり)”をセット、ダウン判定の場合に”0”をセットするという変形実施を行ってもよい。この例では、両方アップ判定であれば繰り上がり、両方ダウン判定であれば繰り下がり、”1”でアップ判定且つ”10”でダウン判定の場合は”1”に決定、“1”でダウン判定且つ”0”でアップ判定の場合は”0”に決定すればよい。

#### 【0201】

以上のように、処理部 23 は、第 1 ~ 第 N のビット範囲のうちの、第 r ( r は 2 ~ N を満たす整数 ) のビット範囲での判定結果に基づいて、第 r のビット範囲の M S B 側の第 r - 1 のビット範囲の結果を変更する。

10

#### 【0202】

例えば、図 15 の例では、第 4 のビット範囲 ( D [ 8 : 7 ] ) の判定結果が繰り下がりであることにより、それよりも M S B に近いビット範囲である第 3 のビット範囲 ( D [ 10 : 9 ] ) が変更される。具体的には、D [ 10 : 9 ] が”11”から”10”に変更されている。同様に、第 5 のビット範囲 ( D [ 6 : 5 ] ) の判定結果が繰り上がりであることにより、それよりも M S B に近いビット範囲である第 4 のビット範囲 ( D [ 8 : 7 ] ) が変更される。なお、繰り上がりや繰り下がりが上位ビットに波及していくことがあるため、第 r のビット範囲での判定結果に基づいて、第 r - 2 のビット範囲やさらに M S B 側のビット範囲の結果が変更される場合も考えられる。

20

#### 【0203】

##### 4 . D T C X O の場合の他の構成の例

図 4 を用いて上述したように、本実施形態に係る回路装置は、D / A 変換器 26 と、比較部 27 と、処理部 23 とを含む A / D 変換部 20 と、温度検出データ D T D に基づいて発振周波数の温度補償処理を行い、発振周波数の周波数制御データを出力するデジタル信号処理部 50 と、デジタル信号処理部 50 からの周波数制御データと振動子 X T A L を用いて、周波数制御データにより設定される発振周波数の発振信号を生成する発振信号生成回路 140 と、を含むものであってもよい。

#### 【0204】

この例において、周波数ホッピングは A / D 変換部 20 の出力である温度検出データ D T D の変化を k × L S B 以下に抑制することで実現されてもよい。しかし、周波数ホッピングは直接的には発振信号生成回路 140 の出力の変動に関連するものであるため、当該出力に関係する他の構成において周波数ホッピングを抑止する手法を併用してもよい。

30

#### 【0205】

以下、具体的な手法を説明した後、当該手法を実現するデジタル信号処理部 50 、 D / A 変換部 80 の構成例について説明する。また、 D T C X O に用いられる温度センサー部 10 や発振回路 150 の構成例についても説明する。

#### 【0206】

##### 4 . 1 A / D 変換部以外の構成による周波数ホッピングの抑止手法

周波数ホッピングを抑止するには、図 16 に示すように、第 1 の温度 T 1 から第 2 の温度 T 2 に温度が変化した場合に、第 1 の制御電圧 V C 1 と第 2 の制御電圧 V C 2 の差分電圧 V D F の絶対値よりも小さい電圧幅で変化する出力電圧 V Q が、D / A 変換部 80 から発振回路 150 に出力されるようにすればよい。

40

#### 【0207】

差分電圧 V D F の絶対値は、例えば | V C 1 - V C 2 | である。この場合に V C 1 > V C 2 であってもよいし、V C 1 < V C 2 であってもよい。また、温度変化が無いことなどにより、V C 1 = V C 2 ( D T D 1 = D T D 2 ) である場合には、出力電圧 V Q の変化電圧幅も当然に 0 V になり、差分電圧 V D F の絶対値と出力電圧 V Q の変化電圧幅は一致する。即ちこのケースは本実施形態の手法の例外のケースとなる。

#### 【0208】

50

例えばこの手法を採用しなかった場合には、温度が  $T_1$  から  $T_2$  に変化した場合に、D/A 変換部 80 の出力電圧  $V_Q$  は、図 16 の D1 に示すように差分電圧  $V_{DF}$  のステップ幅で変化してしまう。

#### 【0209】

これに対して本実施形態の手法では、図 16 の D2 に示すように、この差分電圧  $V_{DF}$  の絶対値よりも小さい電圧幅  $V_A$  で、D/A 変換部 80 の出力電圧  $V_Q$  を変化させる。電圧幅  $V_A$  は例えば期間 T DAC 内での出力電圧  $V_Q$  の電圧変化である。

#### 【0210】

図 16 の D2 に示すように、 $V_A < V_{DF}$  となるように D/A 変換部 80 の出力電圧  $V_Q$  を変化させれば、D1 の場合に比べて、発振回路 150 の発振周波数の変化も非常に小さくなる。従って、図 2C のような周波数ホッピングの発生が抑制され、図 9 で説明した通信エラーの発生も防止できるようになる。

#### 【0211】

具体的には、デジタル信号処理部 50 が、第 1 の温度から第 2 の温度に温度が変化した場合に、第 1 の温度（第 1 の温度検出データ）に対応する第 1 のデータから、第 2 の温度（第 2 の温度検出データ）に対応する第 2 のデータへと、 $k' \times LSB$  単位で変化（ $k' \times LSB$  ずつ変化）する周波数制御データ DDS を出力すればよい。ここで  $k'$  は 1 以上の整数である。なお、 $k'$  は上述した  $k$  と同じ値であってもよいし、異なる値であってもよい。

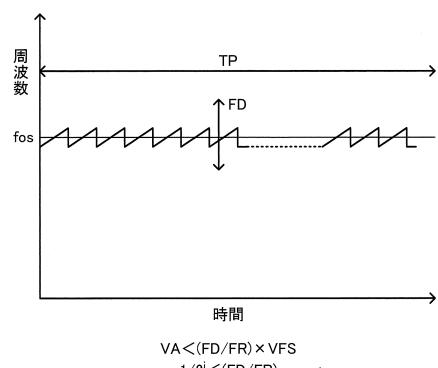

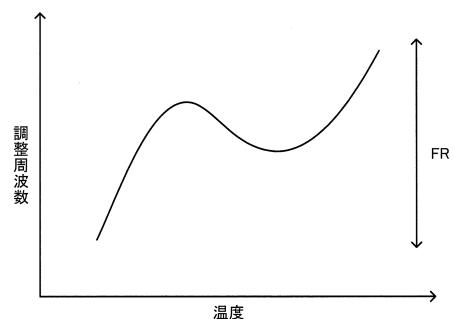

#### 【0212】

図 17A は、本実施形態の手法を周波数領域において説明する図である。例えば発振信号生成回路 140（D/A 変換部 80 及び発振回路 150）による発振周波数の周波数可変範囲を  $F_R$  とする。例えば発振信号生成回路 140 は、温度変化に対して図 17B に示すような周波数調整を行うが、この周波数調整での周波数可変範囲が  $F_R$  になる。即ち、この周波数可変範囲  $F_R$  内に収まる温度変化であれば、発振信号生成回路 140 による周波数調整が可能となる。

#### 【0213】

また所定期間  $T_P$  内における発振周波数の許容周波数ドリフトを  $F_D$  とする。例えば図 9 で説明した通信エラーの発生を防止するためには、所定期間  $T_P$  内での発振周波数の周波数ドリフトを、許容周波数ドリフト  $F_D$  内に収める必要がある。図 2C に示すような周波数ホッピングにより、発振周波数の周波数ドリフトが許容周波数ドリフト  $F_D$  内に収まらなくなると、例えば GPS 衛星信号等の受信信号の復調処理において誤判定が発生して、通信エラーが生じてしまう。

#### 【0214】

また D/A 変換部 80 のフルスケール電圧を  $V_{FS}$  とする。D/A 変換部 80 は、このフルスケール電圧  $V_{FS}$  の範囲で、出力電圧  $V_Q$  を変化させることができる。このフルスケール電圧  $V_{FS}$  は、例えば D/A 変換部 80 に入力される周波数制御データ DDS が、 $0 \sim 2^i$  というようにフルレンジで変化した場合の電圧範囲に相当する。

#### 【0215】

そして図 16 で説明した D/A 変換部 80 の D/A 変換間隔（T DAC）での出力電圧  $V_Q$  の電圧変化の電圧幅  $V_A$  とする。この場合に本実施形態の手法では、図 17A に示すように、下式（3）が成立する。

$$V_A < (F_D / F_R) \times V_{FS} \quad (3)$$

#### 【0216】

具体的には、D/A 変換部 80 の分解能を  $i$  ビットとした場合に、下式（4）が成立する。

$$1 / 2^i < (F_D / F_R) \quad (4)$$

#### 【0217】

上式（3）、（4）に示す本実施形態の手法を採用することで、図 17A に示すように、所定期間  $T_P$ （例えば 20 msec）での、公称発振周波数  $f_{os}$ （例えば 16 MHz）

10

20

30

40

50

程度)に対する発振周波数の周波数ドリフトを、許容周波数ドリフトFD内(例えば数p<sub>p</sub>b程度)に収めることができる。これにより、図2C等で説明した周波数ホッピングを原因とする通信エラー等の発生を抑制できるようになる。

#### 【0218】

例えば上式(3)の右辺である( $FD / FR$ ) × VFSは、周波数可変範囲FRに対する許容周波数ドリフトFDの比率である( $FD / FR$ )を、D/A変換部80のフルスケール電圧VFSに乗算したものである。

#### 【0219】

そしてD/A変換部80のD/A変換間隔(TDAC)での出力電圧VQの変化の電圧幅VAを、この( $FD / FR$ ) × VFSよりも小さくすれば、周波数領域においては、図17Aに示すように、公称発振周波数f<sub>os</sub>に対する周波数ドリフトを、許容周波数ドリフトFD内に収めることができるとなる。即ち、D/A変換部80の出力電圧VQの変化の電圧幅VAを、図16のD2に示すように小さくすることができ、周波数ホッピングの発生を抑制できるようになる。

10

#### 【0220】

例えば上式(3)が成り立たないと、図18に示すように、公称発振周波数f<sub>os</sub>に対する周波数ドリフトが許容周波数ドリフトFD内に収まらなくなる周波数ホッピングが生じ、図9で説明した通信エラー等が発生してしまう。本実施形態では上式(3)が成り立つように、D/A変換部80の出力電圧VQを変化させることで、このような周波数ホッピングの発生が抑制され、通信エラー等を防止できるようになる。

20

#### 【0221】

上記の手法を実現するためのD/A変換部80の構成は種々考えられる。例えば、D/A変換部80は、変調回路と、D/A変換器と、フィルター回路(LPF)とを含んでもよい。デジタル信号処理部50は、D/A変換器の分解能であるnビット(例えば16ビット)よりもビット数が多いi = m + nビットの周波数制御データDDSを出力する。デジタル信号処理部50は、例えば温度補償処理等のデジタル信号処理を実現するために、浮動小数点演算等を行っているため、このようなnビット(例えばn = 16ビット)よりもビット数が多いi = m + nビットの周波数制御データDDSを出力することは容易である。

#### 【0222】

30

そして変調回路は、i = m + nのうちのmビットのデータに基づいて、i = m + nのうちのnビットのデータの変調(PWM変調等)を行い、変調後のnビットのデータDMをD/A変換器に出力する。そしてD/A変換器がデータDMのD/A変換を行い、得られた出力電圧VDAの平滑化処理をフィルター回路が行うことで、i = m + nビット(例えば20ビット)というような高分解能のD/A変換を実現できるようになる。

#### 【0223】

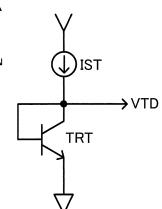

##### 4.2 温度センサー部、発振回路

図19Aに温度センサー部10の第1の構成例を示す。図19Aの温度センサー部10は、電流源ISTと、電流源ISTからの電流がコレクターに供給されるバイポーラートランジスターTRTを有する。バイポーラートランジスターTRTは、そのコレクターとのベースが接続されるダイオード接続となっており、バイポーラートランジスターTRTのコレクターのノードに、温度特性を有する温度検出電圧VTDが出力される。温度検出電圧VTDの温度特性は、バイポーラートランジスターTRTのベース・エミッター間電圧の温度依存性によって生じる。図19Cに示すように温度検出電圧VTDは、負の温度特性(負の勾配を有する1次の温度特性)を有する。

40

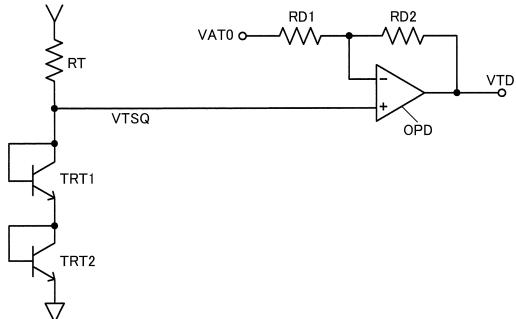

#### 【0224】

図19Bに温度センサー部10の第2の構成例を示す。図19Bでは、図19Aの電流源ISTが抵抗RTにより実現される。そして抵抗RTの一端は電源電圧のノードに接続され、他端はバイポーラートランジスターTRT1のコレクターに接続される。またバイポーラートランジスターTRT1のエミッターは、バイポーラートランジスターTRT2

50

のコレクターに接続される。そしてバイポーラートランジスターTRT1、TRT2は共にダイオード接続されており、バイポーラートランジスターTRT1のコレクターのノードに出力される電圧VTSQは、図19Cのように負の温度特性（負の勾配を有する1次の温度特性）を有している。

#### 【0225】

また図19Bの温度センサー部10では、オペアンプOPDと抵抗RD1、RD2が更に設けられている。オペアンプOPDの非反転入力端子には、電圧VTSQが入力され、反転入力端子には、抵抗RD1の一端及び抵抗RD2の一端が接続される。そして抵抗RD1の他端には基準温度電圧VTA0が供給され、抵抗RD2の他端はオペアンプOPDの出力端子に接続される。

10

#### 【0226】

このようなオペアンプOPD及び抵抗RD1、RD2により、基準温度電圧VAT0を基準として電圧VTSQを正転増幅する増幅アンプが構成される。これにより、温度検出電圧VTD = VAT0 + (1 + RD2 / RD1) × (VTSQ - VAT0) が、温度センサー部10から出力されるようになる。そして基準温度電圧VAT0を調整することにより、基準温度T0の調整が可能になる。

#### 【0227】

図20に発振回路150の構成例を示す。この発振回路150は、電流源IBX、バイポーラートランジスターTRX、抵抗RX、可変容量キャパシターCX1、キャパシターCX2、CX3を有する。

20

#### 【0228】

電流源IBXは、バイポーラートランジスターTRXのコレクターにバイアス電流を供給する。抵抗RXは、バイポーラートランジスターTRXのコレクターとベースの間に設けられる。

#### 【0229】

容量が可変である可変容量キャパシターCX1の一端は、振動子XTALの一端に接続される。具体的には、可変容量キャパシターCX1の一端は、回路装置の第1の振動子用端子（振動子用パッド）を介して振動子XTALの一端に接続される。キャパシターCX2の一端は、振動子XTALの他端に接続される。具体的には、キャパシターCX2の一端は、回路装置の第2の振動子用端子（振動子用パッド）を介して振動子XTALの他端に接続される。キャパシターCX3は、その一端が振動子XTALの一端に接続され、その他端がバイポーラートランジスターTRXのコレクターに接続される。

30

#### 【0230】

バイポーラートランジスターTRXには、振動子XTALの発振により生じたベース・エミッター間電流が流れる。そしてベース・エミッター間電流が増加すると、バイポーラートランジスターTRXのコレクター・エミッター間電流が増加し、電流源IBXから抵抗RXに分岐するバイアス電流が減少するので、コレクター電圧VCXが低下する。一方、バイポーラートランジスターTRXのベース・エミッター間電流が減少すると、コレクター・エミッター間電流が減少し、電流源IBXから抵抗RXに分岐するバイアス電流が増加するので、コレクター電圧VCXが上昇する。このコレクター電圧VCXはキャパシターCX3を介して振動子XTALにフィードバックされる。

40

#### 【0231】

振動子XTALの発振周波数は温度特性（例えば図5の温度特性）を有しており、この温度特性は、D/A変換部80の出力電圧VQ（周波数制御電圧）により補償される。即ち、出力電圧VQは可変容量キャパシターCX1に入力され、出力電圧VQにより可変容量キャパシターCX1の容量値が制御される。可変容量キャパシターCX1の容量値が変化すると、発振ループの共振周波数が変化するので、振動子XTALの温度特性による発振周波数の変動が補償される。可変容量キャパシターCX1は、例えば可変容量ダイオード（バラクター）などにより実現される。

#### 【0232】

50

なお、本実施形態の発振回路 150 は、図 20 の構成に限定されず、種々の変形実施が可能である。例えば図 20 では CX1 を可変容量キャパシターとする場合を例に説明したが、CX2 又は CX3 を、出力電圧 VQ で制御される可変容量キャパシターとしてもよい。また、CX1 ~ CX3 のうち複数を、VQ で制御される可変容量キャパシターとしてもよい。

#### 【0233】

##### 5. 変形例

次に本実施形態の種々の変形例について説明する。図 21 に本実施形態の変形例の回路装置の構成例を示す。図 21 の回路装置は、温度センサー部 10 からの温度検出電圧 VTD の A/D 変換を行い、温度検出データ DTD を出力する A/D 変換部 20 と、温度検出データ DTD に基づいて発振周波数の温度補償処理を行い、発振周波数の周波数制御データ DDS を出力するデジタル信号処理部 50 と、発振信号生成回路 140 を含む。

10

#### 【0234】

そしてデジタル信号処理部 50 は、第 1 の温度から第 2 の温度に温度が変化した場合に、第 1 の温度に対応する第 1 のデータから第 2 の温度に対応する第 2 のデータへと、 $k' \times LSB$  単位で変化する周波数制御データ DDS を出力する。そして発振信号生成回路 140 は、デジタル信号処理部 50 からの周波数制御データ DDS と振動子 XTEL を用いて、周波数制御データ DDS により設定される発振周波数の発振信号 SSC を生成する。

#### 【0235】

即ち図 21 では、図 4、図 19 とは異なり、発振信号生成回路 140 に D/A 変換部 80 が設けられていない。そして発振信号生成回路 140 により生成される発振信号 SSC の発振周波数が、デジタル信号処理部 50 からの周波数制御データ DDS に基づいて、直接に制御される。即ち D/A 変換部を介さずに発振信号 SSC の発振周波数が制御される。

20

#### 【0236】

例えば図 21 では、発振信号生成回路 140 が、可変容量回路 142 と発振回路 150 を有する。この発振信号生成回路 140 には図 4、図 19 の D/A 変換部 80 は設けられていない。そして図 20 の可変容量キャパシター CX1 の代わりに、この可変容量回路 142 が設けられ、可変容量回路 142 の一端が振動子 XTEL の一端に接続される。

30

#### 【0237】

この可変容量回路 142 は、デジタル信号処理部 50 からの周波数制御データ DDS に基づいて、その容量値が制御される。例えば可変容量回路 142 は、複数のキャパシター（キャパシターアレイ）と、周波数制御データ DDS に基づき各スイッチ素子のオン、オフが制御される複数のスイッチ素子（スイッチアレイ）を有する。これらの複数のスイッチ素子の各スイッチ素子は、複数のキャパシターの各キャパシターに電気的に接続される。そして、これらの複数のスイッチ素子がオン又はオフされることで、複数のキャパシターのうち、振動子 XTEL の一端に、その一端が接続されるキャパシターの個数が変化する。これにより、可変容量回路 142 の容量値が制御されて、振動子 XTEL の一端の容量値が変化する。従って、周波数制御データ DDS により、可変容量回路 142 の容量値が直接に制御されて、発振信号 SSC の発振周波数を制御できるようになる。

40

#### 【0238】

このように、 $k' \times LSB$  単位で周波数制御データ DDS を変化させる本実施形態の手法は、図 21 のように発振信号生成回路 140 に D/A 変換部 80 を設けない構成においても実現可能である。そして、 $k' \times LSB$  単位で周波数制御データ DDS を変化させることで、図 16 ~ 図 17B で説明した本実施形態の手法と同様の効果を実現することが可能となり、図 2C の周波数ホッピングの発生を抑制して、周波数ホッピングを原因とする通信エラー等の発生を防止できるようになる。なお図 21 の構成においても、発振信号 SSC をダイレクト・デジタル・シンセサイザー方式で生成することが可能である。

#### 【0239】

##### 6. 発振器、電子機器、移動体

10

20

30

40

50

図22Aに、本実施形態の回路装置500を含む発振器400の構成例を示す。図22Aに示すように、発振器400は、振動子420と回路装置500を含む。振動子420と回路装置500は、発振器400のパッケージ410内に実装される。そして振動子420の端子と、回路装置500（IC）の端子（パッド）は、パッケージ410の内部配線により電気的に接続される。

#### 【0240】

図22Bに、本実施形態の回路装置500を含む電子機器の構成例を示す。この電子機器は、本実施形態の回路装置500、水晶振動子等の振動子420、アンテナANT、通信部510、処理部520を含む。また操作部530、表示部540、記憶部550を含むことができる。振動子420と回路装置500により発振器400が構成される。なお電子機器は図22Bの構成に限定されず、これらの一部の構成要素を省略したり、他の構成要素を追加するなどの種々の変形実施が可能である。10

#### 【0241】

図22Bの電子機器としては、例えばGPS内蔵時計、生体情報測定機器（脈波計、歩数計等）又は頭部装着型表示装置等のウェアラブル機器や、スマートフォン、携帯電話機、携帯型ゲーム装置、ノートPC又はタブレットPC等の携帯情報端末（移動端末）や、コンテンツを配信するコンテンツ提供端末や、デジタルカメラ又はビデオカメラ等の映像機器や、或いは基地局又はルーター等のネットワーク関連機器などの種々の機器を想定できる。20

#### 【0242】

通信部510（無線回路）は、アンテナANTを介して外部からデータを受信したり、外部にデータを送信する処理を行う。処理部520は、電子機器の制御処理や、通信部510を介して送受信されるデータの種々のデジタル処理などを行う。この処理部520の機能は、例えばマイクロコンピューターなどのプロセッサーにより実現できる。20

#### 【0243】

操作部530は、ユーザーが入力操作を行うためのものであり、操作ボタンやタッチパネルディスプレイなどにより実現できる。表示部540は、各種の情報を表示するものであり、液晶や有機ELなどのディスプレイにより実現できる。なお操作部530としてタッチパネルディスプレイを用いる場合には、このタッチパネルディスプレイが操作部530及び表示部540の機能を兼ねることになる。記憶部550は、データを記憶するものであり、その機能はRAMやROMなどの半導体メモリーやHDD（ハードディスクドライブ）などにより実現できる。30

#### 【0244】

図22Cに、本実施形態の回路装置を含む移動体の例を示す。本実施形態の回路装置（発振器）は、例えば、車、飛行機、バイク、自転車、或いは船舶等の種々の移動体に組み込むことができる。移動体は、例えばエンジンやモーター等の駆動機構、ハンドルや舵等の操舵機構、各種の電子機器（車載機器）を備えて、地上や空や海上を移動する機器・装置である。図22Cは移動体の具体例としての自動車206を概略的に示している。自動車206には、本実施形態の回路装置と振動子を有する発振器（不図示）が組み込まれる。制御装置208は、この発振器により生成されたクロック信号により動作する。制御装置208は、例えば車体207の姿勢に応じてサスペンションの硬軟を制御したり、個々の車輪209のブレーキを制御する。例えば制御装置208により、自動車206の自動運転を実現してもよい。なお本実施形態の回路装置や発振器が組み込まれる機器は、このような制御装置208には限定されず、自動車206等の移動体に設けられる種々の機器（車載機器）に組み込むことが可能である。40

#### 【0245】

なお、上記のように本実施形態について詳細に説明したが、本発明の新規事項および効果から実体的に逸脱しない多くの変形が可能であることは当業者には容易に理解できるであろう。従って、このような変形例はすべて本発明の範囲に含まれるものとする。例えば、明細書又は図面において、少なくとも一度、より広義または同義な異なる用語と共に記50

載された用語は、明細書又は図面のいかなる箇所においても、その異なる用語に置き換えることができる。また本実施形態及び変形例の全ての組み合わせも、本発明の範囲に含まれる。また回路装置、発振器、電子機器、移動体の構成・動作や、A / D 変換手法、D / A 変換手法、周波数制御データの処理手法、処理部の周波数制御データの出力手法、D / A 変換部の電圧の出力手法、振動子の周波数制御手法等も本実施形態で説明したものに限定されず、種々の変形実施が可能である。

#### 【符号の説明】

##### 【0 2 4 6】

A N T ... アンテナ、C ... キャパシター、D D S ... 周波数制御データ、

D T D ... 温度検出データ、F D ... 許容周波数ドリフト、F R ... 周波数可変範囲、

I S ... 電流源、S 1 ~ S 4 ... スイッチ素子、T D A C ... 期間、T P ... 所定期間、

T r ... トランジスター、V F S ... フルスケール電圧、X T A L ... 振動子、

1 0 ... 温度センサー部、2 0 ... A / D 変換部、2 2 ... ロジック部、2 3 ... 処理部、

2 4 ... レジスター部、2 5 ... アナログ部、2 6 ... D / A 変換器、2 7 ... 比較部、

2 8 ... 温度センサー部用アンプ、5 0 ... デジタル信号処理部、8 0 ... D / A 変換部、

1 4 0 ... 発振信号生成回路、1 4 2 ... 可変容量回路、1 5 0 ... 発振回路、

1 6 0 ... バッファーハウス回路、2 0 6 ... 自動車、2 0 7 ... 車体、2 0 8 ... 制御装置、

2 0 9 ... 車輪、4 0 0 ... 発振器、4 1 0 ... パッケージ、4 2 0 ... 振動子、

5 0 0 ... 回路装置、5 1 0 ... 通信部、5 2 0 ... 処理部、5 3 0 ... 操作部、

5 4 0 ... 表示部、5 5 0 ... 記憶部

10

20

【図 1】

【図 2】

【図3】

【図4】

【図5】

【図6】

【図 7】

図7A

図7B

図7C

【図 8】

【図 9】

【図 10】

【図11】

図11A

図11B

【図12】

【図14】

図14A

図14B

| 判定結果     |                    |                                          |

|----------|--------------------|------------------------------------------|

| D[14:13] | セッタする値             | DB[14:0]                                 |

| "10"     | "10"→C1<br>"11"→C2 | 100 0000 0000 0000<br>110 0000 0000 0000 |

| up       | up                 | up                                       |

| down     | up                 | up                                       |

| "10"     | "01"               | D[14:3]=“11”に決定→C3                       |

| up       | up                 | up                                       |

| down     | up                 | up                                       |

| "01"     | "01"               | D[12:1]=“01”に決定→C7                       |

| up       | up                 | up                                       |

| down     | up                 | up                                       |

| "00"     | "00"               | D[10:9]=“11”に決定                          |

| up       | up                 | up                                       |

| down     | up                 | up                                       |

| "00"     | "00"               | D[8:7]=“11”且つ繰り下がりに決定                    |

| up       | up                 | up                                       |

| down     | up                 | up                                       |

| "00"     | "00"               | D[6:5]=“100(繰り上り)"に決定                    |

| up       | up                 | up                                       |

| down     | up                 | up                                       |

| "100"    | "100"              | D[4:3]=“10”に決定                           |

| up       | up                 | up                                       |

| down     | up                 | up                                       |

| "100"    | "100"              | D[2:1]=“00”に決定                           |

| up       | up                 | up                                       |

| down     | up                 | up                                       |

| "000"    | "000"              | 通常モードと同様の判定                              |

| up       | up                 | up                                       |

| down     | up                 | up                                       |

図14C

| 判定結果    |                    |                                          |

|---------|--------------------|------------------------------------------|

| D[14:0] | セッタする値             | DB[14:0]                                 |

| "10"    | "10"→C1<br>"11"→C2 | 100 0000 0000 0000<br>110 0000 0000 0000 |

| up      | up                 | up                                       |

| down    | up                 | up                                       |

| "10"    | "01"               | D[12:1]=“11”に決定→C3                       |

| up      | up                 | up                                       |

| down    | up                 | up                                       |

| "01"    | "01"               | D[10:9]=“01”に決定→C7                       |

| up      | up                 | up                                       |

| down    | up                 | up                                       |

| "00"    | "00"               | D[8:7]=“11”且つ繰り下がりに決定                    |

| up      | up                 | up                                       |

| down    | up                 | up                                       |

| "00"    | "00"               | D[6:5]=“100(繰り上り)"に決定                    |

| up      | up                 | up                                       |

| down    | up                 | up                                       |

| "100"   | "100"              | D[4:3]=“10”に決定                           |

| up      | up                 | up                                       |

| down    | up                 | up                                       |

| "100"   | "100"              | D[2:1]=“00”に決定                           |

| up      | up                 | up                                       |

| down    | up                 | up                                       |

| "000"   | "000"              | 通常モードと同様の判定                              |

| up      | up                 | up                                       |

| down    | up                 | up                                       |

【図13】

(39)

JP 6736871 B2 2020.8.5

【図15】

| 判定対象ビット  | セッタする値                           | DB[14:0]                                                       | DB[14:0]                                                       | 判定結果                  |

|----------|----------------------------------|----------------------------------------------------------------|----------------------------------------------------------------|-----------------------|

| D[14:13] | "10"→C1<br>"11"→C2               | 100 0000 0000 0000<br>110 0000 0000 0000                       | 100 0000 0000 0000<br>110 0000 0000 0000                       | D[14:3]=“11”に決定→C3    |

| D[12:11] | "10"→C4<br>"01"→C5<br>"00"→C6    | 110 0000 0000 0000<br>110 0000 0000 0000<br>110 0000 0000 0000 | 110 1000 0000 0000<br>110 1100 0000 0000<br>110 1110 0000 0000 | D[12:1]=“01”に決定→C7    |

| D[10:9]  | "10"→C7<br>"11"→C8               | 110 1000 0000 0000<br>110 1100 0000 0000                       | 110 1000 0000 0000<br>110 1100 0000 0000                       | D[10:9]=“11”に決定       |

| D[8:7]   | "10"→C9<br>"01"→C10<br>"00"→C11  | 110 1110 0000 0000<br>110 1110 0000 0000<br>110 1110 0000 0000 | 110 1110 0000 0000<br>110 1110 0000 0000<br>110 1110 0000 0000 | D[8:7]=“11”且つ繰り下がりに決定 |

| D[6:5]   | "10"→C12<br>"11"→C13             | 110 1110 0000 0000<br>110 1110 0000 0000                       | 110 1110 0000 0000<br>110 1110 0000 0000                       | D[6:5]=“100(繰り上り)"に決定 |

| D[4:3]   | "10"→C14<br>"11"→C15<br>"00"→C16 | 110 1110 0000 0000<br>110 1110 0000 0000<br>110 1110 0000 0000 | 110 1110 0000 0000<br>110 1110 0000 0000<br>110 1110 0000 0000 | D[4:3]=“10”に決定        |

| D[2:1]   | "10"→C17<br>"01"→C18<br>"00"→C19 | 110 1110 0000 0000<br>110 1110 0000 0000<br>110 1110 0000 0000 | 110 1110 0000 0000<br>110 1110 0000 0000<br>110 1110 0000 0000 | D[2:1]=“00”に決定        |

| D[0]     | 現状値<br>1 LSB加算                   | 110 1110 0001 0000<br>110 1110 0001 0001                       | 110 1110 0001 0000<br>110 1110 0001 0001                       | 通常モードと同様の判定           |

時間t

【図16】

【図17】

図17A

図17B

【図18】

【図19】

図19A

図19B

図19C

【図20】

【図21】

【図22】

図22A

図22B

図22C

---

フロントページの続き

(56)参考文献 特開2001-292064(JP,A)

特開2010-063055(JP,A)

特開2009-302716(JP,A)

特開2013-211654(JP,A)

実開平04-019031(JP,U)

国際公開第2008/032695(WO,A1)

特開平10-209870(JP,A)

特開平11-154866(JP,A)

(58)調査した分野(Int.Cl., DB名)

H03M 1/00 - 1/88

H03B 5/32