(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2012-504820

(P2012-504820A)

(43) 公表日 平成24年2月23日(2012.2.23)

(51) Int.Cl.

G06F 12/16

(2006.01)

F 1

G 06 F 12/16

A

テーマコード(参考)

5 B 0 1 8

審査請求 未請求 予備審査請求 未請求 (全 23 頁)

(21) 出願番号 特願2011-530193 (P2011-530193)

(86) (22) 出願日 平成21年9月30日 (2009. 9. 30)

(85) 翻訳文提出日 平成23年5月27日 (2011.5. 27)

(86) 國際出願番号 PCT/US2009/059069

(87) 國際公開番号 WO2010/039859

(87) 國際公開日 平成22年4月8日 (2010. 4. 8)

(31) 優先権主張番号 PCT/US2009/049333

(32) 優先日 平成21年6月30日 (2009. 6. 30)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 61/194, 751

(32) 優先日 平成20年9月30日 (2008. 9. 30)

(33) 優先権主張国 米国(US)

(71) 出願人 508243639

エルエスアイ コーポレーション

アメリカ合衆国 95035 カリフォルニア, ミルピタス, パーパー レーン 1

621

(74) 代理人 100094112

弁理士 岡部 譲

(74) 代理人 100064447

弁理士 岡部 正夫

(74) 代理人 100104352

弁理士 朝日 伸光

(74) 代理人 100128657

弁理士 三山 勝巳

(74) 代理人 100160967

弁理士 ▲濱▼口 岳久

最終頁に続く

(54) 【発明の名称】性能要因調整に基づくメモリ・デバイスの軟データ生成の方法および装置

## (57) 【要約】

性能要因調整に基づくメモリ・デバイスの軟データ生成の方法および装置を提供する。少なくとも1つの軟データ値が、少なくとも1つの読み取り値を入手することと、入手された少なくとも1つの読み取り値とメモリ・デバイスの1つまたは複数の性能要因に基づく調整とに基づいて軟データ値を生成することによって、メモリ・デバイスについて生成される。読み取り値は、たとえば、データ・ビット、電圧レベル、電流レベル、または抵抗レベルを含むことができる。読み取り値は、軟データまたは硬データである。可能な性能要因は、耐久性、読み取りサイクルの個数、保持時間、温度、プロセス・コーナー、セル間干渉影響、メモリ・アレイ内の位置、およびアグレッサ・セルのパターンを含む。1つまたは複数のパターン依存性能要因および/または位置固有性能要因を考慮することもできる。生成される軟データ値は、1つまたは複数の対数尤度比を生成するのに使用される軟読み取り値とすることができる、あるいは、対数尤度比自体とすることができる。

FIG. 1

Prior Art

**【特許請求の範囲】****【請求項 1】**

メモリ・デバイスの少なくとも 1 つの軟データ値を生成する方法であって、少なくとも 1 つの読み取り値を入手するステップと、前記入手された少なくとも 1 つの読み取り値と前記メモリ・デバイスの 1 つまたは複数の性能要因に基づく調整とに基づいて前記軟データ値を生成するステップとを含む方法。

**【請求項 2】**

前記調整は、前記入手された少なくとも 1 つの読み取り値に基づく公称値を調整し、前記調整は、前記メモリ・デバイスの 1 つまたは複数の性能要因に基づくオフセット値を含む、請求項 1 に記載の方法。10

**【請求項 3】**

前記性能要因は、耐久性、プログラム / 消去サイクルの個数、読み取りサイクルの個数、保持時間、温度、温度変化、プロセス・コーナー、セル間干渉影響、メモリ・アレイ内の位置、前記読み取り値がそこから入手されるワード線の位置、前記読み取り値がそこから入手されるページの位置、前記読み取り値がそこから読み取られるワード線内のページの位置、およびアグレッサ・セルのパターンのうちの 1 つまたは複数を含む、請求項 2 に記載の方法。

**【請求項 4】**

前記調整は、セル内の異なるビット、ワード線内の異なるページ、異なるビット線、および異なる硬読み取りデータ値のうちの 1 つまたは複数に関する別々の性能要因に基づく、請求項 2 に記載の方法。20

**【請求項 5】**

前記読み取り値は、データ・ビット、電圧レベル、電流レベル、および抵抗レベルのうちの 1 つまたは複数を含む、請求項 1 に記載の方法。

**【請求項 6】**

前記読み取り値は、軟データおよび硬データのうちの 1 つまたは複数を含む、請求項 1 に記載の方法。

**【請求項 7】**

前記軟データ値は、(i) 1 つまたは複数の対数尤度比を生成するのに使用される軟読み取り値および(ii) 1 つまたは複数の対数尤度比のうちの 1 つまたは複数を含む、請求項 1 に記載の方法。30

**【請求項 8】**

前記軟データ値は、前記少なくとも 1 つの読み取り値の信頼性を示す、請求項 1 に記載の方法。

**【請求項 9】**

前記ステップのうちの 1 つまたは複数は、コントローラ、読み取りチャネル、信号処理ユニット、およびデコーダのうちの 1 つまたは複数によって実施される、請求項 1 に記載の方法。

**【請求項 10】**

前記調整は、前もって入手され、メモリに格納される、請求項 1 に記載の方法。40

**【請求項 11】**

前記調整を測定するステップをさらに含む、請求項 1 に記載の方法。

**【請求項 12】**

前記性能要因は、1 つまたは複数のパターン依存性能要因を含む、請求項 1 に記載の方法。

**【請求項 13】**

前記性能要因は、1 つまたは複数の位置固有性能要因を含む、請求項 1 に記載の方法。

**【請求項 14】**

前記メモリ・デバイスは、フラッシュ・メモリ・デバイスである、請求項 1 に記載の方法。50

**【請求項 15】**

前記調整は、前記讀取値の信頼性値を減らす、請求項1に記載の方法。

**【請求項 16】**

前記調整は、前記公称値の信頼性値を前記オフセット値と等しい量だけ減らす、請求項2に記載の方法。

**【請求項 17】**

メモリ・デバイスの少なくとも1つの軟データ値を生成するシステムであって、

メモリと、

前記メモリに結合され、

少なくとも1つの讀取値を入手し、

10

前記入手された少なくとも1つの讀取値と前記メモリ・デバイスの1つまたは複数の性能要因に基づく調整とに基づいて前記軟データ値を生成する

ようすに動作可能な少なくとも1つのプロセッサと

を含むシステム。

**【請求項 18】**

前記調整は、前記入手された少なくとも1つの讀取値に基づく公称値を調整し、前記調整は、前記メモリ・デバイスの1つまたは複数の性能要因に基づくオフセット値を含む、請求項17に記載のシステム。

**【請求項 19】**

前記性能要因は、耐久性、プログラム／消去サイクルの個数、讀取サイクルの個数、保持時間、温度、温度変化、プロセス・コーナー、セル間干渉影響、メモリ・アレイ内の位置、前記讀取値がそこから入手されるワード線の位置、前記讀取値がそこから入手されるページの位置、前記讀取値がそこから読み取られるワード線内のページの位置、およびアグレッサ・セルのパターンのうちの1つまたは複数を含む、請求項18に記載のシステム。

20

**【請求項 20】**

前記軟データ値は、(i)1つまたは複数の対数尤度比を生成するのに使用される軟讀取値および(ii)1つまたは複数の対数尤度比のうちの1つまたは複数を含む、請求項17に記載のシステム。

30

**【発明の詳細な説明】****【技術分野】****【0001】**

関連出願の相互参照

本願は、それぞれ参照によって本明細書に組み込まれている、2008年9月30日に出願した米国仮出願第61/194,751号および2009年6月30日に出願した国際出願第PCT/US09/49333号、名称「Methods and Apparatus for Soft Demapping and Inter-cell Interference Mitigation in Flash Memories」の優先権を主張するものである。

40

**【0002】**

本願は、それぞれ本願と同時に出願され、参照によって本明細書に組み込まれている、国際出願、名称「Methods and Apparatus for Soft Data Generation for Memory Devices」、国際出願、名称「Methods and Apparatus for Soft Data Generation for Memory Devices Using Reference Cells」、および国際出願、名称「Methods and Apparatus for Soft Data Generation for Memory Devices Using Decoder Performance Feedback」に関連する。

50

**【0003】**

本発明は、全般的にはフラッシュ・メモリ・デバイスに関し、より具体的には、検出および復号性能を改善する性能要因調整に基づく軟データ生成の改善された技法に関する。

#### 【背景技術】

##### 【0004】

フラッシュ・メモリ・デバイスなどの複数のメモリ・デバイスは、データを格納するのにアナログ・メモリ・セルを使用する。各メモリ・セルは、電荷または電圧など、ストレージ・バリュー (storage value) とも称するアナログ値を格納する。ストレージ・バリューは、セルに格納された情報を表す。たとえば、フラッシュ・メモリ・デバイスでは、各アナログ・メモリ・セルは、通常はある電圧を格納する。各セルの可能なアナログ値の範囲は、通常はしきい領域に分割され、各領域は、1つまたは複数のデータ・ビット値に対応する。データは、所望の1つまたは複数のビットに対応する公称アナログ値を書き込むことによってアナログ・メモリ・セルに書き込まれる。

10

##### 【0005】

たとえば、シングルレベル・セル (SLC) フラッシュ・メモリ・デバイスは、メモリ・セルあたり1ビット (すなわち、2つの可能なメモリ状態) を格納する。その一方で、マルチレベル・セル (MLC) フラッシュ・メモリ・デバイスは、メモリ・セルあたり複数のビットを格納する (すなわち、各セルが、4つ以上のプログラム可能な状態を有する)。MLC フラッシュ・メモリ・デバイスのより詳細な議論については、たとえば、参照によって本明細書に組み込まれている、2009年3月11日に出願した国際出願第PCT/US09/36810号、名称「Methods and Apparatus for Storing Data in a Multi-Level Cell Flash Memory Device with Cross-Page Sectors, Multi-Page Coding And Per-Page Coding」を参照されたい。

20

##### 【0006】

メモリ・セルに格納されたアナログ値は、しばしば、ひずむ。ひずみは、通常、たとえばバック・パターン依存 (BPD)、雑音、およびセル間干渉 (ICI) に起因する。フラッシュ・メモリ・デバイスでのひずみのより詳細な議論については、たとえば、それぞれ参照によって本明細書に組み込まれている、J. D. Lee他、「Effects of Floating-Gate Interference on NAND Flash Memory Cell Operation」、IEEE Electron Device Letters、264~266頁(2002年5月)、またはKi-Tae Park他、「A Zeroing Cell-to-Cell Interference Page Architecture With Temporary LSB Storing and Parallel MSB Program Scheme for MLC NAND Flash Memories」、IEEE J. of Solid State Circuits、Vol. 43、No. 4、919~928頁(2008年4月)を参照されたい。

30

##### 【0007】

複数の技法が、ICIおよび他の外乱の影響を軽減するために提案されまたは提唱されてきた。たとえば、Ki-Tae Park他は、ICIを軽減する、偶数/奇数プログラミング (even/odd programming)、ボトム・アップ・プログラミング (bottom up programming)、およびマルチステージ・プログラミング (multi-stage programming) などの既存のプログラミング技法を説明している。さらに、2009年6月30日に出願された国際出願第PCT/US09/49333号、名称「Methods and Apparatus for Soft Demapping and Inter-cell Interference Mitigation in Flash Memories」は、フラッシュ・メモリでの軟デマッピングおよび外乱軽減の方法および装置を開示している。

40

#### 【先行技術文献】

50

## 【特許文献】

## 【0008】

【特許文献1】米国仮出願第61/194,751号

【特許文献2】国際出願第PCT/US09/49333号

【特許文献3】国際出願、名称「Methods and Apparatus for Soft Data Generation for Memory Devices」

【特許文献4】国際出願、名称「Methods and Apparatus for Soft Data Generation for Memory Devices Using Reference Cells」

【特許文献5】国際出願、名称「Methods and Apparatus for Soft Data Generation for Memory Devices Using Decoder Performance Feedback」

【特許文献6】国際出願第PCT/US09/36810号

【特許文献7】米国特許第6,522,580号

【特許文献8】国際出願第PCT/US09/49326号

【特許文献9】国際出願第PCT/US09/49327号

【特許文献10】国際出願第PCT/US09/49328号

【特許文献11】国際出願、名称「Methods and Apparatus for Soft Data Generation in Flash Memories」

10

20

30

40

50

## 【非特許文献】

## 【0009】

【非特許文献1】J. D. Lee他、「Effects of Floating-Gate Interference on NAND Flash Memory Cell Operation」、IEEE Electron Device Letters、264~266頁(2002年5月)

【非特許文献2】Ki-Tae Park他、「A Zeroing Cell-to-Cell Interference Page Architecture With Temporary LSB Storing and Parallel MSB Program Scheme for MLC NAND Flash Memories」、IEEE J. of Solid State Circuits、Vol. 43、No. 4、919~928頁(2008年4月)

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0010】

これらの既存の方法は、フラッシュ・メモリの復号性能を改善するのを助けたが、複数の制約をこうむり、この制約は、克服されたならば、フラッシュ・メモリの信頼性をさらに改善することができる。たとえば、現在のフラッシュ・メモリは、通常、復号のためにフラッシュ制御システムに硬データ(hard data)のみを供給する。しかし、軟データが、復号プロセスの誤り率性能を改善できることが周知である。したがって、フラッシュ・メモリからの硬データを使用して軟データを推定するかその質を高め、これによって復号性能を改善する、軟データ生成技法の必要が存在する。

## 【課題を解決するための手段】

## 【0011】

一般に、性能要因調整に基づくメモリ・デバイスの軟データ生成の方法および装置を提供する。本発明の一態様によれば、メモリ・デバイスの少なくとも1つの軟データ値が、少なくとも1つの読み取り値を入手することと、入手された少なくとも1つの読み取り値とメモリ・デバイスの1つまたは複数の性能要因に基づく調整とに基づいて軟データ値を生成することによって生成される。読み取り値は、軟データおよび/または硬データとすることがで

き、データ・ビット、電圧レベル、電流レベル、または抵抗レベル（あるいはその組合せ）を含むことができる。生成される軟データ値は、たとえば、（*i*）1つまたは複数の対数尤度比を生成するのに使用される軟読取値または（*ii*）1つまたは複数の対数尤度比を含むことができる。

【0012】

1つの例示的実施形態では、調整は、入手された少なくとも1つの読取値に基づく公称値を調整し、調整は、メモリ・デバイスの1つまたは複数の性能要因に基づくオフセット値を含む。

【0013】

性能要因は、たとえば、耐久性、プログラム／消去サイクルの個数、読取サイクルの個数、保持時間、温度、温度変化、プロセス・コーナー、セル間干渉影響、メモリ・アレイ内の位置、読取値がそこから入手されるワード線の位置、読取値がそこから入手されるページの位置、読取値がそこから読み取られるワード線内のページの位置、およびアグレッサ・セルのパターンのうちの1つまたは複数を含むことができる。1つまたは複数の性能要因を、セル内の1つまたは複数の異なるビット、ワード線内の異なるページ、異なるビット線、または異なる硬読取データ値について変更することができる。

【0014】

本発明ならびに本発明のさらなる特徴および利益のより完全な理解は、次の詳細な説明および図面を参照することによって得られる。

【図面の簡単な説明】

【0015】

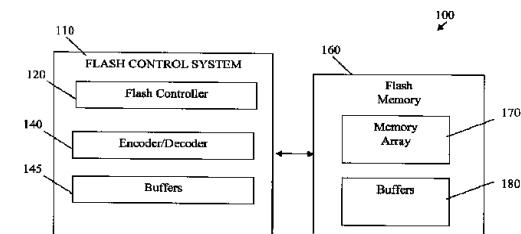

【図1】従来のフラッシュ・メモリ・システムを示す概略ブロック図である。

【図2】図1の例示的なフラッシュ・メモリの例示的なしきい電圧分布を示す図である。

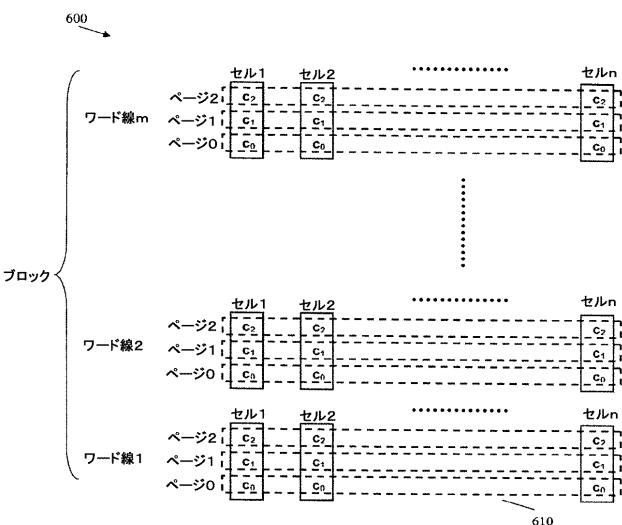

【図3】マルチレベル・セル（MLC）フラッシュ・メモリ・デバイス内の例示的なフラッシュ・セル・アレイのアーキテクチャを示す図である。

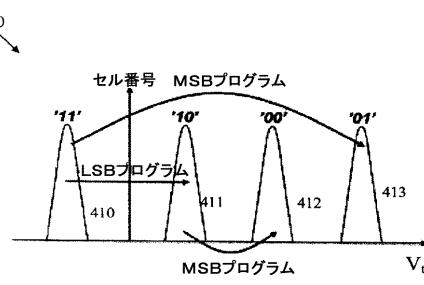

【図4】図2の電圧割当て方式の例示的な2ステージMLCプログラミング方式を示す図である。

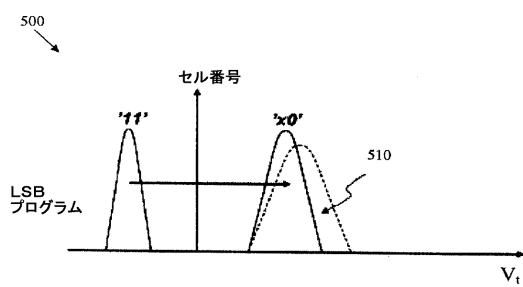

【図5A】隣接セルに加えられるICIを減らす代替MLCプログラミング方式を集合的に示す図である。

【図5B】隣接セルに加えられるICIを減らす代替MLCプログラミング方式を集合的に示す図である。

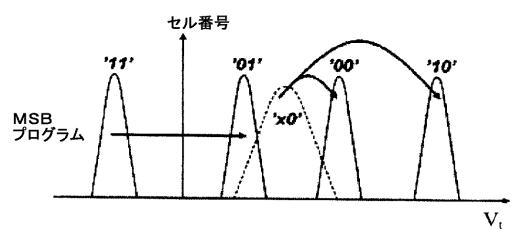

【図6】マルチレベル・セル（MLC）フラッシュ・メモリ・デバイス内の例示的なフラッシュ・セル・アレイをさらに詳細に示す図である。

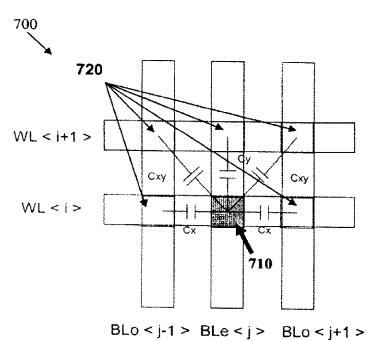

【図7】セル間干渉、バック・パターン依存、雑音、および他のひずみなどの複数の例示的なアグレッサ・セルに起因するターゲット・セルについて存在する外乱を示す図である。

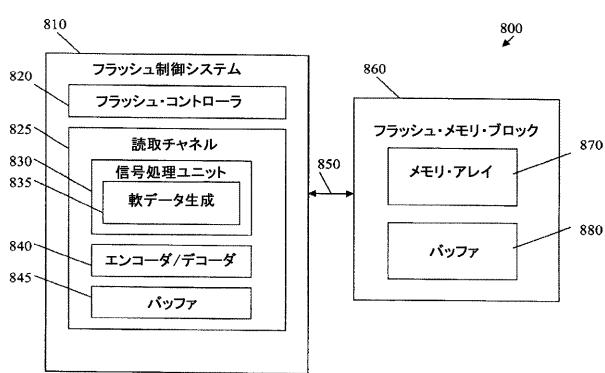

【図8】本発明によるコントローラ・ベースの軟データ生成技法を組み込まれた例示的なフラッシュ・メモリ・システムを示す概略ブロック図である。

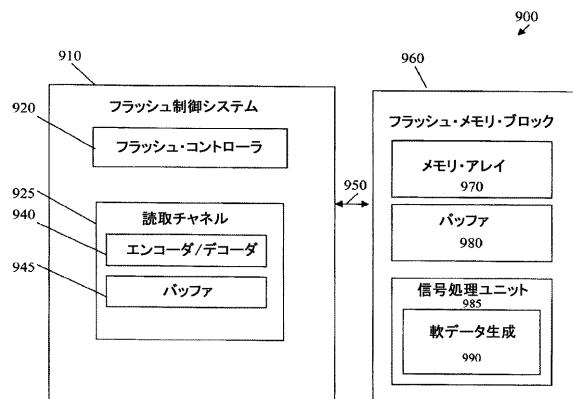

【図9】本発明の代替実施形態によるメモリ・ベースの軟データ生成技法を組み込まれた例示的なフラッシュ・メモリ・システムを示す概略ブロック図である。

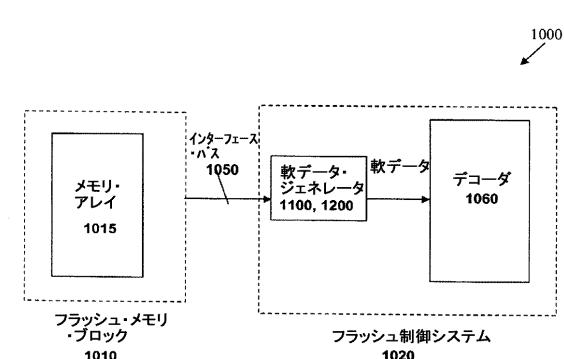

【図10】本発明による軟データ生成を用いる例示的なフラッシュ・メモリ・システムを示す図である。

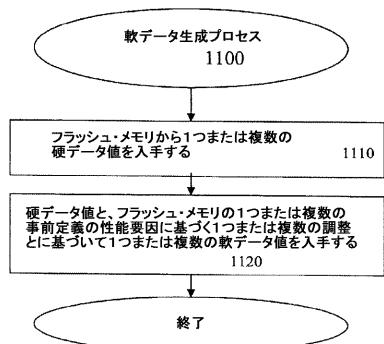

【図11】本発明の特徴を組み込まれた例示的な軟データ生成プロセスを説明する流れ図である。

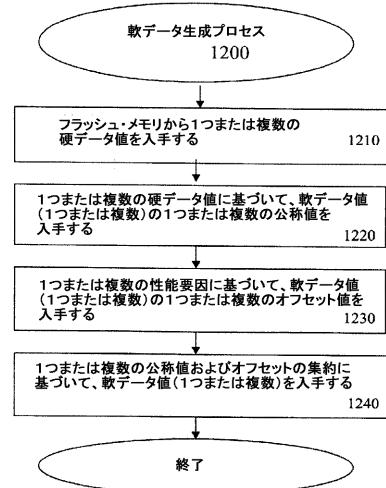

【図12】本発明の特徴を組み込まれた軟データ生成プロセスの例示的な代替実施態様を説明する流れ図である。

【図13】本発明の特徴を組み込まれた例示的な硬データ・軟データ・マッピング・データベースからのサンプル・テーブルを示す図である。

【発明を実施するための形態】

【0016】

10

20

30

40

50

本発明のさまざまな態様は、シングルレベル・セルまたはマルチレベル・セル（MLC）NANDフラッシュ・メモリ・デバイスなどのメモリ・デバイスでの改善された復号のための軟データ生成技法を対象とする。本明細書で使用されるときに、マルチレベル・セル・フラッシュ・メモリは、各メモリ・セルが複数のビットを格納するメモリを含む。通常、1つのフラッシュ・セルに格納される複数のビットは、異なるページに属する。本発明は、本明細書ではアナログ値を電圧として格納するメモリ・セルを使用して例示されるが、当業者に明白であるように、本発明を、格納されたデータを表すのに電圧、電流または抵抗を使用することなど、メモリ・デバイスの任意のストレージ機構と共に使用することができる。

【0017】

10

図1は、従来のフラッシュ・メモリ・システム100の概略ブロック図である。図1に示されているように、例示的なフラッシュ・メモリ・システム100は、フラッシュ制御システム110およびフラッシュ・メモリ・ブロック160を含む。例示的なフラッシュ制御システム110は、フラッシュ・コントローラ120、エンコーダ/デコーダ・ブロック140、および1つまたは複数のバッファ145を含む。代替実施形態では、エンコーダ/デコーダ・ブロック140およびいくつかのバッファ145を、フラッシュ・コントローラ120の内部で実施することができる。エンコーダ/デコーダ・ブロック140およびバッファ145を、たとえば、周知の市販の技法および/または製品を使用して実施することができる。

【0018】

20

例示的なフラッシュ・メモリ・ブロック160は、それぞれ周知の市販の技法および/または製品を使用して実施できる、メモリ・アレイ170および1つまたは複数のバッファ180を含む。メモリ・アレイ170は、NANDフラッシュ・メモリ、相変化メモリ（PCM）、MRAMメモリ、NORフラッシュ・メモリ、または別の不揮発性フラッシュ・メモリなど、シングルレベル・セルまたはマルチレベル・セルのフラッシュ・メモリとして実施することができる。本発明を、主にマルチレベル・セルNANDフラッシュ・メモリの文脈で例示するが、当業者に明白であるように、本発明を、シングルレベル・セル・フラッシュ・メモリおよび他の不揮発性メモリに適用することができる。

【0019】

マルチレベル・セル・フラッシュ・メモリ

30

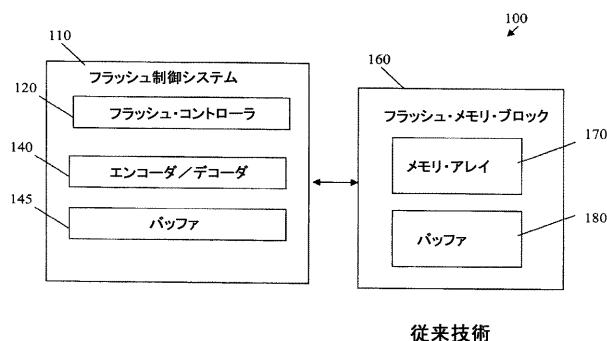

マルチレベル・セルNANDフラッシュ・メモリでは、しきい値検出器が、通常、特定のセルに関連する電圧値を事前定義のメモリ状態に変換するのに使用される。図2に、参照によって本明細書に組み込まれている米国特許第6,522,580号の教示に基づく、図1の例示的なマルチレベル・セル・フラッシュ・メモリ170の例示的なしきい電圧分布を示す。一般に、セルのしきい電圧は、そのセルがある量の電流を導通するようにするためにそのセルに印加される必要がある電圧である。しきい電圧は、セルに格納されるデータに関する測定値である。

【0020】

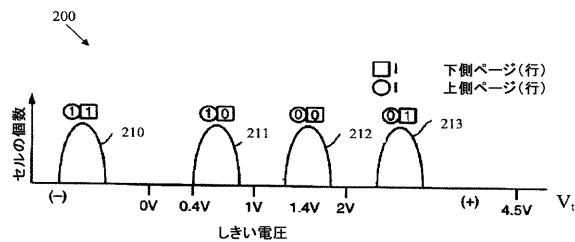

図2に示された例示的な実施形態では、各記憶素子は、各メモリ・セル内に2ビットのデータを格納するために4つの可能なデータ状態を使用する。図2は、4つのピーク210～213を示し、各ピークは1つの状態に対応する。マルチレベル・セル・フラッシュ・デバイスでは、しきい電圧分布グラフ200の異なるピーク210～213が、セルに2ビットを格納するのに使用される。

【0021】

40

しきい電圧分布グラフ200のピーク210～213は、対応する2進値を用いてラベルを付けられている。したがって、あるセルが第1状態210であるときに、そのセルは、下側ビット（最下位ビット、LSBとも称する）について「1」を、上側ビット（最上位ビット、MSBとも称する）について「1」を表す。状態210は、一般に、セルの初期未プログラム状態または消去状態である。同様に、あるセルが、第2状態211であるときに、そのセルは、下側ビットについて「0」、上側ビットについて「1」を表す。あ

50

るセルが第3状態212であるときに、そのセルは、下側ビットについて「0」、上側ビットについて「0」を表す。最後に、あるセルが第4状態213であるときに、そのセルは、下側ビットについて「1」、上側ビットについて「0」を表す。

#### 【0022】

しきい電圧分布210は、0ボルト未満の負のしきい電圧レベルを有する、消去状態（「11」データ状態）であるアレイ内のセルのしきい電圧 $V_t$ の分布を表す。それぞれ「10」および「00」のユーザ・データを格納するメモリ・セルのしきい電圧分布211および212が、それぞれ0ボルトと1ボルトとの間ならびに1ボルトと2ボルトとの間にあるものとして示されている。しきい電圧分布213は、読取経路電圧の2ボルトと4.5ボルトとの間にセットされたしきい電圧レベルを有する、「01」データ状態になるようにプログラムされたセルの分布を示す。

10

#### 【0023】

したがって、図2の例示的実施形態では、0ボルト、1ボルト、および2ボルトを、各レベルまたは各状態の間の電圧レベルしきい値として使用することができる。これらの電圧レベルしきい値は、フラッシュ・メモリ160（たとえば、フラッシュ・メモリ160内のセンシング回路）によって、所与のセルの電圧レベルまたは状態を判定するのに使用される。フラッシュ・メモリ160は、電圧レベルしきい値に対する測定電圧の比較に基づいて各セルに1つまたは複数のビットを割り当てる。この割当ては、その後、硬判定としてフラッシュ制御システム110に送られる。それに加えてまたはその代わりに、軟情報（soft information）を使用する実施態様では、フラッシュ・メモリ160は、測定電圧または測定電圧の量子化版を軟情報としてフラッシュ制御システム110に送ることができ、ここでは、メモリ・セルに格納されたビット数より多数のビットが、測定電圧を表すのに使用される。

20

#### 【0024】

さらに、セルが、通常は周知のプログラム／検証技法を使用してプログラムされることに留意されたい。一般に、プログラム／検証サイクル中には、フラッシュ・メモリ160は、最小ターゲットしきい電圧を超えるまで、セル・トランジスタ内に電荷をたくわえるために増加する電圧を徐々に印加する。たとえば、図2の例で「10」データ状態をプログラムする時に、フラッシュ・メモリ160は、0.4Vの最小ターゲットしきい電圧を超えるまで、セル・トランジスタ内に電荷をたくわえるために増加する電圧を徐々に印加することができる。

30

#### 【0025】

下でさらに述べるように、単一のメモリ・セルに格納された2ビットのそれぞれは、異なるページからのものである。言い換えると、各メモリ・セルに格納された2ビットの各ビットは、異なるページ・アドレスを担う。図2に示された右側ビットは、下側ページ・アドレスが入力される時にアクセスされる。左側ビットは、上側ページ・アドレスが入力される時にアクセスされる。

#### 【0026】

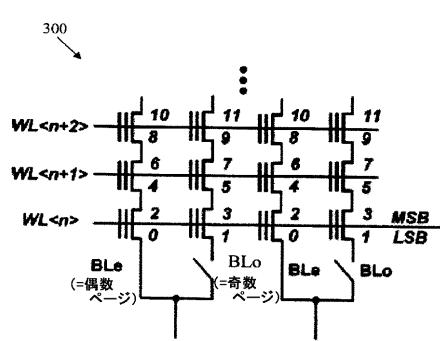

図3に、マルチレベル・セル（MLC）フラッシュ・メモリ・ブロック160内の例示的なフラッシュ・セル・アレイ300のアーキテクチャを示し、ここで、各例示的セルは、通常、2ビットを格納するフローティングゲート・トランジスタに対応する。図3では、各セルが、2ビットが属する2つのページの2つの番号に関連する。例示的なセル・アレイ・セクション300は、ワード線nからn+2および4つのビット線を示す。例示的なフラッシュ・セル・アレイ300は、偶数ページおよび奇数ページに区分され、たとえば、偶数番号を有するセル（番号0および2を有するセルなど）は、偶数ページに対応し、奇数番号を有するセル（番号1および3を有するセルなど）は、奇数ページに対応する。ワード線nは、たとえば、偶数ビット線に偶数ページ0および2を格納し、奇数ビット線に奇数ページ1および3を格納する。

40

#### 【0027】

さらに、図3は、偶数ビット線セルまたは奇数ビット線セルのいずれかが選択され、示

50

された順序で順次（ボトム・アップ）プログラムされる、例示的なプログラム・シーケンスを示す。番号は、ページがプログラムされる順序を示す。たとえば、ページ0は、ページ1の前にプログラムされる。偶数ページおよび奇数ページのプログラミングのさらなる議論については、参照によって本明細書に組み込まれている、K.-T. Park他、「A Zeroing Cell-to-Cell Interference Page Architecture with Temporary LSB Storing and Parallel MSB Program Scheme for MLC NAND Flash Memories」、IEEE Journal of Solid-State Circuits、Vol. 43、No. 4、919～928頁（2008年4月）を参照されたい。

10

#### 【0028】

図4に、図2の電圧割当て方式の例示的な2ステージMLCプログラミング方式400を示す。図4に示されているように、 LSBプログラミング・ステージ中には、消去状態410である選択されたセルの状態は、 LSBが0である場合には最低のプログラム済み状態411に移動する。したがって、 LSBプログラミング状態で、メモリ・セルは、消去状態「11」から「10」にプログラムされる。次に、 MSBプログラミング・ステージ中に、2つの状態すなわち状態「00」（412）および状態「01」（413）が、以前の LSBデータに応じて順次形成される。一般に、 MSBプログラミング状態中には、「10」状態が「00」にプログラムされ、状態「11」が「01」にプログラムされる。

20

#### 【0029】

図4のプログラミング方式400が、状態410から状態413への状態の変化に関連する最大電圧シフトを示すことに留意されたい。複数のプログラミング方式が、状態の変化に関連する最大電圧シフトを減らし、これによって、電圧シフトによって引き起こされるICを減らすために提案されまたは提唱されてきた。

#### 【0030】

図5Aおよび5Bは、隣接セルに加えられるICを減らす代替MLCプログラミング方式500を集合的に示す。図5Aに示されているように、 LSBプログラミング・ステージ中に、メモリ・セルは、 SLCプログラミングに似た形で、状態「11」から一時的（または中間）状態として状態「x0」にプログラムされる。同一ワード線内の隣接セルもLSBプログラムされた後に、分布は、おそらくは、ICに起因して図5Aのピーク510によって示されるように広げられる。その後、図5Bに示されたMSBプログラミング・ステージで、「x0」状態が、入力データに対応する最終状態として「00」および「10」のいずれかにプログラムされ、あるいは、「11」状態が、最終的な「01」状態にプログラムされる。一般に、「11」セルを除くすべてのメモリ・セルは、 MSBプログラミング・ステージで、 LSBデータについて一時的にプログラムされた状態からその最終的な状態に再プログラムされ、その結果、隣接セルによって引き起こされるICを大幅に減らせるようになる。最終的な状態のセルは、最終的な状態に再プログラムされたので、中間状態である間に経験したICから損害を受けない。最終的な状態のセルは、最終的な状態になって以降に経験したICからのみ損害を受ける。上で注記したように、中間プログラム状態を使用する、図5Aおよび5Bのマルチステップ・プログラミング・シーケンスは、最大電圧変化を減らし、したがって、これらの電圧変化によって引き起こされるICを減らす。図5Bで、たとえばMSBプログラミング・ステージ中の最大電圧シフトが、それぞれ状態「11」から「01」へおよび状態「x0」から状態「10」への遷移に関連することがわかる。これらの電圧シフトは、図4の状態「11」から「01」への最大電圧シフトより大幅に小さい。

30

#### 【0031】

図6に、マルチレベル・セル（MLC）フラッシュ・メモリ・ブロック160内の例示的なフラッシュ・セル・アレイ600をさらに詳細に示す。図6に示されているように、フラッシュ・セル・アレイ600は、フラッシュ・セルあたり3つのビット $c_i$ を格納する。図6は、1ブロックのフラッシュ・セル・アレイ・アーキテクチャを示し、ここで、

40

50

各例示的なセルは、通常、3ビットを格納するフローティングゲート・トランジスタに対応する。例示的なセル・アレイ600は、m個のワード線およびn個のビット線からなる。通常、現在のマルチページ・セル・フラッシュ・メモリでは、单一のセル内のビットは、異なるページに属する。図6の例では、各セルの3つのビットは、3つの異なるページに対応し、各ワード線は、3つのページを格納する。以降の議論では、ページ0、1、および2を、ワード線内の下側ページ・レベル、中央ページ・レベル、および上側ページ・レベルと称する。

#### 【0032】

上で示したように、フラッシュ・セル・アレイを、偶数ページおよび奇数ページにさらに区分することができ、たとえば、偶数番号を有するセル（図6のセル2および4など）は、偶数ページに対応し、奇数番号を有するセル（図6のセル1および3など）は、奇数ページに対応する。この場合に、ページ（ページ0など）は、偶数セル内に偶数ページ（偶数ページ0）を含み、奇数セル内に奇数ページ（奇数ページ0）を含む。

10

#### 【0033】

##### セル間干渉および他の外乱

図7に、セル間干渉、バック・パターン依存、雑音、および他のひずみなどの複数の例示的なアグレッサ・セル720に起因するターゲット・セル710について存在する外乱を示す。次の表記が、図7で使用されている。

20

WL ワード線、

BL ビット線、

BLo 奇数ビット線、

BLe 偶数ビット線、および

C キャパシタンス。

#### 【0034】

たとえば、I<sub>C</sub>Iは、ターゲット・セル710がプログラムされた後にプログラムされるアグレッサ・セル720によって引き起こされる。I<sub>C</sub>Iは、ターゲット・セル710の電圧V<sub>t</sub>を変更する。例示的実施形態では、「ボトム・アップ」プログラミング方式が仮定され、ワード線iおよびi+1内の近接アグレッサ・セルが、ターゲット・セル710のI<sub>C</sub>Iを引き起こす。ロックのそのようなボトム・アップ・プログラミングを用いると、図7に示されているように、下側ワード線i-1からのI<sub>C</sub>Iが除去され、5つまでの隣接するセルが、アグレッサ・セル720としてI<sub>C</sub>Iに寄与する。しかし、当業者に明白であるように、本明細書で開示される技法を、ワード線i-1などの他のワード線からのアグレッサ・セルもI<sub>C</sub>Iに寄与する場合に一般化できることに留意されたい。ワード線i-1、i、およびi+1からのアグレッサ・セルがI<sub>C</sub>Iに寄与する場合には、8つまでの最も近い隣接セルを考慮する必要がある。ターゲット・セルからより遠い他のセルは、そのI<sub>C</sub>Iへの寄与を無視できる場合には、無視することができる。一般に、アグレッサ・セル720は、所与のターゲット・セル710の後にプログラムされるアグレッサ・セル720を識別するためにプログラミング・シーケンス方式（ボトム・アップまたは偶数/奇数技法など）を分析することによって識別される。

30

#### 【0035】

一般に、V<sub>t</sub>は、セルに格納されたデータを表す電圧であり、読み取り動作中に入手される。V<sub>t</sub>を、読み取り動作によって、たとえばセルあたりに格納されるビット数より高い精度を有する軟電圧値として、またはセルあたりに格納されるビット数と同一の分解能を有する硬電圧レベル（たとえば、3ビット/セル・フラッシュについて3ビット）に量子化された値として、入手することができる。

40

#### 【0036】

I<sub>C</sub>I軽減技法のより詳細な議論については、たとえば、それぞれ参照によって本明細書に組み込まれている国際出願第PCT/US09/49326号、名称「Method and Apparatus for Read-Side Inter-cell Interference Mitigation in Flash Memory」

50

s」または国際出願第PCT/US09/49327号、名称「Methods and Apparatus for Write-Side Inter-cell Interference Mitigation in Flash Memories」を参照されたい。

【0037】

図8は、本発明によるコントローラ・ベースの軟データ生成技法を組み込まれた例示的なフラッシュ・メモリ・システム800の概略ブロック図である。図8に示されているように、例示的なフラッシュ・メモリ・システム800は、インターフェース850によって接続された、フラッシュ制御システム810およびフラッシュ・メモリ・ブロック860を含む。例示的なフラッシュ制御システム810は、通常は1つまたは複数の集積回路である、フラッシュ・コントローラ820および読み取りチャネル825を含む。

10

【0038】

例示的な読み取りチャネル825は、信号処理ユニット830、エンコーダ/デコーダ・ブロック840、および1つまたは複数のバッファ845を含む。用語「読み取りチャネル」が、書き込みチャネルをも含むことができることに留意されたい。代替実施形態では、エンコーダ/デコーダ・ブロック840およびいくつかのバッファ845を、フラッシュ・コントローラ820の内部で実施することができる。エンコーダ/デコーダ・ブロック840およびバッファ845を、たとえば、本発明の特徴および機能を提供するために本明細書で変更される、周知の市販の技法および/または製品を使用して実施することができる。

20

【0039】

例示的な信号処理ユニット830は、それぞれたとえば図12Aおよび12Bに関連して下でさらに述べる1つまたは複数の軟デマッパおよび/または軟データ生成プロセス835を実施する1つまたは複数のプロセッサを含む。例示的なフラッシュ・メモリ・ブロック860は、それぞれ周知の市販の技法および/または製品を使用して実施できるメモリ・アレイ870および1つまたは複数のバッファ880を含む。

【0040】

開示される軟データ生成技法のさまざまな実施形態では、例示的なインターフェース850は、アグレッサ・セルに関連する情報を表す値など、従来のフラッシュ・メモリ・システムに関連する追加情報を伝える必要がある場合がある。したがって、インターフェース850は、従来のフラッシュ・メモリ・システム内のインターフェースより大きい容量またはより高速のレートを有する必要がある場合がある。インターフェース850を、参照によって本明細書に組み込まれている、2009年6月30日に出願した国際出願第PCT/US09/49328号、名称「Methods and Apparatus for Interfacing Between a Flash Memory Controller and a Flash Memory Array」(弁理士整理番号第08-0769号)の教示に従って任意に実施することができ、この国際出願第PCT/US09/49328号の教示は、たとえばダブル・データ・レート(DDR)技法を使用してインターフェース850の情報搬送容量を高める。書き込み動作中に、インターフェース850は、通常はページ・レベル・アクセス技法またはワード線レベル・アクセス技法を使用して、ターゲット・セルに格納されるプログラム値を転送する。例示的なページ・レベル・アクセス技法またはワード線レベル・アクセス技法のより詳細な議論については、たとえば、参照によって本明細書に組み込まれている、2009年3月11日に出願した国際出願第PCT/US09/36810号、名称「Methods and Apparatus for Storing Data in a Multi-Level Cell Flash Memory Device with Cross-Page Sectors, Multi-Page Coding and Per-Page Coding」を参照されたい。

30

【0041】

読み込み動作中に、インターフェース850は、ターゲット・セルおよびアグレッサ・セルについてメモリ・アレイ870から入手された硬読み取り値および/または軟読み取り値を転送す

40

50

る。たとえば、ターゲット・セルを有するページの読み取り値に加えて、上側／下側ワード線または隣接する偶数ビット線もしくは奇数ビット線内の1つまたは複数の近接ページの読み取り値が、インターフェース・バスを介して転送される。図8の実施形態では、開示される軟データ生成技法は、フラッシュ・メモリの外部で、通常は最小面積を達成するために論理回路用に最適化されたプロセス・テクノロジで実施される。しかし、これは、インターフェース950上で転送される可能性がある追加のアグレッサ・セル・データという犠牲を払うものである。

#### 【0042】

図9は、本発明の代替実施形態によるメモリ・ベースの軟データ生成技法を組み込まれた例示的なフラッシュ・メモリ・システム900の概略ブロック図である。図9に示されているように、例示的なフラッシュ・メモリ・システム900は、インターフェース950によって接続された、フラッシュ制御システム910およびフラッシュ・メモリ・ブロック960を含む。

10

#### 【0043】

例示的なフラッシュ制御システム910は、通常は1つまたは複数の集積回路である、フラッシュ・コントローラ920およびオプションの読み取りチャネル925を含む。代替実施形態では、エンコーダ／デコーダ・ブロック940およびいくつかのバッファ945を、フラッシュ・コントローラ920の内部で実施することができる。例示的なフラッシュ・コントローラ920を、たとえば、本発明の特徴および機能をサポートするために本明細書で変更される、周知の市販の技法および／または製品を使用して実施することができる。例示的な読み取りチャネル925は、エンコーダ／デコーダ・ブロック940および1つまたは複数のバッファ945を含む。エンコーダ／デコーダ・ブロック940およびバッファ945を、周知の市販の技法および／または製品を使用して実施することができる。

20

#### 【0044】

例示的なフラッシュ・メモリ・ブロック960は、それぞれ周知の市販の技法および／または製品を使用して実施することができる、メモリ・アレイ970および1つまたは複数のバッファ980を含む。さらに、例示的なフラッシュ・メモリ・ブロック960は、それぞれたとえば図12Aおよび12Bに関連して下でさらに述べる1つまたは複数の軟デマッピングおよび／または軟データ生成プロセス990を実施する1つまたは複数のプロセッサを含む例示的な信号処理ユニット985を含む。

30

#### 【0045】

開示される軟データ生成技法のさまざまな実施形態では、例示的なインターフェース950は、アグレッサ・セルに関連する情報を表す値など、従来のフラッシュ・メモリ・システムに関連する追加情報を伝える必要がある場合がある。したがって、インターフェース950は、従来のフラッシュ・メモリ・システム内のインターフェースより大きい容量またはより高速のレートを有する必要がある場合がある。インターフェース950を、参照によって本明細書に組み込まれている、2009年6月30日に出願した国際出願第PCT/US09/49328号、名称「Methods and Apparatus for Interfacing Between a Flash Memory Controller and a Flash Memory Array」(弁理士整理番号第08-0769号)の教示に従って任意に実施することができ、この国際出願第PCT/US09/49328号の教示は、たとえばダブル・データ・レート(DDR)技法を使用してインターフェース950の情報搬送容量を高める。

40

#### 【0046】

書き動作中に、インターフェース950は、ターゲット・セルおよびアグレッサ・セルに格納されるプログラム・データを転送する。読み動作中に、インターフェース950は、ターゲット・セル(1つまたは複数)および任意にアグレッサ・セルの新しい硬読み取り値、硬データ、軟読み取り値、または軟データを転送する。通常、単一の読み取りアクセスについて伝えられる情報は、1ページまたは1ワード線のデータである。ターゲット・セルのデータだけを送ることは、通常は論理回路用ではなくメモリ用に最適化された、フラッシュ・

50

メモリの製造に使用されるメモリ・プロセス・テクノロジを使用してメモリの内部で軟データ生成プロセスを実施するという犠牲を払って、インターフェース950の帯域幅要件を減らすことに留意されたい。

#### 【0047】

##### 性能調整に基づく軟データ生成

前に示したように、現在のフラッシュ・メモリ・ブロック860、960は、通常、復号のためにフラッシュ制御システム810、910に硬データだけを供給する。しかし、軟データが、復号プロセスの誤り率性能を改善できることが周知である。したがって、本発明は、軟データを推定するかその質を高め、これによって復号性能を改善するために、フラッシュ・メモリ・ブロック860、960からの硬データを使用する軟データ生成技法を提供する。

10

#### 【0048】

本発明の一態様によれば、軟データは、硬データと1つまたは複数の性能要因に基づく調整とに基づいて、フラッシュ・メモリ・ブロック860、960などのメモリ・デバイスについて生成される。本明細書で使用されるときに、軟データは、測定された電圧を表すのにフラッシュ・メモリ・ブロック860、960のメモリ・セルに格納されたビット数より多数のビットが使用される軟値またはメモリ・セルに格納されたビットの信頼性を示す対数尤度比を含む。硬データは、検出されたデータ・ビット（軟情報なしで）またはメモリ・セルに格納されたレベル（電圧レベルなど）を指し、このデータ・ビットまたはレベルは、メモリ・アレイ870、970から読み出され、従来のフラッシュ・メモリ・デバイス内のフラッシュ制御システムに供給される。

20

#### 【0049】

1つの例示的実施形態では、軟データ値は、フラッシュ・メモリ・ブロック860、960によって割り当てられた硬データ値に基づく公称値とフラッシュ・メモリ・ブロック860、960の性能に影響する1つまたは複数の要因を補償するオフセット値（またはデルタ値）との合計である。この軟データ値は、対数尤度比を計算するのに使用される軟読取値（軟電圧値など）または格納されたビットの信頼性を示す対数尤度比のいずれかである。対数尤度比の生成および使用のより詳細な議論については、たとえば、それぞれ参照によって本明細書に組み込まれている、2009年6月30日に出願した国際出願第PCT/US09/49333号、名称「Methods and Apparatus for Soft Demapping and Inter-cell Interference Mitigation in Flash Memories」、および本願と同時に出願された国際出願、名称「Methods and Apparatus for Soft Data Generation in Flash Memories」を参照されたい。軟データ・ジェネレータ835、990によって生成された対数尤度比は、LPDC（Low Parity Density Check）デコーダなどのデコーダに供給される。

30

#### 【0050】

図10は、例示的なフラッシュ・メモリ・システム1000の概略ブロック図である。図10は、本発明の軟データ生成技法をさらに詳細に示す。図10に示されているように、フラッシュ・メモリ・システム1000は、インターフェース・バス1050によって接続された、フラッシュ・メモリ・ブロック1010およびフラッシュ制御システム1020を含む。

40

#### 【0051】

フラッシュ・メモリ・ブロック1010は、メモリ・アレイ1015を含む。フラッシュ・メモリ・ブロック1010は、メモリ・アレイ1015を読み取り、読み取られる各セルに格納された硬データ値（すなわち、硬電圧レベルなどの硬データ・ビットまたは硬レベル）を判定する。後で述べるように、硬データ値は、通常、フラッシュ・メモリ・ブロック1010によって割り当てられ、さらなる復号および処理のためにインターフェース1050を介してフラッシュ・コントローラ1020に転送される。

50

## 【0052】

例示的なフラッシュ・コントローラ1020は、下で図11および12に関連してさらに述べる軟データ・ジェネレータ1100、1200と、デコーダ1060とを含む。一般に、軟データ・ジェネレータ1100、1200は、フラッシュ・メモリ・ブロック1010によって割り当てられた硬データ値と1つまたは複数の性能要因調整とを使用して軟データを生成する。デコーダ1060は、たとえば、確率伝搬、メッセージ・パッシング、Sum-Product、またはMin-Sumアルゴリズムなど、LDPCアルゴリズムを使用して実施することができる。本明細書で説明される軟データ・ジェネレータ1100、1200の機能を、フラッシュ・コントローラ820、読み取りチャネル825、信号処理ユニット830、およびデコーダ840（たとえば、図8を参照されたい）のうちの1つまたは複数で実施できることに留意されたい。10

## 【0053】

前に示したように、本発明の一態様は、硬データおよび追加の性能要因の関数として軟データを計算する。1つの例示的実施形態では、軟データ値は、フラッシュ・メモリ・ブロック1010によって割り当てられた硬データ・レベルに基づく公称値と、フラッシュ・メモリ・ブロック1010の性能に影響する1つまたは複数の性能要因を補償するオフセット値（またはデルタ値）との合計である。

## 【0054】

1つの例示的実施形態では、フラッシュ・メモリ・ブロック1010の性能に影響する性能要因は、耐久性（たとえば、プログラム／消去サイクルの個数）、読み取りサイクルの個数、保持時間、フラッシュ・メモリの温度または温度変化、フラッシュ・メモリを製造するのに使用されるプロセス・コーナー、セル間干渉の影響または他の外乱機構に起因する影響、メモリ・アレイ内の位置（ワード線内のページ・レベル、偶数ビット線または奇数ビット線その他など）、およびアグレッサ・セルに格納されるデータ・パターンのうちの1つまたは複数を含む。下で図13に関連してさらに述べるように、1つの例示的実施形態では、オフセット値を、プログラム・レベルごとの性能要因ごとに割り当てることができる。性能要因を、前もって、たとえば製造テスト中に測定することができ、あるいは、性能劣化を補償するオフセット値入手するために、間欠的もしくは周期的な基礎で測定することができる。これらの性能要因を、フラッシュ制御システム810、910のレジスタ内またはフラッシュ・メモリ・ブロック860、960内にプログラムするか格納することができる。20

## 【0055】

たとえば、軟データ値を次のように計算することができる。

## 【0056】

## 【数1】

$$\text{軟データ値} = \begin{cases} \text{公称値}_0 - \text{オフセット} & \text{硬データ値が0である場合} \\ \text{公称値}_1 + \text{オフセット} & \text{硬データ値が1である場合} \end{cases}$$

ここで、軟データ値は、たとえば、対数尤度比を示し、軟データ値の符号は、硬データ値を表し、軟データ値の大きさは、信頼性を表し、公称値<sub>0</sub>は、ビット0の最大の可能な信頼性を示す正の数であり、公称値<sub>1</sub>は、ビット1の最大の可能な信頼性を示す負の数であり、オフセットは、フラッシュ・メモリ・ブロック1010の性能に影響する考慮される性能要因を補償する集約オフセット値である。たとえば、公称値<sub>0</sub>は、0と等しい硬データ値について+2と等しく、公称値<sub>1</sub>は、1と等しい硬データ値について-2と等しい。考慮される性能要因に基づいて、公称値の大きさは、オフセットが0より大きいときに減らされる。言い換えると、軟データ値に関連する信頼性は、硬データ値の信頼性を下げる性能要因に基づいて減らされる。40

## 【0057】

通常、軟データ値の大きさは、対応する硬データ値の信頼性を示し、軟データ値の符号は、対応する硬データ値が2進0または2進1のどちらであるのかを示す。例示的実施態

10

20

30

40

50

様では、軟データ値は、-2と+2との間で変化することができ、2は、最大の信頼性を有する2進0の値に対応し、-2は、最大の信頼性を有する2進1の値に対応する。上の式で使用されるオフセット値は、フラッシュ・メモリ・デバイスの信頼性に影響する外乱の特性を表す。一般に、オフセット値は、予想される外乱に比例して変化する（たとえば、外乱が大きければ大きいほど、オフセット値が大きくなる）。

#### 【0058】

1つの例示的実施形態では、オフセットを、事前定義の値に任意に飽和させることができる。たとえば、オフセットが、フラッシュ・メモリ・デバイスによって割り当てられたビットに対応する軟データ値の符号を変更しないことを保証するために、オフセットを飽和させることができる。

10

#### 【0059】

図11は、本発明の特徴を組み込まれた例示的な軟データ生成プロセス1100を説明する流れ図である。一般に、軟データ生成プロセス1100は、たとえばさまざまな考慮される性能要因に対処する硬・軟データ・マッピング・データベース1300を使用して、硬データ値を軟データ値に直接マッピングすることによって、軟データ値を生成する。

20

#### 【0060】

図11に示されているように、軟データ生成プロセス1100は、当初に、ステップ1110中にフラッシュ・メモリ1010から1つまたは複数の硬データ値を入手する。その後、軟データ生成プロセス1100は、ステップ1120中に、1つまたは複数の硬データ値と、フラッシュ・メモリ1010の1つまたは複数の事前定義の性能要因に基づく1つまたは複数の調整とに基づいて1つまたは複数の軟データ値を入手する。たとえば、軟データ生成プロセス1100は、硬・軟データ・マッピング・データベース1300内でルック・アップを実行するのに硬データを使用することができる。軟データ値は、その後に対数尤度比を計算するのに使用される軟読取値（軟電圧値など）または格納されたビットの信頼性を示す対数尤度比のいずれかを表す。

20

#### 【0061】

図12は、本発明の特徴を組み込まれた軟データ生成プロセス1200の例示的な代替実施態様を説明する流れ図である。一般に、軟データ生成プロセス1200は、フラッシュ・メモリ・ブロック1010によって割り当てられた硬データ値に基づく公称値と、フラッシュ・メモリ・ブロック1010の性能に影響する1つまたは複数の性能要因を補償するオフセット値とを合計することによって軟データ値を生成する。軟データ値は、その後に対数尤度比を計算するのに使用される軟読取値（軟電圧値など）または格納されたビットの信頼性を示す対数尤度比のいずれかを表す。

30

#### 【0062】

図12に示されているように、軟データ生成プロセス1200は、当初に、ステップ1210中にフラッシュ・メモリ1010から1つまたは複数の硬データ値を入手する。その後、軟データ生成プロセス1200は、ステップ1220中に、1つまたは複数の硬データ値に基づいて、対応する1つまたは複数の公称値を入手し、ステップ1230中に、1つまたは複数の考慮される性能要因に基づいて、対応する1つまたは複数のオフセット値を入手する。最後に、軟データ生成プロセス1200は、ステップ1240中に、入手された1つまたは複数の公称値およびオフセット値の集約に基づいて、1つまたは複数の所望の軟データ値を入手する。

40

#### 【0063】

図13は、フラッシュ・メモリ・セル内に最下位ビット（ LSB ）および最上位ビット（ MSB ）を格納する例示的な2ビット/セルMLCフラッシュ・メモリの、本発明の特徴を組み込まれた例示的な硬データ・軟データ・マッピング・データベース1300からのサンプル・テーブルである。MLCフラッシュ・メモリ内の異なるページ・レベル（ MSB ページおよび LSB ページなど）は、さまざまな性能要因によって異なる影響を受けるので、フラッシュ・メモリ・システムの誤り率性能を、異なるページ・レベルについて別々のオフセットを使用することによって改善することができる。例示的な硬データ -

50

軟データ・マッピング・データベース1300は、レコード1310で示される硬データ値（たとえば、2進1または2進0）およびレコード1320で示されるプログラム／消去サイクルの個数に基づいて、LSBおよびMSBの軟データをそれぞれレコード1330および1340に格納する。この例示的なデータベース1300では、誤り率性能を改善するために、別々のオフセットが2進1および0について使用される。2進1および0について、ならびにMSBページおよびLSBページなどの異なるページ・レベルについても同一のオフセットを使用することによって、誤り率性能を犠牲にしてデータベースの複雑さを減らすことができる。

#### 【0064】

硬データ - 軟データ・マッピング・データベース1300は、メモリ・アレイ内の偶数／奇数ビット線および／または異なるワード線位置のオフセットなど、追加の位置固有性能要因オフセットを示すこともできる。 10

#### 【0065】

硬データ - 軟データ・マッピング・データベース1300が、上で述べた例示的実施態様をとり、ここで、2進0の値を+2にマッピングすることができ、2進1の値を-2にマッピングすることができることに留意されたい。例示的なテーブル1300を、パターン依存ならびに／または読取サイクルの個数、プロセス・コーナー、および温度変化などの追加の性能要因を考慮に入れるために多次元テーブルとして任意に実施できることに留意されたい。

#### 【0066】

パターン依存および位置固有の性能要因のより詳細な議論については、たとえば、本願と同時に出願され、参照によって本明細書に組み込まれている国際出願、名称「Methods and Apparatus for Soft Data Generation in Flash Memories」を参照されたい。 20

#### 【0067】

プログラム／消去サイクル数および耐久性を考慮に入れ、異なる電圧レベルについて異なるオフセットを使用する、図4に示された電圧分布に関する例示的実施態様を考慮されたい。また、この実施態様では、性能要因オフセットは、通常 - 通常 (TT)、高速 - 高速 (FF)、および低速 - 低速 (SS) など、複数の異なるプロセス・コーナーについて指定される。この例示的実施態様の次の性能要因は、たとえば、対応する性能要因に関する条件の下でフラッシュ・メモリのオフセットの特徴を表す測定または他の製造テストに基づくものとすることができます。 30

(1) 耐久性要因：500消去／プログラム・サイクルのすべてについて、オフセットは、ビット・ラベル「11」を有するレベル0(410)について0.125、ビット・ラベル「10」を有するレベル1(411)およびビット・ラベル「01」を有するレベル3(413)について0.375、ビット・ラベル「00」を有するレベル2(412)について0.25である。

(2) プロセス・コーナー要因：フラッシュ・メモリを製造するのに使用される異なるプロセス・コーナーについて、オフセットは、SS:0.25; TT:0; FF:0.375である。 40

#### 【0068】

したがって、500消去／プログラム・サイクルの後のレベル1およびSSプロセス・コーナーについて、軟データは、LSB(硬データ・ビット=0)について $2 - 0.375 - 0.25 = 1.375$ である。MSBビット(硬データ・ビット=1)の軟データは $-2 + 0.375 + 0.25 = -1.375$ になる。この例示的実施形態では、同一の性能要因オフセットが、1つのセル内のLSBとMSBとの両方に使用される。上で説明したように、誤り率性能をさらに改善するために、異なる性能要因オフセットをLSBとMSBとの両方に使用することができる。

#### 【0069】

本発明のもう1つの態様によれば、質を高められた軟データ値が、フラッシュ・メモリ

・デバイスによって当初に割り当てられる軟データ値から生成される。初期軟データ値は、質を高められた軟データ値を生成するために、1つまたは複数の考慮される性能要因に基づいて調整される。これらの質を高められた軟データ値は、対数尤度比または信頼性を計算するのに使用される軟読取値（軟読取電圧など）のいずれかを表し、あるいは、対数尤度比または信頼性を表す。

【0070】

1つの例示的実施態様では、1つまたは複数の軟読取値が、フラッシュ・メモリから入手され、対数尤度比などの軟情報が、軟読取値に基づいて入手される。その後、軟情報（対数尤度比など）が、フラッシュ・メモリの1つまたは複数の性能要因に基づいて調整されて、質を高められた軟情報が入手され、この質を高められた軟情報は、質を高められた軟データ値であり、その後、誤り率性能を改善するためにデコーダに渡される。

10

【0071】

もう1つの例示的実施態様では、1つまたは複数の軟読取値が、フラッシュ・メモリから入手される。その後、対応する公称値が、軟読取値に基づいて判定され、対応するオフセット値が、1つまたは複数の考慮される性能要因に基づいて入手される。その後、対数尤度比などの軟データ値である所望の軟情報が、公称値およびオフセット値に基づいて入手される。

20

【0072】

プロセス、システム、および製品の詳細

本明細書の複数の流れ図は、ステップの例示的シーケンスを説明するが、そのシーケンスを変更されたものも、本発明の実施形態である。アルゴリズムのさまざまな置換が、本発明の代替実施形態として企図されている。本発明の例示的実施形態を、ソフトウェア・プログラム内の処理ステップに関して説明したが、当業者に明白であるように、さまざまな機能を、ディジタル領域でソフトウェア・プログラム内の処理ステップとして、ハードウェアで回路要素またはステート・マシンによって、あるいはソフトウェアとハードウェアとの両方の組合せで実施することができる。そのようなソフトウェアを、たとえば、ディジタル信号プロセッサ、特定用途向け集積回路、マイクロコントローラ、または汎用コンピュータで使用することができる。そのようなハードウェアおよびソフトウェアを、集積回路内で実施される回路内で実施することができる。

30

【0073】

したがって、本発明の機能を、方法およびこれらの方法を実践する装置の形で実施することができる。本発明の1つまたは複数の態様を、たとえば、記憶媒体に格納されるか、機械にロードされかつ／または機械によって実行されるか、あるいはある伝送媒体を介して伝送されるかのいずれかであるプログラム・コードの形で実施することができ、ここで、そのプログラム・コードがコンピュータなどの機械にロードされ、その機械によって実行されるときに、その機械は、本発明を実践する装置になる。汎用プロセッサで実施される時に、プログラム・コード・セグメントは、特定の論理回路に類似して動作するデバイスを提供するためにプロセッサと組み合わされる。本発明を、集積回路、ディジタル信号プロセッサ、マイクロプロセッサ、およびマイクロコントローラのうちの1つまたは複数で実施することもできる。

40

【0074】

当技術分野で既知のように、本明細書で述べられた方法および装置を、コンピュータ可読コード手段をその上で実施されたコンピュータ可読媒体をそれ自体が含む製品として配布することができる。コンピュータ可読プログラム・コード手段は、本明細書で述べられた方法を実行するステップのすべてまたは一部を実行したまたは本明細書で述べられた装置を作成するために、コンピュータ・システムに関連して動作可能である。コンピュータ可読媒体は、記録可能媒体（たとえば、フロッピ・ディスク、ハード・ドライブ、コンパクト・ディスク、メモリ・カード、半導体デバイス、チップ、特定用途向け集積回路（A S I C））とすることができ、あるいは、伝送媒体（たとえば、光ファイバを含むネットワーク、ワールド・ワイド・ウェブ、ケーブル、または時分割多元接続、符号分割多元接続

50

、もしくは他の無線周波数チャネルを使用する無線チャネル)とすることができます。コンピュータ・システムと共に使用するのに適切な情報を格納できる既知のまたは開発されるすべての媒体を、使用することができます。コンピュータ可読コード手段は、磁気媒体上の磁気変動またはコンパクト・ディスクの表面上の高さ変動など、コンピュータが命令およびデータを読み取ることを可能にするすべての機構である。

### 【0075】

本明細書で説明されるコンピュータ・システムおよびサーバは、それぞれ、本明細書で開示される方法、ステップ、および機能を実施するために関連プロセッサを構成するメモリを含む。メモリを、分散型またはローカルとすることができます、プロセッサを、分散型または単独とすることができます。メモリを、電子メモリ、磁気メモリ、または光メモリ、あるいは上記または他のタイプのストレージ・デバイスの任意の組合せとして実施することができます。さらに、用語「メモリ」は、関連するプロセッサによってアクセスされるアドレス空間内のアドレスから読み取られるかそのアドレスに書き込まれることが可能なすべての情報を包含するのに十分に広く解釈されなければならない。この定義を用いると、ネットワーク上の情報は、それでも、関連するプロセッサがネットワークからその情報を取り出すことができるので、メモリに含まれる。

### 【0076】

本明細書で図示され、説明された実施形態および変形形態が、本発明の原理の単なる例示であり、さまざまな修正形態を、本発明の範囲および趣旨から逸脱せずに当業者が実施できることを理解されたい。

10

20

【図1】

【図3】

【図2】

【図4】

【図 5 A】

【図 5 B】

【図 6】

【図 7】

【図 8】

【図 9】

【図 10】

【 図 1 1 】

【 図 1 2 】

【 図 1 3 】

硬電圧-軟データ・マッピング・データベース 1300

## 【国際調査報告】

## INTERNATIONAL SEARCH REPORT

International application No

PCT/US2009/059069

A. CLASSIFICATION OF SUBJECT MATTER

INV. G11C16/26 G11C16/34 G11C7/10 G11C11/56

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

G11C

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practical, search terms used)

EPO-Internal, WPI Data, PAJ

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category* | Citation of document, with indication, where appropriate, of the relevant passages                                                                                                  | Relevant to claim No. |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|

| X         | US 2008/151617 A1 (ALROD IDAN [IL] ET AL)<br>26 June 2008 (2008-06-26)<br>the whole document                                                                                        | 1-20                  |

| X         | WO 2008/042593 A1 (SANDISK CORP [US];<br>BRANDMAN YIGAL [US]; CONLEY KEVIN M [US])<br>10 April 2008 (2008-04-10)<br>page 2, line 29 - line 30<br>page 15, line 18 - page 16, line 3 | 1                     |

| X         | US 2008/123420 A1 (BRANDMAN YIGAL [US] ET<br>AL) 29 May 2008 (2008-05-29)<br>paragraph [0037] - paragraph [0040]                                                                    | 1                     |

| A         | US 2006/015802 A1 (HOCEVAR DALE E [US])<br>19 January 2006 (2006-01-19)<br>paragraph [0028]                                                                                         | 1                     |

Further documents are listed in the continuation of Box C.

See patent family annex.

## \* Special categories of cited documents:

"A" document defining the general state of the art which is not considered to be of particular relevance

"E" earlier document but published on or after the international filing date

"L" document which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified)

"O" document referring to an oral disclosure, use, exhibition or other means

"P" document published prior to the international filing date but later than the priority date claimed

"T" later document published after the International filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention

"X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone

"Y" document of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art.

"&" document member of the same patent family

Date of the actual completion of the international search

Date of mailing of the international search report

3 December 2009

07/01/2010

Name and mailing address of the ISA/

European Patent Office, P.B. 5818 Patentlaan 2

NL - 2280 HV Rijswijk

Tel. (+31-70) 340-2040

Fax: (+31-70) 340-3016

Authorized officer

Ramcke, Ties

## INTERNATIONAL SEARCH REPORT

Information on patent family members

International application No

PCT/US2009/059069

| Patent document cited in search report |    | Publication date |    | Patent family member(s) |  | Publication date |

|----------------------------------------|----|------------------|----|-------------------------|--|------------------|

| US 2008151617                          | A1 | 26-06-2008       | WO | 2008075351 A2           |  | 26-06-2008       |

| WO 2008042593                          | A1 | 10-04-2008       | KR | 20090086523 A           |  | 13-08-2009       |

| US 2008123420                          | A1 | 29-05-2008       |    | NONE                    |  |                  |

| US 2006015802                          | A1 | 19-01-2006       | EP | 1779524 A1              |  | 02-05-2007       |

|                                        |    |                  | JP | 2008507240 T            |  | 06-03-2008       |

|                                        |    |                  | KR | 20070029846 A           |  | 14-03-2007       |

|                                        |    |                  | WO | 2006020205 A1           |  | 23-02-2006       |

---

フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HR,HU,IE,IS,IT,LT,LU,LV,MC,MK,MT,NL,NO,PL,PT,RO,SE,SI,S,K,SM,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AO,AT,AU,AZ,BA,BB,BG,BH,BR,BW,BY,BZ,CA,CH,CL,CN,CO,CR,CU,CZ,DE,DK,DM,DO,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,GT,HN,HR,HU,ID,IL,IN,IS,JP,KE,KG,KM,KN,KP,KR,KZ,LA,LC,LK,LR,LS,LT,LU,LY,MA,MD,ME,MG,MK,MN,MW,MX,MY,MZ,NA,NG,NI,NO,NZ,OM,PE,PG,PH,PL,PT,RO,RS,RU,SC,SD,SE,SG,SK,SL,SM,ST,SV,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,ZA,ZM,ZW

(72)発明者 ハラッチ,エリッチ,エフ.

アメリカ合衆国 18017 ペンシルヴァニア,ベスレヘム,バーバリー ストリート 510

5

(72)発明者 エン,ジョンソン

アメリカ合衆国 94539 カリフォルニア,フレモント,ローレル グレン テラス 600

F ターム(参考) 5B018 GA10 NA06 QA14