(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(51) Int. Cl.

*G06F 12/00* (2006.01)*H04L 27/14* (2006.01)*H04N 5/217* (2006.01)

(45) 공고일자

2007년03월20일

(11) 등록번호

10-0697153

(24) 등록일자

2007년03월13일

(21) 출원번호

10-2005-0033102

(65) 공개번호

10-2006-0047334

(22) 출원일자

2005년04월21일

(43) 공개일자

2006년05월18일

심사청구일자

2005년04월21일

(30) 우선권주장

JP-P-2004-00126940

2004년04월22일

일본(JP)

(73) 특허권자

산요덴키가부시키가이샤

일본 오사카후 모리구치시 게이한 혼도오리 2쵸메 5반 5고

(72) 발명자

스즈끼 다까유끼

일본 기후켄 기후시 나메끼 369-1

(74) 대리인

장수길

이중희

구영창

(56) 선행기술조사문현

KR1020000026010 A

KR1019980067233 A

KR1002063740000 B \*

\* 심사관에 의하여 인용된 문현

심사관 : 윤혜숙

전체 청구항 수 : 총 7 항

(54) 제어 장치

(57) 요약

회로 면적의 증대 및 제조 코스트의 증대를 억제하면서, 전기적으로 재기입 가능한 내부 불휘발성 메모리에 CPU의 동작 프로그램의 기입을 행할 수 있는 제어 장치를 제공한다. 다운로드 인에이블 신호를 수신한 다운로드 제어 회로(51)는, 제1 커맨드 레지스터(61)의 판독용 커맨드 세트 및 어드레스 레지스터(53)에 세트된 어드레스에 의해, 외부 시리얼 플래시 ROM(30)의 데이터를 판독하여 데이터 레지스터(54)에 일시적으로 기억한다. 그리고, 제2 커맨드 레지스터(62)의 기입용 커맨드 세트, 어드레스 레지스터(53)에 세트된 어드레스 및 데이터 레지스터(54)에 일시적으로 기억된 데이터에 의해, 내부 플래시 ROM(10)에 데이터를 기입한다.

내표도

도 1

## 특허청구의 범위

### 청구항 1.

마이크로컴퓨터에 소정의 동작 제어를 행하게 하는 동작 프로그램을 기억하기 위한 전기적으로 재기입 가능한 내부 불휘발성 메모리와,

상기 내부 불휘발성 메모리와의 입출력을 제어하는 내부 인터페이스와,

외부 불휘발성 메모리와의 입출력을 제어하는 외부 인터페이스와,

외부로부터의 지시에 의해, 상기 외부 인터페이스를 통하여 상기 외부 불휘발성 메모리에 기억된 데이터를 소정의 어드레스 단위로 판독하고, 상기 내부 인터페이스를 통하여 상기 내부 불휘발성 메모리에 상기 소정의 어드레스 단위로 상기 데이터를 기입하는 반복 동작을 제어하는 다운로드 회로

를 포함하고,

외부로부터의 상기 지시에 의해 상기 다운로드 회로가 동작 중에는, 상기 마이크로컴퓨터는 슬립 상태로 되고, 상기 내부 인터페이스는 상기 내부 불휘발성 메모리와 상기 마이크로컴퓨터와의 접속을 절단하는 제어 장치.

### 청구항 2.

제1항에 있어서,

상기 다운로드 회로는,

상기 내부 불휘발성 메모리에 상기 데이터를 기입 중인 상태를 유지하기 위한 플립플롭과,

상기 내부 불휘발성 메모리에의 데이터의 기입 시간을 관리하는 카운터

를 구비하는 제어 장치.

### 청구항 3.

제1항에 있어서,

상기 외부 시리얼 메모리에 기억된 데이터를 판독하기 위한 커맨드 세트를 기억한 내부 불휘발성의 제1 커맨드 레지스터

를 포함하는 제어 장치.

### 청구항 4.

제1항에 있어서,

상기 내부 불휘발성 메모리에 상기 데이터를 기입하기 위한 커맨드 세트를 기억하는 제2 커맨드 레지스터

를 포함하는 제어 장치.

## 청구항 5.

제1항 내지 제4항 중 어느 한 항에 있어서,

상기 다운로드 회로가 동작하지 않을 때에 외부와의 신호의 교환에 사용하는 통상 단자

를 포함하고,

상기 외부 불휘발성 메모리와 상기 외부 인터페이스 사이의 적어도 일부의 외부 단자는 상기 통상 단자의 일부 또는 전부인 제어 장치.

## 청구항 6.

제5항에 있어서,

상기 외부 불휘발성 메모리에 전원을 공급하는 단자

를 포함하는 제어 장치.

## 청구항 7.

제5항에 있어서,

상기 외부 불휘발성 메모리는 시리얼 메모리인 제어 장치.

**명세서**

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 제어 장치에 관한 것이다.

일반적으로, 광 디스크 드라이브 장치 등의 주변 기기에는, 각 회로의 제어를 행하기 위한 마이크로컴퓨터(CPU)의 동작 프로그램을 기억하기 위한 메모리로서, ROM이 탑재되어 있다. 최근에는, 이 ROM으로서, 데이터를 전기적으로 재기입 가능한 플래시 ROM이 사용되는 것이 일반적이다. 이는, 주변 기기의 개발 중 등에 행해지는 디버그나, 주변 기기의 기능 향상을 위한 업데이트(버전업)에 의해, 동작 프로그램의 갱신이 필요하게 되는 것에 의한다.

플래시 ROM에는 2 종류의 프로그램이 기입되어 있는데, 이는, CPU가 각 회로의 제어를 행하기 위한 상술한 동작 프로그램과, 이를 갱신하기 위한 업데이트용 프로그램이다. 주변 기기의 통상의 동작 시에는, CPU는 플래시 ROM에 기입된 동작 프로그램에 따라 각 회로의 제어를 행한다. 한편, 동작 프로그램의 갱신 시에는, CPU는 플래시 ROM에 기입된 업데이트용 프로그램에 따라 플래시 ROM에 기억된 동작 프로그램을 재기입한다.

이상의 설명은, 플래시 ROM에 동작 프로그램이나 업데이트용 프로그램이 이미 기입되어 있는 상태에서의 동작이다. 그러나, 완전한 초기 상태에서는, 당연히 플래시 ROM에는 어떤 데이터도 기입되어 있지 않다. 즉, CPU가 동작 프로그램을 플래시 ROM에 기입하기 위해서는 적어도 업데이트용 프로그램이 이미 플래시 ROM에 기입되어 있을 필요가 있지만, 완전한 초기 상태에서는 이것도 기입되어 있지 않다.

이 때문에, 종래에는, 플래시 ROM 메이커에 위탁하거나, ROM 라이터 등을 이용하거나 하여, 플래시 ROM 단체(單體)의 상태에서 미리 결정된 초기 데이터(적어도 업데이트용 프로그램을 포함하는 데이터)의 기입을 행하고 있다. 이 초기 데이터가 기입된 플래시 ROM 칩은, 그 후, 해당 기기의 프린트 기판에 납땜 등으로 실장되게 된다.

### 발명이 이루고자 하는 기술적 과제

그런데, 상술한 방법에서는, 주변 기기에 플래시 ROM 칩을 실장하기 전에, 초기 데이터의 기입 작업이 별도로 필요하게 되므로, 공정이 번잡화되어 제조 코스트의 증대가 불가피하다.

따라서, 상기와는 다른 종래 기술에서는, 데이터가 기입되어 있지 않은 플래시 ROM을 실장하고, 그 후에 동작 프로그램의 기입을 행하는 방법이 채용되고 있다. 구체적으로는, 해당 기기에는, 적어도 업데이트용 프로그램을 기억한 마스크 ROM이 내장되고, 이 마스크 ROM은 CPU에 접속되어 있다. 그리고, 마스크 ROM에 기억된 업데이트용 프로그램에 따라 CPU를 동작시키고, 그 CPU가 ATA/ATAPI나 SCSI 등의 인터페이스를 통하여 외부의 호스트 컴퓨터로부터 수신한 동작 프로그램을 플래시 ROM에 기입한다.

그러나, 이 방법에서는, 적어도 업데이트용 프로그램을 기억한 마스크 ROM이 필요하지만, 이 마스크 ROM은 통상의 동작에는 사용되지 않는다. 따라서, 통상의 동작에 전혀 필요가 없는 마스크 ROM을 탑재하는 것은, 제어 장치(제어용 집적 회로)의 칩 면적을 증대시킨다. 또한, 외부에 초기 데이터를 공급하는 외부의 호스트 컴퓨터를 필요로 하기 때문에, 초기 데이터의 기입 작업을 위한 공정 코스트도 여전히 크다.

본 발명의 목적은, 회로 면적의 증대 및 제조 코스트의 증대를 억제하면서, 전기적으로 재기입 가능한 내부 불휘발성 메모리에 CPU의 동작 프로그램의 기입을 행할 수 있는 제어 장치를 제공하는 것에 있다.

### 발명의 구성

상기 문제점을 해결하기 위해, 제어 장치로서, 마이크로컴퓨터에 소정의 동작 제어를 행하게 하는 동작 프로그램을 기억하기 위한 전기적으로 재기입 가능한 내부 불휘발성 메모리와, 상기 내부 불휘발성 메모리와의 입출력을 제어하는 내부 인터페이스와, 외부 불휘발성 메모리와의 입출력을 제어하는 외부 인터페이스와, 외부로부터의 지시에 의해, 상기 외부 인터페이스를 통하여 상기 외부 불휘발성 메모리에 기억된 데이터를 소정의 어드레스 단위로 판독하고, 상기 내부 인터페이스를 통하여 상기 내부 불휘발성 메모리에 상기 소정의 어드레스 단위로 상기 데이터를 기입하는 반복 동작을 제어하는 다운로드 회로를 포함하고, 외부로부터의 상기 지시에 의해 상기 다운로드 회로가 동작 중에는, 상기 마이크로컴퓨터는 슬립 상태로 되고, 상기 내부 인터페이스는 상기 내부 불휘발성 메모리와 상기 마이크로컴퓨터와의 접속을 절단하는 것을 특징으로 한다.

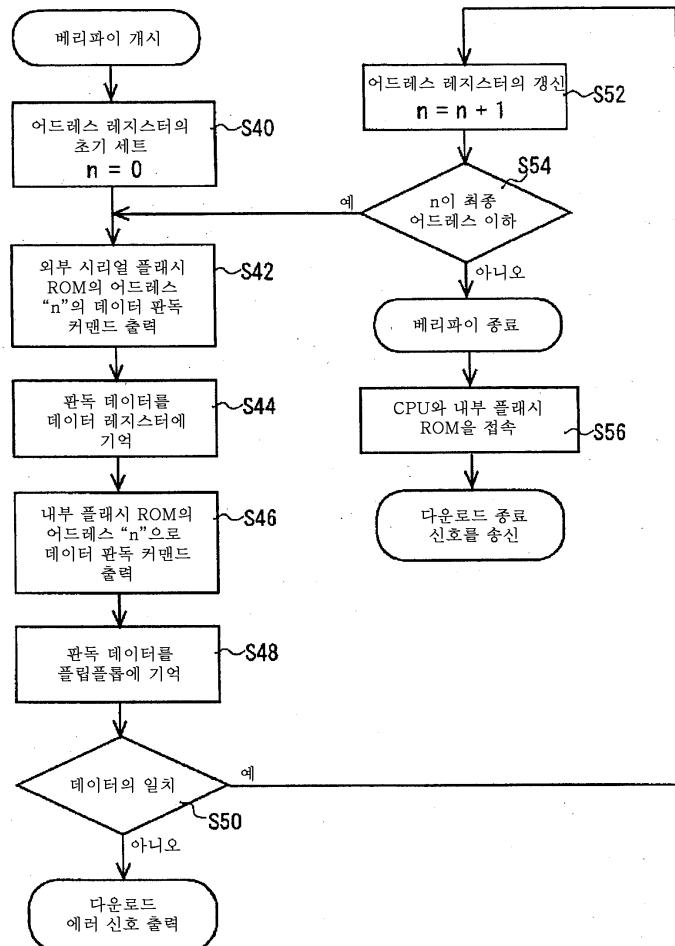

이하, 본 발명을 구체화한 일 실시예를 도 1에 따라서 설명한다.

도 1은, 예를 들면 CD-ROM 드라이브 장치 등의 제어 장치(100)를 도시하는 블록도이다. 도 1에 도시하는 바와 같이, 이 제어 장치(100)는, 전기적으로 재기입 가능한 내부 불휘발성 메모리인 내부 플래시 ROM(10)과, 마이크로컴퓨터(CPU)(20)와, 외부 인터페이스(40)와, 다운로드 회로(50)와, 제1 커맨드 레지스터(61)와, 제2 커맨드 레지스터(62)와, 내부 인터페이스(70)를 구비하고 있다. 내부 플래시 ROM(10)은, 공장에서의 제조 직후에는 초기 데이터(동작 프로그램 및 업데이트용 프로그램)는 기입되어 있지 않아, CPU(20)는 아무런 동작을 행할 수 없다.

이하, 본 실시예에서의 내부 플래시 ROM(10)에의 초기 데이터의 기입(다운로드) 양태에 대하여 개략을 설명한다.

제어 장치(100)는 외부 인터페이스(40)를 통하여 외부 불휘발성 메모리인 외부 시리얼 플래시 ROM(30)이 접속 가능하게 되어 있다. 다운로드 할 때에는, 외부 인터페이스(40)에는 외부 시리얼 플래시 ROM(30)이 접속되어 있고, 이 외부 시리얼 플래시 ROM(30)에는 초기 데이터가 기억되어 있다. 다운로드 인에이블 신호가 외부 단자를 통하여 다운로드 회로(50)에 송신되면, 다운로드 회로(50)는 CPU(20)의 동작을 슬립시키는 제어 신호를 생성하고, 동시에 내부 인터페이스(70)는 CPU(20)와 내부 플래시 ROM(10)과의 접속을 절단한다. 따라서, 다운로드 회로(50)는 CPU(20)에 의해 저해되는 일 없이, 내부 플래시 ROM(10)의 소정 어드레스에 축차적으로 소정의 데이터를 기입할 수 있게 된다.

그 후, 다운로드 회로(50)는 외부 인터페이스(40)를 통하여 외부 시리얼 플래시 ROM(30)에 기억된 데이터를 소정의 어드레스 단위로 판독하고, 판독한 데이터를 내부 인터페이스(70)를 통하여 내부 플래시 ROM(10)에 기입한다. 이후, 다운로드

회로(50)는 소정의 어드레스 단위의 다음 데이터에 대해서도 외부 시리얼 플래시 ROM(30)으로부터 판독하고, 판독한 데이터를 내부 플래시 ROM(10)에 기입한다. 이를 내부 플래시 ROM(10)의 최종 어드레스까지 반복함으로써, 모든 데이터(동작 프로그램)를 내부 플래시 ROM(10)에 기입할 수 있다. 기입 종료 후, 다운로드 회로(50)는 내부 플래시 ROM(10)에 기입된 데이터를 베리파이한다. 베리파이 후, 다운로드 회로(50)는 기입의 종료를 나타내는 다운로드 종료 신호를 외부 단자를 통하여 외부에 송신한다. 외부에서는 다운로드 종료 신호를 수신하면 LED가 발광하도록 해 둠으로써, 내부 플래시 ROM(10)에의 초기 데이터의 기입(다운로드)의 종료를 알 수 있다.

내부 인터페이스(70)에 의해 CPU(20)와 내부 플래시 ROM(10)을 접속하고, CPU(20)의 동작을 슬립 상태로부터 개방하는 것은, 베리파이 직후에 다운로드 회로(50)가 행하여도 되고, 다운로드 종료 후의 전원 재투입에 의해 행하도록 하여도 된다.

다음으로, 본 실시예에서의 내부 플래시 ROM(10)에의 초기 데이터의 기입 양태에 대하여 상세하게 설명한다.

불휘발성 메모리로 구성된 제1 커맨드 레지스터(61)는, 외부 시리얼 플래시 ROM(30)으로부터 데이터를 판독하기 위한 커맨드 세트를 미리 기억한 레지스터 세트이다. 단, 외부 시리얼 플래시 ROM(30)으로부터의 판독용 커맨드 세트가 불필요할 때에는, 제1 커맨드 레지스터(61)는 설치하지 않아도 된다. 커맨드 세트란, 일반적으로 플래시 메모리에 액세스할 때에 필요한 커맨드로서, 복수 쌍의 커맨드 어드레스 및 커맨드 데이터를 플래시 메모리에 송신함으로써, 소거, 기입, 판독 등의 소정의 동작을 플래시 메모리에 행하게 하는 것이다. 커맨드 세트의 내용은 플래시 메모리의 규격에 따라 다르다.

또한, 제2 커맨드 레지스터(62)는, 내부 플래시 ROM(10)에 데이터를 기입하거나 혹은 내부 플래시 ROM(10)으로부터 데이터를 판독하거나 하기 위한 커맨드 세트를 기억하는 레지스터 세트이다. 제2 커맨드 레지스터(62)는 불휘발성 메모리로 구성되어도 되고, 휘발성 메모리로 구성하여 두고 외부 시리얼 플래시 ROM(30)의 소정 어드레스 영역으로부터 커맨드 세트를 판독하고 기억시켜도 된다. 이 때, 외부 시리얼 플래시 ROM(30)의 소정 어드레스 영역에는 미리 내부 플래시 ROM(10)의 커맨드 세트가 기억되어 있다.

다운로드 회로(50)는, 다운로드 제어 회로(51), 플립플롭(52), 어드레스 레지스터(53), 데이터 레지스터(54) 및 카운터(55)를 포함하여 구성되어 있다.

다운로드 제어 회로(51)는 어드레스 레지스터(53), 데이터 레지스터(54) 및 카운터(55)가 접속됨과 함께, 플립플롭(52)을 통하여 내부 인터페이스(70)에 접속되어 있다. 플립플롭(52)은 다운로드 제어 회로(51)와 내부 플래시 ROM(10) 간의 복수의 신호를 보유하도록 설치되어 있다.

어드레스 레지스터(53)는, 외부 시리얼 플래시 ROM(30) 및 내부 플래시 ROM(10)에 액세스하는 어드레스를 기억하는 레지스터이다. 데이터 레지스터(54)는, 어드레스 레지스터(53)에 기억된 어드레스에 대하여 외부 시리얼 플래시 ROM(30)으로부터 판독한 데이터를 기억하는 레지스터이다. 카운터(55)는, 내부 플래시 ROM(10)에 대한 기입에 필요한 사이클 수를 카운트하는 카운터로서, 내부 플래시 ROM(10)의 전기적 특성과 클럭 신호의 주파수에 따른 카운트 설정값(사이클 수)까지 카운트한다. 이 카운트 설정값은, 카운터(55)에 불휘발성 메모리로서 미리 기억해 두어도 되고, 외부 시리얼 플래시 ROM(30)의 소정 어드레스 영역으로부터 판독하여 휘발성 메모리에 기억시켜도 된다.

내부 플래시 ROM(10)은, 셋업이나 홀드 시간에 의해, 그 액세스의 간격에 소정 기간을 요한다. 예를 들면, 내부 플래시 ROM(10)에 데이터를 연속하여 기입하는 경우, 1개의 데이터를 기입하고 나서 다음 데이터를 기입하기까지 소정 기간 대기해야 한다. 이 소정 기간은 내부 플래시 ROM(10)의 전기적 특성에 의한 것이다.

다운로드 제어 회로(51)는 이 대기 시간을 위해 클럭 신호를 이용한다. 즉, 다운로드 제어 회로(51)는, 카운터(55)에 클럭 신호의 폴스 수를 카운트시킴으로써, 소정 기간(대기 시간)을 계측한다. 그리고, 클럭 신호의 주파수는, 이 제어 장치(100)를 탑재하는 주변 기기에 따라 다르다. 따라서, 다운로드 제어 회로(51)는 내부 플래시 ROM(10)의 전기적 특성과 주변 기기의 클럭 신호의 주파수에 따른 설정 카운트값까지 대기하고 나서 내부 플래시 ROM(10)에 액세스하여 다음 데이터를 기입한다.

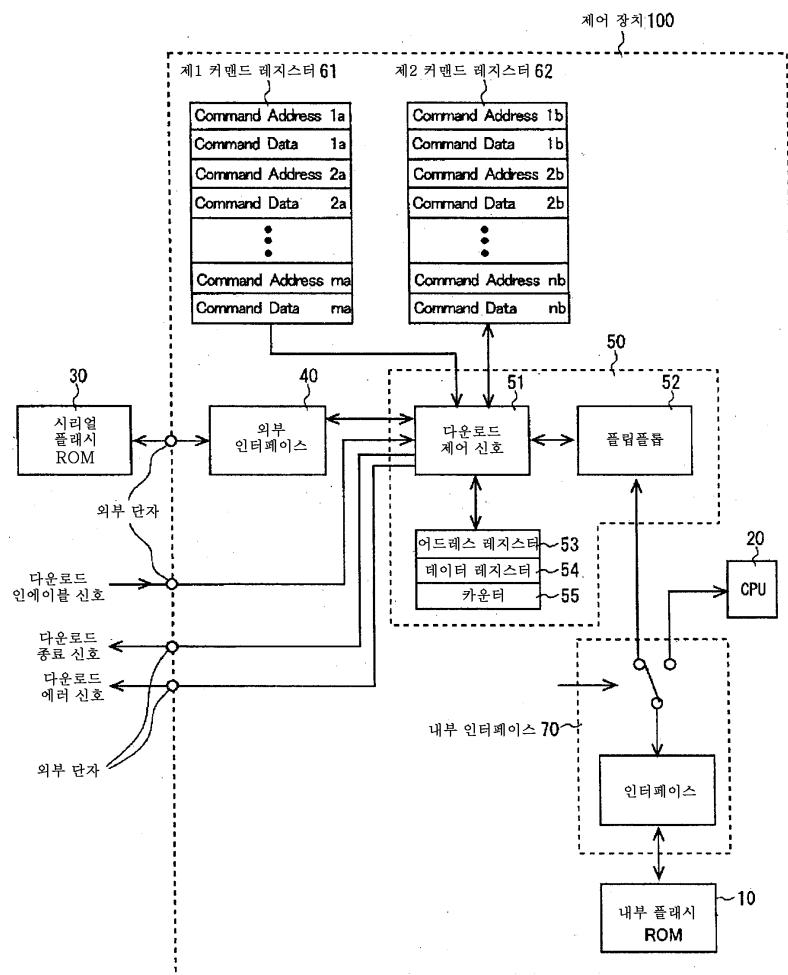

본 실시예에서의 내부 플래시 ROM(10)에의 초기 데이터의 기입 수순을 도 2 및 도 3을 이용하면서 설명한다.

최초에, 다운로드 인에이블 신호가 다운로드 제어 회로(51)에 수신된다(S10). 이에 의해, 다운로드 제어 회로(51)는 CPU(20)의 동작을 슬립시키는 제어 신호를 생성하고, 동시에 내부 인터페이스(70)는 CPU(20)와 내부 플래시 ROM(10)과의 접속을 절단하고 내부 플래시 ROM(10)과 플립플롭(52)을 접속한다(S12). 그리고, 다운로드 제어 회로(51)는, 외부 시리

얼 플래시 ROM(30)에 최초로 액세스하는 어드레스(예를 들면, "0")를 어드레스 레지스터(53)에 세트한다(S14). 그리고, 제1 커맨드 레지스터(61)로부터 순차적으로 판독용 커맨드 세트를 판독하고, 판독한 커맨드 세트 및 어드레스 레지스터(53)에 세트된 어드레스를 순차적으로 외부 인터페이스(40)를 통하여 외부 시리얼 플래시 ROM(30)에 출력한다(S16). 이에 의해, 외부 시리얼 플래시 ROM(30)은, 입력된 어드레스의 데이터를 출력한다. 외부 시리얼 플래시 ROM(30)으로부터 출력된 데이터는 외부 인터페이스(40)를 통하여 다운로드 제어 회로(51)에 판독되고, 데이터 레지스터(54)에 일시적으로 기억된다(S18).

다음으로, 다운로드 제어 회로(51)는 제2 커맨드 레지스터(62)로부터 순차적으로 기입용 커맨드 세트를 판독하고, 판독한 커맨드 세트, 어드레스 레지스터(53)에 세트된 어드레스 및 데이터 레지스터(54)에 일시적으로 기억된 데이터를 순차적으로 플립플롭(52) 및 내부 인터페이스(70)를 통하여 내부 플래시 ROM(10)에 출력한다(S20). 플립플롭(52)은 내부 플래시 ROM(10)에의 기입 동작을 유지하기 위해 설치되는 것이고, 이 때문에, 내부 플래시 ROM(10)에의 기입 중에는, 다운로드 제어 회로(51)는 다른 동작을 실시할 수 있다. 또한, 다운로드 제어 회로(51)는, 플립플롭(52)에 상기의 출력을 행하면, 카운터(55)의 카운트를 스타트시킨다(S22). 카운터(55)는, 예를 들면 인크리먼트 카운터이고, 도시하지 않은 기준 클럭 신호의 펄스 수를 카운트한다. 그리고, 카운터(55)는 그 카운트값이 다운로드 제어 회로(51)의 설정 카운트값과 일치하는 경우에는 소정 레벨의 카운트 종료 신호를 다운로드 제어 회로(51)에 출력하고, 카운트값을 리셋한다. 다운로드 제어 회로(51)는 소정 레벨의 카운트 종료 신호에 응답하여 내부 플래시 ROM(10)에 대한 다음 액세스를 할 수 있다는 것을 검지한다.

그런데, 다운로드 제어 회로(51)는 카운터(55)의 카운트를 스타트시킴과 함께, 어드레스 레지스터(53)의 어드레스를 갱신(예를 들면, 카운트업)하고, 외부 시리얼 플래시 ROM(30)에 다음으로 액세스하는 어드레스를 어드레스 레지스터(53)에 세트한다(S24). 그리고, 다운로드 제어 회로(51)는, 어드레스 레지스터(53)에 세트된 어드레스가 내부 플래시 ROM(10)의 최종 어드레스 설정값 이하인지의 여부를 판정한다(S26). 이 최종 어드레스 설정값은 다운로드 제어 회로(51)에 불휘발성 메모리로서 미리 기억해 두어도 되고, 외부 시리얼 플래시 ROM(30)의 소정 어드레스 영역으로부터 판독하여 휘발성 메모리에 기억시켜도 된다. 최종 어드레스 설정값 이하인 경우에는, 제1 커맨드 레지스터(61)로부터 순차적으로 판독용 커맨드 세트를 판독하고, 판독한 커맨드 세트 및 어드레스 레지스터(53)에 세트된 어드레스를 순차적으로 외부 인터페이스(40)를 통하여 외부 시리얼 플래시 ROM(30)에 출력한다(S28). 이에 의해, 외부 시리얼 플래시 ROM(30)은, 입력된 어드레스의 데이터를 출력한다. 외부 시리얼 플래시 ROM(30)으로부터 출력된 데이터는 외부 인터페이스(40)를 통하여 다운로드 제어 회로(51)에 판독되고, 데이터 레지스터(54)에 일시적으로 기억된다(S30).

그리고, 다운로드 제어 회로(51)는 카운터(55)로부터의 카운트 종료 신호가 출력되는 것을 대기한다(S32). 카운트 종료 신호가 출력되면 단계 S20으로 진행하여, 다운로드 제어 회로(51)는 제2 커맨드 레지스터(62)로부터 순차적으로 기입용 커맨드 세트를 판독하고, 판독한 커맨드 세트, 어드레스 레지스터(53)에 세트된 어드레스 및 데이터 레지스터(54)에 일시적으로 기억된 데이터를 순차적으로 플립플롭(52) 및 내부 인터페이스(70)를 통하여 내부 플래시 ROM(10)에 출력한다.

이후, 단계 S20으로부터 단계 S32까지를 반복하고, 어드레스 레지스터(53)에 세트된 어드레스가 내부 플래시 ROM(10)의 최종 어드레스 설정값을 초과하면, 다운로드 제어 회로(51)는 카운터(55)로부터의 카운트 종료 신호가 출력되는 것을 대기하고(S34), 베리파이의 단계로 진행한다.

또한, 제2 커맨드 레지스터(62)의 커맨드 세트, 카운트 설정값, 최종 어드레스 설정값을 휘발성 메모리에 기억시키는 경우에는, 단계 S10 후, 시리얼 플래시 ROM(30)의 소정 어드레스(예를 들면, 내부 플래시 ROM(10)의 최종 어드레스보다 큰 어드레스 영역)로부터 판독하여 기억시킨다. 그리고, 단계 S12로 진행하면 된다.

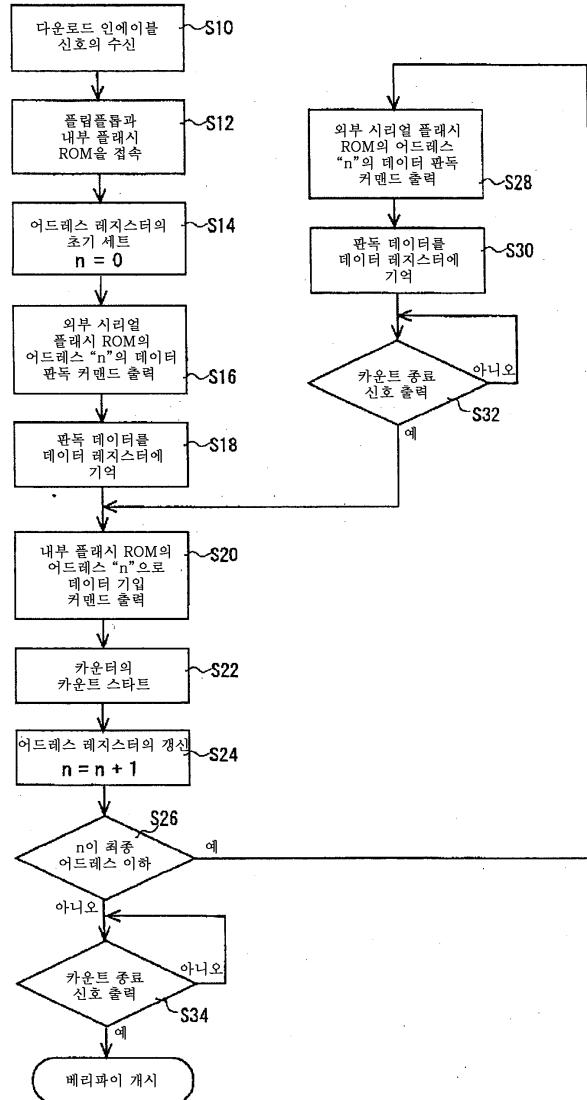

베리파이에서는, 우선, 다운로드 제어 회로(51)는, 외부 시리얼 플래시 ROM(30)에 최초로 액세스하는 어드레스(예를 들면, "0")를 어드레스 레지스터(53)에 세트한다(S40). 제1 커맨드 레지스터(61)로부터 순차적으로 판독용 커맨드 세트를 판독하고, 판독한 커맨드 세트 및 어드레스 레지스터(53)에 세트된 어드레스를 순차적으로 외부 인터페이스(40)를 통하여 외부 시리얼 플래시 ROM(30)에 출력한다(S42). 이에 의해, 외부 시리얼 플래시 ROM(30)은, 입력된 어드레스의 데이터를 출력한다. 외부 시리얼 플래시 ROM(30)으로부터 출력된 데이터는 외부 인터페이스(40)를 통하여 다운로드 제어 회로(51)에 판독되고, 데이터 레지스터(54)에 일시적으로 기억된다(S44).

다음으로, 다운로드 제어 회로(51)는 제2 커맨드 레지스터(62)로부터 순차적으로 판독용 커맨드 세트를 판독하고, 판독한 커맨드 세트, 어드레스 레지스터(53)에 세트된 어드레스를 순차적으로 플립플롭(52) 및 내부 인터페이스(70)를 통하여 내부 플래시 ROM(10)에 출력한다(S46). 이에 의해, 내부 플래시 ROM(10)은, 입력된 어드레스의 데이터를 출력한다. 내부 플래시 ROM(10)으로부터 출력된 데이터는 내부 인터페이스(70)를 통하여 플립플롭(52)에 판독된다(S48).

다운로드 제어 회로(51)는, 플립플롭(52)에 기억된 데이터와 데이터 레지스터(54)에 기억된 데이터를 비교한다(S50).

양 데이터가 일치하지 않는 경우에는, 다운로드 제어 회로(51)는 다운로드 에러 신호를 출력한다.

양 데이터가 일치하는 경우에는, 다운로드 제어 회로(51)는 어드레스 레지스터(53)의 어드레스를 갱신(예를 들면, 카운트 업)하고, 외부 시리얼 플래시 ROM(30)에 다음으로 액세스하는 어드레스를 어드레스 레지스터(53)에 세트한다(S52). 그리고, 다운로드 제어 회로(51)는, 어드레스 레지스터(53)에 세트된 어드레스가 내부 플래시 ROM(10)의 최종 어드레스 설정 값 이하인지의 여부를 판정한다(S54). 최종 어드레스 설정 값 이하인 경우에는 단계 S42로 되돌아가 단계 S42~S54를 반복하고, 최종 어드레스 설정 값보다 큰 경우에는 베리파이를 종료한다.

베리파이 후, 내부 인터페이스(70)는 CPU(20)와 내부 플래시 ROM(10)을 접속하고, 다운로드 회로(50)는 CPU(20)의 동작을 슬립 상태로부터 개방한다(S56). 그리고, 다운로드 회로(50)는 기입의 종료를 나타내는 다운로드 종료 신호를 외부 단자를 통하여 외부에 송신한다.

이와 같이 하여, 내부 플래시 ROM(10)에는, CPU(20)가 주변 기기의 각 회로의 제어를 행하기 위한 동작 프로그램과, CPU(20)가 동작 프로그램의 갱신을 행하기 위한 업데이트용 프로그램의 2 종류가 기입된다. 따라서, CPU(20)는 내부 인터페이스(70)를 통하여 내부 플래시 ROM(10)에 기입된 동작 프로그램을 판독하고, 그에 따라 각 회로의 제어를 행한다. 예를 들면 주변 기기가 CD-ROM 드라이브 장치인 경우에는, 레이저를 조사하기 위한 광업을 광 디스크의 소정 위치로 이동시키거나, 레이저의 반사광을 판독하여 광 디스크에 기억된 데이터를 판독하기도 한다. 한편, 동작 프로그램의 갱신 시에는, CPU(20)는 업데이트용 프로그램에 따라 동작 프로그램의 데이터 재기입을 행할 수 있게 된다.

이상, 상술한 바와 같이, 본 실시예에 따르면, 이하에 기재하는 효과가 얻어지게 된다.

(1) 본 실시예에서는, CPU를 통하지 않고 다운로드 제어 회로의 전용 회로에서 외부 시리얼 플래시 ROM에 기억된 초기 데이터를 플래시 ROM에 복사하도록 기입하기 때문에, 다운로드의 스피드가 빠르다. 동작 프로그램을 기입하기 위한 업데이트용 프로그램을 기억한 마스크 ROM을 별도로 설치할 필요도 없어, 제어 장치(100)의 회로 면적의 증대를 억제할 수 있다. 즉, 시리얼 내부 플래시 ROM(10) 및 플래시 ROM(30)에 액세스하는 데 필요한 커맨드 세트만 준비하면 된다. 또한, 내부 플래시 ROM(10) 단체의 상태에서 미리 초기 데이터를 기입해 놓고, 이것을 실장하는 등의 작업도 불필요하므로, 제조 코스트의 증대도 억제할 수 있다.

(2) 본 실시예에서는, 다운로드 제어 회로의 전용 회로에서 외부 시리얼 플래시 ROM에 기억된 초기 데이터를 플래시 ROM에 복사하도록 기입하기 때문에, 초기 데이터를 플래시 ROM에 기입할 때, 초기 데이터를 공급하는 외부의 호스트 컴퓨터를 불필요하게 하는 것이 가능하다.

(3) 본 실시예에서는, 내부 플래시 ROM(10)에의 기입 동작을 유지하기 위해 플립플롭(52)이 설치되고, 기입 시간의 관리는 카운터(55)가 행하고 있기 때문에, 내부 플래시 ROM(10)에의 데이터의 기입 중에 다음 기입 데이터를 외부 시리얼 플래시 ROM(30)으로부터 판독하여 놓을 수 있기 때문에, 다운로드의 시간을 단축할 수 있다.

(4) 본 실시예에서는, 내부 플래시 ROM(10)에 미리 초기 데이터를 기억해 둘 필요가 없기 때문에, 예를 들면 제어 장치(100)에 일체적으로 집적하는 것도 가능하고, 이 경우에는 주변 기기 전체로서의 회로 면적을 저감할 수 있다.

또한, 본 발명의 실시예는 상기 실시예에 한정되는 것이 아니고, 다음과 같이 변경하여도 된다.

본 실시예에서는, 외부 플래시 ROM(30)은 시리얼 메모리이지만, 이에 한하는 것이 아니고, 어드레스 단자 및 데이터 단자를 복수 구비하는 메모리이어도 된다.

본 실시예에서는, 내부 플래시 ROM(10)에의 기입마다 필요하게 되는 1 어드레스당 데이터 기입 시간의 관리는 카운터(55)에서 행하고 있지만, 다운로드 제어 회로(51)가 기입이 충분하게 행해지는 시간만큼 대기하고, 내부 플래시 ROM(10)에 다음 기입 데이터를 보내도록 하여도 된다. 혹은, 다운로드 제어 회로(51)가 내부 플래시 ROM(10)의 기입 종료를 톤글 비트나 폴링으로 검지하도록 하여도 된다.

본 실시예에서는, 내부 플래시 ROM(10)에 다운로드하는 초기 데이터를 외부 시리얼 플래시 ROM(30)으로부터 판독하는 구성으로 하고 있기 때문에, 제어 장치(100)가 다운로드 시에 필요로 하는 외부 단자 수를 적게 할 수 있다. 이 때문에, 이

러한 다운로드 시에 사용하는 외부 단자를, 다운로드 시 이외에 제어 장치(100)가 외부와의 신호의 교환에 사용하는 통상 단자와 공용시킴으로써, 외부 단자와 통상 단자를 합계한 총 수를 늘리지 않고 구성할 수 있다. 또한, 외부 시리얼 플래시 ROM(30)의 전원을, 제어 장치(100)로부터 외부 단자를 통하여 공급함으로써, 외부 시리얼 플래시 ROM(30)을 외부 인터페이스(40)에 삽입하여 다운로드 인에이블 신호를 송신하는 것으로 다운로드시키는 것도 가능하다.

본 실시예에서는, 1 어드레스 단위로 외부 시리얼 플래시 ROM(30)으로부터 데이터를 판독하고, 1 어드레스 단위의 데이터를 내부 플래시 ROM(10)에 기입하고 있다. 그러나, 복수의 소정 어드레스 단위로 외부 시리얼 플래시 ROM(30)으로부터 데이터를 판독하고, 버스트 모드를 이용하는 등 하여, 이들 복수의 소정 어드레스 단위의 데이터를 내부 플래시 ROM(10)에 기입하여도 된다. 이 경우, 데이터 레지스터(54)에는 복수 어드레스에 따른 복수의 데이터를 기억할 수 있도록 하고, 다운로드 제어 회로(51)는 버스트 모드에 따른 커맨드 세트 등을 플립플롭에 출력하도록 한다.

본 실시예에서는, 마이크로컴퓨터에 소정의 동작 제어를 행하게 하는 동작 프로그램을 기억하기 위한 전기적으로 재기입 가능한 불휘발성 메모리로서 플래시 ROM을 설명하고 있지만, 데이터의 기입이 가능하면, 그 밖의 PROM을 채용하여도 된다.

본 실시예에서는, 내부 플래시 ROM(10)은 제어 장치(100)에 일체적으로 집적해 두어도 되고, 혹은 패키징 시에 복수의 반도체 칩을 1개로 집적하는 멀티칩 패키지로 하여도 된다.

본 실시예에서, 주변 기기는 CD-ROM 드라이브 장치에 한하지 않고, 컴퓨터와 접속하여 데이터의 교환이 가능하면 어떠한 기기이어도 된다. 예를 들면 MD나 DVD-RAM 등의 광 디스크 드라이브 장치나, MO와 같은 광 자기 디스크 드라이브 장치, 하드디스크와 같은 자기 디스크 드라이브 장치 등이어도 된다. 또한, 이러한 정보 기억 장치에 한하지 않고, 예를 들면 프린터와 같은 출력 장치나 스캐너와 같은 판독 장치, 모뎀이나 LAN과 같은 통신 장치 등이어도 된다.

### **발명의 효과**

본 발명에 따르면, 회로 면적의 증대 및 제조 코스트의 증대를 억제하면서 전기적으로 재기입 가능한 내부 불휘발성 메모리에 CPU의 동작 프로그램의 기입을 행할 수 있다.

### **도면의 간단한 설명**

도 1은 본 발명의 일 실시예를 도시하는 블록도.

도 2는 본 실시예에서의 초기 데이터의 기입 수순.

도 3은 본 실시예에서의 초기 데이터의 기입 수순.

<도면의 주요 부분에 대한 부호의 설명>

10 : 내부 플래시 ROM

20 : 마이크로컴퓨터(CPU)

30 : 외부 시리얼 플래시 ROM

40 : 외부 인터페이스

50 : 다운로드 회로

51 : 다운로드 제어 회로

52 : 플립플롭

53 : 어드레스 레지스터

54 : 데이터 레지스터

55 : 카운터

61 : 제1 커맨드 레지스터

62 : 제2 커맨드 레지스터

70 : 내부 인터페이스

100 : 제어 장치

도면

도면1

## 도면2

도면3