(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6271812号

(P6271812)

(45) 発行日 平成30年1月31日(2018.1.31)

(24) 登録日 平成30年1月12日(2018.1.12)

(51) Int.Cl.

F 1

|            |           |      |       |      |

|------------|-----------|------|-------|------|

| GO6F 12/10 | (2016.01) | GO6F | 12/10 | 505B |

| GO6F 12/08 | (2016.01) | GO6F | 12/08 | 559D |

| GO6F 12/02 | (2006.01) | GO6F | 12/02 | 570K |

| GO6F 12/00 | (2006.01) | GO6F | 12/02 | 570J |

| GO6T 1/20  | (2006.01) | GO6F | 12/00 | 580  |

請求項の数 14 (全 25 頁) 最終頁に続く

|               |                               |

|---------------|-------------------------------|

| (21) 出願番号     | 特願2017-517240 (P2017-517240)  |

| (86) (22) 出願日 | 平成27年9月16日 (2015.9.16)        |

| (65) 公表番号     | 特表2017-535848 (P2017-535848A) |

| (43) 公表日      | 平成29年11月30日 (2017.11.30)      |

| (86) 國際出願番号   | PCT/US2015/050465             |

| (87) 國際公開番号   | W02016/053628                 |

| (87) 國際公開日    | 平成28年4月7日 (2016.4.7)          |

| 審査請求日         | 平成29年11月16日 (2017.11.16)      |

| (31) 優先権主張番号  | 14/504,047                    |

| (32) 優先日      | 平成26年10月1日 (2014.10.1)        |

| (33) 優先権主張国   | 米国(US)                        |

早期審査対象出願

|           |                                                                                                                |

|-----------|----------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 595020643<br>クアアルコム・インコーポレイテッド<br>QUALCOMM INCORPORATED<br>アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775 |

| (74) 代理人  | 100108855<br>弁理士 蔵田 昌俊                                                                                         |

| (74) 代理人  | 100109830<br>弁理士 福原 淑弘                                                                                         |

| (74) 代理人  | 100158805<br>弁理士 井関 守三                                                                                         |

| (74) 代理人  | 100112807<br>弁理士 岡田 貴志                                                                                         |

最終頁に続く

(54) 【発明の名称】透過的画素フォーマット変換器

## (57) 【特許請求の範囲】

## 【請求項 1】

画素処理のための方法であって、

第1のデータフォーマットをサポートする少なくとも1つのプロセッサから、第1のデータバッファに保存されたデータに関する要求を、グラフィックス処理ユニット(GPU)によって受信することと、ここでにおいて、前記要求は、前記データの仮想アドレスを備える。

前記第1のデータフォーマットと関連する仮想アドレス範囲内にある、前記データの前記仮想アドレスに少なくとも一部基づいて、前記少なくとも1つのプロセッサによってサポートされる前記第1のデータフォーマットをインジケートする1つまたは複数のカラービットを、前記GPUのメモリ管理ユニット(MMU)によって、決定することと、

前記1つまたは複数のカラービットに連結される前記データの前記仮想アドレスで構成される、翻訳されたアドレスを、前記MMUによって、決定することと、

第2のデータフォーマットにある前記データを、前記翻訳されたアドレスにおける前記仮想アドレスに対応する物理アドレスで前記第1のデータバッファから、透過的フォーマット変換器(TFC)によって、取得することと、

前記取得されたデータを前記第2のデータフォーマットから、前記翻訳されたアドレスにおける前記1つまたは複数のカラービットによってインジケートされる前記第1のデータフォーマットへ、前記TFCによって、変換することと、

前記第1のデータフォーマットにある前記変換されたデータを、前記少なくとも1つの

10

20

プロセッサによってアクセス可能である第2のデータバッファに、前記TFCによって、保存することと

を備える、方法。

【請求項2】

前記第1のデータフォーマットと関連する前記仮想アドレス範囲内にある、前記データの前記仮想アドレスに少なくとも一部基づいて、前記少なくとも1つのプロセッサによってサポートされる前記第1のデータフォーマットをインジケートする前記1つまたは複数のカラービットを決定することは、

前記仮想アドレスに少なくとも一部基づいて中間物理アドレスを、第1のレベルページテーブルを使用する前記MMUによって、決定することと、

10

前記中間物理アドレスに少なくとも一部基づいて前記翻訳されたアドレスを、第2のレベルページテーブルを使用する前記MMUによって、決定することと

をさらに備える、請求項1に記載の方法。

【請求項3】

1つまたは複数のページテーブルのカーネルアドレス空間部分に少なくとも一部基づいて前記物理アドレスを、前記TFCによって、決定することをさらに備える、請求項1に記載の方法。

【請求項4】

前記第2のデータバッファは前記少なくとも1つのプロセッサのためのキャッシュを備える、請求項1に記載の方法。

20

【請求項5】

前記データは画素データを備え、

前記第1のデータフォーマットは第1の画素フォーマットを備え、

前記第2のデータフォーマットは第2の画素フォーマットを備える、請求項1に記載の方法。

【請求項6】

前記第1のデータフォーマットにある第2のデータを、前記少なくとも1つのプロセッサから前記TFCによって、受け取ることと、

前記第2のデータを前記第1のデータフォーマットから前記第2のデータフォーマットへ、前記TFCによって、変換することと、

30

前記第2のデータフォーマットにある前記変換されたデータを前記第1のデータバッファに、前記TFCによって、保存することと

をさらに備える、請求項1に記載の方法。

【請求項7】

第1のデータバッファと、

第2のデータバッファと、

第1のデータフォーマットをサポートする少なくとも1つのプロセッサと、

前記第1のデータバッファに保存されたデータに関する、前記少なくとも1つのプロセッサによる要求を受信すること、ここにおいて、前記要求は、前記データの仮想アドレスを備える、

40

を行うように構成されるグラフィックス処理ユニット(GPU)と、

前記第1のデータフォーマットと関連する仮想アドレス範囲内にある、前記データの前記仮想アドレスに少なくとも一部基づいて、前記少なくとも1つのプロセッサによってサポートされる前記第1のデータフォーマットをインジケートする1つまたは複数のカラービットを決定することと、

前記1つまたは複数のカラービットに連結される前記データの前記仮想アドレスで構成される、翻訳されたアドレスを決定することと、

前記翻訳されたアドレスに少なくとも一部基づいて前記仮想アドレスに対応する物理アドレスを決定することと

を行うように構成される前記GPUのメモリ管理ユニット(MMU)と、

50

第2のデータフォーマットにある前記データを、前記翻訳されたアドレスにおける前記仮想アドレスに対応する物理アドレスで前記第1のデータバッファから取得すること

、

前記取得されたデータを前記第2のデータフォーマットから、前記翻訳されたアドレスにおける前記1つまたは複数のカラービットによってインジケートされる前記第1のデータフォーマットへ変換することと、

前記第1のデータフォーマットにある前記変換されたデータを、前記少なくとも1つのプロセッサによってアクセス可能である前記第2のデータバッファに保存することと

を行うように構成される、前記G P Uの透過的フォーマット変換器(T F C)と

を備える、計算デバイス。

10

**【請求項8】**

前記M M Uは、

第1のレベルページテーブルを使用し、前記仮想アドレスに少なくとも一部基づいて中間物理アドレスを決定し、

第2のレベルページテーブルを使用し、前記中間物理アドレスに少なくとも一部基づいて前記翻訳されたアドレスを決定する

ようにさらに構成される、請求項7に記載の計算デバイス。

**【請求項9】**

前記T F Cは、1つまたは複数のページテーブルのカーネルアドレス空間部分に少なくとも一部基づいて前記物理アドレスを決定するようにさらに構成される、請求項7に記載の計算デバイス。

20

**【請求項10】**

前記第2のデータバッファは前記少なくとも1つのプロセッサのためのキャッシュを備える、請求項7に記載の計算デバイス。

**【請求項11】**

前記データは画素データを備え、

前記第1のデータフォーマットは第1の画素フォーマットを備え、

前記第2のデータフォーマットは第2の画素フォーマットを備える、請求項7に記載の計算デバイス。

**【請求項12】**

30

前記T F Cは、

前記第1のデータフォーマットにある第2のデータを前記少なくとも1つのプロセッサから受け取り、

前記第2のデータを前記第1のデータフォーマットから前記第2のデータフォーマットへ変換し、

前記第2のデータフォーマットにある前記変換されたデータを前記第1のデータバッファに保存する

ようにさらに構成される、請求項7に記載の計算デバイス。

**【請求項13】**

第1のデータバッファに保存されたデータに関する第1のデータフォーマットをサポートする少なくとも1つのプロセッサによる要求を受信するための手段と、ここにおいて、前記要求は、前記データの仮想アドレスを備える、

40

前記第1のデータフォーマットと関連する仮想アドレス範囲内にある、前記データの前記仮想アドレスに少なくとも一部基づいて、前記少なくとも1つのプロセッサによってサポートされる前記第1のデータフォーマットをインジケートする1つまたは複数のカラービットを決定するための手段と、

前記1つまたは複数のカラービットに連結される前記データの前記仮想アドレスで構成される、翻訳されたアドレスを決定するための手段と、

第2のデータフォーマットにある前記データを、前記翻訳されたアドレスにおける前記仮想アドレスに対応する物理アドレスで前記第1のデータバッファから取得するための手

50

段と、

前記取得されたデータを前記第2のデータフォーマットから、前記翻訳されたアドレスにおける前記1つまたは複数のカラービットによってインジケートされる前記第1のデータフォーマットへ変換するための手段と、

前記第1のデータフォーマットにある前記変換されたデータを、前記少なくとも1つのプロセッサによってアクセス可能である第2のデータバッファに保存するための手段とを備える、装置。

【請求項14】

第1のデータバッファに保存されたデータに関する要求を受信することと、ここにおいて、前記要求は、前記データの仮想アドレスを備える、

10

前記第1のデータフォーマットと関連する仮想アドレス範囲内にある、前記データの前記仮想アドレスに少なくとも一部基づいて、前記少なくとも1つのプロセッサによってサポートされる前記第1のデータフォーマットをインジケートする1つまたは複数のカラービットを決定することと、

前記1つまたは複数のカラービットに連結される前記データの前記仮想アドレスで構成される、翻訳されたアドレスを決定することと、

第2のデータフォーマットにある前記データを、前記翻訳されたアドレスにおける前記仮想アドレスに対応する物理アドレスで前記第1のデータバッファから取得することと、

前記取得されたデータを前記第2のデータフォーマットから、前記翻訳されたアドレスにおける前記1つまたは複数のカラービットによってインジケートされる前記第1のデータフォーマットへ変換することと、

20

前記第1のデータフォーマットにある前記変換されたデータを、前記少なくとも1つのプロセッサによってアクセス可能である第2のデータバッファに保存することと

を、プログラマブルプロセッサにさせるための命令を備える、非一時的なコンピュータ可読媒体。

【発明の詳細な説明】

【技術分野】

【0001】

[0001] 本開示は、透過的画素フォーマット変換器に関する。

【0002】

[0002] グラフィックス画像またはビデオのフレームのようなグラフィックスデータは、複数の画素から成り立ち得る。グラフィックスデータの画素に関する情報のような画素データは、1画素のデータに関連付けられたメモリのビットの数を規定し得、またこの画素のデータ内のカラー成分の順序を規定し得る、指定された画素フォーマットに従って配列され得る。指定された画素フォーマットに従ってメモリに配列される画素データはこの画素フォーマットに従って圧縮され得、またこの画素フォーマットに従ってこのメモリの複数のメモリロケーションに配列され得る。一般に、画素フォーマットは線形画素フォーマットまたはタイルベース画素フォーマットに分類される。

30

【発明の概要】

【0003】

[0003] 一般に、本開示は、異なる画素フォーマット相互間で透過的に変換する透過的フォーマット変換器(TFC)に関し、TFCがグラフィックスデータの基底(underlying)画素フォーマットにかかわらずに、処理コアによってサポートされた画素フォーマットに従うグラフィックスデータのビュー(view)をもつ処理コアを提供し得る。TFCは処理コアが、処理コアによってサポートされた画素フォーマットに従ってグラフィックスデータが整列されるようにグラフィックスデータを扱うことを可能にし得る。

40

【0004】

[0004] 一態様において、本開示は画素処理のための方法に向けられている。この方法は、第1のデータバッファに保存されたデータに関する、少なくとも1つのプロセッサによる要求が第1のデータフォーマットにあるこのデータに関する要求を示すものであると

50

、透過的フォーマット変換器(TFC)によって、決定することを含み得る。方法は、第1のデータバッファに保存されたデータに関する要求に少なくとも一部基づいて、第2のデータフォーマットにあるこのデータを第1のデータバッファから、TFCによって、取得することをさらに含み得る。方法は、取得されたデータを第2のデータフォーマットから第1のデータフォーマットへ、TFCによって、変換することをさらに含み得る。方法は、第1のデータフォーマットにある変換されたデータを、少なくとも1つのプロセッサによってアクセス可能である第2のデータバッファに、TFCによって、保存することをさらに含み得る。

**【0005】**

[0005] 別の態様において、本開示は計算デバイスに向けられている。この計算デバイスは、第1のデータバッファを含み得る。計算デバイスは、第2のデータバッファをさらに含み得る。計算デバイスは、少なくとも1つのプロセッサをさらに含み得る。計算デバイスは、第1のデータバッファに保存されたデータに関する、少なくとも1つのプロセッサによる要求が第1のデータフォーマットにあるこのデータに関する要求を示すものであると決定し、第1のデータバッファに保存されたデータに関する要求に少なくとも一部基づいて、第2のデータフォーマットにあるこのデータを第1のデータバッファから取得し、取得されたデータを第2のデータフォーマットから第1のデータフォーマットへ変換し、第1のデータフォーマットにある変換されたデータを、少なくとも1つのプロセッサによってアクセス可能である第2のデータバッファに保存するように構成される透過的フォーマット変換器をさらに含み得る。

**【0006】**

[0006] 別の態様において、本開示は装置に向けられている。この装置は、第1のデータバッファに保存されたデータに関する、少なくとも1つのプロセッサによる要求が第1のデータフォーマットにあるこのデータに関する要求を示すものであると決定するための手段を含み得る。装置は、第1のデータバッファに保存されたデータに関する要求に少なくとも一部基づいて、第2のデータフォーマットにあるこのデータを第1のデータバッファから取得するための手段をさらに含み得る。装置は、取得されたデータを第2のデータフォーマットから第1のデータフォーマットへ変換するための手段をさらに含み得る。装置は、第1のデータフォーマットにある変換されたデータを、少なくとも1つのプロセッサによってアクセス可能である第2のデータバッファに保存するための手段をさらに含み得る。

**【0007】**

[0007] 別の態様において、本開示は命令を有するコンピュータ可読媒体に向けられている。この命令は、第1のデータバッファに保存されたデータに関する、少なくとも1つのプロセッサによる要求が第1のデータフォーマットにあるこのデータに関する要求を示すものであると、透過的フォーマット変換器(TFC)によって、決定することと、第1のデータバッファに保存されたデータに関する要求に少なくとも一部基づいて、第2のデータフォーマットにあるデータを第1のデータバッファから、TFCによって、取得することと、取得されたデータを第2のデータフォーマットから第1のデータフォーマットへ、TFCによって、変換することと、第1のデータフォーマットにある変換されたデータを、少なくとも1つのプロセッサによってアクセス可能である第2のデータバッファに、TFCによって、保存することとをプログラマブルプロセッサにさせる。

**【0008】**

[0008] 本開示の1つまたは複数の態様の詳細は、添付図面および以下の説明において記述される。本開示で説明される技術の他の特徴、目的、および利点は、説明、図面、および特許請求の範囲から明らかになる。

**【図面の簡単な説明】**

**【0009】**

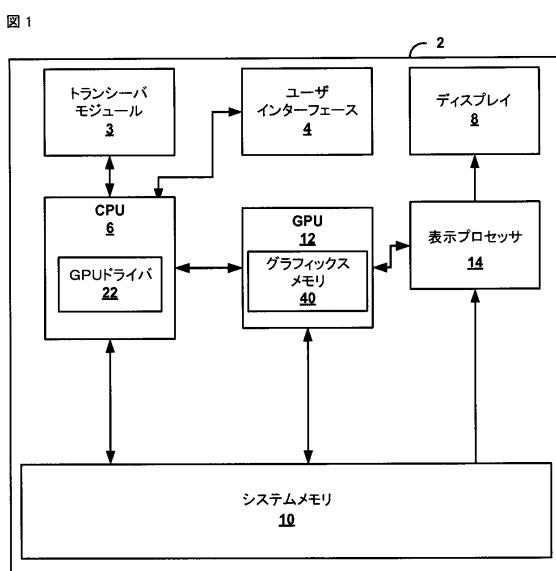

**【図1】**図1は、本開示の1つまたは複数の態様を実施するように構成され得る例示的な計算デバイスを例示するブロック図である。

10

20

30

40

50

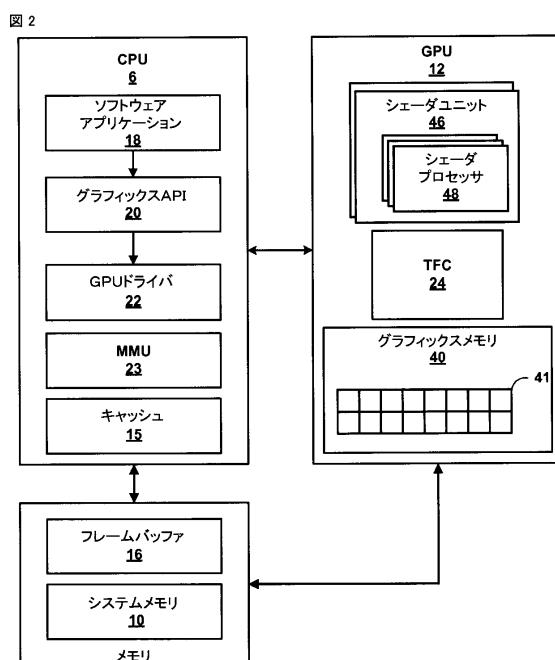

【図2】図2は、さらに詳細に図1のプロセッサ、GPU、およびシステムメモリの例示的な実施形態を例示するブロック図である。

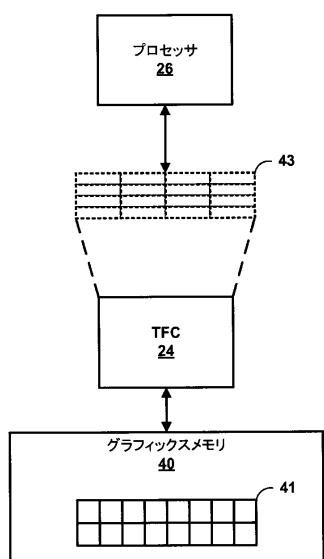

【図3】図3は、図2のTFCの例示的な機能を例示する概念図である。

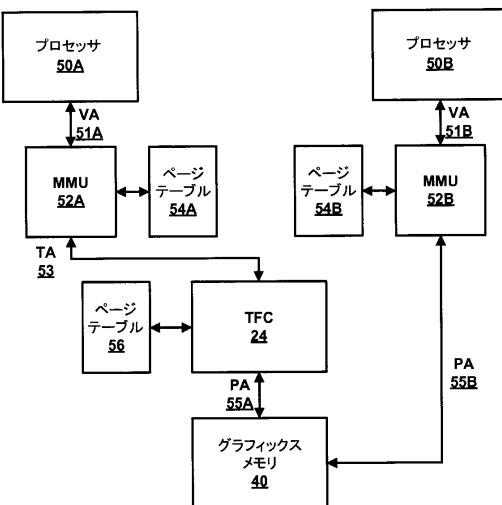

【図4】図4は、さらに詳細に図2のTFCの例示的な実施形態を例示するブロック図である。

【図5】図5は、図4の翻訳されたアドレスの例示的なフォーマットを例示するブロック図である。

【図6】図6は、さらに詳細に図2のTFCの例示的な実施形態を例示するブロック図である。

【図7】図7は、例示的な仮想アドレスを例示的な物理アドレスに翻訳するために2レベルページテーブルマッピングを利用する図2のTFCを例示するブロック図である。

【図8】図8は、透過的に画素フォーマットを変換するためのプロセスを例示するフローチャートである。

【発明を実施するための形態】

【0010】

[0017] 一般に、本開示は、異なる画素フォーマット相互間で透過的に変換する透過的フォーマット変換器(TFC)に関し、TFCが画素データのビュー(view)を提供するよう 10 にし得る。画素データは様々な異なる画素フォーマットで保存され得る。ハードウェア設計者は、ハードウェア設計者によって設計されたハードウェアによって周知の標準画素フォーマットよりも効率的に処理され得る新たな独自画素フォーマットを作成することがよくある。例えば、タイルベース画素フォーマットが、線形画素フォーマットの代わりに、増大されたメモリ効率および効率的帯域利用効率のために作成され得る。

【0011】

[0018] しかしながら、画素データを操作するソフトウェアアプリケーションの開発者は、網羅的な様々な画素フォーマットを実施する代わりに、僅かな周知画素フォーマットだけについてのサポートを実施することがよくある。加えて、ハードウェア設計者によって作成されたタイルベース画素フォーマットは独自のものであって、ソフトウェア開発者がそれらタイルベース画素フォーマットの知識を持たないことがある。いくつかの例において、そのようなソフトウェアアプリケーションの稼働するオペレーティングシステムはまた、広い様々な画素フォーマットを網羅してサポートし得ない。既存のオペレーティングシステムは新規ハードウェア上で稼働するように適応されることがよくあるため、オペレーティングシステムがこうした新規ハードウェア上で実施された新規作成の画素フォーマットを継続的にサポートすることが可能でないことがよくある。

【0012】

[0019] 本開示のTFCは、第1の画素フォーマットをサポートするプロセッサが、このプロセッサによってサポートされる第1の画素フォーマットに従って代わりに配列されたものであるかのように、第2のフォーマットに従って配列された画素データを、TFCを介して、見れるよう画素フォーマット間で透過的に変換するように構成され得る。本開示の態様に従って、TFCは、第1のデータバッファに保存されたデータに関する、少なくとも1つのプロセッサによる要求が第1のデータフォーマットにあるこのデータに関する要求を示すものであると決定するように構成され得る。TFCは、第1のデータバッファに保存されたデータに関する要求に少なくとも一部基づいて、第2のデータフォーマットにあるこのデータを第1のデータバッファから取得するようにさらに構成され得る。TFCは、取得されたデータを第2のデータフォーマットから第1のデータフォーマットへ変換するようにさらに構成され得る。TFCは、第1のデータフォーマットにある変換されたデータを、少なくとも1つのプロセッサによってアクセス可能である第2のデータバッファに保存するようにさらに構成され得る。

【0013】

[0020] 図1は、本開示の1つまたは複数の態様を実施するように構成され得る例示的な計算デバイスを例示するブロック図である。図1に示されるように、計算デバイス2は

10

20

30

40

50

、ビデオデバイス、メディアプレーヤ、セットトップボックス、モバイル電話およびいわゆるスマートフォンのようなワイヤレスハンドセット、携帯情報端末（PDA s）、デスクトップコンピュータ、ラップトップコンピュータ、ゲーミングコンソール、ビデオ会議ユニット、タブレット計算デバイス等を、限定されずに含む計算デバイスであり得る。図1の例では、計算デバイス2は、中央処理装置（CPU）6、システムメモリ10、およびGPU12を含み得る。計算デバイス2はまた、ディスプレイプロセッサ14、トランシーバモジュール3、ユーザインタフェース4、およびディスプレイ8を含み得る。トランシーバモジュール3およびディスプレイプロセッサ14は両方ともに、CPU6および／またはGPU12として同じ集積回路（IC）の一部であることができ、両方ともにCPU6および／またはGPU12を含むICまたは複数のICの外部に存在することができ、またはCPU6および／またはGPU12を含むICで形成され得る。10

#### 【0014】

[0021] 計算デバイス2は、明確さのために図1に示されない追加のモジュールまたはユニットを含み得る。例えば、計算デバイス2は、どちらも図1に示されない、スピーカおよびマイクロホンを、計算デバイス2がモバイルワイヤレス電話である例において、または計算デバイス2がメディアプレーヤであるスピーカにおいて電話通信を果たすために含み得る。計算デバイス2はまた、ビデオカメラを含み得る。さらに、図2に示される様々なモジュールおよびユニットは、計算デバイス2の全ての例において必要とは限らない。例えば、ユーザインタフェース4およびディスプレイ8は、計算デバイス2が、外部ユーザインタフェースまたはディスプレイとインタフェースするように装備されるデスクトップコンピュータまたは他のコンピュータである例において計算デバイス2の外部にあり得る。20

#### 【0015】

[0022] ユーザインタフェース4の例は、トラックボール、マウス、キーボード、および他のタイプの入力デバイスを、限定されずに含む。ユーザインタフェース4は、タッチスクリーンであることもでき、ディスプレイ8の一部として組み込まれ得る。トランシーバモジュール3は、計算デバイス2と他のデバイスまたはネットワークとの間で無線または有線通信を可能にする回路を含み得る。トランシーバモジュール3は、変調器、復調器、増幅器、並びに有線または無線通信のための他のそうした回路を含み得る。30

#### 【0016】

[0023] 図6は、実行のためにコンピュータプログラムの命令を処理するように構成される中央処理装置（CPU）のような、マイクロプロセッサであり得る。プロセッサ6は、計算デバイス2の動作を制御する汎用、または専用プロセッサを備え得る。ユーザは、1つまたは複数のソフトウェアアプリケーションをプロセッサ6に実行させるために計算デバイス2に入力を提供し得る。プロセッサ6上で実行するソフトウェアアプリケーションは、例えば、オペレーティングシステム、ワードプロセッサアプリケーション、電子メールアプリケーション、スプレッドシートアプリケーション、メディアプレーヤアプリケーション、ビデオゲームアプリケーション、グラフィカルユーザインタフェースアプリケーションまたは他のプログラムを含み得る。加えて、プロセッサ6は、GPU12の動作を制御するためにGPUドライバ22を実行し得る。ユーザは、キーボード、マウス、マイクロフォン、タッチパッドまたはユーザインタフェース4を介して計算デバイス2に結合される他の入力デバイスのような1つまたは複数の入力デバイス（図示されない）を介して入力を計算デバイス2に提供し得る。40

#### 【0017】

[0024] プロセッサ6上で実行するソフトウェアアプリケーションは、ディスプレイ8に対するグラフィックスデータのレンダリングをプロセッサ6に命じる1つまたは複数のグラフィックスレンダリング命令を含み得る。いくつかの例において、ソフトウェア命令は、グラフィックスアプリケーションプログラミングインタフェース（API）、例えば、オープングラフィックスライブラリ（OpenGL（登録商標））API、オープングラフィ

10

20

30

40

50

ツクスライブラリ埋め込みシステム (Open Graphics Library Embedded Systems) (OpenGL ES) API、ダイレクト3D API、X3D API、RenderMan API、WebGL API、オープンコンピューティング言語(OpenCL(トレードマーク))または任意の他のパブリックまたは独自規格グラフィックスAPI等、に準拠し得る。グラフィックスレンダリング命令を処理するため、プロセッサ6は、1つまたは複数のグラフィックスレンダリングコマンドをGPU12に(例えば、GPUドライバ22を通して)発行してグラフィックスデータのレンダリングのいくつか、または全てをGPU12に行わせ得る。いくつかの例では、レンダリングされるべきグラフィックスデータが、例えば、点、線、三角形、四角形、トライアングルストライプなどのグラフィックス基本形状(graphics primitives)のリストを含み得る。

10

#### 【0018】

[0025] GPU12は、ディスプレイ8に1つまたは複数のグラフィックス基本形状をレンダリングするためのグラフィックス動作を行うように構成され得る。このため、プロセッサ6上で実行するソフトウェアアプリケーションのうちの1つがグラフィックス処理を要求するとき、プロセッサ6は、ディスプレイ8へのレンダリングのためにグラフィックスコマンドおよびグラフィックスデータをGPU12に提供し得る。グラフィックスデータは、例えば、描画コマンド(drawing commands)、ステート情報、プリミティブ情報(primitive information)、テクスチャ情報(texture information)等を含み得る。GPU12は、いくつかの例において、プロセッサ6に比べて複雑なグラフィック関連動作のより効率的な処理を提供する高度に並列な構造(highly-parallel structure)で構築され得る。例えば、GPU12は、並列方式で複数の頂点または画素について動作するよう構成される、シェーダユニットのような、複数の処理要素を含み得る。GPU12の高度な並列性は、いくつかの例において、GPU12が、プロセッサ6を使用してディスプレイ8に直接シーンを描くより早くディスプレイ8上にグラフィックスイメージ(例えば、GUISおよび2次元(2D)および/または3次元(3D)のグラフィックスシーン)を描くことを可能し得る。

20

#### 【0019】

[0026] GPU12は、いくつかの例において、計算デバイス2のマザーボードに統合され得る。他の例において、GPU12は、計算デバイス2のマザーボード内のポートにインストールされるグラフィックスカード上に存在するか、または、そうでなければ計算デバイス2と相互運用するように構成される周辺デバイス内に組み込まれ得る。GPU12は、1つまたは複数のマイクロプロセッサ、特定用途向け集積回路(ASICs)、フィールドプログラマブルゲートアレイ(FPGAs)、デジタルシグナルプロセッサ(DSPs)、または他の等価な集積またはディスクリート論理回路のような1つまたは複数のプロセッサを含み得る。GPU12はまた、1つまたは複数のプロセッサコアを含み得、GPU12はマルチコアプロセッサと称され得る。

30

#### 【0020】

[0027] グラフィックスメモリ40はGPU12の一部であり得る。このため、GPU12は、バスを使用せずに、グラフィックスメモリ40からデータを読み取り、グラフィックスメモリ40へデータを書き込み得る。言替えると、GPU12は、オフチップメモリの代わりに、ローカルストレージを使用してローカルにデータを処理し得る。このようなグラフィックスメモリ40は、オンチップメモリと称され得る。これは、重いバストラフィックを経験し得るバスを介してデータを読み書きGPU12の必要性を無くすことによる、より効率的な方式でGPU12が動作することを可能にする。グラフィックスメモリ40は、例えば、ランダムアクセスメモリ(RAM)、スタティックRAM(SRAM)、ダイナミックRAM(DRAM)、消去可能プログラマブルROM(EPROM)、電気的消去可能プログラマブルROM(EEPROM(登録商標))、フラッシュメモリ、磁気データ媒体または光学記憶媒体のような1つまたは複数の揮発性または不揮発性メモリ、または記憶デバイスを含み得る。

40

#### 【0021】

50

[0028] いくつかの例において、GPU12は、完全に形成された画像をシステムメモリ10に保存し得る。ディスプレイプロセッサ14は、システムメモリ10から画像を取り出して、ディスプレイ8の複数の画素に画像を表示するように照明させる値を出力し得る。ディスプレイ8は、GPU12によって生成された画像コンテンツを表示する計算デバイス2のディスプレイであり得る。ディスプレイ8は、液晶ディスプレイ(LCD)、有機発光ダイオードディスプレイ(OLED)、または陰極線管(CRT)ディスプレイ、プラズマディスプレイ、または他のタイプのディスプレイデバイスであり得る。

#### 【0022】

[0029] 図2は、さらに詳細に図1のプロセッサ6、GPU12、およびシステムメモリ10の例示的な実施形態を例示するブロック図である。図2に示すように、プロセッサ6は、各々1つまたは複数のソフトウェアアプリケーションまたはサービスである、少なくとも1つのソフトウェアアプリケーション18、グラフィックスAPI20、GPUドライバ22、およびメモリ管理ユニット(MMU)23を実行し得る。いくつかの例において、グラフィックスAPI20およびGPUドライバ22はCPU6のハードウェアユニットとして実施され得る。

#### 【0023】

[0030] プロセッサ6およびGPU12に利用可能なメモリは、システムメモリ10およびフレームバッファ16を含み得る。フレームバッファ16は、システムメモリ10の一部であり得、またはシステムメモリ10から分離され得る。フレームバッファ16は、レンダリングされた画像データを保存し得る。MMU23は、CPU6から、システムメモリ10またはグラフィックスメモリ40のようなメモリへのアクセスのための要求を扱うように構成されるハードウェアであり得る。例えば、MMU23はソフトウェアアプリケーション18からのメモリアクセス要求を扱い得る。MMU23は、こうしたメモリアクセス要求を扱うために1つまたは複数のページテーブルまたは翻訳ルックアサイドバッファ(TLBs: translation lookaside buffers)を使用して物理メモリアドレスへの仮想メモリアドレスの翻訳を行い得る。

#### 【0024】

[0031] いくつかの例において、プロセッサ6は、レベル1(L1)キャッシュ、レベル2(L2)キャッシュ、レベル3(L3)キャッシュ、などの1つまたは複数のキャッシュ15を含む、または有し得る。1つまたは複数のキャッシュ15はシステムメモリ10に比べて速いメモリアクセスをプロセッサ6に提供し得、システムメモリ10の頻繁にアクセスされるメモリロケーションからのデータのコピーを保存し得る。

#### 【0025】

[0032] ソフトウェアアプリケーション18は、GPU12の機能を利用する任意のアプリケーションであり得る。例えば、ソフトウェアアプリケーション18は、グラフィカルユーザインターフェース(GUI)アプリケーション、オペレーティングシステム、ポートブルマッピングアプリケーション、エンジニアリングまたは美術的アプリケーション(*artistic applications*)のためのコンピュータ支援設計プログラム(*computer-aided design program*)、ビデオゲームアプリケーション、または2Dまたは3Dグラフィックスを使用する他のタイプのソフトウェアアプリケーションであり得る。

#### 【0026】

[0033] ソフトウェアアプリケーション18は、GUIおよび/またはグラフィックスシーンをレンダリングするようにGPU12に命じる1つまたは複数の描画命令を含み得る。例えば、描画命令は、GPU12によってレンダリングされるべき1つまたは複数のグラフィックス基本形状のセットを定義する命令を含み得る。いくつかの例において、描画命令は、GUIで使用される複数のウィンドウイングサーフェス(windowing surfaces)の全てまたは一部を集合的に定義し得る。追加の例において、描画命令は、アプリケーションによって定義されるモデル空間またはワールド空間内で1つまたは複数のグラフィックスオブジェクトを含むグラフィックスシーンの全てまたは一部を集合的に定義し得る。

#### 【0027】

10

20

30

40

50

[0034] ソフトウェアアプリケーション 18 は、1つまたは複数のグラフィックス基本形状をレンダリングして表示可能なグラフィックス画像にするための G P U 1 2 への 1 つまたは複数のコマンドを発行するためにグラフィックス A P I 2 0 を介して G P U ドライバ 2 2 を呼び出し得る。例えば、ソフトウェアアプリケーション 18 は、G P U 1 2 に基本形状定義 (primitive definition) を提供するために、グラフィックス A P I 2 0 を介して、G P U ドライバ 2 2 を呼び出し得る。いくつかの例において、基本形状は、例えば、三角形、四角形、扇形三角形 (triangle fans)、または帯状連結三角形 (triangle strips) 等の描画基本形状のリストの形式で G P U 1 2 に提供され得る。基本形状定義は、レンダリングされるべき基本形状と関連する 1 つまたは複数の頂点を特定する頂点仕様 (vertex specifications) を含み得る。頂点仕様は、各頂点についての位置座標 (positional coordinates) と、いくつかの例において、頂点と関連する他の属性、例えば、カラーライバ 10 座標、法線ベクトル (normal vectors)、およびテクスチャ座標などと、を含み得る。基本形状定義はまた、基本形状タイプ情報 (例えば、三角形、四角形、扇形三角形、帯状連結三角形等)、スケーリング情報、回転情報等も含み得る。

#### 【 0 0 2 8 】

[0035] ソフトウェアアプリケーション 18 によって G P U ドライバ 2 2 に発行された命令に基づき、G P U ドライバ 2 2 は、G P U 1 2 が基本形状をレンダリングするために行う 1 つまたは複数の動作を特定する 1 つまたは複数のコマンドを作成し (formulate) 得る。G P U 1 2 が C P U 6 からのコマンドを受け取ると、グラフィックス処理パイプラインが、このコマンドを復号し、コマンドにおいて特定された動作を行うようにグラフィックス処理パイプラインを構成することをシェーダプロセッサ 4 8 上で実行し得る。例えば、グラフィックス処理パイプラインにおける入力アセンブラーは、基本形状データを読み取ることができ、グラフィックス処理パイプラインにおける他のグラフィックスパイプラインステージによる使用のためにデータを基本形状にアセンブルし得る。特定された動作を行った後、グラフィックス処理パイプラインは、ディスプレイベイスと関連するフレームバッファ 1 6 にレンダリングされたデータを出力する。 20

#### 【 0 0 2 9 】

[0036] フレームバッファ 1 6 は、G P U 1 2 のための宛先画素 (destination pixels) を保存する。各宛先画素は、一意的なスクリーン画素位置と関連し得る。いくつかの例において、フレームバッファ 1 6 は、カラーコンポーネントおよび各宛先画素のための宛先アルファ値 (destination alpha value) を保存し得る。例えば、フレームバッファ 1 6 は、各画素のための赤、緑、青、アルファ (RGBA) を記憶し得、ここで「RGB」コンポーネントがカラー値に対応し、「A」コンポーネントが宛先アルファ値に対応する。フレームバッファ 1 6 およびメモリ 1 0 が別個のメモリユニットであるものとして例示されているが、他の例において、フレームバッファ 1 6 は、システムメモリ 1 0 の一部であり得る。 30

#### 【 0 0 3 0 】

[0037] いくつかの例において、グラフィックス処理パイプラインが、1 つまたは複数の頂点 (vertex) シェーダステージ、ハル (hull) シェーダステージ、ドメイン (domain) シェーダステージ、ジオメトリ (geometry) シェーダステージ、および画素 (pixel) シェーダステージを含み得る。グラフィックス処理パイプラインのこれらステージは考慮されたシェーダユニット 4 6 上で実行する 1 つまたは複数のシェーダプログラムとして実施され得る。シェーダユニット 4 6 は、処理コンポーネントのプログラマブルパイプラインとして構成され得る。いくつかの例において、シェーディングユニット 4 6 は、「シェーダプロセッサ」、または「統合シェーダ (unified shaders)」と称されることができ、グラフィックスをレンダリングするためにジオメトリ、頂点、画素、または他のシェーディング動作を行い得る。シェーダユニット 4 6 は、各々がフェッチおよび復号動作のための 1 つまたは複数のコンポーネント、算術計算 (arithmetic calculations) を行う 1 つまたは複数の A L U、1 つまたは複数のメモリ、キャッシュ、およびレジスタを含み得るシェーダプロ 40

セッサ48を含み得る。

【0031】

[0038] G P U 1 2 は、グラフィックス処理パイプラインにおける頂点シェーダステージ、ハルシェーダステージ、ドメインシェーダステージ、ジオメトリシェーダステージ、および画素シェーダステージのうちの1つまたは複数を実行するためにコマンドをシェーダユニット46に送ることによって、頂点シェーディング、ハルシェーディング、ドメインシェーディング、ジオメトリシェーディング、画素シェーディング等のような様々なシェーディング動作を行うようにシェーダユニット46を指定し得る。いくつかの例において、G P U ドライバ22は、1つまたは複数のシェーダプログラムをコンパイルし、コンパイルされたシェーダプログラムをG P U 1 2 内に包含される1つまたは複数のプログラム 10 マブルシェーダユニット上にダウンロードするように構成され得る。シェーダプログラムは、例えば、OpenGLシェーディングランゲージ (G L S L) 、ハイレベルシェーディングランゲージ (H L S L) 、グラフィックスのためのC言語 (C for Graphics) (Cg) シェーディングランゲージ等のような、ハイレベルシェーディングランゲージで書かれ得る。コンパイルされたシェーダプログラムは、G P U 1 2 内のシェーダユニット46の動作を制御する1つまたは複数の命令を含み得る。例えば、シェーダプログラムは、頂点シェーダステージの機能を行うためにシェーダユニット46によって実行され得る頂点シェーダプログラム、ハルシェーダステージの機能を行うためにシェーダユニット46によって実行され得るハルシェーダプログラム、ドメインシェーダステージの機能を行うためにシェーダユニット46によって実行され得るドメインシェーダプログラム、ジオメトリシェーダステージの機能を行うためにシェーダユニット46によって実行され得るジオメトリシェーダプログラム、および/または画素シェーダの機能を行うためにシェーダユニット46によって実行され得る画素シェーダプログラムを含み得る。頂点シェーダプログラムは、プログラムブル頂点シェーダユニット、または統合されたシェーダユニットの実行を制御でき、1つまたは複数の頂点単位の動作を特定する命令を含み得る。 20

[0039] グラフィックスメモリ40は、G P U 1 2 の集積回路に物理的に統合されたオンチップ記憶装置、またはメモリを含み得る。グラフィックスメモリ40がオンチップである場合、G P U 1 2 は、システムバスを介してシステムメモリ10から値を読み取ること、またはシステムメモリ10に値を書き込むことより速くグラフィックスメモリ40から値を読み取り、またはグラフィックスメモリ40に値を書き込むことが可能であり得る 30 。

【0032】

[0040] G P U 1 2 はまた、透過的フォーマット変換器(T F C)24を含み得る。T F C 2 4 は、C P U 6 または任意の他の処理コアをイネーブルするハードウェアであり得、グラフィックスメモリ40に保存された画素データ41に従う画素フォーマットをサポートしない任意の他の処理コアがあたかもC P U 6 によってサポートされた画素フォーマットに従ってグラフィックスメモリ40に保存された画素データ41を見るようとする。イネーブルするハードウェアであり得る。

言替えると、C P U 6 は、T F C 2 4 を通じて、グラフィックスメモリ40に保存された画素データを、それがサポートする画素フォーマットで読み書き可能である。例えば、画素データがグラフィックスメモリ40にタイル画素フォーマットで保存される場合であって、C P U 6 がN V 1 2 のような線形画素フォーマットをサポートする場合に、T F C 2 4 は、画素データ41がC P U 6 によってサポートされるN V 1 2 のような線形フォーマットで整列されてC P U 6 に現れるようにして、画素データ41の線形ベースビューをC P U 6 に提供し得る。T F C 2 4 は、C P U 6 によってサポートされる画素フォーマットに従う画素データ41に対するC P U 6 によるどの書き込みもそれがグラフィックメモリ40に保存されるフォーマットに戻すように翻訳し得る。このため、T F C 2 4 は、画素データ41がC P U 6 によってサポートされる画素フォーマットにあったかのように画素データ41を扱うことをC P U 6 にイネーブルして、画素データ41がC P U 6 によってサポートされない画素フォーマットでグラフィックスメモリ40に保存される一方でC P 40 50

U 6 が画素データ 4 1 を C P U 6 によってサポートされる画素フォーマットに従って読み書きできるようにする。

【 0 0 3 3 】

[0041] 本開示の態様に従って、T F C 2 4 はグラフィックスメモリ 4 0 に保存された画素データ 4 1 に関する、C P U 6 による要求が第 1 のデータフォーマットにある画素データ 4 1 に関する要求を示すものであると決定し得る。T F C 2 4 は、グラフィックスメモリ 4 0 における画素データ 4 1 に関する要求に少なくとも一部基づいて、第 2 のデータフォーマットにある画素データ 4 1 をグラフィックスメモリ 4 0 から取得し得る。T F C 2 4 は、取得された画素データ 4 1 を第 2 のデータフォーマットから第 1 のデータフォーマットへ変換し得る。T F C 2 4 は、第 1 のデータフォーマットにある変換された画素データ 4 1 を、プロセッサ 6 によってアクセス可能であるキャッシュのようなメモリに保存し得る。 10

【 0 0 3 4 】

[0042] いくつかの例において、T F C 2 4 は G P U 1 2 に含まれる特定のハードウェアロジックであり得る。いくつかの他の例において、T F C 2 4 はシェーダユニット 4 6 のシェーダプロセッサ 4 8 によって実行されるシェーダコードを含み得る。他の例において、T F C 2 4 は計算デバイス 2 に含まれるもの、厳密には G P U 1 2 に含まれない特定のハードウェアロジックであり得る。例えば、T F C 2 4 は C P U 6 に組み込まれ得るか、または C P U 6 および G P U 1 2 から分離された独立型ハードウェアコンポーネントであり得る。 20

【 0 0 3 5 】

[0043] 図 3 は、図 2 の T F C 2 4 の例示的な機能を例示するブロック図である。図 3 に示すように、グラフィックスメモリ 4 0 は、タイルベース画素フォーマットに従う画素データ 4 1 を保存し得る。プロセッサ 2 6 は、タイルベース画素フォーマットからの読み取りおよびタイルベース画素フォーマットへの書き込みのできない処理コアであり得る。例えば、プロセッサ 2 6 は線形画素フォーマットをサポートし得るもの、タイルベース画素フォーマットをサポートし得ない。プロセッサ 2 6 が画素データ 4 1 に対して読み書きすることをイネーブルするために、T F C 2 4 は、どのように画素データ 4 1 がグラフィックスメモリ 4 0 に保存されているかとは無関係(independent)のプロセッサ 2 6 にグラフィックスメモリ 4 0 に保存された画素データ 4 1 のビュー 4 3 を提供し得る。ビュー 4 3 はプロセッサ 2 6 によってサポートされる画素フォーマットにある画素データ 4 1 を表し、プロセッサ 2 6 の視点から、グラフィックスデータがプロセッサ 2 6 のサポートする、Y U V、N V 1、および同等なもののような画素フォーマットに従ってビュー 4 3 でレイアウトされるようにし得る。T F C 2 4 はそれゆえ、画素データ 4 1 がグラフィックスメモリ 4 0 に保存されるかのように、プロセッサ 2 6 が画素データ 4 1 に対して読み書きすることをイネーブルし得る。T F C 2 4 はプロセッサ 2 6 から読み出しあり得るかの確認を受けることができ、これら読み出しあり得るかの確認を画素データ 4 1 のタイルベース画素フォーマットのための適切な読み出しあり得るかの確認に翻訳できる。 30

【 0 0 3 6 】

[0044] プロセッサ 2 6 にビュー 4 3 を提示する T F C 2 4 は、プロセッサ 2 6 に色アパチャ (colored aperture) を提示することを含み得る。色アパチャは、特定のターゲット画素フォーマットで物理メモリをアクセスするために使用できる、物理的および/または仮想のうちのどちらかのアドレス範囲であり得る。例えば、T F C 2 4 は、プロセッサ 2 6 によってサポートされる画素フォーマットにある画素データ 4 1 をアクセスするためにプロセッサ 2 6 がメモリアクセスし得る仮想アドレス範囲をプロセッサ 2 6 に提示し得る。T F C 2 4 は、プロセッサ 2 6 が色アパチャを読み出しあり得るかの確認を受けるかの確認を画素データ 4 1 のタイルベース画素フォーマットのための適切な読み出しあり得るかの確認に翻訳できる。複数の異なるソフトウェアアプリケーションおよび/または異なるプロセッサ 40

が画素データ41へのアクセスを要求する場合、TFC24が重複しない異なるソフトウェアアプリケーションおよび/または異なるプロセッサの各々ために一意の色アパチャを提供し得る。このようにして、TFC24は要求しているソフトウェアアプリケーションおよび/またはプロセッサを、これらソフトウェアアプリケーションおよび/またはプロセッサからの画素データ41に関するアクセスのための要求に含まれた仮想アドレスに少なくとも一部基づいてこれらソフトウェアアプリケーションおよび/またはプロセッサによってサポートされる画素フォーマットと共に決定することが可能であり得る。

#### 【0037】

[0045] 図4は、図2のTFC24の例示的な実施形態を例示するブロック図である。図4に示すように、プロセッサ50Aおよびプロセッサ50Bは各々グラフィックスメモリ40に保存された画素データ41に対するアクセスを要求し得る。プロセッサ50Aがアクセスを要求しているグラフィックスメモリ40に保存された画素データの基底画素フォーマットをプロセッサ50Aがサポートしないかまたはその知識を持たない一方で、プロセッサ50Bがアクセスを要求しているグラフィックスメモリ40に保存された画素データ41の基底画素フォーマットをサポートするおよび/またはその知識を持ち得る。プロセッサ50Aの例は、CPU6を、グラフィックスメモリ40に保存された画素データ41の画素フォーマットをサポートしないか、またはその知識を持たない任意の他の処理ハードウェアと共に含み得る。より具体的には、プロセッサ50AがCPU6である場合に、CPU6上で実行するソフトウェアアプリケーション18がグラフィックスメモリ40に保存された画素データに対するアクセスを要求し得る。プロセッサ50Bの例は、GPU12、シェーダプロセッサ48、ビデオエンコーダ、複数のビデオデコーダ、ディスプレイプロセッサ、ディスプレイ、デジタル信号プロセッサ(DPSs)、カメラプロセッサ、ビデオプロセッサ、およびグラフィックスメモリ40に保存された画素データの画素フォーマットをサポートするおよび/またはその知識をもつようなものを含み得る。

#### 【0038】

[0046] プロセッサ50Aおよび50Bは各々グラフィックスメモリ40に保存された画素データ41に対するアクセスを要求し得る。上で論じたように、プロセッサ50Aおよび50Bがアクセスを要求する画素データ41は、プロセッサ50Bによってサポートされるもののプロセッサ50Aによってサポートされない特定の画素フォーマットに従つて配列され得る。

#### 【0039】

[0047] プロセッサ50Aは仮想アドレス51Aからデータに関する要求をでき、プロセッサ50Bは仮想アドレス51Bからデータに関する要求をできる。MMU52Aは、プロセッサ50Aからのデータに関する要求を扱って仮想アドレス51Aを翻訳されたアドレス53に変換するためにページテーブル54Aを使用し得る。例えば、プロセッサ50AがCPU6である場合に、MMU52AがMMU23であり得る。MMU52Aは仮想アドレス51Aを、1つまたは複数のカラービットを仮想アドレス51Aの前に添付することを含む翻訳されたアドレス53に変換し、翻訳されたアドレス53の1つまたは複数の上位ビットが仮想アドレス51を続けた1つまたは複数のカラービットを含むようにし得る。カラービットはプロセッサ50Aによってサポートされる画素フォーマットをTFC24へインジケートし得る。例えば、64ビットアドレス可能空間において、仮想アドレス51Aは全64ビットをとり得ない。このため、MMU52Aは64ビット以下の翻訳アドレス53を生成するために1つまたは複数のカラービットを仮想アドレスに連結可能であり得る。同様に、MMU52Bは、プロセッサ50Bからのデータに関する要求を扱い、仮想アドレス51Bを使用して物理アドレス55Bを調べるためにページテーブル54Bを使用し得る。プロセッサ50Bはピクセルデータ41がグラフィックスメモリ40に保存された画素フォーマットをサポートすることから、MMU52は、仮想アドレス51Bを翻訳されたアドレスに翻訳する代わりに、グラフィックスメモリ40における要求されたデータの物理アドレスである物理アドレス55Bへ仮想アドレス51Bを直接的に翻訳できる。

10

20

30

40

50

## 【0040】

[0048] TFC24は、翻訳されたアドレス53を受け取ることができ、ページテーブル56へインデックスするための翻訳アドレス53を使用することに少なくとも一部基づいて、プロセッサ50Aによって要求されたグラフィックスメモリ40における画素データ41のロケーションをインジケートする物理アドレス55Aを決定できる。TFCは、少なくとも物理アドレス55Aに一部基づいてグラフィックスメモリ40における画素データ41を取得でき、取得された画素データ41を、画素データ41がそれに従ってグラフィックスメモリ40に保存された画素フォーマットから、プロセッサ50Aによってサポートされる画素フォーマットに翻訳できる。取得された画素データ41を翻訳することは、画素データ41を圧縮解除して、プロセッサ50A等によってサポートされる画素フォーマットに従って画素情報を再編成することを含み得る。TFC24は、変換された画素データ41をプロセッサ50A内の1つまたは複数のキャッシュ(例えば、1つまたは複数のキャッシュ15)に保存することなどで、変換された画素データ41をプロセッサ50Aに戻し得る。 10

## 【0041】

[0049] プロセッサ50Aは、プロセッサ50Aによってサポートされる画素フォーマットに従ってその1つまたは複数のキャッシュに保存された画素データ41に対して読み書きし得る。プロセッサ50Aがその1つまたは複数のキャッシュフラッシュから画素データ41を追い出したときである、キャッシュフラッシュに応答して、TFC24は仮想アドレス51Aに少なくとも一部基づいて翻訳されたものである、翻訳されたアドレス53と一緒にプロセッサ50Aから画素データ41を受け取り得る。TFC24は画素データ41をグラフィックスメモリ40にそれが保存される画素フォーマットに戻るように変換でき、画素データ41がグラフィックスメモリ40に保存される画素フォーマットに画素情報を再編成すること、および画素データ41がグラフィックスメモリ40に保存される画素フォーマットに従って画素情報を圧縮することを含む。TFC24はまた、翻訳されたアドレス53をページテーブル56を使用して物理アドレス55Aに変換でき、物理アドレス55Aで画素データ41をグラフィックスメモリ40に保存できる。 20

## 【0042】

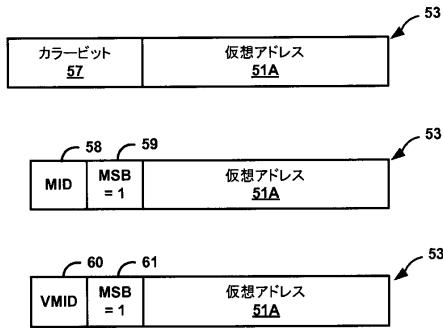

[0050] 図5は、図4の翻訳されたアドレス53の例示的なフォーマットを例示するブロック図である。図5に示すように、翻訳されたアドレス53は、画素データ41へのアクセスを要求しているプロセッサを識別する1つまたは複数の上位ビットと共にこのプロセッサによってサポートされた1つまたは複数の画素フォーマットを含み得る。翻訳されたアドレス53は、仮想アドレス51に連結された1つまたは複数の上位ビットを含み得る。一例において、翻訳されたアドレス53の1つまたは複数の最上位ビットはカラービット57を含み得る。カラービット57は、要求しているプロセッサによってサポートされた画素フォーマットを特定する1つまたは複数のビットであり得る。他の例において、翻訳されたアドレス53の1つまたは複数の最上位ビットは、要求しているプロセッサを識別するマスターID58と共に、翻訳されたアドレス53の最上位ビットが1である場合に1にセットされるビット59を含み得る。他の例において、翻訳されたアドレス53の1つまたは複数の最上位ビットは、同様のアクセス許可を持つ複数のプロセッサのグループ内にあるものとして要求しているプロセッサを識別する仮想マシンID60と共に、翻訳されたアドレス53の最上位ビットが1である場合に1にセットされるビット61を含み得る。 30 40

## 【0043】

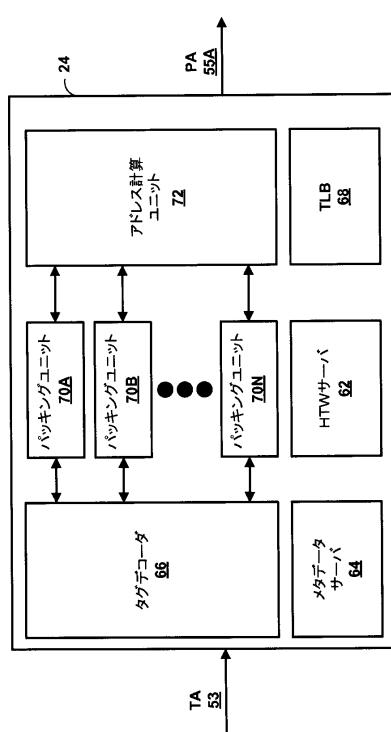

[0051] 図6は、図2のTFC24の例示的実施形態を例示するプロック図である。図5に示すように、TFC24は、タグデコーダ66、翻訳ルックアサイドバッファ(TLB)68、パッキングユニット69A-69N、「パッキングユニット69」)、およびアドレス計算ユニット67を含み得る。TFC24はまた、メタデータサーバ64およびハードウェアテーブルウォーカ(HTW)サーバ62を含み得る。 50

## 【0044】

[0052] 上で論じたように、TFC24は、翻訳されたアドレス53を物理アドレス55Aに翻訳し得る。TFCはまた、プロセッサによってサポートされた画素フォーマットと、グラフィックメモリ40に保存された画素データ41の画素フォーマットとの間の変換をし得る。タグデコーダ66は、翻訳されたアドレス53を復号して、グラフィックスメモリ40における画素データ41をアクセスすることを試みている処理コア(例えば、プロセッサ50A)によってサポートされた画素フォーマットのような、翻訳されたアドレスに含まれる情報を決定すし得る。

【0045】

[0053] メタデータサーバ64は、TFC24によって受け取った、翻訳されたアドレス53のために1つまたは複数のビュー定義を決定し得る。翻訳されたアドレス53のためのビュー定義は、画素データ41に関する要求を送ったプロセッサ50Aに関する情報と共に、翻訳されたアドレス53を介して要求された画素データ41に関する情報を含み得る。1つまたは複数のビュー定義は、要求された画素データ41のステータス、要求された画素データ41の開始アドレス、要求された画素データ41の長さ、要求しているプロセッサ50Aによってサポートされたターゲット画素フォーマット、要求された画素データ41のタイル幅およびタイル長、要求された画素データ41のストライド(stride)、等と共に、画素データ41を要求しているプロセッサ50Aによってサポートされる画素フォーマットに変換するために必要であり得る任意の他の必要データを含み得る。いくつかの例において、メタデータサーバ64は、それが受け取る、翻訳されたアドレス53毎の1つまたは複数のビュー定義を含み得る。

【0046】

[0054] アドレス計算ユニット67は、翻訳されたアドレス53から物理アドレス55Aを決定し得る。TLB68は、物理アドレス翻訳に対する1つまたは複数の翻訳されたアドレスをキャッシュし得る。アドレス計算ユニット67は、TLB68が翻訳されたアドレス53の物理アドレス55Aをキャッシュしたかどうか決定するためにTLB68に問い合わせ得る。TLB68が翻訳されたアドレス53の物理アドレス55Aをキャッシュしていれば、TFC24がメタデータサーバ64によって提供された画素データ41のためのビュー定義に基づいて物理アドレス55Aで画素データ41をアクセスし得る。

【0047】

[0055] TLB68が翻訳されたアドレス53の物理アドレス55Aをキャッシュしていないければ、アドレス計算ユニット67が翻訳されたアドレス53のカラービットをはがし(strip)得、このはがされた翻訳されたアドレスを翻訳されたアドレス53の物理アドレスを決定するためにHTWサーバ62へ提供し得る。HTWサーバ62は、1つまたは複数のページテーブル(例えば、ページテーブル54Aおよび/またはページテーブル56)をアクセスし、翻訳されたアドレス53の物理アドレス55Aを決定するためのハードウェアであり得る。HTWサーバ62が翻訳されたアドレス53の物理アドレス55Aを決定することに応答して、TFC24はメタデータサーバ64によって提供された画素データ41のためのビュー定義に基づいて物理アドレス55Aで画素データ41をアクセスし得る。

【0048】

[0056] パッキングユニット69は、要求している処理コアによってサポートされた画素フォーマットと、グラフィックスメモリ40に保存された画素データ41の画素フォーマットとの間の翻訳をし得る。パッキングユニット69は、画素フォーマット間で変換するためにカラー変換、タイル貼り、タイルはがし、圧縮、圧縮解除、等を行い得る。いくつかの例において、パッキングユニット69は固定の機能ハードウェアを含み得る。他の例において、パッキングユニット69の機能は、GPU12、シェーダユニット46、専用デジタル信号プロセッサ、等を介するような他の手段で実施され得る。いくつかの例において、TFC24の全機能は、シェーダユニット46上で実行するシェーダコードで実施され得る。

【0049】

10

20

30

40

50

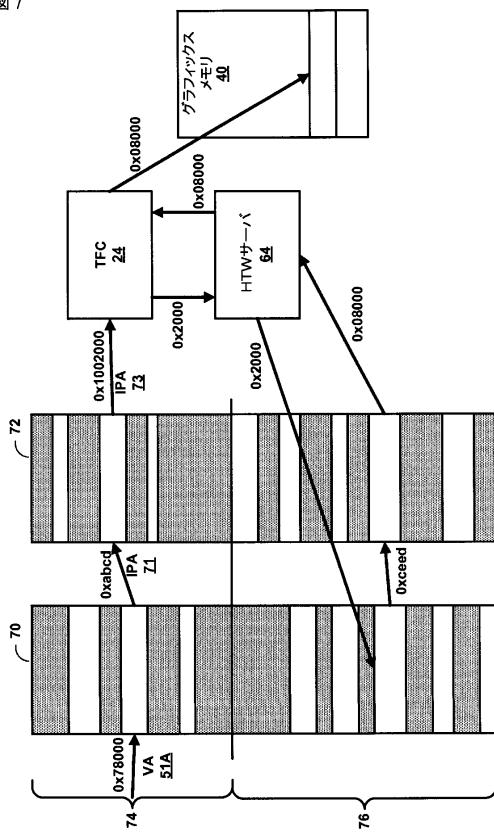

[0057] 図7は、例示的な仮想アドレスを例示的な物理アドレスに翻訳するために2レベルページテーブルマッピングを利用する図2のTFC24を例示するブロック図である。単一レベルページテーブルは概ね高レベルオペレーティングシステム(HLOS)によって管理され得ることから、2レベルページテーブルはTFC24がアドレスの翻訳および画素フォーマットの変換をHLOSから隠すことをイネーブルし、MMUが単一ページテーブルを使用して仮想アドレスを物理アドレスに単純に翻訳することにHLOSに見えるようにできる。

#### 【0050】

[0058] 図7に示すように、MMU52Aは、ページテーブル70およびページテーブル72を備える2ステージページテーブルを利用する2レベルMMUであり得る。HLOSは、ハイパーバイザーまたは仮想マシンモニタ(VMM)がページテーブル72を管理し得る一方でページテーブル70を管理し得る。上で論じたように、ハイパーバイザーまたはVMMがページテーブル72を使用して第2のステージマッピングを管理し得ることから、こうした第2のレベルマッピングがHLOSから隠され得る。

#### 【0051】

[0059] ページテーブル70および72は、ソフトウェアアプリケーション18が画素フォーマット変換のためにノーマルページをマッピング可能であり得る場合に専用メモリセグメントを有し得る。MMU52Aはまた、ページテーブル70および72を使用してユーザアドレス空間およびカーネルアドレス空間を管理し得る。ユーザアドレス空間は、カーネルアドレス空間がカーネルのような低レベル特権コードによってアクセス可能であり得る一方で、HLOS上で稼働しているソフトウェアアプリケーションによってアクセス可能であり得る。こうして、カーネルアドレス空間は無特権ソフトウェアアプリケーションによるアクセスから保護され得る。ページテーブル70および72は、ユーザアドレス空間仮想アドレスを翻訳するためのユーザアドレス空間部分74およびカーネルアドレス空間仮想アドレスを翻訳するためのカーネルアドレス空間部分76を含み得る。

#### 【0052】

[0060] 図7の例において、仮想アドレス51Aは、ユーザアドレス空間にあり得る0x7800であり得る。MMU52Aは、ページテーブル70へインデックスするための仮想アドレス51Aを利用して、仮想アドレス51Aを0xabcdの中間物理アドレス(intermediate physical address)71へ翻訳し得る。IPA71は、カラービット57のようなカラービットに連結された仮想アドレス51Aであり得、MMU52Aはページテーブル72へインデックスするためのIPAを使用して、中間物理アドレス71を0x1002000の中間物理アドレス73へ翻訳し得る。IPA73は、その1つまたは複数の最上位ビットにあるIPA71のカラービットに保持され得る。中間物理アドレス73は、図4の変換されたアドレス53と同じであり得る。

#### 【0053】

[0061] TFC24は、0x1002000の物理アドレス73からカラービット0x1000000をはがし、物理アドレス55Aを決定するために結果のアドレス0x2000をHTWサーバ62に提供し得る。結果のアドレス0x2000はカーネルアドレス空間にあり得ることから、HTWサーバ62は、結果のアドレス0x2000を利用して、ページテーブル72のカーネルアドレス空間部分76へインデックスして、0xceedのアドレスをもたらし得る。HTWサーバ62は、さらにページテーブル72のカーネルアドレス空間部分76へインデックスするために0xceedのアドレスを利用して0x0800の物理アドレス55Aをもたらし得る。HTWサーバ62は、0x0800の物理アドレス55AをTFC24に提供でき、TFCは0x0800の物理アドレス55Aでグラフィックスメモリ40をアクセスできる。こうして、ページテーブル70および72のカーネルアドレス空間部分76は図4のページテーブル56の役を務め得る。

#### 【0054】

[0062] 物理アドレス55Aを決定するためにページテーブル70および72のカーネルアドレス空間およびカーネルアドレス空間部分76を利用することによって、TFC2

10

20

30

40

50

4はCPU6のようなプロセッサによって課せられたセキュリティ体制を使用して物理アドレス55Aへの仮想アドレス51Aの翻訳を行い得る。このセキュリティ体制はまた、複数のソフトウェアアプリケーションおよび/または複数の処理コアのための複数のカラーアパチャを生成することにおいてTFC24をメモリ効率的にできる。

#### 【0055】

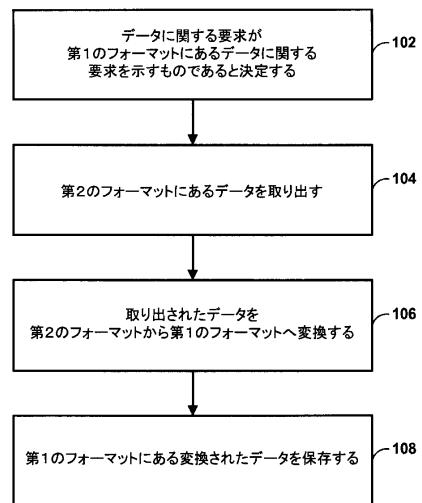

[0063] 図8は、透過的に画素フォーマットを変換するためのプロセスを例示するフローチャートである。図8に示すように、このプロセスは、第1のデータバッファに保存されたデータに関する、少なくとも1つのプロセッサによる要求が第1のデータフォーマットにあるこのデータに関する要求を示すものであると、TFC24によって、決定すること(102)を含み得る。方法は、第1のデータバッファに保存されたデータに関する要求に少なくとも一部基づいて、第2のデータフォーマットにあるこのデータを第1のデータバッファから、TFC24によって、取得すること(104)をさらに含み得る。方法は、取得されたデータを第2のデータフォーマットから第1のデータフォーマットへ、TFC24によって、変換すること(106)をさらに含み得る。方法は、第1のデータフォーマットにある変換されたデータを、少なくとも1つのプロセッサによってアクセス可能である第2のデータバッファに、TFC24によって、保存すること(108)をさらに含み得る。

10

#### 【0056】

[0064] いくつかの例において、第1のデータバッファに保存されたデータに関する、少なくとも1つのプロセッサによる要求が、仮想アドレス51Aで保存されたデータに関する要求を含み、第2のデータフォーマットにあるこのデータを第1のデータバッファから、TFC24によって、取得することは、第2のデータフォーマットにあるこのデータを仮想アドレスに対応する物理アドレスで第1のデータバッファから、TFC24によって、取得することをさらに備える。いくつかの例において、プロセスは仮想アドレス51Aに少なくとも一部基づき、翻訳されたアドレス53をMMU52Aによって、決定することと、翻訳されたアドレス53に少なくとも一部基づいて、物理アドレス55AをTFC24によって、決定することとをさらに含む。

20

#### 【0057】

[0065] いくつかの例において、翻訳されたアドレス53の1つまたは複数の最上位ビットは、1つまたは複数のカラービットを備え、ここにおいて1つまたは複数のカラービットは1つまたは複数のプロセッサによってサポートされた少なくとも画素フォーマットをインジケートする。いくつかの例において、翻訳されたアドレス53を決定することは、仮想アドレス51Aに少なくとも一部基づいて1つまたは複数のカラービットを、MMU52Aによって、決定することをさらに含む。いくつかの例において、プロセスは、仮想アドレス51Aに少なくとも一部基づいて、第1のレベルページテーブル70を使用するMMU52Aによって、中間物理アドレス71を決定することと、中間物理アドレス71に少なくとも一部基づいて、第2のレベルページテーブル72を使用するMMU52Aによって、翻訳されたアドレス53を決定することとをさらに含む。いくつかの例において、翻訳されたアドレス53に少なくとも一部基づいて物理アドレス55Aを、TFC24によって、決定することは、1つまたは複数のページテーブル70および72のカーネルアドレス空間部分76に少なくとも一部基づいて物理アドレス55Aを、TFC24によって、決定することさらに含む。

30

#### 【0058】

[0066] いくつかの例において、第2のデータバッファは、少なくとも1つのプロセッサのためにキャッシュを備える。いくつかの例において、データは画素データ41を備え、第1のデータフォーマットは第1の画素フォーマットを備え、第2のデータフォーマットは第2の画素フォーマットを備える。いくつかの例において、プロセスは、第1のデータフォーマットにある第2のデータを少なくとも1つのプロセッサから、TFC24によって、受け取ることと、第2のデータを第1のデータフォーマットから第2のデータフォーマットへ、TFC24によって、変換することと、第2のデータフォーマットにある、

40

50

変換されたデータを第1のデータバッファに、T F C 2 4によって、保存することとをさらに含む。

【0059】

[0067] 1つまたは複数の例において、記載された機能は、ハードウェア、ソフトウェア、ファームウェア、またはそれらの任意の組合せに実施され得る。ソフトウェアで実施される場合、機能は、コンピュータ可読媒体上における1つまたは複数の命令またはコードとして記憶または送信され得る。コンピュータ読取可能媒体は、1つの場所から別の場所へのコンピュータプログラムの転送を容易にする任意の媒体を含む通信媒体またはコンピュータデータ記憶媒体を含みうる。データ記憶媒体は、本開示内で説明された技法の実施形態のための命令、コード、および/またはデータ構造を取り出すために、1つまたは複数のコンピュータまたは1つまたは複数のプロセッサによってアクセスされることができる任意の利用可能な媒体であり得る。限定ではなく例として、そのようなコンピュータ可読媒体は、R A M、R O M、E E P R O M、C D - R O Mまたは他の光学ディスク記憶装置、磁気ディスク記憶装置または他の磁気記憶デバイス、あるいは命令またはデータ構造の形式で所望のプログラムコードを搬送または記憶するよう使用されることができ、コンピュータによってアクセスされることができる任意の他の媒体を備えることができる。また、任意の接続は、厳密にはコンピュータ可読媒体と称される。例えば、ソフトウェアがウェブサイト、サーバ、または他の遠隔ソースから、同軸ケーブル、光ファイバーケーブル、ツイストペア、デジタル加入者回線 (D S L)、あるいは赤外線、無線、およびマイクロ波のようなワイヤレス技法を使用して送信される場合、同軸ケーブル、光ファイバーケーブル、ツイストペア、D S L、あるいは赤外線、無線、およびマイクロ波のようなワイヤレス技法は送信媒体の定義に含まれている。ディスク (disk) およびディスク (disc) は、本明細書で使用される場合、コンパクトディスク (C D) (disc)、レーザーディスク (登録商標) (disc)、光ディスク (disc)、デジタル多用途ディスク (D V D) (disc)、フロッピー (登録商標) ディスク (disk) およびB l u - r a y (登録商標) ディスク (disc) を含み、ここで、ディスク (disk) は通常、磁気的にデータを再生し、その一方でディスク (disc) は、レーザーを用いて光学的にデータを再生する。上記の組み合わせはまた、コンピュータ可読媒体の範疇に含まれるべきである。

【0060】

[0068] コードは、1つまたは複数の1デジタルシグナルプロセッサ (D S P s)、汎用マイクロプロセッサ、特定用途向け集積回路 (A S I C s)、フィールドプログラマブル論理アレイ (F P G A s)、または他の同等な集積またはディスクリートな論理回路等の、1つまたは複数のプロセッサによって実行され得る。従って、本開示で使用される場合、「プロセッサ」および「処理ユニット/処理装置」という用語は、前述の構造、または本開示に説明される技法の実施形態に適した任意の他の構造のいずれかを指し得る。加えて、いくつかの態様では、本開示に説明される機能は、符号化および復号のために構成された専用ハードウェアおよび/またはソフトウェアモジュール内で提供され得る、あるいは組み合わせられたコーデック内に組み込まれ得る。また、技法は、1つまたは複数の回路または論理要素で完全に実施され得る。

[0069] 本開示の技法は、ワイヤレスハンドセット、集積回路 (I C) またはI C sのセット (例えば、チップセット) を含む、幅広い様々なデバイスまたは装置で実施され得る。様々なコンポーネント、モジュール、またはユニットは、開示された技法を行うように構成されるデバイスの機能的な態様を強調するように本開示において説明されるが、必ずしも異なるハードウェアユニットによる実現を必要としない。むしろ、上に説明されたように、様々なユニットは、コーデックハードウェアユニットに組み合わされ得るか、または適切なソフトウェアおよび/またはファームウェアと併せて、上に説明されたような1つまたは複数のプロセッサを含む、相互運用のハードウェアユニット (interoperative hardware units) の集合によって提供され得る。

【0061】

[0070] 本開示の様々な態様が説明されてきた。これらおよび他の態様は、特許請求の

10

20

30

40

50

範囲の範疇にある。

以下に本願の出願当初の特許請求の範囲に記載された発明を付記する。

[C 1] 画素処理のための方法であって、

第1のデータバッファに保存されたデータに関する、少なくとも1つのプロセッサによる要求が第1のデータフォーマットにある前記データに関する要求を示すものであると、透過的フォーマット変換器(TFC)によって、決定することと、

前記第1のデータバッファに保存されたデータに関する前記要求に少なくとも一部基づいて、第2のデータフォーマットにある前記データを前記第1のデータバッファから、前記TFCによって、取得することと、

前記取得されたデータを前記第2のデータフォーマットから前記第1のデータフォーマットへ、前記TFCによって、変換することと、

前記第1のデータフォーマットにある前記変換されたデータを、前記少なくとも1つのプロセッサによってアクセス可能である第2のデータバッファに、前記TFCによって、保存することと

を備える、方法。

[C 2] 前記第1のデータバッファに保存されたデータに関する、前記少なくとも1つのプロセッサによる前記要求は、仮想アドレスに保存されたデータに関する要求を備え、

前記第2のデータフォーマットにある前記データを前記第1のデータバッファから、前記TFCによって、取得することは、前記第2のデータフォーマットにある前記データを、前記仮想アドレスに対応する物理アドレスで前記第1のデータバッファから、前記TFCによって、取得することをさらに備える、C 1に記載の方法。

[C 3] 前記仮想アドレスに少なくとも一部基づいて翻訳されたアドレスを、メモリ管理ユニット(MMU)によって、決定することと、

前記翻訳されたアドレスに少なくとも一部基づいて前記物理アドレスを、前記TFCによって、決定することと

をさらに備える、C 2に記載の方法。

[C 4] 前記翻訳されたアドレスの1つまたは複数の最上位ビットは1つまたは複数のカラービットを備え、前記1つまたは複数のカラービットは前記1つまたは複数のプロセッサによってサポートされた少なくとも画素フォーマットをインジケートする、C 3に記載の方法。

[C 5] 前記翻訳されたアドレスを決定することは、前記仮想アドレスに少なくとも一部基づいて前記1つまたは複数のカラービットを、MMUによって、決定することをさらに備える、C 3に記載の方法。

[C 6] 前記仮想アドレスに少なくとも一部基づいて中間物理アドレスを、第1のレベルページテーブルを使用するMMUによって、決定することと、

前記中間物理アドレスに少なくとも一部基づいて前記翻訳されたアドレスを、第2のレベルページテーブルを使用するMMUによって、決定することとをさらに備える、C 3に記載の方法。

[C 7] 前記翻訳されたアドレスに少なくとも一部基づいて前記物理アドレスを、前記TFCによって、決定することは、1つまたは複数のページテーブルのカーネルアドレス空間部分に少なくとも一部基づいて前記物理アドレスを、前記TFCによって、決定することをさらに備える、C 3に記載の方法。

[C 8] 前記第2のデータバッファは前記少なくとも1つのプロセッサのためのキャッシュを備える、C 1に記載の方法。

[C 9] 前記データは画素データを備え、

前記第1のデータフォーマットは第1の画素フォーマットを備え、

前記第2のデータフォーマットは第2の画素フォーマットを備える、C 1に記載の方法

。

[C 10] 前記第1のデータフォーマットにある第2のデータを、前記少なくとも1つのプロセッサから前記TFCによって、受け取ることと、

10

20

30

40

50

前記第2のデータを前記第1のデータフォーマットから前記第2のデータフォーマットへ、前記TFCによって、変換することと、

前記第2のデータフォーマットにある前記変換されたデータを前記第1のデータバッファに、前記TFCによって、保存することと

をさらに備える、C1に記載の方法。

[C11] 第1のデータバッファと、

第2のデータバッファと、

少なくとも1つのプロセッサと、

前記第1のデータバッファに保存されたデータに関する、少なくとも1つのプロセッサによる要求が第1のデータフォーマットにある前記データに関する要求を示すものであると決定し、

前記第1のデータバッファに保存されたデータに関する前記要求に少なくとも一部基づいて、第2のデータフォーマットにある前記データを前記第1のデータバッファから取得し、

前記取得されたデータを前記第2のデータフォーマットから前記第1のデータフォーマットへ変換し、

前記第1のデータフォーマットにある前記変換されたデータを、前記少なくとも1つのプロセッサによってアクセス可能である前記第2のデータバッファに保存するように構成される透過的フォーマット変換器と

を備える、計算デバイス。

[C12] 前記第1のデータバッファに保存されたデータに関する、前記少なくとも1つのプロセッサによる前記要求は、仮想アドレスに保存されたデータに関する要求を備え、

前記TFCは、前記第2のデータフォーマットにある前記データを、前記仮想アドレスに対応する物理アドレスで前記第1のデータバッファから取得するようにさらに構成される、C11に記載の計算デバイス。

[C13] 前記仮想アドレスに少なくとも一部基づいて翻訳されたアドレスを決定するように構成されるメモリ管理ユニット(MMU)をさらに備え、

前記TFCは、前記翻訳されたアドレスに少なくとも一部基づいて前記物理アドレスを決定するようにさらに構成される、C12に記載の計算デバイス。

[C14] 前記翻訳されたアドレスの1つまたは複数の最上位ビットは1つまたは複数のカラービットを備え、前記1つまたは複数のカラービットは前記1つまたは複数のプロセッサによってサポートされた少なくとも画素フォーマットをインジケートする、C13に記載の計算デバイス。

[C15] 前記MMUは、前記仮想アドレスに少なくとも一部基づいて前記1つまたは複数のカラービットを決定するようにさらに構成される、C13に記載の計算デバイス。

[C16] 前記MMUは、

第1のレベルページテーブルを使用し、前記仮想アドレスに少なくとも一部基づいて中間物理アドレスを決定し、

第2のレベルページテーブルを使用し、前記中間物理アドレスに少なくとも一部基づいて前記翻訳されたアドレスを決定する

ようにさらに構成される、C13に記載の計算デバイス。

[C17] 前記TFCは、1つまたは複数のページテーブルのカーネルアドレス空間部分に少なくとも一部基づいて前記物理アドレスを決定するようにさらに構成される、C13に記載の計算デバイス。

[C18] 前記第2のデータバッファは前記少なくとも1つのプロセッサのためのキャッシュを備える、C11に記載の計算デバイス。

[C19] 前記データは画素データを備え、

前記第1のデータフォーマットは第1の画素フォーマットを備え、

前記第2のデータフォーマットは第2の画素フォーマットを備える、C11に記載の計算デバイス。

10

20

30

40

50

[C 2 0] 前記 T F C は、

前記第1のデータフォーマットにある第2のデータを前記少なくとも1つのプロセッサから受け取り、

前記第2のデータを前記第1のデータフォーマットから前記第2のデータフォーマットへ変換し、

前記第2のデータフォーマットにある前記変換されたデータを前記第1のデータバッファに保存する

ようにさらに構成される、C 1 1 に記載の計算デバイス。

[C 2 1] 第1のデータバッファに保存されたデータに関する、少なくとも1つのプロセッサによる要求が第1のデータフォーマットにある前記データに関する要求を示すものであると決定するための手段と、

前記第1のデータバッファに保存されたデータに関する前記要求に少なくとも一部基づいて、第2のデータフォーマットにある前記データを前記第1のデータバッファから取得するための手段と、

前記取得されたデータを前記第2のデータフォーマットから前記第1のデータフォーマットへ変換するための手段と、

前記第1のデータフォーマットにある前記変換されたデータを、前記少なくとも1つのプロセッサによってアクセス可能である第2のデータバッファに保存するための手段とを備える、装置。

[C 2 2] 前記第1のデータバッファに保存されたデータに関する、前記少なくとも1つのプロセッサによる前記要求は、仮想アドレスに保存されたデータに関する要求を備え、

前記第2のデータフォーマットにある前記データを前記第1のデータバッファから取得するための前記手段は、前記第2のデータフォーマットにある前記データを、前記仮想アドレスに対応する物理アドレスで前記第1のデータバッファから取得するための手段をさらに備える、C 2 1 に記載の装置。

[C 2 3] 前記仮想アドレスに少なくとも一部基づいて翻訳されたアドレスを決定するための手段と、

前記翻訳されたアドレスに少なくとも一部基づいて前記物理アドレスを決定するための手段と

をさらに備える、C 2 2 に記載の装置。

[C 2 4] 前記翻訳されたアドレスの1つまたは複数の最上位ビットは1つまたは複数のカラービットを備え、前記1つまたは複数のカラービットは前記1つまたは複数のプロセッサによってサポートされた少なくとも画素フォーマットをインジケートする、C 2 3 に記載の装置。

[C 2 5] 前記翻訳されたアドレスを決定するための前記手段は、前記仮想アドレスに少なくとも一部基づいて前記1つまたは複数のカラービットを決定するための手段をさらに備える、C 2 3 に記載の装置。

[C 2 6] 第1のデータバッファに保存されたデータに関する、少なくとも1つのプロセッサによる要求が第1のデータフォーマットにある前記データに関する要求を示すものであると、透過的フォーマット変換器(T F C)によって、決定することと、

前記第1のデータバッファに保存されたデータに関する前記要求に少なくとも一部基づいて、第2のデータフォーマットにある前記データを前記第1のデータバッファから、前記T F C によって、取得することと、

前記取得されたデータを前記第2のデータフォーマットから前記第1のデータフォーマットへ、前記T F C によって、変換することと、

前記第1のデータフォーマットにある前記変換されたデータを、前記少なくとも1つのプロセッサによってアクセス可能である第2のデータバッファに、前記T F C によって、保存することと

をプログラマブルプロセッサにさせるための命令を備える、コンピュータ可読媒体。

[C 2 7] 前記第1のデータバッファに保存されたデータに関する、前記少なくとも1つ

10

20

30

40

50

のプロセッサによる前記要求は、仮想アドレスに保存されたデータに関する要求を備え、前記第2のデータフォーマットにある前記データを前記第1のデータバッファから、前記TFCによって、取得することは、前記第2のデータフォーマットにある前記データを、前記仮想アドレスに対応する物理アドレスで前記第1のデータバッファから、前記TFCによって、取得することをさらに備える、C26に記載のコンピュータ可読媒体。

[C 2 8] 前記仮想アドレスに少なくとも一部基づいて翻訳されたアドレスを、メモリ管理ユニット(MMU)によって、決定することと、

前記翻訳されたアドレスに少なくとも一部基づいて前記物理アドレスを、前記ＴＦＣによって、決定することと

をさらに備える、C27に記載のコンピュータ可読媒体。

[C 2 9] 前記翻訳されたアドレスの 1 つまたは複数の最上位ビットは 1 つまたは複数のカラービットを備え、前記 1 つまたは複数のカラービットは前記 1 つまたは複数のプロセッサによってサポートされた少なくとも画素フォーマットをインジケートする、C 2 8 に記載のコンピュータ可読媒体。

[C 3 0] 前記翻訳されたアドレスを決定することは、前記仮想アドレスに少なくとも一部基づいて前記1つまたは複数のカラーピットを、MMUによって、決定することをさらに備える、C 2 8に記載のコンピュータ可読媒体。

10

( 1 )

【 2 】

FIG. 1

**FIG. 2**

【図3】

図3

FIG. 3

【図4】

図4

FIG. 4

【図5】

図5

FIG. 5

【図6】

図6

FIG. 6

【図7】

图 7

【 四 8 】

图 8

**FIG. 8**

---

フロントページの続き

(51)Int.Cl.

F I

G 0 6 T 1/20

Z

(72)発明者 コッティリンガル、スティーブ・ラビ

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

(72)発明者 カン、モイヌル

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

(72)発明者 シャープ、コリン・クリストファー

アメリカ合衆国、カリフォルニア州 92121-1714、サン・ディエゴ、モアハウス・ドライブ 5775

審査官 後藤 彰

(56)参考文献 特表2015-526806 (JP, A)

特表2015-524979 (JP, A)

国際公開第2014/028120 (WO, A1)

国際公開第2014/028109 (WO, A2)

米国特許出願公開第2013/0275649 (US, A1)

特開2003-84751 (JP, A)

米国特許出願公開第2012/0242671 (US, A1)

特開平11-85963 (JP, A)

(58)調査した分野(Int.Cl., DB名)

G 0 6 F 12/10

G 0 6 F 12/00 - 12/08

G 0 6 T 1/20