(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property

Organization

International Bureau

(43) International Publication Date

24 November 2005 (24.11.2005)

PCT

(10) International Publication Number

WO 2005/111874 A2

- (51) International Patent Classification<sup>7</sup>: G06F 17/50

- (21) International Application Number: PCT/US2005/016115

- (22) International Filing Date: 6 May 2005 (06.05.2005)

- (25) Filing Language: English

- (26) Publication Language: English

- (30) Priority Data:

- 60/568,849 7 May 2004 (07.05.2004) US

60/655,837 23 February 2005 (23.02.2005) US

- (71) Applicant (for all designated States except US): MENTOR GRAPHICS CORPORATION [US/US]; 8005 S.W. Boeckman Road, Wilsonville, OR 97070 (US).

- (72) Inventor; and

- (75) Inventor/Applicant (for US only): TORRES ROBLES, Juan, A. [MX/US]; 7870 SW Oak Patch Court, Wilsonville, OR 98070 (US).

- (74) Agent: TULLETT, Rodney, C.; Christensen O'Connor Johnson Kindness PLLC, 1420 Fifth Avenue, Suite 2800, Seattle, WA 98101 (US).

- (81) Designated States (unless otherwise indicated, for every kind of national protection available): AE, AG, AL, AM, AT, AU, AZ, BA, BB, BG, BR, BW, BY, BZ, CA, CH, CN, CO, CR, CU, CZ, DE, DK, DM, DZ, EC, EE, EG, ES, FI, GB, GD, GE, GH, GM, HR, HU, ID, IL, IN, IS, JP, KE, KG, KM, KP, KR, KZ, LC, LK, LR, LS, LT, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NA, NI, NO, NZ, OM, PG, PH, PL, PT, RO, RU, SC, SD, SE, SG, SK, SL, SM, SY, TJ, TM, TN, TR, TT, TZ, UA, UG, US, UZ, VC, VN, YU, ZA, ZM, ZW.

- (84) Designated States (unless otherwise indicated, for every kind of regional protection available): ARIPO (BW, GH, GM, KE, LS, MW, MZ, NA, SD, SL, SZ, TZ, UG, ZM, ZW), Eurasian (AM, AZ, BY, KG, KZ, MD, RU, TJ, TM), European (AT, BE, BG, CH, CY, CZ, DE, DK, EE, ES, FI, FR, GB, GR, HU, IE, IS, IT, LT, LU, MC, NL, PL, PT, RO, SE, SI, SK, TR), OAPI (BF, BJ, CF, CG, CI, CM, GA, GN, GQ, GW, ML, MR, NE, SN, TD, TG).

Published:

- without international search report and to be republished upon receipt of that report

[Continued on next page]

(54) Title: INTEGRATED CIRCUIT LAYOUT DESIGN METHODOLOGY WITH PROCESS VARIATION BANDS

Enhanced design flow using the methodology proposed in this work

WO 2005/111874 A2

- (57) Abstract: A system for analyzing IC layouts and designs by calculating variations of a number of objects to be created on a semiconductor wafer as a result of different process conditions. The variations are analyzed to determine individual feature failures or to rank layout designs by their susceptibility to process variations. In one embodiment, the variations are represented by PV-bands having an inner edge that defines the smallest area in which an object will always print and an outer edge that defines the largest area in which an object will print under some process conditions.

*For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette.*

**INTEGRATED CIRCUIT LAYOUT DESIGN METHODOLOGY

WITH PROCESS VARIATION BANDS**

**FIELD OF THE INVENTION**

5        The present invention relates to photolithographic processing in general, and in particular, to methods of verifying integrated circuit designs for manufacturability due to process variations.

**BACKGROUND OF THE INVENTION**

10      In a conventional integrated circuit design process, a circuit designer begins with a conceptual idea of what functions an integrated circuit is to perform. The circuit designer then creates a circuit design on a computer and verifies it using one or more simulation tools to ensure that the circuit will operate as desired. The design at this stage may be represented by what is commonly viewed as a circuit schematic, but may also be represented by higher level abstractions within the computer.

15      These abstract designs are then converted to physical definitions of the circuit elements to be fabricated. These definitions, often called the circuit layout, represent the geometric boundaries for the physical devices to be fabricated – transistor gates, capacitors, resistive interconnecting wires, etc. A number of data formats have been created to represent these physical layouts, including GDS-II and OASISTM. Often, each 20 physical layer of the circuit has a corresponding data layer to represent the polygonal boundaries of the elements in that layer.

Once the circuit layout has been defined, additional verification checks are performed. Some of these verification checks are to insure that the physical structures will correctly represent the desired electrical behavior. This is commonly called a LVS, 25 for Layout vs. Schematic or Layout vs. Source. Additional extraction of parasitic resistances and capacitances can be done, and the dynamic behavior of the circuit can be estimated for the layout as well. This step is traditionally called parasitic extraction.

Other verification checks are carried out to ensure that the circuit layout can be manufactured with a particular process. For example, the layout may be subject to one or 30 more design rule checks (DRCs) to ensure that the circuit does not contain any violations of circuit element placement or configurations that cannot be manufactured by the specified manufacturing process. In addition, resolution enhancement techniques (RETs), such as optical and process correction (OPC), may be applied to pre-compensate for the

expected optical distortions that occur in the photolithographic process. The verified and OPC corrected layout data is then used to make a number of photolithographic masks or reticles that are used in the selected photolithographic process to image patterns on a semiconductor wafer in order to manufacture the desired circuit.

5 While the above methodology works well for manufacturing integrated circuits under expected photolithographic process conditions, these process conditions can vary. For example, variations can occur in the focus of the image on the wafer, the dose of illumination light through the mask or reticle, the placement of a stepper, as well as other process conditions that affect how the circuit will be created on the wafer. In the past, 10 there has not been a reliable method of taking into account the process variations that may occur when designing a circuit so that the circuit will operate as intended regardless of the conditions used to actually manufacture the circuit. As such, there is a need for a system that can consider and compensate for expected process variations during the design and verification procedure so that the layout can be made more robust and easier 15 to manufacture.

#### SUMMARY OF THE INVENTION

To address the problems discussed above, the present invention is a method for verifying and/or compensating IC layouts for expected variations that occur in photolithographic processing. In accordance with one embodiment of the present 20 invention, objects to be created on a wafer are modeled to determine ranges in the way the objects would be printed on the wafer under a variety of process conditions. In one embodiment, the ranges are stored as process variation bands (PV-bands) that specify the smallest and largest dimensions of an object that may be expected to print on a wafer. The PV-bands are analyzed by one or more rules to see if the circuit can be manufactured 25 with the expected process conditions.

In accordance with an embodiment of the invention, different IC layouts can be ranked by their manufacturability in accordance with the PV-bands created for the objects. In another embodiment of the invention, the PV-bands can be used to determine when an IC layout is acceptable for manufacture.

#### 30 BRIEF DESCRIPTION OF THE DRAWINGS

The foregoing aspects and many of the attendant advantages of this invention will become more readily appreciated as the same become better understood by reference to

the following detailed description, when taken in conjunction with the accompanying drawings, wherein:

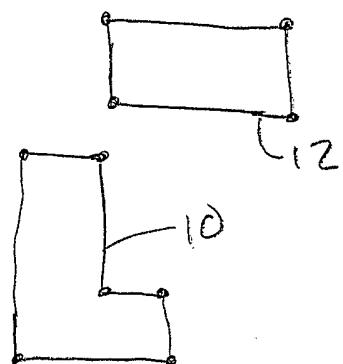

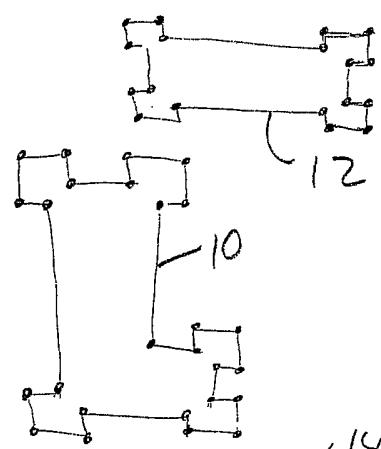

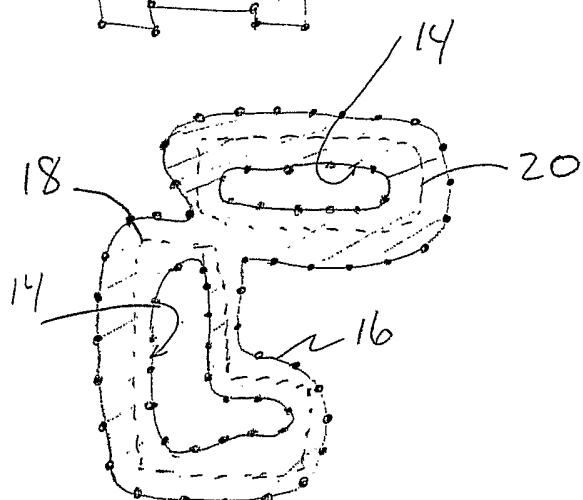

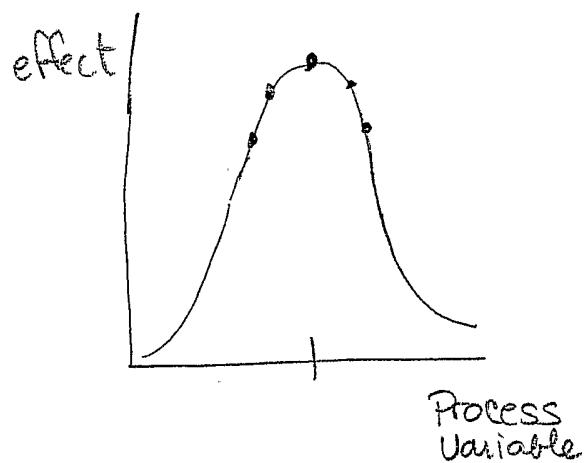

FIGURES 0A-0D illustrate a portion of a simplified IC layout, its corresponding PV-bands and a variable process in accordance with one embodiment of the present invention.

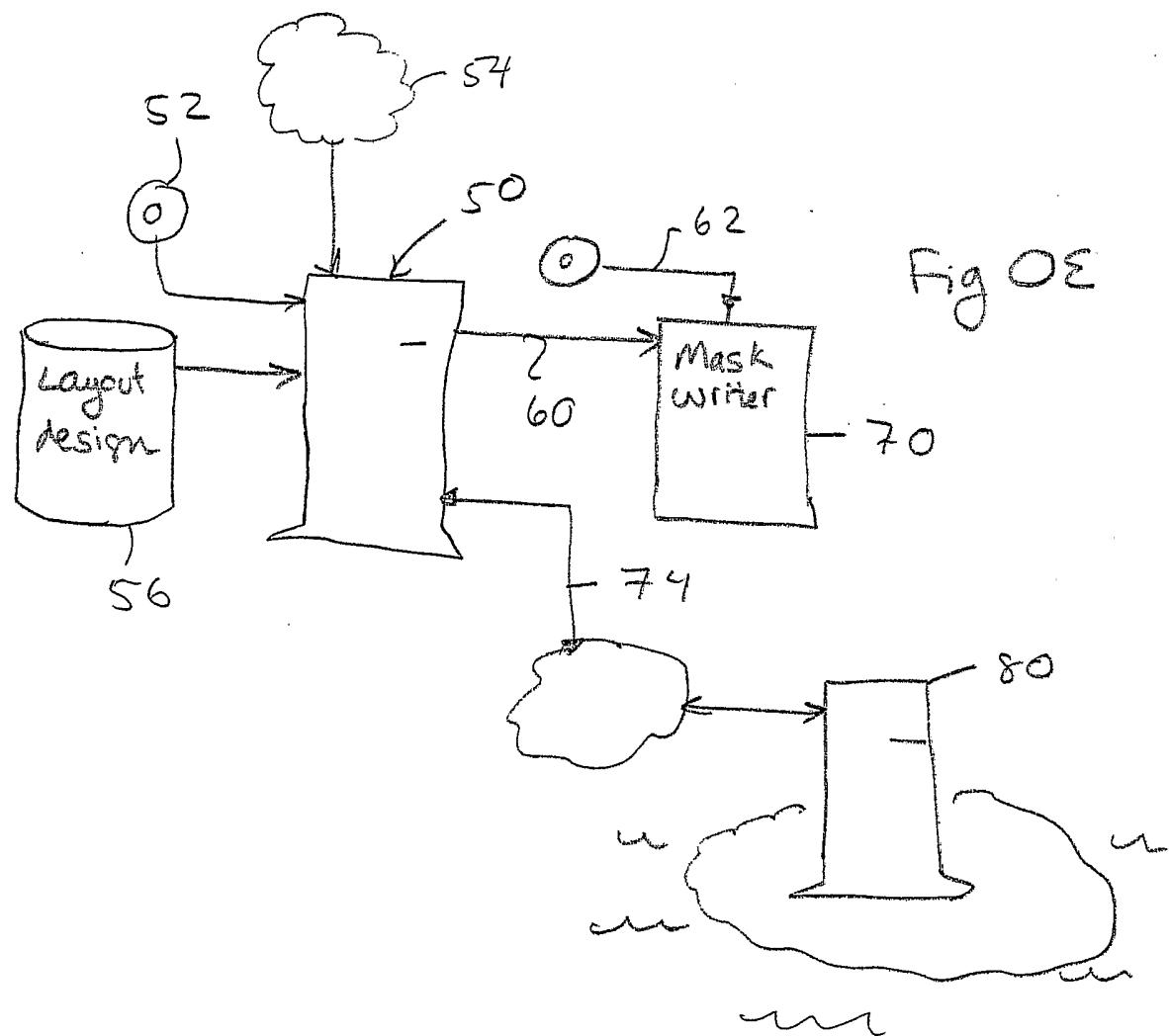

FIGURE 0E illustrates a representative computer system in which an embodiment of the present invention may be implemented.

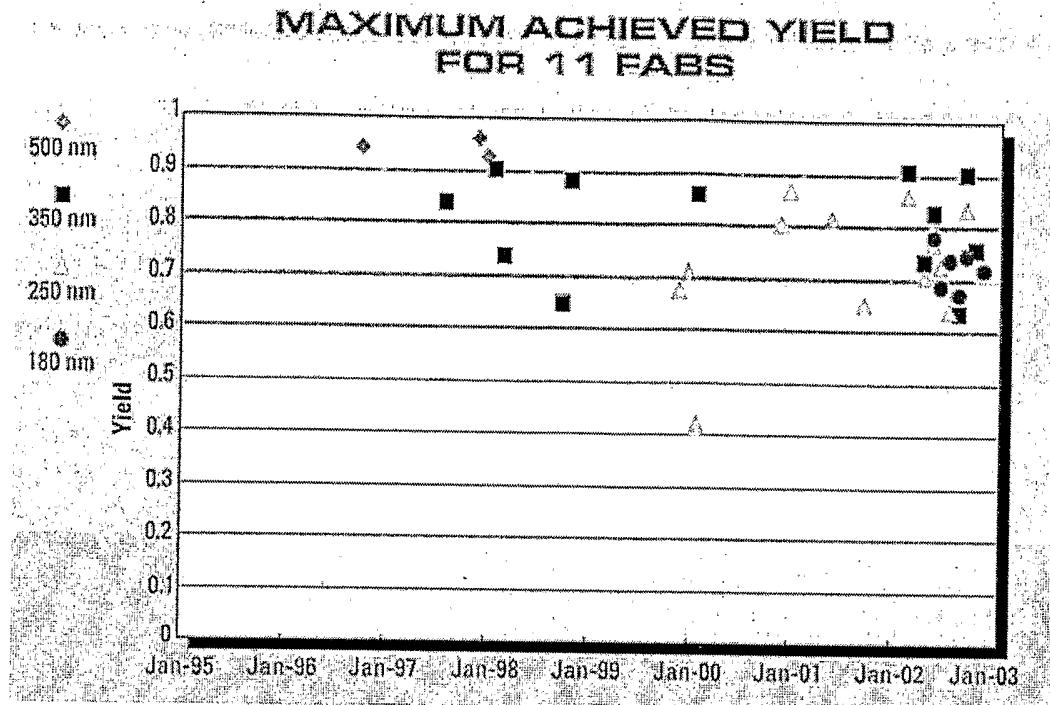

FIGURE 1 illustrates a maximum attainable yield for 500 nm, 350 nm, 250 nm, and 180 nm processes.

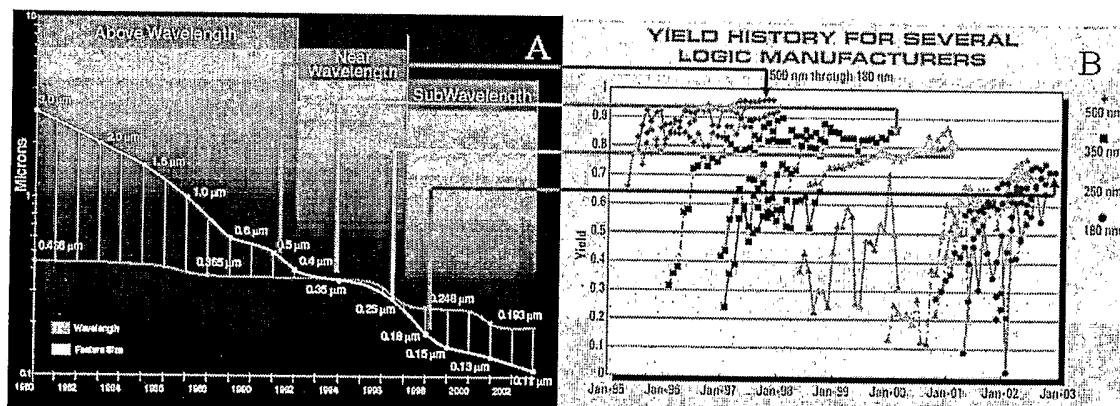

FIGURE 2 illustrates a sub-wavelength gap and its correlation to maximum attainable yield.

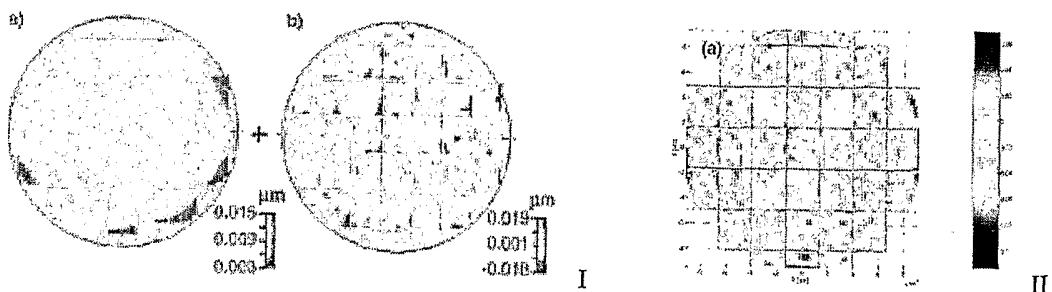

FIGURE 3 illustrates a mean defocus: Wafer component (Ia), field-by-field defocus residuals (removing systematic wafer component) (Ib) and field-by-field residuals.

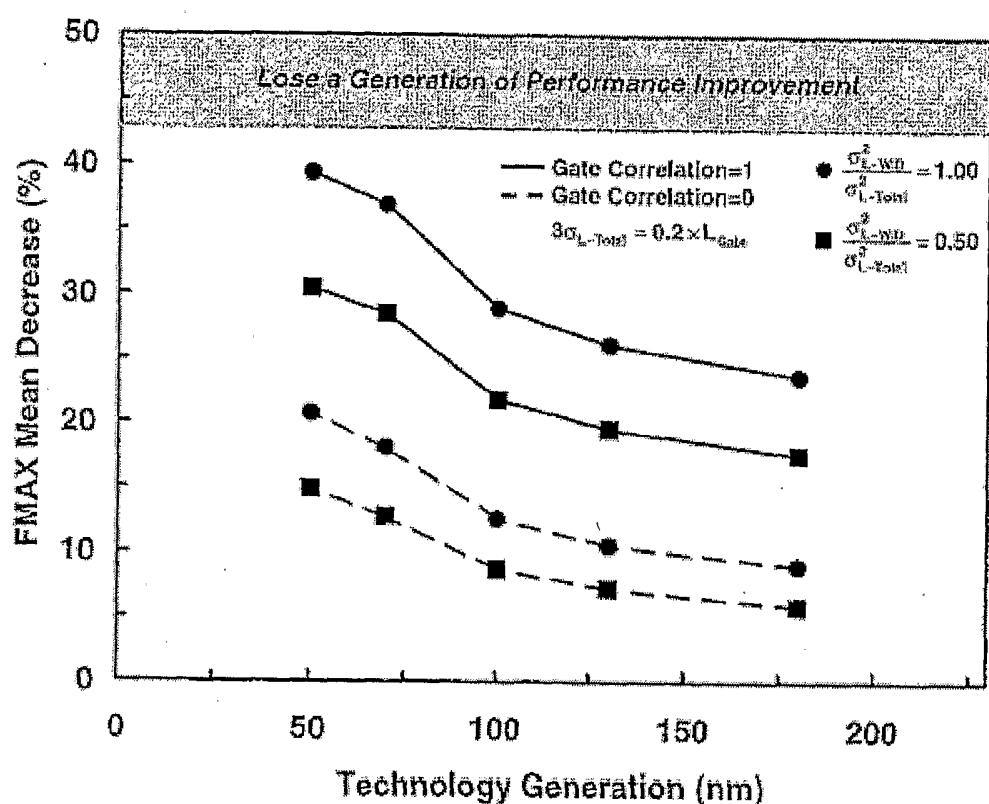

FIGURE 4 illustrates a reduction in maximum frequency resulting from within-die parameter fluctuations versus technology generation.

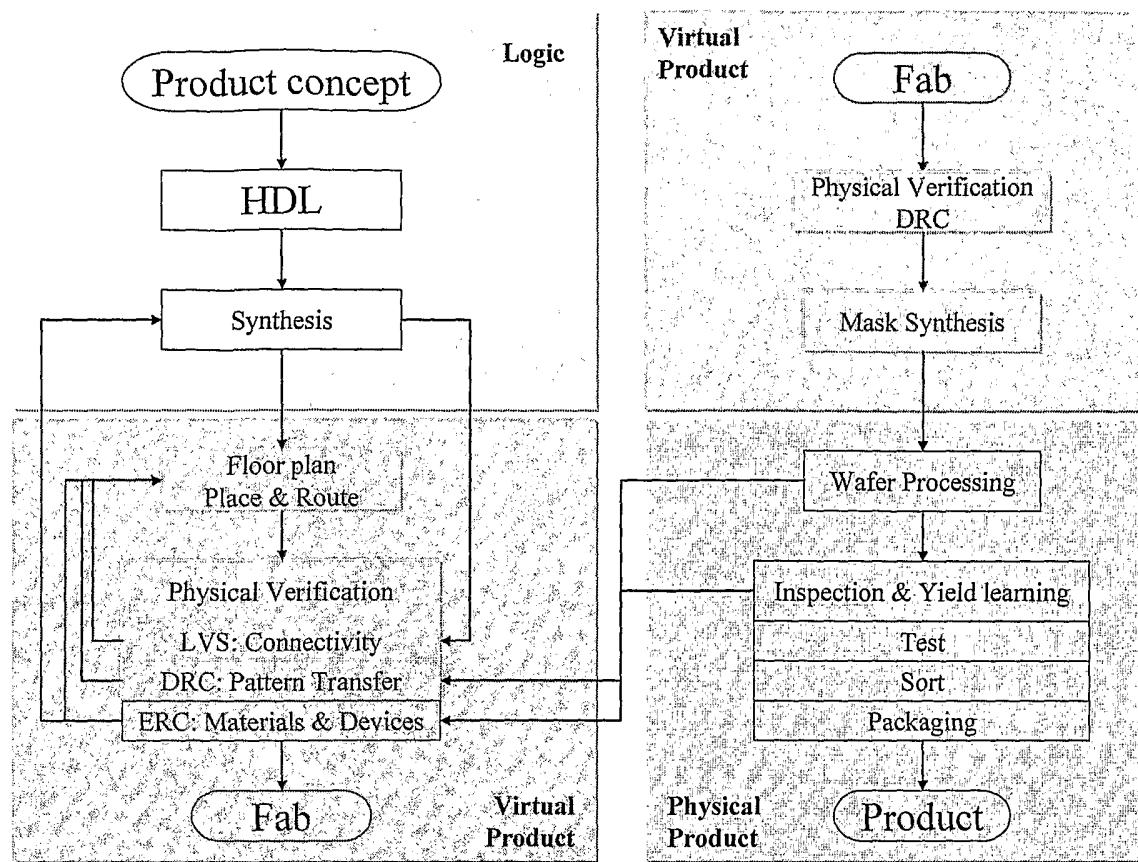

FIGURE 5 illustrates a typical IC-design flow.

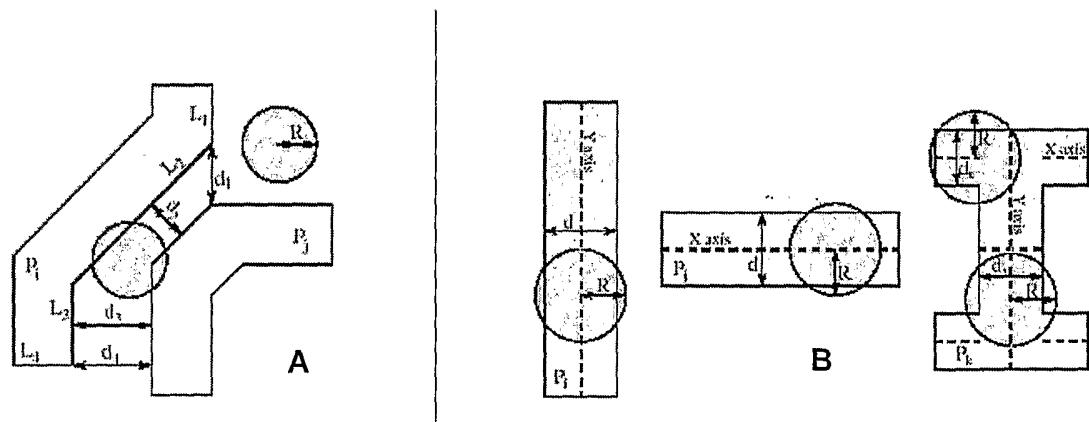

FIGURE 6 illustrates a critical area calculation depicting short (A) and open (B) defects.

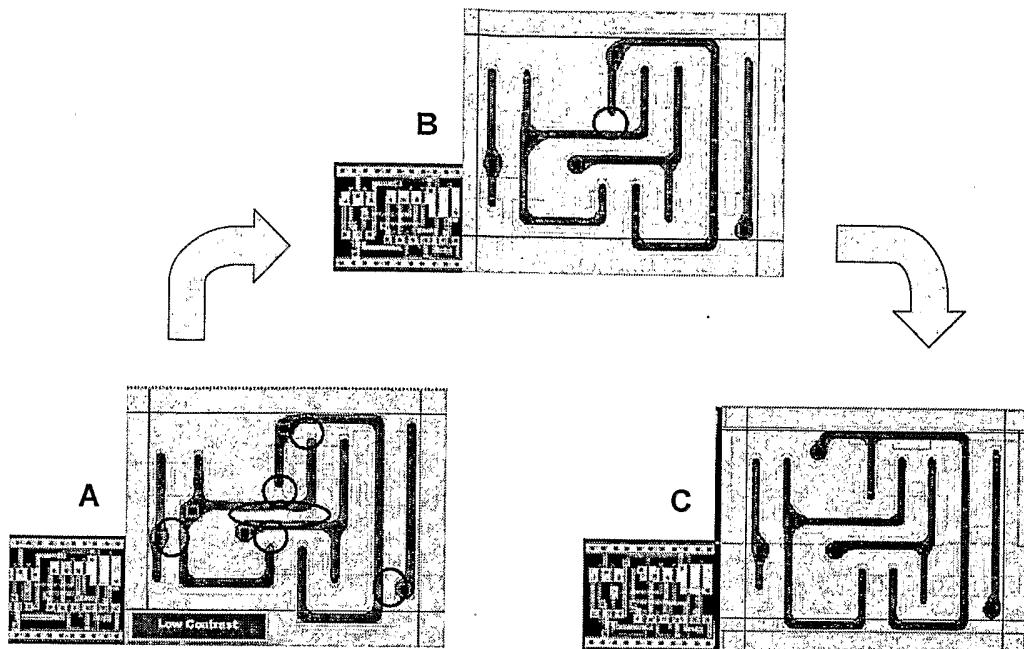

FIGURE 7 illustrates an example of contrast-based driven DFM optimization for a 130 nm standard cell. Original layout (A), Intermediate Layout (B), and Optimal Layout (C).

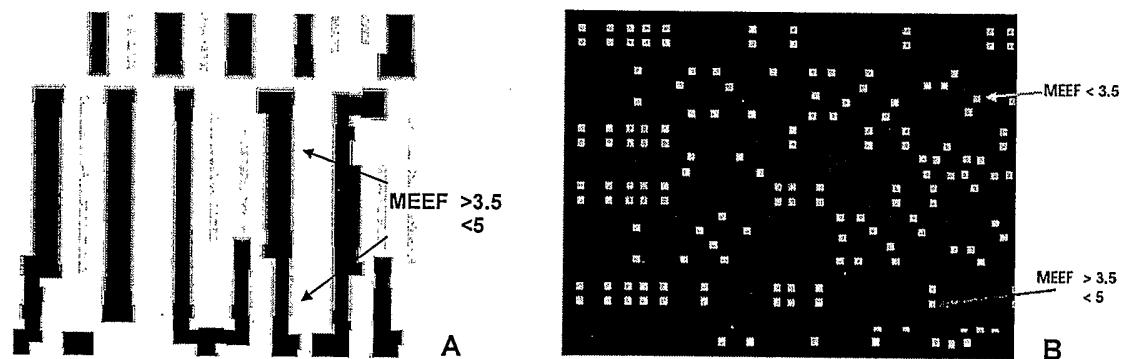

FIGURE 8 illustrates high-sensitivity feature detection: typical poly layer (A) and typical contact array (B).

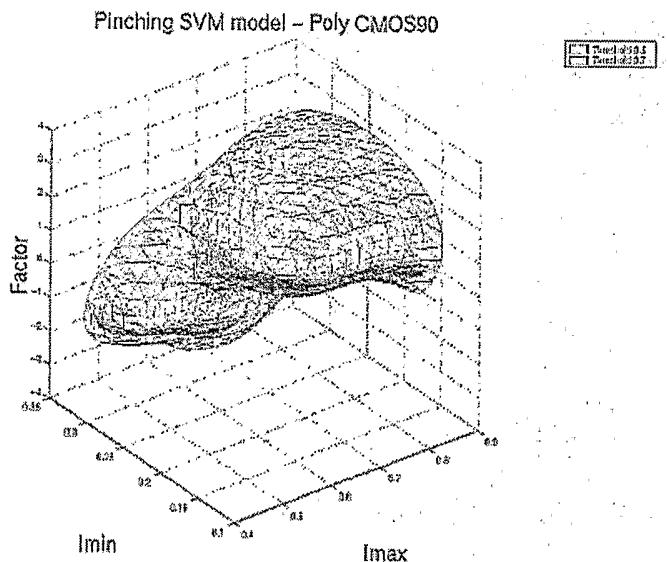

FIGURE 9 illustrates a pinch-failure model for a 90 nm process. The surface indicates the boundary between failure and robust printing.

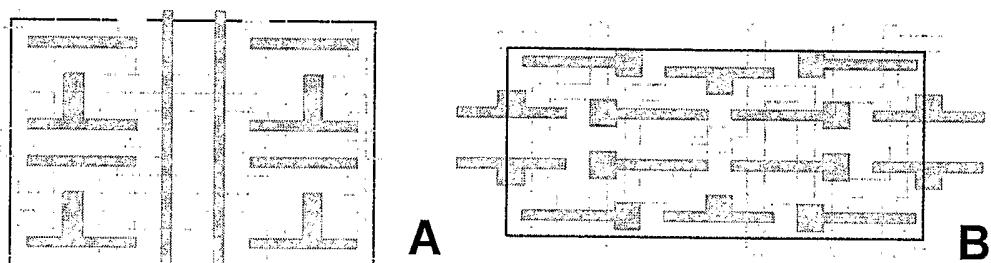

FIGURE 10 illustrates an example of restricted design rules. Polysilicon layer for a typical (A) and a more manufacturable (B) SRAM cell.

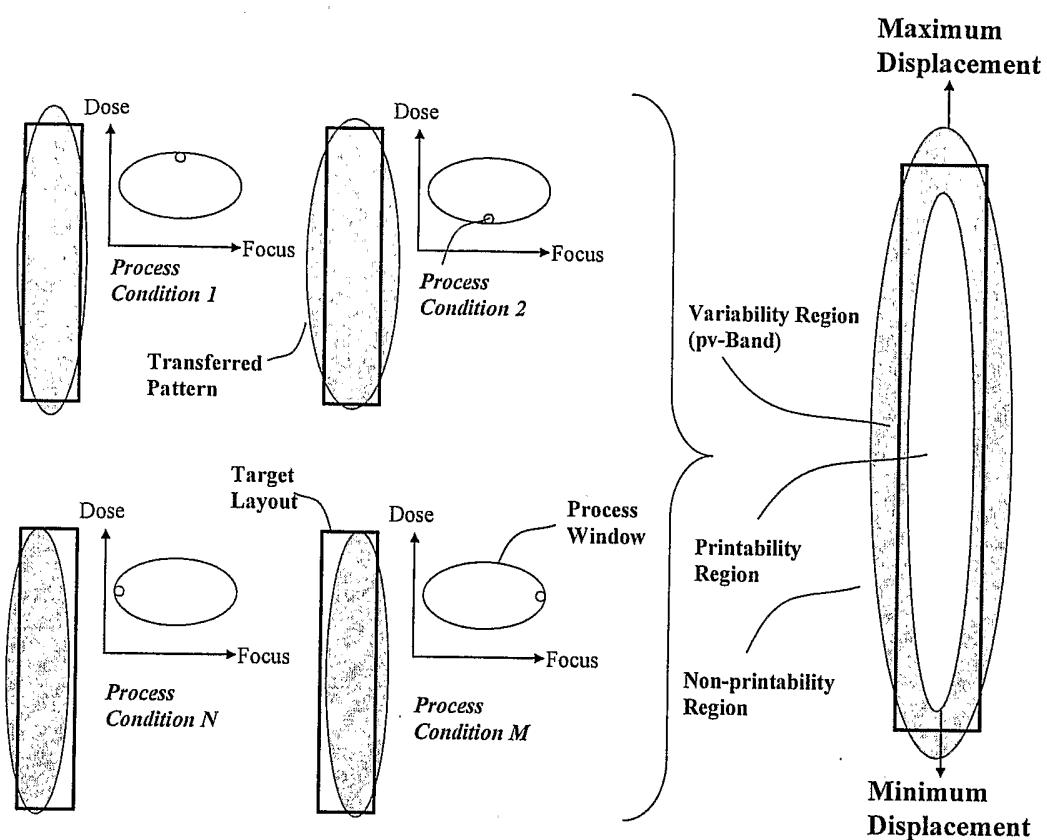

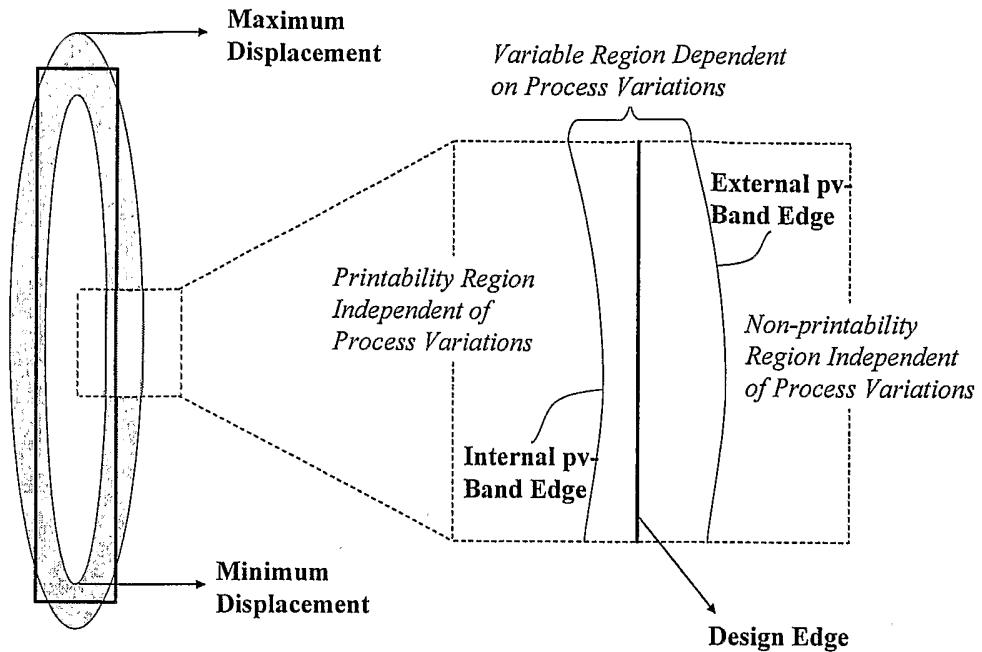

FIGURE 11 illustrates a PV-band calculation in accordance with one embodiment of the invention. At every point within the process window, a pattern transfer image is calculated. The region inside the PV-band corresponds to the constantly printing region, and the band itself (gray) corresponds to the variability region that indicates probable locations of the boundary between printing and non-printing.

FIGURE 12 illustrates PV-band elements in accordance with one embodiment of the invention. The internal PV-band edge is the boundary between the printability and variable regions. The external PV-band edge is the boundary between the variable and non-probability regions.

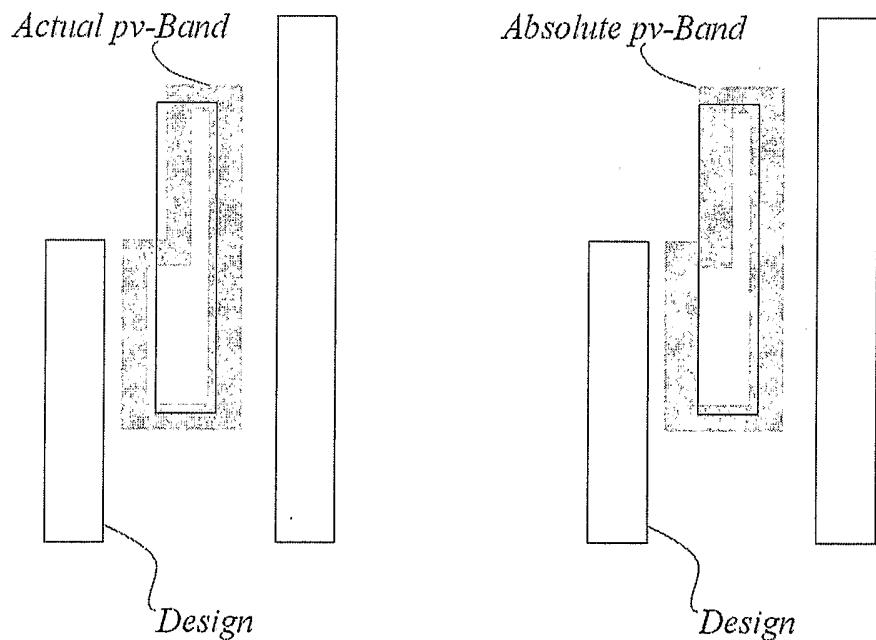

5 FIGURE 13 illustrates actual versus relative PV-bands in accordance with one embodiment of the invention.

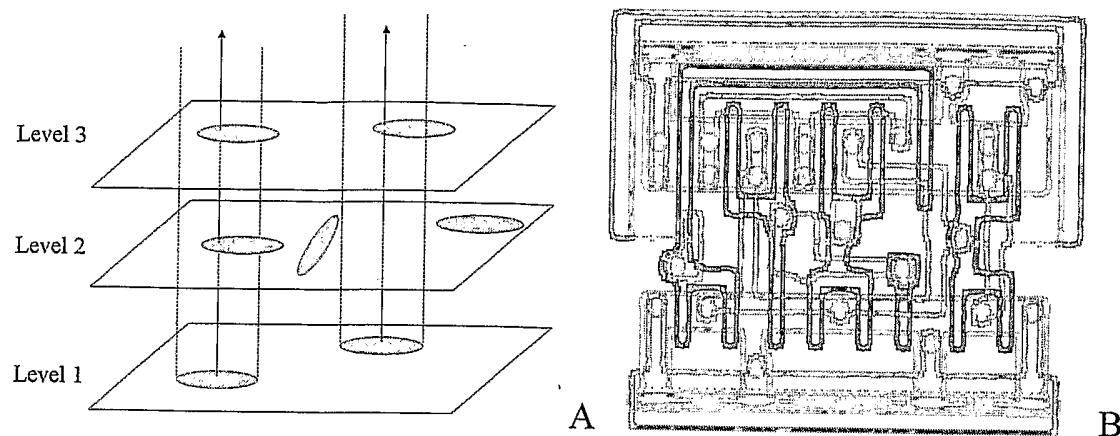

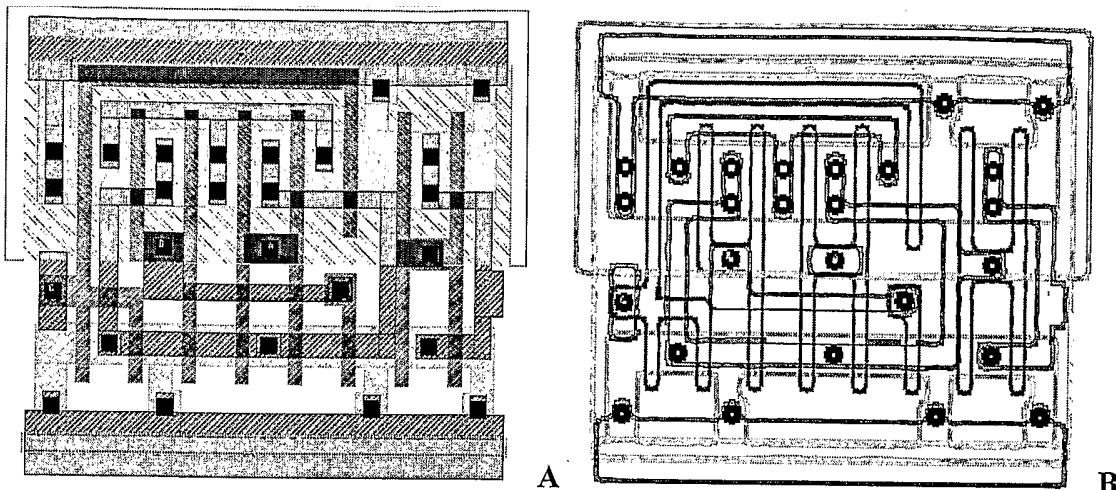

10 FIGURE 14 illustrates a layout comprising several layers, and the final composite sensitivity is a weighted combination of all individual sensitivities along the connectivity line-of-sight and the unconnected line-of-sight. A shows the concept, and B shows the actual implementation in a 130nm cell.

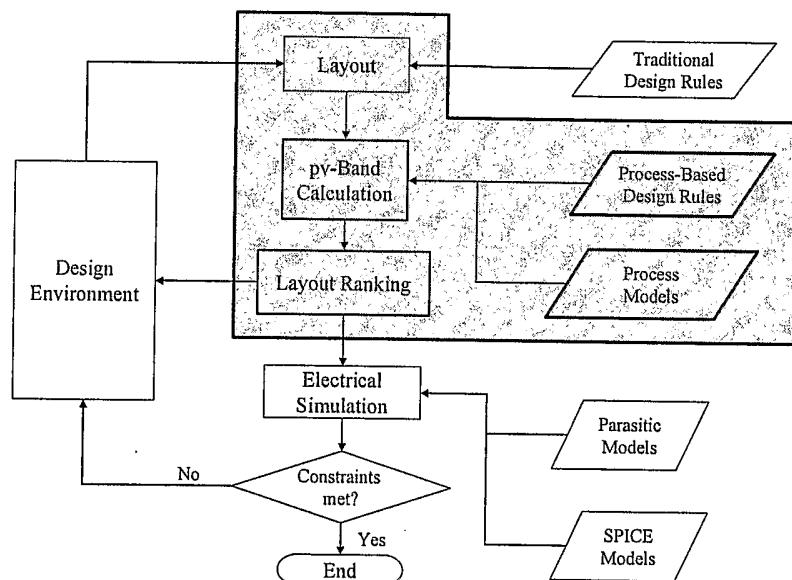

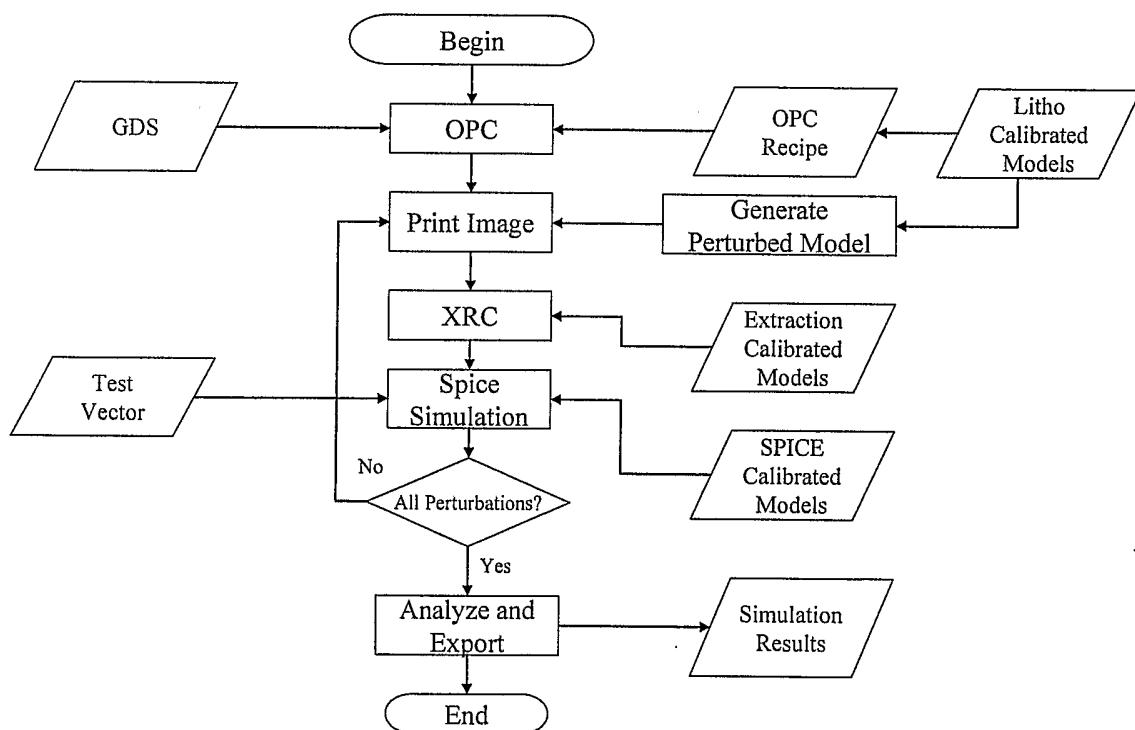

FIGURE 15 illustrates an enhanced design flow using the methodology proposed in this work in accordance with one embodiment of the invention.

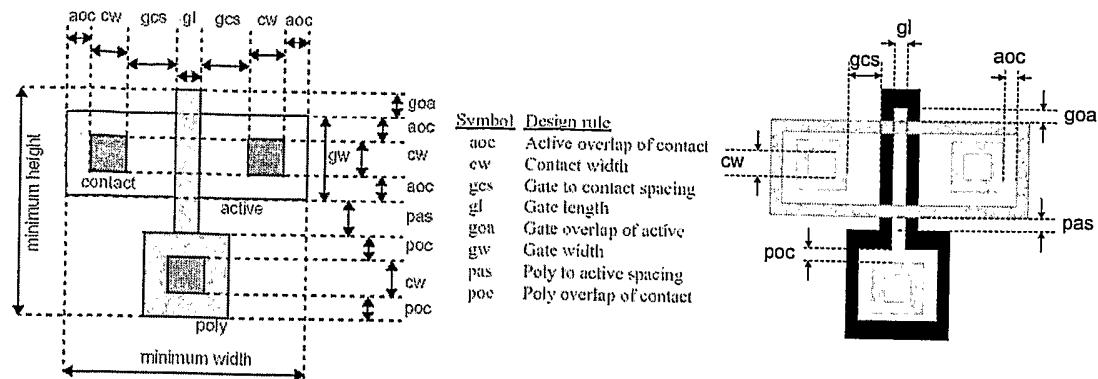

15 FIGURE 16 illustrates typical design rules (left) versus PV-band-based design rules (right) in accordance with one embodiment of the invention.

FIGURE 17 illustrates a single-layer PV-band interaction. The internal and external distances of the PV-Bands determine the pass-fail criterion.

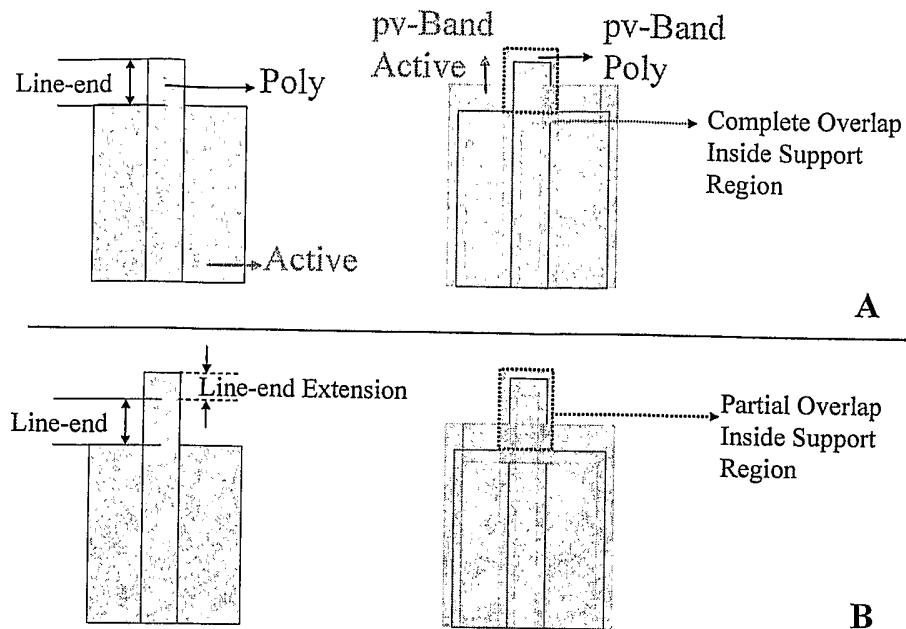

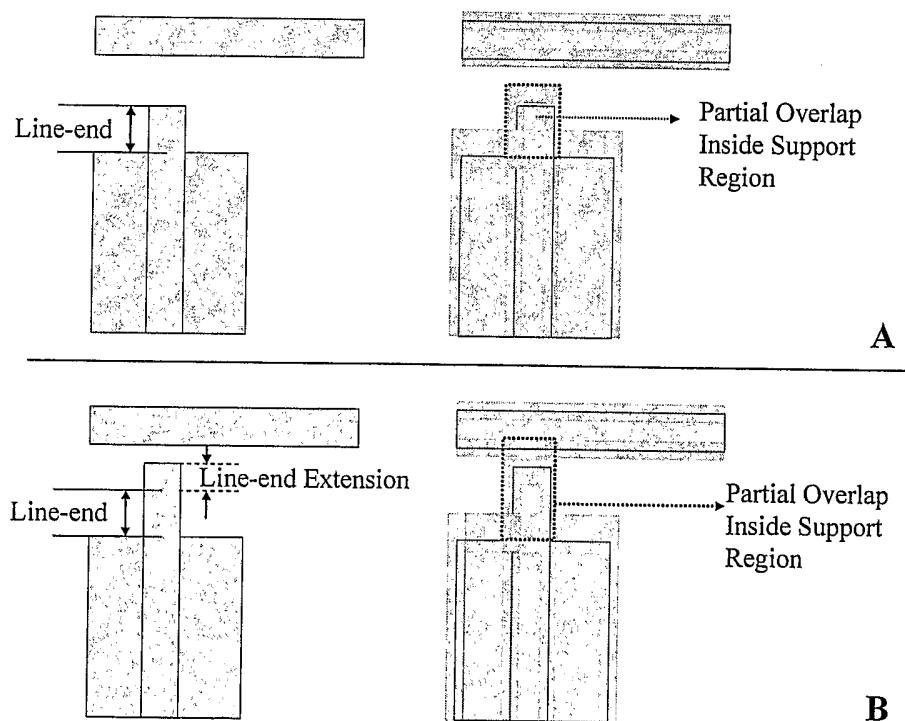

FIGURE 18 illustrates a two-layer PV-band interaction. The enclosure rules are determined by incomplete overlap existence.

20 FIGURE 19 illustrates a two-layer PV-band interaction. Different topology environment.

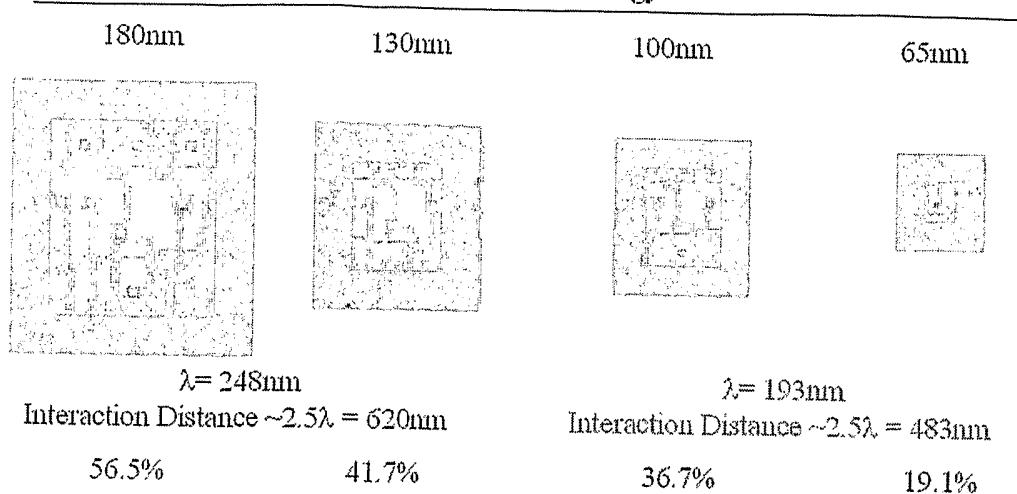

FIGURE 20 illustrates placement-independent areas for multiple process nodes.

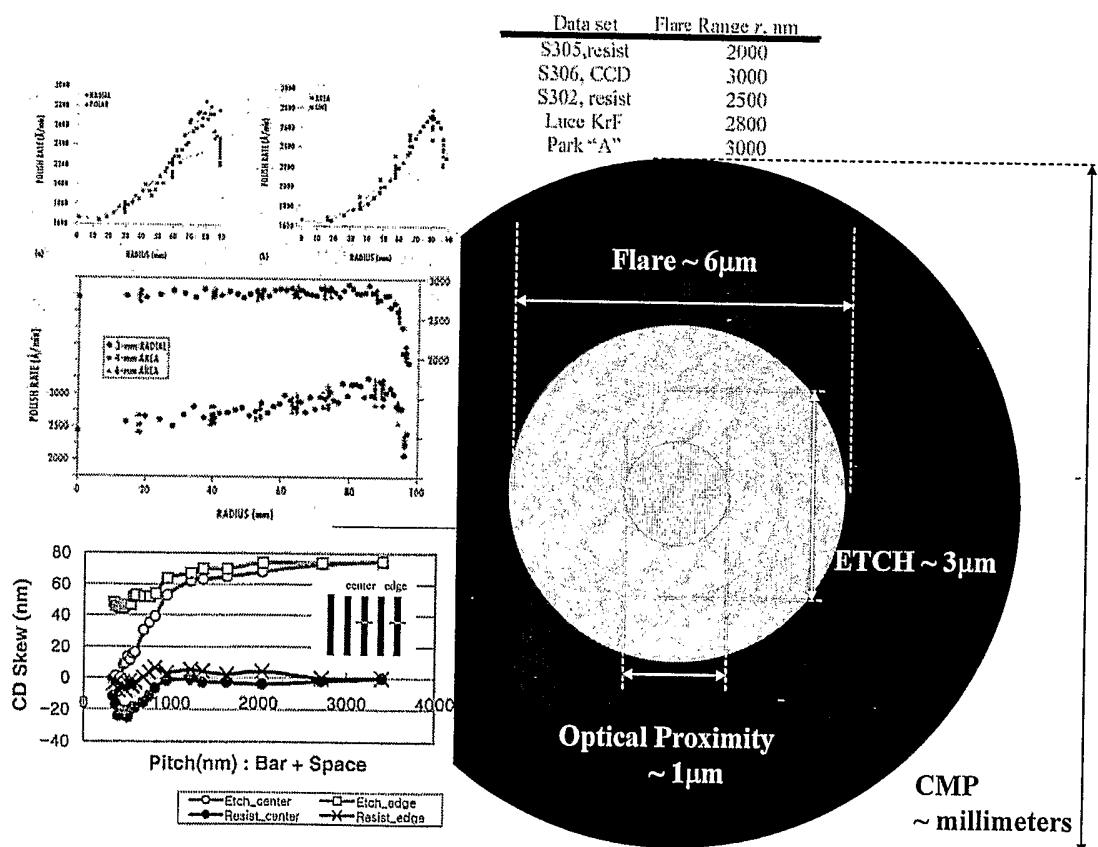

FIGURE 21 illustrates typical ranges for four mechanisms involved during pattern transfer: chemical metal polish (CMP), optical flare, etch, and optical proximity.

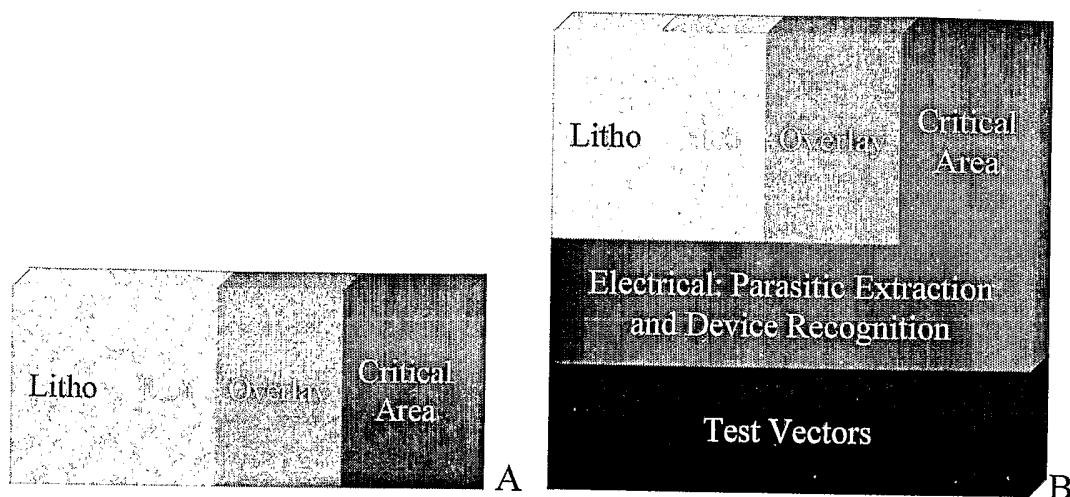

25 FIGURE 22 illustrates a DFM model proposal for analysis and correction (A); coupling the manufacturing information with electrical information to determine the functionality of a device for analysis purposes (B).

FIGURE 23 illustrates a 90 nm isolated feature with SRAF at five points of a process window.

FIGURE 24 illustrates a dense calculation of multiple process conditions.

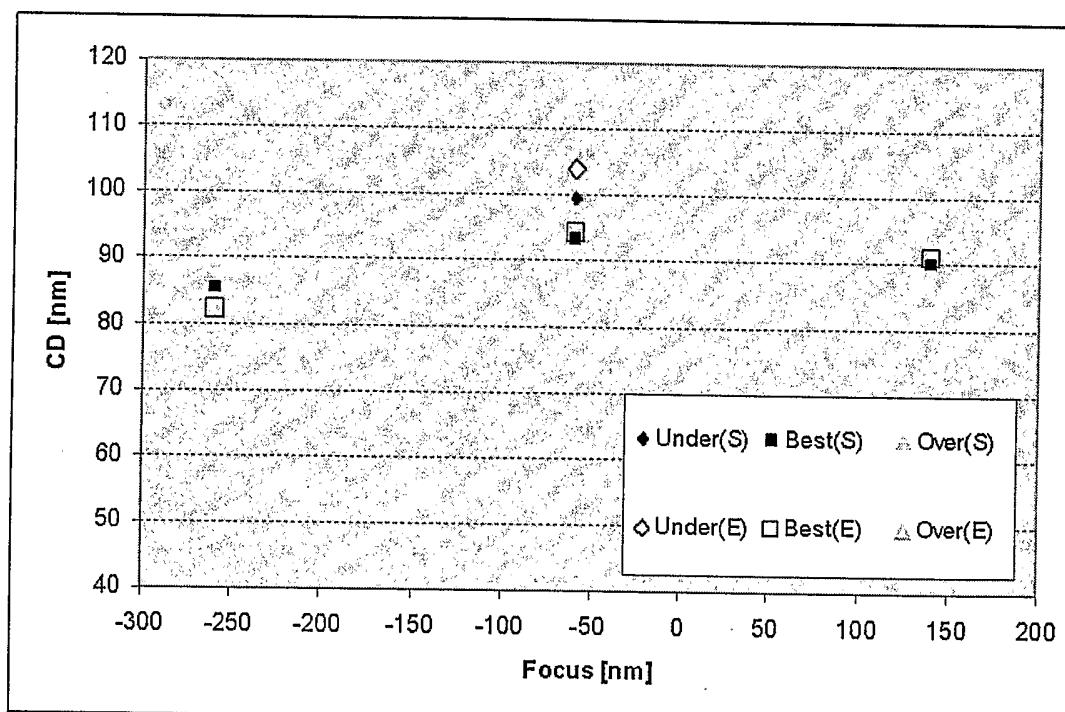

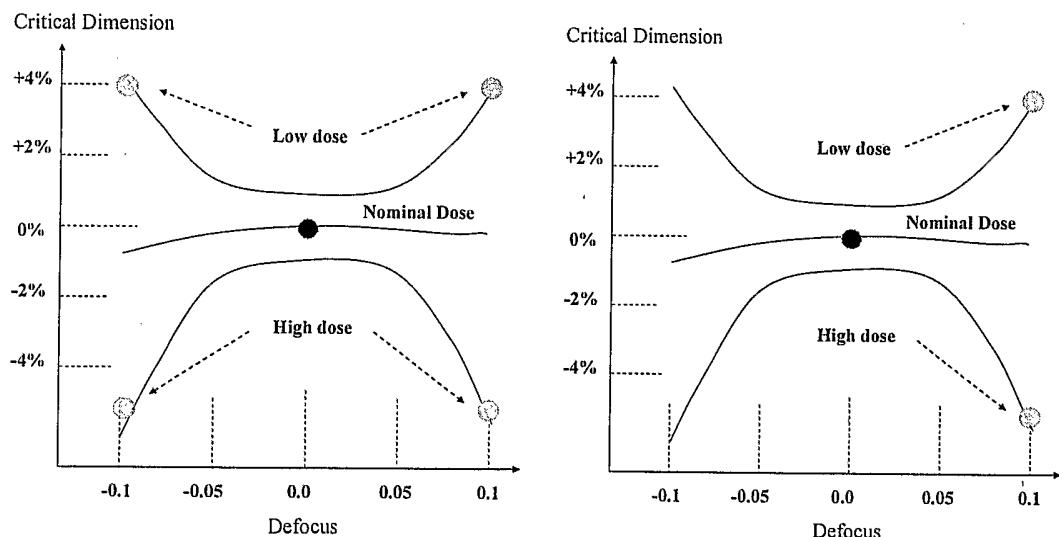

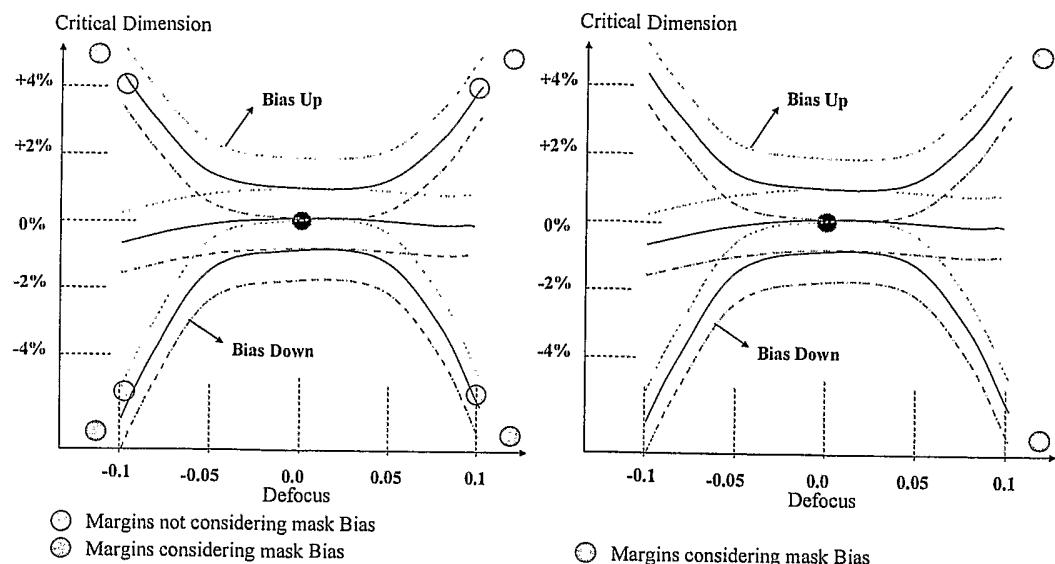

30 FIGURE 25 illustrates the Effect of Exposure Dose and Defocus for a Clear field line. Indicating four process corners (left). Indicating response corners (right).

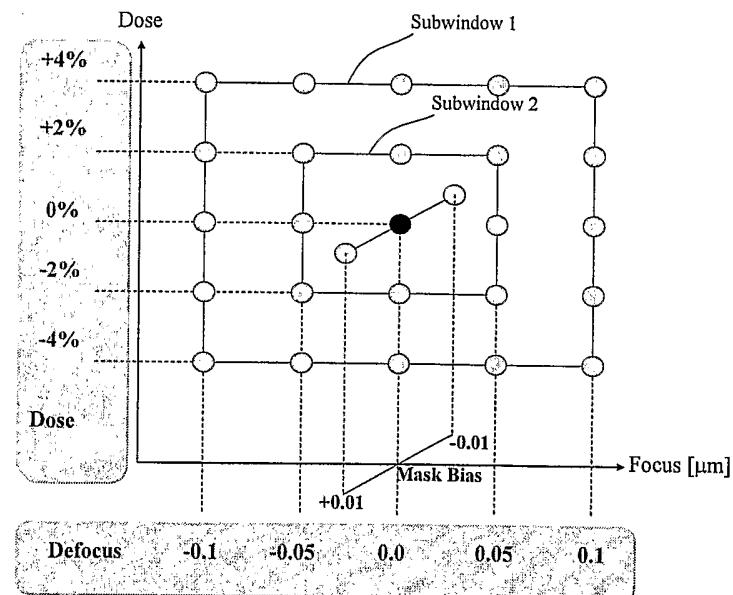

FIGURE 26 illustrates Dose, Defocus and Mask Bias variations and their impact in CD for a clear field, dark feature.

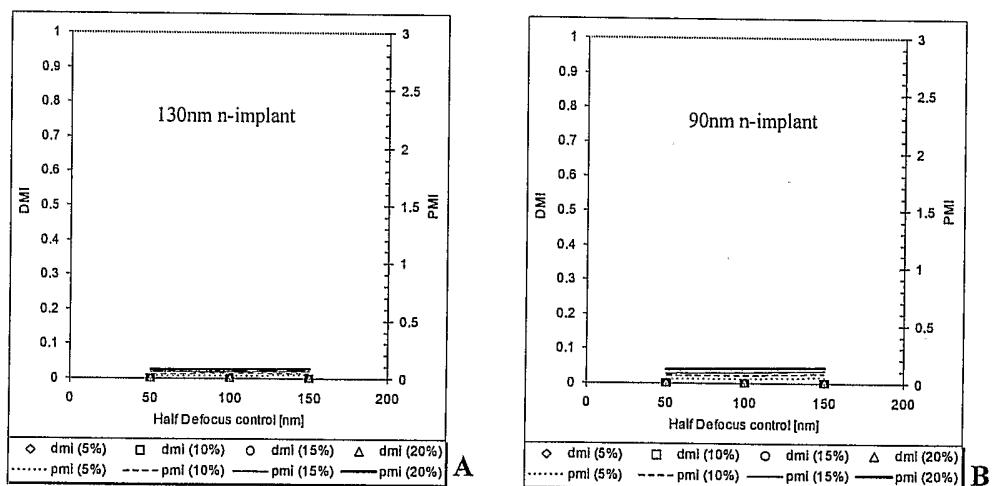

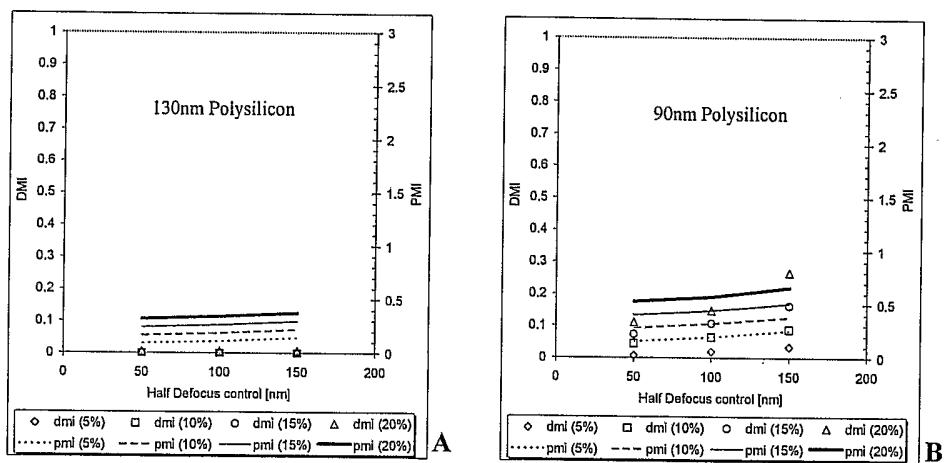

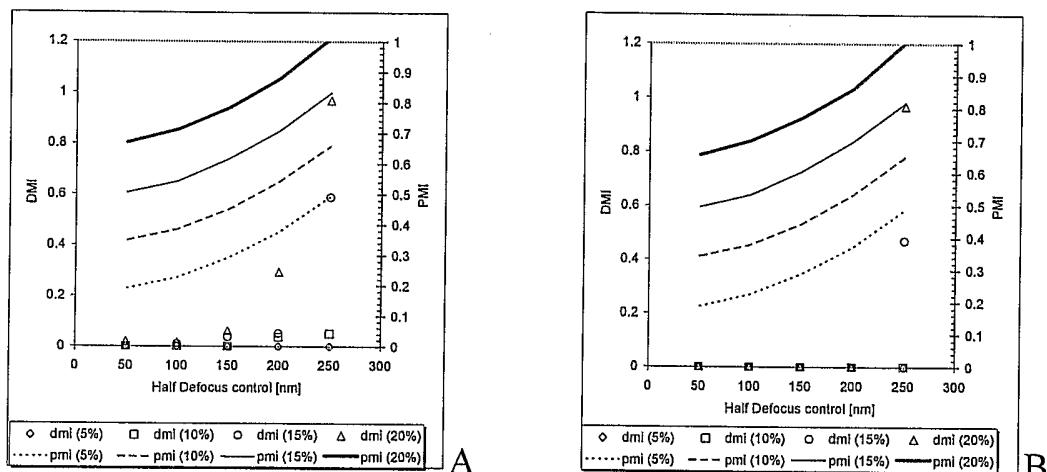

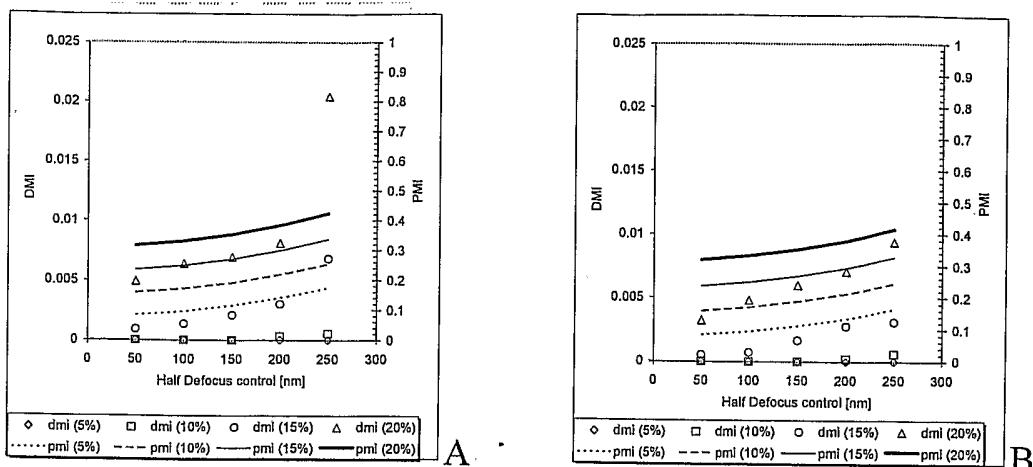

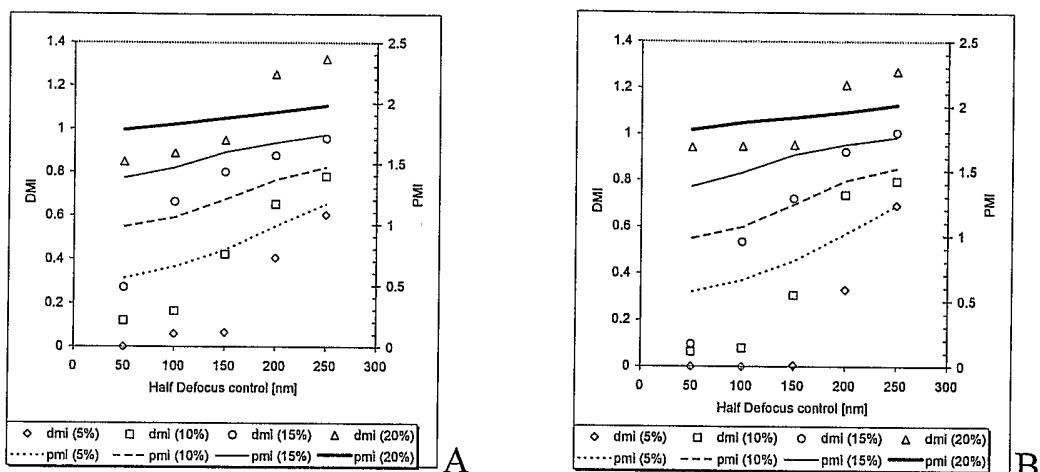

FIGURE 27 illustrates process and design variability indices for an n-implant layer: 130 nm process (A) and 90 nm process (B). n-implant layers are typically composed of large features.

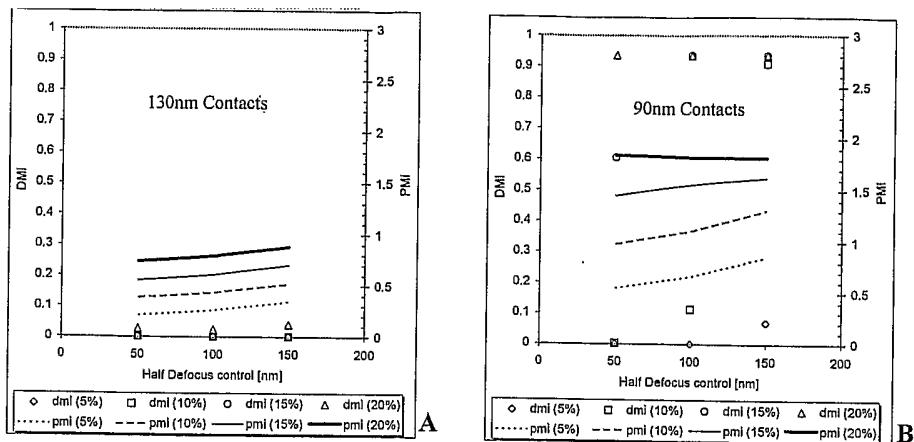

FIGURE 28 illustrates process and design variability indices for a contact layer:

5 130 nm process (A) and 90 nm process (B).

FIGURE 29 illustrates process and design variability indices for a polysilicon layer: 130 nm process (A) and 90 nm process (B).

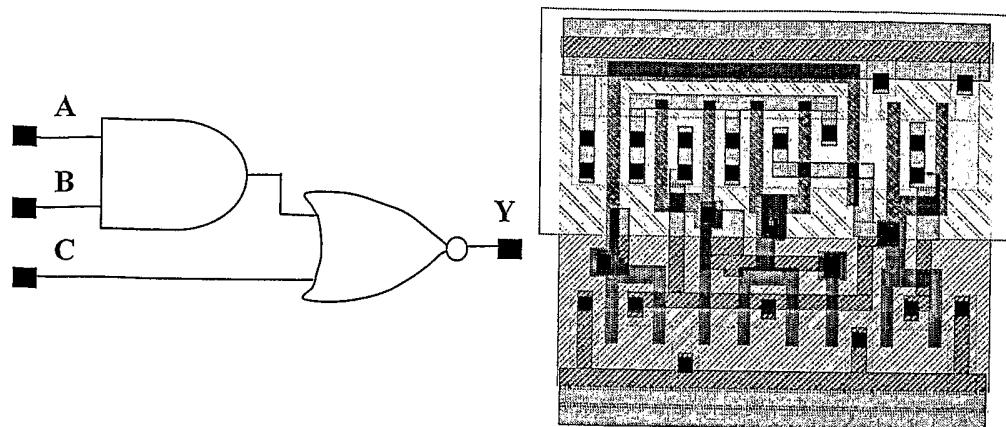

FIGURE 30 illustrates a schematic and initial physical implementation.

FIGURE 31 illustrates an event definition. Thirteen events were sampled for

10 every litho-process condition.

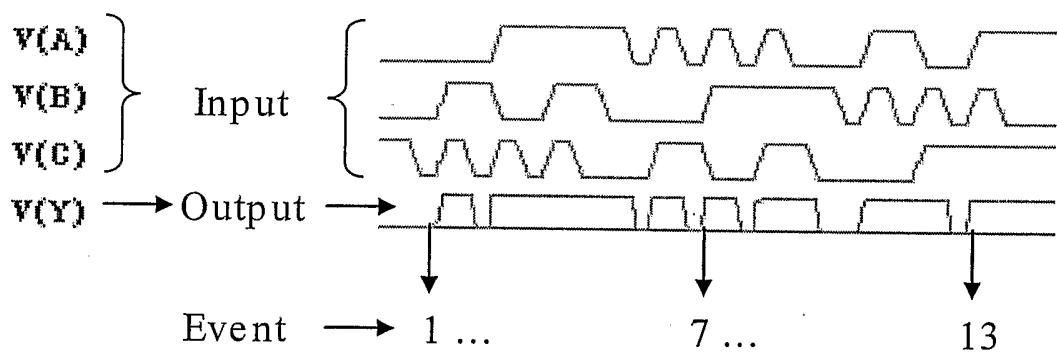

FIGURE 32 illustrates optimal 130 nm physical implementation of the test cell (A) and respective PV-Bands for all layers (B).

FIGURE 33 illustrates manufacturability indices for contacts (130 nm technology): original cell (A) and optimized cell (B).

15 FIGURE 34 illustrates manufacturability for polysilicon (130 nm technology): original cell (A) and optimized cell (B).

FIGURE 35 illustrates manufacturability indices for contacts (90 nm technology): original 130 nm cell shrunk to 90 nm (A) and optimized 130 nm cell shrunk to 90 nm (B).

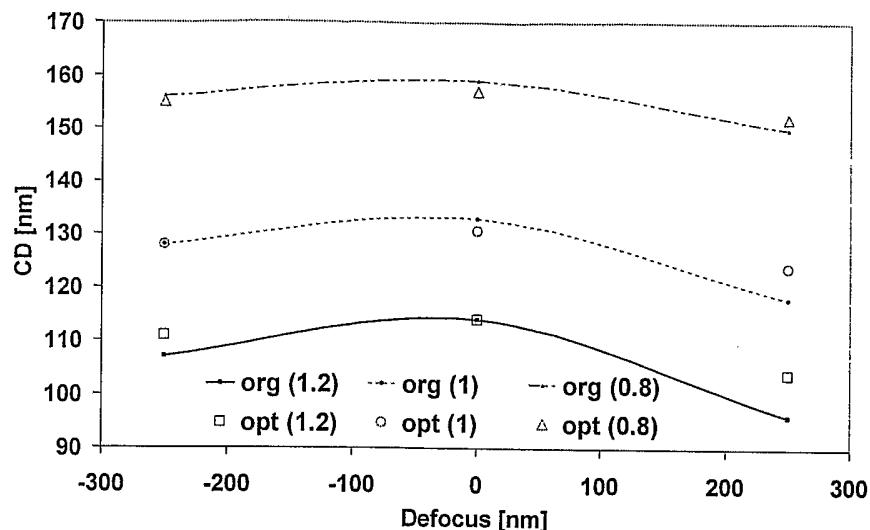

20 FIGURE 36 illustrates a focus-exposure "Bossung" graph showing the CD behavior across focus and energy dose for the same transistor.

FIGURE 37 illustrates electrical analysis for designs subject to process fluctuations during manufacturing.

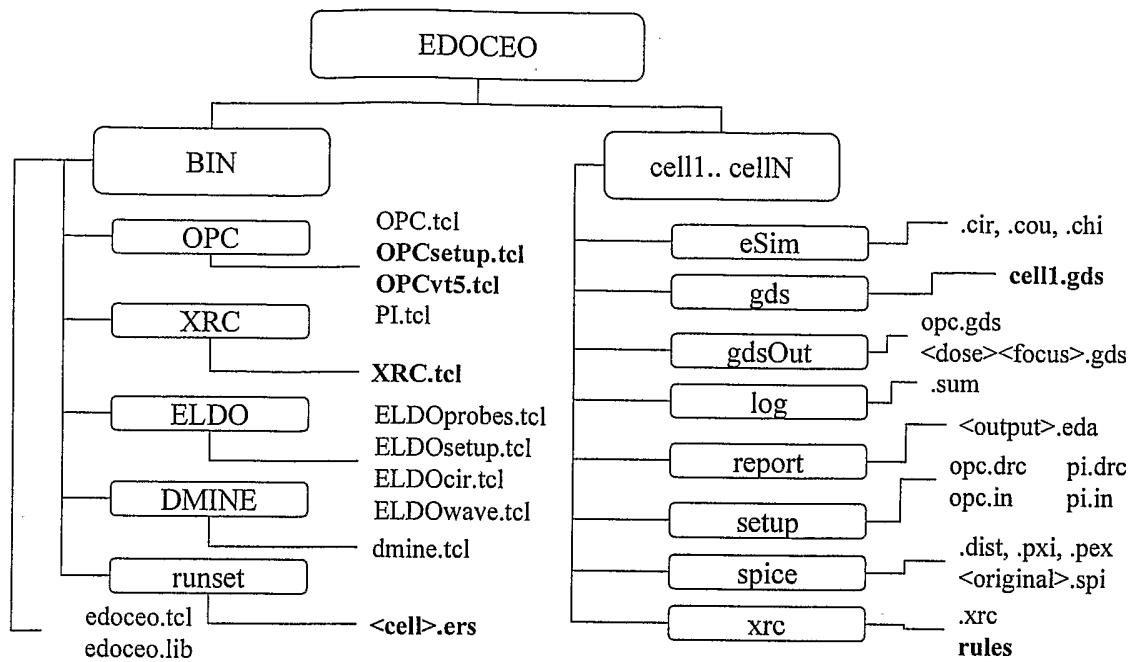

FIGURE 38 illustrates EDOCEO components.

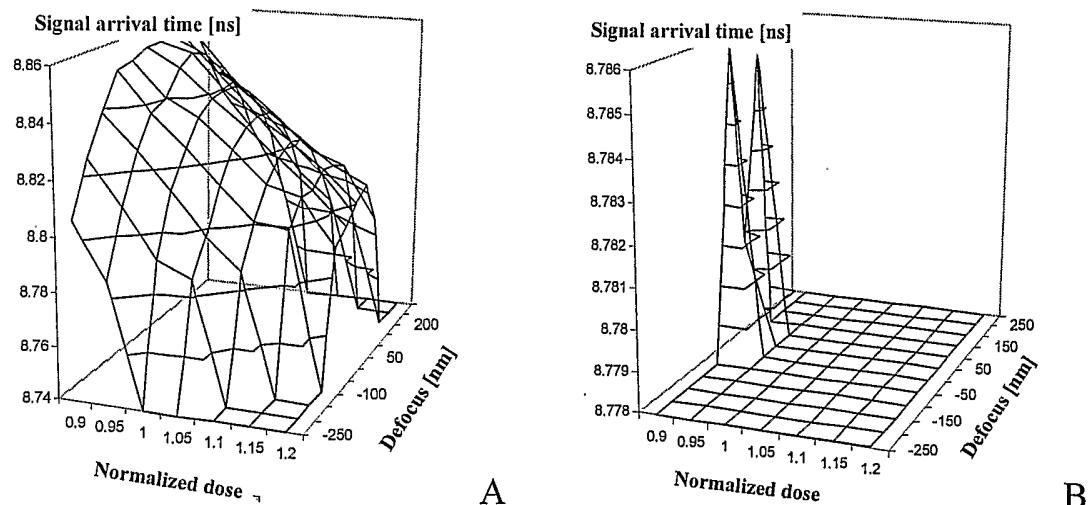

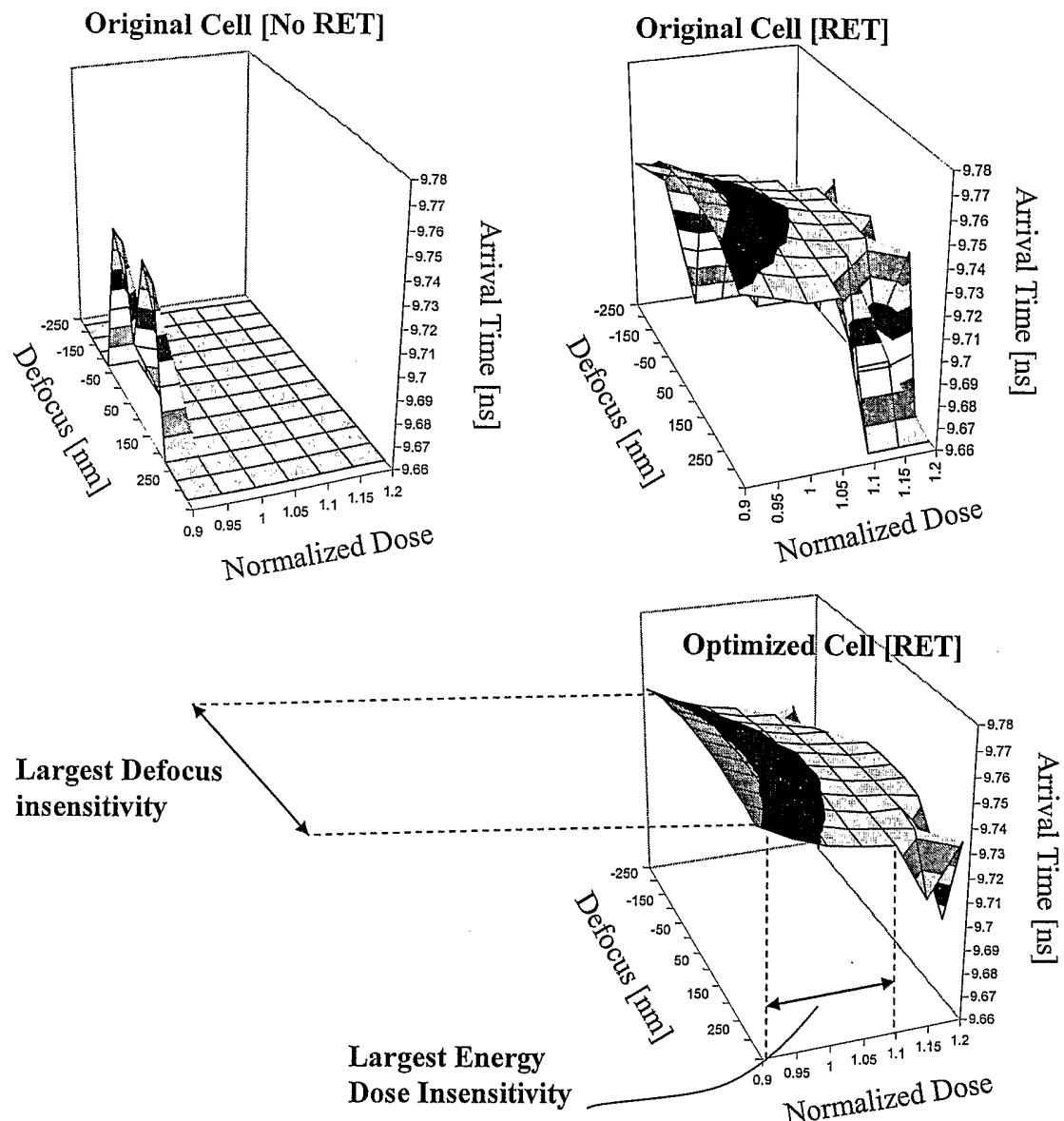

25 FIGURE 39 illustrates clocked element results: dose (front horizontal axis), focus (perpendicular to the page plane axis) and signal arrival time (vertical axis), with OPC (A) and without OPC (B).

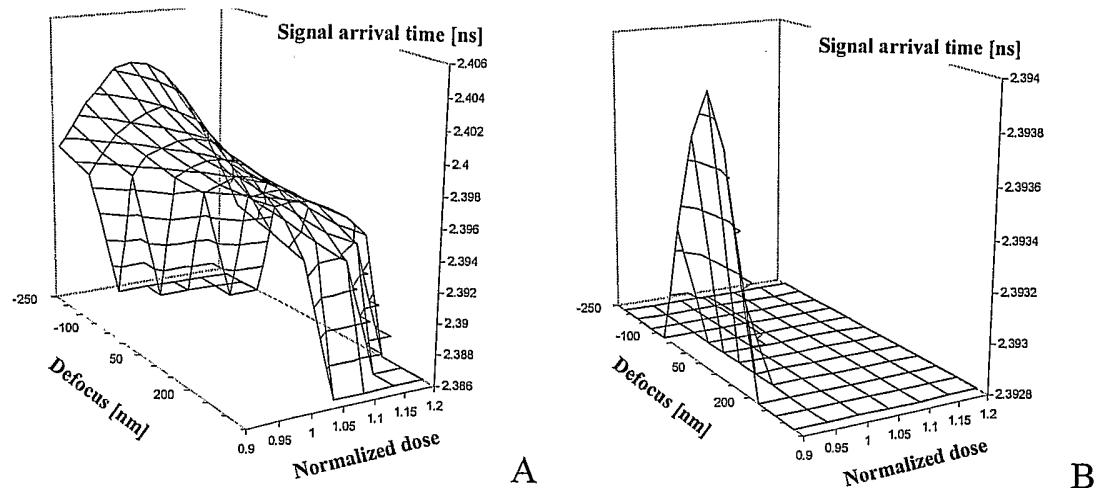

FIGURE 40 illustrates unclocked elements: dose (front horizontal axis), focus (perpendicular to the page plane axis), and signal arrival time (vertical axis), with OPC (A) and without OPC (B).

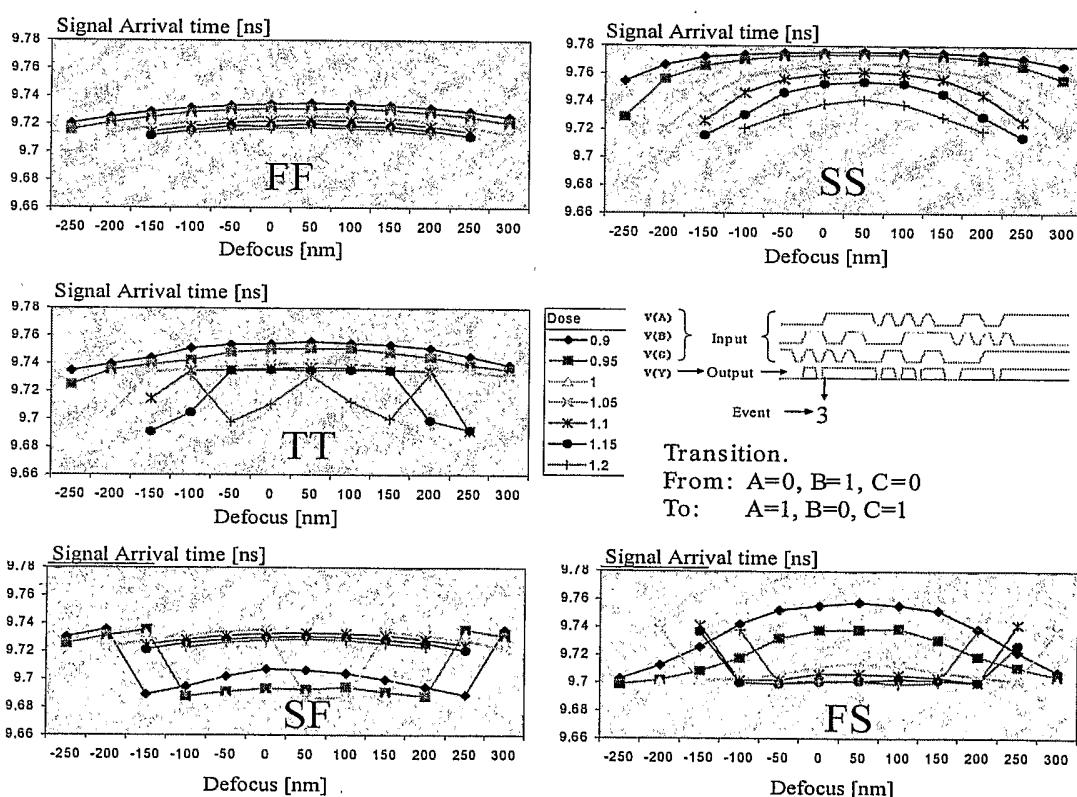

30 FIGURE 41 illustrates original cell timing: signal arrival times for event 3, using FF, SS, TT, SF and FS SPICE models.

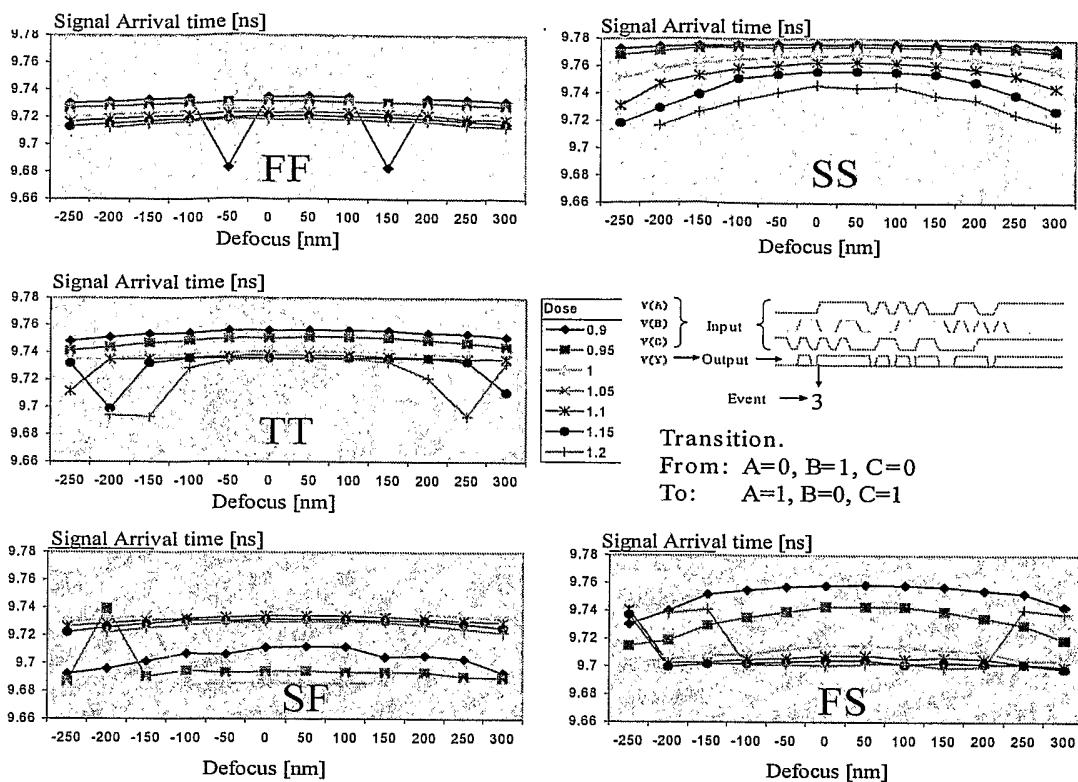

FIGURE 42 illustrates optimized cell timing: signal arrival times for event 3 using FF, SS, TT, SF and FS SPICE models.

FIGURE 43 illustrates pattern robustness translates into more consistent timing.

(Nominal SPICE model shown.)

#### DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENT

As indicated above, the present invention is a system for verifying and/or

5 classifying integrated circuit layouts and designs in accordance with anticipated

variations in the manufacturing process. Although the present invention is described with

respect to the creation of integrated circuits, it will be appreciated that the techniques of

the invention can be applied to any manufacturing process that is subject to process

variations. Examples of such processes include, but are not limited to mask bias, overlay

10 errors, film stack thickness variations, mask phase errors, post-exposure bake

temperatures, resist development times and post exposure bake times. Other devices

fabricated lithographically where this invention may be applied may include Micro-

electro-mechanical systems (MEMS), magnetic heads for disk drives, photonic devices,

diffractive optical elements, nanochannels for transporting biological molecules, etc.

15 FIGURE 0A illustrates a simplified integrated circuit layout including a pair of

objects or features 10, 12 to be created on a semiconductor wafer. In conventional

lithographic processing, a layout for an IC design is stored in a layout format, such as

GDS-II or OASISTM, that defines the objects as a number of vertices that in turn define

corresponding polygons. The edges of the polygons defined between the vertices can

20 then be further fragmented into additional, smaller edge segments and adapted to ensure

the manufacturability of the polygons on a wafer.

FIGURE 0B illustrates the polygons after a resolution enhancement technique

(RET), such as optical and process correction (OPC), is performed. In the example

shown, the OPC tool varies the polygons by biasing the edge fragments found at corners

25 of the polygons outwardly in order to compensate for line-end, shortening, and other

defects that occur during the photolithographic printing process.

Although the OPC corrected layout of the features 10, 12, shown in FIGURES 0B

compensates for expected optical distortions, such distortions are generally calculated

assuming a set of known process conditions. However, as indicated above, process

30 conditions can vary from wafer to wafer or from chip to chip within a wafer. Examples

of process conditions that may vary include, but are not limited to, focus, dose, etch

processing, polishing variations, etc.

To take into consideration how process variations will affect the objects created on a wafer, one embodiment of the invention calculates process variation bands (PV-bands) that estimate how the objects will be printed on a wafer under a variety of process conditions. As shown in FIGURE 0C, each PV-band includes an inner edge 14 that 5 defines the expected minimum area an object will occupy on a wafer when printed under all process conditions. The PV-bands also include an outer edge 16 that define the maximum size that may be occupied by the objects when printed under some process conditions. The space between the inner edge 14 and the outer edge 16 defines a zone of uncertainty where the edges of the objects may be printed depending upon process 10 conditions. Similarly, a PV-band may lack an inner edge if, under certain process conditions, an object will not print at all.

In one embodiment of the invention, the PV-bands are calculated by computing a number of silicon images of the objects under a number of process conditions. As shown in FIGURE 0D, a representative process generally has a Gaussian type distribution, 15 whereby changes in the process vary a desired effect on the wafer. The process variations may affect the position of a printed edge, the slope of the edge density, or a number of other factors that can be used to predict the final edge placement of the objects on the wafer. In one embodiment, aerial images are calculated at the nominal condition of the process, as well as at several sample points around the nominal. Those points are 20 typically supplied by a user who is familiar with actual process variations.

Increasing the number of process points for which the aerial image is computed increases the precision of the PV-band contours at the expense of increasing the processing time required to compute the PV-bands. For example, if the aerial images are calculated assuming  $N$  different variables in a process, and aerial images are computed at 25  $M$  values for each variable, then a total of  $N*M$  aerial images must be computed for each object. In one embodiment, the combination producing the smallest printing of the object is selected as the inner edge of the PV-band, and the aerial image that produces the largest printing of the object is selected as the outer edge of the PV-band.

As will be appreciated, if additional process variations are analyzed and/or if 30 additional points are analyzed for each process, the number of aerial images to be computed rises geometrically. Although each aerial image calculation can be handled by a multi-processor or parallel processing computer system, the time required to calculate the PV-bands may be a factor in selecting how many process variables and how many

sample points of each process are analyzed. One technique to reduce the number of aerial images that must be calculated is described in further detail below.

In one embodiment of the invention, the selected inner edge and outer edge of the PV-bands are stored as separate data layers of an OASIS data file, separate layers of a GDSII file or any other layout database representation. Each data layer includes a number of vertices that define the contours of the outer or inner edges of the PV-bands. 5 Alternatively, a single data layer could contain both edges of the PV-bands.

As an alternative to calculating the aerial images under a variety of different process conditions, it is also possible to estimate the variations that occur with different 10 process conditions by, for example, convolving the desired layout with a Gaussian function that is representative of the variations in process conditions.

Once the PV-bands are calculated for the objects to be created on a wafer, processing is performed with the PV-bands as surrogates for the objects to determine if the design meets acceptable criteria or if variations to the circuit layout need to be made. 15 For example, as shown in FIGURE 0C, the outer edge of the PV-band indicates that the objects 10 and 12 will blend together creating a short circuit under certain process conditions. Therefore, the designer can be alerted to this fact and can vary the layout by, for example, increasing the space between the objects 10, 12, or rearranging the layout so that the objects can be manufactured correctly regardless of process conditions. The 20 present invention can also be used to compare two or more layouts by their sensitivity to manufacturing process variations. In one embodiment, the area occupied by the PV-bands for the objects is indicative of the sensitivity of its objects to changes in process conditions. The smaller the area generally, the less sensitive the layout is to variations in the manufacturing processes. By summing the areas of all PV-bands in a layout, different 25 layouts can be ranked. The layouts can represent different circuit designs or may represent iterations of the same design in order to determine if a change has improved the manufacturability of the design.

In addition, as will be explained by further detail below, areas of interest can be defined for different object or feature types. For example, contacts or circuit vias can 30 have areas of interest that define a standard against which the feature can be compared. The PV-bands for an object are compared to the area of interest to check if the object will be formed correctly on the wafer. Alternatively, properties derived from the PV-bands such as PV-band width, area, perimeter, offset, enclosure, relative distance and overlaps

can be compared to the areas of interest. Individual objects can then be ranked based on the comparison so that a designer can redesign those objects that vary the most from an ideal standard.

FIGURE 0E illustrates one embodiment of a computer system that can be used to 5 implement the present invention. A computer 50 comprising a stand alone or linked computer system receives a set of executable instructions on a computer readable media 52 or over a communication link 54. The computer 50 executes the sequence of instructions to perform the layout and design verification methods of the present invention.

10 A layout is received from a database 56 (or may be created with a circuit design tool running on the computer 50) that defines any number of objects to be created in an integrated circuit. The computer system analyzes the layout as described briefly above and in further detail below. In one embodiment, the instructions cause the computer system to read the layout, or a portion thereof, and create PV-bands that are analyzed 15 with one or more design rules to determine whether the layout design can be manufactured given variable process conditions. In one embodiment, the computer system alerts the designer to areas or particular objects in the layout that cannot be manufactured or can rank various layouts or designs by their sensitivity to process variations.

20 If the layout does not contain any errors or violations of the rules used to analyze the PV-bands, the layout is declared "LFD CLEAN" or some other designation indicating that the design can be manufactured by the selected photolithographic process. Here, LFD is an acronym standing for "Litho-Friendly Design". This is a term currently being used for layouts and designs with no detected manufacturability errors that have been "passed" 25 for manufacturing, just as layouts that are "DRC CLEAN" are those with no design rule violations that have been "passed" for manufacturing. If desired, additional tools can analyze the design or the layout to ensure that it has the desired electrical characteristics once the manufacturability is confirmed. The computer system 50 then can forward the verified layout or design over a communication link 60 or on one or more computer 30 readable media 62 to a mask writing tool 70. The mask writing tool then produces a number of masks or reticles that are used to produce the IC according to the specifications of the design using the selected photolithographic process.

Alternatively, the computer system 50 may transmit all or a portion of the layout or design to a remote computer system 80 over a wired or wireless communication link 74. The remote computer system 80 may be inside or outside of the United States. The remote computer system 80 can then generate and/or analyze the PV-bands for the 5 layout and can analyze the PV-bands with one or more design rules. Upon checking, the corrected layout can be returned to the computer system 50 over the communication link 74. Alternatively, the computer system 80 can send the corrected layout directly to the mask writing tool 70.

As discussed above, during the design stage of integrated circuits (ICs), electronic 10 designers have relied on functional and physical verification. The objective of functional verification is to determine the electrical correctness of the design; physical verification assures that an IC design will yield sufficient quantities to make the IC product commercially viable.

As we approach volume production of 90 nm devices, enter prototype production 15 of 65 nm and carry out active research for 45 nm and 32 nm processes, there is one clear trend: the interdependence of manufacturing and design processes necessary to build integrated circuits has reached the point where an insufficient description of the process in physical verification design rules seriously jeopardizes the successful production of advanced microelectronic devices.

Existing physical verification design rules are primarily geometric in nature (e.g., spacing, enclosure, width, connectivity and area checks). These geometrical rules are empirical approximations of complex manufacturing behavior that includes optical, chemical and electrical phenomena. Unfortunately, the process and design communities have acknowledged that the current process information being transferred to the designer 20 is no longer sufficient. Evidence of this lack of relevant process information during the design stage has been quantified in the form of historical yield learning curves and maximum attainable yield information. The study of such data indicates a decline in yield for the past process generations from a half micron to 180 nm.

To comprehend why newer process generations seem to produce lower maximum 30 attainable yields (as shown in FIGURE 1), it is important to understand the mechanisms that produce yield loss. Yield-loss mechanisms can be classified in two groups: random and systematic. The random classification includes particle contamination, scratches, solvent drips, residues, dose or focus drift and vibrations, and can be minimized only

5 during the manufacture of a product. The second classification refers to predictable and reproducible phenomena that in principle can be pre-corrected. For example, by introducing optical proximity corrections it is possible to prevent lithography-induced, iso-dense biases. Similarly, dummy fill insertion is routinely used to minimize the feature degradation that arises from chemical and mechanical polishing (CMP) or optical flare induced by heterogeneous density environments.

10 Traditionally, there has been a strong drive to minimize the random components of yield loss, and special emphasis has been placed on reducing the concentration of particles that can land on the surface of a device. In 1995, Stapper and Rosnerin made an important observation: "The inverse-cube probability distribution function for defect sizes has an interesting consequence. It causes the random defect yield to remain invariant when linearly shrinking the ground rules of the photolithographic patterns and hence the chip dimensions." If this observation were correct, the yield curves presented in FIGURE 1 should fluctuate around the same maximum yield number after the process 15 is mature. Unfortunately, this finding applies only to processes where supra-wavelength effects dominate.

20 Prior to 1995, the wavelength of light was equal to or smaller than the target feature to be printed by the lithography process. FIGURE 2A shows a well publicized graph that ties target feature dimensions to the wavelength used by the lithography process. Although resolution depends on many other variables in addition to wavelength, this graph nevertheless provides a good qualitative description of the effects that yield analysis tools need to address in order to process features smaller than a quarter micron.

25 FIGURE 2B presents the maximum attainable yield per feature size and the yield learning curve for each process for a large variety of products and process implementations. The arrows connecting insets A and B attempt to qualitatively correlate the sudden jump in yield-loss to the size of the sub-wavelength gap. Interestingly, 180 nm processes were the first to introduce rudimentary forms of optical proximity corrections that are now used extensively and in more advanced forms for all processes with target features smaller than 130 nm.

30 At this point, it would be sensible to assume these new resolution enhancement technologies (RET) could fill the sub-wavelength gap, as they have successfully done until now. Although certain new RET methods can in theory address these problems, they do so only for specific patterns or geometric topologies. This means that for any

sub-wavelength process, there will be specific restrictions that, unless implemented, will cause the resolution to remain limited by the more traditional optical limits of numerical aperture, partial coherence and wavelength.

It is now possible to extend the classification of yield loss mechanisms by 5 including explicitly process variations. This is necessary because a complete elimination of the systematic yield-loss components would require an absolute and perfect control of the defining process variables. Since such precise control does not exist for any real processes, all yield-loss mechanisms have in essence a random origin. However, the impact these random variations will have on the design depends on the systematic 10 sensitivity of a given element to the type and magnitude of the process variation.

For example, imagine variations in the thickness of the resist. This variation translates into different defocus conditions between dies or wafers. Recent studies place the intrinsic process control within a wafer at about 20 nm for one standard deviation. Since processes should typically be controlled within six standard deviations, the intrinsic 15 requirement for depth of focus (DOF) is about 240 nm.

How much a process fluctuation affects the final yield depends on the magnitude and systematic sensitivity of the design to such variation. By following a statistical process fluctuation approach, Bowman determined that the impact of these random process fluctuations could mean a loss in performance equivalent to a process generation 20 (FIGURE 4).

What Bowman's work does not consider is that the process fluctuations do not affect all features in the design equally. Thus, even if the process variation itself cannot be completely eliminated, it is possible to minimize the sensitivity to this variation by modifying the layout.

25 Process variations can be observed at the topological or the electrical level. The topological level refers to the shape and physical attributes of the devices, including critical dimension (CD), minimum pitch and pattern density. Depending on the topological change, the electrical behavior can be affected if the variations occur in electrically sensitive areas of the design (e.g., polysilicon gate width differences between 30 a pair of matched transistors, or narrowing of long metal lines that subsequently increase resistance). At the same time, topological changes induced by some types of dummy fill, short interconnect paths or noncritical corners of diffusion layers will not present any observable differences in the electrical behavior of the devices.

Until now, shape-centric parameters such as fidelity (achieved by aggressive RET) and pattern robustness (achieved by manufacturing-aware design) have been primarily considered in the manufacturability of designs. However, other processing effects that are less dependent on shape or structure can also contribute to the final 5 operation of the electronic devices. For example, even when poly gate widths are perfectly matched and robustly built, processing steps such as ion implantation, diffusion or material selection can make an otherwise correct design fail.

With the former paragraph in mind, the present invention applies relevant DFM principles to the topological or shape aspects of manufacturing. The description set forth 10 below does not include the material science or electrical characterization aspects necessary for a complete description of the manufacture of integrated circuits. Instead, it quantifies some electrical variables that shape and topology have on the electrical behavior of devices.

While the present invention is primarily directed to shape-related effects, it will be 15 appreciated that the invention can be extended to non-shape-related effects (such as lack of adequate processing materials or quantum tunneling).

## 1.2 TOWARD AN IC-DFM METHODOLOGY

At present, there are widely known DFM principles, many of which are directly applicable to IC manufacturing, as described by D. M. Anderson (2004):

- 20 • Understand manufacturing problems: Issues of current/past products.

- Design for easy fabrication, processing, and assembly.

- Adhere to specific process design guidelines.

- Minimize tooling complexity by concurrently designing tooling.

- Specify optimal tolerances for a Robust Design.

- 25 • Understand tolerance step functions and specify tolerances wisely.

DFM concepts have already been demonstrated in other manufacturing fields (e.g., automotive and consumer products) and provide clear competitive advantages applicable to any manufacturing business.

- 30 • Product design establishes the feature set, how well the features work, hence the marketability of the product.

- The product development process determines how quickly a new product can be introduced into the marketplace.

- The product design determines how easily the product is manufactured and how easy it will be to introduce manufacturing improvements.

5 The value associated with these concepts has propelled a strong interest in the semiconductor industry. Unfortunately, while there is no shortage of ideas about the objective of DFM, there is no general agreement on the specifics. In other words, there is agreement on the outcome of DFM, but there is no consensus on how to achieve it. Considering all the requirements expressed by many authors, perhaps Liebmann has laid out the best general requirements of a successful DFM system:

- *Improve manufacturability at extremely aggressive patterning resolution:* A layout that does not rely on tight control of 2-d detail will function even within the limitations of two-beam imaging lithography.

- *Ensure migrateability of designs into future technology nodes:* The resource and time investment in a new layout make it necessary to use a given chip design for multiple technology generations with minimal redesign effort.

- *Allow for density- and performance-competitive chip designs:* Constraints that optimize lithography but erase any benefit of moving to the next technology node do not make sense.

- *Address a broad spectrum of customer objectives with a single design and process solution:* To leverage the cost of mask and wafer manufacturing, different customers' needs have to be addressed with a common process solution.

25 Before proposing and presenting existing new approaches to DFM, it is important to know about existing IC-design flows. These are extremely varied and evolving constantly. FIGURE 5 depicts a typical IC design flow in very general terms by grouping the design and production activities into three main categories: logic, virtual product and physical product.

30 This organization is based on the evolution of the product, which means that during the logic design, the objective is to capture the functional requirements established by the product concept. At this point the product has incorporated very little information about its final implementation and remains at a conceptual or architectural stage. As the different operations progress, the product starts to take a virtual form in which macros,

cells and libraries are first generated. More information is needed about the final implementation of the product, and continuing verification steps are needed.

The first step involves a layout vs. schematic (LVS, also known as layout vs. source) check in which primarily connectivity and consistency between the logic and the physical objects is compared. A second verification, commonly known as Design Rule Check (DRC), is used mainly to address pattern transfer and pattern integration issues during manufacturing. Finally, an Electrical Rule Check (ERC) evaluates the electrical behavior of devices in the context of the product by performing a thorough characterization of the process. Especially important are effects such as resistance, capacitance and inductance, which are specific to the final topology and material selection.

The product remains in a virtual state while transferred from the design teams to the fabrication facilities (Fab). After the information arrives at the Fab, it is checked again for pattern transfer-related issues. Mask synthesis operations are used to further modify the layout to make it more manufacturable by using Resolution Enhancement Technologies (RET), fill for CMP planarization and data fracturing for mask production. The mask synthesis should be done for each level in the virtual product.

When there are no further modifications to the virtual product, actual manufacturing can proceed. It is at this point that the product takes its final physical form, so it can be inspected, tested, sorted and packaged for distribution. It is also at this stage that the process groups can learn about the problematic topologies or configurations that present a challenge for manufacture, and learn more about the actual performance of the materials being used. Newly acquired data is gathered, and ERC and DRC rules are constantly updated to represent the present state of the process.

As of today, multiple companies have tools to efficiently perform a typical design flow. In 1999, Weiler and Schellenberg expressed the need to integrate existing design and manufacturing tools into a single flow that could provide the basis for a DFM system, but five years later little has been done in the realm of DFM.

The main impediments to a more general adoption of DFM in the IC industry were the advent and subsequent success of RET. RET operations started to gain momentum in 1999 and were widely used, allowing the other parts of the current infrastructure to remain almost unaltered. Only the mask synthesis operation had to undergo a fundamental transformation. Although prior to sub-wavelength, simple

Boolean operations, rotations and fracturing were required to manufacture a successful mask, a complete series of more radical modifications was necessary to guarantee an adequate pattern fidelity. The success of RET and the difficulty of achieving continuous and seamless communication between production and design teams have encouraged IC 5 and EDA companies to focus their resources on RET activities while accomplishing little in the area of more general approaches to DFM. When performed properly, DFM refers to the action of making modifications to the "target" layout; by contrast, RET makes modifications to the layout so that it can meet the given "target".

Now that the relative effectiveness of RET is diminishing with each successive 10 process node, true DFM activities need to be studied and evaluated. The hardware used for production is reaching its resolution limits, and layout sensitivities to process variations account for a large (although not yet well defined) contribution to yield loss.

One of the challenges for a successful implementation of DFM is the lack of a framework to guide it. The large number of experiments needed to quantify the 15 manufacturability of a design, by using simple extensions to traditional verification and correction methods, makes such approach impractical. The point of having a framework is to provide a predefined set of guidelines for integrating the available knowledge into a consistent and compact formulation that can be used to compensate for manufacturing variations. This means that the framework has to provide a mechanism to detect and rank 20 manufacturability problems in a design, and also to guide the correction process. In addition, such a framework should alter the existing design flow as little as possible to qualify for widespread adoption, which is one of the main reasons RET has become ubiquitous.

At present, there are groups who believe that it will be possible to improve 25 process corner modeling of devices by massive electrical characterizations, thus achieving a more robust design at logic synthesis. Although these methods have clear applications in interconnect delays and timing closure, they fail to provide information about forbidden topologies that cannot be characterized adequately due to their high sensitivity to process variations. By approaching DFM from the standpoint of pattern 30 robustness, and by making the layout less sensitive to process variations, these methods can be relevant when trying to explain the material aspects and electrical behavior of devices without having to explain pattern transfer effects that cannot be captured effectively in traditional electrical models. For this reason, such approaches are

considered complementary to this pattern transfer-centric proposal for DFM rather than competing.

The following sections evaluate the advantages and challenges for each of the leading prior art techniques being explored to improve pattern manufacturability.

- 5 Although many of these techniques are currently being evaluated for post-RET verification, in principle they could be used within a design environment to allow the designer to dictate the topology changes required to make the design more manufacturable.

### 1.2.1 CRITICAL AREA ANALYSIS

10 Critical area analysis has traditionally been the workhorse for yield prediction in the semiconductor industry. Such methods continue to be an open area of investigation. In 2004, Asami and co-authors presented a methodology on how critical area can be used successfully to predict yield loss for an 180 nm process under a wide variety of product conditions.

15 Critical area ( $A_c$ ) is a function defined for a particle defect size of equivalent radius ( $r$ ), as Equation 1 suggests:

$$F(R) = \sum_{layers=0}^R P_d(r) \cdot A_c(r) \quad (1)$$

20 Critical area along a defect density function typically defines a failure factor  $F(R)$ , which as expected depends on the equivalent radius of defect particle size. The continued success of critical area methods is based on the extension of the "particle" concept to formulate failure rates originated by random defects independent of their physical origin. These formulae are constantly being used to explain non-particle (as in "non-physical particle", such as dust) failure mechanisms (e.g., resist collapse, resist bridging or pinching and metal stress). The use of critical area formulae is possible when clear 25 failure mechanisms and their respective failure rates can be clearly characterized by continuous sampling during manufacturing.

30 However, critical area analysis has two main drawbacks. It is incapable of early yield assessment for new processes, and it lacks the mathematical machinery to incorporate more complex process effects. Although critical area can, on average, provide a good estimate of the expected yield of a product, the analysis can be performed

only after enough data has been gathered during manufacturing. Critical area alone cannot predict the yield of an IC product before going into a new process. Only by using massive amounts of historical information can this method predict expected yields.

The second limitation results from the use of empirical models, which depend on 5 short-range effects. For supra-wavelength processes, it is possible to use only space and width measurements to define critical area. As the resolution of the systems approaches the domain of deep sub-wavelength (below 1/2 wavelength), however, larger regions of layout context are needed to adequately capture high-sensitivity regions.

As does any technique, critical area analysis also has advantages. It is attractive 10 and is expected to remain so, since it depends on geometrical rules (which make it fast to calculate) and a large body of experimental information (which makes it an accurate predictor when enough data is available).

### 1.2.2 CONTRAST IMPROVEMENT

Because lithography is one of the most critical drivers for systematic yield loss 15 due to the sub-wavelength gap (FIGURE 2A), and image contrast has long been used as a criterion for image robustness it is not surprising that many DFM groups have tried to use contrast as a metric for evaluating the robustness of a given layout.

Among the advantages of improving image contrast is the control of line-end 20 roughness and traditional lithographic process windows (larger depth of focus and exposure latitude). However, because image contrast remains an optical quantity (albeit with known positive effects in resist- and mask-induced errors), it cannot be extended to incorporate other process effects such as etch, chemical metal polish or overlay. In addition, as FIGURE 7 suggests, it is not trivial to maximize image contrast for multiple layers concurrently. The authors of this figure restricted their analysis to the polysilicon 25 layer, and offered little explanation for the effect that such changes had on the manufacturability of other layers present in the design.

Another consideration is that an image contrast can capture only major 30 sensitivities in the design and does not directly translate into actual CD control because most chemically amplified resists perform in a non-linear fashion. Knowing the impact or variations in CD is one of the critical challenges that analog design faces and that cannot be reliably addressed with this method.

Based on this discussion, we can identify immediately the range of applications for these methods: primarily digital design and single-layer applications. This is one of

the fastest model-based methods, since might require single optical simulations to produce a good estimate of the image quality across process window conditions. This is a very desirable characteristic of any model-based DFM method, as will be highlighted later in this work.

5 1.2.3 MASK ERROR ENHANCEMENT FACTOR (MEEF) REDUCTION

One of the first metrics that relies on sensitivity of the layout is MEEF (Mask Error Enhancement Factor). MEEF is defined as the change in the width of a feature ( $CD_{wafer}$ ) with the change in the width of the feature in the mask ( $CD_{mask}$ ), divided by the image reduction factor (M), which typically is 4X. MEEF is expressed in Equation 2.

10

$$MEEF = \frac{\partial(CD_{wafer})}{\partial\left(\frac{CD_{mask}}{M}\right)} \quad (2)$$

While critical area and image contrast methods rely on a single-pass calculation, MEEF is a perturbation quantity. To be adequately calculated, the features on the mask need to be biased prior to measuring the induced CD on the wafer in order to make it possible to obtain the corresponding MEEF value. Even with this apparent limitation, 15 this metric is now proposed for use as a post-RET verification.

MEEF is well suited for post-RET verification because the RET objective is to bring all features as close as possible to the target layout. But there is an assumption that the mask can be perfectly manufactured. By using MEEF as an additional metric, it is possible to highlight locations in the mask that will be more susceptible to CD error 20 induced by imperfect masks.

Although this metric incorporates a relative measure of a process-induced CD variation (the process of making the mask), it also remains primarily optical in nature. In addition, MEEF remains a fairly one-dimensional metric because CD is not well defined in corners and in low-aspect-ratio features in general. Especially for sub-wavelength 25 features, in which high-frequency objects (such as corners or dense structures) are not well captured by the optical system and other pattern transfer effects start to become important, it is necessary to adopt a more general definition for CD variation and control. It is also interesting to note that, aside from critical area analysis, all the present proposals

for a pattern transfer DFM system have been developed by RET and lithography groups trying, in one way or another, to detect the locations most likely to fail in a layer.

#### 1.2.4 CRITICAL FAILURE OPTICAL RULE CHECK (CFORC)

A recent methodology to detect probable failure points in the layout also depends 5 on optical image quantities. This technique, called Critical Failure Optical Rule Check (CFORC) maps out the failure and non-failure regions across the process window. FIGURE 9 shows a process envelope (or boundary) separating process regions that will print reliably from those that will not.

This failure model is calibrated by empirical binary data in which a feature either 10 does or does not print. This is different from traditional process model calibrations, in which many CD values are captured for any given feature, and locations that cannot be measured reliably are removed during calibration.

This model relies on an empirical mapping between image parameters (such as minimum and maximum intensities and a two dimensional image parameter, shown as 15 **Factor** in FIGURE 9) and the printability or non-printability of the layout. Therefore, it offers the advantage that a single optical simulation is able to detect regions most likely to fail across process window conditions. However, the speed of the calculation is improved by trading a physical for an empirical model that lacks predictive power outside the domain used for calibration, making this method very sensitive to process space 20 sampling resulting from the test features included for calibration.

#### 1.2.5 RESTRICTIVE DESIGN RULES (RDR)

Although all the previous techniques can detect and highlight regions in the layout that will most likely create problems during manufacturing, they do not directly address 25 or forbid specific layout topologies. One approach widely supported by lithography groups is the use of restricted design rules (RDR). This approach is guided by the general principle that homogenous structures with well defined frequencies can be manufactured more easily than objects that are highly bi-dimensional.

Liebmann (2003) establishes the following principles for a more manufacturable layout: Limited number of narrow line widths....

- 30

- Single orientation of narrow features....

- Narrow features placed on uniform and coarse pitch....

- Uniform proximity environment for all critical gates....

- Limited number of pitches for critical gates.

Traditionally, designers do not receive such restrictive rules well because they appear to require much larger design areas. Since area, timing and power are the three main quantities for which designers are responsible, having restricted design rules affecting any of these three criteria results in an unwelcoming response. However, a 5 multitude of investigations suggests that the area penalty incurred by aggressive design rules is not as large as expected when the designer and the lithography groups work together toward a solution that includes pattern transfer manufacturability as a new target metric.

Unfortunately, the use of restrictive design rules has not been adopted widely 10 because there is no systematic method in which the layout can be analyzed and ranked according to manufacturability. All other design objectives have clear procedures and figures of merit: timing (maximum clock frequency, which defines the performance of the devices), power (wattage, which with mobile applications improves battery life) and area (square microns that translate into more product per wafer, thus reducing price). But 15 until now, there has been no metric that relates early enough in the process to product yield or reliability.

In addition, although most RDR guidelines are adequate in general, they still require the layout designer to have a good understanding of the process being used for manufacture, or at the very least a strong interaction between the layout designer and 20 RET experts who are able to determine what a "uniform proximity environment" really means.

As is apparent by now, different groups along the IC production chain use various 25 approaches for improving their methods to better and more economically produce aggressive designs. The objective of this framework is to build on the strengths and bypass the weaknesses inherent in all current pattern transfer DFM proposals. While many of the individual building blocks used in this proposal already exist, it is the integration of these tools into a formal and logical pattern transfer DFM framework that is lacking.

The following sections describe one embodiment of the present invention and test 30 the details of its implementation to achieve designs less sensitive to process variations. Although the primary objective of the present invention is the development of more robust layouts, the invention can also be used to evaluate the impact that more robust structures have on the electrical behavior of the devices.

## 2. AN IC-DFM FRAMEWORK

In one embodiment, the present invention is implemented as a software framework for the verification of IC layouts to insure that they are "LFD-Clean". This framework can be applied more generally to any layout verification method that considers 5 manufacturability criteria in the evaluation of the layout, and is not restricted to only manufacturability problems that occur during lithography.

This software framework comprises three components:

- Objects: Elements that capture design intent and process conditions.

- Operators: Operations that can be performed on the objects selecting or 10 extracting quantitative information.

- Guidelines: Recommendations for integrating the objects and operators consistently.

Each of these described in more detail below. As with any new technique, this DFM method is open to extensions and enhancements as more information about the 15 interactions between process and design are identified. To maintain its consistency and usefulness, however, only elements that fall into one of the three previously defined categories may be desirable.

The present invention operates on the assumption that fast manufacturing models are available. Although pattern transfer depends on the interaction of lithography, etch 20 and planarization, the invention uses compact lithography models to illustrate the proposed methodology. The reasoning is that fast process window lithography models have been previously calibrated and shown to reproduce lithography effects with an accuracy level comparable to that of experimental metrology.

Although only lithography effects are explored in the following pages, it will be 25 appreciated that as new process models are made available for other pattern transfer effects, such as CMP or metallization, they can be incorporated into the framework described herewith.. This can be achieved because the manufacturability object described in the following section is a variability response to a process variable. The nature of the process variation is relevant only with respect to the actual calculation of the 30 manufacturability object. The number and type of process variations affect the framework only by requiring additional computing time during the calculation of the manufacturability object. The analysis methods described by the framework remain constant and applicable.

## 2.1 MANUFACTURABILITY OBJECTS: LAYOUT AND PV-BANDS

Any DFM methodology will incorporate design and manufacturing components. In this case, the design object is the physical layout still residing within the design environment. This condition is desired for two reasons: the final layout is the only object 5 that has enough information about the intended topology, and any correction to the layout topology should be re-evaluated electrically. Otherwise, it might be possible to achieve a highly manufacturable grid structure with zero functional contribution.

For the manufacturing object, this work introduces the concept of process variability bands (PV-bands). A PV-band is defined as the physical representation of the 10 layout sensitivity to process variations. Regions within the PV-Bands will be positions where the final edge is likely to occur during manufacturing, while the regions outside the bands are positions where the edge is unlikely to occur. The typical representation for a PV-Band will be in the same medium as the representation of the layout itself: as one or more data layers in a layout encapsulation format such as GDS-II or OASIS<sup>TM</sup>. One way 15 to calculate a PV-band is to compute the pattern transfer image at multiple process conditions, and then perform a series of Boolean operations that extract the maximum and minimum edge displacement using certain probability criteria, as indicated in FIGURE 11.

It is clear that an intelligent sampling method of all possible process conditions 20 should be considered, as well as an adequate description of the processes under study (for example, the choice of RET in lithography, or the statistical variation in etch biases due to wafer processing).

As FIGURE 12 suggests, the PV-band is an uncertainty region between areas that will always print and areas that will never print, thus providing a mechanism to assess the 25 likelihood of a particular topology transfer. In other words, the smaller the PV-band, the higher the probability of correct pattern transfer. Although FIGURE 12 shows energy dose and image defocus (typical lithographic process control variables), any process variation can be incorporated because it will introduce its own printability signature as long as a well calibrated, physical model is available.

30 These simple objects have intrinsic properties that provide the basis of this framework. The PV-bands can be made small in one of the following ways: very good process control, a more advanced process or a more robust design. In addition, PV-bands can be calculated for any layer or process and, when combined, account for inter-layer

variations. For example, when the landing pad and contact variability bands overlap, the likelihood of an improper connection increases; when polysilicon and diffusion layer variability bands overlap, the likelihood of a short circuit increases. The ability to evaluate the interaction of PV-Bands for different layers and synthesize another PV-band 5 that incorporates information from this interaction represents an especially valuable embodiment of the invention.

Each effect can be weighed according to its importance. A variability that produces a short or bridge should account for a larger contribution than the same variability in another region that does not cause a fatal defect. And because these highly 10 process-sensitive regions are local in nature, they provide intra-die variation information.

Because process variability can be reduced over time, the same formulation can be used for processes under development (when the uncertainty is higher) and for mature processes (when the uncertainty is well controlled but not completely eliminated), thus providing a consistent evolution path. Although all these are qualitative benefits of using 15 a PV-band formulation, the framework also provides a mechanism for ranking designs and manufacture processes in a quantitative way.

For certain design checks it is also important to determine the total pattern transfer variation with respect to the drawn layout. As FIGURE 13 indicates the actual PV-band is solely defined by process variations. In contrast, an absolute PV-band should 20 completely enclose design layers by biasing the internal or external PV-band edges until they are coincident to the target layout.

The main application of an absolute PV-band is to measure the departure of the pattern transfer with respect to the intended layout. For the rest of the discussion PV-bands refer to actual PV-bands, unless otherwise noticed.

25 Another novelty of this approach is that sensitivities are calculated across multiple layers because the manufacturability of the design depends on the interaction of the PV-bands. A composite map can be created to account for all the manufacturability sensitivities and highlight regions that have worse or better pattern robustness for a certain process, as indicated in FIGURE 14. The information contained in the PV-bands 30 can be efficiently displayed and processed during design, thanks to advances in layout data representation/compression.

## 2.2 OPERATORS

Operators are software structures that act on the objects. Some of the more commonly used operators are widely used during layout creation (e.g., Boolean OR, AND and NOT) and may be common to other software products that operate on GDS-II or OASIS™ data, while others depend on the PV-band object itself (e.g., E2I, E2E and I2I). Table 1 lists and describes several representative operators.

TABLE 1. DESCRIPTION OF FRAMEWORK OPERATORS

| Operator                                                       | Description                                                                                                                                                                                                                                           |

|----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PVBAND( <i>Layer</i> )                                         | Calculates the process variability band of <i>Layer</i> and creates a <i>pvBand</i> object.                                                                                                                                                           |

| E2I( <i>pvBand<sub>i</sub></i> , <i>pvBand<sub>j</sub></i> )   | Measures the distance between the external <i>pvBand<sub>i</sub></i> edge and the internal <i>pvBand<sub>j</sub></i> edge and creates a marker layer that completely encloses the selected region.                                                    |

| E2E( <i>pvBand<sub>i</sub></i> , <i>pvBand<sub>j</sub></i> )   | Measures the distance between the external <i>pvBand<sub>i</sub></i> edge and the external <i>pvBand<sub>j</sub></i> edge and creates a marker layer that completely encloses the selected region.                                                    |

| I2I( <i>pvBand<sub>i</sub></i> , <i>pvBand<sub>j</sub></i> )   | Measures the distance between the internal <i>pvBand<sub>i</sub></i> edge and the internal <i>pvBand<sub>j</sub></i> edge and creates a marker layer that completely encloses the selected region.                                                    |

| OR( <i>Object<sub>i</sub></i> ... <i>Object<sub>j</sub></i> )  | Boolean operation that adds all the contents of <i>Object<sub>i</sub></i> through <i>Object<sub>j</sub></i> to create a derived layer. <i>Object</i> can be an original or derived <i>Layer</i> or <i>pvBand</i> .                                    |

| AND( <i>Object<sub>i</sub></i> ... <i>Object<sub>j</sub></i> ) | Boolean operation that adds the common contents of <i>Object<sub>i</sub></i> through <i>Object<sub>j</sub></i> to create a derived layer. <i>Object</i> can be an original or derived <i>Layer</i> or <i>pvBand</i> .                                 |

| NOT( <i>Object<sub>i</sub></i> , <i>Object<sub>j</sub></i> )   | Boolean operation that discounts the common contents of <i>Object<sub>i</sub></i> and <i>Object<sub>j</sub></i> from <i>Object<sub>i</sub></i> to create a derived layer. <i>Object</i> can be an original or derived <i>Layer</i> or <i>pvBand</i> . |

| AREA( <i>Object</i> )                                          | Calculates the area of the <i>Object</i> . <i>Object</i> can be an original or derived <i>Layer</i> or <i>pvBand</i> .                                                                                                                                |

As with any embodiment of logical interactions, a wide variety of programming languages can be used to create these Operators. They can be written within the structures of common DRC tools, in a language such as SVRF by Mentor Graphics; they can be written as scripts using a common scripting language such as Tcl/tk; they can be written 5 directly as coded instructions in a computer language to be compiled such as C, C++, or FORTRAN, or they can be created as dedicated microcode for hardware specifically designed for these layer specific operations. The only requirement is that these software structures be able to read the designated Objects and deliver a result that the user can interpret.

10

### 2.3 GUIDELINES

After manufacturability objects and operators are defined, the third component is 15 a series of Guidelines on integrating and using them effectively. These Guidelines may be as simple as a set of design rules, but can also be augmented to incorporate a number of manufacturability rules and behaviors in codified form. These Guidelines will generally be expressed as sets of inequalities relating various parameters of the layout and manufacturing process, and can be incorporated into any of the programming representations used for the Operators mentioned above.

FIGURE 15 shows (in gray) how the new design components can be incorporated 20 into a traditional design flow with minimal impact on existing design methodologies, thus defining the natural insertion points of this methodology within the existing IC design process. Because this method determines whether the layout is likely to fail, it should primarily be used prior to electrical simulations, as shown in FIGURE 15. Only after the layout can be reliably manufactured does it make sense to proceed with its electrical 25 analysis.

Each of the new or modified operations should comply with new requirements.

1. Layout: The layout should be large enough to address the areas of influence imposed by the process, since pattern transfer effects are highly dependent on the surrounding topology.

2. Process models: These models should reliably identify the maximum and minimum pattern responses within the process variations. In the absence of a single model that can explain all process variations, they should limit prediction to specific and well defined effects. In this way, a composite

PV-band can be used to identify regions that present maximum variability across many process effects and retain information on the largest contributor to the pattern variation.

3. Process-based design rules: These rules define the design violations and help to identify regions that are most sensitive. The results are used to flag regions of maximum variability and extract a quantitative metric to manufacturability.

5. PV-band calculation: This calculation uses the process models in conjunction with the process-based design rules.

10. Layout ranking: Before proceeding with electrical simulations, this layout-ranking metric serves as a design manufacturability target. Even when the process-based design rules do not return errors, it is possible to look at a continuous metric that provides additional opportunities for improvement.

15. Correction (inside the design environment): The correction resides in the design environment and requires a different interpretation of the results provided by the process-based design rules. While typical design-rule violations can be fixed by topological changes (e.g., compacting features) or morphological changes (e.g., clipping corners), these rules will generally require a topological change.

- 20.

### 2.3.1 MANUFACTURING RULE CHECKS

RDR makes a design more manufacturable by aggressively restricting the types of topologies allowed in a design but it relies heavily on past experience and on the assumption of the existence of a geometric representation of the restricted rule. One 25 possible way to enhance RDR is by using process-based design rules which are derived from the actual simulation of the layout.

This method derives process-based design rules from PV-bands rather than from nominal distortions and shape analysis. A pattern manufacturability rule is constructed by performing Boolean and spacing checks of the PV-bands. In this fashion, a typical set 30 of design rules can be translated into new design rules based on PV-bands.

FIGURE 16 shows a simple example of target geometry (left) and a schematic representation of the PV-bands (right) for three layers: poly, active and contact. For a perfectly modeled process, the rules can be as simple as identifying the respective PV-

band overlaps. However, a more general description specifies rule tolerances that serve as an additional safety margin or depend on electrical rules.

The rules depicted in FIGURE 16 can now be formally expressed as a collection of equations that use the previously defined operators and objects, and each of the 5 traditional pattern-related design rules can be tied to its original intention. Not all design rules are included in this formulation. For example, all the electrical design rules are not incorporated because they depend on the material aspects of manufacture.

$$aoc_{Violation} = OR \left( \begin{array}{l} AND((pvBand(contact), pvBand(active))), \\ E2I(pvBand(contact), pvBand(active)) \leq aoc_{min} \end{array} \right) \quad (3)$$

$$cw_{Violation} = OR \left( \begin{array}{l} AND(pvBand(contact)), \\ I2I(pvBand(contact)) \leq cw_{min} \end{array} \right) \quad (4)$$

10

$$gcs_{Violation} = OR \left( \begin{array}{l} AND((pvBand(poly), pvBand(contact))), \\ E2E(pvBand(poly), pvBand(contact)) \leq gcs_{min} \end{array} \right) \quad (5)$$

$$goa_{Violation} = OR \left( \begin{array}{l} AND((pvBand(poly), pvBand(contact)), endCap), \\ E2I(pvBand(active), pvBand(poly)) \leq goa_{min} \end{array} \right) \quad (6)$$

$$gw_{Violation} = OR \left( \begin{array}{l} AND(pvBand(poly)), \\ I2I(pvBand(poly)) \leq gw_{min} \end{array} \right) \quad (7)$$

$$pas_{Violation} = OR \left( \begin{array}{l} AND((pvBand(active), pvBand(poly))), \\ E2E(pvBand(active), pvBand(poly)) \leq pas_{min} \end{array} \right) \quad (8)$$

$$poc_{Violation} = OR \left( \begin{array}{l} AND((pvBand(contact), pvBand(poly))), \\ E2I(pvBand(contact), pvBand(poly)) \leq poc_{min} \end{array} \right) \quad (9)$$

### 2.3.1.1 CRITICAL AREA IDENTIFICATION: INTRA LAYER

The AND operator can be applied to single layers since each of the PV-bands are generated per edge. The AND operation can also serve as an explicit PV-band overlap detection. This simplifies the rule writing and avoids the unnecessary definition of 5 positive or negative distances. The second part of the equations relates to user-defined margins that are used to incorporate limitations of the process model, or electrically-justified design rules.

### 2.3.1.2 CRITICAL AREA IDENTIFICATION: INTER LAYER

By using the operators described in Table 1, it is possible to identify a particular 10 type of failure mechanism. This is the case of the *goa* design rule (Equation 6), in which an *endCap* failure is detected by the overlap of polysilicon (poly) and active PV-bands as depicted in FIGURE 18.

The support region includes the drawn line-end, plus the area defined by the 15 boundaries of the external edges of the polysilicon PV-band. While support regions are useful in single layer, they are more important for most inter layer design rules.

One of the advantages of using models to detect critical regions is highlighted 20 with the following example. When line-ends fail (FIGURE 18A) due to PV-band overlap, a typical correction extends the line-end (FIGURE 18B). But as FIGURE 19 suggests, there might be other configurations in which a line-end extension is not required 25 (FIGURE 19A), and forcing such extension can result into another type of violation such as a polysilicon bridge (FIGURE 19B).

### 2.3.2 SYSTEM RANKING: MANUFACTURABILITY INDICES

Although manufacturing checks are useful for highlighting regions prone to failure in the layout, thus far there is no mechanism to assess the viability of the layout 25 from the manufacturing point of view.

Introducing manufacturability indices, by defining a process variability index and a design variability index, solves the problem that results when two layouts with clean design rules return different pattern manufacturability behavior.

The process variability index (PVI) is related to the average difficulty of image 30 transfer for a given design. The design variability index (DVI) is related to the number of locations in a layout that are sensitive to a given process. These can also be referred to as the process manufacturability index (PMI) and the design manufacturability index (DMI).

By definition, PVI is a global metric and does not provide specific information about the failure locations in the design. However, this apparent shortcoming makes it ideal for qualifying the process capabilities or the global behavior of a complete layer. In its simplest form, the PVI can be expressed as follows:

$$5 \quad PVI = \sum_{layer} \frac{AREA(pvBand(layer))}{AREA(layer)} + \sum_{layer_i, layer_j} \frac{AREA(AND(pvBand(layer_i), pvBand(layer_j)))}{AREA(AND(layer_i, layer_j))} \quad (10)$$

In addition, we can define DVI that primarily serve to highlight the regions most likely to fail in the design. The desirable number in this case is zero.

$$DVI = \sum \frac{AREA(DesignRule\ Violations)}{AREA(SupportLayer)} \quad (11)$$

In Equation 11, design rule violations result from the manufacturing checks, and 10 the support layer is used to normalize the errors with respect to the area of interest.

The design rule violation concept can be enhanced by including only defects that occur in non-redundant regions of the design. For the present discussion, however, the formulation is limited to non-redundant logic.

Immediately we can identify four conditions:

15

Regime I. Desirable: The process is stable and the design is manufacturable  $PVI \rightarrow 0$  Regime III. Process limited: The process is unstable but the design is manufacturable  $PVI \gg 0$

$$DVI = 0 \quad DVI = 0$$

Regime II. Design limited: The process is stable and the design is not manufacturable Regime IV. Undesirable: The process is unstable and the design is not manufacturable

$$PVI \rightarrow 0 \quad PVI \gg 0$$

$$DVI > 0 \quad DVI > 0$$

DVI can have a value of zero because it depends on user-definable tolerances and it is in a discontinuous function. However, PVI is a continuous function that has a fundamental limit ( $PVI_{min}$ ). Therefore, a more realistic definition of the manufacturability regimes is as follows:

20

|                                                                                                                                   |                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| Regime I. Desirable: The process is stable and the design is manufacturable<br>$PVI \rightarrow PVI_{min}$<br>$DVI = 0$           | Regime III. Process limited: The process is unstable but the design is manufacturable<br>$PVI \gg PVI_{min}$<br>$DVI = 0$ |

| Regime II. Design limited: The process is stable and the design is not manufacturable<br>$PVI \rightarrow PVI_{min}$<br>$DVI > 0$ | Regime IV. Undesirable: The process is unstable and the design is not manufacturable<br>$PVI \gg PVI_{min}$<br>$DVI > 0$  |

Both indices are process specific; they depend on the number of design rules used as well as the existing process margins. However, after the definition of the indices and their arguments is fixed, the indices have the potential to permit a quantitative comparison between evolving processes and design styles.

### 5 2.3.3 AREAS OF INFLUENCE: NECESSARY DESIGN DOMAIN