(19)日本国特許庁(JP)

## (12)特許公報(B2)

(11)特許番号

特許第7647472号

(P7647472)

(45)発行日 令和7年3月18日(2025.3.18)

(24)登録日 令和7年3月10日(2025.3.10)

(51)国際特許分類

|         |                 |     |         |       |         |

|---------|-----------------|-----|---------|-------|---------|

| G 0 6 F | 12/00 (2006.01) | F I | G 0 6 F | 12/00 | 5 6 0 B |

| G 0 6 F | 12/06 (2006.01) |     | G 0 6 F | 12/00 | 5 6 4 A |

|         |                 |     | G 0 6 F | 12/06 | 5 2 1 G |

|         |                 |     | G 0 6 F | 12/06 | 5 2 5 A |

請求項の数 8 (全35頁)

(21)出願番号 特願2021-153722(P2021-153722)

(22)出願日 令和3年9月22日(2021.9.22)

(65)公開番号 特開2023-45362(P2023-45362A)

(43)公開日 令和5年4月3日(2023.4.3)

審査請求日 令和6年6月11日(2024.6.11)

(73)特許権者 000005223

富士通株式会社

神奈川県川崎市中原区上小田中4丁目1

番1号

(74)代理人 100107766

弁理士 伊東 忠重

(74)代理人 100070150

弁理士 伊東 忠彦

(72)発明者 吉本 和矢

神奈川県川崎市中原区上小田中4丁目1

番1号 富士通株式会社内

(72)発明者 近藤 祐史

神奈川県川崎市中原区上小田中4丁目1

番1号 富士通株式会社内

審査官 後藤 彰

最終頁に続く

(54)【発明の名称】 演算処理装置およびメモリアクセス方法

## (57)【特許請求の範囲】

## 【請求項1】

データの読み出しサイズが異なる複数のメモリアクセス要求に基づいてメモリのアクセスを制御可能なメモリアクセスコントローラを有する演算処理装置であって、

前記メモリアクセスコントローラは、

複数のメモリアクセス要求を受けた場合、前記メモリから出力される読み出しデータの競合を避けるタイミングで前記複数のメモリアクセス要求に対応するリードコマンドを前記メモリにそれぞれ出力し、前記メモリから読み出されるデータの外部への出力開始タイミングを生成するアクセス制御部と、

前記リードコマンドにそれぞれ対応して前記メモリから読み出されるデータをそれぞれ保持する複数のバッファと、

前記複数のバッファの動作を制御し、前記出力開始タイミングに基づいて前記複数のバッファのいずれかからデータを出力させるバッファ制御部と、を有し、

前記アクセス制御部は、先行のメモリアクセス要求に対応するメモリアクセスの実行中以後続のメモリアクセス要求を受けた場合、前記後続のメモリアクセス要求に対応する前記バッファからのデータの出力開始タイミングを、前記先行のメモリアクセス要求に対応する前記バッファからのデータの出力開始タイミングより遅らせる

演算処理装置。

## 【請求項2】

前記アクセス制御部は、

先行のメモリアクセス要求に対応するメモリアクセスの実行中に後続のメモリアクセス要求を受けた場合、前記後続のメモリアクセス要求に対応する前記出力開始タイミングを、受付可能なメモリアクセス要求のうち、データの読み出しサイズが最大のメモリアクセス要求を受けたときの前記出力開始タイミングに設定する

請求項 1 に記載の演算処理装置。

【請求項 3】

前記バッファ制御部は、前記後続のメモリアクセス要求に対応する前記出力開始タイミングが、前記先行のメモリアクセス要求に対応する前記バッファからの最終データの出力タイミングより早い場合、前記後続のメモリアクセス要求に対応する前記出力開始タイミングを前記最終データの出力タイミングより後に設定する

請求項 1 または請求項 2 に記載の演算処理装置。

【請求項 4】

前記アクセス制御部は、メモリアクセス要求を受けたとき、先行のメモリアクセス要求に対応するメモリアクセスが実行されていない場合、受けたメモリアクセス要求のアクセス仕様に応じた出力開始タイミングを設定する

請求項 1 ないし請求項 3 のいずれか 1 項に記載の演算処理装置。

【請求項 5】

前記複数のバッファの各々は、データの出力時にシフト動作するシフトレジスタの構造を有し、

前記バッファ制御部は、前記複数のバッファの各々のデータの格納先を示すライトポインタ値を生成する複数のカウンタと、前記複数のカウンタの各々をカウントアップまたはカウントダウンするカウンタ制御部と、を有し、

前記カウンタ制御部は、前記バッファからデータを出力することなく前記バッファにデータの格納するときに前記カウンタをカウントアップし、前記バッファにデータの格納することなく前記バッファからデータを出力するときに前記カウンタをカウントダウンし、前記バッファからデータを出力するとともに前記バッファにデータを格納するときに前記カウンタのカウントアップおよびカウントダウンを停止する

請求項 1 ないし請求項 4 のいずれか 1 項に記載の演算処理装置。

【請求項 6】

前記カウンタが生成するライトポインタ値を前記バッファのいずれかに供給するセレクタを有し、

前記カウンタの数は、前記バッファの数より少ない

請求項 5 に記載の演算処理装置。

【請求項 7】

演算を実行する演算実行部と、

外部デバイスに接続されるインターフェース部と、

前記演算実行部が出力する前記メモリアクセス要求および前記インターフェース部を介して外部デバイスが出力する前記メモリアクセス要求を受信し、受信したメモリアクセス要求を前記メモリアクセスコントローラに出力するネットワーク制御部と、を有する

請求項 1 ないし請求項 6 のいずれか 1 項に記載の演算処理装置。

【請求項 8】

データの読み出しサイズが異なる複数のメモリアクセス要求に基づいてメモリのアクセスを制御可能なメモリアクセスコントローラによるメモリアクセス方法であって、

複数のメモリアクセス要求を受けた場合、前記メモリから出力される読み出しデータの競合を避けるタイミングで前記複数のメモリアクセス要求に対応するリードコマンドを前記メモリにそれぞれ出力し、

前記メモリから読み出されるデータの外部への出力開始タイミングを生成し、

前記リードコマンドにそれぞれ対応して前記メモリから読み出されるデータをそれぞれ保持する複数のバッファの動作を制御し、前記出力開始タイミングに基づいて前記複数のバッファのいずれかからデータを出力させ、

10

20

30

40

50

先行のメモリアクセス要求に対応するメモリアクセスの実行中に後続のメモリアクセス要求を受けた場合、前記後続のメモリアクセス要求に対応する前記バッファからのデータの出力開始タイミングを、前記先行のメモリアクセス要求に対応する前記バッファからのデータの出力開始タイミングより遅らせる

メモリアクセス方法。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、演算処理装置およびメモリアクセス方法に関する。

【背景技術】

【0002】

主記憶装置のアクセス単位である単位データ長より大きい単位のアクセス要求を、単位データ長に相当するアクセス要求に分割し、主記憶装置から出力される単位データの順序を揃えてバッファに保持し、応答する手法が知られている（例えば、特許文献1参照）。

【0003】

複数のリクエスタからの可変長のリクエストの記憶装置への送出回数と記憶装置からのリプライデータの回数とを計数することで、リプライバッファのオーバーフローを抑止する手法が知られている（例えば、特許文献2参照）。

【先行技術文献】

【特許文献】

【0004】

【文献】特開平1-180663号公報

【文献】特開平10-307747号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

複数種のデバイスによりメモリをアクセスする場合、1回のメモリアクセス要求によりメモリから読み出すデータの読み出しサイズは、デバイスに応じて異なる場合がある。例えば、メモリのアクセスを制御するメモリアクセスコントローラが、データの読み出しサイズの大きいメモリアクセス要求の後にデータの読み出しサイズの小さいメモリアクセス要求を受けるとする。この場合、メモリアクセス要求の発行順と、メモリアクセス要求に対応してメモリから読み出される応答データのデバイスへの出力順とが入れ替わるおそれがある。この場合、先行のメモリアクセス要求に対応する読み出しデータの発行元への応答が遅れるため、先行のメモリアクセス要求を発行するデバイスの処理性能が低下するおそれがある。

【0006】

1つの側面では、本発明は、データの読み出しサイズが異なる複数のメモリアクセス要求を受ける場合にも、メモリから読み出されるデータをアクセス要求の発行順にしたがって発行元に出力することを目的とする。

【課題を解決するための手段】

【0007】

一つの観点によれば、演算処理装置は、データの読み出しサイズが異なる複数のメモリアクセス要求に基づいてメモリのアクセスを制御可能なメモリアクセスコントローラを有する演算処理装置であって、前記メモリアクセスコントローラは、複数のメモリアクセス要求を受けた場合、前記メモリから出力される読み出しデータの競合を避けるタイミングで前記複数のメモリアクセス要求に対応するリードコマンドを前記メモリにそれぞれ出力し、前記メモリから読み出されるデータの外部への出力開始タイミングを生成するアクセス制御部と、前記リードコマンドにそれぞれ対応して前記メモリから読み出されるデータをそれぞれ保持する複数のバッファと、前記複数のバッファの動作を制御し、前記出力開始タイミングに基づいて前記複数のバッファのいずれかからデータを出力させるバッファ

10

20

30

40

50

制御部と、を有し、前記アクセス制御部は、先行のメモリアクセス要求に対応するメモリアクセスの実行中に後続のメモリアクセス要求を受けた場合、前記後続のメモリアクセス要求に対応する前記バッファからのデータの出力開始タイミングを、前記先行のメモリアクセス要求に対応する前記バッファからのデータの出力開始タイミングより遅らせる。

【発明の効果】

【0008】

1つの側面では、本発明は、データの読み出しサイズが異なる複数のメモリアクセス要求を受ける場合にも、メモリから読み出されるデータをアクセス要求の発行順にしたがって発行元に出力することができる。

【図面の簡単な説明】

【0009】

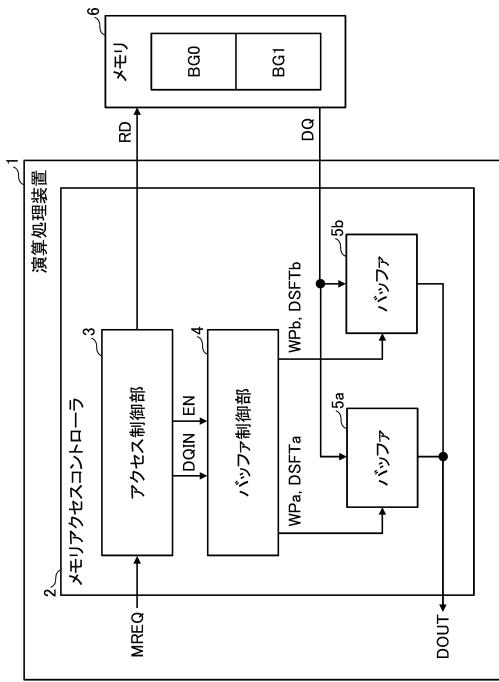

【図1】一実施形態におけるメモリアクセスコントローラを含む演算処理装置の一例を示すブロック図である。

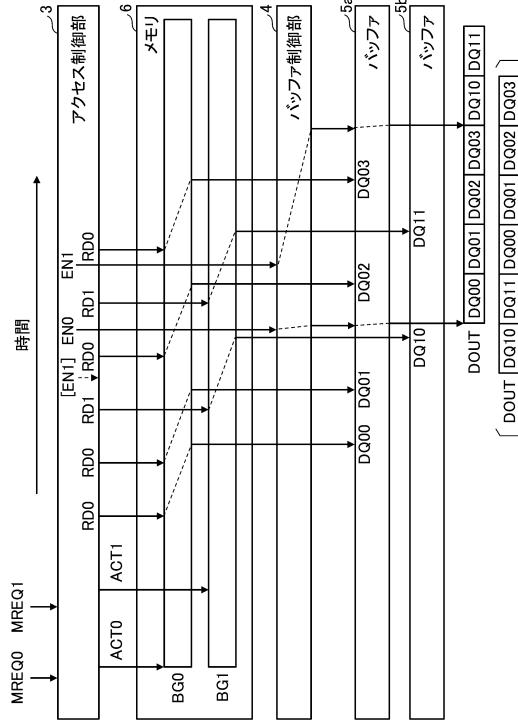

【図2】図1のメモリアクセスコントローラの動作の一例を示すタイミング図である。

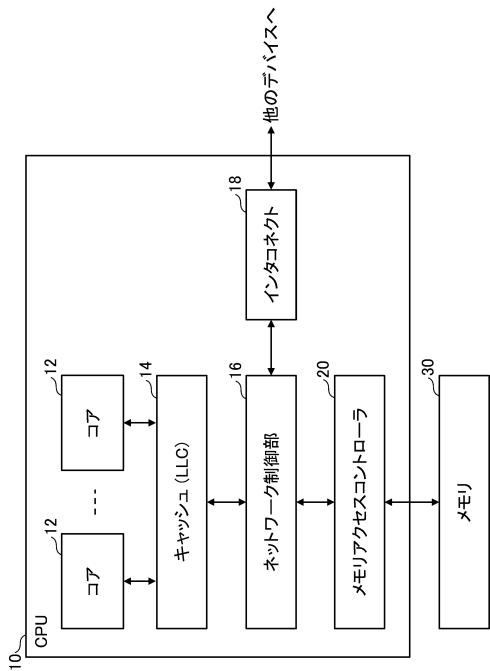

【図3】別の実施形態におけるメモリアクセスコントローラを含む演算処理装置の一例を示すブロック図である。

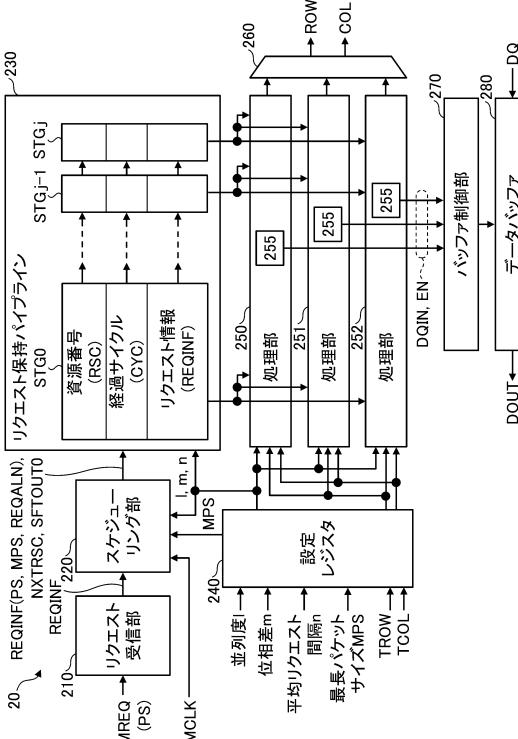

【図4】図3のメモリアクセスコントローラの一例を示すブロック図である。

【図5】図4のスケジューリング部の一例を示すブロック図である。

【図6】図5のスケジューリング部の動作の一例を示すタイミング図である。

【図7】図4のリクエスト保持パイプラインのステージの一例を示すブロック図である。

【図8】図4の処理部の一例を示すブロック図である。

【図9】図4のバッファ制御部およびデータバッファの一例を示すブロック図である。

【図10】図4のメモリアクセスコントローラによりメモリにリードアクセスする一例を示すタイミング図である。

【図11】メモリのリードアクセス時のバッファ制御部およびデータバッファの動作の一例を示すタイミング図である。

【図12】図11と同じ期間でのメモリアクセスコントローラの動作の一例を示すタイミング図である。

【図13】図11の続きを示すタイミング図である。

【図14】図12の続きを示すタイミング図である。

【図15】図13の続きを示すタイミング図である。

【図16】図14の続きを示すタイミング図である。

【図17】図15の続きを示すタイミング図である。

【図18】図16の続きを示すタイミング図である。

【図19】他のメモリアクセスコントローラの動作の一例を示すタイミング図である。

【図20】別の実施形態におけるメモリアクセスコントローラの例を示すブロック図である。

【発明を実施するための形態】

【0010】

以下、図面を用いて実施形態が説明される。以下では、信号等の情報が伝達される信号線には、信号名と同じ符号を使用する。また、図中に単線で示す信号線が、複数ビットの場合もある。

【0011】

図1は、一実施形態におけるメモリアクセスコントローラを含む演算処理装置の一例を示す。図1に示す演算処理装置1は、メモリアクセスコントローラ2を有する。メモリアクセスコントローラ2は、データの読み出しサイズが異なる複数のメモリアクセス要求MR EQに基づいてメモリ6のアクセスを制御可能である。例えば、データの読み出しサイズは、1回のメモリアクセス要求MR EQに応じてメモリ6から読み出されるデータDQのサイズまたはデータDQの出力回数である。

【0012】

10

20

30

40

50

メモリアクセスコントローラ 2 は、アクセス制御部 3、バッファ制御部 4 および複数のバッファ 5 ( 5 a、5 b ) を有する。アクセス制御部 3 は、複数のメモリアクセス要求 MREQ を受けた場合、メモリ 6 にアクセスコマンドを出力する。例えば、メモリ 6 は、データを保持する複数のバンクグループ BG ( BG 0、BG 1 ) を有してもよい。

#### 【 0 0 1 3 】

以下では、メモリアクセス要求 MREQ が読み出しアクセス要求であり、アクセス制御部 3 がメモリ 6 にリードコマンド RD を出力する例が説明される。なお、メモリ 6 が DRAM ( Dynamic Random Access Memory ) の場合、アクセス制御部 3 は、リードコマンド RD を出力する前にアクティブコマンド ACT を出力してもよい。

#### 【 0 0 1 4 】

アクセス制御部 3 は、複数もメモリアクセス要求 MREQ に対応してメモリ 30 から出力されるデータ DQ ( 読み出しデータ ) の競合を避けるタイミングで、複数のメモリアクセス要求 MREQ に対応するリードコマンド RD をメモリ 30 にそれぞれ出力する。アクセス制御部 3 は、リードコマンド RD に応答してメモリ 6 からデータ DQ が outputされるタイミングに合わせてデータ入力タイミング信号 DQIN をバッファ制御部 4 に出力する。

#### 【 0 0 1 5 】

バッファ制御部 4 は、データ入力タイミング信号 DQIN に基づいてバッファ 5 a、5 b のいずれかにライトポインタ値 WP ( WP a、WP b ) を出力する。ライトポインタ値 WP は、メモリ 6 から読み出されるデータ DQ を格納するバッファ 5 の格納位置を示す。そして、バッファ 5 a、5 b には、リードコマンド RD にそれぞれ対応してメモリ 6 から読み出されるデータ DQ が、メモリアクセス要求 MREQ 毎に格納される。例えば、各バッファ 5 は、保持したデータ DQ の出力時にシフト動作するシフトレジスタの構造 ( すなわち、FIFO ( First-In First-Out ) の構造 ) を有する。

#### 【 0 0 1 6 】

アクセス制御部 3 は、所定量のデータ DQ がバッファ 5 に格納されたタイミングで、バッファ 5 に保持されたデータ DQ の外部への出力開始タイミングを示すイネーブル信号 EN を、バッファ 5 每にバッファ制御部 4 に出力する。バッファ制御部 4 は、イネーブル信号 EN に基づいて、対応するバッファ 5 にデータシフト信号 DSFT ( DSFT a、DSFT b ) を出力する。例えば、データシフト信号 DSFT は、パルス信号であり、バッファ 5 から出力するデータ DQ の数のパルスを含む。バッファ 5 は、データシフト信号 DSFT に応じて、保持しているデータ DQ を出力データ DOUT として順次出力する。

#### 【 0 0 1 7 】

ここで、アクセス制御部 3 が、先行のメモリアクセス要求 MREQ に対応するメモリアクセスの実行中に後続のメモリアクセス要求 MREQ を受けとる。この場合、アクセス制御部 3 は、後続のメモリアクセス要求 MREQ に対応するイネーブル信号 EN を、先行のメモリアクセス要求 MREQ に対応するイネーブル信号 EN の後に出力する。すなわち、アクセス制御部 3 は、後続のメモリアクセス要求 MREQ に対応するバッファ 5 からの出力データ DOUT の出力開始タイミングを、先行のメモリアクセス要求 MREQ に対応するバッファ 5 からの出力データ DOUT の出力開始タイミングより遅らせる。

#### 【 0 0 1 8 】

図 2 は、図 1 のメモリアクセスコントローラ 2 の動作の一例を示す。すなわち、図 2 は、メモリアクセスコントローラ 2 によるメモリアクセス方法の一例を示す。図 2 では、メモリアクセスコントローラ 2 は、バンクグループ BG 0 に対するメモリアクセス要求 MREQ0 と、バンクグループ BG 1 に対するメモリアクセス要求 MREQ1 とを順次受け。メモリアクセスコントローラ 2 は、メモリアクセス要求 MREQ0 に対応するアクティブコマンド ACT0 をメモリ 6 に出力した後、メモリアクセス要求 MREQ1 に対応するアクティブコマンド ACT1 をメモリ 6 に出力する。

#### 【 0 0 1 9 】

次に、メモリアクセスコントローラ 2 は、メモリアクセス要求 MREQ0 に対応する複数のリードコマンド RD0 と、メモリアクセス要求 MREQ1 に対応する複数のリードコ

10

20

30

40

50

マンド R D 1 とをメモリ 6 に出力する。例えば、メモリアクセス要求 M R E Q 0 のデータの読み出しサイズに対応するデータの出力回数は "1 6" であり、メモリアクセス要求 M R E Q 1 のデータの読み出しサイズに対応するデータの出力回数は "8" である。また、1 回のリードコマンド R D で 4 個のデータ D Q がメモリ 6 から出力される。このため、メモリアクセスコントローラ 2 は、メモリアクセス要求 M R E Q 0 に対応してリードコマンド R D 0 を 4 回出力し (バースト長 = "4") 、メモリアクセス要求 M R E Q 1 に対応してリードコマンド R D 1 を 2 回出力する。

#### 【 0 0 2 0 】

リードコマンド R D 0 に応答してメモリ 6 から読み出されるデータ D Q 0 ( D Q 0 0 、 D Q 0 1 、 D Q 0 2 、 D Q 0 3 ) は、バッファ 5 a に順次格納される。リードコマンド R D 1 に応答してメモリ 6 から読み出されるデータ D Q 1 ( D Q 1 0 、 D Q 1 1 ) は、バッファ 5 b に順次格納される。なお、各データ D Q 0 0 、 D Q 0 1 、 D Q 0 2 、 D Q 0 3 、 D Q 1 0 、 D Q 1 1 は、4 個のデータ D Q を含む。

10

#### 【 0 0 2 1 】

アクセス制御部 3 は、所定量のデータ D Q 0 がバッファ 5 a に格納されたタイミングで、イネーブル信号 E N 0 をバッファ制御部 4 に出力する。また、アクセス制御部 3 は、イネーブル信号 E N 0 の出力後、所定量のデータ D Q 1 がバッファ 5 b に格納されたタイミングで、イネーブル信号 E N 1 をバッファ制御部 4 に出力する。

#### 【 0 0 2 2 】

バッファ制御部 4 は、イネーブル信号 E N 0 に基づいてバッファ 5 a を制御し、バッファ 5 a に保持されたデータを D Q 0 0 、 D Q 0 1 、 D Q 0 2 、 D Q 0 3 を出力データ D O U T として順次出力させる。バッファ制御部 4 は、イネーブル信号 E N 1 を受信したとき、バッファ 5 a からデータ D Q 0 1 が出力中であるため、バッファ 5 b からのデータ D Q 1 0 の出力制御を保留する。

20

#### 【 0 0 2 3 】

そして、バッファ制御部 4 は、バッファ 5 a からのデータ D Q 0 3 の出力完了タイミングに合わせてバッファ 5 b を制御し、バッファ 5 b に保持されたデータを D Q 1 0 、 D Q 1 1 を出力データ D O U T として順次出力させる。すなわち、アクセス制御部 3 は、後続のメモリアクセス要求 M R E Q に対応するバッファ 5 からの出力データ D O U T の出力開始タイミングを、先行のメモリアクセス要求 M R E Q に対応するバッファ 5 からの出力データ D O U T の出力開始タイミングより遅らせる。これにより、メモリアクセスコントローラ 2 は、様々なデータの読み出しサイズのメモリアクセス要求 M R E Q に応じてメモリ 3 0 からデータ D Q を読み出す場合にも、メモリアクセス要求 M R E Q の受付順にしたがってデータ D Q を出力できる。

30

#### 【 0 0 2 4 】

なお、かぎ括弧で示したイネーブル信号 E N 1 は、先行のメモリアクセス要求 M R E Q 0 の有無にかかわりなく、最初のリードコマンド R D 1 から所定の期間後に output するタイミングの例を示す。すなわち、かぎ括弧で示したイネーブル信号 E N 1 は、メモリアクセスコントローラ 2 が、先行のメモリアクセス要求 M R E Q 0 の有無に応じてイネーブル信号 E N 1 の出力タイミングを遅らせる機能を持たない場合の例を示す。

40

#### 【 0 0 2 5 】

この場合、かぎ括弧で示すように、メモリアクセス要求 M R E Q 1 に対応するデータ D Q 1 が、メモリアクセス要求 M R E Q 0 に対応するデータ D Q 0 より先に出力される。すなわち、メモリアクセス要求 M R E Q の受付順と逆の順序でデータ D Q 1 、 D Q 0 が順次出力されてしまう。

#### 【 0 0 2 6 】

以上、この実施形態では、メモリアクセスコントローラ 2 は、データ D Q の読み出しサイズが異なる複数のメモリアクセス要求 M R E Q に応じてメモリ 6 から出力されるデータ D Q をアクセス要求 M R E Q の発行順にしたがって発行元のデバイスに出力できる。これにより、例えば、読み出しサイズの小さいメモリアクセス要求 M R E Q 1 の前に発行され

50

た読み出しサイズの大きいメモリアクセス要求 M R E Q 0 に対応する読み出しデータのデバイスへの応答の遅れを抑制することができる。この結果、メモリアクセス要求 M R E Q の発行元のデバイスの処理性能が、他のメモリアクセス要求 M R E Q のデータの読み出しサイズにより低下することを抑制することができる。

#### 【 0 0 2 7 】

バッファ制御部 4 は、後続のメモリアクセス要求 M R E Q 1 に対応するデータ D Q の出力が、先行のメモリアクセス要求 M R E Q 0 に対応するデータ D Q の出力と重複する場合、イネーブル信号 E N 1 の受信に基づくデータ D Q 1 の出力の開始を遅らせる。これにより、2つのバッファ 5 a、5 b からのデータ D Q 0、D Q 1 の衝突を抑止することができる。この結果、誤ったデータ D Q ( D O U T ) がメモリアクセスコントローラ 2 から出力されることを抑止することができる。

#### 【 0 0 2 8 】

図 3 は、別の実施形態におけるメモリアクセスコントローラを含む演算処理装置の一例を示す。図 3 に示す演算処理装置 1 0 は、例えば、C P U ( Central Processing Unit ) である。以下では、演算処理装置 1 0 を C P U 1 0 とも称する。

#### 【 0 0 2 9 】

C P U 1 0 は、複数のコア 1 2、キャッシュ 1 4、ネットワーク制御部 1 6、インタコネクト 1 8 およびメモリアクセスコントローラ 2 0 を有する。各コア 1 2 は、キャッシュ 1 4 に格納された命令を実行し、キャッシュ 1 4 に格納されたデータの演算を実行する。各コア 1 2 は、演算実行部の一例である。

#### 【 0 0 3 0 】

例えば、キャッシュ 1 4 は、L L C ( Last Level Cache ) であり、複数のコア 1 2 に共通に接続される。キャッシュ 1 4 は、メインメモリ等のメモリ 3 0 に記憶されたデータおよび命令の一部および他のデバイスに接続されるメモリに記憶されたデータおよび命令の一部を記憶可能である。特に限定されないが、メモリ 3 0 は、D D R ( Double Data Rate ) 4 - S D R A M である。

#### 【 0 0 3 1 】

ネットワーク制御部 1 6 は、キャッシュ 1 4、インタコネクト 1 8 およびメモリアクセスコントローラ 2 0 を相互に接続する。インタコネクト 1 8 は、他のデバイス等に接続され、他のデバイスとの間で通信を実行する。ここで、他のデバイスは、C P U 1 0 に接続される外部デバイスである。他のデバイスは、C P U 1 0 とともに情報処理装置(システム)に搭載される他のC P U 1 0 でもよく、C P U 1 0 とともに情報処理装置に搭載されるD M A C ( Direct Memory Access Controller ) でもよい。インタコネクト 1 8 は、外部デバイスに接続されるインターフェース部の一例である。

#### 【 0 0 3 2 】

メモリアクセスコントローラ 2 0 は、メモリ 3 0 に接続され、メモリ 3 0 のアクセスを制御する。例えば、メモリアクセスコントローラ 2 0 は、コア 1 2 またはインタコネクト 1 8 を介して C P U 1 0 の外部から発行されるメモリアクセス要求(図 4 の M R E Q )に基づいてメモリ 3 0 のアクセスを制御する。

#### 【 0 0 3 3 】

メモリアクセスコントローラ 2 0 が C P U 1 0 の内部および外部からメモリアクセス要求 M R E Q を受ける場合、データの読み出しサイズ(後述するパケットサイズ P S )が様々になる場合がある。後述するように、メモリアクセスコントローラ 2 0 は、データの読み出しサイズが互いに異なる複数のメモリアクセス要求 M R E Q に応じて、メモリ 3 0 からデータを読み出し、読みだしたデータをデータバッファ 2 8 0 ( 図 4 ) に保持できる。そして、メモリアクセスコントローラ 2 0 は、データバッファ 2 8 0 に保持したデータを、メモリアクセス要求 M R E Q の受付順に出力できる。

#### 【 0 0 3 4 】

例えば、メモリアクセス要求がリードアクセス要求の場合、メモリアクセスコントローラ 2 0 は、リードアクセス要求に基づいて、メモリ 3 0 にリードアクセスし、メモリ 3 0

10

20

30

40

50

に記憶されたデータをリードする。また、メモリアクセス要求がライトアクセス要求の場合、メモリアクセスコントローラ 20 は、ライトアクセス要求に基づいて、メモリ 30 にライトアクセスし、メモリ 30 にデータをライトする。

#### 【 0 0 3 5 】

例えば、メモリアクセスコントローラ 20 は、1 つのメモリアクセス要求に応じて、メモリアクセス要求に含まれる読み出しサイズのデータをメモリ 30 から読み出す。データの読み出しサイズは、CPU 10 と DMA C 等の他のデバイスとで相違されてもよく、CPU 10 のグループ毎に相違されてもよい。

#### 【 0 0 3 6 】

なお、CPU 10 に搭載されるコア 12 の数は、1 つでもよい。また、CPU 10 は、キャッシュ 14 およびネットワーク制御部 16 を持たなくてもよい。その場合、各コア 12 がメモリアクセスコントローラ 20 に接続される。

10

#### 【 0 0 3 7 】

図 4 は、図 3 のメモリアクセスコントローラ 20 の一例を示す。メモリアクセスコントローラ 20 は、リクエスト受信部 210、スケジューリング部 220、リクエスト保持パイプライン 230、設定レジスタ 240、複数の処理部 25 (250, 251, 252) およびセレクタ 260 を有する。また、メモリアクセスコントローラ 20 は、バッファ制御部 270 およびデータバッファ 280 を有する。スケジューリング部 220、リクエスト保持パイプライン 230 および複数の処理部 25 は、アクセス制御部の一例である。

#### 【 0 0 3 8 】

リクエスト受信部 210 は、ネットワーク制御部 16 (図 3) から受けるメモリアクセス要求 MREQ に含まれるリクエスト情報 REQINF をスケジューリング部 220 に出力する。例えば、リクエスト情報 REQINF は、動作種別 (ライトまたはリード)、バンクアドレス、ロウアドレス、カラムアドレス、バリッドフラグおよびパケットサイズ PS 等を含む。リクエスト受信部 210 は、有効レベルのバリッドフラグを含むメモリアクセス要求 MREQ を受け付け、無効レベルのバリッドフラグを含むメモリアクセス要求 MREQ を受け付けない。

20

#### 【 0 0 3 9 】

スケジューリング部 220 は、メモリ 30 に供給するクロックであるメモリクロック MCLK に同期して動作する。なお、メモリクロック MCLK は、スケジューリング部 220 だけでなく、メモリアクセスコントローラ 20 内のクロック同期回路に供給される。スケジューリング部 220 は、設定レジスタ 240 に設定された並列度 1 (エル)、位相差 m および平均リクエスト間隔 n に基づいて、資源番号 NXTRS およびシフト信号 SHIFTOUT 0 をリクエスト情報 REQINF とともにリクエスト保持パイプライン 230 に出力する。

30

#### 【 0 0 4 0 】

また、スケジューリング部 220 は、設定レジスタ 240 に設定された最長パケットサイズ MPS をリクエスト情報 REQINF に含めてリクエスト保持パイプライン 230 に出力する。例えば、リクエスト情報 REQINF に対応するメモリアクセスが実行されていないときに、スケジューリング部 220 が他のリクエスト情報 REQINF を受信したとする。この場合、スケジューリング部 220 は、メモリアクセス要求を単独で受信したことを示す単独要求情報 REQLN をリクエスト情報 REQINF に含めてリクエスト保持パイプライン 230 に出力する。

40

#### 【 0 0 4 1 】

並列度 1 は、メモリアクセスの並列度を示し、メモリ 30 のアクセスを制御する、並列に動作する処理部 25 (250, 251, 252) の数を示す。並列度 1 は、メモリ 30 の動作周波数に応じて変更されてもよい。以下では、メモリアクセスの並列度が "2" であるとして説明される。位相差 m は、メモリ 30 に供給するアクティブコマンド ACT の最小供給間隔 (メモリクロック MCLK のサイクル数) を示し、並列度 1 (処理部 25 の動作数) に応じて異なる。

50

## 【0042】

平均リクエスト間隔  $n$  は、アクティブコマンド A C T の平均供給間隔（メモリクロック M C L K のサイクル数）を示す。最長パケットサイズ M P S は、メモリアクセスコントローラ 2 0 に供給されるメモリアクセス要求 M R E Q が示すパケットサイズ P S のうち、最長のパケットサイズ P S を示し、C P U 1 0 およびメモリ 3 0 が搭載されるシステムの仕様に応じて設定される。パケットサイズ P S は、1 回のメモリアクセス要求 M R E Q に対応してメモリ 3 0 から読み出されるデータ D Q のサイズまたはデータ D Q の出力回数を示す。最長パケットサイズ M P S は、最大のデータの読み出しサイズの一例である。

## 【0043】

資源番号 N X T R S C は、アクティブコマンド A C T およびリードコマンド R D 等のアクセスコマンドを生成する処理部 2 5 を識別する番号であり、"0" が処理部 2 5 0 、"1" が処理部 2 5 1 、"2" が処理部 2 5 2 を示す。スケジューリング部 2 2 0 の例は、図 5 に示し、アクティブコマンド A C T およびリードコマンド R D の例は、図 1 0 以降に示す。例えば、アクティブコマンド A C T は、メモリ 3 0 に含まれる複数のワード線のいずれかを選択するためにメモリ 3 0 に出力される。リードコマンド R D は、選択されたワード線に接続される複数のメモリセルのうちの所定数を選択するためにメモリ 3 0 に出力される。

10

## 【0044】

リクエスト保持パイプライン 2 3 0 は、シフト信号 S F T O U T 0 に基づいて動作する直列に接続された複数（この例では、 $j + 1$  個）のステージ S T G ( S T G 0 - S T G  $j$  ) を有する。"j" は、2 以上の整数であり、例えば、"7" である。各ステージ S T G は、資源番号 N X T R S C ( 以下、単に資源番号 R S C とも称する ) と経過サイクル C Y C とリクエスト情報 R E Q I N F とを保持する保持領域を有する。例えば、経過サイクル C Y C は、メモリクロック M C L K のクロックサイクル数で示される。互いに隣接するステージ S T G 間での情報のシフトは、図 7 で説明するシフト入力信号 S F T I N に同期して実行される。

20

## 【0045】

リクエスト保持パイプライン 2 3 0 は、動作モードに応じたタイミングで初段のステージ S T G 0 から後段のステージ S T G 1 - S T G  $j$  に資源番号 R S C 、経過サイクル C Y C およびメモリアクセス要求 R E Q I N F をシフトするシフトレジスタとして動作する。但し、リクエスト保持パイプライン 2 3 0 は、並列度 1 と資源番号 R S C とに応じて、ステージ S T G が情報を保持する期間（サイクル数）が変化する点で、通常のシフトレジスタと異なる。リクエスト保持パイプライン 2 3 0 の各ステージ S T G の例は、図 7 に示す。

30

## 【0046】

設定レジスタ 2 4 0 は、並列度 1 、位相差  $m$  、平均リクエスト間隔  $n$  、最長パケットサイズ M P S 、ロウタイミング T R O W およびカラムタイミング T C O L がそれぞれ設定されるレジスタを有する。例えば、並列度 1 、位相差  $m$  、平均リクエスト間隔  $n$  、最長パケットサイズ M P S 、ロウタイミング T R O W およびカラムタイミング T C O L は、メモリ 3 0 および C P U 1 0 等の仕様に応じて、設定レジスタ 2 4 0 に設定される。例えば、設定レジスタ 2 4 0 への設定は、C P U 1 0 の初期化プログラムにより実行される。並列度 1 、位相差  $m$  、平均リクエスト間隔  $n$  は、各処理部 2 5 とスケジューリング部 2 2 0 とに供給される。最長パケットサイズ M P S は、スケジューリング部 2 2 0 に供給される。ロウタイミング T R O W およびカラムタイミング T C O L は、各処理部 2 5 に供給される。

40

## 【0047】

各処理部 2 5 ( 2 5 0 、 2 5 1 、 2 5 2 ) は、リクエスト保持パイプライン 2 3 0 の各ステージ S T G から出力されるリクエスト情報 R E Q I N F ( メモリアクセス要求 ) を含む情報に基づいて、複数のアクセスコマンドをメモリ 3 0 に出力する。複数のアクセスコマンドは、ロウ制御信号 R O W およびカラム制御信号 C O L としてメモリ 3 0 に出力される。ロウ制御信号 R O W は、アクティブコマンド A C T 、バンクアドレスおよびロウアドレスを含む。カラム制御信号 C O L は、リードコマンド R D ( またはライトコマンド ) 、バンクアドレスおよびカラムアドレスを含む。

50

## 【0048】

例えば、各処理部25は、自処理部25を示す資源番号RSCを保持するステージSTGが出力する経過サイクルCYCに基づいて、リクエスト情報REQINFを使用してロウ制御信号ROWまたはカラム制御信号COLを出力する。例えば、並列度1=2の場合、処理部250、251が動作し、処理部252は動作を停止する。並列度1=3の場合、処理部250、251、252が動作する。

## 【0049】

また、各処理部25は、データ入力タイミング信号DQINおよびイネーブル信号ENを生成するデータタイミング制御部255を有する。データタイミング制御部255は、リードコマンドRDに対応してメモリ30からデータDQが出力されるタイミングに合わせてデータ入力タイミング信号DQINを生成する。また、データタイミング制御部255は、メモリアクセス要求MREQ毎にデータバッファ290から出力データDOUTの出力が可能になったことに基づいてイネーブル信号ENを生成する。イネーブル信号ENは、データバッファ280に保持されたデータDQをメモリアクセスコントローラ20の外部に出力する出力開始タイミングを示す。

10

## 【0050】

さらに、データタイミング制御部255は、カラム制御信号COLの出力に使用したりクエスト情報REQINFをバッファ制御部270に出力してもよい。なお、バッファ制御部270に出力するリクエスト情報REQINFは、処理部25内の別の要素から出力されてもよい。処理部25の例は、図8に示す。

20

## 【0051】

セレクタ260は、各処理部25が出力するロウ制御信号ROWおよびカラム制御信号COLを選択してメモリ30に出力する。なお、セレクタ260は、オア回路の論理で設計されてもよい。

## 【0052】

バッファ制御部270は、データ入力タイミング信号DQINに基づいて、メモリ30から読み出されたデータDQをデータバッファ280に格納する制御を実行する。また、バッファ制御部270は、イネーブル信号ENに基づいて、データバッファ280に保持されたデータDQを出力データDOUTとして出力する制御を実行する。データバッファ280は、メモリ30から読み出されるデータDQを保持する複数のバッファを有する。バッファ制御部270およびデータバッファ280の例は、図9に示す。

30

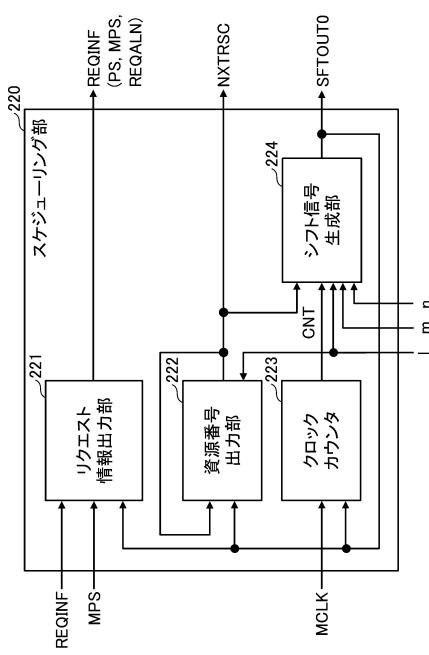

## 【0053】

図5は、図4のスケジューリング部220の一例を示す。スケジューリング部220は、リクエスト情報出力部221、資源番号出力部222、クロックカウンタ223およびシフト信号生成部224を有する。

## 【0054】

リクエスト情報出力部221は、リクエスト受信部210から受けるリクエスト情報REQINFと設定レジスタ240に保持された最長パケットサイズMPSを順次保持する。リクエスト情報出力部221は、保持した情報と単独要求情報REQALNとをリクエスト情報REQINFとして、シフト信号SFTOUT0に同期してリクエスト保持バイオペライン230に順次出力する。

40

## 【0055】

資源番号出力部222は、リクエスト情報REQINFを使用してメモリ30に出力するアクセスコマンドを生成する処理部25(250、251、252)を示す資源番号NXTRSCを順次生成して出力する。資源番号出力部222は、並列度1=2の場合、シフト信号SFTOUT0に同期して、例えば、処理部250、251を示す"0"、"1"を資源番号NXTRSCとして交互に出力する。資源番号出力部222は、並列度1=3の場合、シフト信号SFTOUT0に同期して、処理部250、251、252を示す"0"、"1"、"2"を資源番号NXTRSCとして交互に出力する。

## 【0056】

50

これにより、資源番号出力部 222 を、"並列度 1 - 1"を最大値として資源番号 N X T R S C を交互に生成するカウンタとして動作させることができ、資源番号 N X T R S C の総数を、並列度 1 (動作モード) に応じて相違させることができる。並列度 1 に応じて資源番号 N X T R S C を交互に出力できるため、並列度 1 の設定にかかわりなく、リクエスト保持パイプライン 230 を動作させることができる。この結果、メモリアクセスコントローラ 20 は、並列度 1 に応じたタイミングでアクセスコマンドをメモリ 30 に出力することができる。

#### 【0057】

クロックカウンタ 223 は、メモリクロック M C L K に同期してカウンタ値 C N T を生成し、生成したカウンタ値 C N T をシフト信号生成部 224 に出力する。例えば、クロックカウンタ 223 は、シフト信号 S F T O U T 0 が出力されていない間、メモリクロック M C L K に同期してカウンタ値 C N T をインクリメントする。また、クロックカウンタ 223 は、シフト信号 S F T O U T 0 の出力に応答してカウンタ値 C N T を"1"にリセットする。

10

#### 【0058】

シフト信号生成部 224 は、資源番号 N X T R S C 、カウンタ値 C N T 、並列度 1 、位相差 m および平均リクエスト間隔 n に基づいて決定される時間間隔でシフト信号 S F T O U T 0 を生成し、出力する。

#### 【0059】

シフト信号生成部 224 は、並列度 1 = 2 、資源番号 N X T R S C = 0 の場合、カウンタ値 C N T = m のときにシフト信号 S F T O U T 0 を出力する。シフト信号生成部 224 は、並列度 1 = 2 で資源番号 N X T R S C = 1 の場合、カウンタ値 C N T = "2 n - m" のときにシフト信号 S F T O U T 0 を出力する。シフト信号生成部 224 は、並列度 1 = 3 の場合、カウンタ値 C N T が" n "になる毎にシフト信号 S F T O U T 0 を出力する。

20

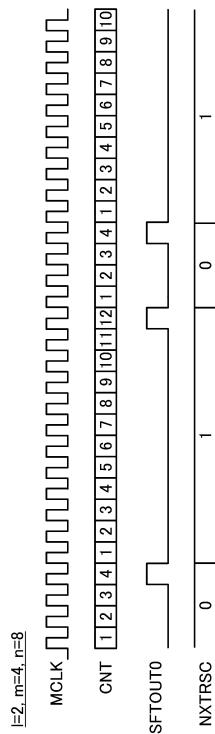

#### 【0060】

図 6 は、図 5 のスケジューリング部 220 の動作の一例を示す。図 6 は、並列度 1 = 2 、位相差 m = 4 、平均リクエスト間隔 n = 8 の例を示す。

#### 【0061】

スケジューリング部 220 は、並列度 1 = 2 の場合、資源番号 N X T R S C = 0 のとき、クロックカウンタ 223 が"4"をカウントしたことに基づいてシフト信号 S F T O U T 0 を出力する。また、スケジューリング部 220 は、並列度 1 = 2 の場合、資源番号 N X T R S C = 1 のとき、クロックカウンタ 223 が"12"をカウントしたことに基づいてシフト信号 S F T O U T 0 を出力する。

30

#### 【0062】

スケジューリング部 220 は、C P U 10 に接続されるメモリ 30 の仕様に応じて設定された並列度 1 、位相差 m および平均リクエスト間隔 n と、現在の資源番号 N X T R S C とに基づいて、カウンタ値 C N T の最大値を変更することができる。そして、スケジューリング部 220 は、最大値が可変なカウンタ値 C N T に基づいて、所望のタイミングでシフト信号 S F T O U T 0 を出力することができ、シフト信号 S F T O U T 0 の出力に合わせて資源番号 N X T R S C を更新することができる。

40

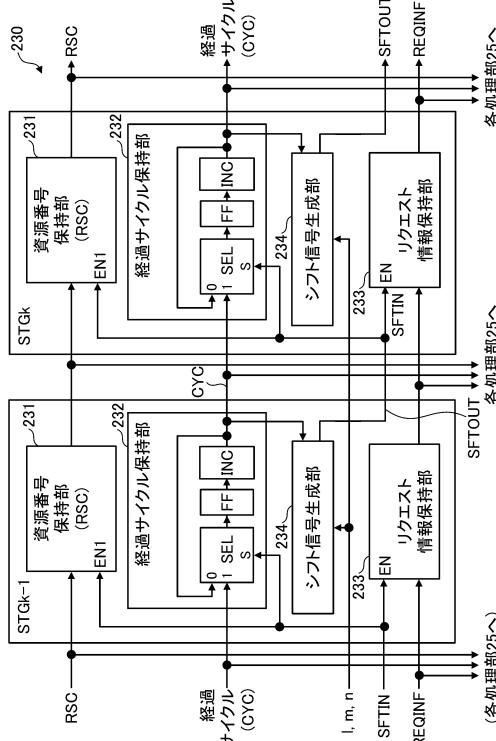

#### 【0063】

図 7 は、図 4 のリクエスト保持パイプライン 230 のステージ S T G の一例を示す。各ステージ S T G の構成は、互いに同じであるため、図 7 では、2 段分 ( k - 1 段目と k 段目 ( k は、1 以上、8 以下の整数) ) を示す。各ステージ S T G は、資源番号保持部 231 、経過サイクル保持部 232 、リクエスト情報保持部 233 およびシフト信号生成部 234 を有する。

#### 【0064】

なお、初段のステージ S T G 0 は、図 5 のスケジューリング部 220 から出力される資源番号 R S C 、リクエスト情報 R E Q I N F およびシフト信号 S F T O U T 0 を受ける。ステージ S T G 0 は、スケジューリング部 220 からのシフト信号 S F T O U T 0 をシフ

50

ト入力信号 SFTIN として受ける。ステージ STG0 に供給される経過サイクル CYC は、スケジューリング部 220 からリクエスト情報 REQINF を受けたときを基準 (= "0") として積算される経過サイクルであり、図示しないクロックカウンタにより生成される。また、初段のステージ STG0 に入力される情報は、各処理部 25 に供給されない。

#### 【0065】

資源番号保持部 231 は、有効レベル（例えば、ハイレベル）のシフト入力信号 SFTIN をイネーブル端子 EN1 で受けている間、前段からの資源番号 RSC を取り込んで保持し、保持した資源番号 RSC を後段のステージ STG と各処理部 25 とに出力する。2 段目以降のステージ STG は、前段のステージ STG が output するシフト信号 SFTOUT 0 をシフト入力信号 SFTIN として受けて動作する。なお、初段のステージ STG0 の資源番号保持部 231 は、図 5 のスケジューリング部 220 の資源番号出力部 222 が output する資源番号 NXTRSC（並列度  $l = 2$  の場合、"0"、"1" の繰り返し）を順次受け 10 る。

#### 【0066】

経過サイクル保持部 232 は、セレクタ SEL、フリップフロップ FF およびインクリメンタ INC を有する。セレクタ SEL は、シフト入力信号 SFTIN がハイレベルの間、前段からの経過サイクル CYC を選択し、シフト入力信号 SFTIN がロウレベルの間、インクリメンタ INC からの経過サイクル CYC を選択する。そして、セレクタ SEL は、選択した経過サイクル CYC をフリップフロップ FF に出力する。

#### 【0067】

フリップフロップ FF は、セレクタ SEL から受ける経過サイクル CYC を図示しないメモリクロック MCLK に同期して取り込み、取り込んだ経過サイクル CYC をインクリメンタ INC に出力する。インクリメンタ INC は、経過サイクル CYC を "1" 増加させ、増加させた経過サイクル CYC をセレクタ SEL の入力に戻すとともに、次段のステージ STG および各処理部 25 に出力する。

#### 【0068】

2 段目以降の各ステージ STG1 - STG8 の経過サイクル保持部 232 は、前段のステージ STG の経過サイクル保持部 232 が保持する経過サイクル CYC（サイクル数）を、前段のステージ STG が output するシフト信号 SFTOUT に同期して保持する。また、各ステージ STG1 - STGj の経過サイクル保持部 232 は、前段のステージ STG がシフト信号 SFTOUT を出力しない間、保持しているサイクル数を順次更新する。これにより、各ステージ STG の経過サイクル保持部 232 は、初段のステージ STG0 でリクエスト情報 REQINF を受けてからのサイクル数を保持することができ、保持しているサイクル数を各処理部 25 に出力することができる。この結果、各処理部 25 は、各ステージ STG からのサイクル数に基づいて、メモリ 30 へのアクセスコマンドの出力タイミングを判断することができる。

#### 【0069】

シフト信号生成部 234 は、並列度  $l$ 、位相差  $m$  および平均リクエスト間隔  $n$  と、経過サイクル保持部 232 が output する経過サイクル CYC とに基づいてシフト信号 SFTOUT を生成する。シフト信号生成部 234 が生成したシフト信号 SFTOUT は、次段のステージ STG にシフト入力信号 SFTIN として供給される。このように、各ステージ STG のシフト信号生成部 234 は、経過サイクル CYC が、並列度  $l$ 、位相差  $m$  および平均リクエスト間隔  $n$  と自ステージ STG の位置 ( $= k$ ) とにより決定される値になった場合、シフト信号 SFTOUT を出力する。

#### 【0070】

シフト信号生成部 234 は、並列度  $l = 2$  で、資源番号保持部 231 が保持する資源番号 RSC が "0" の場合、経過時刻が " $k * n + m$ " のとき、シフト信号 SFTOUT を 1 サイクルの期間、有効レベル（例えば、ハイレベル）に設定する。符号 \* は、積を示す。シフト信号生成部 234 は、並列度  $l = 2$  で、資源番号保持部 231 が保持する資源番号 RSC が "1" の場合、経過時刻が " $(k + 1) * n$ " のとき、シフト信号 SFTOUT を 1 サイクルの期間、有効レベル（ハイレベル）に設定する。

10

20

30

40

50

イクルの期間、有効レベルに設定する。シフト信号生成部 234 は、並列度  $l = 3$  の場合、経過時刻が"  $(k + 1) * n$ " のとき、シフト信号 SFTOUT を 1 サイクルの期間、有効レベルに設定する。

#### 【0071】

すなわち、シフト信号生成部 234 は、メモリ 30 の仕様に応じて予め設定された並列度  $l$ 、位相差  $m$  および平均リクエスト間隔  $n$  と、現在の資源番号 NXTRSC とに応じて、シフト信号 SFTOUT の出力タイミングを変更することができる。この結果、アクティブコマンド ACT の供給間隔が一定でない場合にも、各ステージ STG のシフト信号 SFTOUT の出力タイミングを揃えることができ、リクエスト保持パイプライン 230 の誤動作を抑止することができる。

10

#### 【0072】

例えば、並列度  $l = 2$ 、位相差  $m = 4$ 、平均リクエスト間隔  $n = 8$  であるとする。この場合、資源番号 RSC = 0 を保持する初段のステージ STG0 は、リクエスト情報 REQINF を受けてから 4 サイクル後にシフト信号 SFTOUT を出力する。資源番号 RSC = 0 を保持する 2 段目のステージ STG1 は、リクエスト情報 REQINF を受けてから 12 サイクル後にシフト信号 SFTOUT を出力する。資源番号 RSC = 0 を保持する 3 段目のステージ STG2 は、リクエスト情報 REQINF を受けてから 20 サイクル後にシフト信号 SFTOUT を出力する。

#### 【0073】

また、資源番号 RSC = 1 を保持する初段のステージ STG0 は、リクエスト情報 REQINF を受けてから 8 サイクル後にシフト信号 SFTOUT を出力する。資源番号 RSC = 1 を保持する 2 段目のステージ STG1 は、リクエスト情報 REQINF を受けてから 16 サイクル後にシフト信号 SFTOUT を出力する。資源番号 RSC = 1 を保持する 3 段目のステージ STG2 は、リクエスト情報 REQINF を受けてから 24 サイクル後にシフト信号 SFTOUT を出力する。

20

#### 【0074】

一方、並列度  $l = 3$ 、位相差  $m = 8$ 、平均リクエスト間隔  $n = 8$  であるとする。この場合、初段のステージ STG0 は、リクエスト情報 REQINF を受けてから 8 サイクル後にシフト信号 SFTOUT を出力する。2 段目のステージ STG1 は、リクエスト情報 REQINF を受けてから 16 サイクル後にシフト信号 SFTOUT を出力する。3 段目のステージ STG2 は、リクエスト情報 REQINF を受けてから 24 サイクル後にシフト信号 SFTOUT を出力する。

30

#### 【0075】

リクエスト情報保持部 233 は、有効レベルのシフト入力信号 SFTIN をイネーブル端子 EN1 で受けている間、前段からのリクエスト情報 REQINF を取り込んで保持する。リクエスト情報保持部 233 は、取り込んだリクエスト情報 REQINF を次段のステージ STG および各処理部 25 に出力する。初段のステージ STG0 のリクエスト情報保持部 233 は、スケジューリング部 220 のリクエスト情報出力部 221 が出力するリクエスト情報 REQINF を取り込む。

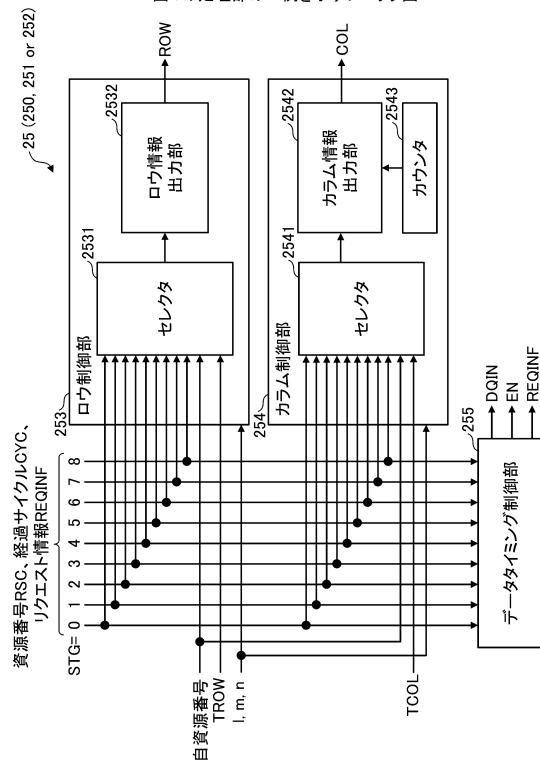

#### 【0076】

図 8 は、図 4 の処理部 25 ( 250, 251, 252 ) の一例を示す。図 8 では、リクエスト保持パイプライン 230 が 9 個のステージ STG0 - STG8 を有するとする。各処理部 25 は、データタイミング制御部 255 に加えて、セレクタ 2531 およびロウ情報出力部 2532 を有するロウ制御部 253 と、セレクタ 2541、カラム情報出力部 2542 およびカウンタ 2543 を有するカラム制御部 254 とを有する。

40

#### 【0077】

セレクタ 2531 は、リクエスト保持パイプライン 230 の各ステージ STG0 - STG8 から資源番号 RSC、経過サイクル CYC およびリクエスト情報 REQINF を受けれる。また、セレクタ 2531 は、設定レジスタ 240 からロウタイミング TROW および並列度  $l$  を受ける。

50

## 【0078】

セレクタ2531は、自処理部25の識別番号である自資源番号と一致する資源番号RSCと、ロウタイミングROWで示されるサイクルと一致する経過サイクルCYCとを出力するステージSTGから出力されるリクエスト情報REQINFを選択する。そして、セレクタ2531は、選択したリクエスト情報REQINFをロウ情報出力部2532に出力する。ロウ情報出力部2532は、セレクタ2531から受けるリクエスト情報REQINFに応答して、リクエスト情報REQINFを使用してロウ制御信号ROWを生成し、メモリ30に出力する。

## 【0079】

セレクタ2541は、リクエスト保持パイプライン230の各ステージSTG0-STG8からの資源番号RSC、経過サイクルCYCおよびリクエスト情報REQINFを受ける。また、セレクタ2541は、設定レジスタ240からカラムタイミングTCOLおよび並列度1を受ける。

10

## 【0080】

セレクタ2541は、自処理部25の識別番号である自資源番号と一致する資源番号RSCと、カラムタイミングTCOLで示されるサイクルと一致する経過サイクルCYCとを出力するステージSTGから出力されるリクエスト情報REQINFを選択する。そして、セレクタ2541は、選択したリクエスト情報REQINFをカラム情報出力部2542に出力する。カウンタ2543は、カラム制御信号COLの出力回数を計数する。カラム情報出力部2542は、セレクタ2541から受けるリクエスト情報REQINFに応答して、リクエスト情報REQINFを使用してカラム制御信号COLを生成し、メモリ30に出力する。この際、カラム情報出力部2542は、カウンタ2543が計数する回数分のカラム制御信号COLを、所定数のサイクルの経過毎に出力する。

20

## 【0081】

このように、各処理部25は、リクエスト保持パイプライン230の複数のステージSTGが保持する資源番号RSCと経過サイクルCYCとリクエスト情報REQINFとを受ける。そして、各処理部25は、受けた資源番号RSCが自資源番号と一致する場合、受けたリクエスト情報REQINFに対応するアクセスコマンド（アクティブコマンドACTまたはリードコマンドRDなど）をメモリ30に出力する。換言すれば、各処理部25は、自資源番号RSCを出力するステージSTGが保持する経過サイクルCYCが示すサイクル数が、並列度1に応じて決定されるアクセスコマンドの出力サイクルを示す場合、対応するアクセスコマンドをメモリ30に出力する。したがって、並列度1によってアクセスコマンドの出力サイクルが変更される場合にも、並列度1と資源番号RSCと経過サイクルCYCとに基づいて、正しいタイミングでアクセスコマンドをメモリ30に出力することができる。

30

## 【0082】

データタイミング制御部255は、自資源番号と一致する資源番号RSCと、カラムタイミングTCOLで示されるサイクルと一致する経過サイクルCYCとを出力するステージSTGから出力されるリクエスト情報REQINFを受ける。リクエスト情報REQINFは、単独要求情報REQALNを含む。データタイミング制御部255は、受けた情報に基づいてデータ入力タイミング信号DQINおよびイネーブル信号ENを生成する。また、データタイミング制御部255は、図4で説明したように、カラム制御信号COLの出力に使用したリクエスト情報REQINFを出力する。

40

## 【0083】

なお、データ入力タイミング信号DQINおよびイネーブル信号ENは、どのメモリアクセス要求REQ（リードアクセス要求）に対応するかを識別する識別情報を含んでもよい。この場合、識別情報は、シーケンス番号でもよい。データ入力タイミング信号DQINに基づくライトポインタ値WPの生成タイミングおよびイネーブル信号ENの生成タイミングは、図13および図15等で説明される。

## 【0084】

50

また、メモリアクセスコントローラ 20 は、設定レジスタ 240 に設定された並列度 1、位相差  $m$  および平均リクエスト間隔  $n$  に基づいてメモリ 30 のアクセスを制御する。例えば、並列度 1 は、"2" または "3" である。並列度 1、位相差  $m$  および平均リクエスト間隔  $n$  が可変であるため、図 5、図 7 および図 8 に示すようにメモリアクセスのための制御回路が複雑になる。しかしながら、図 5、図 7 および図 8 に示す制御回路は、一例であり、メモリアクセスコントローラ 20 は、他の制御回路を有してもよい。例えば、並列度 1 = 2、位相差  $m = 4$ 、平均リクエスト間隔  $n = 8$  に限定される場合、図 6 に示したように、シフト信号 SFTOUT0 の出力タイミングは、固定化される。このため、メモリアクセスのための制御回路を図 5、図 7 および図 8 に比べて簡易にすることができる。

#### 【0085】

なお、メモリアクセスコントローラ 20 がメモリ 30 に発行するアクティブコマンド A CT およびリードコマンド RD のタイミングの例は、特願 2020-097826 号の図 9 - 図 17 に記載されている。

#### 【0086】

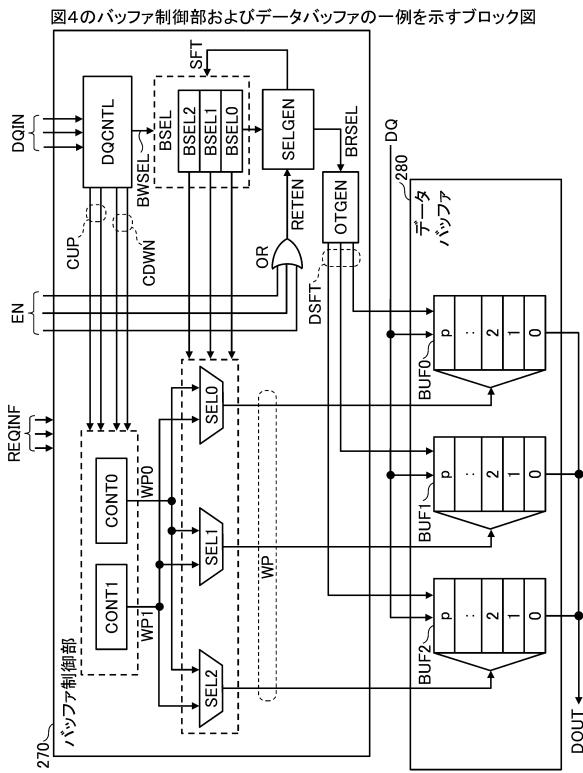

図 9 は、図 4 のバッファ制御部 270 およびデータバッファ 280 の一例を示す。バッファ制御部 270 およびデータバッファ 280 の動作の例は、図 11 - 図 18 で説明される。バッファ制御部 270 は、データ出力制御部 DQCTL、バッファセレクタ BSEL、カウンタ CONT (CONT0、CONT1) およびセレクタ SEL (SEL0、SEL1、SEL2) を有する。また、バッファ制御部 270 は、オア回路 OR、選択信号生成部 SELGEN および出力タイミング生成部 OTGEN を有する。

#### 【0087】

データバッファ 280 は、バッファ BUF (BUF0、BUF1、BUF2) を有する。各バッファ BUF0 - BUF2 は、メモリ 30 から読み出されるデータ DQ を保持する  $p + 1$  個のエントリを有し、ライトポインタ値 WP で指定されたエントリにデータ DQ を書き込む。各バッファ BUF0 - BUF2 は、シフトレジスタの構造を有する。この例では、"p" は、"3" 以上の整数である。

#### 【0088】

データ出力制御部 DQCTL は、各処理部 25 のデータタイミング制御部 255 からのデータ入力タイミング信号 DQIN に応答して、バッファ BUF0 - BUF2 のいずれかを示す書き込み選択信号 BWSEL をバッファセレクタ BSEL に出力する。また、データ出力制御部 DQCTL は、データ入力タイミング信号 DQIN に応答して、カウンタ CONT0、CONT1 のいずれかにカウントアップ信号 CUP を出力する。さらに、データ出力制御部 DQCTL は、あらかじめ設定された所定の条件にしたがって、カウンタ CONT0 (または CONT1) にカウントダウン信号 CDWN を出力する。データ出力制御部 DQCTL は、カウンタ CONT0、CONT1 の各々をカウントアップまたはカウントダウンするカウンタ制御部の一例である。

#### 【0089】

所定の条件は、カウンタ CONT0 (または CONT1) のライトポインタ値 WP0 (または WP1) がパケットサイズ PS に対応する最大値になる前に、バッファ BUF に保持されたデータ DQ の出力が開始される場合である。例えば、データ出力制御部 DQCTL は、カウントダウン信号 CDWN を生成するタイミングを、図 8 のデータタイミング制御部 255 から受けるリクエスト情報 REQINF に基づいて決定してもよい。

#### 【0090】

シフトレジスタの構造を有するバッファ BUF に対して、データ出力制御部 DQCTL は、バッファ BUF からデータ DQ を出力させるとときにカウンタ CONT をカウントダウンさせる。これにより、バッファ BUF のシフト動作により新たなデータ DQ の格納位置がずれる場合にも、正しい位置にデータ DQ を格納することができる。

#### 【0091】

また、データ出力制御部 DQCTL は、バッファ BUF へのデータ DQ の格納とバッファ BUF からデータ DQ の出力とを同時にを行うときにカウンタ CONT のカウントアッ

10

20

30

40

50

プおよびカウントダウンを停止する。これにより、バッファBUFのシフト動作にかかわりなく、バッファBUFの同じ位置に新たなデータDQを格納することができる。すなわち、バッファBUFへのデータDQの格納とバッファBUFからデータDQの出力とを同時に使うときにも、正しい位置に新たなデータDQを格納することができる。

#### 【0092】

なお、データ出力制御部DQCNTLは、メモリ30へのアクセスを実行していないアイドル状態において、データ入力タイミング信号DQINを受けた場合、"0"の書き込み選択信号BWSLEを出力する。また、データ出力制御部DQCNTLは、アイドル状態において、カウンタCONT0にカウントアップ信号CUPを出力する。この後、データ出力制御部DQCNTLは、異なるメモリアクセス要求REQに対応するデータ入力タイミング信号DQINを受けた場合、カウンタCONT1にカウントアップ信号CUPを出力する。

10

#### 【0093】

データ出力制御部DQCNTLは、アイドル状態を、リクエスト情報REQINFに含まれる、メモリアクセス要求REQを単独で受信したことを示す単独要求情報REQALNに基づいて判定可能である。また、データ出力制御部DQCNTLは、リクエスト情報REQINFに単独要求情報REQALNが含まれない場合、アイドル状態でないことを判定可能である。

#### 【0094】

データ出力制御部DQCNTLは、同じメモリアクセス要求REQに対応するデータ入力タイミング信号DQINを受ける毎に、同じカウンタCONTに所定数（例えば"4"）のカウントアップ信号CUPを出力する。また、データ出力制御部DQCNTLは、データ入力タイミング信号DQINの出力元の処理部25が変わる毎に、カウンタCONT0、CONT1を交互に使用するためにカウントアップ信号CUPを出力するカウンタCONTを切り替える。

20

#### 【0095】

バッファセレクタBSELは、選択するバッファBUFを識別するバッファ選択値をそれぞれ保持する3つの保持部BSEL0、BSEL1、BSEL2を有する。保持部BSEL0 - BSEL2に保持されたバッファ選択値は、各処理部25のデータタイミング制御部255からのデータ入力タイミング信号DQINに応答して、セレクタSEL0 - SEL2に出力される。以下では、保持部BSEL0 - BSEL2にそれぞれ保持されたバッファ選択値は、バッファ選択値BSEL0 - BSEL2とも称される。

30

#### 【0096】

バッファセレクタBSELは、保持部BSEL0、BSEL1、BSEL2を、番号が小さい順に優先的に使用する。例えば、バッファセレクタBSELは、アイドル状態において、"0"の書き込み選択信号BWSLEを受けた場合、受けた"0"を優先度が最も高い保持部BSEL0に保持する。バッファセレクタBSELは、この状態で"1"の書き込み選択信号BWSLEを受けた場合、受けた"1"を優先度が次に高い保持部BSEL1に保持する。バッファセレクタBSELは、さらにこの状態で"2"の書き込み選択信号BWSLEを受けた場合、受けた"2"を優先度が最も低い保持部BSEL2に保持する。

40

#### 【0097】

バッファセレクタBSELは、保持部BSEL0に保持しているバッファ選択値を選択信号生成部SELGENに出力する。そして、バッファセレクタBSELは、保持部BSEL1、BSEL2にそれぞれ保持したバッファ選択値を、シフト信号SFTに基づいて優先度が1つ低い保持部BSEL0、BSEL1に移動する。

#### 【0098】

カウンタCONT0は、カウントアップ信号CUPに応答してライトポインタ値WP0を"1"ずつ増加し、カウントダウン信号CDWNに応答してライトポインタ値WP0を"1"ずつ減少する。カウンタCONT1は、カウントアップ信号CUPに応答してライトポインタ値WP1を"1"ずつ増加し、カウントダウン信号CDWNに応答してライトポインタ

50

値WP1を"1"ずつ減少する。

【0099】

セレクタSEL0-SEL2は、カウンタCONT0、CONT1とバッファBUF0-BUF2の間に配置される。セレクタSEL0は、データ出力制御部DQCTLから"0"の書き込み選択信号BWSLEが出力されたことに基づいてライトポインタ値WP0、WP1のいずれかをライトポインタ値WPとしてバッファBUF0に出力する。セレクタSEL1は、データ出力制御部DQCTLから"1"の書き込み選択信号BWSLEが出力されたことに基づいてライトポインタ値WP0、WP1のいずれかをライトポインタ値WPとしてバッファBUF1に出力する。

【0100】

セレクタSEL2は、データ出力制御部DQCTLから"2"の書き込み選択信号BWSLEが出力されたことに基づいてライトポインタ値WP0、WP1のいずれかをライトポインタ値WPとしてバッファBUF2に出力する。上述したように、アイドル状態においてカウンタCONT0が使用された後、データ入力タイミング信号DQINの出力元の処理部25が変わる毎に、カウンタCONT1、CONT0が交互に使用される。そして、各セレクタSELは、対応するバッファBUFにメモリアクセス要求MREQに含まれるパケットサイズPSに対応する数のデータDQが格納されるまで、最初に選択したライトポインタ値WPを選択し続ける。例えば、各セレクタSELは、パケットサイズPSを、リクエスト情報REQINFに基づいて検出する。

【0101】

カウンタCONT0、CONT1とバッファBUF0-BUF2との間にセレクタSEL0-SEL2を配置することで、任意のカウンタCONTが生成するライトポインタ値WPを任意のバッファBUFに供給することができる。この結果、カウンタCONTの数をバッファBUFの数より少なくすることができ、バッファBUFの数と同じ数のカウンタCONTを設ける場合に比べて、メモリアクセスコントローラ20の回路規模を削減することができる。

【0102】

オア回路ORは、各処理部25のデータタイミング制御部255からのイネーブル信号ENを応答イネーブル信号RETEENとして選択信号生成部SELGENに出力する。選択信号生成部SELGENは、応答イネーブル信号RETEENを受けたときに保持部BSEL0で保持しているバッファ選択値を読み出し選択信号BRSSELとして出力タイミング生成部OTGENに出力する。読み出し選択信号BRSSELは、メモリアクセス要求MREQに対応してメモリ30から読み出されたデータDQを保持しているバッファBUFを示す。

【0103】

出力タイミング生成部OTGENは、選択信号生成部SELGENからの読み出し選択信号BRSSELをデコードし、読み出し選択信号BRSSELの値が示すバッファBUFを選択する。出力タイミング生成部OTGENは、選択したバッファBUFにデータシフト信号DSFTを出力する。ここで、出力タイミング生成部OTGENは、メモリアクセス要求MREQに含まれるパケットサイズPSで示されるデータ数分のパルスを有するデータシフト信号DSFTを連続して出力する。なお、メモリ30がDDRタイプである場合、データシフト信号DSFTのパルスは、メモリクロックMCLKの1周期に2回出力される。

【0104】

各バッファBUF0-BUF2は、シフト信号DSFTに応答して数値の大きいエントリから数値の小さいエントリに保持しているデータDQをシフトする。そして、各バッファBUF0-BUF2は、"0"番のエントリから取り出したデータDQを出力データDOUTとして、共通の出力データ線DOUTに出力する。なお、バッファ制御部270は、バッファBUF0-BUF2から出力する出力データDOUTが出力データ線DOUT上で衝突しないようにシフト信号DSFTを生成する。

10

20

30

40

50

**【0105】**

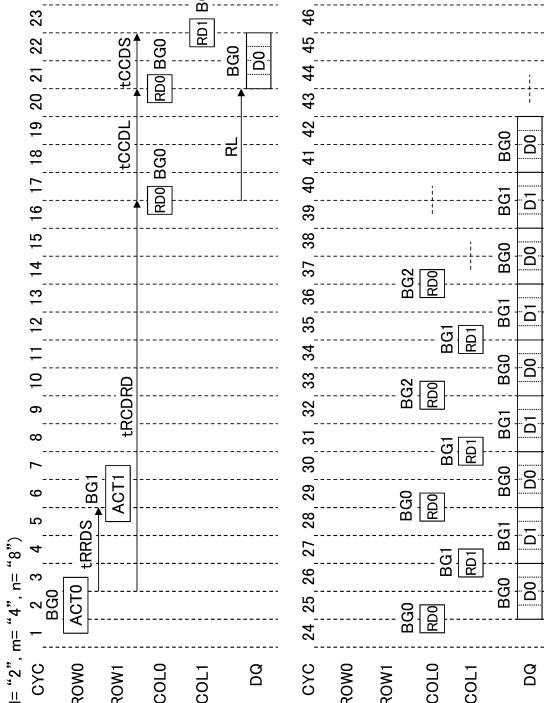

図10は、図4のメモリアクセスコントローラ20によりメモリ30にリードアクセスする一例を示す。図10は、並列度 $l = 2$ 、位相差 $m = 4$ 、平均リクエスト間隔 $n = 8$ に設定される場合の動作の例を示す。ロウ制御信号ROW0およびカラム制御信号COL0は、処理部250から出力され、ロウ制御信号ROW1およびカラム制御信号COL1は、処理部251から出力される。メモリ30は、2つのバンクグループBG0、BG1を有するとする。図10において、順次増加する数値は、経過サイクルCYC(メモリクロックMCLKのサイクル数の積算値)を示す。

**【0106】**

まず、処理部250は、CYC1において、バンクグループBG0にアクティブコマンドACT0を出力する。例えば、アクティブコマンドACTは、2クロックサイクルを使用してメモリ30に供給される。処理部251は、処理部250がアクティブコマンドACT0を出力してから $t_{RRDS}$ (RAS to RAS Delay)後であるCYC5において、バンクグループBG1にアクティブコマンドACT1を出力する。 $t_{RRDS}$ は、異なるバンクグループBG間でのアクティブコマンドACTの最小間隔の仕様である。

10

**【0107】**

処理部250は、アクティブコマンドACT0を出力してから $t_{RCDRD}$ (RAS to CAS Delay)後であるCYC16において、バンクグループBG0に最初のリードコマンドRD0を出力する。処理部250は、リードコマンドRD0を出力してから $t_{CCDL}$ (CAS to CAS Delay Long)後であるCYC20において、バンクグループBG0に2番目のリードコマンドRD0を出力する。 $t_{CCDL}$ は、同一のバンクグループBG間でのカラム系コマンド(リードコマンドRD等)の最小間隔の仕様である。

20

**【0108】**

処理部251は、処理部250がリードコマンドRD0を出力してから $t_{CCDS}$ (CAS to CAS Delay Short)後であるCYC22において、バンクグループBG1に最初のリードコマンドRD1を出力する。 $t_{CCDS}$ は、異なるバンクグループBG間でのカラム系コマンドの最小間隔の仕様である。

30

**【0109】**

この後、処理部250、251は、2サイクル毎にリードコマンドRD(RD0またはRD1)を交互に出力する。各処理部250、251によるリードコマンドRDの出力間隔は4サイクルである。

**【0110】**

処理部250が最初のリードコマンドRD0を出力してからリードレイテンシRLに対応するサイクル後、最初のリードコマンドRD0に対応する最初のリードデータD0がバンクグループBG0から出力される。この例では、バースト長が"4"に設定されているため、メモリクロックMCLKの立ち上がりエッジと立ち下がりエッジのそれぞれに同期して4つのデータが読み出される。さらに、各リードコマンドRDからリードレイテンシRLが経過後に、リードデータD(D0またはD1)が各バンクグループBGからそれぞれ読み出される。

40

**【0111】**

図10に示す動作は、並列度 $l = 2$ 、位相差 $m = 4$ および平均リクエスト間隔 $n = 8$ に応じて、シフト信号SFTOUT0を出力するスケジューリング部220と、ステージSTGのシフト動作を実行するリクエスト保持パイプライン230とにより実現される。これにより、メモリアクセスコントローラ20は、複数の並列度1に共通のリクエスト保持パイプライン230のステージSTGに順次転送される情報を使用して、並列度 $l = 2$ でのリードアクセス動作を実行することができる。

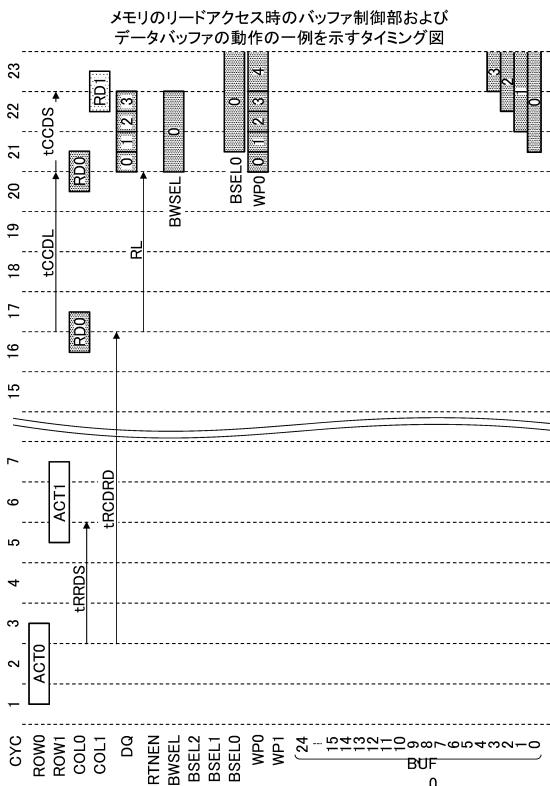

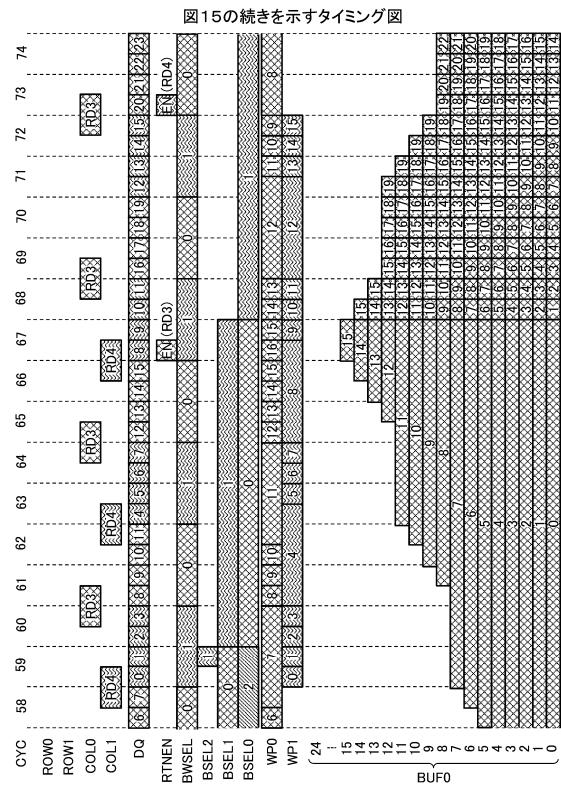

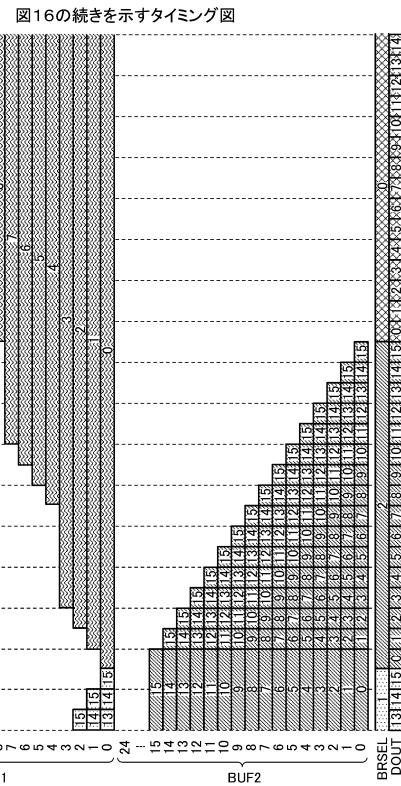

**【0112】**

図11-図18は、メモリ30のリードアクセス時のバッファ制御部270およびデータバッファ280の動作の一例を示す。すなわち、図11-図18は、メモリアクセスコントローラ20によるメモリアクセス方法の一例を示す。図10と同様の動作については

50

、詳細な説明は省略する。

【0113】

図11-図18に示す動作は、図10と同様に、並列度 $l = 2$ 、位相差 $m = 4$ 、平均リクエスト間隔 $n = 8$ に設定されて実行される。最長パケットサイズMPSは、1回のメモリアクセス要求REQに応答してメモリ30からデータDQが32回読み出される"32"に設定される。

【0114】

図11および図12は、同じサイクル期間での動作を示し、図13および図14は、同じサイクル期間での動作を示す。図15および図16は、同じサイクル期間での動作を示し、図17および図18は、同じサイクル期間での動作を示す。以下では、メモリクロックMCLKの経過サイクル数であるサイクルCYC1-CYC74は、符号のみで説明される。アクティブコマンドACT0の元となるメモリアクセス要求REQのパケットサイズPSは、"32"であり、アクティブコマンドACT1の元となるメモリアクセス要求REQのパケットサイズPSは、"16"である。

10

【0115】

CYC37までのメモリ30に対するアクセスは、図10と同様である。例えば、図1-図18では、メモリアクセスコントローラ20の処理部250は、CYC16で最初のリードコマンドRD0を出力し、4サイクル毎に後続のリードコマンドRD0を7回出力する。メモリアクセスコントローラ20の処理部251は、CYC22で最初のリードコマンドRD1を出力し、4サイクル毎に後続のリードコマンドRD1を3回出力する。

20

【0116】

処理部251は、図13のCYC38で、アクティブコマンドACT1に対応する2つのパケットサイズPSのアクセスの最初のリードコマンドRD2を出力し、4サイクル毎に後続のリードコマンドRD2を3回出力する。2回目のアクセスの最初のリードコマンドRD2は、4番目のリードコマンドRD1の4サイクル後に発行される。

20

【0117】

処理部250は、図15のCYC48で、アクティブコマンドACT1に対応する3つのパケットサイズPSのアクセスの最初のリードコマンドRD3を出力し、4サイクル毎に後続のリードコマンドRD3を7回出力する。2回目のアクセスの最初のリードコマンドRD2は、4番目のリードコマンドRD1の4サイクル後に発行される。処理部251は、CYC54で最初のリードコマンドRD4を出力し、4サイクル毎に後続のリードコマンドRD4を7回出力する。

30

【0118】

メモリアクセスコントローラ20は、アクティブコマンドACT0を出力するとき、メモリ30に対する他のアクティブコマンドACTによるアクセスを実行しておらず、図11の開始時、メモリ30は、動作していないアイドル状態である。すなわち、メモリアクセスコントローラ20は、アクティブコマンドACT0の契機となるメモリアクセス要求REQを単独で受信する。上述したように、アイドル状態は、リクエスト情報REQINに含まれる単独要求情報REALNに基づいて判定される。

40

【0119】

メモリ30がアイドル状態の場合、図9のデータ出力制御部DQCTLは、アクティブコマンドACT0を発行した処理部250からのデータ入力タイミング信号DQINの受信に基づいて、図11のCYC21で"0"の書き込み選択信号BWSLEを出力する。"0"の書き込み選択信号BWSLEは、メモリ30から読み出されるデータDQをバッファBUF0に格納することを示す。なお、処理部250は、メモリ30からの4つの連続するデータDQの出力タイミング(例えば、CYC21、CYC22)に合わせて、図示しないデータ入力タイミング信号DQINを出力する。

【0120】

データ出力制御部DQCTLは、処理部250からのデータ入力タイミング信号DQINに基づいてカウンタCONT0にカウントアップ信号CUPを出力する。カウンタC

50

ONT0は、カウントアップ信号CUPに応答して、データDQの出力タイミングに合わせてライトポインタ値WP0を"1"ずつ増加させる。なお、カウンタCONT0、CONT1がそれぞれ出力するライトポインタ値WP0、WP1の初期値は、"0"である。

【0121】

図9のバッファセレクタBSELは、CYC21において、書き込み選択信号BSELの"0"を、優先度が最も高い保持部BSEL0に保持する。保持部BSEL0に保持された"0"によりセレクタSEL0が選択され、ライトポインタ値WP0は、セレクタSEL0を介してバッファBUF0に供給される。そして、バッファBUF0は、CYC21-CYC51に掛けてライトポインタ値WP0が示すエントリにリードコマンドRD0に対応するデータDQ0-DQ31を順次書き込む。

10

【0122】

図13において、図11の2番目のリードコマンドRD0に応答して、CYC25、CYC26でメモリ30からデータDQ4-DQ7が順次読み出される。この後、リードコマンドRD1、RD0に対応してメモリから4つのデータDQが交互に読み出される。パケットサイズPSに対応する32個のデータDQ0-DQ31をメモリ30から読み出すために、リードコマンドRD0は8回発行される。パケットサイズPSに対応する16個のデータDQ0-DQ15をメモリ30から読み出すために、リードコマンドRD1は4回発行される。

【0123】

データ出力制御部DQCTLは、処理部250からのデータ入力タイミング信号DQINの受信に基づいて、"0"の書き込み選択信号BWSLELを出力する。また、データ出力制御部DQCTLは、処理部251からのデータ入力タイミング信号DQINの受信に基づいて、"1"の書き込み選択信号BWSLELを出力する。"1"の書き込み選択信号BWSLELは、メモリ30から読み出されるデータDQをバッファBUF1に格納することを示す。

20

【0124】

なお、図11-図18において、各バッファBUF0-BUF2に付した"0"から"24"は、エントリ番号を示す。タイミング図上において、各バッファBUF0-BUF2のエントリに付した数値は、各エントリが保持するデータDQの番号を示す。

【0125】

30

データ出力制御部DQCTLは、処理部250、251の各々からのデータ入力タイミング信号DQINに基づいてカウンタCONT0、CONT1の各々にカウントアップ信号CUPを出力する。各カウントアップ信号CUPは、メモリ30からのデータDQの受信タイミングに合わせて出力される。これにより、カウンタCONT0、CONT1の各々は、ライトポインタ値WP0、WP1の各々を"1"ずつ増加する。

【0126】

図11および図13において、保持部BSEL0は、バッファBUF0にデータDQ15が格納されるまで"0"を保持している。このため、セレクタSEL0を介してライトポインタ値WP0を受けるバッファBUF0は、ライトポインタ値WP0が示すエントリに、リードコマンドRD0に対応するデータDQを順次書き込む。

40

【0127】

バッファセレクタBSELは、図13のCYC27において、"1"の書き込み選択信号BSELの最初の受信に応答して、書き込み選択信号BSELの"1"を、空いている保持部BSELのうち、優先度が最も高い保持部BSEL1に保持する。保持部BSEL1に保持された"1"によりセレクタSEL1が選択され、ライトポインタ値WP1はバッファBUF1に供給される。

【0128】

保持部BSEL1は、CYC27-CYC35の間、"1"を保持し、"1"の保持部BSEL1によりセレクタSEL1が選択される。このため、CYC27-CYC35において、セレクタSEL1を介してライトポインタ値WP1を受けるバッファBUF1は、ラ

50

イトポインタ値WP0が示すエントリに、リードコマンドRD1に対応するデータDQを順次書き込む。

【0129】

アクティブコマンドACT0を出力した処理部250のデータタイミング制御部255は、図13のCYC35でイネーブル信号EN(RD0)を生成する。この例では、データタイミング制御部255は、最初のリードコマンドRD0の出力から18サイクル後(CYC35)にイネーブル信号EN(RD0)を生成する。18サイクルは、最初のリードコマンドRD0の出力から出力データDOUTの出力が完了するまでの34サイクルから32個の出力データDOUTの出力に掛かる16サイクルを引くことで求められる。CYC35でリードコマンドRD0に対応するイネーブル信号ENを出力することで、データDQ31がバッファBUF0に保持されたCYC51に、バッファBUF0からデータDQ31を出力データDOUTとして出力することができる。

10

【0130】

処理部250からのイネーブル信号ENを応答イネーブル信号RETEENとして受けた選択信号生成部SELGENは、図14のCYC35において、保持部BSEL0で保持しているバッファ選択値="0"を読み出し選択信号BSELとして出力する。図9の出力タイミング生成部OTGENは、"0"の読み出し選択信号BSELに基づいてバッファBUF0にデータシフト信号DSFTを順次出力する。これにより、メモリアクセスコントローラ20は、CYC34-CYC51に掛けて、バッファBUF0に保持されたデータDQ0-DQ31を出力データDOUTとして図3のネットワーク制御部16に連続して出力する(図14、図16)。

20

【0131】

選択信号生成部SELGENは、"0"の読み出し選択信号BSELの出力に応答してバッファセレクタBSELにシフト信号SFTを出力する。バッファセレクタBSELは、シフト信号SFTに応答してシフト動作し、図13のCYC36において、保持部BSEL1に保持しているバッファ選択値="1"を保持部BSEL0に移行する。これにより、バッファBUF0からの出力データDOUTを出力後、バッファBUF1から出力データDOUTを出力することが決定される。

【0132】

保持部BSEL0は、CYC36-CYC51の間、"1"を保持し、"1"の保持部BSEL1によりセレクタSEL1が選択され続ける。CYC36-CYC41において、セレクタSEL1を介してライトポインタ値WP1を受けるバッファBUF1は、ライトポインタ値WP0が示すエントリに、リードコマンドRD1に対応するデータDQを順次書き込む。

30

【0133】

データ出力制御部DQCNTLは、バッファBUF0からデータDQが出力されるタイミングに合わせてカウントダウン信号CDWNを出力する。これにより、ライトポインタ値WP0は、図13のCYC36から"1"ずつ減少する。但し、バッファBUF0からのデータDQの出力とメモリ30から読み出されたデータDQのバッファBUF0への格納とが同時に実行される場合、データ出力制御部DQCNTLは、カウントダウン信号CDWNおよびカウントアップ信号CUPの出力を停止する。このため、例えば、CYC37、CYC38とCYC39の前半とでは、バッファBUF0においてライトポインタ値WP0="12"で示されるエントリにデータDQ15-DQ19が順次格納される。

40

【0134】

図15のCYC41において、リードコマンドRD1を出力する処理部251のデータタイミング制御部255は、イネーブル信号EN(RD1)を生成する。この例では、データタイミング制御部255は、最初のリードコマンドRD1の出力から18サイクル後にイネーブル信号ENを生成する。18サイクルは、最初のリードコマンドRD1の出力から出力データDOUTの出力が完了するまでの18サイクルから16個の出力データDOUTの出力に掛かる8サイクルを引き、さらに8サイクルを追加することで求められる。

50

## 【0135】

図11に示したように、メモリアクセスコントローラ20は、アクティブコマンドACT1を発行するとき、メモリ30に対する他のアクティブコマンドACT0を発行している。このため、メモリ30はアイドル状態でない。メモリ30がアイドル状態でない場合、アクティブコマンドACT1に対応する出力データDOUTの出力を、先行するアクティブコマンドACT0に対応する出力データDOUTの出力後に行わせるために、8サイクルが追加される。

## 【0136】

ここで、18サイクルは、メモリアクセスコントローラ20が受付可能なメモリアクセス要求MR EQのうち、最長パケットサイズMPSのメモリアクセス要求MR EQにおいて、最初のリードコマンドからイネーブル信号ENが出力されるまでの期間と等しい。すなわち、データタイミング制御部255は、メモリ30がアイドル状態でない場合、後続のメモリアクセス要求MR EQに対応するデータの出力開始タイミングを、最長パケットサイズMPSのメモリアクセス要求を受けたときの出力開始タイミングに設定する。例えば、この実施形態では、最長パケットサイズMPSは、32個のデータDQに対応する。

10

## 【0137】

これにより、メモリアクセス要求MR EQのパケットサイズPSによらず、最初のリードコマンドRDからデータDQの出力開始タイミングまでの期間を一定にすることができる。したがって、先行するメモリアクセス要求MR EQのパケットサイズPSに応じて出力開始タイミングを設定する場合に比べて、データタイミング制御部255によるイネーブル信号ENの出力制御を簡易にことができる。なお、データタイミング制御部255は、先行のメモリアクセス要求MR EQのパケットサイズPSに応じてイネーブル信号ENの出力タイミング（すなわち、出力開始タイミング）を設定してもよい。

20

## 【0138】

なお、アクティブコマンドACT1の発行時に他のアクティブコマンドACTが発行されておらず、メモリ30がアイドル状態の場合、データタイミング制御部255は、最初のリードコマンドRD1の出力から10サイクル後にイネーブル信号ENを生成する。10サイクルは、メモリアクセス要求MR EQ (ACT1)を発行するデバイスのアクセス仕様（例えば、パケットサイズPS = 16個のデータDQ）に応じて設定されるイネーブル信号ENの出力タイミングである。これにより、メモリアクセスコントローラ20は、メモリアクセス要求MR EQに対応するデータDOUTを最短のタイミングでメモリアクセス要求MR EQの発行元のデバイスに出力することができる。

30

## 【0139】

図15のCYC41において、選択信号生成部SELGENは、処理部251からのイネーブル信号EN (RD1)を応答イネーブル信号RETEENとして受ける。バッファBUF0からデータDQを出力中であるため、選択信号生成部SELGENは、保持部BSEL1で保持しているバッファ選択値="1"の応答イネーブル信号RETEENに応答するデータDQの出力を抑止する。

## 【0140】

すなわち、選択信号生成部SELGENは、後続のメモリアクセス要求MR EQのデータDOUTが、先行のメモリアクセス要求MR EQに対応する最終データDOUTより早く出力されないように、後続のデータDOUTの出力開始タイミングを設定する。これにより、バッファBUF0、BUF1からのデータDQの出力が衝突することを抑止することができ、メモリアクセスコントローラ20の誤動作を抑止することができる。

40

## 【0141】

バッファセレクタBSELは、図15のCYC43において、"2"の書き込み選択信号BSELの最初の受信に応答して、書き込み選択信号BSELの"2"を、空いている保持部BSELのうち、優先度が最も高い保持部BSEL1に保持する。保持部BSEL1に保持された"2"によりセレクタSEL2が選択され、ライトポインタ値WP1はバッファBUF2に供給される。そして、バッファBUF2は、順次増加するライトポインタ

50

値WP1が示すエントリに、リードコマンドRD2に対応するデータDQを図16のCYC43から順次書き込む。

【0142】

なお、ライトポインタ値WP0、WP1のいずれを使用するかは、データ出力制御部DQCNTLにより設定される。データ出力制御部DQCNTLは、メモリ30のアイドル状態が解除された後、ライトポインタ値WP0の使用を決定し、その後、空いているライトポインタ値WPの使用を順次決定する。

【0143】

CYC51において、選択信号生成部SELGENは、バッファBUF0からのデータDQ31の出力完了に合わせて、保持部BSEL0で保持しているバッファ選択値="1"を読み出し、選択信号BSEL（図16）として出力する。出力タイミング生成部OTGENは、"1"の読み出し選択信号BSELに基づいてバッファBUF1にデータシフト信号DSFTを順次出力する。これにより、メモリアクセスコントローラ20は、CYC51-CYC59に掛けて、バッファBUF1に保持されたデータDQ0-DQ15を出力データDOUTとして図3のネットワーク制御部16に順次出力する（図16、図18）。

10

【0144】

このように、メモリアクセスコントローラ20は、メモリ30がアイドル状態でない場合、アクティブコマンドACTに対応する出力データDOUTの出力を遅らせることで、メモリアクセス要求MREQの発行順に出力データDOUTを出力できる。したがって、出力データDOUTの遅れによりメモリアクセス要求MREQの発行元のデバイスによるデータ処理等が遅れることを抑制することができる。この結果、複数のパケットサイズPSのメモリアクセス要求MREQを処理可能なメモリアクセスコントローラ20の動作に依存して、出力データDOUTを受けるデバイスの処理性能が低下することを抑制することができる。

20

【0145】

なお、バッファBUF1からデータDQを出力するときに、リードコマンドRD1に対応してメモリ30から読み出されたデータDQ0-DQ15は、バッファBUF1に既に保持されている。このため、データ出力制御部DQCNTLは、ライトポインタ値WP1を減少させるカウントダウン信号CDWNを生成せず、ライトポインタ値WP1は、"15"から減少されない（図13）。

30

【0146】

選択信号生成部SELGENは、"1"の読み出し選択信号BSELの出力に応答してバッファセレクタBSELにシフト信号SFTを出力する。バッファセレクタBSELは、シフト信号SFTに応答してシフト動作し、図15のCYC52において、保持部BSEL1に保持しているバッファ選択値="2"を保持部BSEL0に移行する。これにより、バッファBUF1からの出力データDOUTを出力後、バッファBUF2から出力データDOUTを出力することが決定される。

30

【0147】

図15のCYC57において、リードコマンドRD2を出力する処理部251のデータタイミング制御部255は、バッファBUF2からのデータDQが、バッファBUF1からのデータDQの出力後に出力されるようにイネーブル信号EN（RD2）を生成する。リードコマンドRD2に対応するイネーブル信号ENは、リードコマンドRD1に対応するイネーブル信号ENと同様に、最初のリードコマンドRD2の出力から18サイクル後に生成される。

40

【0148】

バッファセレクタBSELは、図15のCYC53において、リードコマンドRD3に対応する"0"の書き込み選択信号BSELの最初の受信に応答して、書き込み選択信号BSELの"0"を保持部BSEL1に保持する。書き込み選択信号BSELの"0"が保持された保持部BSEL1は、空いている保持部BSELのうち、優先度が最も高い。

50

保持部 B S E L 1 に保持された"0"によりセレクタ S E L 0 が選択され、ライトポインタ値 W P 0 はバッファ B U F 0 に供給される。そして、バッファ B U F 0 は、順次増加するライトポインタ値 W P 0 が示すエントリに、リードコマンド R D 3 に対応するデータ D Q を C Y C 5 3 - C Y C 8 3 ( 図示せず ) に掛けてから順次書き込む。

#### 【 0 1 4 9 】

選択信号生成部 S E L G E N は、処理部 2 5 1 からのイネーブル信号 E N ( R D 2 ) を応答イネーブル信号 R E T E N として受ける。バッファ B U F 1 からデータ D Q を出力中であるため、選択信号生成部 S E L G E N は、保持部 B S E L 0 で保持しているバッファ選択値 = "2" の応答イネーブル信号 R E T E N に応答するデータ D Q の出力を抑止する。そして、選択信号生成部 S E L G E N は、バッファ B U F 1 からのデータ D Q 1 5 の出力完了に合わせて、保持部 B S E L 0 で保持しているバッファ選択値 = "2" を C Y C 5 9 で読み出し、選択信号 B R S E L として出力する ( 図 1 8 )。

10

#### 【 0 1 5 0 】

出力タイミング生成部 O T G E N は、"2" の読み出し選択信号 B R S E L に基づいてバッファ B U F 2 にデータシフト信号 D S F T を順次出力する。これにより、メモリアクセスコントローラ 2 0 は、図 1 8 の C Y C 5 9 - C Y C 6 7 に掛けて、バッファ B U F 2 に保持されたデータ D Q 0 - D Q 1 5 を出力データ D O U T として図 3 のネットワーク制御部 1 6 に順次出力する。

20

#### 【 0 1 5 1 】

なお、バッファ B U F 2 からデータ D Q を出力するときに、リードコマンド R D 2 に対応してメモリ 3 0 から読み出されたデータ D Q 0 - D Q 1 5 は、バッファ B U F 2 に既に保持されている。このため、データ出力制御部 D Q C N T L は、ライトポインタ値 W P 1 を減少させるカウントダウン信号 C D W N を生成せず、ライトポインタ値 W P 1 は、"1 5" から減少されない ( 図 1 5 )。

20

#### 【 0 1 5 2 】

バッファセレクタ B S E L は、図 1 7 の C Y C 5 9 において、リードコマンド R D 4 に対応する"1"の書き込み選択信号 B W S E L の最初の受信に応答して、書き込み選択信号 B W S E L の"1"を空いている保持部 B S E L 2 に保持する。保持部 B S E L 2 に保持された"1"によりセレクタ S E L 1 が選択され、ライトポインタ値 W P 1 はバッファ B U F 1 に供給される。そして、バッファ B U F 1 は、順次増加するライトポインタ値 W P 1 が示すエントリに、リードコマンド R D 4 に対応するデータ D Q を図 1 8 の C Y C 5 9 から順次書き込む。

30

#### 【 0 1 5 3 】

選択信号生成部 S E L G E N は、図 1 8 の C Y C 5 9 において、"2" の読み出し選択信号 B R S E L の出力に応答してバッファセレクタ B S E L にシフト信号 S F T を出力する。バッファセレクタ B S E L は、シフト信号 S F T に応答してシフト動作する。そして、バッファセレクタ B S E L は、図 1 7 の C Y C 6 0 において、保持部 B S E L 1 に保持しているバッファ選択値 = "0" を保持部 B S E L 0 に移行し、保持部 B S E L 2 に保持しているバッファ選択値 = "1" を保持部 B S E L 1 に移行する。これにより、バッファ B U F 2 から出力データ D O U T を出力後、バッファ B U F 0 から出力データ D O U T を出力することが決定される。

40

#### 【 0 1 5 4 】

図 1 7 の C Y C 6 7 において、リードコマンド R D 3 を出力する処理部 2 5 0 のデータタイミング制御部 2 5 5 は、バッファ B U F 0 からのデータ D Q が、バッファ B U F 2 からのデータ D Q の出力後に出力されるようにイネーブル信号 E N ( R D 3 ) を生成する。リードコマンド R D 3 に対応するイネーブル信号 E N は、リードコマンド R D 1 に対応するイネーブル信号 E N と同様に、最初のリードコマンド R D 3 の出力から 1 8 サイクル後に生成される。

#### 【 0 1 5 5 】

選択信号生成部 S E L G E N は、処理部 2 5 0 からのイネーブル信号 E N ( R D 3 ) を

50

応答イネーブル信号 R E T E N として受ける。選択信号生成部 S E L G E N は、バッファ B U F 2 からのデータ D Q 1 5 の出力完了に合わせて、保持部 B S E L 0 で保持しているバッファ選択値 = " 0 " を C Y C 6 7 で読み出し、選択信号 B R S E L として出力する ( 図 18 )。

#### 【 0 1 5 6 】

出力タイミング生成部 O T G E N は、" 0 " の読み出し選択信号 B R S E L に基づいてバッファ B U F 0 にデータシフト信号 D S F T を順次出力する。これにより、メモリアクセスコントローラ 2 0 は、C Y C 6 7 - C Y C 8 3 ( 図示せず ) に掛けて、バッファ B U F 0 に保持されたデータ D Q 0 - D Q 3 1 を出力データ D O U T として図 3 のネットワーク制御部 1 6 に順次出力する。

10

#### 【 0 1 5 7 】

図 17 の C Y C 7 3 において、リードコマンド R D 4 を出力する処理部 2 5 1 のデータタイミング制御部 2 5 5 は、バッファ B U F 2 からのデータ D Q が、バッファ B U F 0 からのデータ D Q の出力後に出力されるようにイネーブル信号 E N ( R D 4 ) を生成する。イネーブル信号 E N は、リードコマンド R D 1 に対応するイネーブル信号 E N と同様に、最初のリードコマンド R D 4 の出力から 1 8 サイクル後に生成される。

#### 【 0 1 5 8 】

選択信号生成部 S E L G E N は、処理部 2 5 1 からのイネーブル信号 E N を応答イネーブル信号 R E T E N として受ける。バッファ B U F 0 からデータ D Q を出力中であるため、選択信号生成部 S E L G E N は、保持部 B S E L 0 で保持しているバッファ選択値 = " 1 " の応答イネーブル信号 R E T E N に応答するデータ D Q の出力を抑止する。

20

#### 【 0 1 5 9 】

その後、選択信号生成部 S E L G E N は、バッファ B U F 0 からのデータ D Q 3 1 の出力完了に合わせて、保持部 B S E L 0 で保持しているバッファ選択値 = " 1 " を読み出し、選択信号 B R S E L として出力する。そして、図示は省略するが、メモリアクセスコントローラ 2 0 は、バッファ B U F 1 に保持されたデータ D Q 0 - D Q 3 1 を出力データ D O U T として図 3 のネットワーク制御部 1 6 に順次出力する

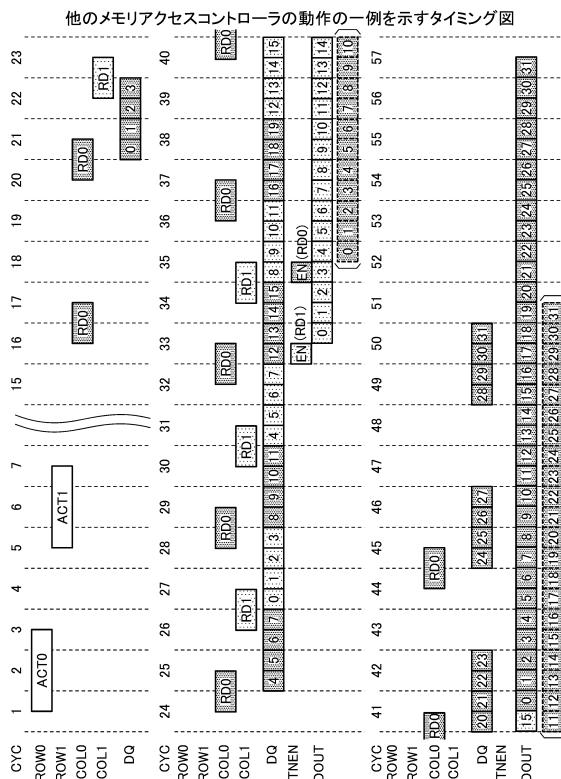

図 19 は、他のメモリアクセスコントローラの動作の一例を示す。図 10 - 図 18 と同様の動作については、詳細な説明は省略する。メモリアクセスコントローラからメモリに出力されるアクティブコマンド A C T 0 、 A C T 1 およびリードコマンド R D 0 、 R D 1 のタイミングは、図 10 、図 11 、図 13 および図 15 と同じである。なお、図 19 では、リードコマンド R D 3 、 R D 4 は、発行されない。

30

#### 【 0 1 6 0 】

図 19 の動作を実行するメモリアクセスコントローラは、アクティブコマンド A C T の発行時に他のアクティブコマンド A C T が発行されているか否かを判定する機能を持たない。換言すれば、図 19 の動作を実行するメモリアクセスコントローラは、メモリがアイドル状態でない場合に、バッファ B U F からの出力データ D O U T の出力を遅らせる機能を持たない。

#### 【 0 1 6 1 】

このため、メモリアクセスコントローラは、最初のリードコマンド R D 1 の出力から 1 0 サイクル後である C Y C 3 3 にイネーブル信号 E N ( R D 1 ) を生成する。メモリアクセスコントローラは、バッファ B U F から他の出力データ D O U T が出力されていないため、リードコマンド R D 1 に対応してバッファ B U F に保持されるデータ D Q 0 - D Q 1 5 を出力データ D O U T として C Y C 3 3 - C Y C 4 1 に掛けて出力する。

40

#### 【 0 1 6 2 】

メモリアクセスコントローラは、最初のリードコマンド R D 0 の出力から 1 8 サイクル後である C Y C 3 5 にイネーブル信号 E N ( R D 0 ) を生成する。C Y C 3 5 では、リードコマンド R D 1 に対応する出力データ D O U T がバッファ B U F から出力されている。このため、メモリアクセスコントローラは、リードコマンド R D 1 に対応する出力データ D O U T がバッファ B U F から出力された後、C Y C 4 1 - C Y C 5 7 に掛けて、リード

50

コマンド R D 0 に対応する出力データ D O U T 出力する。

【 0 1 6 3 】

図 1 9 においてかぎ括弧で囲った破線の出力データ D O U T は、バッファ B U F から他の出力データ D O U T が output されていない場合のイネーブル信号 E N ( R D 0 ) に応答する出力タイミングを示す。メモリアクセスコントローラは、メモリから読み出したデータ D Q を、コマンドを受けた順に出力することが好ましい。

【 0 1 6 4 】

しかしながら、図 1 9 に示すように、パケットサイズ P S が異なるメモリアクセス要求 M R E Q を処理可能なメモリアクセスコントローラは、メモリアクセス要求 M R E Q の受付順により出力データ D O U T のネットワーク制御部への出力順が逆になる場合がある。例えば、パケットサイズ P S の大きいメモリアクセス要求 M R E Q の後にパケットサイズ P S の小さいメモリアクセス要求 M R E Q が発行される場合、出力データ D O U T の出力順が逆になるおそれがある。

10

【 0 1 6 5 】

出力データ D O U T の出力順が逆になる場合、メモリアクセス要求 M R E Q の発行元のデバイスによるメモリからの読み出しデータを使用したデータ処理等が遅れるおそれがあり、デバイスの処理性能が低下するおそれがある。また、メモリアクセス要求 M R E Q の発行元のシステムが、メモリからの読み出しデータの受信の完了時刻を予測し、予測した完了時刻に基づいて投機的に動作する場合、投機的な動作が無駄になるおそれがある。

20

【 0 1 6 6 】

以上、この実施形態においても上述した実施形態と同様の効果を得ることができる。例えば、メモリアクセスコントローラ 2 0 は、C P U 1 0 の内部または外部から受けるパケットサイズ P S が異なるメモリアクセス要求 M R E Q に基づいてメモリ 3 0 から読み出されるデータ D Q を、メモリアクセス要求 M R E Q の受付順に出力できる。

【 0 1 6 7 】

バッファ制御部 2 7 0 は、後続のリードコマンド R D 1 に対応するデータ D Q の出力が、先行のリードコマンド R D 0 に対応するデータ D Q の出力と重複する場合、イネーブル信号 E N ( R D 1 ) に基づくデータ D Q の出力の開始を遅らせる。これにより、複数のバッファ B U F からのデータ D Q の衝突を抑止することができ、誤ったデータ D Q ( D O U T ) がメモリアクセスコントローラ 2 0 から出力されることを抑止することができる。

30

【 0 1 6 8 】

さらに、この実施形態では、以下に示す効果を得ることができる。例えば、データタイミング制御部 2 5 5 は、メモリ 3 0 がアイドル状態でない場合、後続のメモリアクセス要求 M R E Q に対応するデータの出力開始タイミングを、最長パケットサイズ M P S のメモリアクセス要求を受けたときの出力開始タイミングに設定する。これにより、メモリアクセス要求 M R E Q のパケットサイズ P S によらず、最初のリードコマンド R D からデータ D Q の出力開始タイミングまでの期間を一定にすることができます。したがって、先行するメモリアクセス要求 M R E Q のパケットサイズ P S に応じて出力開始タイミングを設定する場合に比べて、データタイミング制御部 2 5 5 によるイネーブル信号 E N の出力制御を簡易にすることができます。

40

【 0 1 6 9 】

選択信号生成部 S E L G E N は、後続のメモリアクセス要求 M R E Q のデータ D O U T が、先行のメモリアクセス要求 M R E Q に対応する最終データ D O U T より早く出力されないように、後続のデータ D O U T の出力開始タイミングを設定する。これにより、バッファ B U F 0 、 B U F 1 からのデータ D Q の出力が衝突することを抑止することができ、メモリアクセスコントローラ 2 0 の誤動作を抑止することができる。

【 0 1 7 0 】

メモリ 3 0 がアイドル状態の場合、データタイミング制御部 2 5 5 は、メモリアクセス要求 M R E Q を発行するデバイスのアクセス仕様（例えば、パケットサイズ P S ）に応じてイネーブル信号 E N の出力タイミングを設定する。これにより、メモリアクセスコント

50

ローラ20は、メモリアクセス要求MREQに対応するデータDOUTを最短のタイミングでメモリアクセス要求MREQの発行元のデバイスに出力することができる。

【0171】

シフトレジスタの構造を有するバッファBUFに対して、データ出力制御部DQCTLは、バッファBUFからデータDQを出力させるとときにカウンタCONTをカウントダウンさせる。これにより、バッファBUFのシフト動作により新たなデータDQの格納位置がずれる場合にも、正しい位置にデータDQを格納することができる。

【0172】

また、データ出力制御部DQCTLは、バッファBUFへのデータDQの格納とバッファBUFからデータDQの出力とを同時に使うときにカウンタCONTのカウントアップおよびカウントダウンを停止する。これにより、バッファBUFのシフト動作にかかわりなく、バッファBUFの同じ位置に新たなデータDQを格納することができる。

10

【0173】

カウンタCONT0、CONT1とバッファBUF0-BUF2との間にセレクタSEL0-SEL2を配置することで、任意のカウンタCONTが生成するライトポインタ値WPを任意のバッファBUFに供給することができる。この結果、カウンタCONTの数をバッファBUFの数より少なくすることができ、バッファBUFの数と同じ数のカウンタCONTを設ける場合に比べて、メモリアクセスコントローラ20の回路規模を削減することができる。

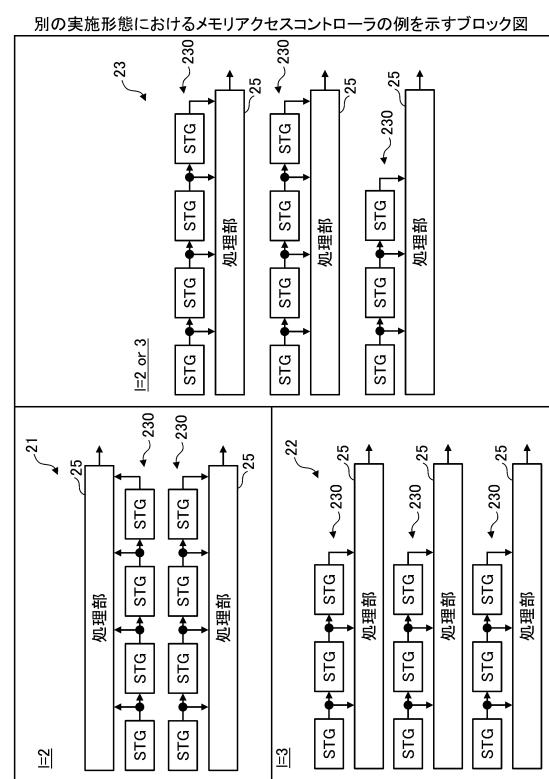

【0174】

図20は、別の実施形態におけるメモリアクセスコントローラの例を示す。メモリアクセスコントローラ21は、2つの処理部25と、各処理部25に対応するリクエスト保持パイプライン230を有し、並列度1は"2"である。メモリアクセスコントローラ22は、3つの処理部25と、各処理部25に対応するリクエスト保持パイプライン230を有し、並列度1は"3"である。

20

【0175】

メモリアクセスコントローラ23は、3つの処理部25と、各処理部25に対応するリクエスト保持パイプライン230を有し、"2"または"3"の両方の並列度1に対応する。メモリアクセスコントローラ23は、並列度1が"2"の場合、4つのステージSTGに接続された2つの処理部25を使用し、並列度1が"3"の場合、3つの処理部25を使用する。各処理部25の構成は、接続されるステージSTGの数が少ないことを除き、図8に示す処理部25と同様の構成である。

30

【0176】

各メモリアクセスコントローラ21、22、23は、各処理部25に接続されるバッファ制御部270およびデータバッファ280を有する。バッファ制御部270およびデータバッファ280の構成は、図9と同様である。これにより、各メモリアクセスコントローラ21、22、23は、上述した実施形態と同様の効果を得ることができる。例えば、各メモリアクセスコントローラ21、22、23は、パケットサイズPSが異なるメモリアクセス要求MREQに基づいてメモリ30から読み出されるデータDQを、メモリアクセス要求MREQの受付順に出力できる。

40

【0177】

以上の詳細な説明により、実施形態の特徴点および利点は明らかになるであろう。これは、特許請求の範囲がその精神および権利範囲を逸脱しない範囲で前述のような実施形態の特徴点および利点にまで及ぶことを意図するものである。また、当該技術分野において通常の知識を有する者であれば、あらゆる改良および変更に容易に想到できるはずである。したがって、発明性を有する実施形態の範囲を前述したものに限定する意図はなく、実施形態に開示された範囲に含まれる適当な改良物および均等物に拡ることも可能である。

【符号の説明】

【0178】

|                                     |    |  |

|-------------------------------------|----|--|

| 2 メモリアクセスコントローラ                     |    |  |

| 3 アクセス制御部                           |    |  |

| 4 バッファ制御部                           |    |  |

| 5 ( 5 a、 5 b ) バッファ                 |    |  |

| 6 メモリ                               |    |  |

| 1 0 演算処理装置                          |    |  |

| 1 2 コア                              |    |  |

| 1 4 キャッシュ                           |    |  |

| 1 6 ネットワーク制御部                       |    |  |

| 1 8 インタコネクト                         | 10 |  |

| 2 0 、 2 1 、 2 2 、 2 3 メモリアクセスコントローラ |    |  |

| 2 5 ( 2 5 0 、 2 5 1 、 2 5 2 ) 処理部   |    |  |

| 3 0 メモリ                             |    |  |

| 2 1 0 リクエスト受信部                      |    |  |

| 2 2 0 スケジューリング部                     |    |  |

| 2 2 1 リクエスト情報出力部                    |    |  |

| 2 2 2 資源番号出力部                       |    |  |

| 2 2 3 クロックカウンタ                      |    |  |

| 2 2 4 シフト信号生成部                      |    |  |

| 2 3 0 リクエスト保持パイプライン                 | 20 |  |

| 2 3 1 資源番号保持部                       |    |  |

| 2 3 2 経過サイクル保持部                     |    |  |

| 2 3 3 リクエスト情報保持部                    |    |  |

| 2 3 4 シフト信号生成部                      |    |  |

| 2 4 0 設定レジスタ                        |    |  |

| 2 5 3 ロウ制御部                         |    |  |

| 2 5 4 カラム制御部                        |    |  |

| 2 5 5 データタイミング制御部                   |    |  |

| 2 6 0 セレクタ                          |    |  |

| 2 7 0 バッファ制御部                       | 30 |  |

| 2 8 0 データバッファ                       |    |  |

| 2 5 3 1 セレクタ                        |    |  |

| 2 5 3 2 ロウ情報出力部                     |    |  |

| 2 5 4 1 セレクタ                        |    |  |

| 2 5 4 2 カラム情報出力部                    |    |  |

| 2 5 4 3 カウンタ                        |    |  |

| A C T アクティブコマンド                     |    |  |

| B G ( B G 0 - B G 3 ) バンクグループ       |    |  |

| B S E L バッファセレクタ                    |    |  |

| B S E L 0 - B S E L 2 保持部           | 40 |  |

| B U F 0 - B U F 2 バッファ              |    |  |

| B W S E L 書き込み選択信号                  |    |  |

| B R S E L 読み出し選択信号                  |    |  |

| C N T カウンタ値                         |    |  |

| C D W N カウントダウン信号                   |    |  |

| C O L ( C O L 0 、 C O L 1 ) カラム制御信号 |    |  |

| C O N T 0 、 C O N T 1 カウンタ          |    |  |

| C U P カウントアップ信号                     |    |  |

| C Y C サイクル                          |    |  |

| D O U T 出力データ                       | 50 |  |

|                                              |    |

|----------------------------------------------|----|

| D Q データ                                      |    |

| D Q C N T L データ出力制御部                         |    |

| D Q I N データ入力タイミング信号                         |    |

| D S F T 、 D S F T a 、 D S F T b データシフト信号     |    |

| E N イネーブル信号                                  |    |

| F F フリップフロップ                                 |    |

| I N C インクリメンタ                                |    |

| l 並列度                                        |    |

| m 位相差                                        |    |

| M C L K メモリクロック                              | 10 |

| M P S 最長パケットサイズ                              |    |

| M R E Q メモリアクセス要求                            |    |

| n 平均リクエスト間隔                                  |    |

| O T G E N 出力タイミング生成部                         |    |

| P S パケットサイズ                                  |    |

| R D ( R D 0 - R D 4 ) リードコマンド                |    |

| R E Q A L N 単独要求情報                           |    |

| R E Q I N F リクエスト情報                          |    |

| R E T E N 応答イネーブル信号                          |    |

| R L リードレイテンシ                                 | 20 |

| R O W ( R O W 0 、 R O W 1 ) ロウ制御信号           |    |

| R S C 資源番号                                   |    |

| S E L 、 S E L 0 - S E L 2 セレクタ               |    |

| S E L G E N 選択信号生成部                          |    |

| S F T I N シフト入力信号                            |    |

| S T G ( S T G 0 - S T G 1 0 ) ステージ           |    |

| T 経過時刻                                       |    |

| T C O L カラムタイミング                             |    |

| T R O W ロウタイミング                              |    |

| W P 、 W P 0 、 W P 1 、 W P a 、 W P b ライトポインタ値 | 30 |

## 【 図面 】

【 図 1 】

## 一実施形態におけるメモリアクセスコントローラを含む 演算処理装置の一例を示すブロック図

## 【図2】

図1のメモリアクセスコントローラの動作の一例を示すタイミング図

【図3】

## 別の実施形態におけるメモリアクセスコントローラを含む 演算処理装置の一例を示すブロック図

〔 四 4 〕

図3のメモリアクセスコントローラの一例を示すブロック図

【図5】

【 図 6 】

図4のスケジューリング部の一例を示すブロック図

図5のスケジューリング部の動作の一例を示すタイミング図

【 図 7 】

【 図 8 】

図4のリクエスト保持パイプラインのステージの一例を示すブロック図

図4の処理部の一例を示すブロック図

【図 9】

【図 10】

図4のメモリアクセスコントローラにより

メモリにリードアクセスする一例を示すタイミング図

10

20

【図 11】

【図 12】

図11と同じ期間でのメモリアクセスコントローラの動作の一例を示すタイミング図

30

40

50

【図 1 3】

【図 1 4】

10

20

30

40

【図 1 5】

【図 1 6】

50

【図 17】

【図 18】

10

20

【図 19】

【図 20】

30

40

50

---

フロントページの続き

(56)参考文献      特表2005-525652(JP,A)

特表2015-500541(JP,A)

(58)調査した分野 (Int.Cl., DB名)

G 06 F 12 / 00

G 06 F 12 / 06