OFFICE FÉDÉRAL DE LA PROPRIÉTÉ INTELLECTUELLE

H 03 L

Demande de brevet déposée pour la Suisse et le Liechtenstein

Traité sur les brevets, du 22 décembre 1978, entre la Suisse et le Liechtenstein

## **® FASCICULE DE LA DEMANDE A3**

(11)

643 106 G

(21) Numéro de la demande: 8742/80

(71) Requérant(s):

Société Suisse pour l'Industrie Horlogère Management Services S.A., Biel/Bienne

(22) Date de dépôt:

26.11.1980

(42) Demande publiée le:

30.05.1984

(72) Inventeur(s):

Mario Dellea, Les Geneveys-sur-Coffrane

(44) Fascicule de la demande

publié le:

30.05.1984

(56) Rapport de recherche au verso

## (54) Garde-temps comprenant une chaîne de diviseurs au rapport de division ajustable.

(57) Le garde-temps comprend un oscillateur basse-fréquence (1) comme base de temps alimentant une première chaîne de diviseurs de fréquence (3) à rapport de division ajustable pour afficher le temps et un oscillateur haute-fréquence (5) alimentant une seconde chaîne de diviseurs de fréquence (7).

Pendant une période prédéterminée réputée inexacte fournie par la première chaîne (3), on compte un nombre d'impulsions de référence délivrées par la seconde chaîne (7) de façon à produire une valeur binaire (BF - HF) qui représente l'écart de marche de la première chaîne par rapport à la référence. Cette valeur est transférée dans une mémoire (9) pour corriger soit directement soit indirectement le rapport de division du premier diviseur (3).

L'invention propose un oscillateur qui présente tous les avantages de stabilité d'un oscillateur haute-fréquence mais avec une consommation qui excède peu celle d'un oscillateur basse-fréquence.

Bundesamt für geistiges Eigentum Office fédéral de la propriété intellectuelle Ufficio federale della proprietà intellectuale

## RAPPORT DE RECHERCHE RECHERCHENBERICHT

Demande de prevet No.: Patentgesuch Nr.

CH 8742/80

HC 14 274

| 1   | EINSCHLÄGIGE DOKUMENTE                                                                                                                                                                                           | cernées<br>Betrifft Anspruch<br>Nr. |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

|     | Citation du document avec indication, en cas de besoin, des parties pertinentes<br>Kennzeichnung des Dokuments, mit Angabe, soweit erforderlich, der massgeblichen Teile                                         |                                     |

|     | <u>US - A - 4 264 967</u> (FUJITA et al.)                                                                                                                                                                        | 1,3,5                               |

|     | * revendication 1; figures *<br>& JP - A - 55 057 181 (26-04-1980)                                                                                                                                               |                                     |

|     | <u>US - A - 4 115 687</u> (BOESE et al.)                                                                                                                                                                         | 1,2,4                               |

|     | * colonne 4, ligne 49 - colonne 5, ligne 63; figures *                                                                                                                                                           |                                     |

|     | JAHRBUCH DER DEUTSCHEN GESELLSCHAFT FUER CHRONOMETRIE, vol. 28, 1977 STUTTGART (DE) H. EFFENBURGER: "Digitale Temperaturkompensation von Schwingquarzoszillatoren mit automatischem Frequenzabgleich" pages 9-15 | 1,3                                 |

|     | * en entier *                                                                                                                                                                                                    |                                     |

|     | <u>US - A - 3 364 439</u> (COHEN et al.)                                                                                                                                                                         | 1-5                                 |

|     | * colonne 1, ligne 59 - colonne 2, ligne 5; colonne 2, ligne 58 - colonne 7, ligne 17; figures 1a, 1b *                                                                                                          |                                     |

| A   | <u>FR - A - 2 197 265</u> (DYNACORE)                                                                                                                                                                             | 1                                   |

|     | * en entier *<br>& CH - A - 12 570/72                                                                                                                                                                            |                                     |

| D/A | EP - A - O 015 873 (STE. SUISSE POUR L'INDUSTRIE HORLOGERE)                                                                                                                                                      | 1                                   |

|     | * en entier *<br>& CH - A - 620 087                                                                                                                                                                              |                                     |

| D/A | <u>CH - A - 534 913</u> (CENTRE ELECTRONIQUE HORLOGER)  * en entier *                                                                                                                                            | 1                                   |

| D/A | CH - A - 570 651 (CENTRE ELECTRONIQUE HORLOGER)                                                                                                                                                                  | 1                                   |

|     | * en entier *                                                                                                                                                                                                    |                                     |

| D/A | CH - A - 554 O15 (CENTRE ELECTRONIQUE HORLOGER)                                                                                                                                                                  |                                     |

|     | * en entier *                                                                                                                                                                                                    |                                     |

|     |                                                                                                                                                                                                                  |                                     |

|     | techniques recherchés erte Sachgebiete G 04 G 3/02 7/00 H 03 L 7/00                                                                                                                                              |                                     |

## REVENDICATIONS

- 1. Garde-temps comprenant un oscillateur basse-fréquence (1) comme base de temps alimentant une première chaîne (3) de diviseurs de fréquence à rapport de division ajustable pour afficher le temps et un oscillateur haute-fréquence (5) alimentant une seconde chaîne (7) de diviseurs de fréquence, caractérisé par le fait qu'il comprend des moyens d'asservissement aptes à être mis prériodiquement en fonction pour compter sous forme binaire, pendant une période prédéterminée (BL) fournie par la première chaîne de diviseurs, un nombre d'impulsions de référence délivrées par la seconde chaîne de diviseurs pour produire une valeur binaire (BF-HF) représentant l'écart de marche de la première chaîne par rapport à une référence, ladite valeur étant transférée dans une première mémoire (9) pour corriger, lors de la mar- 15 che normale du garde-temps, le rapport de division de ladite première chaîne de diviseurs.

- 2. Garde-temps selon la revendication 1, caractérisé par le fait que la première chaîne de diviseurs comporte un circuit d'inhibition (2) sur lequel agit ladite valeur binaire (BF-HF) pour ajuster son rapport de division.

- 3. Garde-temps selon la revendication 1, caractérisé par le fait que ladite valeur binaire (BF-HF) est comparée à une valeur étalon (HF-Nom.) contenue dans une seconde mémoire (17), le résultat de la comparaison (BF-Nom.) agissant sur la première chaîne (3) de diviseurs pour corriger son rapport de division.

- 4. Garde-temps selon la revendication 3, caractérisé par le fait que ladite comparaison est effectuée dans un circuit soustracteur (16).

- 5. Garde-temps selon la revendication 3, caractérisé par le fait que l'oscillateur haute-fréquence (5) produit un signal

- réel ajusté grossièrement autour d'une fréquence nominale et que la valeur étalon (HF-Nom.) contenue dans la seconde mémoire comporte la valeur binaire de l'écart entre la valeur réelle produite par la seconde chaîne de diviseurs et la valeur nominale que produirait ladite seconde chaîne de diviseurs si elle était alimentée par un signal de fréquence nominale.

- 6. Garde-temps selon la revendication 1, caractérisé par le fait que les moyens d'asservissement comprennent un circuit logique de commande (10) dont les entrées (11 à 15) sont connectées à certaines sorties (fa, fm, fos, fRo, ft) de la première chaîne de diviseurs, choisies pour assurer, dans un ordre établi, la mise en marche ou l'arrêt de l'oscillateur haute-fréquence, le blocage ou le déblocage de la seconde chaîne de diviseurs, la remise à zéro de ladite seconde chaîne et le transfert de ladite valeur binaire dans la première mémoire.

- 7. Garde-temps selon la revendication 6, caractérisé par le fait que les moyens d'asservissement sont arrangés pour parcourir un cycle s'étendant du temps to au temps to dans lequel, au temps t<sub>0</sub>, correspondant à l'état zéro de tous les diviseurs composant la première chaîne (3), l'oscillateur haute-fréquence est mis en marche (OS), au temps t<sub>1</sub> la seconde chaîne (7) de diviseurs est mise en fonction (BL) pour compter les impulsions de référence délivrées par l'oscillateur hau-25 te-fréquence (5) pendant une durée prédéterminée t<sub>2</sub>-t<sub>1</sub> fournie par la première chaîne de diviseurs, au temps t<sub>2</sub> la seconde chaîne de diviseurs est bloquée (BL) en même temps qu'est arrêté (OS) l'oscillateur haute-fréquence (5), au temps t<sub>3</sub> le contenu de la seconde chaîne (7) de diviseurs est transféré (Tt) dans la première mémoire (9) pendant une durée  $t_4-t_3$ , au temps  $t_5$  la seconde chaîne (7) de diviseurs est mise à zéro (Rc) et au temps t<sub>6</sub> le même cycle recommence.

L'invention a pour objet un garde-temps comprenant un oscillateur basse-fréquence comme base de temps alimentant une première chaîne de diviseurs de fréquence à rapport de division ajustable pour afficher le temps et un oscillateur haute-fréquence alimentant une seconde chaîne de diviseurs de fréquence.

Un tel arrangement est connu de la publication EP 0 015 873. Dans cette publication, il est revendiqué un oscillateur à quartz haute-fréquence qui, dans le but d'abaisser la consommation de courant, comprend un circuit équipé d'un oscillateur à quartz basse-fréquence, des moyens pour produire un signal de correction qui sert à commander un diviseur de fréquence programmable et un interrupteur électronique pour interrompre périodiquement l'oscillateur à quartz haute-fréquence.

On sait en effet qu'un oscillateur à quartz haute-fréquence de 1 MHz ou plus présente une stabilité en température et au vieillissement qui est plus favorable que celle d'un oscillateur à quartz basse-fréquence conventionnel à 32 kHz. Par contre, cet oscillateur à quartz haute-fréquence avec le diviseur de fréquence qui lui est lié présente une consommation de courant substantiellement plus élevée, ce qui exige de fréquents remplacements de la batterie. Ainsi, l'invention citée ci-dessus propose un oscillateur qui présente tous les avantages d'un oscillateur à haute-fréquence mais dont la consommation n'excède pas celle montrée par un oscillateur à basse-fréquence. Pour y parvenir, la publication citée fait appel à un interrupteur électronique qui enclenche périodiquement (toutes les 15 minutes) pendant un temps relative-

40 ment court (16 secondes) l'oscillateur HF. Les signaux émis par les oscillateurs HF et BF alimentent l'un et l'autre des diviseurs de fréquence secondaires qui produisent chacun à leur sortie un signal dont la période vaut environ 16 secondes. Ces deux signaux alimentent un générateur à battement dont la résultante de sortie correspond à l'écart existant entre la période BF à régler et la période HF de référence. Cet écart est alors utilisé pour corriger le rapport de division du diviseur de fréquence principal. Ainsi, dans ce système, toutes les 15 minutes on remet en cause le rapport de division du diviseur principal et, dans le cas où la fréquence de l'oscillateur basse-fréquence a varié, on corrige ledit rapport de division par un signal issu d'un circuit d'apprentissage constitué par un générateur de battement.

Le système dont on vient de rappeler le fonctionnement présente plusieurs inconvénients. Celui d'abord de nécessiter plusieurs diviseurs de fréquence secondaires, ce qui complique la construction. Celui ensuite de transformer les signaux issus des oscillateurs HF et BF pour produire un battement, au lieu de les utiliser directement tels qu'ils existent sous forme binaire, ce qui diminue la précision. Celui enfin de ne pas prendre en considération que, pour des raisons de prix de revient, le quartz HF peut être ajusté grossièrement autour d'une fréquence nominale, cas dans lequel des moyens doivent être mis en œuvre pour mémoriser l'écart existant.

On a cité dans le rapport de recherche le document US 4 264 967 dans lequel on vise au même but que la présente invention par des moyens analogues, à savoir la production, dans un garde-temps, d'un signal à basse-fréquence périodi-

30

quement corrigé par comparaison avec un signal à haute-fréquence et action sur le diviseur du signal à basse-fréquence, et cela sans consommation exagérée d'énergie. Pour ce faire, il est fait appel, dans le brevet cité, à un comparateur de phase dont le signal de sortie est utilisé pour modifier la fréquence du signal à basse-fréquence dans un circuit particulier de telle façon que le signal issu dudit circuit particulier mesuré pendant un certain intervalle de temps, se présente comme un sous-multiple entier du signal à haute-fréquence. Ce signal est alors utilisé comme signal de base de temps standard. La démarche de la présente invention est différence en ce sens que pendant une période prédéterminée (BL) établie par la chaîne de diviseurs à basse-fréquence (3) on compte sous forme binaire un nombre d'impulsions de référence délivrée par la chaîne de diviseurs à haute-fréquence (7) de manière à déterminer une valeur binaire BF-HF représentative de la variation de marche de la chaîne de diviseurs à basse-fréquence par rapport à la référence. Ainsi, dans la présente invention et comme cela sera expliqué en détail plus loin, il suffit de mesurer l'état de chaque étage de la chaîne de diviseurs haute-fréquence (après la période de mesure BL) pour obtenir directement la variation de marche d'un oscillateur par rapport à l'autre. Ainsi, le système que propose la présente invention est plus direct et partant plus simple que celle décrite dans le brevet cité.

Aussi, la présente invention propose-t-elle de régler la marche du garde-temps comprenant un diviseur de fréquence au rapport de division ajustable par des moyens de réglage qui apparaissent dans les revendications.

L'invention sera mieux comprise à la lumière de la description qui suit et des dessins qui représentent à titre d'exemple un mode de réalisation permettant le réglage de la marche du garde-temps.

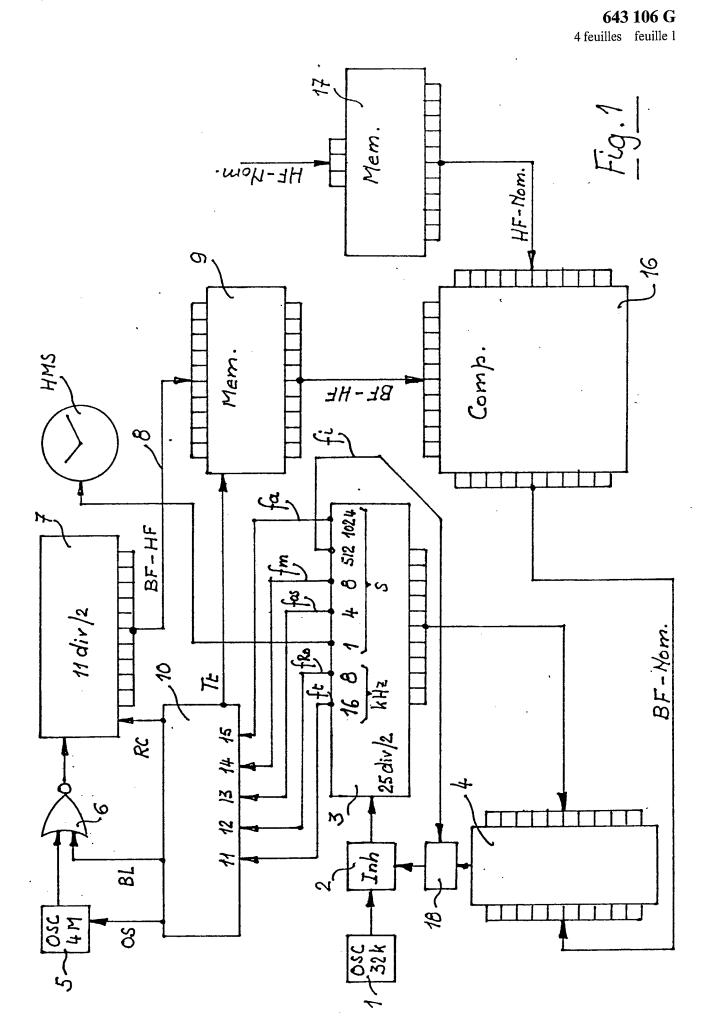

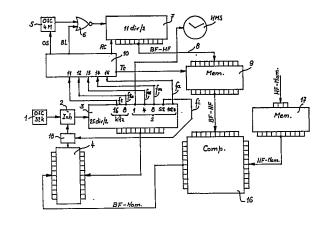

La fig. 1 est un schéma de principe du système de réglage du garde-temps selon l'invention.

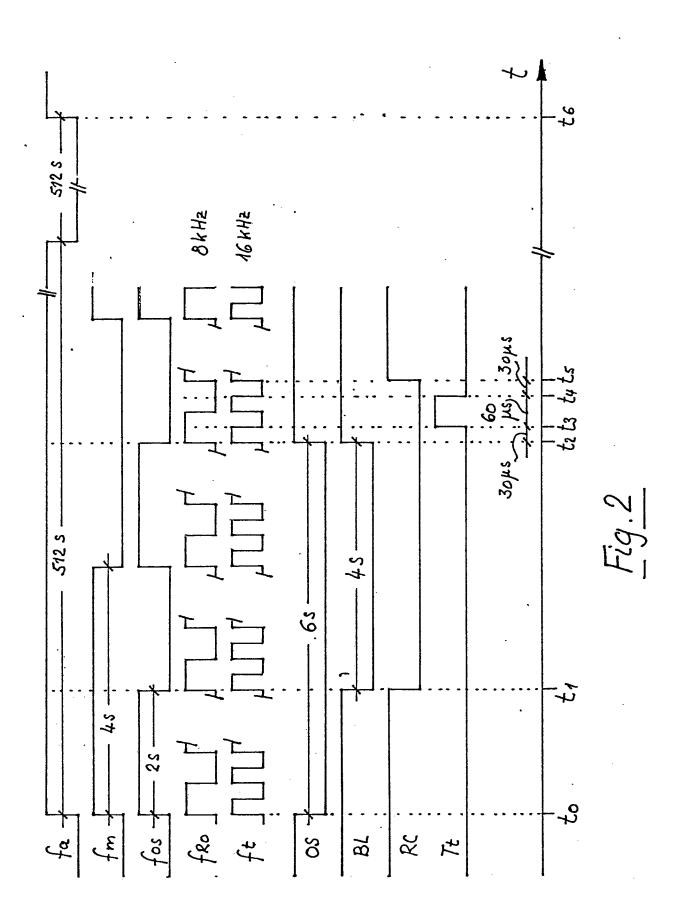

La fig. 2 est un diagramme explicatif du fonctionnement du circuit logique de commande d'asservissement qui apparaît en fig. 1.

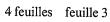

La fig. 3 est un schéma détaillé de la logique de commande d'asservissement telle qu'elle apparaît au bloc 10 de la fig. 1.

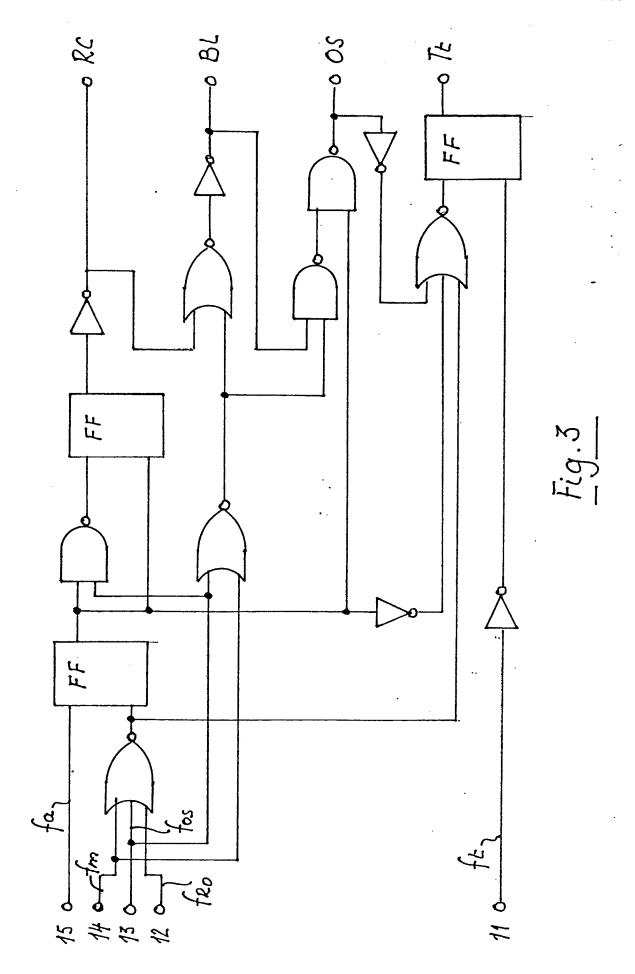

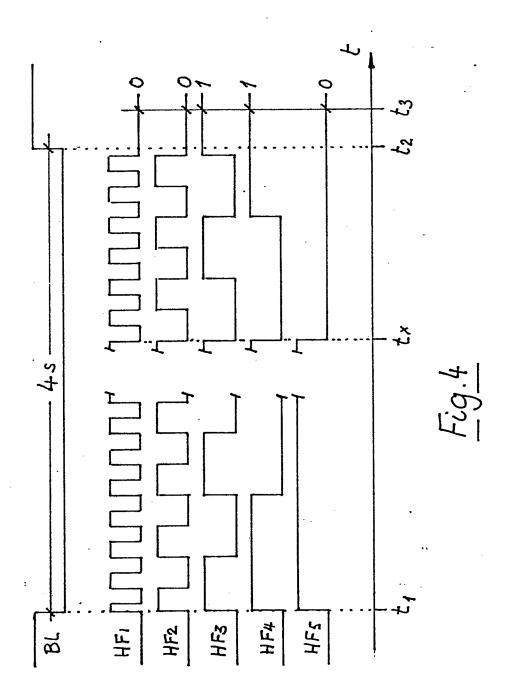

La fig. 4 est un diagramme montrant le comportement de la chaîne de diviseurs HF pendant une période de réglage

jet de l'invention. Il comprend un oscillateur basse-fréquence, généralement à cristal de quartz 1, qui attaque par l'intermédiaire d'un circuit d'inhibition 2 une chaîne de diviseurs de fréquence 3. Circuit d'inhibition et chaîne de diviseurs forment ensemble un système à rapport ajustable. Dans les garde-temps connus et si la fréquence de l'oscillateur BF est de l'ordre de 33 kHz, il faudra quinze diviseurs par deux pour obtenir à la sortie de commande de l'affichage (1 s) une fréquence de 1 Hz pour afficher le temps (HMS). Ici la chaîne 3 est prolongée de dix diviseurs supplémentaires pour fournir les sorties supplémentaires à 4,8 et 1024 secondes. Ainsi dans l'exemple donné, la chaîne 3 totalise vingt-cinq diviseurs binaires. A l'entrée de la chaîne 3, le circuit d'inhibition 2 est commandé par les blocs 4 et 18 qui permettent de supprimer une certaine proportion des impulsions fournies par la base de temps et d'abaisser ainsi la fréquence de commande du moteur actionnant l'affichage jusqu'à la valeur désirée.

Cette technique est connue; elle a été suffisamment expliquée par exemple dans les exposés d'inventions CH 534 913, 554 015 et 570 651 pour qu'il ne soit pas nécessaire d'y revenir ici. On rappellera cependant que l'ajustement par rétroaction sur un circuit d'inhibition ou sur le diviseur de fréquence ne nécessite plus l'ajustement mécanique de la base de temps et la stabilité de l'ensemble n'est plus affectée puisqu'on peut se passer d'un trimmer de réglage.

La fig. 1 montre encore que l'arrangement comprend, s outre l'oscillateur BF, un second oscillateur à haute-fréquence 5, généralement à cristal de quartz, qui, à travers une porte NOR 6, alimente une seconde chaîne de diviseurs de fréquence 7. Dans l'exemple, cette seconde chaîne comprend onze diviseurs par deux et l'oscillateur HF est équipé d'un quartz à 4 MHz. La figure montre également que l'oscillateur HF est susceptible d'être enclenché ou déclenché périodiquement par la ligne OS, que la porte NOR 6 reçoit sur sa seconde entrée un signal BL susceptible de bloquer ou de débloquer la chaîne 7 et que ladite chaîne peut être remise à 15 zéro par l'intermédiaire de la ligne RC. Le mot binaire que l'on trouve à la sortie de la chaîne 7 se compose, dans l'exemple choisi, de onze bits qui peuvent être transférés par la ligne 8 dans une première mémoire 9 lorsqu'un ordre de transfert Tt est donné à ladite mémoire 9.

Les signaux OS, BL, RC et Tt sont issus d'un circuit logique de commande d'asservissement 10 lui-même commandé par des signaux 11 à 15 issus de la chaîne de division 3. Comme cela apparaîtra par la suite, le contenu binaire de la mémoire 9 est exploité, lors de la marche normale du garde-25 temps, pour ajuster le rapport de division de la chaîne de diviseurs 3, soit directement, soit indirectement par l'intermédiaire d'un circuit de comparaison 16 qui compare le contenu de la première mémoire 9 avec le contenu d'une seconde mémoire 17.

Dans le but d'améliorer la précision du garde-temps, sans augmenter sa consommation, on propose selon l'invention un système où la fréquence pilotée par un quartz BF est périodiquement asservie à une fréquence pilotée par un quartz HF plus stable en température. Des moyens sont mis en 35 œuvre pour qu'en dehors des périodes d'asservissement les circuits HF soient déclenchés.

Dans le brevet CH 570 651, déjà cité ci-dessus, on compte les impulsions de la fréquence à corriger pendant une période étalon extérieure à la montre. Comme ici, on désire que 40 ce signal étalon soit intérieur à la montre, on pourrait envisager de remplacer l'étalon externe par un étalon interne fourni par un quartz HF. Cependant, comme la précision de réglage est proportionnelle au nombre d'impulsions comptées durant la période étalon, cette dernière serait longue La fig. 1 montre comment est arrangé le garde-temps ob- 45 pour une fréquence à régler basse. Il s'en suivrait donc que la durée de fonctionnement de l'oscillateur HF et des diviseurs qui le suivent serait beaucoup trop longue et aurait pour conséquence une consommation exagérée pour la précision de réglage considérée. Par exemple et pour fixer les idées, si 50 l'on désire discerner un écart de fréquence de 0,06 ppm ou  $1/2^{24}$  (ce qui permet une précision de marche de  $31,1 \cdot 10^6$  secondes/année  $\times$  0,06  $\cdot$  10<sup>-6</sup> = 1,86 seconde/année), il faudra compter 224 impulsions de référence. Or, si c'est le nombre de cycles de l'oscillateur BF (32 kHz = 215) qui est mesuré 55 pendant la période de référence fournie par l'oscillateur HF, la mesure va durer  $2^{24}/2^{15} = 512$  secondes. Si on admet, d'autre part, que la consommation de l'oscillateur HF plus celle de la chaîne de division est de l'ordre de 15 µA (oscillateur seul 5 μA) et que l'on néglige dans ce cas la consom-60 mation due au temps de démarrage de l'oscillateur (environ 2 s), l'augmentation de la consommation moyenne occasionnée seulement par le système de mesure et pour une période d'asservissement de 1024 s sera de

$$\frac{15 \mu A}{1024 \text{ s}}$$

512 s = 7,5  $\mu A$ ,

ce qui est incompatible avec une durée de vie raisonnable de la pile.

Selon l'invention et pour réduire le temps de fonctionnement des circuits HF, on mesure, au moyen d'impulsions de référence générées par l'oscillateur ou quartz HF, une période pilotée par la fréquence BF à corriger. L'écart se mesure en comptant le nombre d'impulsions de référence contenues dans la période à corriger. En d'autres termes, la chaîne de division sur laquelle s'effectue la mesure n'est pas celle dont il faut corriger la valeur, mais la référence mesurée au moyen d'une période fausse. En reprenant l'exemple donné à l'alinéa précédent et pour la même précision exigée de 0,06 ppm, on va mesurer pendant une période BF fausse un nombre de cycles de référence fournis par un quartz HF (par exemple 4 MHz =  $2^{22}$ ) et la mesure va durer  $2^{24}/2^{22} = 4$  secondes. En admettant la même période d'asservissement de 1024 s, les mêmes consommations de 5  $\mu A$  pour l'oscillateur HF seul, de 15 μA pour les circuits HF et un temps de démarrage de 2 s pour l'oscillateur, l'augmentation de la consommation moyenne occasionnée par le système de mesure sera réduite à

$$\frac{15 \, \mu A}{1024 \, s} \, 4s + \frac{5 \, \mu A}{1024 \, s} \, 2s = 0,068 \, \mu A,$$

ce qui est parfaitement acceptable. En fait, le gain théorique sur la consommation se trouve être dans le rapport des fréquences en présence soit f(HF)/f(BF), ici égal à 4 · 10<sup>6</sup>/  $32 \cdot 10^4 = 128$ , alors que la gain réel n'est que de 7,5/ 0,068 = 110 car on doit tenir compte de la consommation de l'oscillateur HF pendant son temps de démarrage.

On l'a vu, le système objet de l'invention exige un oscillateur BF qui est la base de temps utilisée pour l'affichage de 35 l'heure dont il s'agit de corriger l'imprécision et un oscillateur HF qui sert de référence pour effectuer cette correction. Chacun des oscillateurs est suivi d'une chaîne de diviseurs de fréquence et l'on considère ici un système de correction purement digital. Si l'on désigne par X (en ppm) l'écart de fréquence totale présenté par l'oscillateur BF et par Y (en ppm) la précision désirée, le nombre de pas de réglage nécessaires  $N_1$  sera de  $N_1 = X/Y$ . Le nombre de bits nécessaires pour réaliser ces pas sera de  $d_1 = log_2 N_1$ ,  $d_1$  donnant le nombre d'étages diviseurs de la chaîne HF. En ce qui concerne la période de réglage, le nombre de pas N<sub>2</sub> à considérer pour qu'un pas ait Y ppm sera de  $N_2 = 1/Y$  et le nombre de bits nécessaires, représentant le nombre d'étages diviseurs de la chaîne BF sera de  $d_2 = \log_2 N_2$ . Enfin, si l'on désigne par f(BF)min la fréquence la plus basse que peut présenter l'oscillateur BF, la période totale de réglage (inhibition) en secondes va durer 2<sup>d2</sup>/f(BF)min. Une application à un exemple concret des relations qui viennent d'être données sera exposée plus loin.

explique le fonctionnement du système. La chaîne 3 délivre à la sortie de son dernier diviseur un signal d'asservissement fa qui est émis par exemple toutes les dix-sept minutes (1024 s). Chaque cycle d'asservissement fa débute par un cycle de mesure fm qui se décompose en cinq phases successives (voir lignes des temps t du diagramme):

- 1. Au temps t<sub>0</sub>, l'oscillateur HF est mis en marche (signal OS) pendant une durée t<sub>1</sub>-t<sub>0</sub> assez longue pour permettre sa stabilisation (2 s).

- 2. Au temps t<sub>1</sub>, la chaîne de division HF est débloquée (signal BL) en même temps que lui est supprimée sa remise à zéro (signal RC). Dès cet instant t<sub>1</sub>, on procède à la mesure proprement dite en comptant le nombre d'impulsions de ré-

férence délivrées par la chaîne HF et ceci pendant une période prédéterminée t<sub>2</sub>-t<sub>1</sub> fournie par le diviseur BF (4 s).

- 3. A la fin de ladite période prédéterminée, au temps t2, on bloque les diviseurs HF (signal BL) et on stoppe l'oscillateur HF (signal OS).

- 4. Après un court laps de temps de durée t<sub>3</sub>-t<sub>2</sub> (30 μs) qui tient compte du temps de propagation de l'effet de blocage, on transfert au temps t<sub>3</sub> le contenu des diviseurs HF dans la première mémoire 9 (signal Tt) pendant une durée t<sub>4</sub>-t<sub>3</sub> 10 (60 µs).

5. Enfin, après une courte durée de sécurité t<sub>5</sub>-t<sub>4</sub> (30 μs), on remet à zéro la chaîne HF au temps t<sub>5</sub> (signal RC).

Le même cycle de mesure recommencera au temps to où la durée t<sub>6</sub>-t<sub>0</sub> (1024 s) se trouve représenter le cycle d'asservissement.

Les valeurs en secondes données ci-dessus entre parenthèses sont un exemple et ne limitent pas la portée de l'invention pour laquelle d'autres valeurs pourraient être choisies sans pour autant s'écarter de l'objet de l'invention. La même remarque vaut pour certaines valeurs chiffrées qui seront données par la suite.

Comme le montre la fig. 1, les signaux OS, RC, BL et Tt sont issus du circuit logique de la commande d'asservissement 10 et sont le résultat de la combinaison des signaux fa, fm, fos, fRo et ft en provenance de la chaîne BF 3. Ces derniers sont représentés en tête du diagramme de la fig. 2.

La fig. 3 montre un arrangement possible pour réaliser cette combinaison. Le schéma présenté se compose de circuits logiques élémentaires: inverseurs, portes NOR et 30 NAND, flip-flop, qui forment le contenu du bloc 10 montré en fig. 1. On y trouve les signaux fa, fm, fos, fRo et ft appliqués aux entrées 15, 14, 13, 12 et 11 respectives. L'homme du métier comprendra, sans que des explications soient données ici, comment l'agencement des divers circuits logiques est fait pour parvenir aux signaux RC, BL, OS et Tt présents à la sortie du bloc. En plus des cycles fa et fm dont il a été question plus haut, on trouve le signal fos (4 s) qui représente le cycle de démarrage de l'oscillateur HF et les fréquences fRo (8 kHz) et ft (16 kHz) qui assurent les temps de transfert (60 μs) et de sécurité (30 μs).

On comprend qu'il est nécessaire, pendant la mesure des impulsions de référence, d'empêcher toute inhibition. Pour ce faire, la période d'inhibition est déterminée par le signal fi (dont le rapport cyclique est de 1) en provenance de la chaîne 3 et agissant sur la commande d'inhibition 18 comme le montre la fig. 1. L'inhibition est exécutée quand ce signal est à l'état 0, ce qui est le cas pendant une demi-période seulement. Au début de l'autre demi-période pendant laquelle aucune autre inhibition n'a lieu, correspond périodiquement le début d'une période d'asservissement fa qui est aussi le début d'une mesure. Cette coïncidence est automatique du fait que le signal d'inhibition fi est généré par la même chaîne de division 3 qui génère aussi le signal d'asservissement fa.

Pour illustrer ce qui vient d'être dit, on prendra main-On se reportera maintenant au diagramme de la fig. 2 qui 55 tenant un cas pratique. On utilise un quartz BF dont la fréquence la plus basse est de  $2^{15} = 32768$  Hz. A cela s'ajoutent les tolérances usuelles comme par exemple la précision d'usinage, le vieillissement et la dérive due à la température qui totalisent 115 ppm. Si on désire une précision de 0,06 ppm (ce qui, on l'a vu plus haut, autorise une précision de marche de 1,86 seconde/année), le nombre de pas de réglage nécessaires  $N_1$  sera de  $N_1 = 115/0,06 \cong 1900$ . Pour réaliser ces pas, le nombre de bits nécessaires sera de  $d_1 = log_2$  1900 = 11 qui est le nombre de diviseurs de la chaîne HF. En ce qui concerne la période de réglage, le nombre de pas à considérer pour qu'un pas ait 0,06 ppm sera de  $N_2 = 1/0,06 \cdot 10^{-6}$ =  $16.6 \cdot 10^6$  et le nombre de diviseurs de la chaîne BF sera de  $d_2 = \log_2 16.6 \cdot 10^6 = 24$ . Enfin, puisque la fréquence la plus

basse présentée par l'oscillateur BF est de 2<sup>15</sup> Hz, la période totale d'inhibition va durer 2<sup>24</sup>/2<sup>15</sup> = 512 secondes. Aux vingt-quatre diviseurs de la chaîne 3, nécessaires au fonctionnement du système (le signal émis par le vingt-quatrième agissant sur la commande d'inhibition 18), s'en ajoute un vingt-cinquième (1024 s) qui toutes les dix-sept minutes fait redémarrer un cycle d'asservissement.

Le diagramme de la fig. 4 montre ce qui se passe pendant la durée de la période à corriger. Cette période, issue de la chaîne BF, commence au temps  $\mathbf{t}_1$  dès que le signal BL passe à l'état 0 et s'arrête au temps t2 dès que ledit signal revient à l'état 1. Dès l'instant  $t_1$ , la chaîne HF se met à compter les impulsions émises par l'oscillateur HF. On a représenté sur la fig. 4 les signaux présents à la sortie (HF1 à HF5) de cinq diviseurs successifs de la chaîne HF (qui en comporte normalement onze dans l'exemple cité ici). Pour rendre le diagramme explicite, on comprendra qu'il a fallu choisir une autre échelle des temps pour représenter en superposition la période BF (4 s) et les impulsions HF dont la fréquence la plus basse, après onze divisions, est encore de 4 kHz. A un certain moment (temps tx), tous les diviseurs HF se trouvent à 0 et ceci avant que la période à corriger BL soit terminée. Ceci est dû au fait qu'on a choisi un quartz HF aux tolérances plus éloignées (par exemple + 140 à +4140 ppm) que les tolérances du quartz BF (par exemple + 60 à + 100 ppm). A 25 partir de cet instant tx, la chaîne HF va recommencer un cycle de comptage, lequel sera interrompu au temps t2. A ce moment, l'état logique de tous les diviseurs HF est une mesure de l'écart séparant le moment (tx) où tous les diviseurs HF ont passé par 0 et celui où se termine la période à corriger (t2). Dans la figure, les cinq diviseurs représentés possèdent la valeur binaire 00110 lors de l'arrêt du comptage de la chaîne. Cette valeur est retenue momentanément par la chaîne 7 avant d'être transférée par la ligne 8 à partir du temps t<sub>3</sub> dans la première mémoire 9, comme cela ressort de la fig. 2.

On dispose maintenant à la sortie de la mémoire 9 d'une valeur binaire correspondant à l'écart entre la période BF à corriger et la période HF de référence. On appellera cette valeur écart BF-HF.

Théoriquement, on pourrait imaginer que l'oscillateur HF délivre une fréquence nominale exacte. Dans ce cas,

l'écart BF-HF pourrait être mis à profit pour agir directement sur le circuit de commande d'inhibition 4, comme cela est proposé par les exposés d'invention suisses cités plus haut.

En réalité, quels que soient les moyens qu'on prenne pour ajuster le quartz HF le plus près possible de sa fréquence nominale, il subsistera toujours une différence entre cette valeur nominale et la valeur réelle. Par ailleurs, pour simplifier les opérations de fabrication, on peut même penser utiliser des quartz HF très grossièrement ajustés. Dans ce cas, on propose de les grouper par catégories. Pour chacune de ces catégories, on mesure l'écart entre la valeur réelle produite par le second diviseur et la valeur nominale que produirait ledit second diviseur s'il était alimenté par un signal de fré-15 quence nominale. Cette différence ou valeur étalon qu'on appellera écart HF-Nom. est introduite une fois pour toutes par la ligne 19 dans une seconde mémoire 17 (qui peut être une mémoire non volatile, si l'on désire garder son information lors d'un changement de pile). On s'arrange pour que la 20 sortie de la mémoire 17 présente une valeur binaire qui soit exprimée avec des bits de poids identiques à ceux issus de la première mémoire 9. Il est dès lors possible de comparer l'écart BF-HF avec l'écart HF-Nom. dans un circuit soustracteur 16 de façon à obtenir un signal binaire à la sortie du soustracteur qui représente l'écart BF-Nom. pour agir sur le circuit de commande d'inhibition 4.

On est ainsi parvenu à régler avec précision la marche du garde-temps. Ce réglage se fait périodiquement et automatiquement grâce à des moyens qui sont internes au garde-temps. Aucune intervention extérieure n'est nécessaire sauf naturellement celle qui consiste, lors de la fabrication de la montre, à mémoriser une fois pour toutes l'écart existant entre le quartz HF choisi et la fréquence nominale que devrait donner ce quartz.

On remarquera que le système décrit est applicable à n'importe quel type d'oscillateur. Dans le cas où la dérive de l'oscillateur BF serait plus importante que celle donnée par un quartz (ici 115 ppm), il suffirait d'augmenter le nombre de diviseurs de la chaîne HF. Dans l'état actuel de la technique cependant, on pourrait difficilement envisager un oscillateur HF autre que celui dont la fréquence de référence serait donnée par un quartz.