(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4359561号

(P4359561)

(45) 発行日 平成21年11月4日(2009.11.4)

(24) 登録日 平成21年8月14日(2009.8.14)

(51) Int.Cl.

G 11 C 11/15 (2006.01)

F 1

G 11 C 11/15 140

請求項の数 4 (全 19 頁)

(21) 出願番号 特願2004-517527 (P2004-517527)

(86) (22) 出願日 平成15年4月29日 (2003.4.29)

(65) 公表番号 特表2005-531876 (P2005-531876A)

(43) 公表日 平成17年10月20日 (2005.10.20)

(86) 国際出願番号 PCT/US2003/013179

(87) 国際公開番号 WO2004/003922

(87) 国際公開日 平成16年1月8日 (2004.1.8)

審査請求日 平成18年4月28日 (2006.4.28)

(31) 優先権主張番号 10/186,141

(32) 優先日 平成14年6月28日 (2002.6.28)

(33) 優先権主張国 米国(US)

(73) 特許権者 509052894

エバースピン テクノロジーズ インコーポレイテッド

E v e r S p i n T e c h n o l o g i e s, l n c.

アメリカ合衆国 85225 アリゾナ州

チャンドラー ノース アルマ スターブル ロード 1300

(74) 代理人 100142907

弁理士 本田 淳

(74) 代理人 100149641

弁理士 池上 美穂

最終頁に続く

(54) 【発明の名称】トグルメモリに書き込む回路および方法

## (57) 【特許請求の範囲】

## 【請求項 1】

トグルメモリの読み取りおよび書き込み方法であって、

前記トグルメモリの所定のアドレス位置の読み取り動作を開始するステップ、

前記所定のアドレス位置における書き込みトグル動作の一部を、現在格納されている値に影響を及ぼすことなく開始するステップ、

前記所定のアドレス位置における前記現在格納されているデータ値を、該所定のアドレスに書き込むべき新たな値と比較するステップであって、それによって、該新たな値が前記格納されているデータ値と異なっているか同一であるかを判定する、比較するステップ、および

前記新たな値が前記格納されているデータ値と異なる場合には前記所定のアドレス位置に前記新たな値を書き込むことによって前記書き込みトグル動作を完了し、または前記書き込むべき新たな値が前記格納されているデータ値と同じである場合には前記所定のアドレス位置に前記新たな値を書き込むことなく前記トグル動作を完了するステップの一連のステップを備える、トグルメモリの読み取りおよび書き込み方法。

## 【請求項 2】

トグルメモリの読み取りおよび書き込み方法であって、

前記トグルメモリの所定のアドレス位置において読み取り動作を実施するために必要な第1の時間長を定義するステップ、

前記トグルメモリの前記所定のアドレス位置において書き込み動作を実施するために必

要な第2の時間長を定義するステップ、

前記トグルメモリの読み取りワード線ドライバによって前記読み取り動作を開始するステップ、および

前記読み取り動作が完了する前に前記トグルメモリの書き込みビット線ドライバによって前記書き込み動作を開始し、前記所定のアドレス位置が、前記書き込み動作中に書き込みたい書き込み値と同じ情報値を含むと判定された場合に、前記書き込み動作を選択的に終了するステップ

の一連のステップを含む、トグルメモリの読み取りおよび書き込み方法。

【請求項3】

2つの論理状態間でトグルして情報格納値を示すメモリセルのアレイと、

10

列アドレスを受け取って、前記メモリセルのアレイ内の所定のビット列を選択するビット選択信号を前記メモリセルのアレイに供給するビットデコードロジックと、

行アドレスを受け取って、前記メモリセルのアレイ内の所定のビット行を選択するワード選択信号を前記メモリセルのアレイに供給するワードデコードロジックと、

前記メモリセルのアレイに結合され、前記ワードデコードロジックに応答して所定のワード線を駆動する読み取りワード線ドライバと、

前記メモリセルのアレイに結合され、前記ワードデコードロジックおよび書き込みイネーブル信号に応答して所定のワード線を駆動する書き込みワード線ドライバと、

前記ビットデコードロジックに結合され、前記行アドレスおよび列アドレスによって選択されたビットが前記2つの論理状態のどちらを有するかを判定するセンス回路と、

20

該センス回路に結合され、該センス回路の出力を、前記行アドレスおよび前記列アドレスを含む所定のアドレスに書き込むべき新たな値と比較して、該新たな値が、格納されているデータ値と異なっているか同じであるかを判定する比較器と、

該比較器に結合され、前記書き込みイネーブル信号に応答して前記ビットデコードロジックによって確定される所定の列を駆動し、前記新たな値が前記格納されているデータ値と異なる場合には前記所定のアドレスに前記新たな値を書き込むことによって前記書き込みトグル動作を完了し、前記書き込むべき新たな値が前記格納されているデータ値と同じである場合には前記所定のアドレスに前記新たな値を書き込むことなく前記トグル動作を終了する回路部とを備えるトグルメモリ。

【請求項4】

30

書き込むべきビット位置の論理状態のトグルを行うことによって情報を格納するアレイと、

前記アレイに結合されて、読み取りワード線ドライバによって読み取り動作を開始した後で読み取り動作が完了する前に書き込みビット線ドライバによって書き込み動作を開始することによって前記アレイに情報を書き込む制御回路部であって、書き込みたい新たな値に電流格納値が対応する場合に前記書き込み動作を選択的に終了する制御回路部とを備えるメモリ。

【発明の詳細な説明】

【技術分野】

【0001】

40

本発明はメモリへの書き込みに関し、より詳細にはトグルするメモリへの書き込みに関する。

【背景技術】

【0002】

不揮発性メモリ装置は、電子システムの非常に重要な構成部品である。FLASHは現在使用されている主要な不揮発性メモリ装置である。通常の不揮発性メモリ装置は、浮遊酸素層に捕獲された電荷を用いて情報を格納する。FLASHメモリの欠点としては、高電圧要件および遅いプログラム時間および消去時間がある。また、FLASHメモリは書き換え耐久性が低く、 $10^4 \sim 10^6$ サイクルでメモリが故障してしまう。また、妥当なデータ保持を維持するために、ゲート酸化膜のスケーリングは電子が受ける(see)トン

50

ネル障壁によって制限される。よって、F L A S H メモリの寸法は、スケーリングすることのできる範囲に制限される。

【0003】

これらの欠点を克服するために、磁気メモリ装置が評価されている。このような装置の1つに、磁気抵抗RAM(以下では「MRAM」と呼ぶ)がある。しかし、商業的に実用的なものとするには、MRAMは、現在のメモリ技術に匹敵するメモリ密度を有し、将来的な生産に関してスケーラブルであり、低電圧で動作し、電力消費量が低く、匹敵する読み取り/書き込み速度を有しなければならない。

【0004】

MRAM装置の場合、その設計特性の最も重要な側面として、不揮発性メモリの状態の安定性、読み取り/書き込みサイクルの繰り返し性、およびメモリエレメント間のスイッチング磁界の均一性の3つがある。MRAMのメモリ状態は、電力によって維持されるのではなく、磁気モーメントベクトルの方向によって維持される。データの格納は、磁界を印加し、MRAM装置の磁性体を2つの可能なメモリ状態のいずれかに磁化させることによって達成される。データの呼び出しは、MRAM装置における2つの状態間の抵抗差を検知することによって達成される。書き込みのための磁界は、磁気構造外部のストリップ線または磁気構造自体に電流を流すことによって生成される。

10

【0005】

MRAM装置の横寸法が小さくなるにつれて、3つの問題が生じる。第1に、所与の形状および膜厚に対するスイッチング磁界が大きくなり、スイッチングにより大きな磁界を必要とする。第2に、全体のスイッチング量が減り、反転のためのエネルギー障壁が減る。エネルギー障壁とは、磁気モーメントベクトルを或る状態からもう一方の状態にスイッチングさせるために必要なエネルギーの量を指す。エネルギー障壁により、MRAM装置のデータ保持および誤り率が決まり、障壁が小さすぎる場合、熱変動(超常磁性)により意図しない反転が生じる可能性がある。エネルギー障壁が小さいことに伴う主な問題は、アレイ内の1つのMRAM装置を選択的にスイッチングさせることができることである。選択性により、他のMRAM装置を意図せずスイッチングすることなくスイッチングを行うことができる。最後に、スイッチング磁界は、形状により生成されるため、MRAM装置のサイズが小さくなるにつれて形状の変化により敏感になる。フォトリソグラフィーによるスケーリングは小さな寸法になるほど難しくなるため、MRAM装置は、密なスイッチング分布を維持することが難しくなるであろう。

20

【0006】

したがって、従来技術にあった上記および他の欠点を改善することが非常に有利であろう。

【発明を実施するための最良の形態】

【0007】

本発明の上記およびさらなるより具体的な目的および利点は、当業者には、添付図面とともに解釈される以下の本発明の好適な実施形態の詳細な説明から容易に明らかとなるであろう。

【0008】

30

トグルメモリは、メモリセルの状態を反転させるか、あるいはメモリセルを同一の論理状態のままにしておくことによって書き込まれる。これらのどちらが選択されたかを判定するためには、書き込むべき論理状態を既存の状態と比較しなければならない。この場合、書き込みシーケンスは、この比較が完了する前に開始される。比較の結果が、論理状態を反転すべきであるというものである場合、書き込みシーケンスを続行する。論理状態を同一のままですべき場合、書き込みシーケンスを終了する。

【0009】

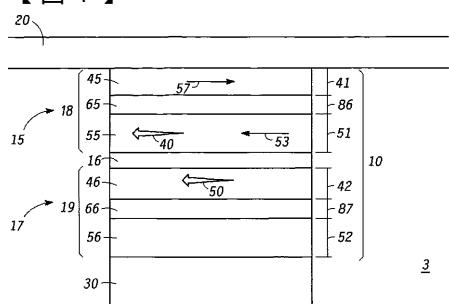

次に図1を参照して、図1は、本発明の好適な実施形態によるMRAMアレイ3の略断面図を示す。この例では、単一の磁気抵抗メモリ装置10のみを示すが、MRAMアレイ3はいくつかのMRAM装置10からなり、本発明では、書き込み方法の説明を簡潔にす

40

50

るために、そのような装置を1つだけ示していることが理解されるであろう。

【0010】

MRAM装置10は、書き込みワード線20および書き込みビット線30を備える。書き込みワード線20および書き込みビット線30は、電流を流すことができるよう導電体を含む。この例示において、書き込みワード線20はMRAM装置10の上部に配置され、書き込みビット線30はMRAM装置10の下部に配置されて、ワード線20に対して90°の角度に向けられる(図2を参照)。代替として、書き込みワード線20はMRAM装置10の下部に配置されてもよく、書き込みビット線30はMRAM装置10の上部に配置されてもよい。

【0011】

MRAM装置10は、第1の磁性体領域15、トンネル障壁16、および第2の磁性体領域17を含むトンネル接合部を備え、トンネル障壁16は第1の磁性体領域15と第2の磁性体領域17の間に挟まれる。好適な実施形態において、磁性体領域15は、2つの強磁性体層45および55の間の反強磁性体結合スペーサ層65を有する三層構造18を含む。反強磁性体結合スペーサ層65は厚さ86を有し、強磁性体層45および55はそれぞれ厚さ41および51を有する。さらに、磁性体領域17は、2つの強磁性体層46および56の間の反強磁性体結合スペーサ層66を有する三層構造19を有する。反強磁性体結合スペーサ層66は厚さ87を有し、強磁性体層46および56はそれぞれ厚さ42および52を有する。

【0012】

一般に、反強磁性体結合スペーサ層65および66は、Ru、Os、Re、Cr、Rh、Cu、またはそれらの組み合わせの元素のうちの少なくとも1つを含む。さらに、強磁性体層45、55、46、および56は、Ni、Fe、Mn、Co、またはそれらの組み合わせの元素のうちの少なくとも1つを含む。また、磁性体領域15および17は、三層構造以外の合成反強磁性体(SAF)層構造を含むこともでき、本実施形態での三層構造の使用は例示目的に過ぎないことが理解されるであろう。例えば、そのような合成反強磁性体層構造の1つとして、強磁性体層/反強磁性体結合スペーサ層/強磁性体層/反強磁性体結合スペーサ層/強磁性体層の構造である五層の積層体が含まれる可能性がある。

【0013】

強磁性体層45および55はそれぞれ、反強磁性体結合スペーサ層65の結合により通常は反平行に保持される磁気モーメントベクトル57および53を有する。また、磁性体領域15は、結果として生じる磁気モーメントベクトル40を有し、磁性体領域17は、結果として生じる磁気モーメントベクトル50を有する。結果として生じる磁気モーメントベクトル40および50は、書き込みワード線20および書き込みビット線30から或る角度、好ましくは45°の方向にある異方性の容易軸に沿って配向している(図2を参照)。さらに、磁性体領域15は浮遊強磁性体領域である、すなわち、結果として生じる磁気モーメントベクトル40が、磁界が印加されても自由に回転できる。磁性体領域17はピン止め(pin:固定)された強磁性体領域である、すなわち、結果として生じる磁気モーメントベクトル50が、適度な磁界が印加された状態では自由に回転できず、基準層として用いられる。

【0014】

各三層構造18において2つの強磁性体層の間にある反強磁性体結合層を示すが、強磁性体層は、静磁界または他の特徴といった他の手段により反強磁性体結合されることもできることが理解されるであろう。例えば、セルのアスペクト比を5以下に小さくした場合、強磁性体層は、静磁束還流(magnetostatic flux closure)により反平行結合される。

【0015】

好適な実施形態において、MRAM装置10は、非円形の平面の場合に長さ/幅の比が1~5の範囲である三層構造18を有する。しかし、本発明では円形の平面を示す(図2を参照)。MRAM装置10は好適な実施形態において、形状異方性によるスイッチング磁界への貢献を最小化するために、また、フォトリソグラフィー加工を用いて装置をより

10

20

30

40

50

小さな横寸法にスケーリングするほうが容易するために円形形状である。しかし、M R A M 装置 1 0 は他の形状、例えば正方形、楕円形、長方形、またはひし形とすることができるものの、簡略化のために円形のものとして図示されることが理解されるであろう。

#### 【 0 0 1 6 】

さらに、M R A M アレイ 3 の作製中、それ以後の各層（すなわち 3 0、5 5、6 5 等）は、順に堆積または他の方法で形成され、各 M R A M 装置 1 0 は、半導体業界において既知の技法のいずれかで選択的堆積、フォトリソグラフィー加工、エッチング等によって画定されてもよい。少なくとも強磁性体層 4 5 および 5 5 の堆積中に、このペアに優先（preferred）磁気容易軸を設定するために磁界が与えられる（誘導異方性）。与えられた磁界は、磁気モーメントベクトル 5 3 および 5 7 に優先異方性軸を生じる。優先軸は、じきに説明するように、書き込みワード線 2 0 と書き込みビット線 3 0 の間で 4 5 ° の角度となるように選択される。

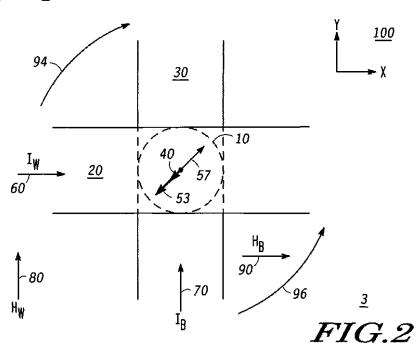

#### 【 0 0 1 7 】

次に図 2 を参照して、図 2 は、本発明による M R A M アレイ 3 の略平面図を示す。M R A M 装置 1 0 の説明を簡略化するために、全ての方向は、図示のような x および y 座標系 1 0 0 ならびに時計回り方向 9 4 および反時計回り方向 9 6 を基準にする。説明をさらに簡略化するために、ここで再度、N は 2 に等しく、M R A M 装置 1 0 が、磁気モーメントベクトル 5 3 および 5 7 ならびに結果として生じる磁気モーメントベクトル 4 0 を有する領域 1 5 において 1 つの三層構造を含むものと仮定する。また、磁気モーメントベクトルはスイッチングされるため、領域 1 5 の磁気モーメントベクトルのみを図示する。

#### 【 0 0 1 8 】

書き込み方法がどのように機能するかを例示するために、磁気モーメントベクトル 5 3 および 5 7 の優先異方性軸は、負の x 方向および負の y 方向に対して 4 5 ° の角度、および正の x 方向および正の y 方向に対して 4 5 ° の角度の向きにあると仮定する。一例として、図 2 は、磁気モーメントベクトル 5 3 が負の x 方向および負の y 方向に対して 4 5 ° の角度の向きにあることを示す。磁気モーメントベクトル 5 7 は通常、磁気モーメントベクトル 5 3 に対して反平行に配向されるため、正の x 方向および正の y 方向に対して 4 5 ° の角度に方向付けされる。この初期配向は、じきに説明するように、書き込み方法の例を示すために用いられる。

#### 【 0 0 1 9 】

好適な実施形態において、書き込みワード電流 6 0 は、正の x 方向に流れる場合に正であるものとして定義され、書き込みビット電流 7 0 は、正の y 方向に流れる場合に正であるものとして定義される。書き込みワード線 2 0 および書き込みビット線 3 0 の目的は、M R A M 装置 1 0 内に磁界を生成することである。正の書き込みワード電流 6 0 は周囲の書き込みワード磁界  $H_w$  8 0 を誘導し、正の書き込みビット電流 7 0 は周囲の書き込みビット磁界  $H_b$  9 0 を誘導する。この例では、書き込みワード線 2 0 が M R A M 装置 1 0 の上にあるため、要素平面において、 $H_w$  8 0 は正の書き込みワード電流 6 0 の場合に M R A M 装置 1 0 に正の y 方向で印加される。同様に、書き込みビット線 3 0 は M R A M 装置 1 0 の下にあるため、要素平面において、 $H_b$  9 0 は正の書き込みビット電流 7 0 の場合に M R A M 装置 1 0 に正の x 方向で印加される。正および負の電流の定義は任意であり、ここでは例示目的で定義されることが理解されるであろう。電流を反転させる効果は、M R A M 装置 1 0 内で誘導される磁界の方向を変化させるものである。電流によって誘導される磁界の挙動は当業者にはよく知られているため、ここでさらに詳述することはしない。

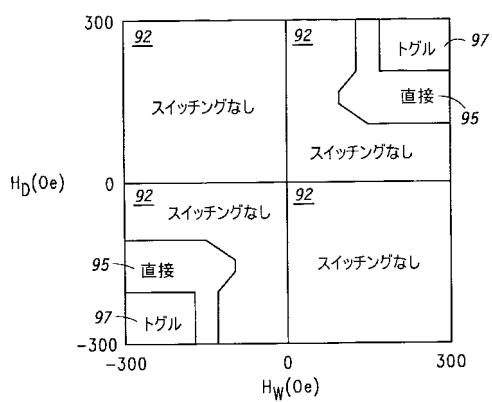

#### 【 0 0 2 0 】

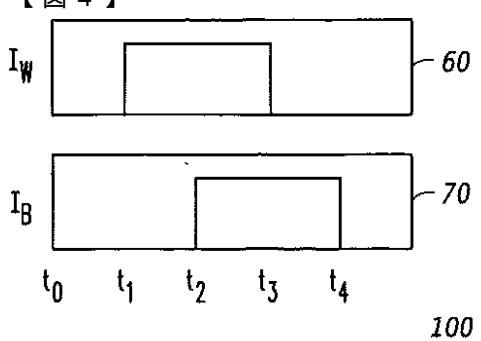

次に図 3 を参照して、図 3 は、S A F 三層構造のシミュレートされたスイッチング挙動を示す。シミュレーションは、内因性の異方性とほぼ同一のモーメント（ほぼ釣り合いの取れた S A F ）を有し、反強磁性体結合され、磁化ダイナミクスがランダウ - リフシツ（Landau-Lifshitz）方程式によって記述される 2 つの単磁区層からなる。x 軸は、書き込みワード線の磁界の大きさ（エルステッド（1 エルステッド 7 9 . 5 7 7 アンペア毎

10

20

30

40

50

メートル) ) であり、y 軸は、書き込みビット線の磁界の大きさ(エルステッド)である。磁界は、図4に示すようなパルスシーケンス100で印加され、パルスシーケンス100は、時間に応じた書き込みワード電流60および書き込みビット電流70を含む。

#### 【0021】

図3には3つの動作領域が示されている。領域92ではスイッチングが起こらない。領域95におけるM R A M動作には、直接書き込み方法が実施される。直接書き込み方法を用いる場合、状態がスイッチングするのは、書き込まれる状態が格納されている状態と異なる場合のみであるため、M R A M装置の初期状態を判定する必要はない。書き込み状態の選択は、書き込みワード線20および書き込みビット線30の両方における電流の方向によって判定される。例えば、「1」を書き込みたい場合、両方の線の電流の方向は正になる。「1」が既に要素に格納されており、「1」が書き込まれる場合、M R A M装置の最終的な状態は「1」であり続ける。さらに、「0」が格納されており、正の電流を用いて「1」が書き込まれる場合、M R A M装置の最終的な状態は「1」となる。書き込みワード線と書き込みビット線の両方に負の電流を用いることによって、「0」を書き込む場合も同様の結果が得られる。したがって、いずれの状態であっても、初期の状態に関係なく適切な極性の電流パルスを用いて所望の「1」または「0」にプログラムすることができる。本開示を通して、領域95における動作は「直接書き込みモード」として定義される。

#### 【0022】

領域97におけるM R A Mの動作には、トグル書き込み方法が実施される。トグル書き込み方法を用いる場合、書き込みの前にM R A M装置の初期状態を判定する必要がある。これは、書き込みワード線20と書き込みビット線30の両方に同一極性の電流パルスが選択される限り、電流の方向に関係なくM R A M装置に書き込みが行われる度に状態がスイッチングするためである。例えば、「1」が最初に格納されている場合、書き込みワード線と書き込みビット線に正の電流パルスシーケンスを1回流すと、装置の状態は「0」にスイッチングされる。格納された「0」の状態に繰り返し正の電流パルスシーケンスを与えると、状態は「1」に戻る。したがって、メモリエレメントを所望の状態に書き換える(write)可能とするには、M R A M装置10の初期状態をまず読み取って、書き込むべき状態と比較しなければならない。この読み取りおよび比較は、情報を格納するバッファと、メモリ状態を比較する比較器とを含むさらなる論理回路部を必要とする場合がある。次に、格納されている状態と書き込むべき状態とが異なる場合にのみ、M R A M装置10に書き込みを行う。この方法の利点の1つに、異なるビットのみをスイッチングさせるため、消費電力が少なくなることがある。トグル書き込み方法を用いるさらなる利点として、単極電圧のみが必要であり、結果として、より小さなNチャネルトランジスタを使用してM R A M装置を駆動できることがある。本開示を通して、領域97における動作は「トグル書き込みモード」として定義される。

#### 【0023】

両方の書き込み方法が、磁気モーメントベクトル53および57を上述のような2つの優先方向の一方に配向させることができるように、書き込みワード線20と書き込みビット線30に電流を供給することを伴う。2つのスイッチングモードを完全に説明するために、磁気モーメントベクトル53、57、および40の時間発展を説明する具体的な例を次に示す。

#### 【0024】

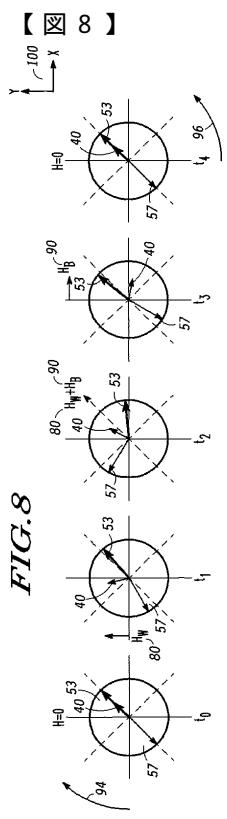

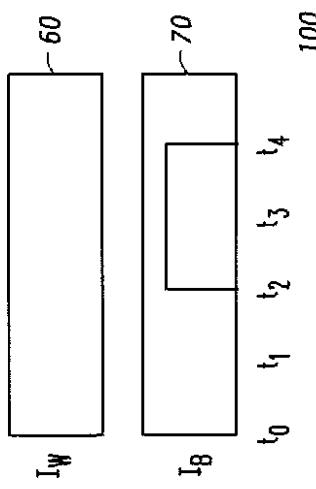

次に図5を参照すると、図5は、パルスシーケンス100を用いて「1」を「0」に書き換えるトグル書き込みモードを示す。この図の時間 $t_0$ において、磁気モーメントベクトル53および57は、図2に示すような優先方向に配向している。この配向を「1」として定義する。

#### 【0025】

時間 $t_1$ において、正の書き込みワード電流60がオンにされ、これにより、正のy方向に方向付けされる $H_w$ 80を誘導する。正の $H_w$ 80の作用は、ほぼ釣り合いの取れた

10

20

30

40

50

反整列の(anti-aligned) M R A M 三層構造を「フロップ」させ、印加された磁界の方向に対して約90°の配向にすることである。強磁性体層45および55間の有限の反強磁性体交換相互作用により、磁気モーメントベクトル53および57を今度は小さな角度で磁界の方向に偏向させることができ、結果として生じる磁気モーメントベクトル40は、磁気モーメントベクトル53および57の間の角度に延び(subtend)、 $H_w$ 80と整列する。よって、磁気モーメントベクトル53は時計回り方向94に回転する。結果として生じる磁気モーメントベクトル40は、磁気モーメントベクトル53および57のベクトル加算であるため、磁気モーメントベクトル57もまた時計回り方向94に回転する。

#### 【0026】

時間 $t_2$ において、正の書き込みビット電流70がオンにされ、これにより正の $H_B$ 90を誘導する。その結果、結果として生じる磁気モーメントベクトル40は同時に、 $H_w$ 80によって正のy方向に、 $H_B$ 90によって正のx方向に方向付けされ、これは、有効な磁気モーメントベクトル40を時計回り方向94に、正のx方向と正のy方向の間の45°の角度に概ね配向されるまでさらに回転させる効果を持つ。その結果、磁気モーメントベクトル53および57もまた時計回り方向94にさらに回転する。

#### 【0027】

時間 $t_3$ において、書き込みワード電流60がオフにされ、この場合、 $H_B$ 90のみが結果として生じる磁気モーメントベクトル40を方向付けし、磁気モーメントベクトル40は今、正のx方向に配向している。磁気モーメントベクトル53および57は今両方とも、異方性困難軸の不安定点を越えた角度に概ね方向付けされる。

#### 【0028】

時間 $t_4$ において、書き込みビット電流70がオフにされ、磁界の力が、結果として生じる磁気モーメントベクトル40に作用しなくなる。その結果、磁気モーメントベクトル53および57は、異方性エネルギーを最小化するために、それぞれの最も近い優先方向に配向される。この場合、磁気モーメントベクトル53の優先方向は正のy方向および正のx方向に対して45°の角度にある。この優先方向はまた、時間 $t_0$ における磁気モーメントベクトル53の最初の方向から180°のところにあり、「0」として定義される。よって、M R A M 装置10は「0」にスイッチングされている。M R A M 装置10は、書き込みワード線20と書き込みビット線30の両方に負の電流を用いることによって磁気モーメントベクトル53、57、および40を反時計回り方向96に回転させることによってもスイッチングすることができるものの、例示目的でそうでない方法で示されることが理解されるであろう。

#### 【0029】

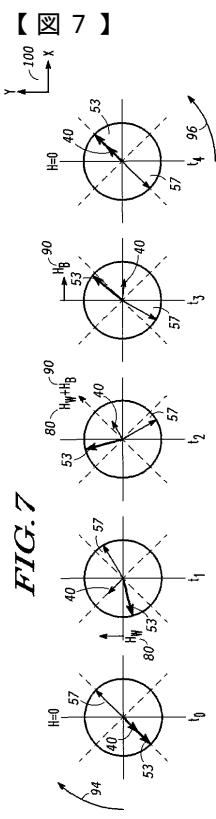

次に図6を参照すると、図6は、パルスシーケンス100を用いて「0」を「1」に書き換えるトグル書き込みモードを示す。磁気モーメントベクトル53および57、ならびに結果として生じる磁気モーメントベクトル40を時間 $t_0$ 、 $t_1$ 、 $t_2$ 、 $t_3$ 、および $t_4$ のそれれにおいて上述のように図示し、同一の電流および磁界方向を用いてM R A M 装置10の状態を「0」から「1」にスイッチングさせる能力を示している。したがって、M R A M 装置10の状態は、図3の領域97に対応するトグル書き込みモードで書き込まれる。

#### 【0030】

直接書き込みモードの場合、磁気モーメントベクトル53の大きさは磁気モーメントベクトル57よりも大きく、磁気モーメントベクトル40は、磁気モーメントベクトル53と同じ方向を指すが、ゼロ磁界の大きさがより小さいと仮定される。この不釣り合いなモーメントにより、印加された磁界に全モーメントを整列させる傾向がある二極エネルギーが、ほぼ釣り合いの取れたS A Fの対称性を壊すことが可能になる。したがってスイッチングは、所与の極性の電流に対して1方向にしか起こり得ない。

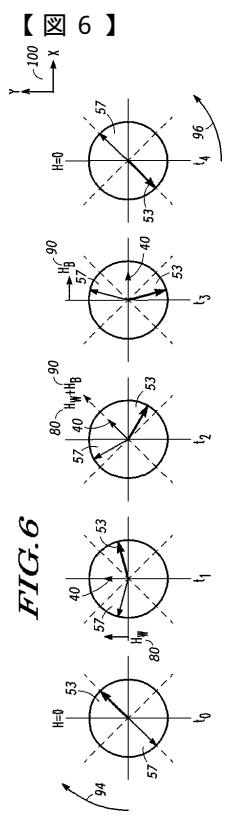

#### 【0031】

次に図7を参照すると、図7は、直接書き込みモードを用い、パルスシーケンス100を用いて「1」を「0」に書き換える一例を示す。ここでもまた、メモリ状態は最初は「

10

20

30

40

50

1」であり、磁気モーメントベクトル 53 は負の x 方向および負の y 方向に対して 45° に方向付けされ、磁気モーメントベクトル 57 は正の x 方向および正の y 方向に対して 45° に方向付けされる。上述の正の書き込みワード電流 60 および正の書き込みビット電流 70 によるパルスシーケンスに続いて、上述のトグル書き込みモードと同様の方法で書き込みが行われる。モーメントは時間  $t_1$  において再び「フロップ」するが、結果として得られる角度は、不釣り合いなモーメントおよび異方性により 90° から傾いていることに留意されたい。時間  $t_4$  の後、MRAM 装置 10 は「0」状態にスイッチングされており、結果として生じる磁気モーメント 40 は、所望通りに正の x 方向および正の y 方向において 45° の角度に配向される。同様の結果が、「0」を「1」に書き換える場合にも得られ、ここでは負の書き込みワード電流 60 および負の書き込みビット電流 70 のみが用いられる。

10

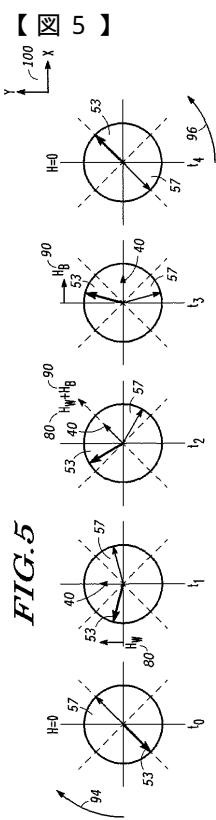

#### 【0032】

次に図 8 を参照すると、図 8 は、直接書き込みモードを用いた書き込みの、新たな状態が既に格納されている状態と同じである場合の一例を示す。この例では、MRAM 装置 10 に「0」が既に格納されており、ここで、電流パルスシーケンス 100 を繰り返して「0」を格納する。磁気モーメントベクトル 53 および 57 は、時間  $t_1$  において「フロップ」しようとするが、印加された磁界に対して不釣り合いの磁気モーメントが作用しなければならないため、回転は損なわれる。よって、反転状態から回転するにはさらなるエネルギー障壁がある。時間  $t_2$  において、ドミナント (dominant) モーメント 53 は、正の x 軸とほぼ整列しており、その最初の異方性方向から 45° 未満である。時間  $t_3$  において、磁界は正の x 軸に沿って方向付けされる。さらに時計方向に回転する代わりに、システムはこの場合、印加された磁界に対する SAF モーメントの対称性を変化させることによってエネルギーを下げる。パッシブ (passive) モーメント 57 が x 軸を越え、システムは、ドミナントモーメント 53 がその元の方向の近くに戻った状態で安定する。したがって、時間  $t_4$  において、磁界を取り除くと、MRAM 装置 10 に格納されている状態は「0」のままとなる。このシーケンスは、図 3 において領域 95 として示される直接書き込みモードの機構を示す。よって、この規則 (convention) において、「0」を書き込むには、書き込みワード線 60 と書き込みビット線 70 の両方に正の電流が必要であり、逆に「1」を書き込むには、書き込みワード線 60 と書き込みビット線 70 の両方に負の電流が必要である。

20

30

#### 【0033】

より大きな磁界を印加する場合、最終的に、フロップおよびシザー (scissor) に関するエネルギー低下は、トグル事象を防止する不釣り合いなモーメントの二極エネルギーによって生じるさらなるエネルギー障壁を越える。この時点で、トグル事象が生じ、領域 97 によってスイッチングが記述される。

#### 【0034】

時間  $t_3$  および  $t_4$  が等しいか、限りなく等しい状態に近づけられた場合、直接書き込みモードが適用される領域 95 を拡張することができる、すなわち、トグルモード領域 97 をより高い磁界に移動させることができる。この場合、磁界の方向は、書き込みワード電流 60 がオンにされたときビット異方性軸に対して 45° で開始し、次に書き込みビット電流 70 がオンにされるとビット異方性軸に平行となるように移動する。この例は、通常の磁界印加シーケンスと同様である。しかし、ここで書き込みワード電流 60 と書き込みビット電流 70 がほぼ同時にオフになり、磁界の方向がそれ以上回転しなくなる。したがって、印加される磁界は、書き込みワード電流 60 と書き込みビット電流 70 の両方がオンになった状態で、結果として生じる磁界モーメントベクトル 40 がその困難軸の不安定点を既に通過しているように十分に大きくなければならない。この場合、磁界の方向がここでは、以前のような 90° ではなく 45° しか回転されないため、トグル書き込みモード事象が生じる可能性は低い。下降時間  $t_3$  および  $t_4$  がほぼ同時であることの利点は、この場合、磁界上昇時間  $t_1$  および  $t_2$  の順番にさらなる制約がないことである。したがって、磁界は任意の順番でオンにするか、あるいはほぼ同時とすることもできる。

40

50

## 【0035】

上述の書き込み方法は、時間  $t_2$  と時間  $t_3$  の間に書き込みワード電流 60 と書き込みビット電流 70 の両方がオンにされた M R A M 装置のみで状態がスイッチングするため、非常に選択的である。この特徴を図 9 および図 10 に示す。図 9 は、書き込みワード電流 60 をオンにせず書き込みビット電流 70 をオンにしたときのパルスシーケンス 100 を示す。図 10 は、M R A M 装置 10 の状態の対応する挙動を示す。時間  $t_0$  において、磁気モーメントベクトル 53 および 57、ならびに結果として生じる磁気モーメントベクトル 40 は、図 2 において説明したように配向される。パルスシーケンス 100 において、書き込みビット電流 70 は時間  $t_1$  においてオンにされる。この間、 $H_B$  90 により、結果として生じる磁気モーメントベクトル 40 が正の x 方向に方向付けられる。

10

## 【0036】

書き込みワード電流 60 は決してオンに切り換えられないため、結果として生じる磁気モーメントベクトル 53 および 57 は決して、異方性困難軸の不安定点を通過して回転しない。結果として、磁気モーメントベクトル 53 および 57 は、書き込みビット電流 70 が時間  $t_3$  においてオフにされると、最も近い優先方向に再配向するようになり、この場合これは、時間  $t_0$  における最初の方向である。したがって、M R A M 装置 10 の状態はスイッチングされない。書き込みワード電流 60 を上記と同様の時間にオンにし、書き込みビット電流 70 をオンにしない場合も同じ結果が得られることが理解されるであろう。この特徴により、アレイ中の 1 つの M R A M 装置のみが確実にスイッチングされ、他の装置はその最初の状態に留まる。結果として、意図せぬスイッチングが防止され、ビット誤り率が最小化される。

20

## 【0037】

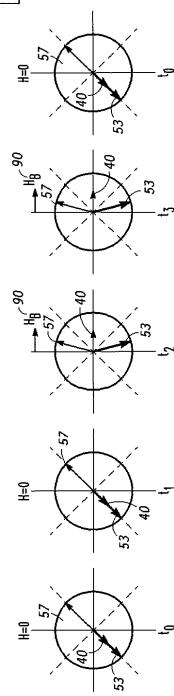

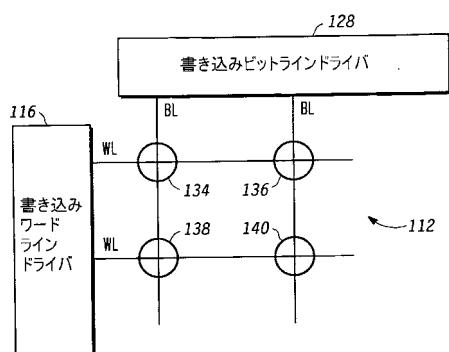

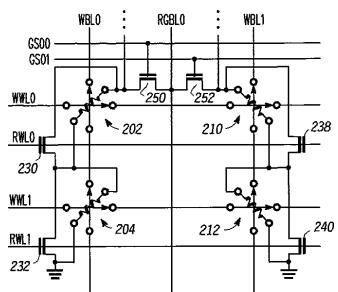

図 11 には、メモリアレイ 112、書き込みワードデコーダ 114、書き込みワード線ドライバ 116、読み取りワードデコーダ 118、読み取りワード線ドライバ 120、1 つまたは複数のセンス増幅器 122、読み取りビットデコーダ 124、書き込みビットデコーダ 126、書き込みビットドライバ 128、比較器 130、および出力ドライバ 132 を備えるメモリ 110 を示す。これらの要素は複数の線によってともに結合される。例えば、読み取りビットデコーダ 124 は、複数のアドレス信号からなる列アドレスを受け取る。メモリアレイ 112 は、トグル動作によりスイッチングすることができるメモリセルのアレイである。メモリアレイ 112 のメモリセルの一部分が図 14 に示すメモリアレイ 200 であり、これは、書き込みが 45° の角度の 4 段階で 180° に達するまで行われるという点で、図 1 のメモリアレイ 3 について説明した方法で書き込まれる M R A M セルアレイである。この特に好ましいセルアレイにおいて、書き込み動作用と読み取り動作用に別個のワード線およびビット線がある。

30

## 【0038】

読み取りワードデコーダ 118 は、行アドレスを受け取り、読み取りワード線ドライバ 120 に結合され、これがさらにメモリアレイ 112 に結合される。読み取りのために、読み取りワードデコーダ 118 が行アドレスに基づいてメモリアレイ 112 の読み取りワード線を選択する。選択されたワード線は読み取り線ドライバ 120 によって駆動される。列アドレスを受け取り、センス増幅器 122 とメモリアレイ 112 の間に結合される読み取りビットデコーダ 124 は、読み取りビットデコーダ 124 から列アドレスに基づいて、メモリアレイ 112 から読み取りビット線を選択し、これをセンス増幅器 122 に結合させる。センス増幅器 122 は、論理状態を検出し、これを出力ドライバ 132 および比較器 130 に結合する。出力ドライバ 132 は、読み取りのために、データ出力信号 D O を供給する。書き込み動作のために、比較器 130 は、センス増幅器 122 によって供給される選択されたセルの論理状態を、データ入力部 (data in) によって供給される書き込むべき所望の論理状態と比較する。

40

## 【0039】

書き込みワードデコーダ 114 は、行アドレスを受け取り、書き込みワード線ドライバ 116 に結合され、これがさらにメモリアレイ 112 に結合される。書き込みのために、

50

書き込みワードデコーダ114は、行アドレスに基づいてメモリアレイ112の書き込みワード線を選択し、次に書き込みワード線ドライバがその選択された書き込みワード線を駆動する。書き込みビットデコーダ126は、列アドレスを受け取り、書き込みビットドライバ128に結合され、これがメモリアレイ112に結合される。書き込みビットデコーダ126は、列アドレスに基づいて書き込みビット線を選択し、次に書き込みビットドライバ128がその選択された書き込みビット線を駆動することにより、選択されたセルの状態をトグルする。

【0040】

メモリアレイ112はトグルメモリであるため、書き込みトグル動作は、選択されたセルに対して所望の結果として生じる論理状態を達成するためにセルの論理状態をフリップする必要がある場合にのみ完了する。したがって、比較器130は、選択されたセルに対する読み取り動作の出力をセンス増幅器122から受け取り、選択されたセルが既に所望の論理状態を有するかを判定する。行および列アドレスによって決まる選択されたセルが所望の論理状態を有する場合、書き込み動作を終了する。選択されたセルの論理状態が所望の状態と異なる場合、比較器は書き込みビットドライバ128に、書き込みを続けるよう指示し、選択された書き込みビット線用の書き込みビットドライバが、選択された書き込みビット線を駆動する。

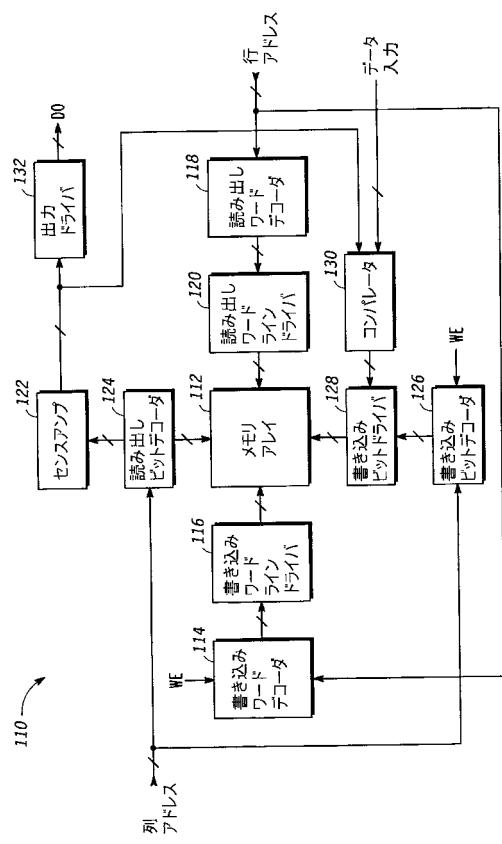

【0041】

図12には、図11のメモリ110の、書き込みワード線WLに結合された書き込みワード線ドライバ116、書き込みビット線BLに結合された書き込みビットドライバ128、および書き込みビット線BLと書き込みワード線WLの交点に結合されたセル134、136、138、および140を含む一部を示す。書き込みを行うには、十分な時間のあいだ、選択された書き込みビット線には電流が流れていらない状態で、選択されたワード線WLに電流を供給し、メモリセルの選択された書き込みワード線に沿って第1の角度変化を生じる。選択された書き込みワード線に電流が依然として流れている間に、選択された書き込みビット線に電流を流して、選択されたメモリセルに第2の角度変化を生じる。電流が流れている書き込みビット線と書き込みワード線の交点のみで、この第2の角度変化が生じる。書き込みビット線に電流が依然として流れている間に、選択された書き込みワード線に流れる電流を止め、選択されたメモリセルに第3の角度変化を生じる。選択された書き込みビット線と選択された書き込みワード線の交点のみで、この第3の変化が生じる。選択されたメモリセルの第4の角度変化は、選択された書き込みビット線に流れる電流を止めると生じる。

【0042】

図13のタイミング図を参照してメモリ110の書き込み動作をさらに説明する。図示のような行または列アドレスの変化により、図13に示すように読み取りワード線WL Aをイネーブルすることによって、読み取り動作と書き込みトグル動作の両方が開始される。論理状態をフリップさせる必要があると判定されるまで書き込みは実行できないが、それでもなお、センス増幅器がその出力を供給し、かつ比較器が論理状態をフリップする必要があるかを判定する前に書き込みワード線がイネーブルされることによって示されるように、書き込みサイクルを開始することができる。書き込みワード線をイネーブルする（書き込みワード線に電流を流す）ことで、選択されたセルならびに選択された書き込みワード線に沿った全てのセルにおいて第1の角度変化が生じるが、書き込みビット線をイネーブルせずに電流を止めた場合、この変化は反転する。

【0043】

したがって、単に電流を取り除くことによって第1の角度変化が反転されるため、選択された書き込みワード線は、比較器が判定を行う前にイネーブルされることがある。これは、選択された書き込みワード線上の全てのセルが第1の角度変化を受け、1つを除く全てが選択されないため、当てはまらなければならない。しかし、選択されたセルのみが第2の角度変化を受け、このことは、書き込みビット線がイネーブルされると起こる。これは、論理状態の変化が望ましいという判定を比較器が行った後に起こるものとして示さ

10

20

30

40

50

れる。第1の角度変化は0°から45°へのものとして示され、第2の変化は45°から90°へのものである。第3の角度変化は、書き込みワード線がディセーブルされる（電流が止まる）と起こるものとして示される。これは、90°から135°へのものとして示される。図示される最後の角度変化は第4の角度変化であり、書き込みビット線がディセーブルされると起こる。この角度変化は135°から180°へのものとして示される。

#### 【0044】

これはまた、別のサイクルを開始させる次のアドレス変化の後に最後の書き込み段階を継続できることを示す。サイクルの開始は、それが書き込みサイクルであっても、常に読み取りとともに開始する。アドレスAがアドレスBに変化し、読み取りワード線Bを選択させる。これは、前に選択されたセルの書き込みを妨害しない。これは読み取りワード線の変化を示すが、アドレスが列のみ変化し、選択された読み取りワード線が変化しない場合でも、継続する電流の流れが書き込みの完了に悪影響を及ぼすことはない。全てのサイクルはいずれにせよ読み取り動作で開始するため、サイクルの開始時に書き込みイネーブルがアクティブである必要はないことにも留意されたい。しかし、書き込みビット線をアクティブにするには、書き込みイネーブル信号が十分早くアクティブでなければならない。

#### 【0045】

選択されている単一セルに関して説明を行ってきたが、これは理解を容易にするためである。実際には、通常いくつかのセルが選択されることになり、これを図11に、複数の信号線である要素間の信号接続によって示す。したがって、例えば、メモリ110が×16メモリである場合、比較器130は実際には16回の別個の比較を、選択されたセルにつき1回ずつ行う。16回の比較のうち、不一致を示す比較のみが、それらの不一致のある選択されたセルの書き込み動作を生じる。選択されたセルのうち結果的に一致したものはフリップされない。

#### 【0046】

図14には、メモリアレイ200の一部、ならびにまとまってメモリコア201を形成する複数のドライバ、デコーダ、および検知ブロックを示す。このメモリアレイ200の部分は、MRAM装置202、204、206、208、210、212、213、214、216、218、220、222、224、226、227、および228を備える。これらのMRAM装置はそれぞれ3つの電流経路を有する。これら3つの経路のうち、互いに直交するものとして示される第1の電流経路および第2の電流経路は書き込み経路を表す。これらの2つの経路は、図12および図13に示される、セルの論理状態をスイッチングさせる信号を運ぶ。45度の角度の抵抗器として示される第3の電流経路は、2つの可能な抵抗状態の一方にプログラムされる磁気抵抗トンネル接合部を通る読み取り電流経路を表す。メモリアレイ200はさらに、対応するMRAM装置202、204、206、208、210、212、213、214、216、218、220、222、224、226、227、および228の読み取り電流経路である第3の電流経路とそれ直列につながれた選択トランジスタ230、232、234、236、238、240、242、244、260、262、264、266、268、270、272、および274を備える。この選択トランジスタの接続は、これらのトランジスタの、第3の電流経路に結合された1つの電流電極と、アース(VSS)に結合された第2の電流電極により行われる。選択トランジスタ装置とMRAM装置の各組み合わせがメモリセルを構成する。

#### 【0047】

メモリコア201は、MRAM装置の第1の電流経路を通って延在する書き込みワード線WWL0、WWL1、WWL2、およびWWL3を備える。WWL0は、MRAM装置202、210、216、および224を通って延在する。WWL1は、MRAM装置204、212、218、および226を通って延在する。WWL2は、MRAM装置206、213、220、および227を通って延在する。WWL3は、MRAM装置208

10

20

30

40

50

、214、222、および228を通って延在する。メモリアレイ200はさらに、MRAM装置の第2の電流経路を通って延在する書き込みビット線WBL0、WBL1、WBL2、およびWBL3を備える。WBL0は、MRAM装置202、204、206、および208を通って延在する。WBL1は、MRAM装置210、212、213、および214を通って延在する。WBL2は、MRAM装置216、218、220、および222を通って延在する。WBL3は、MRAM装置224、226、227、および228を通って延在する。さらになお、メモリアレイ200は、選択トランジスタのゲートに結合される読み取りワード線RWL0、RWL1、RWL2、およびRWL3を備える。RWL0は、選択トランジスタ230、238、260、および268に結合される。RWL1は、選択トランジスタ232、240、262、および270に結合される。RWL2は、選択トランジスタ234、242、264、および272に結合される。RWL3は、選択トランジスタ236、244、266、および274に結合される。メモリアレイ200はまた、読み取りグローバルビット線RGBL0およびRGBL1ならびにグループ選択線GS0、GS1、GS2、およびGS3を備える。

#### 【0048】

メモリアレイ200はさらに、メモリセルのグループを読み取りグローバルビット線に結合するためのグループ選択トランジスタ250、252、254、256、276、278、280、および282を備える。さらにメモリアレイ200を構成するものとして、ローカルビット線251、253、255、257、277、279、281、および283があり、そのそれぞれが、それらのグループのMRAM装置の第3の電流経路に結合される。つまり、これらのローカルビット線が各グループにつき1本ある。

#### 【0049】

トランジスタ250および252は、ともに結合されるとともに読み取りグローバルビット線RGBL0に結合された第1の電流電極を有する。トランジスタ254および256は、ともに結合されるとともに読み取りグローバルビット線RGBL0に結合された第1の電流電極を有する。トランジスタ276および278は、ともに結合されるとともに読み取りグローバルビット線RGBL1に結合された第1の電流電極を有する。トランジスタ280および282は、ともに結合されるとともに読み取りグローバルビット線RGBL1に結合された第1の電流電極を有する。トランジスタ250、252、254、256、276、278、280、および282はそれぞれ、ローカルビット線251、253、255、257、277、279、281、および283に結合された第2の電流電極を有する。ローカルビット線251、253、255、257、277、279、281、および283は、MRAM装置202および204、206および208、210および212、213および214、216および218、220および222、224および226、ならびに227および228の第3の電流経路にそれぞれ結合される。グループ選択線GS0はグループ選択トランジスタ250および276に結合される。グループ選択線GS1はグループ選択トランジスタ252および278に結合される。グループ選択線GS2はグループ選択トランジスタ254および280に結合される。グループ選択線GS3はグループ選択トランジスタ256および282に結合される。

#### 【0050】

メモリアレイ200に加えて、メモリコア201は、書き込み列デコーダ/ドライバ283、284、285、および286、書き込み行デコーダ/ドライバ287、289、291、および293、読み取り行デコーダ/ドライバ288、290、292、および294、ならびに読み取り列デコーダ/センス增幅器295および296を備える。書き込み列デコーダ/ドライバ283、284、285、および286は、書き込みビット線WBL0、WBL1、WBL2、およびWBL3にそれぞれ接続される。書き込み行デコーダ/ドライバ287、289、291、および293は、書き込みワード線WWL0、WWL1、WWL2、およびWWL3にそれぞれ結合される。読み取り行デコーダ/ドライバ288、290、292、および294は、読み取りワード線RWL0、RWL1、RWL2、およびRWL3にそれぞれ結合される。読み取り列デコーダ/センス增幅器2

96 および 295 は、読み取りグローバルビット線 R G B L 0 および R G B L 1 にそれぞれ結合される。

#### 【0051】

動作中、M R A M 装置（例えば M R A M 装置 202）は、選択された書き込みワード線（例えば W W L 0）および選択された書き込みビット線（例えばこの例では W B L 0）に電流を印加して、メモリの状態をトグルすることによって書き込まれる。状態はまた、メモリセルがトグルセルではなく直接書き込みセルである場合、W W L 0 および W B L 0 により直接書き込むこともできる。全ての M R A M 装置は、特定の M R A M 装置の書き込みワード線および書き込みビット線に電流を流すことによって選択される。M R A M 装置（例えば M R A M 装置 202）の状態は、その対応する選択トランジスタ（例えばトランジスタ 230）のゲートに、読み取りワード線 R W L 0 により十分な電圧を印加し、対応するグループトランジスタ（例えばトランジスタ 250）のゲートに、グループ選択線 G S 0 により十分な電圧を印加し、選択された M R A M 装置（この例では M R A M 装置 202）の状態を、読み取りグローバルビット線 R G B L 0 により、列デコーダ／センス増幅器 296 によって検知することによって読み取られる。1つのグループは、第3の電流経路を共通して接続された複数の M R A M 装置で構成される。よって、セル自体が読み取りグローバルビット線に加える静電容量は、そのグループ内にあるセルに限定される。また、トランジスタ 250 および 252 は電流電極が共通して接続されており、ゲートは異なる選択線に結合される。これは、グループを折り返して（fold）グローバルビット線を共有させ、グループ間の選択を別個のグローバル選択線によって達成させる作用をもたらす。したがって、行方向に線が追加されており、列方向のほうが少ない。利点は、行方向における線の増加が各セルグループにつき1本であることである。そのグループが、好ましい量であると考えられる 32 である場合、セル 32 個分の距離にさらなるグローバル選択線がある。折り返さない場合、読み取りグローバルビット線が、折り返した場合の2列毎に1本ではなく列毎に1本ある。したがって、折り返さない場合の効果としては、折り返した場合と比較して、セル 2 つ分の幅の読み取りグローバルビット線が2列毎に1本増える。したがって、このトレードオフは明らかに、折り返したビット線が有利である。この空間的な利点は、線のサイズを大きくして抵抗を減らすため、メモリコアのサイズを小さくするため、あるいはその2つの組み合わせのために用いることができる。

#### 【0052】

さらに、書き込み線を読み取り線と分離することによって、書き込み線の一端を電源 V D D に直接接続し、読み取りと書き込みが同一線を共用する場合に必要とされる第2の電流スイッチを排除することができる。したがって、書き込みドライバのための全面積が小さくなり、メモリコアの平均ビットサイズが小さくなる。また、読み取りと書き込みの間で1本の線をスイッチングする必要性をなくすことにより、読み取り回路を損傷する危険性を負うことなく、書き込み電圧を性能について最適化することができる。さらに、選択トランジスタは書き込み電圧を受け取らないため、これらの選択トランジスタを、書き込みレベルの電圧を受け取らなくてよいことから遙かに小さなサイズにすることができる。これにより、メモリセルのサイズが小さくなる。これは特に、トランジスタを異なる電圧要件に合わせて別々に作製することが一般的である場合に顕著である。

#### 【0053】

図 15 には、M R A M 装置 202 およびトランジスタ 230 からなるメモリセルの断面を示す。これは、図 14 の機構を利用するように構成された M R A M 装置の共通の要素を示す。M R A M 技術の通常の応用において、M R A M 装置は、拡張ロジックを有する回路（例えばマイクロプロセッサ）上に存在する。このような場合、論理設計に対応する金属階層がいくつもあり、M R A M 装置の記憶エレメントは、これらの金属層が形成されてから製造される。これは、通常のトンネル接合部では、劣化することなく約 400 セルシウス度より高い温度を処理できないことによるものである。

#### 【0054】

M R A M 装置 202 は、トンネル接合部 300、相互接続部 306、相互接続部 304

10

20

30

40

50

、ならびに書き込み電流経路 314 および 302 を備える。相互接続部 304 はローカルビット線 251 でもある。トランジスタ 230 は、ソース 324、ドレイン 322、およびゲート 323 を備える。トランジスタ 230 のドレイン 322 は、ロジックとして使用するために金属層として形成される相互接続部 318、相互接続部 308、相互接続部 310、および相互接続部 312 を介して MRAM 装置 202 に接続される。これらの金属相互接続層は、よく知られているように、バイアを介してともに接続される。書き込み電流経路 314 は、相互接続部 318 と同じ金属層に形成される。ゲート 323 は、相互接続部 320 に周期的に接続される読み取りワード線 RWL0 の一部である。相互接続部 320 の使用により、RWL0 の抵抗が小さくなる。これは、ポリシリコンの比較的高い抵抗を防ぐためのよく見られるストラッピング技法である。

10

#### 【0055】

図 16 には、図 15 に示すような MRAM 装置 202 およびトランジスタ 230 の断面を示す。この断面は、MRAM 装置 210 およびトランジスタ 238 を含むように拡張されている。これは、相互接続部 310 と同じ相互接続階層に読み取りグローバルビット線 RGBL0 を示す。トンネル接合部 300 および WWL0 は断面線とずれているため、図 16 中には存在しないことに留意されたい。図 16 中に存在する MRAM 装置 210 の部分は書き込みビット線 WBL1 である。MRAM 装置 202 と同様に、MRAM 装置 210 の第 3 の電流経路は、相互接続部 340、相互接続部 338、相互接続部 336、相互接続部 334、および相互接続部 330 によってトランジスタ 232 に接続される。相互接続部 330 および 306 はそれぞれ、MRAM 装置 210 および 202 のトンネル接合部への直接接続を行う。これらの断面は、この機構が、特別な処理を必要とする異常な構造を必要とすることなく作製できることを示す。

20

#### 【0056】

図 17 には、図 14 に示すものの代替形態の一部を示す。この場合、各グループのメモリセルは直列メモリとして配置される。隣接ビットセルの複数のグループはそれぞれ、基準電位 (reference) に直列接続される。この場合、基準電位はアースである。この代替形態にはローカルビット線がない。同様の特徴に対して同様の装置数が維持される。

#### 【0057】

例示目的で選択される本明細書中の実施形態に対する様々な変更および修正を当業者であれば容易に思い付くであろう。そのような修正および変形が本発明の精神から逸脱しない範囲において、それらの修正および変形は、添付の特許請求の範囲の公正な解釈のみによって評価される本発明の範囲に含まれることが意図される。

30

#### 【図面の簡単な説明】

#### 【0058】

【図 1】磁気抵抗ランダムアクセスメモリ装置の概略を示す断面図。

【図 2】ワード線およびビット線を有する磁気抵抗ランダムアクセスメモリ装置の略平面図。

【図 3】磁気抵抗ランダムアクセスメモリ装置において直接書き込みモードまたはトグル書き込みモードを生じる磁界の大きさの組み合わせのシミュレーションを示すグラフ。

【図 4】ワード電流およびビット電流の、両方がオンになった場合のタイミング図を示すグラフ。

40

【図 5】「1」を「0」に書き換える場合のトグル書き込みモードの磁気抵抗ランダムアクセスメモリ装置の磁気モーメントベクトルの回転を示す概念図。

【図 6】「0」を「1」に書き換える場合のトグル書き込みモードの磁気抵抗ランダムアクセスメモリ装置の磁気モーメントベクトルの回転を示す概念図。

【図 7】「1」を「0」に書き換える場合の直接書き込みモードの磁気抵抗ランダムアクセスメモリ装置の磁気モーメントベクトルの回転を示す概念図。

【図 8】既に「0」である状態に「0」を書き込んでいる場合の直接書き込みモードの磁気抵抗ランダムアクセスメモリ装置の磁気モーメントベクトルの回転を示す概念図。

【図 9】ビット電流のみをオンにした場合のワード電流およびビット電流のタイミング図

50

を示すグラフ。

【図10】ピット電流のみをオンにした場合の磁気抵抗ランダムアクセスメモリ装置の磁気モーメントベクトルの回転を示す概念図。

【図11】本発明の1実施形態によるトグルメモリのブロック図。

【図12】図11のメモリの一部のより詳細なブロック図。

【図13】図11のメモリの動作を理解する上で役立つタイミング図。

【図14】図11のメモリの一部の、本発明の機構の1実施形態を示す回路図。

【図15】図14の機構の実施形態において用いられるメモリセルの第1の断面を示す断面図。

【図16】図15のメモリセルの第2の断面を示す断面図。

【図17】図14の回路図に対する変形を示す回路図。

10

〔 図 1 〕

【図3】

〔 2 〕

【图4】

FIG. 4

【図 9】

FIG.9

【図 10】

FIG.10

【図 11】

【図 12】

【図 13】

【 図 1 4 】

【 図 1 5 】

FIG.15

【図16】

FIG. 16

【 図 1 7 】

FIG. 17

---

フロントページの続き

(72)発明者 ナハス、ジョセフ ジェイ .

アメリカ合衆国 78731 テキサス州 オースティン ジェントル ブリーズ テラス 58

24

(72)発明者 アンドレ、トーマス ダブリュ .

アメリカ合衆国 78732 テキサス州 オースティン ラティマー ドライブ 3508

(72)発明者 スプラマニアン、チトラ ケイ .

アメリカ合衆国 78750 テキサス州 オースティン ピックフェア ドライブ 10601

(72)発明者 ガーニ、プラッドリー ジェイ .

アメリカ合衆国 78735 テキサス州 オースティン イーグル フェザー ドライブ 45

32

審査官 須原 宏光

(56)参考文献 特公昭50-033623(JP, B1)

特表2004-528665(JP, A)

(58)調査した分野(Int.Cl., DB名)

G11C 11/15