(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5752877号

(P5752877)

(45) 発行日 平成27年7月22日(2015.7.22)

(24) 登録日 平成27年5月29日(2015.5.29)

|                       |                |

|-----------------------|----------------|

| (51) Int.Cl.          | F 1            |

| GO2F 1/1343 (2006.01) | GO2F 1/1343    |

| GO2F 1/1368 (2006.01) | GO2F 1/1368    |

| GO2F 1/133 (2006.01)  | GO2F 1/133 575 |

請求項の数 16 (全 18 頁)

|              |                               |

|--------------|-------------------------------|

| (21) 出願番号    | 特願2009-116545 (P2009-116545)  |

| (22) 出願日     | 平成21年5月13日 (2009.5.13)        |

| (65) 公開番号    | 特開2009-276767 (P2009-276767A) |

| (43) 公開日     | 平成21年11月26日 (2009.11.26)      |

| 審査請求日        | 平成24年3月22日 (2012.3.22)        |

| (31) 優先権主張番号 | 10-2008-0044140               |

| (32) 優先日     | 平成20年5月13日 (2008.5.13)        |

| (33) 優先権主張国  | 韓国 (KR)                       |

|           |                                                                                                                                                        |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| (73) 特許権者 | 512187343<br>三星ディスプレイ株式会社<br>Samsung Display Co., Ltd.<br>大韓民国京畿道龍仁市器興区三星二路95<br>95, Samsung 2 Ro, Gih<br>eung-Gu, Yongin-City<br>, Gyeonggi-Do, Korea |

| (74) 代理人  | 100121382<br>弁理士 山下 託嗣                                                                                                                                 |

| (72) 発明者  | 金 東 奎<br>大韓民国京畿道龍仁市豊徳川2洞三星5次<br>アパート523棟1305号                                                                                                          |

最終頁に続く

(54) 【発明の名称】アレイ基板、アレイ基板を有する表示装置、及び表示装置の駆動方法

## (57) 【特許請求の範囲】

## 【請求項 1】

液晶表示装置のアレイ基板であって、

ベース基板と、

前記ベース基板上で第1方向へ延長されたゲート線と、

前記ベース基板上で前記第1方向と交差する第2方向へ延長されたデータ線と、

各前記ゲート線及び各前記データ線に接続されるスイッチング素子と、

前記スイッチング素子に電気的に接続された画素電極を含み、

前記スイッチング素子及び前記画素電極は、単位画素を形成し、

前記画素電極は、

第1スリットパターンを有する第1サブ画素電極と、第2スリットパターンを有して前記第1サブ画素電極と隣接する第2サブ画素電極を含む画素電極を有し、

前記第1スリットパターン及び前記第2スリットパターンは、前記スイッチング素子と電気的に接続され、

前記第1スリットパターンは前記第1方向及び前記第2方向と交差する第3方向に沿って配置され、

前記第2スリットパターンは前記第3方向と交差する第4方向に沿って配置され、

前記画素電極は、第2方向に沿って交互に第1画素電圧と第2画素電圧が印加され、

前記第1画素電圧は、前記単位画素によって表示される画像の階調より高いレベルの画素電圧であり、

前記第2画素電圧は、前記単位画素によって表示される画像の階調より低いレベルの画素電圧であり、

互いに隣接する4つの単位画素が2行2列を有するマトリックスタイプに配置されて画素ユニットを形成し、前記画素ユニットは、8つのドメインを形成する、ことを特徴とするアレイ基板。

【請求項2】

前記第2方向に沿って前記ベース基板上に配置された縦電極棒をさらに含み、

前記第1スリットパターンは前記第3方向に沿って延長されて前記縦電極棒に接続され、前記第2スリットパターンは前記第4方向へ延長されて前記縦電極棒に接続されることを特徴とする請求項1に記載のアレイ基板。

10

【請求項3】

前記ゲート線付近で前記縦電極棒と交差するように配置され、前記スイッチング素子の出力電極と電気的に接続された横電極棒をさらに含むことを特徴とする請求項2に記載のアレイ基板。

【請求項4】

前記第1スリットパターンと前記第2スリットパターンは各々前記第1スリット方向及び前記第2方向に沿って順次に単位画素に交互に配置されることを特徴とする請求項2に記載のアレイ基板。

【請求項5】

液晶表示装置のアレイ基板であって、

20

ベース基板と、

前記ベース基板上で第1方向へ延長されたゲート線と、

前記ベース基板上で前記第1方向と交差する第2方向へ延長されたデータ線と、

各前記ゲート線及び各前記データ線に接続されるスイッチング素子と、

前記スイッチング素子に電気的に接続された画素電極を含み、

前記スイッチング素子及び前記画素電極は単位画素を形成し、

第1単位画素は第1スイッチング素子及び第1画素電極を含み、

前記第1単位画素と隣り合った第2単位画素は第2スイッチング素子及び第2画素電極を含み、

前記第1画素電極は、前記第1方向及び前記第2方向と交差する第3方向に沿って配置されて、前記第1スイッチング素子に電気的に連結される第1スリットパターンを含み、

30

前記第2画素電極は前記第3方向と交差する第4方向に沿って配置されて、前記第2スイッチング素子に電気的に連結される第2スリットパターンを含み、

前記画素電極は、第2方向に沿って交互に第1画素電圧と第2画素電圧が印加され、

前記第1画素電圧は、前記単位画素によって表示される画像の階調より高いレベルの画素電圧であり、

前記第2画素電圧は、前記単位画素によって表示される画像の階調より低いレベルの画素電圧であり、

互いに隣接する4つの単位画素が2行2列に配列されて画素ユニットを形成し、前記画素ユニットは、4つのドメインを形成することを特徴とするアレイ基板。

40

【請求項6】

前記第2方向に沿って前記ベース基板上に配置された縦電極棒をさらに含み、

前記第1スリットパターンと前記第2スリットパターンのうち、何れかの1つは前記第3方向と前記第4方向のうち、何れかの1つに沿って延長されて前記縦電極棒に接続されることを特徴とする請求項5に記載のアレイ基板。

【請求項7】

複数の縦電極棒をさらに含み、縦電極棒のうち、第1縦電極棒はデータラインの左側周辺に隣接するように前記マトリックスの第1行に配置され、

縦電極棒のうち、第2縦電極棒はデータラインの右側周辺に隣接するように前記マトリックスの第2行に配置され、

50

前記第1スリットパターンと前記第2スリットパターンとは前記行方向及び前記列方向各々に沿って交互に配置されることを特徴とする請求項6に記載のアレイ基板。

【請求項8】

ベース基板、前記ベース基板上で第1方向に延長されたゲート線、前記ベース基板上で前記第1方向と交差する第2方向に延長されたデータ線、各前記ゲート線及び各前記データ線を接続するスイッチング素子、前記スイッチング素子に電気的に接続された画素電極を含むアレイ基板と、

前記画素電極と対向する共通電極を含む対向基板と、

前記アレイ基板と前記対向基板との間で垂直に配向される液晶層と、

前記単位画素に表示される画像の階調より高いレベルの第1画素電圧及び低いレベルの第2画素電圧を交互に印加する駆動装置と、

を有し、

前記スイッチング素子及び前記画素電極は、単位画素を形成し、

前記画素電極は、

第1スリットパターンを有する第1サブ画素電極と、第2スリットパターンを有して、前記第1サブ画素電極と隣接する第2サブ画素電極を含む画素電極を有し、

前記第1スリットパターン及び前記第2スリットパターンは、前記スイッチング素子と電気的に接続され、

前記第1スリットパターンは前記第1方向及び前記第2方向と交差する第3方向に沿って配置され、

前記第2スリットパターンは前記第3方向と交差する第4方向に沿って配置され、

前記駆動装置は、第2方向に沿って交互に前記第1画素電圧と前記第2画素電圧を印加し、

互いに隣接する4つの単位画素が2行2列を有するマトリックスタイプに配置されて画素ユニットを形成し、前記画素ユニットは、8つのドメインを形成することを特徴とする液晶表示装置。

【請求項9】

前記スリットパターンは、前記第1スリットパターン及び前記第2スリットパターンの境界に配置された縦電極棒をさらに含み、

前記第1スリットパターン及び第2スリットパターンは、液晶の方向子を前記縦電極棒に向かって整列することを特徴とする請求項8に記載の液晶表示装置。

【請求項10】

前記第1スリットパターン及び前記第2スリットパターンのスリットの幅は、前記液晶層の厚さより小さいことを特徴とする請求項9に記載の液晶表示装置。

【請求項11】

1行1列及び2行2列の単位画素では前記行方向に前記第2スリットパターン及び第1スリットパターンの順序に配置し、

1行2列及び2行1列の単位画素では前記行方向に前記第1スリットパターン及び第2スリットパターンの順序に配置したことを特徴とする請求項9に記載の液晶表示装置。

【請求項12】

前記駆動装置が前記1行の単位画素を前記第1画素電圧でドット反転駆動し、前記2行の単位画素を前記第2画素電圧でドット反転駆動して前記画像の階調を表示することを特徴とする請求項11に記載の液晶表示装置。

【請求項13】

前記対向基板は、各前記単位画素と対応して前記共通電極上に形成されたカラーフィルタをさらに含むことを特徴とする請求項8に記載の液晶表示装置。

【請求項14】

前記カラーフィルタは、前記行方向に各前記単位画素と対応するように配置された赤色フィルタ、緑色フィルタ、及び青色フィルタを含むことを特徴とする請求項13に記載の液晶表示装置。

10

20

30

40

50

## 【請求項 15】

ベース基板、前記ベース基板上で第1方向に延長されたゲート線、前記ベース基板上で前記第1方向と交差する第2方向に延長されたデータ線、各前記ゲート線及び各前記データ線を接続するスイッチング素子、前記スイッチング素子に電気的に接続された画素電極を含むアレイ基板と、

前記画素電極と対向する共通電極を含む対向基板と、

前記アレイ基板と前記対向基板との間で垂直に配向される液晶層と、

を有し、

前記スイッチング素子及び前記画素電極は、単位画素を形成して、互いに隣接する4つの単位画素が2行2列に配列されて画素ユニットを形成し、

10

前記各画素電極に形成された前記スリットパターンは、前記第1方向及び前記第2方向と交差する第3方向に配列された第1スリットパターンまたは前記第3方向と交差する第4方向に配列された第2スリットパターンのうち、選択されたいずれか1つを含み、

前記画素電極は、列方向に沿って交互に第1画素電圧と第2画素電圧が印加され、

前記第1画素電圧は、前記単位画素によって表示される画像の階調より高いレベルの画素電圧であり、

前記第2画素電圧は、前記単位画素によって表示される画像の階調より低いレベルの画素電圧であり、

前記画素ユニットは、4つのドメインを形成することを特徴とする液晶表示装置。

## 【請求項 16】

20

第1スリットパターンを有する第1サブ画素電極、第2スリットパターンを有して前記第1サブ画素電極と隣接する第2サブ画素電極を含み、前記第1サブ画素電極と前記第2サブ画素電極とが第1の位置関係にある第1画素電極及び第2画素電極と、前記第1サブ画素電極と前記第2サブ画素電極とを含み、前記第1サブ画素電極と前記第2サブ画素電極とが前記第1の位置関係とは異なる第2の位置関係にある第3画素電極及び第4画素電極とを含むアレイ基板、対向基板、及び前記アレイ基板と対向基板との間に介在された液晶層を含み、前記第1乃至第4画素電極を含む4つの画素が2行2列を有するマトリックスタイルに配置されて画素ユニットを形成された液晶表示装置の駆動方法であって、

前記第1スリットパターンは行方向及び列方向と交差する第3方向に沿って配置され、

前記第2スリットパターンは前記第3方向と交差する第4方向に沿って配置され、

30

前記第1画素電極に画像の階調電圧より高い第1画素電圧を印加する第1段階と、

前記第3画素電極に前記画像の階調電圧より低い第2画素電圧を印加する第2段階と、

前記第2画素電極に前記第2画素電圧を印加する第3段階と、

前記第4画素電極に前記第1画素電圧を印加する第4段階と、

を含み、

前記画素ユニットは、前記第1段階乃至前記第4段階により、8つのドメインを形成することを特徴とする液晶表示装置の駆動方法。

## 【発明の詳細な説明】

## 【技術分野】

40

## 【0001】

本発明は、アレイ基板、これを有する表示装置、及びこれの駆動方法に関する。より詳しくはスリットパターンが形成された電極に垂直配向された液晶を制御するアレイ基板、アレイ基板を有する表示装置、及び表示装置の駆動方法に関する。

## 【背景技術】

## 【0002】

一般的に、液晶表示装置は現在最も広く使われている平板表示装置の1つで、電界生成電極が形成されている2枚の表示板とその間に挿入されている液晶層からなり、電極に電圧を印加して液晶層の液晶分子を再配列させることによって液晶層を通過する光の透過率を調節する表示装置である。

50

## 【0003】

液晶表示装置は、2つの表示板と前記2つの基板各々に具備される電界生成電極とを含む。1つの表示板には複数の画素電極が行列形態で配列されており、他の表示板には1つの共通電極が全面的に形成されている。前記液晶表示装置の画像表示は各画素電極に別途の電圧を印加することによって遂行される。これのために前記画素電極に印加される電圧をスイッチングするための薄膜トランジスタが各画素電極に接続され、前記薄膜トランジスタを制御するための信号を伝達するゲート線と前記画素電極に印加される電圧を伝達するデータ線が表示板に形成される。

## 【0004】

液晶表示装置は他の液晶表示装置に比べて視野角が狭い。このような短所を克服するために視野角を広げる多様な技術が開発されている。その中でも、液晶分子を上下基板に対して垂直に配向し、画素電極とその対向電極である共通電極に一定のスリットパターンを形成するか或いは突起パターンを形成して画素を多重ドメインに分割する方法が有力化されている。

10

## 【0005】

単位画素でドメインの個数を増加させるために画素電極をサブ画素電極に分割し、レベルの差がある画素電圧を各々印加する電荷分割方式の駆動方法も使用される。

## 【0006】

しかし、マルチドメインを具現するために1つの単位画素に4つ以上のドメインを形成し、複数のサブ電極を形成すると、スイッチング素子の個数及び配線個数が増加して画素の開口率が大きく低下する短所がある。

20

## 【発明の概要】

## 【発明が解決しようとする課題】

## 【0007】

これに本発明の技術的課題はこのような従来の問題点を解決することで、本発明は開口率及び視野角を向上させるアレイ基板を提供する。

## 【0008】

また、本発明は前記アレイ基板を有する表示装置を提供する。

## 【0009】

また、本発明は前記表示装置の駆動方法を提供する。

30

## 【課題を解決するための手段】

## 【0010】

前述の本発明の技術的課題を解決するために、実施例によるアレイ基板はベース基板、ゲート線、データ線、スイッチング素子、及び画素電極を含む。前記ゲート線は前記ベース基板の行方向に伸び、前記データ配線は前記ベース基板の列方向に伸びる。前記スイッチング素子は各前記ゲート線及び前記データ線に接続される。前記画素電極は前記スイッチング素子に接続され、前記画素電極にはスリットパターンが形成される。前記画素電極は隣接する画素電極に形成されたスリットパターンとは別の方向に互いに平行して配列される。

## 【0011】

40

本発明の一実施例で、前記スイッチング素子及び前記画素電極は単位画素を形成し、互いに隣接する4つの単位画素が2行2列に配列されて前記4つの単位画素のスリットパターンからなる1対のスリットパターンを有する画素ユニットを形成する。

## 【0012】

本発明の一実施例で、前記スリットパターンは縦電極棒、第1スリットパターン、及び第2スリットパターンを含む。前記縦電極棒は前記データ線と平行に配置される。前記第1スリットパターンは第1方向に延長されて前記縦電極棒に接続される。前記第2スリットパターンは前記第1方向に交差する第2方向に延長されて、前記縦電極棒に接続される。前記スリットパターンは横電極棒をさらに含むことができる。前記横電極棒は前記ゲート線付近で前記縦電極棒と直交するように配置され、前記スイッチング素子の出力電極と

50

電気的に接続される。

【0013】

本発明の一実施例で、1行1列及び2行2例に配置された前記単位画素においては前記行方向に前記第2スリットパターン及び前記第1スリットパターン順に配置され、2行1列及び1行2列に配置された前記単位画素においては前記行方向に前記第1スリットパターン及び前記第2スリットパターン順に配置されることができる。

【0014】

本発明の他の実施例で、前記スイッチング素子及び前記画素電極は単位画素を形成し、互いに隣接する8つの単位画素が2行4列に配列され、前記8つの単位画素のスリットパターンからなる1対のスリットパターンを有する画素ユニットを形成することができる。

10

【0015】

本発明の一実施例で、前記スリットパターンは第1スリットパターン及び第2スリットパターンのうち、選択された1つと縦電極棒を含むことができる。前記縦電極棒は前記データ線と平行に前記データ線付近に配置される。前記第1スリットパターンは前記行方向と交差する第1方向に伸びて縦電極棒に接続される。前記第2スリットパターンは前記第1方向と交差する第2方向に伸びて前記縦電極棒に接続される。

【0016】

本発明の一実施例で、第1行に配置された縦電極棒は左側データ線付近に配置され、第2行に配置された前記縦電極棒は右側データ線付近に配置され、前記行方向及び列方向に前記第1スリットパターン及び第2スリットパターンが交互に配置されることがある。

20

【0017】

前述の本発明の技術的課題を解決するために、実施例による表示装置は、アレイ基板、対向基板、及び液晶層を含む。アレイ基板はベース基板、ゲート線、データ線、スイッチング素子、及び画素電極を含む。前記ゲート線は前記ベース基板の行方向に伸び、前記データ配線は前記ベース基板の列方向に伸びる。前記スイッチング素子は各前記ゲート線及び前記データ線に接続される。前記画素電極は前記スイッチング素子に接続され、前記画素電極にはスリットパターンが形成される。前記画素電極は隣接する画素電極に形成されたスリットパターンとは別の方向に互いに平行に配列される。前記対向基板は前記画素電極と対向する共通電極を含む。前記液晶層は前記アレイ基板と前記対向基板との間で垂直に配向される。

30

【0018】

前述の本発明の技術的課題を解決するために、表示装置の駆動方法で、前記表示装置は第1スリットパターンを有する第1サブ画素電極、第2スリットパターンを有して前記第1サブ画素電極と隣接する第2サブ画素電極を含むアレイ基板、対向基板、及び前記アレイ基板と対向基板間に介在された液晶層を含む。前記表示装置の駆動方法で、前記画素電極には画像の階調より高い第1画素電圧を印加し、前記画素電極には前記画像の階調より低い第2画素電圧を印加して、画素ユニットによって表示されるドメインの数は前記液晶層のドメイン数の倍であることを特徴とする。

【発明の効果】

【0019】

本発明によるアレイ基板、アレイ基板を有する表示装置、及び表示装置の駆動方法によると、1つの画素ユニットで1行の単位画素は前記第1画素電圧に反転駆動され、2行の単位画素は前記第2画素電圧に反転駆動される。画素ユニットは2つのスリットパターンが配置された4つの領域を有し、第1画素電圧及び第2画素電圧によって駆動されるため、8つのドメインを具現する。従って、単位画素の開口率が増加される。従って、表示装置の視野角が向上される。

40

【図面の簡単な説明】

【0020】

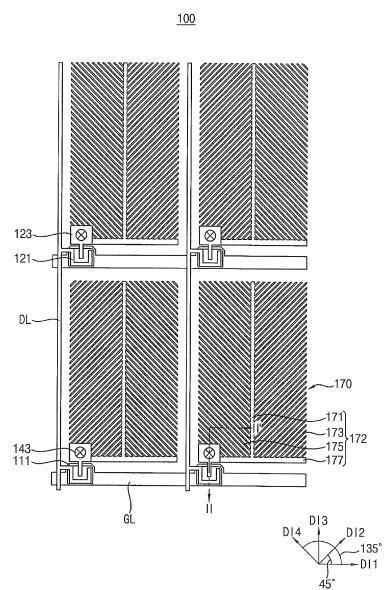

【図1】実施例1による表示装置の平面図である。

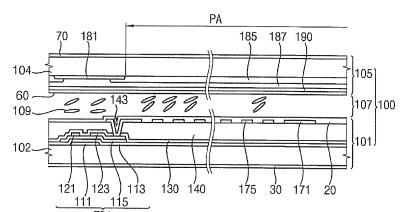

【図2】図1に図示された表示装置をI-I'線に沿って切断した断面図である。

50

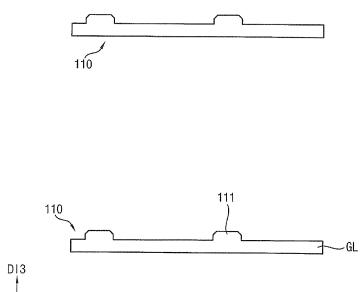

【図3】図1に示したアレイ基板を製造する方法を説明する平面図である。

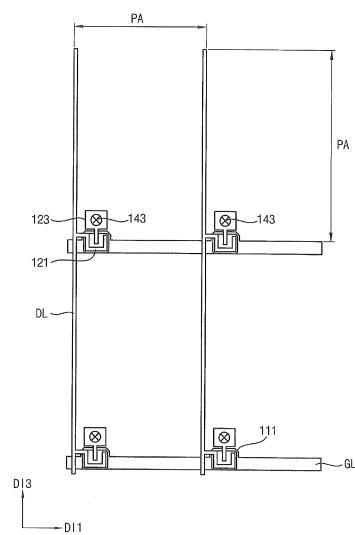

【図4】図1に示したアレイ基板を製造する方法を説明する平面図である。

【図5】図1に示した表示装置のブロック図である。

【図6】図5に示した駆動装置に適用されたガンマ曲線を表すグラフである。

【図7】図5に示した駆動装置に対する詳細なブロック図である。

【図8】図5に示した表示装置の駆動信号に対するタイミング図である。

【図9】実施例2による表示装置が含むアレイ基板の平面図である。

【発明を実施するための最良の形態】

【0021】

以下、添付図面を参照しつつ、本発明の表示装置の望ましい実施例をより詳しく説明する。 10

【0022】

本発明は多様な変更を加えることができ、様々な形態を有することができるため、特定実施例を図面に例示し、本明細書に詳しく説明する。しかし、これは本発明を特定の開示形態に対して限定しようとしているのではなく、本発明の思想及び技術範囲に含まれる全ての変更、均等物、ないしは代替物を含むことと理解されるべきである。

【0023】

各図面を説明しながら類似する参照符号を、類似する構成要素に対して使用した。添付図面において、構造物のサイズは本発明の明確性に基づくために実際より拡大して示した。 20

【0024】

第1、第2などの用語は多様な構成要素を説明するにあたって使用することができるが、各構成要素は使用される用語によって限定されるものではない。各用語は1つの構成要素を他の構成要素と区別する目的で使用されるものであって、例えば、明細書中において、第1構成要素を第2構成要素に書き換えることも可能であり、同様に第2構成要素を第1構成要素とすることができる。単数表現は文脈上、明白に異なる意味を有しない限り、複数の表現を含む。

【0025】

本明細書において、「含む」または「有する」などの用語は、明細書上に記載された特徴、数字、段階、動作、構成要素、部分品、またはこれらを組み合わせたものが存在することを指定しようとすることであって、1つまたはそれ以上の別の特徴、数字、段階、動作、構成要素、部分品、またはこれらを組み合わせたものの存在または付加可能性を予め排除しないことと理解されるべきである。 30

【0026】

また、別に定義しない限り、技術的或いは科学的用語を含んで、ここにおいて使用される全ての用語は本発明が属する技術分野で通常の知識を有する者であれば、一般的に理解されることと同一な意味を有する。一般的に使用される辞書において定義する用語と同じ用語は関連技術の文脈上に有する意味と一致する意味を有することと理解されるべきで、本明細書において明白に定義しない限り、理想的或いは形式的な意味として解釈しない。 40

【0027】

<実施例1>

図1は、実施例1による表示装置の平面図である。図2は、図1に図示された表示装置をI-I'線に沿って切断した断面図である。

【0028】

図1及び図2を参照すると、表示装置100はアレイ基板101、対向基板105、及び液晶層107を含む。

【0029】

図1には、説明の便宜上、アレイ基板101の平面図のみ図示されており、図2にはアレイ基板101、対向基板105、及び液晶層107の断面が図示されている。

【0030】

10

20

30

40

50

図3及び図4は、図1に示したアレイ基板101を製造する方法を説明する平面図である。

【0031】

図1、図3及び図4を参照すると、アレイ基板101はベース基板102、複数のゲート線GL、データ線DL、スイッチング素子108、及び画素電極170を含む。

【0032】

先ず、ガラス質のベース基板102上にゲート金属を蒸着させ、エッチングして、図3に示したようにゲート線GLを形成する。ゲート線GLはベース基板102上で略行方向DI1へ互いに平行して伸びる。ゲート線GLの一部は突起形状のゲート電極111を形成する。その後、図2に示したように、ゲート線GLを覆うゲート絶縁膜113を形成する。

10

【0033】

その後、ゲート絶縁膜113上に半導体層及びソース金属層を順次に形成しエッチングして、図2及び図4に示したように、データ線DL、チャンネル層115、及びドレイン電極123を形成する。データ線DLはゲート絶縁膜113上に略列方向DI3へ延長されている。ゲート線GLとデータ線DLの交差点近くのデータ線DLでソース電極121が突出されて、ゲート電極111と一部重畳するように形成される。ドレイン電極123はゲート電極111上にソース電極121付近で一部が配置されて画素領域PAに一部が延長されている。

【0034】

20

ゲート線GL及びデータ線DLが交差して略長方形の領域を定義し、前記長方形領域には、その後、画素電極170が形成される。従って、前記長方形領域を前記画素領域PAに定義する。

【0035】

半導体層とソース金属層を單一エッチング工程で共にエッチングする場合、データ線DL、ソース電極121、ドレイン電極123の下、及びゲート電極111の上部に半導体層が形成され、ソース電極121とドレイン電極123との間の半導体層はチャンネル層115に形成される。

【0036】

ゲート電極111、ゲート絶縁膜113、チャンネル層115、ソース電極121、及びドレイン電極123は三端子素子であるスイッチング素子108を構成する。

30

【0037】

その後、図2に示したように、データ線DLが形成されたベース基板102を覆うパッシベーション膜130を形成し、パッシベーション膜130上に有機絶縁膜140を形成する。有機絶縁膜140及びパッシベーション膜130にドレイン電極123の一部を露出させるコンタクトホール143を形成する。

【0038】

その後、有機絶縁膜140上にITOまたはIZOのような透明な伝導性物質層を蒸着する。伝導性物質層はコンタクトホール143を通じてドレイン電極123に接触される。伝導性物質をエッチングして、図1に示したように、画素電極170を形成する。画素電極170にはスリットパターン172が形成されている。

40

【0039】

最後に、図2に示したように、画素電極170を覆う下部配向膜20を形成し、ベース基板102の背面に下部偏光板30を付着してアレイ基板101を製造する。

【0040】

下部配向膜20は、後述される対向基板105と共に液晶層107の液晶分子を垂直方向、即ち、アレイ基板101から対向基板105に向かう方向に配向する。

【0041】

下部偏光板30は下部偏光軸が行方向DI1と実質的に一致するように配置される。画素電極170には、図1に示したように、下部偏光軸と略45°または135°を成すス

50

リットが形成されている。

【0042】

前記スイッチング素子108及び前記画素電極170は単位画素を形成し、互いに隣接する4つの単位画素が2行2列に配列されて画素ユニットを形成する。

【0043】

再び、図2を参照すると、対向基板105は上部基板104、遮光パターン181、カラーフィルタパターン185、オーバーコーティング層187、共通電極190、上部配向膜60、及び上部偏光板70を含むことができる。

【0044】

遮光パターン181はゲート線GL、データ線DL、スイッチング素子108、及び図示しないストレージ電極に対応するように、上部基板104に形成されている。遮光されない前記画素領域PAにはカラーフィルタパターン185が形成される。カラーフィルタパターン185は例えば、赤フィルタ、緑フィルタ、及び青フィルタを含むことができる。赤フィルタ、緑フィルタ、及び青フィルタ順に行方向DI1に各単位画素に対応するように配置できる。オーバーコーティング層187はカラーフィルタパターン185及び遮光パターン181を覆い、共通電極190はオーバーコーティング層187上に形成されている。上部配向膜60は共通電極190上に形成されて液晶層107を垂直配向させる。上部偏光板70は上部基板104の上面に付着され、上部偏光板70の偏光軸は下部偏光板30の偏光軸と実質的に直交するように配置される。

【0045】

再び、図1及び図2を参照すると、本実施例で画素電極170がパターニングされており、垂直配向される液晶が使用される。従って表示装置は複数の種類のドメインを形成することができる。

【0046】

画素ユニットは表示装置100が具現できるドメインの種類を全て有する画素セットである。従って画素ユニットは複数の単位画素を含み、本実施例で画素ユニットは2行2列のマトリックス形態に配列された4つの単位画素を含む。

【0047】

画素電極170に形成されたスリットパターン172は液晶の方向子を略一定方向に整列させる。画素ユニット内の単位画素は隣接する画素電極170の液晶整列方向が互いに異なるように配置される。

【0048】

本実施例で、各単位画素はスリットパターン172によって形成された2つのドメインを有する。スリットパターン172によって画素電極170は特殊な形状で形成される。例えば、スリットパターン172は縦電極棒171、第1スリットパターン173、及び第2スリットパターン175を含むことができる。

【0049】

縦電極棒171はデータ線DLと平行に2つのドメインの境界を形成する。即ち、縦電極棒171によって画素領域PAは左側ドメイン及び右側ドメインに分割される。

【0050】

第1スリットパターン173は左側または右側ドメインで行方向DI1と45°を成す第1斜線方向DI2に縦電極棒171に接続される。第2スリットパターン175は左側または右側ドメインで第1スリットパターン173と直交する第2斜線方向DI4に、即ち、行方向DI1と135°を成す方向に縦電極棒171に接続される。

【0051】

第1及び第2スリットパターン(173、175)のスリットの幅は液晶層107の厚さより薄く形成される。第1及び第2スリットパターン(173、175)は液層の方向子が縦電極棒171に向かうように整列する。

【0052】

画素電極170は横電極棒177をさらに含むことができる。横電極棒177はゲート

10

20

30

40

50

線 G L 付近で縦電極棒 1 7 1 と直交するように配置され、コンタクトホール 1 4 3 を通じてスイッチング素子 1 0 8 のドレイン電極と電気的に接続される。

【 0 0 5 3 】

4 つの単位画素で第 1 スリットパターン 1 7 3 及び第 2 スリットパターン 1 7 5 が配置される順番は多様な方式で変更されることができる。本実施例においては、図 1 に示したように、1 行 1 列及び 2 行 2 列に配置された単位画素においては行方向 D I 1 に第 2 スリットパターン 1 7 5 及び第 1 スリットパターン 1 7 3 順に配置され、2 行 1 列及び 1 行 2 列に配置された単位画素においては行方向 D I 1 に第 1 スリットパターン 1 7 3 及び第 2 スリットパターン 1 7 5 順に配置されている。

【 0 0 5 4 】

第 1 スリットパターン 1 7 3 及び第 2 スリットパターン 1 7 5 の延長方向及び単位画素内に配置される位置によって、画素ユニットは液晶整列方向が規定された 4 つの領域を有する。画素電極 1 7 0 には後述される電圧レベルが互いに異なる画素電圧が印加され、その結果、表示装置 1 0 0 は画素ユニットで 8 つのドメインを形成する。ドメインは液晶の方向子が互いに異なる領域に定義される。

【 0 0 5 5 】

以下、表示装置 1 0 0 が画素ユニットで 8 つのドメインを駆動して画像を表示する表示装置 1 0 0 の駆動方法を説明する。

【 0 0 5 6 】

図 5 は、図 1 に示した表示装置 1 0 0 のブロック図である。図 6 は、図 5 に示した駆動装置に適用されたガンマ曲線を表すグラフである。

【 0 0 5 7 】

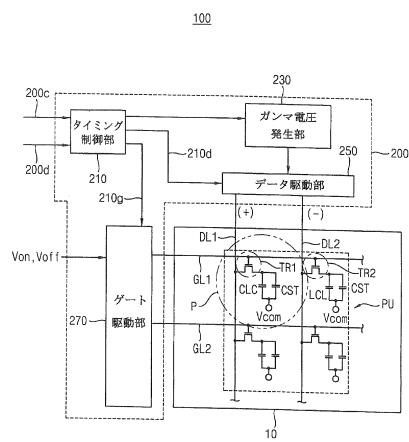

図 5 及び図 6 を参照すると、表示装置 1 0 0 は駆動装置 2 0 0 をさらに含むことができる。複数の画素ユニットを行方向 D I 1 及び列方向 D I 3 に配列されている。各単位画素 P は 1 つのデータ線 D L 1 及び 1 つのゲート線 G L 1 によって伝達されるデータ信号及びゲート信号によって駆動される。

【 0 0 5 8 】

2 行 2 列に配列された単位画素 P を含む画素ユニット P U は第 1 及び第 2 データ線 ( D L 1, D L 2 ) と第 1 及び第 2 ゲート線 ( G L 1, G L 2 ) によって伝達されるデータ信号及びゲート信号によって駆動される。

【 0 0 5 9 】

例えば、等価回路の観点で、単位画素 P はスイッチング素子 1 0 8 、液晶コンデンサ C L C 及びストレージコンデンサ C S T を含む。

【 0 0 6 0 】

スイッチング素子 1 0 8 は、上述のように、ゲート線 G L 1 に接続されたゲート電極 1 1 1 、データ線 D L 1 に接続されたソース電極 1 2 1 及び液晶コンデンサの一端と接続されたドレイン電極 1 2 3 を含む。

【 0 0 6 1 】

列方向単位画素 P にはデュアル極性のデータ信号が各々印加される。例えば、1 行 1 列の単位画素 P には基準電圧対比両極性のデータ信号 ( + ) ( 以下、第 1 画素電圧とする ) が印加され、2 行 1 列の単位画素 P には前記基準電圧対比陰極性のデータ信号 ( - ) ( 以下、第 2 画素電圧とする ) が印加される。

【 0 0 6 2 】

即ち、前記第 1 画素電圧は前記単位画素 P によって表示される画像の階調より高いレベルの画素電圧であり、前記第 2 画素電圧は前記画像の階調より低いレベルの画素電圧である。

【 0 0 6 3 】

駆動装置 2 0 0 はタイミング制御部 2 1 0 、ガンマ電圧発生部 2 3 0 、データ駆動部 2 5 0 、及びゲート駆動部 2 7 0 を含む。

10

20

30

40

50

## 【0064】

タイミング制御部210は、外部から制御信号200C及びデータ200Dを受信する。タイミング制御部210は受信された前記制御信号200Cを利用してデータ駆動部250及びゲート駆動部270の駆動タイミングを制御するタイミング制御信号（以下、データ制御信号及びゲート制御信号と称す）を生成する。前記タイミング制御部210は前記データ制御信号210d及び前記ゲート制御信号210gを前記データ駆動部250及び前記ゲート駆動部270に各々出力する。前記タイミング制御部210は外部から受信された前記データ200Dを前記ガンマ電圧発生部230に伝達する。

## 【0065】

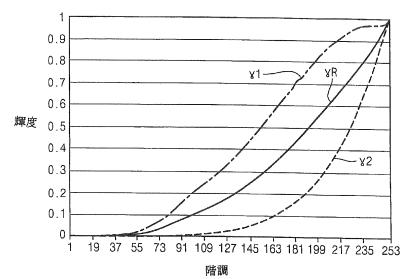

前記ガンマ電圧発生部230は前記タイミング制御部210から提供された前記データを第1ガンマ曲線（1）及び第2ガンマ曲線（2）が各々適用される第1ガンマデータ及び第2ガンマデータを出力する。 10

## 【0066】

図6に図示したガンマ曲線（1、2、R）は、X軸は階調（例えば、256階調）を示し、Y軸は輝度（または透過率（%））を示す。基準ガンマ曲線（R）は正面視認性が最適化されたガンマ曲線で、第1ガンマ曲線（1）と第2ガンマ曲線（2）は側面視認性が最適化されたガンマ曲線である。

## 【0067】

前記ガンマ電圧発生部230は前記タイミング制御部210から受信された前記データを、第1区間には前記第1ガンマ曲線（1）が適用された第1ガンマデータを生成し、第2区間には前記第2ガンマ曲線（2）が適用された第2ガンマデータを生成する。前記第1区間は奇数行単位画素Pが充電されるフレーム区間であり、前記第2区間は偶数行単位画素Pが充電されるフレーム区間である。 20

## 【0068】

前記データ駆動部250は前記ガンマ電圧発生部230から生成された前記第1及び第2ガンマデータをアナログのデータ電圧に変換してアレイ基板（101、100）の第1データ線DL1に出力する。 20

## 【0069】

データ駆動部250は前記第2データ線DL2には前記第1データ線DL1に出力される前記データ電圧に位相が反転されたデータ電圧を出力する。例えば、基準電圧が0Vで、前記第1データ線DL1に+5Vのデータ電圧が出力される場合、前記第2データ線DL2には-5Vのデータ電圧が出力される。 30

## 【0070】

前記ゲート駆動部270は前記タイミング制御部210から提供された前記ゲート制御信号210g及び外部から受信されたゲートオン及びオフ電圧（Von、Voff）を利用してゲートファルスを生成する。例えば、前記ゲート駆動部270は前記第1区間の間、奇数ゲート線GLに前記ゲートオン電圧（Von）を有するゲートファルスを出力し、前記第2区間の間、偶数ゲート線GLに前記ゲートファルスを出力する。

## 【0071】

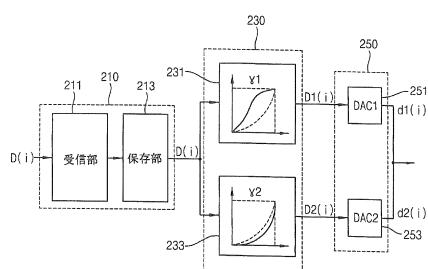

図7は、図5に示した駆動装置に対する詳細なブロック図である。 40

## 【0072】

図5及び図7を参照すると、前記タイミング制御部210は受信部211、保存部213を含む。前記受信部211は外部からデータDを受信する。前記受信されたデータDは前記保存部213に保存される。前記保存部213は例えば、前記表示パネル100の行に含まれる画素に該当するラインデータを保存するラインメモリである。

## 【0073】

前記ガンマ電圧発生部230は、第1バッファーパート231及び第2バッファーパート233を含む。前記第1バッファーパート231は前記第1ガンマ曲線（1）が適用された第1ガンマデータが保存され、前記第2バッファーパート233は前記第2ガンマ曲線（2）が適用された第2ガンマデータが保存される。ここでは、前記ガンマ電圧発生部230が前記第 50

1 及び第 2 ガンマデータが保存された前記第 1 及び第 2 バッファー部 ( 231、233 ) を含むことを例としてあげたが、前記第 1 及び第 2 ガンマ曲線 ( 1、2 ) が適用された抵抗ストリングを各々適用することができる。

【 0074 】

前記ガンマ電圧発生部 230 は前記第 1 区間には前記データを前記第 1 ガンマ曲線 ( 1 ) が適用された前記第 1 ガンマデータに生成し、前記第 2 区間には前記データを前記第 2 ガンマ曲線 ( 2 ) が適用された前記第 2 ガンマデータに生成する。

【 0075 】

前記データ駆動部 250 は第 1 デジタルアナログ変換部 251 ( 以下、D A C 1 と称す ) 及び第 2 デジタルアナログ変換部 253 ( 以下、D A C 2 と称す ) を含む。前記 D A C 1 ( 251 ) は前記第 1 バッファー部 231 から受信された前記第 1 ガンマデータをアナログの第 1 データ信号に変換する。前記 D A C 2 ( 253 ) は前記第 2 バッファー部 233 から受信された前記第 2 ガンマデータをアナログの第 2 データ信号に変化する。例えば、前記 D A C 1 ( 251 ) から出力された前記第 1 データ信号は前記第 1 データ配線 D L 1 に印加され、前記第 1 データ信号に対して位相が反転されたデータ信号は前記第 2 データ配線 D L 2 に印加される。

10

【 0076 】

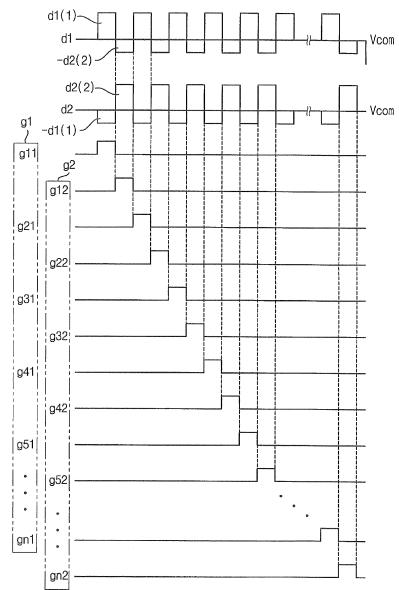

図 8 は、図 5 に示した表示装置の駆動信号に対するタイミング図である。

【 0077 】

図 1、図 5、図 7、及び図 8 を参照すると、1 つのフレーム ( 1 F R A M E ) の間、前記表示パネル 100 の駆動方式を説明する。前記アレイ基板 101、前記対向基板 105、及び前記液晶層 107 を含む表示パネル 100 は、m ( m は、自然数 ) 個の垂直画素列と n ( n は、自然数 ) 個の水平画素列を含み、前記第 1 及び第 2 データ配線 ( D L 1、D L 2 ) と接続された i ( i < m ) 番目垂直画素列の駆動方式を説明する。

20

【 0078 】

前記データ駆動部 250 は前記第 1 区間には前記第 1 ガンマ曲線 ( 1 ) が適用された前記第 1 データ信号 d 1 を前記第 1 データ配線 D L 1 に出力し、前記第 1 データ信号 d 1 と位相が反転されたデータ信号 - d 1 を前記第 2 データ配線 D L 2 に出力する。続いて、前記第 2 区間には前記第 2 ガンマ曲線 ( 2 ) が適用された前記第 2 データ信号 d 2 を前記第 2 データ配線 D L 2 に出力し、前記第 2 データ信号 d 2 と位相が反転するデータ信号 - d 2 を前記第 2 データ配線 D L 2 に出力する。

30

【 0079 】

前記ゲート駆動部 270 は 1 つのフレームの間、ゲートファルス g 1 を有するゲート信号 G を n 個のゲート配線に順次に出力する。

【 0080 】

例えば、前記データ駆動部 250 は前記第 1 区間の間、前記 i 番目垂直画素列の 1 番目から n 番目画素に該当する前記第 1 データ信号、d 1 ( 1 )、d 1 ( 2 )、d 1 ( 3 )、...、d 1 ( n ) を前記第 1 データ配線 D L 1 に出力し、前記第 1 データ信号に反転するデータ信号、- [ d 1 ( 1 ) ]、- [ d 1 ( 2 ) ]、- [ d 1 ( 3 ) ]、...、- [ d 1 ( n ) ] を前記第 2 データ配線 D L 2 に出力する。

40

【 0081 】

一方、前記ゲート駆動部 270 は前記第 1 区間の間、前記 n 個のゲート配線に前記ゲートファルス、g 1 1、g 2 1、g 3 1、...、g n 1 を順次に出力する。前記第 1 区間の間、前記 i ( i < m ) 番目垂直画素列は前記ゲートファルスによってスイッチング素子 108 がターン・オンされて前記第 1 ガンマ曲線 ( 1 ) が適用された画像を表示する。

【 0082 】

続いて、前記データ駆動部 250 は前記第 2 区間の間、前記 i 番目垂直画素列の 1 番目から n 番目画素に該当する前記第 2 データ信号、d 2 ( 1 )、d 2 ( 2 )、d 2 ( 3 )、...、d 2 ( n ) を前記第 1 データ配線 D L 1 に出力し、前記第 2 データ信号に反転されたデータ信号、- [ d 2 ( 1 ) ]、- [ d 2 ( 2 ) ]、- [ d 2 ( 3 ) ]、...、- [ d 2 (

50

n ) ] を前記第 2 データ配線 D L 2 に出力する。

【 0 0 8 3 】

一方、前記ゲート駆動部 270 は前記第 2 区間の間、前記 n 個のゲート配線に前記ゲートファルス g12、g22、g32、…、gn2 を順次に出力する。前記第 2 区間の間、前記 i ( i < m ) 番目垂直画素列は前記ゲートファルスによってスイッチング素子 108 がターン・オンされて前記第 2 ガンマ曲線 ( 2 ) が適用された画像を表示する。

【 0 0 8 4 】

その結果、列方向 D I 3 に隣接する 2 つの単位画素 P は画像表示のための 1 つの階調を表示することができる。奇数行の単位画素 P は前記第 1 画素電圧によってドット反転駆動されることがある。偶数行の単位画素 P は前記第 2 画素電圧によって反転駆動されることがある。

10

【 0 0 8 5 】

従って、駆動装置は第 1 画素電圧及び第 2 画素電圧を単位画素 P に交互的に印加して画素ユニット P U が有する、液晶配列方向が規定された領域数 4 の倍である 8 つのドメインを具現する。従って、前記表示パネル 100 の側面視認性を向上させることができる。

【 0 0 8 6 】

一般的なスーパー垂直配向モード ( S P V モード ) においては単位画素 P に複数のドメインを形成するために 1 つの単位画素 P に 4 つの方向を有するスリットが形成された画素電極 170 を形成し、電荷分割 ( charge sharing ) 方式の駆動をして 8 つのドメインを具現することができる。しかし、この場合には単位画素 P に複数のスイッチング素子 108 と配線が多数形成されて画素の開口率を大きく減少させる。

20

【 0 0 8 7 】

本発明による表示装置 100 で画素ユニット P U は前記 8 つのドメインを具現するためには、4 つの単位画素 P を有する。即ち、表示装置 100 はマルチドメインを 1 つの画素領域 P A で具現するのではなく、複数の単位画素 P を含む画素ユニット P U でマルチドメインを具現する。従って、単位画素 P に形成されるスイッチング素子 108 の個数が減少され、単位画素 P に形成される配線の個数も減少される。従って、画素の開口率が大きく向上されることがある。

< 実施例 2 >

【 0 0 8 8 】

30

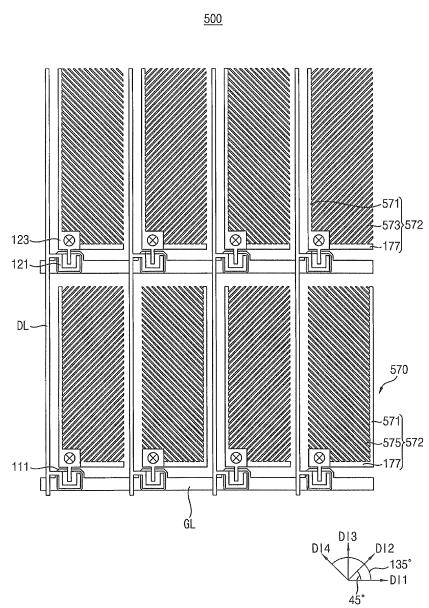

図 9 は、実施例 2 による表示装置 500 が含むアレイ基板 501 の平面図である。

【 0 0 8 9 】

本実施例で、表示装置 500 はアレイ基板 501 の構成を除いては図 1 ~ 図 8 で説明した表示装置 100 と実質的に同一である。従って、対応する構成要素に対しては対応する参照番号を使用し、重複される説明は省略する。

【 0 0 9 0 】

本実施例で、アレイ基板 501 は、画素ユニット P U が 2 行 2 列に配列された 4 つの単位画素 P を含み、単位画素 P に形成された画素電極 570 のスリットパターン 572 が変更されて 1 つの単位画素 P が 1 つのドメインを具現することを除いては図 1 ~ 図 4 において説明されたアレイ基板 101 と実質的に同一である。従って、対応する構成要素に対しては対応する参照番号を使用し、重複される説明は省略する。なお、図面においては連続する 2 つの画素ユニットを図示している。

40

【 0 0 9 1 】

アレイ基板 501 の画素ユニット P U は 2 行 2 列に配列された 4 つの単位画素 P を有し、各単位画素 P はスリットパターン 572 によって形成された 1 つのドメインを有することができる。

【 0 0 9 2 】

画素電極 570 は縦電極棒 571 と、第 1 スリットパターン 573 及び第 2 スリットパターン 875 のうち、選択された何れかの 1 つを含むことができる。縦電極棒 571 はデータ線 D L と平行にデータ線付近に配置される。第 1 スリットパターン 573 は行方向 D

50

I 1 と 4 5 ° を成す第 1 斜線方向 D I 2 に伸びて縦電極棒 5 7 1 に接続される。第 2 スリットパターン 8 7 5 は行方向 D I 1 と 1 3 5 ° を成す第 2 斜線方向 D I 4 に伸びて縦電極棒 5 7 1 に接続される。第 1 及び第 2 スリットパターン ( 5 7 2, 8 7 5 ) は液層の方向子を縦電極棒 5 7 1 に向かって整列する。

【 0 0 9 3 】

第 1 行の縦電極棒 5 7 1 は左側データ線 D L 付近に配置され、第 2 行の縦電極棒 5 7 1 は右側データ線 D L 付近に配置され、行方向 D I 1 及び列方向 D I 3 に第 1 スリットパターン 5 7 2 及び第 2 スリットパターン 8 7 5 が交互に配置されることができる。

【 0 0 9 4 】

本実施例の表示装置 5 0 0 の駆動方法は画素ユニット P U に含まれる 2 行 2 列の 4 つの単位画素 P を 2 つつなげてみると、図 5 ~ 図 8 で説明された駆動方法と実施的に同一である。従って、重複される説明は省略する。 10

【 0 0 9 5 】

以上、添付図面を参照しながら本発明の好適な実施形態について詳細に説明したが、本発明はかかる例に限定されない。本発明の属する技術の分野における通常の知識を有する者であれば、特徴請求の範囲に記載された技術的思想の範疇内において、各種の変更例または修正例に想到し得ることは明らかであり、これらについても、当然に本発明の技術的範囲に属するものと了解される。

【 産業上の利用可能性 】

【 0 0 9 6 】

本発明によるアレイ基板及びこれを有する表示装置によると、単位画素の開口率及び視野角が向上される。従って、本発明は表示装置の表示品質を向上させる技術に適用されることができる。 20

【 符号の説明 】

【 0 0 9 7 】

|       |              |    |

|-------|--------------|----|

| D I 1 | 行方向          |    |

| D I 3 | 列方向          |    |

| 1 0   | 表示パネル        |    |

| 1 0 0 | 表示装置         |    |

| 1 0 1 | アレイ基板        | 30 |

| 1 0 5 | 対向基板         |    |

| 1 0 7 | 液晶層          |    |

| 1 0 8 | スイッチング素子     |    |

| 1 7 0 | 画素電極         |    |

| 1 7 1 | 縦電極棒         |    |

| 1 7 2 | スリットパターン     |    |

| 1 7 3 | 第 1 スリットパターン |    |

| 1 7 5 | 第 2 スリットパターン |    |

| P     | 単位画素         |    |

| P U   | 画素ユニット       | 40 |

| G L   | ゲート線         |    |

| D L   | データ線         |    |

| P A   | 画素領域         |    |

| 2 0 0 | 駆動装置         |    |

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

---

フロントページの続き

(72)発明者 金 相 洙

大韓民国ソウル江南区道谷2洞三星タワー・パレスF棟3104号

審査官 鈴木 俊光

(56)参考文献 特開2007-256906 (JP, A)

特開2003-149647 (JP, A)

特開2005-352483 (JP, A)

特開2005-300821 (JP, A)

(58)調査した分野(Int.Cl., DB名)

|        |          |

|--------|----------|

| G 02 F | 1 / 1343 |

| G 02 F | 1 / 1368 |

| G 02 F | 1 / 133  |

| G 02 F | 1 / 1337 |