(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2007-515079

(P2007-515079A)

(43) 公表日 平成19年6月7日(2007.6.7)

(51) Int.C1.

F 1

テーマコード(参考)

HO1L 29/78 (2006.01)

HO1L 21/336 (2006.01)HO1L 29/78 652H

HO1L 29/78 658A

審査請求 未請求 予備審査請求 未請求 (全 20 頁)

|               |                              |          |                                                                                                                                          |

|---------------|------------------------------|----------|------------------------------------------------------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2006-545755 (P2006-545755) | (71) 出願人 | 506207200<br>サード ディメンジョン (スリーディ)<br>セミコンダクタ インコーポレイテッド<br>アメリカ合衆国 アリゾナ州 85285<br>、テンペ、サウス リバー パークウェイ<br>7855、スイート 122、ビーオー<br>ボックス 24619 |

| (86) (22) 出願日 | 平成16年12月10日 (2004.12.10)     | (74) 代理人 | 100087653<br>弁理士 鈴江 正二                                                                                                                   |

| (85) 翻訳文提出日   | 平成18年7月7日 (2006.7.7)         | (74) 代理人 | 100121474<br>弁理士 木村 俊之                                                                                                                   |

| (86) 國際出願番号   | PCT/US2004/041302            | (72) 発明者 | シリー、フュー イュアン<br>アメリカ合衆国 カリフォルニア州 95<br>070、サラトガ、セヴィラ レーン 2<br>0768                                                                       |

| (87) 國際公開番号   | W02005/065140                |          |                                                                                                                                          |

| (87) 國際公開日    | 平成17年7月21日 (2005.7.21)       |          |                                                                                                                                          |

| (31) 優先権主張番号  | 60/531,501                   |          |                                                                                                                                          |

| (32) 優先日      | 平成15年12月19日 (2003.12.19)     |          |                                                                                                                                          |

| (33) 優先権主張国   | 米国(US)                       |          |                                                                                                                                          |

最終頁に続く

(54) 【発明の名称】従来の端子を備えた超接合装置の製造方法

## (57) 【要約】

半導体ディバイスの製造方法は、強くドープされた第1導電率形の第1領域と、軽くドープされた第2導電率形の第2領域とを含む。半導体基板には複数個の溝が、その作動領域にエッティングされて形成され、複数個のメサを形成する。、作動領域の所定領域が酸化され、乾式酸化物エッティング法を用いてエッティングされて溝の酸化物を除去する。保護シールドが所定領域上から部分的に除去される。ドーパントが所定領域のメサに或る角度で打込まれる。複数個の溝は絶縁材料を備え、構造体の頂面が平坦化されて、この構造体に超接合装置が形成される。

【選択図】 なし

## 【特許請求の範囲】

## 【請求項 1】

半導体ディバイスの製造方法であって、

相互に対向する第1及び第2の主表面を有する半導体基板を設け、上記の半導体基板は、第2主表面に第1導電率形の強くドープされた領域を有し、第1主表面に第1導電率形の軽くドープされた領域を有し、

上記の半導体基板において、その作動領域に複数個の溝と複数個のメサとをエッチングにより設け、各溝は、強くドープされた領域に向け、第1主表面から第1深さ位置まで伸びる第1延長部分を有し、各メサは、第1主表面に対し所定の傾斜を維持する側壁面を有し、上記の複数個の溝の各々は、複数個のメサの1つにより、その他の溝の各々から離れていて、

作動領域と、作動領域の外側およびこれに隣接する端子領域内に延びる、複数個のメサと複数個の溝との所定領域を、各メサの頂部、複数個の溝の各々の両側面および底部ならばに端子領域の頂部を酸化物が覆うまで酸化し、

複数個のメサと複数個の溝との所定領域を、乾式酸化物エンチング法を用いてエッチングし、複数個の溝の底部にある酸化物を除去し、

作動領域と端子領域との間の境界の所定領域上に保護シールドを形成し、

その後複数個のメサと複数個の溝との所定領域の上から保護シールドを部分的に除去し、

複数個のメサと複数個の溝との所定領域の少なくとも1つの所定のメサに、隣接対の溝において、1つの溝の側壁面で、第1導電率形のドーパントを、第1所定打込み角度で打込み、上記の1つの溝の側壁面に、強くドープされた領域より低いドープ濃度を有する第1導電率形の第1ドープ領域を形成し、

複数個のメサと複数個の溝との所定領域の少なくとも1つのメサに、第1導電率形のドーパントを打込んだ側壁に対向する上記の少なくとも1つのメサの側壁面で、第2導電率形のドーパントを、第2所定打込み角度で打込んで、第1導電率形のドーパントを打込んだ側壁に対向する側壁面に第2導電率形の第2ドープ領域を設けて、複数個の溝の少なくとも1つの溝の深さ方向に沿って位置する第1および第2ドープ領域のP-N接合を形成すると共に、作動領域のイオンが打込まれていない外側壁を設け、

複数個の溝に絶縁材料を充填し、

構造体の頂面を平坦化して、

超接合装置をこの構造体上に形成するもの。

## 【請求項 2】

請求項1に記載の半導体ディバイスの製造方法であって、保護シールドを形成する工程が、

複数個のメサと複数個の溝との所定領域の上にフォトレジストの層を沈着させ、

複数個のメサと複数個の溝との所定領域の各側の最後の溝の外側壁上のフォトレジストが保護され、上記の所定領域の残りの個所は保護されないように、マスクを置き、

フォトレジストの保護されていない部分を、紫外線光、深紫外線光、電子ビームおよびX線を含むグループから選ばれたフォトレジスト反応体に晒すことからなるものにおいて、

上記の保護シールドを部分的に除去する工程が、

複数個のメサと複数個の溝との所定領域上からマスクを除き、

反応したフォトレジストを構造体から取除き、

複数個のメサと複数個の溝の所定領域を湿式酸化物エッチング法によりエッチングして、反応しなかったフォトレジストにより酸化物が保護されていた上記の所定領域の各側の最後の溝の外側壁をのぞいて、上記の所定領域から反応しなかったフォトレジストと酸化物とを除去し、上記の酸化物は上記の各最後の溝の外側壁へのイオン打込みを阻止するため残されているもの。

## 【請求項 3】

10

20

30

40

50

請求項 2 に記載の半導体ディバイスの製造方法であって、

第 2 ドープ領域と電気的に連結する第 3 ドープ領域を第 1 および第 2 ドープ領域の第 1 主表面に設け、

第 1 導電率形の第 4 ドープ領域を、これが第 3 ドープ領域を挟んで第 1 ドープ領域と対向するように、上記の 1 つの溝の第 1 主表面と側壁面の少なくとも一方に設け、

ゲート電極層を、第 1 ドープ領域と第 4 ドープ領域との間で、ゲート絶縁層を介在させて第 3 ドープ領域に対向させて設けることからなるもの。

【請求項 4】

請求項 3 に記載の半導体ディバイスの製造方法であって、ゲート電極層が少なくとも 1 つの溝に形成されるもの。

【請求項 5】

請求項 3 に記載の半導体ディバイスの製造方法であって、ゲート電極層が第 1 主表面上に形成されるもの。

【請求項 6】

請求項 1 に記載の半導体ディバイスの製造方法であって、保護シールドを形成する工程が、

複数個のメサと複数個の溝との所定領域を乾式酸化物エッチング法を用いてエッチングして、複数個の溝の各々の両側部と底部にある酸化物を除去し、

マスクを、このマスクの開口部のみが、作動領域の各側の最後の溝とこれに隣接するメサ領域上に位置するように位置決めし、

作動領域の最後の溝とこれに隣接するメサ領域のみが、フォトレジストが沈着する領域であるようにフォトレジストの層をマスク上に沈着させることからなるものにおいて、

部分的に保護シールドを除去する工程が、最後の溝とこれに隣接するメサ領域とを除いて、フォトレジストが沈着するのを阻止したマスクを除去することからなるもの。

【請求項 7】

請求項 6 に記載の半導体ディバイスの製造方法であって、更に、

第 2 ドープ領域と電気的に連結する第 3 ドープ領域を第 1 および第 2 ドープ領域の第 1 主表面に設け、

第 1 導電率形の第 4 ドープ領域を、これが第 3 ドープ領域を挟んで第 1 ドープ領域と対向するように、上記の複数個の溝の第 1 主表面と側壁面のいずれか一方に設け、

ゲート電極層を、第 1 ドープ領域と第 4 ドープ領域との間で、ゲート絶縁層を介在させて第 3 ドープ領域に対向させて設けることからなるもの。

【請求項 8】

請求項 6 に記載の半導体ディバイスの製造方法であって、ゲート電極層が第 1 主表面上に形成されるもの。

【請求項 9】

請求項 6 に記載の半導体ディバイスの製造方法であって、更に、

第 2 ドープ領域と電気的に連結する第 3 ドープ領域を第 1 および第 2 ドープ領域の第 1 主表面に設けることからなるもの。

【請求項 10】

請求項 6 に記載の半導体ディバイスの製造方法であって、更に、電極層を第 1 ドープ領域とオーム接触させるもの。

【請求項 11】

請求項 6 に記載の半導体ディバイスの製造方法であって、更に、

半導体ディバイスの製造において第 1 および第 2 導電率形のドーパントの各々の拡散長さが、隣接対の側壁面から、第 1 および第 2 ドープ領域の P - N 接合までの距離より長いもの。

【請求項 12】

請求項 1 に記載の半導体ディバイスの製造方法であって、更に、

第 2 ドープ領域と電気的に連結する第 3 ドープ領域を第 1 および第 2 ドープ領域の第 1 主

10

20

30

40

50

表面に設けることからなるもの。

【請求項 1 3】

請求項 1 に記載の半導体ディバイスの製造方法であって、更に、

電極層を第 1 ドープ領域とショットキー(Schottky)接触させることからなるもの。

【請求項 1 4】

請求項 1 に記載の半導体ディバイスの製造方法であって、

半導体ディバイスの製造において第 1 および第 2 導電率形のドーパントの各々の拡散長さが、隣接対の溝の側壁面から、第 1 および第 2 ドープ領域の P - N 接合までの距離より長いもの。

10

【発明の詳細な説明】

【技術分野】

【0 0 0 1】

本発明は、作動領域の最後の溝の、イオンが打込まれていない外側壁を含む縁部端子構造体を備えた半導体ディバイスの製造方法、特に、作動中の抵抗が低く破壊電圧の高い、電力スイッチングに適した金属酸化物(MOS)ゲート半導体である半導体ディバイスに関するものである。

【背景技術】

【0 0 0 2】

米国特許第 5,216,275 号に開示されている、キシンビ チェン博士(Dr. Xingbi Chen)による超接合装置の発明以来、彼の発明の超接合効果を拡大及び改良する多くの試みがなされた。米国特許第 6,410,958 号および米国特許第 6,300,171 号ならびに米国特許第 6,307,246 号はそのような努力の例であり、これらを言及することによりそれらの内容を本願に組み込むこととする。

【0 0 0 3】

米国特許第 6,410,958 号(Usui, et al.)は縁部端子構造と半導体構成要素としてのドリフト領域に関する。1つの導電率形の半導体本体は、他の導電率形の複数個の領域が2つ以上の異なる面に埋め込まれている縁領域を有する。半導体構成要素の作動領域の下方に、その下にある基板を用いてドリフト領域が結合されている。

【0 0 0 4】

米国特許第 6,307,246 号(Nitta, et al.)は高電圧維持縁部構造体を有する半導体構成要素を開示する。この構造体内では、多数の平行に結合した個別の構成要素がセル通路の多数のセルに配置されている。縁領域では、半導体構成要素は、遮光源ゾーン領域を備えたセルを有する。この遮光源ゾーン領域では電力半導体構成要素の整流中、不均一に大きい逆電流密度によって寄生バイポーラトランジスタの電源が入るのを抑制する。更に、遮光源ゾーン領域を有する縁部構造体は、Nitta, et al. で論じられている科学技術条件で非常に簡単に製造できる。Nitta, et al. はパラメータの効果を明確にし、on 状態で導電し、off 状態では、導電しない平行 P N 層からなるドリフト層を有する超接合半導体ディバイスの大量生産を可能にしている。N 形のドリフト領域での作動不純物の総量は、P 形の区分領域の作動不純物の総量の 100% から 150% の範囲内である。加えて、N 形ドリフト領域と P 形区分領域とのいずれか一方の幅は、他方の領域の 94% から 106% の範囲内である。

【0 0 0 5】

米国特許第 6,300,171 号(Frisina)は、高電圧半導体ディバイスの縁部構造体の製造方法を開示する。この方法は、第 1 導電率形の第 1 半導体層を形成する第 1 工程と、この第 1 半導体層の頂面上に第 1 マスクを形成する第 2 工程と、このマスクの一部を除去して、マスクに少なくとも 1 つの開口部を形成する第 3 工程と、この少なくとも 1 つの開口部を介して、第 1 半導体層に第 2 導電率形のドーパントを導入する第 4 工程と、第 1 マスクを完全に除去し、第 1 半導体層上に、第 1 導電率形の第 2 半導体層を形成する第 5 工程と、第 1 半導体層に打込んだドーパントを拡散させて、第 1 および第 2 の半導体層に第

20

30

40

50

2導電率形のドープされた領域を形成する第6工程とを含む。第2工程から第6工程までを1回以上繰り返し、多数の第1導電率形の積層された半導体層と、第2導電率形の2列以上のドープ領域を含む最終縁部構造体を形成する。上記の列は、上記の多数の積層された半導体層に挿入され、その後マスクの開口部を介して打込まれたドープ領域を積層することにより形成され、高電圧半導体ディバイスに近い列は、それより遠い列よりも深い。

### 【0006】

半導体ディバイスの製造のため、唯一のエピタキシャル沈着工程を使用する方法に匹敵する技術を用いて製造される、イオンが打込まれていない、作動領域の最後の溝の外側壁を備えた縁部端子領域を提供することが望ましい。

【特許文献1】米国特許第5,216,275号

【特許文献2】米国特許第6,410,958号

【特許文献3】米国特許第6,300,171号

【特許文献4】米国特許第6,307,246号

### 【発明の開示】

#### 【課題を解決するための手段】

### 【0007】

簡単に述べると、本発明は、相互に対向する第1及び第2の主表面を有する半導体基板を設けることを含む半導体ディバイスの製造方法からなる。上記の半導体基板は、第2主表面に第1導電率形の強くドープされた領域を有し、第1主表面に第1導電率形の軽くドープされた領域を有する。この方法は、上記の半導体基板において、その作動領域に複数個の溝と複数個の台地(メサ)とをエッチングして設けることを含む。各溝は、強くドープされた領域に向か、第1主表面から第1深さ位置まで伸びる第1延長部分を有し、各メサは、第1主表面に対し所定の傾斜を維持する側壁面を有する。上記の複数個の溝の各々は、複数個のメサの1つにより、他の溝の各々から離れている。この方法は、作動領域と、作動領域の外側およびこれに隣接する端子領域内に伸びる、複数個のメサと複数個の溝との所定領域を、各メサの頂部、複数個の溝の各々の両側壁面および底部ならびに端子領域の頂部を酸化物が覆うまで酸化することを含む。この方法は、複数個のメサと複数個の溝との所定領域を、乾式酸化物エンチング法によってエッチングし、複数個の溝の底部にある酸化物を除去することを含む。この方法は、作動領域と端子領域との間の境界の所定領域上に保護シールドを形成し、その後複数個のメサと複数個の溝との所定領域の上から保護シールドを部分的に除去することを含む。この方法は、複数個のメサと複数個の溝との所定領域の少なくとも1つのメサに、隣接対の溝において、1つの溝の側壁面で、第1導電率形のドーパントを、第1所定打込み角度で打込み、上記の1つの溝の側壁面に、強くドープされた領域より低いドープ濃度を有する第1導電率形の第1ドープ領域を形成することを含む。また、この方法は、複数個のメサと複数個の溝との上記所定の少なくとも1つのメサに、第1導電率形のドーパントを打込んだ側壁に対向する上記少なくとも1つのメサの側壁面で、第2導電率形のドーパントを、第2所定打込み角度で打込んで、第1導電率形のドーパントを打込んだ側壁に対向する側壁面に第2導電率形の第2ドープ領域を設けて、複数個の溝の少なくとも1つの溝の深さ方向に沿って位置する第1および第2ドープ領域のP-N接合を形成すると共に、作動領域の、イオンが打込まれていない外側壁を設けることを含む。この方法は、複数個の溝に絶縁材料を充填し、構造体の頂面を平坦化して、超接合装置をこの構造体上に形成することを含む。

### 【0008】

本発明の第2実施例では、半導体ディバイスの製造方法は、第1及び第2の主表面を有する半導体基板を設けることを含む。この半導体基板は、第2主表面に第1導電率形の強くドープされた領域を有し、第1主表面に第1導電率形の軽くドープされた領域を有する。複数個の溝と複数個のメサとが基板に形成されており、各溝は、強くドープされた領域に向か、第1主表面から第1深さ位置まで伸びる第1延長部分を有し、その側壁面は、第1主表面に対し所定の傾斜を維持する。上記の複数個の溝の各々は、メサ領域により、他の溝から離れている。次の工程で、酸化物が沈着されて各メサの頂部ならびに各溝の

10

20

30

40

50

側壁と底部とを酸化物の厚い層で被覆する。この方法は乾式酸化物エンチング法を用いて、各溝の側壁上と底部にある酸化物を除去することを含む。ついで、最後の溝とこの溝に隣接するメサの一部分を除いて所定領域の溝とメサ上にマスクが置かれる。フォトレジストが沈着されて、マスクが取り除けられる。この方法は、所定領域の溝とメサとのイオン打込みを含む。然し、フォトレジストが最後の溝の上に置かれているので、この溝へのイオン打込みは阻止される。構造体の他方端上の最後の溝へのイオン打込みも、同様の方法で阻止される。マスクが置かれているので、フォトレジストが最後の溝と、これに隣接するメサの一部分上に沈着し、マスクが除かれる。この溝へのイオン打込みは、また、フォトレジストにより阻止される。最後の溝へのイオン打込みを阻止することにより、この基板の上に形成されるディバイスの雪崩破壊電圧の劣化を防ぐ。イオン打込み後フォトレジストが溝とメサとから取りのけられる。最後の溝を洗浄した後、全ての溝に絶縁材料が充填され、ディバイスの頂面が平坦化される。ついで基板が超接合装置の形成準備態勢にはいる。

10

【発明を実施するための最良の形態】

【0009】

上記の要約ならびに以下の本発明の好ましい実施例の詳細な説明は、添付図面と共に読めばより良く理解される。本発明を図示するため、図中には、現在好ましい実施例が図示されているが、本発明は、開示されている装置および手段そのものに限定されるものではない。

20

【0010】

ある種の言葉が便宜上のみ以下の記載に使用されているが、これに限るものではない。“右”、“左”、“下方”および“上方”的言葉は、言及している図面の方向を示すものである。“内方”および“外方”的言葉は、記載している物体とその示されている部分の幾何学的中心に向かうおよびこれから遠のく方向のことを言う。加えて、クレームおよび明細書の対応部分中で使われている“a”的言葉は“少なくとも1つの”を意味する。

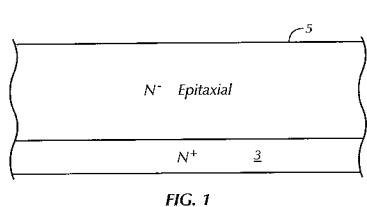

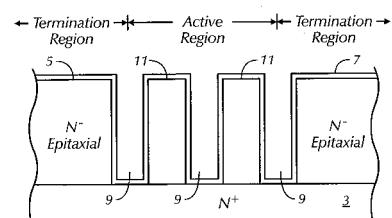

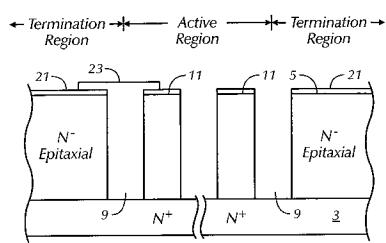

図1から図11は、本発明の第1の好ましい実施例による、従来の端子を備えた超接合装置の製造方法を示す。

【0011】

図1に関しては、強くドープされたN<sup>+</sup>基板3と軽くドープされたN<sup>-</sup>層5とを含む半導体ウエハの部分図が示されている。ここで用いられているように、導電率とは、記載の実施例に制限されるが、当業者であれば、P形導電率は、N形導電率に変えることができ、上記の半導体ディバイスはそれでも機能的には正しい(即ち、第1あるいは第2導電率形を用いると言っている。)ことが分かる。よって、ここで使用する場合、NまたはPと言っているのはNはPに置き換えることができ、PはNに置き換えることができることを意味する。

30

【0012】

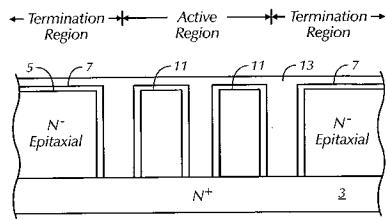

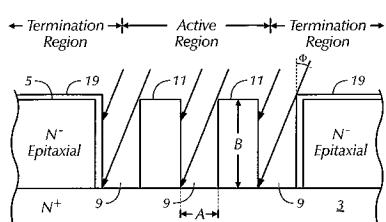

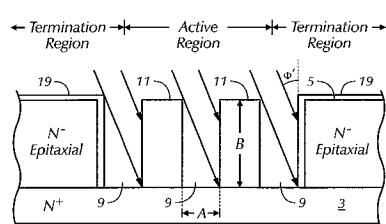

図2に関しては、当業界で周知の技術を用いて、N<sup>-</sup>層5がエッチングされて、エッチングで形成された溝の底部が、N<sup>+</sup>基板3と、N<sup>-</sup>層5と間の界面に接触あるいは接近している。このエッチング方法で、溝9とメサ11とが形成されている。メサ11は、この方法で、トランジスタ装置をその上に形成する構造体を形成する、周囲の端子領域に対向する作動領域にあるので、“ディバイス・メサ”と言う。メサ11に隣接する溝9の幅(A)はその他の溝と比べてほぼ同じである。明確には図示していないが、溝9は、各々、溝埋め方法を容易にするため各底部より各頂部において1%から10%分広いほうが好ましい。よって、メサ11の側壁面は、エピタキシャル層5の第1主表面に対し所定の傾斜を維持する。溝9が、基板(強くドープされている領域)3に向け、エピタキシャル層5の第1主表面から第1深さ位置まで深さ(B)で伸びているが、基板(強くドープされた領域)3に到る全ての距離に亘って延びる必要はない。

40

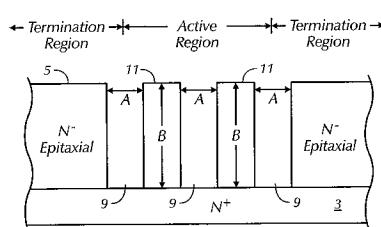

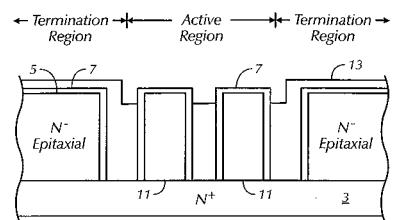

【0013】

図3は、化学蒸着法(CVD)により、深さ約1~3マイクロメータ(μm)の酸化物層7で各メサ11の頂部と各溝9とを被覆した後の複数個のメサ11と、複数個の溝9とを示

50

す。

【0014】

図4は、当業界では周知のタイプの乾式酸化物エッティング工程により、複数個の溝9の各々の底部から酸化物7を除去した後の図3の構造体を示す。

【0015】

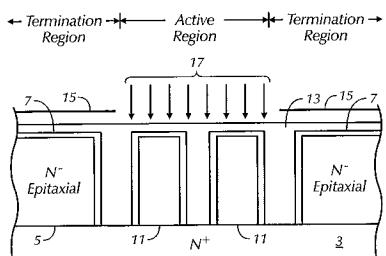

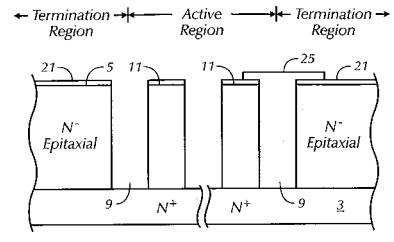

図5は、当業者には周知の方法でフォトレジストの層13を沈着させた後の図4の構造体を示す。

【0016】

図6は、マスク15(即ち、保護シールド)を置き、既知の反応体17を、マスク15では保護されない非保護フォトレジスト13に当てがった図5の構造体を示す。マスク15は、全ての端子領域と、作動領域と端子領域との間の境界に近接した所定の領域にある作動領域の一部との上に置くのが好ましい。既知の反応体17は紫外線光、深紫外線光、電子ビーム、X線等を含む。

【0017】

図7は、反応したフォトレジスト13は取り除かれ、反応しないフォトレジスト(以前はマスクの下にあったもの)が当業界では既知の場所に残っている図6の構造体を示す。

【0018】

図8は、湿式酸化物エッティング工程でフォトレジスト13と、作動領域の各側の最後の溝の外壁上と、端子領域の頂部上の酸化物19以外の酸化物を除いた後の図7の構造体を示す。

【0019】

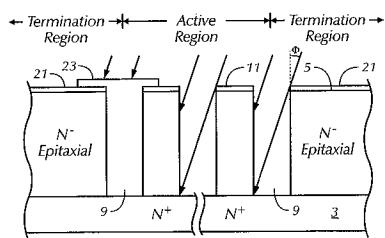

図9は、第1所定角度(即ち、第1所定打込み角度)で、図8の構造体へのイオン打込みを示す。第1所定打込み角度は、溝9の幅(A)と深さ(B)とで決定され、(即ち、 $A/B = \text{打込み角度}$ のタンジェント(正切))垂線から約2度から12度までである。イオンは、各溝9の底部に打込まれない角度で打ち込まれる。周囲の領域に打込みの拡散が起こらないよう溝9の底部へのイオンの打込みは回避される。イオンの打込みは、約30~200キロ電子ボルト(k eV)のエネルギー・レベルで、約 $1 E 1 3$ から $1 E 1 4 c m^{-2}$ の範囲(即ち、約 $1 \times 1 0^{13}$ から $1 \times 1 0^{14} c m^{-2}$ )のドープ量で行われる。よって、第1導電率形のドーパントは、複数個のメサと複数個の溝との所定領域の少なくとも1つのメサに、隣接する対の溝9において、1つの溝9の一側面で打込まれ、1つの溝9の一側面に、強くドープされた領域より低いドープ濃度を有する第1導電形の第1ドープ領域を形成する。図示のように、最後の溝9の外壁上の酸化物19(図9左側)がその面へのイオン打込みを阻止している。

【0020】

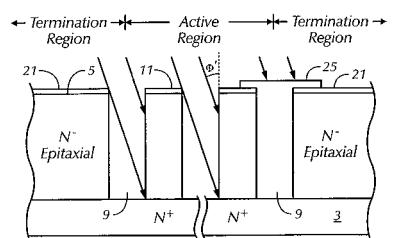

図10は、第2所定角度(即ち、第2所定打込み角度)での、図9の構造体へのイオン打込みを示す。第2所定打込み角度も、溝9の幅(A)と深さ(B)とで決定され、(即ち、 $-A/B = \text{打込み角度}$ のタンジェント)垂線から約-2度から-12度までである。イオンは、各溝9の底部に打込まれない角度で打ち込まれる。第1所定打込み角度と第2所定打込み角度とはほぼ同じ大きさでも、少し異なっていても良い。周囲の領域に打込みの拡散が起こらないよう溝9の底部へのイオンの打込みは回避される。イオンの打込みは、約30~200 k eVのエネルギー・レベルで、約 $1 E 1 3$ から $1 E 1 4 c m^{-2}$ の範囲のドープ量で行われる。よって、第2導電率形のドーパントは、複数個のメサ11と複数個の溝との所定領域の少なくとも1つのメサ11に、第1導電率形のドーパントが打込まれた側壁と対向している上記の少なくとも1つのメサの側壁面に打込まれ、第1導電率形のドーパントが打込まれた側壁に対向する側壁面に第2導電率形の第2ドープ領域を設け、複数個の溝9の少なくとも1つの深さ方向にそって位置する第1および第2ドープ領域のP-N接合を形成すると共に、作動領域の、イオンが打込まれていない外側壁を設ける。図示のように、最後の溝9の外壁上の酸化物19(図9右側)がその面へのイオン打込みを阻止している。

【0021】

10

20

30

40

50

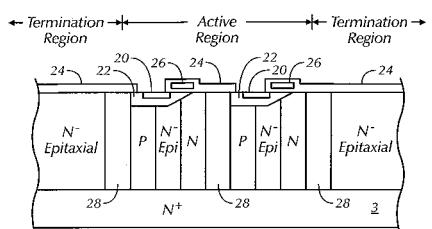

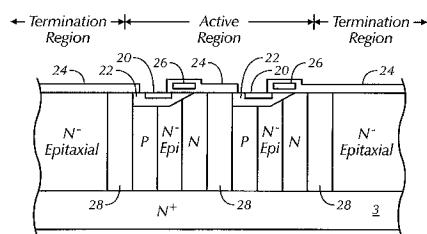

図11は、図9と図10の構造体の溝9から酸化物19が除去された後の第10の構造体に形成されている超接合装置を示す。全ての溝9に絶縁材料28が充填され、頂面が平坦化されている。構造体に超接合装置を製造した後イオン打込み22を行い、イオンを打込んだ領域にゲート20を沈着し、ゲート導電体26およびゲート酸化物24を加える。これら全ては、当業界で既知の方法で為される。よって、ゲート電極層20は、溝9の少なくとも1つでその第1主表面上に形成される。ゲート電極層20は、第1ドープ領域とオーム接觸しているが、ショットキー(Schottky)接觸しているほうが好ましい。

#### 【0022】

この構造体に建造ないし形成された装置の性能は、従来の半導体トランジスタ装置に比べて、雪崩破壊電圧(Vb)特性が向上している。第2ドープ領域と電気的に連結する第3ドープ領域を第1および第2ドープ領域の第1主表面に設け、第1導電率形の第4ドープ領域を、これが第3ドープ領域を挟んで第1ドープ領域と対向するように、上記の1つの溝9の第1主表面と側壁面の1方あるいは両方に設けることにより追加の打込みをすることもできる。ゲート電極層20は、第1ドープ領域と第4ドープ領域との間で、ゲート絶縁層を介在させて第3ドープ領域に対向させて設けられている。

#### 【0023】

図12から図17図は、本発明の第2実施例による、従来の端子を備えた超接合装置を製造する方法を示す。

#### 【0024】

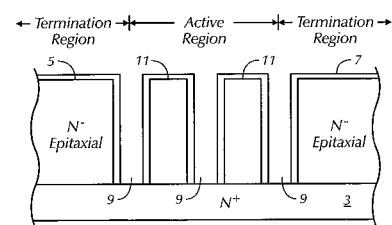

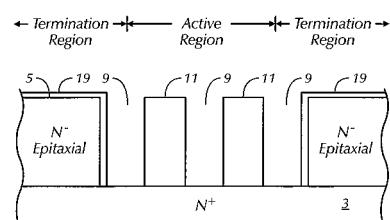

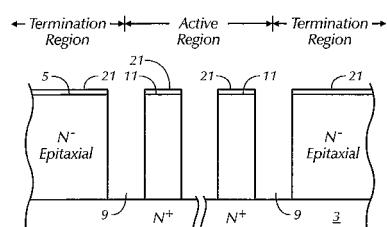

図12は、酸化物の沈着とその後の溝9の側壁と底部とのエッティング後の図2の構造体を示す。

#### 【0025】

図13は、マスク(図示されていないが、図6のマスクと同様のもの)が、作動領域の片側の最後の溝9(左側)と、これに隣接するメサ領域の一部にのみフォトレジスト23を沈着するため置かれ、フォトレジスト23が沈着された後の図12の構造体を示す。フォトレジスト23が溝の両側壁へのイオンの打込みを阻止する。

#### 【0026】

図15は、第1所定角度 $\theta_1$ での、図13の構造体へのイオン打込みを示す。第1所定角度 $\theta_1$ は、溝9の幅(A)と深さ(B)とで決定され、(即ち、 $A/B = \tan \theta_1$ )のタンジェントから約2度から12度までである。イオンは、各溝9の底部に打込まれない角度 $\theta_1$ で打ち込まれる。周囲の領域に打込みの拡散が起こらないよう溝9の底部へのイオンの打込みは回避される。イオンの打込みは、約30~200keVのエネルギー・レベルで、約1E13から1E14cm<sup>-2</sup>の範囲のドープ量で行われる。よって、第1導電率形のドーパントは、複数個のメサ11と複数個の溝9との所定領域のとくなくとも1つのメサに、隣接対の溝9において、1つの溝9の側壁面で、打込まれ、上記の1つの溝9の一側面に、強くドープされた領域より低いドープ濃度を有する第1導電形の第1ドープ領域を形成する。図示のように、最後の溝9のフォトレジスト23(左側)が溝9へのイオン打込みを阻止している。

#### 【0027】

図15は、マスク(図示されていないが、図6のマスクと同様のもの)を、最後の溝9(右側)と、図13のフォトレジスト23の位置とは反対側の作動領域側の、この溝と隣接するメサ領域の一部にのみフォトレジスト25を沈着するため置かれ、フォトレジスト25が沈着された後の図14の構造体を示す。フォトレジスト25は溝の両側壁へのイオンの打込みを阻止する。

#### 【0028】

図16は、第2所定角度 $\theta_2$ (即ち、第2所定打込み角度 $\theta_2$ )での、図15の構造体へのイオン打込みを示す。第2所定打込み角度 $\theta_2$ は、溝の幅(A)と深さ(B)とで決定され、(即ち、 $-A/B = \tan \theta_2$ )のタンジェントで)から約-2度から-12度までである。イオンは、各溝9の底部に打込まれない角度 $\theta_2$ で打ち込まれる。周囲の領域に打込みの拡散が起こらないよう溝9の底部にはイオンの打込みは回避される。イオン

10

20

30

40

50

の打込みは、約30から200keVのエネルギー・レベルで、約1E13から1E14 cm<sup>-2</sup>の範囲のドープ量で行われる。よって、第2導電率形のドーパントは、複数個のメサ11と複数個の溝との所定領域の少なくとも1つのメサ11に、第1導電率形のドーパントが打込まれた側壁に対向する上記の少なくとも1つのメサの側壁面で、打込まれ、第1導電率形のドーパントが打込まれた側壁に対向する側壁面に第2導電率形の第2ドープ領域を設け、複数個の溝9の少なくとも1つの深さ方向にそって位置する第1および第2ドープ領域のP-N接合を形成すると共に、作動領域の、イオンが打込まれていない外側壁を設ける。図示のように、最後の溝9のフォトレジスト25(右側)が溝9へのイオン打込みを阻止している。

## 【0029】

10

よって、第2の好ましい実施例では、最後の溝9(図中右あるいは左)上にフォトレジスト23、25が置かれ、溝9へのイオンの打込みが阻止されている。構造体の他端での最後の溝9へのイオンの打込みも同様に阻止される。最後の溝9(図中右と左)へのイオンの打込みを阻止することにより、基板上に形成されるディバイスの雪崩破壊電圧(V<sub>b</sub>)の劣化を防ぐ。フォトレジスト23、25はイオン打込み後メサ11及び溝9から取り除けられる。

## 【0030】

20

図17は、図14に示されているフォトレジスト23と図16に示されているフォトレジスト25が構造体から除去され、溝9に絶縁材料28が充填され、頂面が平坦化された後の図16に対応する構造体を示す。構造体に超接合装置を製造した後イオン打込み22を行い、イオンを打込んだ領域にゲート20を沈着し、ゲート導電体26およびゲート酸化物24を加える。これら全ては、当業界で既知の方法で為される。よって、ゲート電極層20は、溝9の少なくとも1つでその主表面上に形成される。ゲート電極層20は、第1ドープ領域とオーム接觸しているが、ショットキー(Schottky)接觸しているほうが好ましい。この構造体に建造ないし形成された装置の性能は、従来の半導体トランジスタ装置に比べて、雪崩破壊電圧(V<sub>b</sub>)特徴が向上している。

## 【0031】

30

第2ドープ領域のP-N接合を提供する。そして作動領域上に従来のMOS電界効果トランジスタ(MOSFET)装置が、ゲート酸化物層24の形成、ゲート導電体26の沈着と形成およびゲート電極20の沈着を含む周知の工程を用いて、作製される。選択的に第2導電率形の作動領域を打込み、その後選択的に第1導電率形の領域を打込む追加の工程によりディバイスが完成する。前面の領域と後面への接点も作られ、不動態化層が沈着され、パターン化されディバイスの製造順序が終了する。

## 【0032】

上記より、本発明は、半導体ディバイスおよび半導体ディバイスの製造方法に関する。当業者であれば、上記の実施例には、その広い発明概念から逸脱することなく変形が可能であることが感得せられる。よって、本発明は、開示されている特定の実施例に限定されるものではなく、本発明の精神内の変形例もカバーするものである。

## 【図面の簡単な説明】

## 【0033】

40

【図1】本発明の第1の好ましい実施例による、エピタキシャル層が当てがわれた半導体基板の部分断面図である。

【図2】エッチングでエピタキシャル層に溝を形成した後の図1の半導体基板およびエピタキシャル層の部分断面図である。

## 【図3】酸化物沈着工程後の図2の構造体の部分断面図である。

## 【図4】乾式エッチング工程後の図3の構造体の部分断面図である。

## 【図5】フォトレジスト層沈着後の図4の構造体の部分断面図である。

【図6】マスクが置かれ、開発媒体が非保護領域に当てがわれているのを示す図5の構造体の部分断面図である。

## 【図7】開発されたフォトレジストが取り除けられた後の図6の構造体の部分断面図であ

50

る。

【図 8】湿式酸化物エッチング法により、残っているフォトレジストと、作動領域の最後の溝の外壁上のもの以外の酸化物とを除いた後の図 7 の構造体の部分断面図である。

【図 9】第 1 打込み角度でのイオン打込みを示す図 8 の構造体の部分断面図である。

【図 10】第 2 打込み角度でのイオン打込みを示す図 8 の構造体の部分断面図である。

【図 11】図 10 の構造体に形成された超接合装置を示す部分断面図である。

【図 12】本発明の第 2 実施例による、酸化物の沈着と、その後の溝の側壁と底部とのエッチング後の図 2 対応の構造体を示す部分断面図である。

【図 13】構造体の片側の最後の溝をマスクすると共にフォトレジストを沈着させた後の図 12 の構造体を示す部分断面図である。

【図 14】或る第 1 角度でのイオン打込みを示す図 13 の構造体の部分断面図である。

【図 15】構造体の図 13 とは反対側の最後の溝にマスクをすると共に、フォトレジストを沈着させた後の図 12 の構造体を示す部分断面図である。

【図 16】或る第 2 角度でのイオン打込みを示す図 15 の構造体の部分断面図である。

【図 17】図 16 の構造体に形成された超接合装置を示す部分断面図である。

10

【図 1】

【図 3】

【図 2】

【図 4】

【図5】

FIG. 5

【図7】

FIG. 7

【図6】

FIG. 6

【図8】

FIG. 8

【図9】

FIG. 9

【図11】

FIG. 11

【図10】

FIG. 10

【図12】

FIG. 12

【図13】

FIG. 13

【図15】

FIG. 15

【図14】

FIG. 14

【図16】

FIG. 16

【図17】

FIG. 17

**【手続補正書】**

【提出日】平成19年2月1日(2007.2.1)

**【手続補正1】**

【補正対象書類名】特許請求の範囲

【補正対象項目名】全文

【補正方法】変更

**【補正の内容】**

【特許請求の範囲】

**【請求項1】**

半導体ディバイスの製造方法であって、

相互に対向する第1及び第2の主表面を有する半導体基板を設け、この半導体基板は、第2主表面に第1導電率形の強くドープされた領域を有し、第1主表面に第1導電率形の軽くドープされた領域を有し、

上記基板の作動領域に複数個の溝と複数個のメサとを形成し、各溝は、強くドープされた領域に向け、第1主表面から第1深さ位置まで延びる第1延長部分を有し、各メサは側壁面を有し、上記の複数個の溝の各々は、複数個のメサの1つにより、その他の溝の各々から離れていて、

作動領域と、作動領域の外側およびこれに隣接する端子領域内に延びる、複数個のメサと複数個の溝との所定領域上に、誘電体層が、複数個のメサのうち上記所定領域内の各メサの頂部、複数個の溝の各々の両側面および底部ならびに端子領域の頂部を覆うまで上記の誘電体層を形成し、

複数個のメサと複数個の溝との所定領域から上記の誘電体層を取り除いて、複数個の溝の底部にある誘電体層を除去し、

作動領域と端子領域との間の境界の領域上に保護シールドを形成し、

その後複数個のメサと複数個の溝との所定領域の上から保護シールドを部分的に除去し、

複数個のメサと複数個の溝との所定領域の少なくとも1つのメサに、隣接対の溝において、1つの溝の側壁面で、第1導電率形のドーパントを打込み、上記の1つの溝の側壁面に、強くドープされた領域より低いドープ濃度を有する第1導電率形の第1ドープ領域を形成し、

複数個のメサと複数個の溝との所定領域の上記少なくとも1つのメサに、第1導電率形のドーパントを打込んだ側壁に対向する上記の少なくとも1つのメサの側壁面で、第2導電率形のドーパントを打込んで、第1導電率形のドーパントを打込んだ側壁に対向する側壁に第2導電率形の第2ドープ領域を設けるもの。

**【請求項2】**

請求項1に記載した半導体ディバイスの製造方法であって、保護シールドを形成する工程が、

複数個のメサと複数個の溝との所定領域の上にフォトレジストの層を沈着させ、

複数個のメサと複数個の溝との所定領域の各側の最後の溝の外側壁上のフォトレジストが保護され、上記の所定領域の残りの個所は保護されないように、マスクを置き、

フォトレジストの保護されていない部分を、紫外線光、深紫外線光、電子ビームおよびX線を含むグループから選ばれたフォトレジスト反応体に晒すことからなるものにおいて、

上記の保護シールドを部分的に除去する工程が、

複数個のメサと複数個の溝との所定領域上からマスクを除き、

反応したフォトレジストを構造体から取除き、

複数個のメサと複数個の溝の所定領域を湿式エッチング法によりエッチングして、開発されなかったフォトレジストにより誘電体層が保護されていた、上記の所定領域の各側の最後の溝の外側壁をのぞいて、上記の所定領域から開発されなかったフォトレジストと誘電体層とを除去し、上記の誘電体層は上記の各最後の溝の外側壁へのイオン打込みを阻止

するため残されているもの。

【請求項 3】

請求項 2 に記載した半導体ディバイスの製造方法であって、

第 2 ドープ領域と電気的に連結する第 3 ドープ領域を第 1 および第 2 ドープ領域の第 1 主表面に設け、

第 1 導電率形の第 4 ドープ領域を、これが第 3 ドープ領域を挟んで第 1 ドープ領域と対向するように、上記の 1 つの溝の第 1 主表面と側壁面の少なくとも一方に設け、

ゲート電極層を、第 1 ドープ領域と第 4 ドープ領域との間で、ゲート絶縁層を介在させて第 3 ドープ領域に対向させて設けることからなるもの。

【請求項 4】

請求項 3 に記載した半導体ディバイスの製造方法であって、ゲート電極層が少なくとも 1 つの溝に形成されるもの。

【請求項 5】

請求項 3 に記載した半導体ディバイスの製造方法であって、ゲート電極層が第 1 主表面上に形成されるもの。

【請求項 6】

請求項 1 に記載した半導体ディバイスの製造方法であって、保護シールドを形成する工程が、

複数個のメサと複数個の溝との所定領域を乾式エッチング法を用いてエッチングして、複数個の溝の各々の両側部と底部とにある誘電体層を除去し、

マスクを、このマスクの開口部のみが、作動領域の各側の最後の溝とこれに隣接するメサ領域上に位置するように位置決めし、

作動領域の最後の溝とこれに隣接するメサ領域のみが、フォトレジストが沈着する領域であるようにフォトレジストの層をマスク上に沈着させることからなるものにおいて、

部分的に保護シールドを除去する工程が、最後の溝とこれに隣接するメサ領域とを除いて、フォトレジストが沈着するのを阻止したマスクを除去することからなるもの。

【請求項 7】

請求項 6 に記載した半導体ディバイスの製造方法であって、更に、

第 2 ドープ領域と電気的に連結する第 3 ドープ領域を第 1 および第 2 ドープ領域の第 1 主表面に設け、

第 1 導電率形の第 4 ドープ領域を、これが第 3 ドープ領域を挟んで第 1 ドープ領域と対向するように、上記の複数個の溝の第 1 主表面と側壁面のいずれかに設け、

ゲート電極層を、第 1 ドープ領域と第 4 ドープ領域との間で、ゲート絶縁層を介在させて第 3 ドープ領域に対向させて設けることからなるもの。

【請求項 8】

請求項 6 に記載した半導体ディバイスの製造方法であって、ゲート電極層が第 1 主表面上に形成されるもの。

【請求項 9】

請求項 6 に記載した半導体ディバイスの製造方法であって、更に、

第 2 ドープ領域と電気的に連結する第 3 ドープ領域を第 1 および第 2 ドープ領域の第 1 主表面に設けることからなるもの。

【請求項 10】

請求項 6 に記載した半導体ディバイスの製造方法であって、更に、電極層を第 1 ドープ領域とオーム接觸させるもの。

【請求項 11】

請求項 6 に記載した半導体ディバイスの製造方法であって、更に、

半導体ディバイスの製造において第 1 および第 2 導電率形のドーパントの各々の拡散長さが、隣接対の溝の側壁面から、第 1 および第 2 ドープ領域の P - N 接合までの距離より長いもの。

【請求項 12】

請求項 1 に記載した半導体ディバイスの製造方法であって、更に、

第 2 ドープ領域と電気的に連結する第 3 ドープ領域を第 1 および第 2 ドープ領域の第 1 主表面に設けることからなるもの。

【請求項 13】

請求項 1 に記載した半導体ディバイスの製造方法であって、更に、

電極層を第 1 ドープ領域とショットキー (Schottky) 接触させることからなるもの。

【請求項 14】

請求項 1 に記載した半導体ディバイスの製造方法であって、

半導体ディバイスの製造において第 1 および第 2 導電率形のドーパントの各々の拡散長さが、隣接対の溝の側壁面から、第 1 および第 2 ドープ領域の P - N 接合までの距離より長いもの。

【請求項 15】

請求項 1 に記載した半導体ディバイスの製造方法であって、各側壁面が、第 1 主表面に対し所定の傾斜角度を維持するもの。

【請求項 16】

請求項 1 に記載した半導体ディバイスの製造方法であって、乾式エッチング法を用いて、複数個のメサと複数個の溝との所定領域から誘電体層を除去するもの。

【請求項 17】

請求項 1 に記載した半導体ディバイスの製造方法であって、第 1 導電率形のドーパントが第 1 所定打込み角度で打込まれるもの。

【請求項 18】

請求項 1 に記載した半導体ディバイスの製造方法であって、第 2 導電率形のドーパントが第 2 所定打込み角度で打込まれるもの。

【請求項 19】

請求項 1 に記載した半導体ディバイスの製造方法であって、更に、

複数個の溝に絶縁材料を充填し、

構造体の頂面を平坦化して、

その構造体に超接合装置を形成するもの。

【請求項 20】

請求項 1 に記載した半導体ディバイスの製造方法によって形成された半導体ディバイス。

【請求項 21】

半導体ディバイスの製造方法であって、

相互に対向する第 1 及び第 2 の主表面を有する半導体基板を設け、この半導体基板は、第 2 主表面に第 1 導電率形の強くドープされた領域を有し、第 1 主表面に第 1 導電率形の軽くドープされた領域を有する、

上記基板の作動領域に複数個の溝と複数個のメサとを形成し、各溝は、強くドープされた領域に向け、第 1 主表面から第 1 深さ位置まで延びる第 1 延長部分を有し、各メサは側壁面を有し、上記の複数個の溝の各々は、複数個のメサの 1 つにより、他の溝の各々から離れていて、

作動領域と、作動領域の外側およびこれに隣接する端子領域内に伸びる、複数個のメサと複数個の溝との所定領域に、誘電体層が、複数個のメサのうち上記所定領域内の各メサの頂部、複数個の溝の各々の両側面および底部ならびに端子領域の頂部を覆うまで上記の誘電体層を形成し、

複数個のメサと複数個の溝との所定領域から上記の誘電体層を除去して、複数個の溝の底部にある誘電体層を除去し、

作動領域と端子領域との間の境界の領域上に保護シールド (遮蔽部) を形成し、

その後複数個のメサと複数個の溝との所定領域の上から保護シールドを部分的に除去し、

複数個のメサと複数個の溝との所定領域の少なくとも 1 つのメサに、隣接対の溝において、1 つの溝の側壁面で、第 1 導電率形のドーパントをドープし、上記の 1 つの溝の側壁

面に、強くドープされた領域より低いドープ濃度を有する第1導電率形の第1ドープ領域を形成し、

複数個のメサと複数個の溝との所定領域の上記少なくとも1つのメサに、第1導電率形のドーパントを打込んだ側壁に対向する上記の少なくとも1つのメサの側壁面で、第2導電率形のドーパントを、ドープし、第1導電率形のドーパントをドープした側壁に対向する側壁面に第2導電率形の第2ドープ領域を設けるもの。

#### 【請求項22】

請求項21に記載した半導体ディバイスの製造方法であって、保護シールドを形成する工程が、

複数個のメサと複数個の溝との所定領域の上にフォトレジストの層を沈着させ、

複数個のメサと複数個の溝との所定領域の各側の最後の溝の外側壁上のフォトレジストが保護され、上記の所定領域の残りの個所は保護されないように、マスクを置き、

フォトレジストの保護されていない部分を、紫外線光、深紫外線光、電子ビームおよびX線を含むグループから選ばれたフォトレジスト反応体に晒すことからるものにおいて、上記の保護シールドを部分的に除去する工程が

複数個のメサと複数個の溝との所定領域上からマスクを除き、

開発されたフォトレジストを構造体から取り除き、

複数個のメサと複数個の溝の所定領域を湿式エッチング法によりエッチングして、開発されなかったフォトレジストにより誘電体層が保護されていた、上記の所定領域の各側の最後の溝の外側壁をのぞいて、上記の所定領域から開発されなかったフォトレジストと誘電体層とを除去し、上記の誘電体層は上記の各最後の溝の外側壁へのイオン打込みを阻止するため残されているもの。

#### 【請求項23】

請求項22に記載した半導体ディバイスの製造方法であって、

第2ドープ領域と電気的に連結する第3ドープ領域を第1および第2ドープ領域の第1主表面に設け、

第1導電率形の第4ドープ領域を、これが第3ドープ領域を挟んで第1ドープ領域と対向するように、上記の1つの溝の第1主表面と側壁面の少なくとも1方に設け、

ゲート電極層を、第1ドープ領域と第4ドープ領域との間で、ゲート絶縁層を介在させて第3ドープ領域に対向させて設けることからなるもの。

#### 【請求項24】

請求項23に記載した半導体ディバイスの製造方法であって、ゲート電極層が少なくとも1つの溝に形成されるもの。

#### 【請求項25】

請求項23に記載した半導体ディバイスの製造方法であって、ゲート電極層が第1主表面上に形成されるもの。

#### 【請求項26】

請求項21に記載した半導体ディバイスの製造方法であって、保護シールドを形成する工程が、

複数個のメサと複数個の溝との所定領域を乾式エッチング法を用いてエッチングして、複数個の溝の各々の両側部と底部とにある誘電体層を除去し、

マスクを、このマスクの開口部のみが、作動領域の各側の最後の溝とこれに隣接するメサ領域上に位置するように位置決めし、

作動領域の最後の溝とこれに隣接するメサ領域のみが、フォトレジストが沈着する領域であるようにフォトレジストの層をマスク上に沈着させることからなるものにおいて、

部分的に保護シールドを除去する工程が、最後の溝とこれに隣接するメサ領域とを除去し、フォトレジストが沈着するのを阻止したマスクを除去することからなるもの。

#### 【請求項27】

請求項26に記載した半導体ディバイスの製造方法であって、更に、

第2ドープ領域と電気的に連結する第3ドープ領域を第1および第2ドープ領域の第1主

表面に設け、

第1導電率形の第4ドープ領域を、これが第3ドープ領域を挟んで第1ドープ領域と対向するように、上記の複数個の溝の第1主表面と側壁面のいずれかに設け、

ゲート電極層を、第1ドープ領域と第4ドープ領域との間で、ゲート絶縁層を介在させて第3ドープ領域に対向させて設けることからなるもの。

**【請求項28】**

請求項26に記載した半導体ディバイスの製造方法であって、ゲート電極層が第1主表面上に形成されるもの。

**【請求項29】**

請求項26に記載した半導体ディバイスの製造方法であって、更に、第2ドープ領域と電気的に連結する第3ドープ領域を第1および第2ドープ領域の第1主表面上に設けることからなるもの。

**【請求項30】**

請求項26に記載した半導体ディバイスの製造方法であって、更に、電極層を第1ドープ領域とオーム接触させるもの。

**【請求項31】**

請求項26に記載した半導体ディバイスの製造方法であって、更に、半導体ディバイスの製造において第1および第2導電率形のドーパントの各々の拡散長さが、隣接対の溝の側壁面から、第1および第2ドープ領域のP-N接合までの距離より長いもの。

**【請求項32】**

請求項21に記載した半導体ディバイスの製造方法であって、更に、第2ドープ領域と電気的に連結する第3ドープ領域を第1および第2ドープ領域の第1主表面上に設けることからなるもの。

**【請求項33】**

請求項21に記載した半導体ディバイスの製造方法であって、更に、電極層を第1ドープ領域とショットキー(Schottky)接觸させることからなるもの。

**【請求項34】**

請求項21に記載した半導体ディバイスの製造方法であって、半導体ディバイスの製造において第1および第2導電率形のドーパントの各々の拡散長さが、隣接対の溝の側壁面から、第1および第2ドープ領域のP-N接合までの距離より長いもの。

**【請求項35】**

請求項21に記載した半導体ディバイスの製造方法であって、複数個の溝の各側壁面が、第1主表面に対し所定の傾斜角度を維持するもの。

**【請求項36】**

請求項21に記載した半導体ディバイスの製造方法であって、乾式エッチング法を用いて、複数個のメサと複数個の溝との所定領域から誘電体層を除去するもの。

**【請求項37】**

請求項21に記載した半導体ディバイスの製造方法であって、第1導電率形のドーパントが第1所定打込み角度でドープされるの。

**【請求項38】**

請求項21に記載した半導体ディバイスの製造方法であって、第2導電率形のドーパントが第2所定打込み角度でドープされるもの。

**【請求項39】**

請求項21に記載した半導体ディバイスの製造方法であって、更に、複数個の溝に絶縁材料を充填し、構造体の頂面を平坦化して、その構造体に超接合装置を形成するもの。

**【請求項40】**

請求項 2 1 に記載した半導体ディバイスの製造方法によって形成された半導体ディバイス。

。

**【請求項 4 1】**

以下の製造方法によって、形成された半導体ディバイスであって、その方法は、

相互に対向する第 1 及び第 2 の主表面を有する半導体基板を設け、上記の半導体基板は、第 2 主表面に第 1 導電率形の重くドープされた領域を有し、第 1 主表面に第 1 導電率形の軽くドープされた領域を有する、

上記の半導体基板において、その作動領域に複数個の溝と複数個のメサとを形成し、各溝は、強くドープされた領域に向か、第 1 主表面から第 1 深さ位置まで延びる第 1 延長部分を有し、各メサは側壁面を有し、上記の複数個の溝の各々は、複数個のメサの 1 つにより、その他の溝の各々から離れていて、

作動領域と、作動領域の外側およびこれに隣接する端子領域内に伸びる、複数個のメサと複数個の溝との所定領域を、複数個のメサのうち上記所定領域内の各メサの頂部、複数個の溝の各々の両側面および底部ならびに端子領域の頂部を酸化物が覆うまで酸化し、

複数個のメサと複数個の溝との所定領域とをエッチングして、複数個の溝の底部にある酸化物を除去し、

作動領域と端子領域との間の境界の所定領域上に保護シールドを形成し、

その後複数個のメサと複数個の溝との所定領域の上から保護シールドを部分的に除去し、

複数個のメサと複数個の溝との所定領域の上記少なくとも 1 つのメサに、隣接対の溝において、1 つの溝の側壁面で、第 1 導電率形のドーパントを打込み、上記の 1 つの溝の側壁面に、重たくドープされた領域より低いドープ濃度を有する第 1 導電率形の第 1 ドープ領域を形成し、

複数個のメサと複数個の溝との所定領域の少なくとも 1 つのメサに、第 1 導電率形のドーパントを打込んだ側壁に対向する上記の少なくとも 1 つのメサの側壁面で、第 2 導電率形のドーパントを打込んで、第 1 導電率形のドーパントを打込んだ側壁に対向する側壁面に第 2 導電率形の第 2 ドープ領域を設け、

複数個の溝に絶縁材料を充填し、

構造体の頂面を平坦化することからなるもの。

## 【国際調査報告】

60601440025

## INTERNATIONAL SEARCH REPORT

International application No.

PCT/US04/41302

## A. CLASSIFICATION OF SUBJECT MATTER

IPC(7) : H01L 21/336, 21/8238

US CL : 438/268, 212, 282, 289, 514

According to International Patent Classification (IPC) or to both national classification and IPC

## B. FIELDS SEARCHED

Minimum documentation searched (classification system followed by classification symbols)

U.S. : 438/268, 212, 282, 289, 514, 270, 271, 272

Documentation searched other than minimum documentation to the extent that such documents are included in the fields searched

Electronic data base consulted during the international search (name of data base and, where practicable, search terms used)

## C. DOCUMENTS CONSIDERED TO BE RELEVANT

| Category * | Citation of document, with indication, where appropriate, of the relevant passages | Relevant to claim No. |

|------------|------------------------------------------------------------------------------------|-----------------------|

| A          | US 6081009 (Neilson) 27 June 2000 (27.06.2000)                                     |                       |

| A          | US 6410958 (Usui et al.) 25 June 2002 (25.06.2002)                                 |                       |

Further documents are listed in the continuation of Box C.

See patent family annex.

|                                                                                                                                                                          |                                                                                                                                                                                                                                                   |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Special categories of cited documents:                                                                                                                                   |                                                                                                                                                                                                                                                   |

| "A" document defining the general state of the art which is not considered to be of particular relevance                                                                 | "T" later document published after the international filing date or priority date and not in conflict with the application but cited to understand the principle or theory underlying the invention                                               |

| "E" earlier application or patent published on or after the international filing date                                                                                    | "X" document of particular relevance; the claimed invention cannot be considered novel or cannot be considered to involve an inventive step when the document is taken alone                                                                      |

| "L" documents which may throw doubts on priority claim(s) or which is cited to establish the publication date of another citation or other special reason (as specified) | "Y" documents of particular relevance; the claimed invention cannot be considered to involve an inventive step when the document is combined with one or more other such documents, such combination being obvious to a person skilled in the art |

| "O" document referring to an oral disclosure, use, exhibition or other means                                                                                             |                                                                                                                                                                                                                                                   |

| "P" documents published prior to the international filing date but later than the priority date claimed                                                                  | "&" document member of the same patent family                                                                                                                                                                                                     |

Date of the actual completion of the international search

11 November 2005 (11.11.2005)

Date of mailing of the international search report

19 JUL 2006

Name and mailing address of the ISA/US

Mail Stop PCT, Attn: ISA/US

Commission for Patents

P.O. Box 1450

Alexandria, Virginia 22313-1450

Facsimile No. (703) 273-3201

Authorized officer

Ha Nguyen

Telephone No. 703-308-0956

Form PCT/ISA/210 (second sheet) (April 2005)

12.12.2006

---

## フロントページの続き

(81)指定国 AP(BW,GH,GM,KE,LS,MW,MZ,NA,SD,SL,SZ,TZ,UG,ZM,ZW),EA(AM,AZ,BY,KG,KZ,MD,RU,TJ,TM),EP(AT,BE,BG,CH,CY,CZ,DE,DK,EE,ES,FI,FR,GB,GR,HU,IE,IS,IT,LT,LU,MC,NL,PL,PT,RO,SE,SI,SK,TR),OA(BF,BJ,CF,CG,CI,CM,GA,GN,GQ,GW,ML,MR,NE,SN,TD,TG),AE,AG,AL,AM,AT,AU,AZ,BA,BB,BG,BR,BW,BY,BZ,CA,CH,CN,CO,CR,CU,CZ,DE,DK,DM,DZ,EC,EE,EG,ES,FI,GB,GD,GE,GH,GM,HR,HU,ID,IL,IN,IS,JP,KE,KG,KP,KR,KZ,LC,LK,LR,LS,LT,L,U,LV,MA,MD,MG,MK,MN,MW,MX,MZ,NA,NI,NO,NZ,OM,PG,PH,PL,PT,RO,RU,SC,SD,SE,SG,SK,SL,SY,TJ,TM,TN,TR,TT,TZ,UA,UG,US,UZ,VC,VN,YU,ZA,ZM,ZW