(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(45) 공고일자 2009년12월30일

(11) 등록번호 10-0934381

(24) 등록일자 2009년12월21일

(51) Int. Cl.

*H01L 33/00* (2006.01)

(21) 출원번호 10-2005-7019395

(22) 출원일자 2004년04월06일

심사청구일자 2007년03월28일

(85) 번역문제출일자 2005년10월12일

(65) 공개번호 10-2006-0015503

(43) 공개일자 2006년02월17일

(86) 국제출원번호 PCT/US2004/010385

(87) 국제공개번호 WO 2004/093267

국제공개일자 2004년10월28일

(30) 우선권주장

10/724,005 2003년11월26일 미국(US)

(뒷면에 계속)

(56) 선행기술조사문헌

US19975600483 A1

US6690268 B1

US20030116767 A1

전체 청구항 수 : 총 10 항

심사관 : 이용배

(54) 발광 디바이스

**(57) 요 약**

발광 디바이스와, 관련 컴포넌트, 시스템 및 방법이 개시되어 있다.

**대 표 도 - 도1**

## (72) 발명자

**브라운, 마이클, 그레고리**

미국, 메사추세츠 01879, 킹스보로, 33 잭키스 로드

**던칸, 스코트, 더블유**

미국, 메사추세츠 01810, 앤도버, 10 월텐 플레이스

## (30) 우선권주장

|            |             |        |

|------------|-------------|--------|

| 60/462,889 | 2003년04월15일 | 미국(US) |

| 60/474,199 | 2003년05월29일 | 미국(US) |

| 60/475,682 | 2003년06월04일 | 미국(US) |

| 60/503,653 | 2003년09월17일 | 미국(US) |

| 60/503,654 | 2003년09월17일 | 미국(US) |

| 60/503,661 | 2003년09월17일 | 미국(US) |

| 60/503,671 | 2003년09월17일 | 미국(US) |

| 60/503,672 | 2003년09월17일 | 미국(US) |

| 60/513,807 | 2003년10월23일 | 미국(US) |

| 60/514,764 | 2003년10월27일 | 미국(US) |

**특허청구의 범위**

청구항 1

삭제

청구항 2

삭제

청구항 3

삭제

청구항 4

삭제

청구항 5

삭제

청구항 6

삭제

청구항 7

삭제

청구항 8

삭제

청구항 9

삭제

청구항 10

삭제

청구항 11

삭제

청구항 12

삭제

청구항 13

삭제

청구항 14

삭제

청구항 15

삭제

청구항 16

삭제

청구항 17

삭제

청구항 18

삭제

청구항 19

삭제

청구항 20

삭제

청구항 21

삭제

청구항 22

삭제

청구항 23

기판과, 상기 기판에 의해 지지되는 광 발생 영역 및 상기 광 발생 영역에 의해 지지되는 제 1층을 포함하는 다층의 재료 스택을 제공하는 단계;

상기 제 1층과 광 발생 영역을 포함하는 상기 다층의 재료 스택으로부터 상기 기판을 분리하는 단계; 및

상기 제 1층 표면에 패턴을 형성하는 단계를 포함하되, 상기 제1층은 상기 패턴에 따라 공간적으로 변하는 유전체 기능을 가지며,

상기 광 발생 영역에서 발생된 광이 상기 제1층을 통하여 방출되는 상기 다층의 재료 스택으로부터 발광 디바이스를 형성하는 단계를 포함하는 것을 특징으로 하는 발광 디바이스의 제조방법.

청구항 24

삭제

청구항 25

제 23항에 있어서, 상기 기판을 분리하는 단계는 상기 제 1층과 상기 기판 사이에 배치된 접합층을 가열하는 단계를 포함하는 발광 디바이스의 제조방법.

청구항 26

제 25항에 있어서, 상기 접합층을 가열 단계는 상기 접합층의 적어도 일부를 분해하는 발광 디바이스의 제조방법.

청구항 27

제 25항에 있어서, 상기 접합층을 가열하는 단계는 상기 접합층을 레이저에 의해 방출된 복사선에 노출시키는 단계를 포함하는 발광 디바이스의 제조방법.

청구항 28

삭제

청구항 29

삭제

### 청구항 30

삭제

### 청구항 31

삭제

### 청구항 32

삭제

### 청구항 33

제 23항에 있어서, 상기 기판을 제거한 후에 상기 제 1층의 표면에 패턴을 형성하는 발광 디바이스의 제조방법.

### 청구항 34

제 33항에 있어서, 상기 패턴의 형성 단계는 나노리소그래피를 이용하는 단계를 포함하는 발광 디바이스의 제조 방법.

### 청구항 35

삭제

### 청구항 36

제 23항에 있어서, 상기 제 1층은 n-도핑 재료층을 포함하고, 상기 다층의 재료 스택은 p-도핑 재료층을 더 포함하며, 상기 광 발생 영역은 p-도핑 재료층과 n-도핑 재료층 사이에 있는 발광 디바이스의 제조방법.

### 청구항 37

삭제

### 청구항 38

제 23항에 있어서, 상기 제 1층의 표면은 크기가  $\lambda/5$  미만인 특징부들을 갖고, 상기  $\lambda$ 는 광 발생 영역에 의해서 발생되어 상기 발광 디바이스로부터 제 1층의 표면을 경유하여 나올 수 있는 광의 파장인 발광 디바이스의 제조방법.

### 청구항 39

삭제

### 청구항 42

제 23항에 있어서, 상기 패턴은 비주기적 패턴, 복합 주기적 패턴 및 0보다 큰 이조 파라미터를 갖는 패턴으로 이루어지는 군에서 선택되는 하나 이상의 패턴을 포함하는 발광 디바이스의 제조방법.

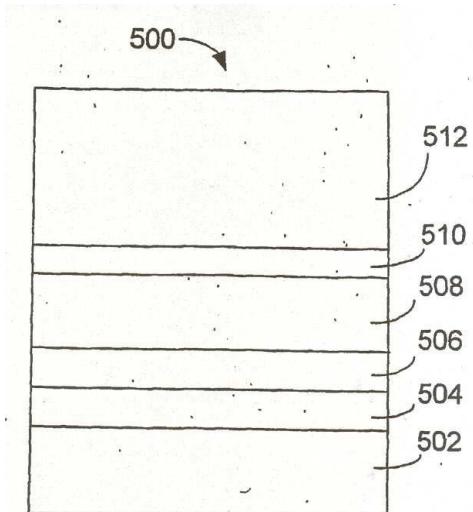

### 청구항 43

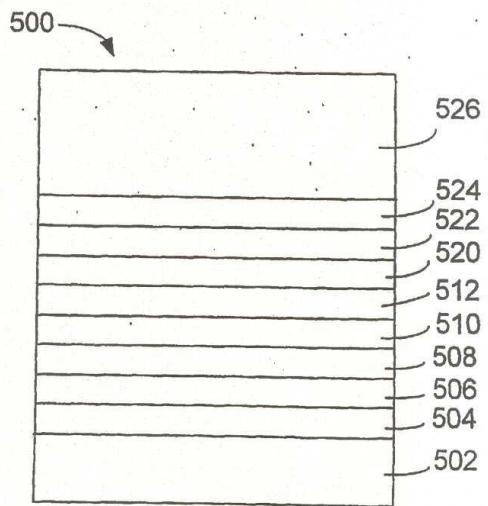

제 23항에 있어서, 개구들의 패턴이 상기 제1층의 표면에 형성되는 발광 디바이스의 제조방법.

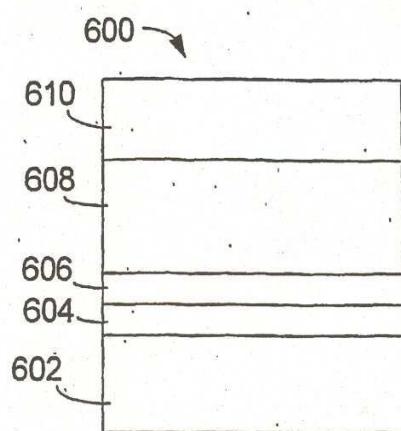

## 명세서

### 기술분야

<1> 본 발명은 디바이스와 관련 컴포넌트, 시스템 및 방법에 관한 것이다.

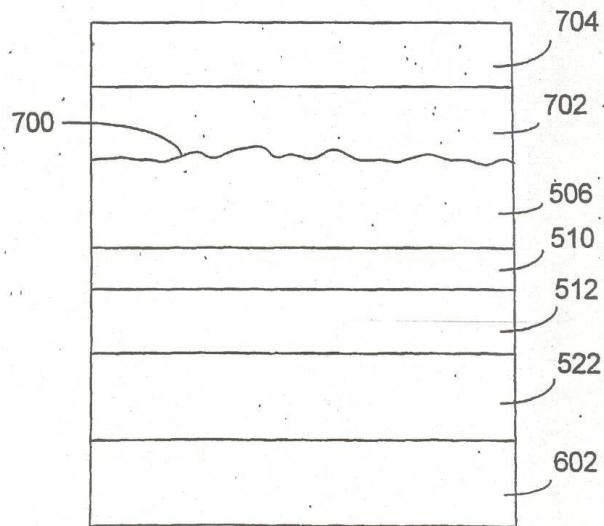

<2> 발광 다이오드(LED)는 흔히 백열 광원 및/또는 형광 광원보다 더욱 효율적인 방식으로 광을 제공할 수 있다. LED와 효율적으로 관련된 비교적 높은 전력은 다양한 조명 용례에서 종래의 광원을 교체하도록 LED를 사용함에

있어 흥미를 유발하였다. 예컨대, 어떤 경우에는 LED가 신호등으로서 그리고 휴대폰 키패드 및 디스플레이를 조명하도록 사용되고 있다.

<3> 통상, LED는 다층으로 구성되는데, 이 다층의 적어도 일부는 다른 재료로 형성된다. 일반적으로, 층에 선택된 재료와 두께는 LED에 의해 방출된 광의 파장(들)을 결정한다. 또한, 층의 화학적 조성은 광 파워로 비교적 효율적으로 전환하기 위해 영역(보통, 양자 웰(quantum well)이라 칭함)으로 주입된 전하 캐리어를 절연시키도록 선택될 수 있다. 일반적으로, 양자 웰이 성장되는 접합점의 한쪽 층은 공여 원자(donor atom)가 도핑되어 전자 농도가 높게 되고(그러한 층을 보통 n형 층이라 칭함), 반대쪽 층은 수용 원자(acceptor atom)가 도핑되어 홀 농도가 비교적 높게 된다(그러한 층을 보통 p형 층이라 칭함).

<4> LED를 제조하는 일반적인 방안은 다음과 같다. 재료의 층들은 웨이퍼 형태로 만들어진다. 통상, 금속-유기 화학적 기상 증착법(MOCVD) 등의 에피택셜 증착법을 이용하여 층들이 형성되고, 초기에 증착된 층은 성장 기판에 형성된다. 다음에, 층들은 다양한 식각 및 금속화 기법에 노출되어 전류 주입용 콘택을 형성하고, 이어서 웨이퍼는 개별적인 LED 칩으로 구획된다. 보통, LED 칩은 패키지된다.

<5> 사용 중에, 전기 에너지는 보통 LED로 주입된 다음 전자기 복사(광)로 전환되고, 그 일부는 LED로부터 추출된다.

### 발명의 상세한 설명

<26> 본 발명은 발광 디바이스와, 관련 컴포넌트, 시스템 및 방법에 관한 것이다.

<27> 일실시예에 있어서, 본 발명은 다층의 재료 스택을 포함하는 발광 디바이스를 특징으로 한다. 상기 다층의 재료 스택은 광 발생 영역과, 이 광 발생 영역에 의해 지지되는 제 1층을 포함한다. 상기 제 1층의 표면은 광 발생 영역에 의해 발생된 광이 발광 디바이스로부터 제 1층의 표면을 경유하여 나올 수 있도록 구성된다. 제 1층의 표면은 패턴에 따라 공간적으로 변하는 유전체 기능을 갖고, 상기 패턴은 이상적인 격자 상수 및 0보다 큰 값을 갖는 이조(離調) 파라미터(detuning parameter)를 갖는다.

<28> 다른 실시예에 있어서, 본 발명은 다층의 재료 스택을 포함하는 발광 디바이스를 특징으로 한다. 상기 다층의 재료 스택은 광 발생 영역과, 이 광 발생 영역에 의해 지지되는 제 1층을 포함한다. 상기 제 1층의 표면은 광 발생 영역에 의해 발생된 광이 발광 디바이스로부터 제 1층의 표면을 경유하여 나올 수 있도록 구성되며, 상기 표면은 비주기적인 패턴(nonperiodic pattern)에 따라 공간적으로 변하는 유전체 기능을 갖는다.

<29> 추가 실시예에 있어서, 본 발명은 다층의 재료 스택을 포함하는 발광 디바이스를 특징으로 한다. 상기 다층의 재료 스택은 광 발생 영역과, 이 광 발생 영역에 의해 지지되는 제 1층을 포함한다. 상기 제 1층의 표면은 광 발생 영역에 의해 발생된 광이 발광 디바이스로부터 제 1층의 표면을 경유하여 나올 수 있도록 구성되며, 상기 표면은 복합 주기적 패턴에 따라 공간적으로 변하는 유전체 기능을 갖는다.

<30> 일실시예에 있어서, 본 발명은 다층의 재료 스택을 포함하는 발광 디바이스를 특징으로 한다. 상기 다층의 재료 스택은 n-도핑 재료층과, p-도핑 재료층과, 광 발생 영역을 포함한다. 상기 발광 디바이스는 또한 상기 광 발생 영역에 의해 발생되어 충돌하는 광의 약 50% 이상을 반사할 수 있는 반사 재료층을 포함한다. 상기 n-도핑 재료층의 표면은 광 발생 영역에 의해 발생된 광이 발광 디바이스로부터 n 도핑 재료층의 표면을 경유하여 나올 수 있도록 구성된다. 상기 n-도핑 재료층의 표면은 패턴에 따라 공간적으로 변하는 유전체 기능을 갖고, p-도핑 재료층과 반사 재료층 사이의 거리는 n-도핑 재료층과 반사 재료층 사이의 거리보다 작다.

<31> 또 다른 실시예에 있어서, 본 발명은 광 발생 영역과, 이 광 발생 영역에 의해 지지되는 제 1층을 포함하는 다층의 재료 스택을 포함하는 발광 디바이스를 특징으로 한다. 상기 제 1층의 표면은 광 발생 영역에 의해 발생된 광이 발광 디바이스로부터 제 1층의 표면을 경유하여 나올 수 있도록 구성되며, 상기 제 1층의 표면은 패턴에 따라 공간적으로 변하는 유전체 기능을 갖는다. 상기 발광 디바이스는 또한 상기 광 발생 영역에 의해 발생되어 충돌하는 광의 약 50% 이상을 반사할 수 있는 반사 재료층을 포함한다. 상기 광 발생 영역은 반사 재료층과 제 1층 사이에 있으며, 상기 패턴은 제 1층을 지나서 연장되지 않는다.

<32> 추가 실시예에 있어서, 본 발명은 다층의 재료 스택을 포함하는 발광 디바이스를 특징으로 한다. 상기 다층의 재료 스택은 광 발생 영역과, 이 광 발생 영역에 의해 지지되는 제 1층을 포함한다. 상기 제 1층의 표면은 광 발생 영역에 의해 발생된 광이 발광 디바이스로부터 제 1층의 표면을 경유하여 나올 수 있도록 구성된다. 상기 발광 디바이스는 또한 제 1층의 표면과 접촉하는 재료를 포함하는데, 상기 재료의 굴절률은 1.5 미만이다. 상기 발광 디바이스는 패키지된다.

- <33> 일실시예에 있어서, 본 발명은 다층의 재료 스택을 포함하는 발광 디바이스를 특징으로 한다. 상기 다층의 재료 스택은 광 발생 영역과, 이 광 발생 영역에 의해 지지되는 제 1층을 포함한다. 상기 제 1층의 표면은 광 발생 영역에 의해 발생된 광이 발광 디바이스로부터 제 1층의 표면을 경유하여 나올 수 있도록 구성된다. 상기 제 1층의 표면은 패턴에 따라 공간적으로 변하는 유전체 기능을 갖는다. 상기 발광 디바이스는 또한 상기 제 1층의 표면에 의해 지지되는 형광 재료를 포함한다. 상기 발광 디바이스의 측벽에는 실질적으로 형광 재료가 없다.

- <34> 다른 실시예에 있어서, 본 발명은 웨이퍼 제조 방법을 특징으로 한다. 상기 방법은 웨이퍼의 표면 상에 형광 재료를 배치하는 단계를 포함한다. 상기 웨이퍼는 복수 개의 발광 디바이스를 포함한다. 각 발광 디바이스는 광 발생 영역과, 이 광 발생 영역에 의해 지지되는 제 1층을 포함하는 다층의 재료층을 포함한다. 상기 제 1층의 표면은 광 발생 영역에 의해 발생된 광이 발광 디바이스로부터 제 1층의 표면을 경유하여 나올 수 있도록 구성되고, 상기 제 1층의 표면은 패턴에 따라 공간적으로 변하는 유전체 기능을 갖는다.

- <35> 추가 실시예에 있어서, 본 발명은 다층의 재료 스택을 포함하는 발광 디바이스를 특징으로 한다. 상기 다층의 재료 스택은 광 발생 영역과, 이 광 발생 영역에 의해 지지되는 제 1층을 포함한다. 상기 제 1층의 표면은 광 발생 영역에 의해 발생된 광이 발광 디바이스로부터 제 1층의 표면을 경유하여 나올 수 있도록 구성되며, 상기 제 1층의 표면은 패턴에 따라 공간적으로 변하는 유전체 기능을 갖는다. 발광 디바이스는 또한 상기 광 발생 영역에 의해 발생되어 제 1층의 표면을 경유하여 나오는 광이 형광 재료와 상호 작용하여, 형광층으로부터 나오는 광이 실질적으로 백색 광이 되도록 구성되는 형광 재료를 포함한다. 상기 발광 디바이스의 높이 대 발광 디바이스의 면적의 비는 백색 광이 모든 방향에서 연장하기에 필요한 만큼 충분히 작다.

- <36> 일실시예에 있어서, 본 발명은 다층의 재료 스택을 포함하는 발광 디바이스를 특징으로 한다. 상기 다층의 재료 스택은 광 발생 영역과, 이 광 발생 영역에 의해 지지되는 제 1층을 포함한다. 상기 제 1층의 표면은 광 발생 영역에 의해 발생된 광이 발광 디바이스로부터 제 1층의 표면을 경유하여 나올 수 있도록 구성된다. 상기 발광 디바이스는 또한 상기 발광 디바이스로부터 나오는 광에 대해 실질적으로 투명인 재료로 구성되는 제 1시트와, 형광 재료를 포함하는 제 2시트를 포함한다. 상기 제 2시트는 상기 제 1시트에 인접한다. 상기 발광 디바이스는 패키지되고, 상기 제 1시트 및 제 2시트는 발광 디바이스 패키지의 일부를 형성한다.

- <37> 또 다른 실시예에 있어서, 본 발명은 광 발생 영역과, 이 광 발생 영역에 의해 지지되는 제 1층을 포함하는 다층의 재료 스택을 포함하는 발광 디바이스를 특징으로 한다. 상기 제 1층의 표면은 광 발생 영역에 의해 발생된 광이 발광 디바이스로부터 제 1층의 표면을 경유하여 나올 수 있도록 구성된다. 상기 제 1층의 표면은 패턴에 따라 공간적으로 변하는 유전체 기능을 갖고, 상기 패턴은 광 발생 영역에 의해 발생되어 발광 디바이스로부터 제 1층의 표면을 경유하여 나오는 광이 광의 람베르시안(Lambertian) 분포보다 양호하게 시준(collimate)되도록 구성된다.

- <38> 추가 실시예에서, 본 발명은 복수 개의 발광 디바이스를 포함하는 웨이퍼를 특징으로 한다. 발광 디바이스의 적어도 일부는 다층의 재료 스택을 포함한다. 상기 다층의 재료 스택은 광 발생 영역과, 이 광 발생 영역에 의해 지지되는 제 1층을 포함한다. 상기 제 1층의 표면은 광 발생 영역에 의해 발생된 광이 발광 디바이스로부터 제 1층의 표면을 경유하여 나올 수 있도록 구성된다. 상기 제 1층의 표면은 패턴에 따라 공간적으로 변하는 유전체 기능을 갖고, 상기 패턴은 광 발생 영역에 의해 발생되어 발광 디바이스로부터 제 1층의 표면을 경유하여 나오는 광이 광의 람베르시안(Lambertian) 분포보다 양호하게 시준되도록 구성된다. 상기 웨이퍼는 제곱 센티미터 당 적어도 약 5개(예컨대, 적어도 약 25개, 적어도 약 50개)의 발광 디바이스를 갖는다.

- <39> 일실시예에 있어서, 본 발명은 다층의 재료 스택을 포함하는 발광 디바이스를 특징으로 한다. 상기 다층의 재료 스택은 광 발생 영역과, 발광 디바이스의 사용 중에 광 발생 영역에 의해 발생된 광이 발광 디바이스로부터 제 1층의 표면을 경유하여 나올 수 있도록 상기 광 발생 영역에 의해 지지되는 제 1층을 포함한다. 상기 제 1층의 표면은 패턴에 따라 공간적으로 변하는 유전체 기능을 갖고, 상기 광 발생 영역에 의해 발생되어 발광 디바이스로부터 나오는 광의 총량 중 약 45% 이상(예컨대, 약 50% 이상, 약 60% 이상, 약 70% 이상)은 발광 디바이스의 표면을 경유하여 나온다.

- <40> 또 다른 실시예에 있어서, 본 발명은 다층의 재료 스택을 포함하는 발광 디바이스를 특징으로 한다. 상기 다층의 재료 스택은 광 발생 영역과, 발광 디바이스의 사용 중에 광 발생 영역에 의해 발생된 광이 발광 디바이스로부터 제 1층의 표면을 경유하여 나올 수 있도록 상기 광 발생 영역에 의해 지지되는 제 1층을 포함한다. 상기 발광 디바이스는 길이가 약 1 mm 이상(예컨대, 약 1.5 mm 이상, 약 2 mm 이상, 약 2.5 mm 이상)인 에지를 갖고, 발광 디바이스는 발광 디바이스의 추출 효율이 실질적으로 발광 디바이스의 에지 길이에 무관하도록 설계된다.

- <41> 추가 실시예에 있어서, 본 발명은 다층의 재료 스택을 포함하는 발광 디바이스를 특징으로 한다. 상기 다층의 재료 스택은 광 발생 영역과, 발광 디바이스의 사용 중에 광 발생 영역에 의해 발생된 광이 발광 디바이스로부터 제 1층의 표면을 경유하여 나올 수 있도록 상기 광 발생 영역에 의해 지지되는 제 1층을 포함한다. 상기 발광 디바이스는 길이가 약 1 mm 이상(예컨대, 약 1.5 mm 이상, 약 2 mm 이상, 약 2.5 mm 이상)인 에지를 갖고, 발광 디바이스는 발광 디바이스의 양자 효율이 실질적으로 발광 디바이스의 에지 길이에 무관하도록 설계된다.

- <42> 일실시예에 있어서, 본 발명은 다층의 재료 스택을 포함하는 발광 디바이스를 특징으로 한다. 상기 다층의 재료 스택은 광 발생 영역과, 발광 디바이스의 사용 중에 광 발생 영역에 의해 발생된 광이 발광 디바이스로부터 제 1층의 표면을 경유하여 나올 수 있도록 상기 광 발생 영역에 의해 지지되는 제 1층을 포함한다. 상기 발광 디바이스는 길이가 약 1 mm 이상(예컨대, 약 1.5 mm 이상, 약 2 mm 이상, 약 2.5 mm 이상)인 에지를 갖고, 발광 디바이스는 발광 디바이스의 벽 플러그 효율이 실질적으로 발광 디바이스의 에지 길이에 무관하도록 설계된다.

- <43> 또 다른 실시예에 있어서, 본 발명은 발광 디바이스의 제조 방법을 특징으로 한다. 상기 방법은 반사 재료층과 p-도핑 재료층을 접착하는 단계를 포함한다. 발광 디바이스는 p-도핑 재료층, 광 발생 영역 및 제 1층을 포함하는 다층의 재료 스택을 포함한다. 상기 제 1층은 패턴에 따라 공간적으로 변하는 유전체 기능을 갖는 표면을 포함하고, 반사 재료는 광 발생 영역에 의해 발생되어 반사 재료층에 충돌하는 광의 약 50% 이상을 반사할 수 있다.

- <44> 추가 실시예에 있어서, 본 발명은 발광 디바이스의 제조 방법을 특징으로 한다. 상기 방법은 제 1층에 접착된 기판을 분리하는 단계를 포함한다. 상기 제 1층은 광 발생 영역을 포함하는 다층의 재료 스택의 일부를 형성하고, 상기 방법은 제 1층의 표면이 패턴에 따라 공간적으로 변하는 유전체 기능을 갖는 표면을 포함하는 발광 디바이스를 형성한다.

- <45> 실시예들은 다음의 양태들 중 하나 이상을 특징으로 할 수 있다.

- <46> 다층의 재료 스택은 다층의 반도체 재료 스택으로 구성될 수 있다. 제 1층은 n-도핑 반도체 재료층일 수 있고, 다층 스택은 p-도핑 반도체 재료층을 더 포함할 수 있다. 광 발생 영역은 n-도핑 반도체 재료층과 p-도핑 반도체 재료층 사이에 있을 수 있다.

- <47> 발광 디바이스는 다층의 재료 스택을 지지하는 지지부를 더 포함할 수 있다.

- <48> 발광 디바이스는 광 발생 영역에 의해 발생되어 충돌하는 광의 약 50% 이상을 반사시킬 수 있는 반사 재료층을 더 포함할 수 있다. 반사 재료층은 상기 지지부와 다층의 재료 스택 사이에 있을 수 있다. p-도핑 반도체 재료층과 반사 재료층 사이의 거리는 n-도핑 반도체 재료층과 반사 재료층 사이의 거리보다 작을 수 있다. 발광 디바이스는 p-도핑 재료층과 반사 재료층 사이에 p-저항 접촉층을 더 포함할 수 있다.

- <49> 발광 디바이스는 제 1층과 광 발생 영역 사이에 전류 확산층을 더 포함할 수 있다.

- <50> 다층의 재료 스택은, 예컨대 III-V 반도체 재료, 유기 반도체 재료 및/또는 실리콘 등의 반도체 재료로 구성될 수 있다.

- <51> 몇몇 실시예에 있어서, 패턴은 광 발생 영역으로 연장되지 않는다.

- <52> 특정 실시예에 있어서, 패턴은 제 1층을 지나서 연장되지 않는다.

- <53> 몇몇 실시예에 있어서, 패턴은 제 1층을 지나서 연장된다.

- <54> 발광 디바이스는 발광 디바이스로 전류를 주입하도록 구성된 전기 콘택을 더 포함할 수 있다. 상기 전기 콘택은 발광 디바이스로 전류를 수직 방향으로 주입하도록 구성될 수 있다.

- <55> 패턴은, 예컨대 제 1층의 표면의 홀, 제 1층의 필라, 제 1층의 연속적인 베인, 제 1층의 비연속적인 베인 및 그들의 조합으로부터 선택된 컴포넌트로 부분적으로 구성될 수 있다.

- <56> 몇몇 실시예에 있어서, 패턴은 삼각형 패턴, 사각형 패턴 및 격자 패턴으로부터 선택될 수 있다.

- <57> 특정 실시예에 있어서, 상기 패턴은 비주기적인 패턴, 준결정 패턴, 로빈슨 패턴 및 암만 패턴으로부터 선택될

수 있다. 몇몇 실시예에 있어서, 상기 패턴은 펜로즈 패턴이다.

<58> 몇몇 실시예에 있어서, 상기 패턴은 허니컴 패턴 및 아르키메데스 패턴으로부터 선택된다. 특정 실시예에 있어서, 패턴(예컨대, 허니컴 패턴)은 직경이 상이한 홀을 가질 수 있다.

<59> 패턴은 부분적으로 제 1층의 표면에 있는 홀로 구성될 수 있다.

<60> 이조 파라미터는, 예컨대 이상적인 격자 상수의 약 1% 이상 및/또는 이상적인 격자 상수의 약 25% 이하일 수 있다. 몇몇 실시예에 있어서, 패턴은 실질적으로 임의로 이조화된 이상적인 패턴에 대응할 수 있다.

<61> 패턴은 제 1층의 표면에 의해 방출된 광이 복사 모드의 스펙트럼을 갖도록 구성될 수 있고, 복사 모드의 스펙트럼은 실질적으로 광 발생 모드의 독특한 방출 스펙트럼과 동일하다.

<62> 발광 디바이스는, 예컨대 발광 다이오드, 레이저 또는 광학 증폭기일 수 있다. 발광 디바이스의 예로는 유기 발광 디바이스(OLED), 평면 방출 LED 및 고휘도 발광 디바이스(HBLED)가 있다.

<63> 몇몇 실시예에 있어서, 제 1층의 표면의 특징부는 크기가 약  $\lambda/5$  미만이고, 여기서  $\lambda$ 는 제 1층에 의해 방출될 수 있는 광의 파장이다.

<64> 특정 실시예에 있어서, 발광 디바이스는 (예컨대, 패키지된 다이 형태로) 패키지된다. 몇몇 실시예에 있어서, 패키지된 발광 디바이스는 밀봉재가 없을 수 있다.

<65> 몇몇 실시예에 있어서, 제 1층의 표면과 접촉하는 재료는 가스(예컨대, 공기)이다. 상기 가스의 압력은 약 100 Torr 미만일 수 있다.

<66> 특정 실시예에 있어서, 제 1층의 표면과 접촉하는 재료의 굴절률은 약 1 이상이다.

<67> 몇몇 실시예에 있어서, 패키지된 LED는 커버를 포함한다. 상기 커버는 형광 재료를 포함할 수 있다. 커버는 광 발생 영역에 의해 발생되어 제 1층의 표면을 경유하여 나오는 광이 형광 재료와 상호 작용할 수 있고, 제 1층의 표면을 경유하여 나와서 형광 재료와 상호 작용하는 광이 실질적으로 백색 광으로서 커버로부터 나오도록 구성될 수 있다.

<68> 특정 실시예에 있어서, 발광 디바이스는 이 발광 디바이스로부터 나오는 광에 대해 실질적으로 투명인 재료를 포함하는 제 1시트와, 형광 재료를 포함하는 제 2시트를 더 포함할 수 있다. 상기 제 2시트는 제 1시트에 인접 할 수 있고, 굴절률이 약 1.5 미만인 재료는 제 1시트와 제 1층의 표면 사이에 있을 수 있다. 제 1 및 제 2시트는 광 발생 영역에 의해 발생되어 제 1층의 표면을 경유하여 나오는 광이 형광 재료와 상호 작용할 수 있고, 제 1층의 표면을 경유하여 나와서 형광 재료와 상호 작용하는 광이 실질적으로 백색 광으로서 제 2시트로부터 나오도록 구성될 수 있다.

<69> 형광 재료는 제 1층의 표면 상에 배치될 수 있다.

<70> 웨이퍼 제조 방법은 형광 재료를 배치하여 약 20% 미만 만큼 변하는 두께를 갖는 층을 형성하는 것을 포함할 수 있다. 상기 방법은 형광 재료층의 두께가 약 20% 미만 만큼 변하도록 형광 재료층을 평탄화하는 단계를 포함할 수 있다. 상기 방법은 또한 형광 재료를 제 1층의 표면 상에 배치한 후에 형광 재료를 평탄화하는 단계를 포함 할 수 있다. 형광 재료는, 예컨대 웨이퍼의 표면 상에 회전 코팅될 수 있다. 상기 방법은 웨이퍼로부터 복수 개의 발광 디바이스를 형성하고, 상기 발광 디바이스의 적어도 일부를 서로 분리시키는 단계를 포함할 수 있다.

<71> 몇몇 실시예에 있어서, 광 발생 영역에 의해 발생된 광이 발광 디바이스로부터 제 1층의 표면을 경유하여 나올 때, 제 1층의 표면을 경유하여 나오는 광의 약 40% 이상은 제 1층의 표면에 수직인 각도의 최대 약 30° 내에서 나온다.

<72> 특정 실시예에 있어서, 발광 디바이스의 충전 팩터는 약 10% 이상 및/또는 최대 약 75%이다.

<73> 발광 디바이스의 제조 방법은 반사 재료층을 p-도핑 재료층과 접합하기 전에, 제 1층을 기판과 접합하는 단계를 더 포함할 수 있고, 다층의 재료 스택은 기판과 반사 재료층 사이에 위치한다. 상기 방법은 또한 제 1층과 기판 사이에 접합층을 형성하는 단계를 포함할 수 있다. 상기 방법은 또한 기판을 제거하는 단계를 포함할 수 있다. 상기 방법은 기판을 제거한 후에 래핑 및 폴리싱하는 단계를 더 포함할 수 있다. 상기 기판은 반사 재료층을 제 1층과 접합한 후에 제거될 수 있다.

<74> 기판의 제거 단계는 제 1층과 기판 사이에 배치된 접합층을 가열하는 단계를 포함할 수 있다. 접합층 가열 단

계는 접합층의 적어도 일부를 분해할 수 있다. 접합층의 가열 단계는 접합층을 레이저에 의해 방출된 복사선에 노출시키는 단계를 포함할 수 있다. 기판의 제거 단계는 레이저 리프트오프 프로세스를 이용하여 기판을 노출시키는 단계를 포함할 수 있다. 기판을 제거하면 제 1층의 표면이 실질적으로 평탄하게 된다. 상기 방법은 제 1층의 표면에 패턴을 형성하기 전에 제 1기판을 제거한 후 제 1층의 표면을 평탄화하는 단계를 포함할 수 있다. 제 1층의 표면의 평탄화 단계는 제 1층의 표면의 화학-기계적 폴리싱 단계를 포함할 수 있다. 제 1층의 표면의 평탄화 단계는 제 1층의 표면 거칠기를 약  $\lambda/5$  이상으로 감소시킬 수 있는데, 여기서  $\lambda$ 는 제 1층에 의해 방출될 수 있는 광의 파장이다. 패턴의 형성 단계는 나노리소그래피를 이용하는 단계를 포함할 수 있다. 상기 방법은 또한 반사 재료층 상에 기판을 배치하는 단계를 포함할 수 있다. 상기 방법은 제 1층과 광 발생 영역 사이에 전류 확산층을 배치하는 단계를 더 포함할 수 있다.

- <75> 실시예들은 다음의 이점 중 하나 이상을 특징으로 할 수 있다.

- <76> 특정 실시예에 있어서, LED 및/또는 비교적 큰 LED 칩은 비교적 높은 광 추출을 보일 수 있다.

- <77> 몇몇 실시예에 있어서, LED 및/또는 비교적 큰 LED 칩은 비교적 높은 표면 휘도, 비교적 높은 평균 표면 휘도, 열 방산에 대한 비교적 낮은 필요성 또는 비교적 높은 열 방산률, 비교적 낮은 너비(etendue) 및/또는 비교적 높은 전력 효율을 보일 수 있다.

- <78> 특정 실시예에 있어서, LED 및/또는 비교적 큰 LED 칩은 LED/LED 칩에 의해 방출된 비교적 적은 광이 패키징에 의해 흡수되도록 설계될 수 있다.

- <79> 몇몇 실시예에 있어서, 밀봉 재료를 사용하지 않고 패키지된 LED(예컨대, 비교적 큰 패키지된 LED)가 준비될 수 있다. 이로 인해, 특정한 밀봉 재료의 사용과 관련된 특정 문제, 예컨대 성능 감소 및/또는 시간의 함수로서 불균일한 성능을 피하는 패키지된 LED가 생김으로써, 비교적 긴 시간에 걸쳐서 비교적 양호하고 및/또는 신뢰성 있는 성능을 나타낼 수 있는 패키지된 LED를 제공할 수 있다.

- <80> 특정 실시예에 있어서, LED(예컨대, 비교적 큰 패키지된 LED일 수 있는 패키지된 LED)는 비교적 균일한 형광 재료 코팅을 포함할 수 있다.

- <81> 몇몇 실시예에 있어서, LED(예컨대, 비교적 큰 패키지된 LED일 수 있는 패키지된 LED)는 특정한 각도 범위 내에서(예컨대, LED 표면 범위에 대해 특정한 각도 범위 내에서) 원하는 광 출력력을 제공하도록 설계될 수 있다.

- <82> 몇몇 실시예에 있어서, LED 및/또는 비교적 큰 LED 칩은 비교적 저렴한 프로세스에 의해 제조될 수 있다.

- <83> 특정 실시예에 있어서, LED 및/또는 비교적 큰 LED 칩은 프로세스를 경제적으로 실시하기 어렵게 하는 비용을 지불하지 않고도 상업적 척도상 수행될 수 있는 프로세스에 의해 제조될 수 있다.

- <84> 본 발명의 특징 및 이점은 상세한 설명, 도면 및 정구범위에서 알 수 있다.

- <85> 이하에서는, 도면에 대한 구체적인 설명과 함께 본 발명을 보다 상세하게 설명한다.

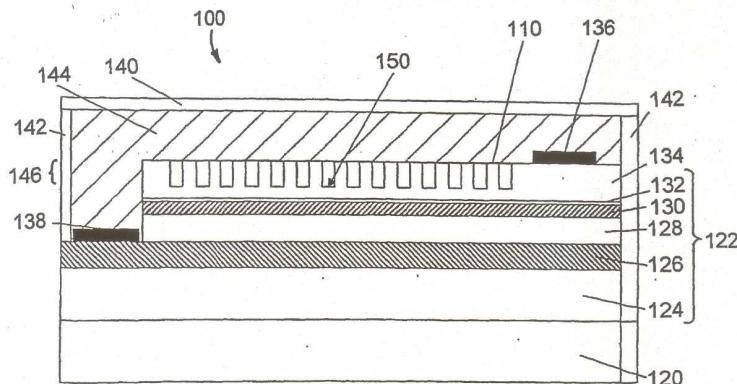

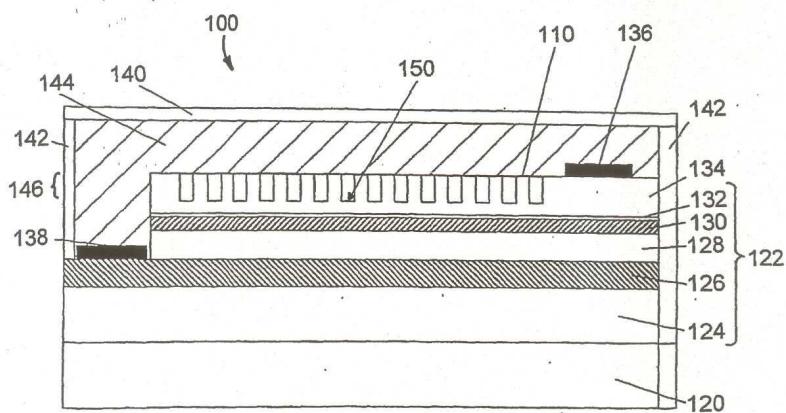

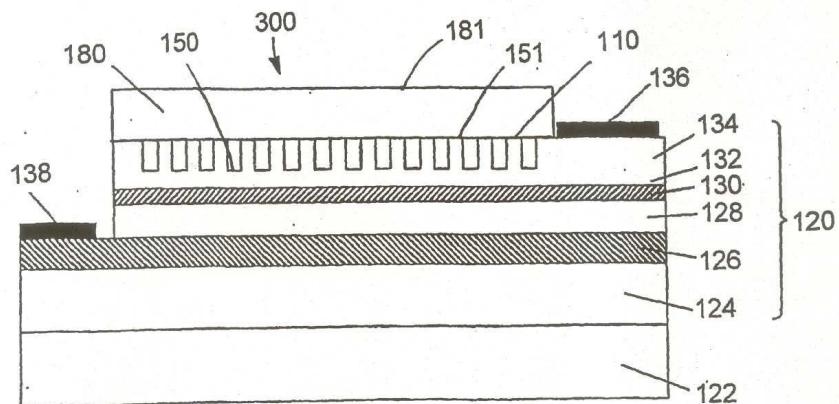

- <86> 도 1은 패키징 다이 형태의 발광 다이오드(100)의 측면도이다. 발광 다이오드(100)는 서브마운트(submount)(120) 상에 배치된 다층 스택(122)을 포함한다. 다층 스택(122)은, 그 상부면(110)에 개구(150)의 패턴을 가지며, 320nm 두께의 실리콘 도핑된 (n-doped) GaN 층(134)을 포함한다. 다층 스택(122)은 또한 접착층(124), 100nm 두께의 실버층(126), 40nm 두께의 마그네슘 도핑된 (p-doped) GaN 층(128), 다층 InGaN/GaN 양자 웨로 이루어진 120nm 두께의 광-발생 영역(130), AlGaN 층(132)을 포함한다. 상기 층(134) 위에 n-측면 콘택 패드(136)가 배치되고, 실버층(126) 위에 p-측면 콘택 패드(138)가 배치된다. 상기 층(134), 커버 슬립(140) 및 지지부(142) 사이에 밀봉재(1.5의 굴절률을 갖는 에폭시)(144)가 개재된다. 상기 밀봉재의 층(144)은 개구(150) 내로 연장되지 않는다.

- <87> 발광 다이오드(100)로부터의 광 발생 과정은 다음과 같다. P-측면 콘택 패드(138)가 n-측면 콘택 패드(136)에 대해 양전위로 유지되어, 발광 다이오드(100) 내로 전류 유입을 야기한다. 전류가 광-발생 영역(130)을 통과할 때 n-도핑 층(134)으로부터의 전자가 상기 영역(130)에서 상기 p-도핑 층(128)으로부터의 홀에 결합되어 상기 영역(130)에서 광 발생을 야기한다. 광-발생 영역(130)은 다수의 포인트 쌍극자 방사원을 포함하며, 방사원은 상기 영역(130) 내에서 상기 광-발생 영역(130) 구성 재료의 특징적인 파장의 스펙트럼으로 발광한다(예, 등방성 발광). InGaN/GaN 양자 웨의 경우, 상기 영역(130)에 의해 발생된 광의 파장의 스펙트럼은 약 445나노미터(nm)의 피크 파장과 약 30nm의 반지전폭(full width at half maximum; FWHM)을 가질 수 있다.

- <88> p-도핑층(126)의 전하 캐리어는 n-도핑 반도체층(134)에서의 전하 캐리어에 비해 그 이동도(mobility)가 비교적

낫다는 것에 주목할 필요가 있다. 결국, p-도핑층(128)의 표면을 따라 실버층(126)(전도성임)을 배치하는 것은 콘택 패드(138)로부터 p-도핑층(128) 및 광-발생 영역(130)으로의 전하 주입의 균일성을 향상시킬 수 있다. 이는 또는 발광 다이오드(100)의 전기적 저항을 감소시키고, 또는 발광 다이오드(100)의 주입 효율을 증가시킬 수 있다. n-도핑층(134)의 비교적 높은 전하 캐리어 이동도 때문에, 전자는 층(132 및 134)의 전반에 걸쳐 n-측면 콘택 패드(136)로부터 비교적 신속하게 분산될 수 있으며, 그에 따라 광-발생 영역(130) 내의 전류 밀도는 상기 영역(130)에 걸쳐 실질적으로 균일하다. 또한 주목할 사항으로서, 실버층(126)은 비교적 높은 열전도도를 가지고 있어서, 실버층(126)이 발광 다이오드(100)의 히트 싱크(다층 스택(122)으로부터 서브마운트(120)로 수직으로 열전달함)로서 기능한다는 점이다.

<89> 영역(130)에서 발생된 광 중 적어도 일부는 상기 실버층(126)을 향한다. 이 광은 실버층(126)에 의해 반사되어 표면(110)을 경유하여 발광 다이오드(100)로부터 나오거나, 실버층(126)에 의해 반사된 후 발광 다이오드(100) 내의 반도체 재료 내에 흡수되어 상기 영역(130) 내에 결합될 수 있는 전자-홀 쌍을 생성함으로써 상기 영역(130)에서 발광이 이루어지도록 한다. 유사하게, 상기 영역(130)에서 발생된 광중 적어도 일부의 광이 패드(136)를 향한다. 패드(136)의 저면은 상기 광-발생 영역(130)에서 발생된 광중 적어도 일부의 광을 반사시킬 수 있는 재료(예, Ti/AI/Ni/Au 합금)로 구성된다. 따라서, 패드(136)로 진행한 광은 패드(136)에 의해 반사되어 연속하여 표면(110)을 경유하여 발광 다이오드(100)로부터 출사되거나(예, 실버층(126)으로부터 반사되는 것에 의해), 또는 패드(136)로 진행된 광은 패드(136)에 의해 반사된 후 발광 다이오드(100) 내의 반도체 재료 내에 흡수되어 상기 영역(130) 내에 결합될 수 있는 전자-홀 쌍을 생성함으로써 상기 영역(130)에서 발광이 이루어지도록 할 수 있다(예, 실버층(126)에 의한 반사를 동반하거나 동반하지 않음).

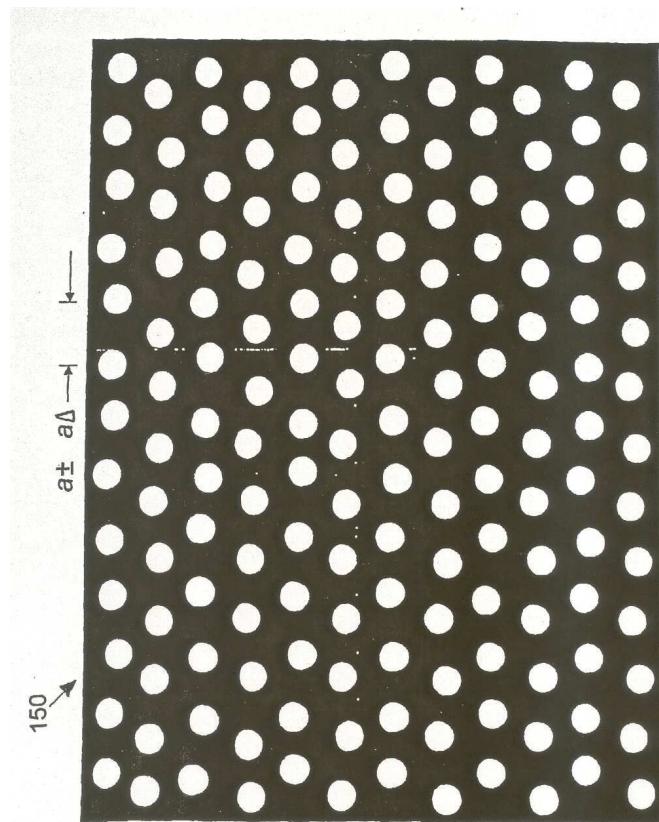

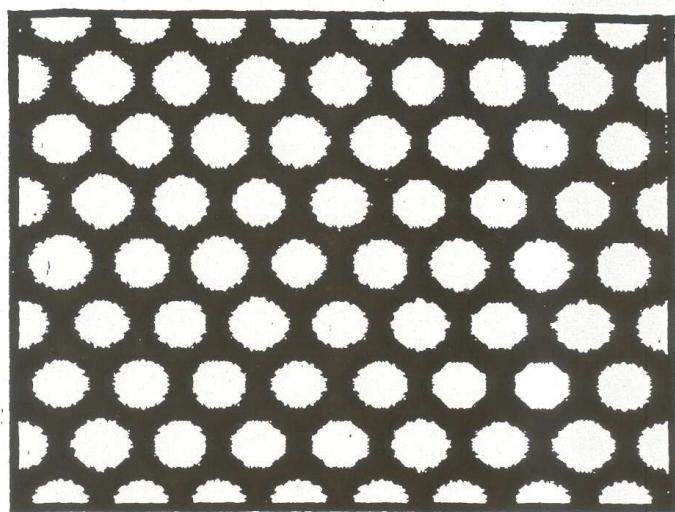

<90> 도 1 및 도 2에 도시된 바와 같이, 발광 다이오드(100)의 표면(110)은 편평하지 않으며 변형된 삼각형 패턴의 개구(150)로 이루어져 있다. 일반적으로, 개구(150)의 깊이는 다양한 값으로 선택할 수 있으며, 이 개구(150)의 직경과 최근접 개구(150) 간의 간격은 변화될 수 있다. 달리 지시된 바가 없으면, 수치 계산의 결과를 보여주는 하기의 도식을 위해, 개구(150)는 그 깊이(146)가 약 128nm이고, 약 160nm의 비-제로 직경(non-zero diameter), 약 220nm의 최근접 간의 간격 및 1.0의 굴절률을 갖는다. 삼각형 패턴은 이조되어(detuned) 있어서, 패턴(150)의 최근접 패턴들은  $(a - \Delta a)$ 와  $(a + \Delta a)$  사이의 수치를 갖는 중심간 거리를 갖는다. 이때, 상기 "a"는 이상적인 삼각형 패턴의 격자 상수이고, " $\Delta a$ "는 길이 치수의 이조 파라미터(detuning parameter)이며, 상기 이조는 임의 방향으로 일어날 수 있다. 발광 다이오드(100)로부터의 광추출(하기 설명 참조)을 향상시키기 위해,  $\Delta a$ 의 이조 파라미터는 일반적으로 이상적 격자 상수 a의 적어도 약 1%(예, 적어도 약 2%, 약 3%, 약 4%, 약 5%)이고, 및/또는 이상적 격자 상수 a의 최대 약 25%(예, 최대 약 20%, 약 15%, 약 10%)이다. 몇몇 실시예에서, 최근접 간격은 패턴(150)이 실질적으로 임의로 이조되도록  $(a - \Delta a)$ 와  $(a + \Delta a)$  사이에서 실질적으로 임의로 변화된다.

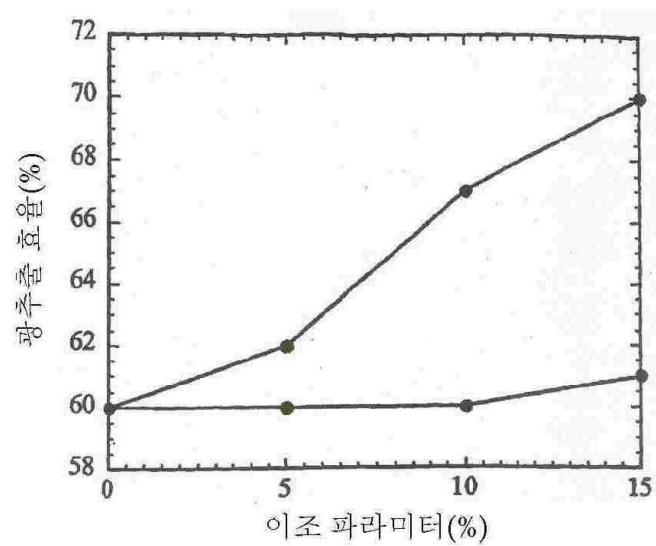

<91> 변형 삼각형 패턴의 개구(150)의 경우, 비-제로 이조 파라미터가 발광 다이오드(100)의 광추출 효율을 향상시키는 것이 확인되었다. 전술한 발송 다이오드(100)의 경우, 이조 파라미터( $\Delta a$ )가 0에서 약 0.15a로 증가됨에 따라, 발광 다이오드(100)의 전자기장의 수치 모델링(하기에 설명됨)은 도 3에 도시된 바와 같이 발광 다이오드의 광추출 효율이 0.60에서 약 0.70으로 증가함을 보여주고 있다.

<92> 도 3에 도시된 광추출 효율 데이터는 3차원 유한-차분 시간-영역법(finite-difference time-domain(FDTD) method)을 이용하여 발광 다이오드(100) 내외의 광에 대한 맥스웰 방정식에서 적절한 해로써 계산된다. 예컨대, 본원에 참조로 언급된 K.S. Kunz 및 R.J. Luebbers의 'The Finite-Difference Time-Domain Methods'(1993년, 플로리다, 보카 라톤의 CRC 출판); A. Taflove의 'Computational Electrodynamics: The Finite-Difference Time-Domain Method'(1995년, 런던, 아키텍트 하우스 출판)를 참조할 수 있다.

<93> 특정 패턴(150)의 발광 다이오드(100)의 광학적 거동을 표현하기 위해, FDTD 계산에서의 입력 파라미터는 광-발생 영역(130)에서 포인트 쌍극자 방사원에 의해 발광된 광의 중심 주파수 및 대역폭, 다층 스택(122) 내의 층의 크기 및 유전 특성, 및 패턴(150)내 개구의 직경, 깊이, 및 개구간 최근접 거리(nearest neighbor distance:NND)를 포함한다.

<94> 소정 실시예에서, 발광 다이오드(100)의 광추출 효율 데이터는 FDTD 방법을 이용하여 다음과 같이 계산된다. 상기 FDTD 방법은 풀-벡터(full-vector) 시간 의존적 Maxwell 방정식을 푸는데 이용된다.

$$\vec{\nabla} \times \vec{E} = -\mu \frac{\partial \vec{H}}{\partial t}, \quad \vec{\nabla} \times \vec{H} = \epsilon \frac{\partial \vec{E}}{\partial t} + \frac{\partial \vec{P}}{\partial t}$$

&lt;95&gt;

<96> 이때, 편극도 ( $\ddot{\vec{P}} = \ddot{\vec{R}}_1 + \ddot{\vec{P}}_2 + \dots + \ddot{\vec{P}}_m$ )는 양자 웨爾생 영역(130), 발광 다이오드(100) 내의 p-콘택총(126) 및 다른 총들의 주파수-의존성 응답을 수집한다. 개별  $\ddot{\vec{P}}_m$  항은 소정 재료의 전체 편극도(예, 속박 전자의 진동에 대한 편극 응답, 자유 전자의 진동에 대한 편극 응답)에 달리 기여하는 경험적으로 유도된 수치이다. 특히,

$$\frac{d^2 \ddot{\vec{P}}_m}{dt^2} + \gamma_m \frac{d\ddot{\vec{P}}_m}{dt} + \omega_m^2 \ddot{\vec{P}}_m = \varepsilon(\omega) \vec{E}$$

&lt;97&gt;

<98> 이때, 상기 편극은 하기의 유전 상수에 대응한다:

$$\varepsilon(\omega) = \varepsilon_\infty + \sum_m \frac{s_m}{\omega_m^2 - \omega^2 - i\gamma_m\omega}$$

&lt;99&gt;

<100> 수치적 계산을 위해, 고려되는 유일한 총들은 밀봉재(144), 실버총(126) 및 이들 밀봉재(144)와 실버총(126) 사이의 총들이다. 이러한 근사식 계산은 밀봉재(144)와 실버총(126)이 충분히 두꺼워서 주변 총들이 발광 다이오드(100)의 광학적 성능에 영향을 미치지 않는다는 전제를 기초로 한다. 주파수 의존형 유전 상수를 갖는 것으로 추측되는 발광 다이오드(100) 내의 관련 구조들은 실버총(126) 및 광-발생 영역(130)이다. 발광 다이오드(100) 내의 다른 관련 총들은 주파수 의존형 유전 상수를 갖지 않는 것으로 추측된다. 주목할 점은 밀봉재(144)와 실버총(126) 사이에 추가의 금속총들을 포함하고 있는 발광 다이오드(100)의 실시예에서 추가 금속총 각각은 대응하는 주파수 의존형 유전 상수를 가질 것이라는 것이다. 또한 주목할 점으로서, 실버총(126)(및 발광 다이오드(100) 내의 다른 소정의 금속총)은 속박 전자 및 자유 전자 모두에 대한 주파수 의존형 항을 가지는 반면, 광-발생 영역(130)은 속박 전자에 대한 주파수 의존형 항을 가질 뿐 자유 전자에 대한 주파수 의존형 항을 갖지 않는다. 소정 실시예에서, 다른 항들은 유전 상수의 주파수 의존성을 모델링할 때 포함될 수 있다. 그러한 항으로서 예컨대, 전자-광자 상호 작용, 원자 편극, 이온 편극 및/또는 분자 편극을 포함할 수 있다.

&lt;101&gt;

광-발생 영역(130)의 양자 웨르로부터의 광 방출은 광-발생 영역(130) 내에 임의로 배치된 다수의 일정-전류 쌍극자 소스들을 결합하는 것에 의해 모델링되며, 각 쌍극자 소스는 실제 양자 웨의 스펙트럼폭에 대응하는 스펙트럼폭의 짧은 가우스 펠스를 발생시키며, 각 펠스는 임의의 초기 위상과 시작-시간을 갖는다.

&lt;102&gt;

발광 다이오드(100)의 표면(110)의 개구(150) 패턴에 대응하기 위해, 주기적 경계 조건과 함께 측방향의 대형 슈퍼셀이 사용된다. 이는 비교적 큰 발광 다이오드 크기(예, 에지상에서 0.01mm 이상)의 시뮬레이션에 도움이 될 수 있다. 전 방출 방정식들(full evolution equations)은 시스템 내에 더 이상 에너지가 남아 있지 않을 때 까지 모든 쌍극자 소스들이 그들의 에너지를 방출한 오랜 후에 적시에 해결된다. 시뮬레이션 시, 총 방출 에너지, 상부 표면(110)을 통해 추출된 에너지 풀러스, 및 양자 웨와 n-도핑총에 의해 흡수된 에너지가 모니터링된다. 시간 및 공간에 대한 퓨리에 변환을 통해, 추출된 풀러스의 주파수 및 각도 분해 데이터(resolved data)가 얻어지며, 따라서, 각도 및 주파수-분해 추출 효율이 계산될 수 있다. 총 방출 에너지를 광-발생 영역(130)의 경험적으로 알고 있는 발광도에 대응시킴으로써, 주어진 전기적 입력에 대해 루멘(lumen)/입체각/칩 면적의 각도 분해된 절대 추출(absolute angle-resolved extraction)이 얻어진다.

&lt;103&gt;

이론에 의해 구속되기를 바라지 않는다면, 이조화된(detuned) 패턴(150)은 개구(150)가 그 패턴(150)에 따라 총(134) 내에서 공간적으로 변화되는 유전 기능을 생성하기 때문에 상기 영역(130)에서 발생된 광이 표면(110)을 경유하여 발광 다이오드(100)로부터 나오는 효율을 향상시킬 수 있는 것으로 생각된다. 이는 발광 다이어드(100) 내의 방사 모드(즉, 표면(110)으로부터 나오는 광 모드)와 가이드 모드(즉, 다층 스택(122) 내에 구속되는 광 모드)의 밀도를 변경시키고, 또한 발광 다이오드(100) 내의 방사 모드 및 가이드 모드의 밀도 변화의 이러한 변경은 그렇지 않은 경우 패턴(150)의 부재시 가이드 모드로 방출될 일부 광이 방사 모드로 누출될 수 있는 모드로 산란되는(예, Bragg 분산) 결과를 초래하는 것으로 생각된다. 소정 실시예에서, 패턴(150)(예, 전술한 패턴 또는 후술할 패턴들 중 하나)은 발광 다이오드(100) 내의 모든 가이드 모드를 제거할 수 있는 것으로 생각된다.

&lt;104&gt;

격자 이조화(detuning)의 효과는 포인트 산란 사이트(site)를 갖는 결정의 브래그 산란(Bragg scattering)을 고려하면 이해될 수 있는 것으로 생각된다. 소정 간격(d)의 격자면에 배열된 완벽한 격자를 위해, 과장( $\lambda$ )의 단색광은 브래그 조건,  $n\lambda=2ds\sin\theta$ 에 따라 소정 각도( $\theta$ )로 산란된다. 이때, n은 산란 차수를 제공하는 정수이다. 그러나, 스펙트럼 대역폭( $\Delta\lambda/\lambda$ )을 가지며 입체각( $\Delta\theta$ )으로 방출되는 광 소스의 경우, 상기 브래그 조

건은 격자 사이트 간의 간격을 이조 파라미터( $\Delta a$ )로 이조화시키는 것에 의해 완화될 수 있다고 생각된다. 격자의 이조화는 소스의 스펙트럼 대역폭 및 공간 방출 프로파일에 대해 패턴의 산란 효율 및 각 수용(angular acceptance)을 증가시키는 것으로 생각된다.

<105> 비-제로 이조 파라미터( $\Delta a$ )를 갖는 변형 삼각형 패턴(150)이 발광 다이오드(100)로부터의 광추출 효율을 향상시키는 것으로 설명하였지만, 발광 다이오드(100)로부터의 광추출 효율을 향상시키기 위해 다른 패턴도 사용이 가능하다. 주어진 패턴이 발광 다이오드(100)로부터의 광추출 효율을 향상시키는지의 여부 및/또는 발광 다이오드(100)로부터의 광추출 효율의 향상을 위해 어떤 패턴의 개구가 사용될 수 있는지를 판단할 때, 수치적 계산을 행하기 이전에 광추출 효율을 향상시킬 수 있는 기본 패턴에 접근하는데 물리적 통찰이 우선 적용될 수 있다.

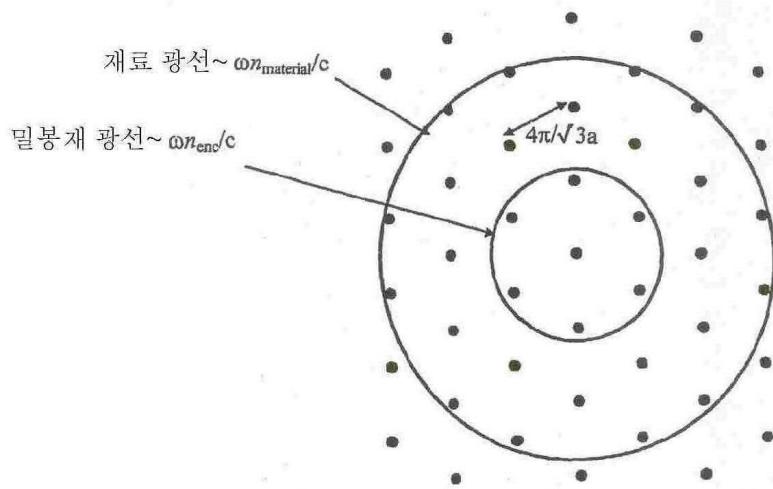

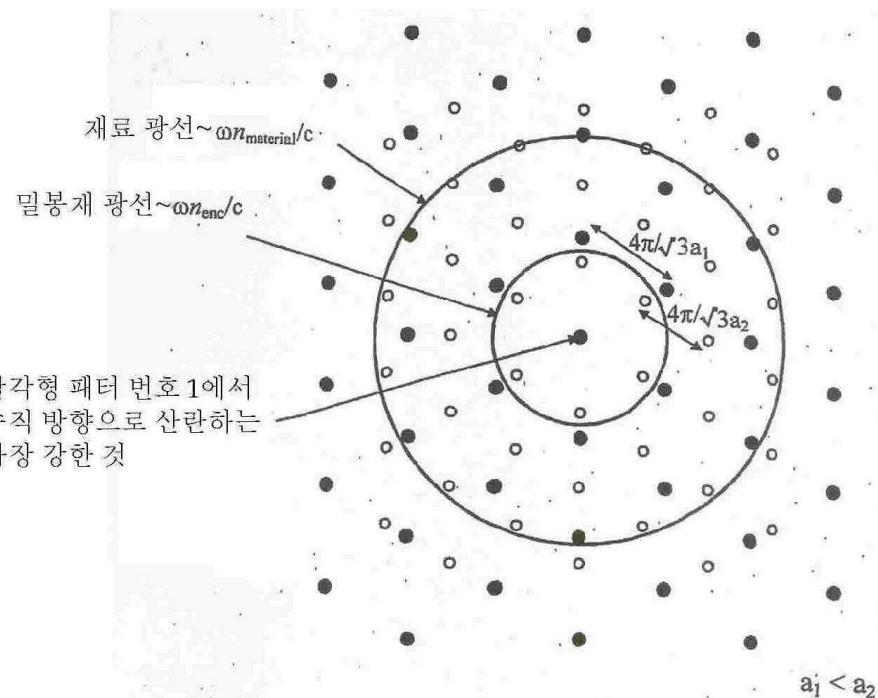

<106> 발광 다이오드(100)의 광추출 효율은 패턴(150)에 따라 공간적으로 변화하는 유전 기능의 퓨리에 변환을 고려하는 것에 의해 더더욱 이해될 수 있다(예, 약한 산란 영역에서). 도 4는 이상적인 삼각형 격자를 위한 퓨리에 변환을 나타낸다. 평면내 파장 벡터( $k$ )를 갖는 특정 방향으로의 광추출은 역격자 벡터( $G$ )의 가감에 의해  $k$ 에 대응하는 평면내 파장 벡터( $k'$ )(즉, 패턴(150)에 평행)(즉,  $k=k' \pm G$ )의 모든 모드로의 소스 방출( $S_{k'}$ )에 관련된다. 광추출 효율은 하기 수학식으로 주어지는 유전 기능( $\varepsilon_G$ )의 대응하는 퓨리에 성분( $F_k$ )의 크기에 비례한다.

$$F_k = c_k \sum_{\tilde{G}} \varepsilon_{\tilde{G}} S_{k-\tilde{G}}, \quad \varepsilon_{\tilde{G}} = \int \varepsilon(\vec{r}) e^{-i\tilde{G}\vec{r}} d\vec{r}$$

<107>

재료내를 전파하는 광은 일반적으로  $k^2$ (평면내)+ $k^2$ (법선)= $\varepsilon (w/c)^2$ 의 수학식을 만족하므로, 고려 대상의 최대  $G$ 는 광-발생 영역(130)에 의해 발생된 주파수( $w$ )와 광-발생 영역의 유전 상수에 의해 고정된다. 도 4에 도시된 바와 같이, 이는 광선(light line)으로도 지칭되는 역격자 공간 내에 링(ring)을 형성한다. 상기 광선은 광-발생 영역의 유한 대역폭에 기인하여 원환(annulus)이 될 것이나, 명확화를 위해 단색 소스의 광선으로 나타내기로 한다. 유사하게, 밀봉재 내로 전파되는 광은 광선(도 4의 내부 원)에 의해 구속된다. 그러므로, 광추출 효율은 밀봉재 광선 내에서  $G$  포인트의 갯수를 증가시키고 또한 재료의 광선 내에 놓여 있는  $G$  포인트에 대한 산란 강도( $\varepsilon_G$ )를 증가시키는 정도로 상기 밀봉재 광선 내에 놓여 있는 모든 방향( $k$ )에 대해 퓨리에 성분( $F_k$ )을 증가시키는 것에 의해 향상된다. 이러한 물리적 고찰은 광추출 효율을 향상시킬 수 있는 패턴의 선택시에 사용될 수 있다.

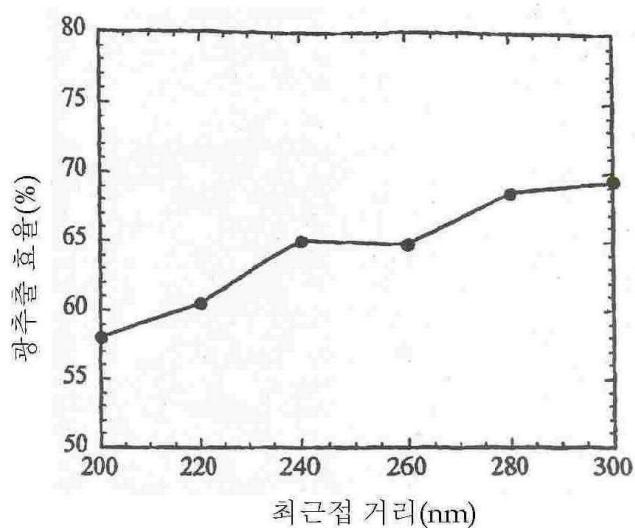

<109> 예로서, 도 5는 이상적인 삼각형 패턴의 격자 상수를 증가시키는 효과를 보여준다. 도 5에 나타낸 데이터는 방출광이 450nm의 피크 파장을 가지고, 최근접 거리  $a$ 를 기준으로 홀의 깊이, 홀의 직경 및 n-도핑층(134)의 두께가 각각 1.27a, 0.72a 및 1.27a+40nm인 점을 제외하고, 도 1에 도시된 발광 다이오드(100)에 대해 주어진 파라미터들을 이용하여 계산된다. 격자 상수의 증가는 밀봉재의 광선 내  $G$  포인트의 밀도 증가를 가져온다. 광추출 효율의 분명한 트렌드는 최근접 거리(NND)에서 관찰된다. 최대 광추출 효율은 NND가 진공 내 광 파장에 대응할 때 일어나는 것으로 생각된다. 최대치가 얻어지는 이유는 NND가 광 파장 보다 훨씬 커지게 됨에 따라 재료가 보다 불균일화되므로 산란 효율이 감소되기 때문이다.

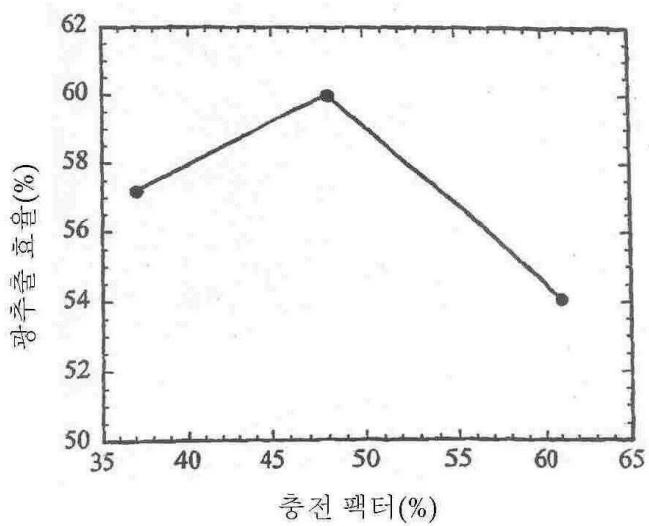

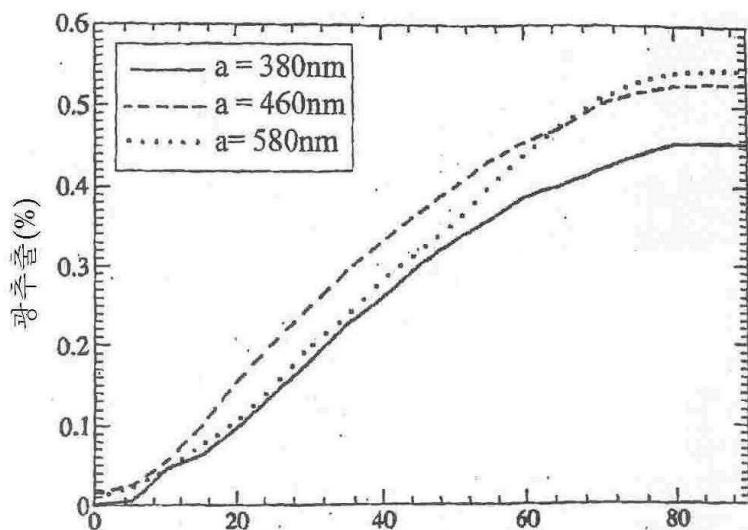

<110> 다른 예로서, 도 6은 홀 크기 또는 충전 팩터(filling factor)의 증가의 영향을 나타낸다. 삼각형 패턴의 충전 팩터는  $(2\pi/\sqrt{3})*(\mathbf{r}/a)^2$ 로 주어지며, 이때,  $r$ 은 홀의 반경이다. 도 6에 나타낸 데이터는 그래프의 x-축상에 주어진 충전 팩터값에 따라 개구의 직경이 달라지는 것을 제외하고, 도 1에 도시된 발광 다이오드(100)에 대해 주어진 파라미터들을 이용하여 계산된다. 광추출 효율은 산란 강도( $\varepsilon_G$ )의 증가에 따라 충전 팩터와 함께 증가된다. 이 특별 시스템에서는 48% 이하의 충전 팩터에서 최대치가 관찰된다. 소정 실시예에서, 발광 다이오드(100)는 적어도 약 10%(예, 적어도 약 15%, 약 20%), 및/또는 최대 약 90%(예, 최대 약 80%, 약 70%, 약 60%)의 충전 팩터를 갖는다.

<111> 변형 삼각형 패턴은 이조 파라미터가 이상적인 삼각형 격자에서의 위치로부터 패턴 내의 개구의 위치에 관련된 것으로 기술하고 있으나, 변형된(이조화된) 삼각형 패턴은 이상적인 삼각형 패턴 내의 홀을 그 중심을 이상적인 삼각형 패턴의 위치에 유지하면서 변형시키는 것에 의해서도 달성될 수 있다. 도 7은 그러한 소정 패턴의 실시 예를 나타낸다. 광추출의 향상, 대응하는 수치 계산을 행하기 위한 방법론 및 도 7에 도시된 패턴을 갖는 발광 디바이스에서 향상된 광추출의 물리적 설명은 대체로 전술한 바와 동일하다. 소정 실시예에서, 변형된(이조화

된) 패턴은 이상적 위치에서 변위된 개구 및 이상적 위치에 있으나 가변 직경인 개구를 가질 수 있다.

<112> 다른 실시예에서, 발광 디바이스로부터의 향상된 광추출은 예컨대, 복합 주기적 패턴과 비주기적 패턴을 포함하는 여러 형태의 패턴을 이용하여 달성할 수 있다. 여기에 언급하는 바와 같이, 복합 주기적 패턴은 주기적인 형태로 반복하는 각 단위 셀 내에서 하나 이상의 특징부를 갖는 패턴이다. 복합 주기적 패턴의 예로서 허니컴 패턴, 허니컴 베이스 패턴,  $(2 \times 2)$  베이스 패턴, 링 패턴 및 아르키메데스 패턴(Archimedean pattern)을 포함한다. 하기에 설명하는 바와 같이, 몇몇 실시예에서, 복합 주기적 패턴은 소정 직경의 개구들과 보다 작은 직경의 다른 개구들을 가질 수 있다. 여기에 언급되는 바와 같이, 비주기적 패턴은 광-발생 영역(130)에 의해 발생된 광의 피크 파장의 적어도 50배인 길이를 갖는 단위 셀에 대해 병진적 대칭 구조가 아닌 패턴이다. 비주기적 패턴의 예로서 비주기 패턴(aperiodic pattern), 준-결정 패턴, 로빈슨 패턴(Robinson pattern) 및 암만 패턴(Amman pattern)을 포함한다.

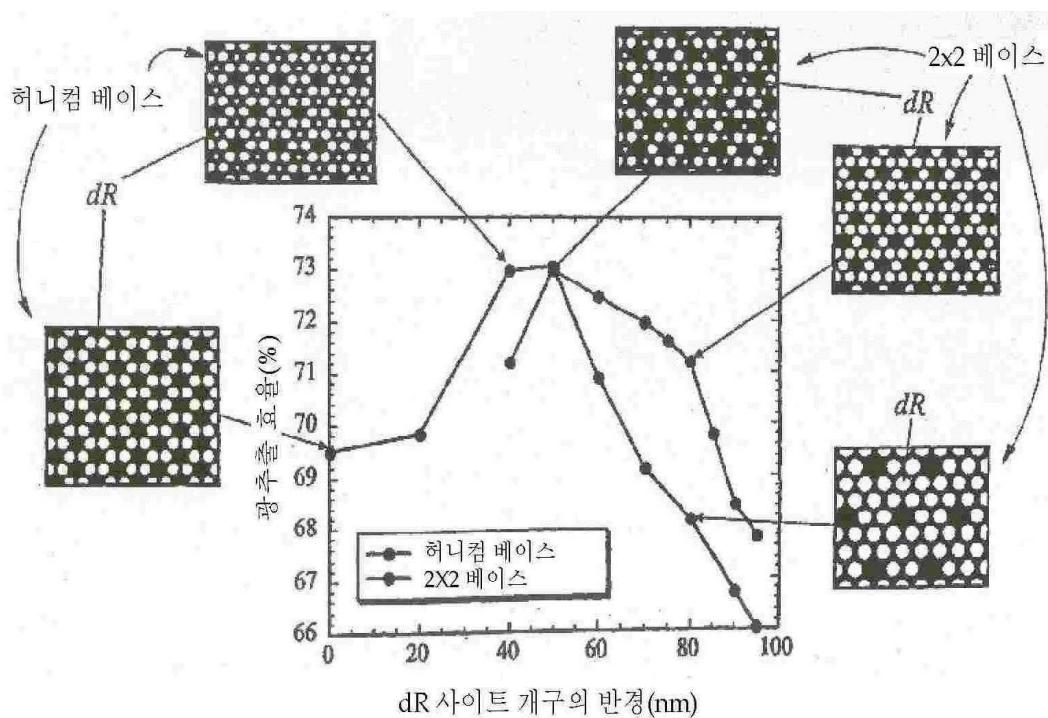

<113> 도 8은 패턴 내의 소정 개구가 특정 직경을 가지고, 패턴 내의 다른 개구가 보다 작은 직경을 갖는 두개의 다른 복합 주기적 패턴에 있어서 발광 다이오드(100)의 수치 계산을 보여주고 있다. 도 8에 나타낸 수치 계산은 보다 작은 구멍(dR)의 직경이 0 nm에서 95 nm로 변화될 때 광추출 효율의 거동(80nm 직경의 보다 큰 구멍)을 나타낸다. 도 6에 나타낸 데이터는 개구의 직경이 그래프의 x-축상에 주어진 충전 팩터값에 따라 변화되는 것을 제외하고, 도 1에 도시된 발광 다이오드(100)에 대해 주어진 파라미터들을 이용하여 계산된다. 이론에 의해 구속되는 것을 원하지 않는다면, 다중 구멍 크기는 패턴 내의 복합적 주기들로부터 산란을 허용하여, 패턴의 각 수용 및 스펙트럼 효율을 증가시킨다. 광추출의 향상, 대응하는 수치 계산을 행하기 위한 방법론 및 도 8에 도시된 패턴을 갖는 발광 디바이스에서 향상된 광추출의 물리적 설명은 대체로 전술한 바와 동일하다.

<114> 도 9는 다른 링 패턴(복합 주기적 패턴)을 갖는 발광 다이오드(100)의 수치 계산을 보여주고 있다. 중심 구멍을 둘러싸는 제 1링에서의 구멍의 수는 다른 링 패턴에서 서로 다르다(예, 6, 8 또는 10). 도 9에 나타낸 데이터는 방출광이 450nm의 피크 파장을 갖는다는 점을 제외하고, 도 1에 도시된 발광 다이오드(100)에 주어진 파라미터들을 이용하여 계산된다. 도 9에 표현된 수치 계산은 단위 셀을 가로질러 반복하는 단위 셀 당 링 패턴의 수가 2에서 4로 변화될 때 발광 다이오드(100)의 광추출 효율을 나타낸다. 광추출의 향상, 대응하는 수치 계산을 행하기 위한 방법론 및 도 9에 도시된 패턴을 갖는 발광 디바이스에서 향상된 광추출의 물리적 설명은 대체로 전술한 바와 동일하다.

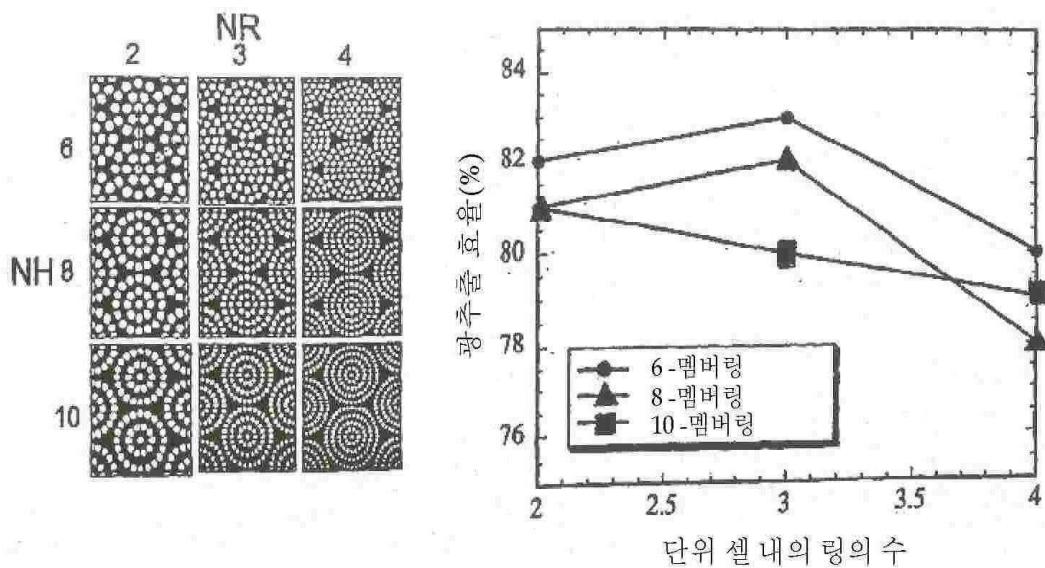

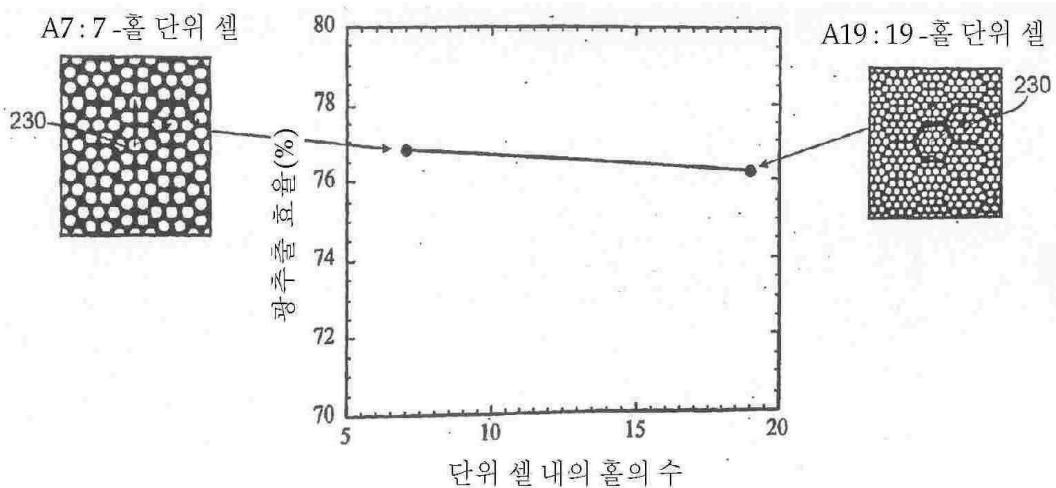

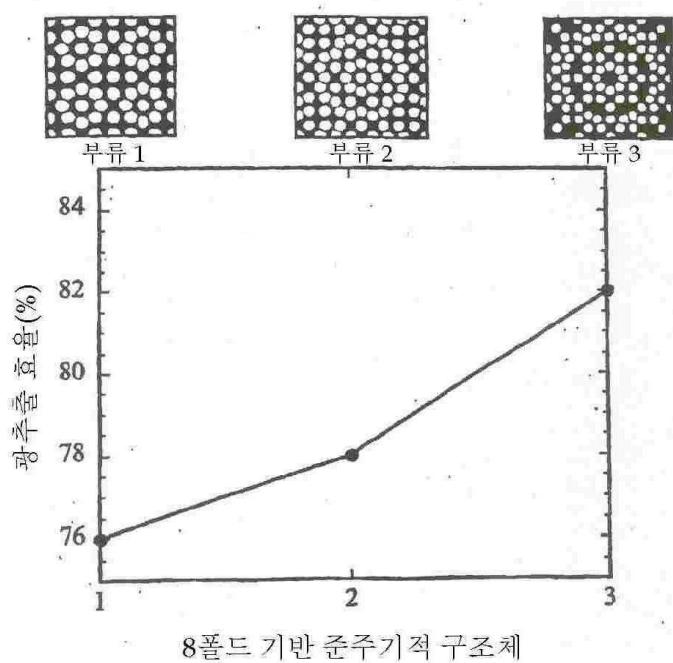

<115> 도 10은 아르키메데스 패턴을 갖는 LED(100)의 수치 계산을 도시한다. 아르키메데스 패턴(A7)은 a의 최근접 거리를 갖는 7개의 등간격 홀을 갖는 6각형 단위 셀(230)로 이루어진다. 단위 셀(230) 내에는, 6개의 홀이 정육각형의 형상으로 배열되고, 제 7의 홀이 6각형의 중심에 위치된다. 다음에, 6각형 단위 셀(230)은 LED의 전체 표면을 패턴화하도록  $a' = a * (\sqrt{1 + \sqrt{3}})$ 의 단위 셀 사이에 중심 간격으로 이들의 예지를 따라 서로 끼워진다. 이는 7개의 홀이 단위 셀을 구성하기 때문에 A7 타일링(tiling)으로서 공지되어 있다. 유사하게, 아르키메데스 타일링(A19)은 a의 NND를 갖는 19개의 등간격 홀로 이루어진다. 홀은 7개의 홀의 내부 6각형, 12개의 홀의 외부 6각형 및 내부 6각형 내의 중심 홀의 형태로 배열된다. 다음에, 6각형 단위 셀(230)은 LED의 전체 표면을 패턴화하도록  $a' = a * (\sqrt{3 + \sqrt{3}})$ 의 단위 셀 사이에 중심 간격으로 이들의 예지를 따라 서로 끼워진다. 도 10에 도시된 패턴을 갖는 발광 디바이스의 광 추출의 향상, 대응 수치 계산을 수행하기 위한 방법론 및 향상된 광 추출의 물리적 설명은 일반적으로 상술한 바와 동일하다. 도 10에 도시된 바와 같이, A7 및 A19의 광추출 효율은 약 77%이다. 도 10에 도시된 데이터는 방출된 광이 450의 피크 파장을 갖고 NND가 개별 셀 내의 개구 사이의 거리로서 정의되는 것을 제외하고는 도 1에 도시된 LED(100)에 제공된 파라미터를 사용하여 계산된다.

<116> 도 11은 준결정 패턴을 갖는 LED(100)의 수치 계산 데이터를 도시한다. 준결정 패턴은 예를 들면 본 명세서에 참조로 인용되어 있는 엠. 세네칼(M. Senechal)의 *Quasicrystals and Geometry*(캡브리지 대학 출판부, 영국 캡브리지, 1996년)에 설명되어 있다. 수치 계산은 8-폴드 기반 준주기적 구조체가 변화됨에 따른 광추출 효율을 나타낸다. 준결정 패턴은 이러한 구조체에 의해 허용되는 고도의 평면내 회전 대칭에 기인하여 높은 광추출 효율을 나타내는 것으로 생각된다. 도 11에 도시된 패턴을 갖는 발광 디바이스의 광 추출의 향상, 대응 수치 계산을 수행하기 위한 방법론 및 향상된 광 추출의 물리적 설명은 일반적으로 상술한 바와 동일하다. 도 11에 도시된 FDTD 계산으로부터 결과는 준결정 구조체의 광추출 효율이 약 82%에 도달한다는 것을 나타낸다. 도 11에 도시된 데이터는 방출된 광이 450의 피크 파장을 갖고 NND가 개별 셀 내의 개구 사이의 거리로서 정의되는 것을 제외하고는 도 1에 도시된 LED(100)에 제공된 파라미터를 사용하여 계산된다.

<117> 특정 패턴의 예를 본 명세서에 설명하였지만, 패턴이 상술된 기본 원리를 만족시키는 경우 다른 패턴이 LED(100)로부터의 광 추출을 또한 향상시킬 수 있는 것으로 생각된다. 예를 들면, 준결정 또는 복합 주기적 구

조체의 추가의 이조화가 광추출 효율을 증가시킬 수 있는 것으로 생각된다.

<118> 몇몇 실시예에서, 광 발생 영역(130)에 의해 발생되어 LED(100)로부터 나오는 총 광량의 적어도 약 45%(예를 들면, 적어도 약 50%, 적어도 약 55%, 적어도 약 60%, 적어도 약 70%, 적어도 약 80%, 적어도 약 90%, 적어도 약 95%)가 표면(110)을 경유하여 나온다.

<119> 특정 실시예에서, LED(100)의 단면적은 LED(100)로부터의 효율적인 광 추출을 여전히 나타내면서 비교적 클 수 있다. 예를 들면, LED(100)의 하나 이상의 에지는 적어도 약 1mm(예를 들면, 적어도 약 1.5mm, 적어도 약 2mm, 적어도 약 2.5mm, 적어도 약 3mm)일 수 있고, LED(100)로부터 나오는 광 발생 영역(130)에 의해 발생된 총 광량의 적어도 약 45%(예를 들면, 적어도 약 50%, 적어도 약 55%, 적어도 약 60%, 적어도 약 70%, 적어도 약 80%, 적어도 약 90%, 적어도 약 95%)가 표면(110)을 경유하여 나온다. 이는 양호한 출력 변환 효율을 나타내면서 LED가 비교적 큰 단면(예를 들면, 적어도 약 1mm×적어도 약 1mm)을 가질 수 있게 한다.

<120> 몇몇 실시예에서, LED(100)의 디자인을 갖는 LED의 광추출 효율은 LED의 에지의 길이와 실질적으로 무관하다. 예를 들면, LED(100)의 디자인 및 약 0.25mm의 길이를 갖는 하나 이상의 에지를 갖는 LED의 광추출 효율과 LED(100)의 디자인 및 1mm의 길이를 갖는 하나 이상의 에지를 갖는 LED의 광추출 효율 사이의 차이는 약 10% 미만(약 8% 미만, 약 5% 미만, 약 3% 미만) 정도로 변경될 수 있다. 본 명세서에 언급된 바와 같이, LED의 광추출 효율은 디바이스에 의해 생성된 광량(에너지 또는 광자의 견지에서 측정될 수 있음)에 대한 LED에 의해 방출된 광의 비이다. 이는 양호한 출력 변환 효율을 나타내면서 LED가 비교적 큰 단면(예를 들면, 적어도 약 1mm×적어도 약 1mm)을 가질 수 있게 한다.

<121> 특정 실시예에서, LED(100)의 디자인을 갖는 LED의 양자 효율은 LED의 에지의 길이와 실질적으로 무관하다. 예를 들면, LED(100)의 디자인 및 약 0.25mm의 길이를 갖는 하나 이상의 에지를 갖는 LED의 양자 효율과 LED(100)의 디자인 및 1mm의 길이를 갖는 하나 이상의 에지를 갖는 LED의 양자 효율 사이의 차이는 약 10% 미만(약 8% 미만, 약 5% 미만, 약 3% 미만) 정도로 변경될 수 있다. 본 명세서에 언급된 바와 같이, LED의 양자 효율은 LED에서 발생하는 홀의 재조합 수에 대한 LED에 의해 생성된 광자의 수의 비이다. 이는 양호한 성능을 나타내면서 LED가 비교적 큰 단면(예를 들면, 적어도 약 1mm×적어도 약 1mm)을 가질 수 있게 한다.

<122> 몇몇 실시예에서, LED(100)의 디자인을 갖는 LED의 벽 플러그 효율은 LED의 에지의 길이와 실질적으로 무관하다. 예를 들면, LED(100)의 디자인 및 약 0.25mm의 길이를 갖는 하나 이상의 에지를 갖는 LED의 벽 플러그 효율과 LED(100)의 디자인 및 1mm의 길이를 갖는 하나 이상의 에지를 갖는 LED의 벽 플러그 효율 사이의 차이는 약 10% 미만(약 8% 미만, 약 5% 미만, 약 3% 미만) 정도로 변경될 수 있다. 본 명세서에 언급된 바와 같이, LED의 벽 플러그 효율은 LED의 주입 효율(디바이스의 광 발생 영역에서 재조합하는 캐리어의 수에 대한 디바이스 내로 주입된 캐리어의 수의 비), LED의 방사 효율(홀 재조합의 총 수에 대한 방사 이벤트를 초래하는 홀 재조합의 비), 및 LED의 광추출 효율(생성된 광자의 총 수에 대한 LED로부터 추출된 광자의 비)의 적이다. 이는 양호한 성능을 나타내면서 LED가 비교적 큰 단면(예를 들면, 적어도 약 1mm×적어도 약 1mm)을 가질 수 있게 한다.

<123> 몇몇 실시예에서, LED(100)로부터 표면(110)을 경유하여 나오는 각도 분포를 조정하는 것이 바람직할 수 있다. 소정의 입체각(표면(110)에 수직인 방향 둘레의 입체각)으로의 광추출 효율을 증가시키기 위하여, (전술한 바와 같이) 패턴(150)에 따라 공간적으로 변하는 유전체 기능의 퓨리에 변환을 시험하였다. 도 12는 상이한 격자 상수를 갖는 2개의 이상적인 삼각형 격자에 대한 퓨리에 변환 구성을 도시하고 있다. 광추출 효율을 증가시키기 위하여, 밀봉재 광선 내의 G 점의 개수와 재료 광선 내의 G 점의 산란 강도를 증가시키려고 한다. 이는 도 5에 도시된 효율을 달성하도록 NND를 증가시키는 것을 내포한다. 그러나, 여기서 수직 방향 둘레의 중심에 놓인 입체각으로 광추출 효율을 증가시키는 것이 중요하다. 따라서, 또한 G의 크기가  $(\omega(n_e))/c$ 보다 크도록 밀봉재 광선의 반경을 감소시킴으로써 더 높은 순서의 G 점을 도입하는 것을 제한하고자 한다. 밀봉재의 굴절률(그 노출된 최소값은 모두 함께 밀봉재를 제거함)을 감소시킴으로써, 보다 큰 NND가 가능하며, 이에 따라 수직 방향 ( $F_{k=0}$ )에서의 추출에 기여할 수 있는 동시에 밀봉재에서 더 높은 순서(경사각)로의 회절을 피하여 재료 광선 내에 G 점의 개수를 증가시킨다는 것을 알 수 있다. 전술한 경향은 입체각(도면에서 수직 1/2 각도로 주어짐)으로의 광추출 효율을 나타내는 도 13에 도시되어 있다. 도 13에 도시된 데이터는 방출광이 530 nm의 피크 파장과 34 nm의 대역폭을 갖고, 밀봉재의 굴절률이 1.0이며, p-도핑층의 두께가 160 nm이고, 광 발생층의 두께가 30 nm이며, 도 13에 3개의 곡선에 대한 NND(a)가 도시되어 있고, 깊이, 홀 직경 및 n-도핑층의 두께가 각각 1.27a, 0.72a 및 1.27a+40 nm으로서 a에 대해 비율이 정해진다는 점을 제외하고는 도 1에 도시된 LED(100)에 제공된 파라미터를 이용하여 계산된다. 격자 상수가 증가되면, 좁은 각도에서의 광추출 효율 뿐만 아니라 모든 각도로의

광추출 효율이 증가된다. 그러나, 매우 큰 격자 상수의 경우, 전체 광추출 효율이 모든 각도로 증가되더라도 밀봉재의 높은 순서 모드로의 회절은 좁은 각도에서의 광추출 효율을 제한한다. 격자 상수가 460 nm인 경우에, 30°의 수집 1/2 각도로 25% 이상의 광추출 효율이 계산된다. 즉, 추출광의 약 1/2이 패턴의 시준 효과를 증명하는 입체각의 상부 반구체의 오직 약 13.4% 내에 수집된다. 재료 광선 내에 G 점의 개수를 증가시키는 동시에, 밀봉재 광선 내에 G 점의 개수를 오직 k=0에서 G 점으로만 제한하는 임의의 패턴은 수직 방향 둘레의 중심에 놓인 입체각으로의 광추출 효율을 향상시킬 수 있다고 믿는다.

<124> 그 방안은 구체적으로 흔히  $n^2$ 에 비례하는 것으로 보이는 소스 너비를 감소시키는 데에 적용할 수 있는데, 여기서 n은 주위 재료(예컨대, 밀봉재)의 굴절률이다. 따라서, LED(100)의 밀봉층의 굴절률을 감소시키는 것은 보다 시준된 방사, 낮은 소스 너비, 이에 따라 높은 표면 회도(여기서는, 소스 너비로 추출된 총 루멘으로 규정함)에 이를 수 있다. 몇몇 실시예에서는, 공기 밀봉재의 사용이 소스 너비를 감소시키는 동시에 수직 방향 둘레의 중심에 놓인 소정의 수집각으로 광추출 효율을 증가시킨다.

<125> 특정 실시예에서, 영역(130)에 의해 발생된 광이 LED(100)로부터 표면(110)을 경유하여 나올 때, 광의 분포는 램베르시안 분포보다 더욱 시준된다. 예컨대, 몇몇 실시예에서, 영역(130)에 의해 발생된 광이 LED로부터 표면(110)을 경유하여 나올 때, 유전체층의 표면을 경유하여 나오는 광의 적어도 약 40%(예컨대, 적어도 약 50%, 적어도 약 70%, 적어도 약 90%)는 표면(110)에 수직인 각도의 최대 약 30°(예컨대, 최대 약 25°, 최대 약 20°, 최대 약 15°) 내에서 나온다.

<126> 원하는 각도로부터 비교적 높은 비율의 광만을 추출하거나 비교적 높은 광 추출과 결부되는 능력은 비교적 높은 밀도의 LED가 주어진 웨이퍼 상에 제조될 수 있게 한다. 예컨대, 몇몇 실시예에서, 웨이퍼는 제곱 센티미터 당 적어도 약 5개의 LED(예컨대, 적어도 약 25개의 LED, 적어도 약 50개의 LED)를 갖는다.

<127> 몇몇 실시예에서는, 광 발생 영역(130)으로부터 나오는 광의 파장에 대해 패키지된 LED(100)로부터 나오는 광의 파장을 변경시키는 것이 요망될 수 있다. 예컨대, 도 14에 도시된 바와 같이, 형광 재료를 포함하는 층(180)을 갖는 LED(300)는 표면(110) 상에 배치될 수 있다. 형광 재료는 원하는 파장으로 광을 제공하도록 영역(130)에 의해 발생된 파장에서 광과 상호 작용할 수 있다. 몇몇 실시예에서는, 패키지된 LED(100)로부터 나오는 광이 실질적으로 백색 광이 되는 것이 요망될 수 있다. 그러한 실시예에서, 층(180)의 형광 재료는, 예컨대 (Y,Gd)(Al<sub>x</sub>Ga<sub>1-x</sub>)G:Ce<sup>3+</sup> 또는 "YAG"(이트륨(Yttrium), 알루미늄(Aluminum), 가넷(Garnet)) 형광체로 형성될 수 있다. 광 발생 영역(130)으로부터 방출된 청색 광에 의해 펌핑될 때, 층(180)의 형광 재료가 활성화되어 황색 파장 둘레의 중심에 놓인 광역 스펙트럼을 (등방성으로) 갖는 광을 방출할 수 있다. 패키지된 LED(100)로부터 나오는 전체 광 스펙트럼의 뷰어는 황색 형광체의 광역 방출 스펙트럼과 청색 InGaN의 협역 방출 스펙트럼을 볼 수 있고, 통상 2개의 스펙트럼을 혼합하여 백색을 인지한다.

<128> 특정 실시예에서, 층(180)은 표면(110) 상에 실질적으로 균일하게 배치될 수 있다. 패턴(150)의 상부(151)와 층(180)의 상부(181) 사이의 거리는 표면(110)을 가로질러 약 20% 미만(예컨대, 약 10% 미만, 약 5% 미만, 약 2% 미만) 변할 수 있다.

<129> 일반적으로, 층(180)의 두께는 통상 1 mm × 1mm인 LED(100)의 표면(130)의 단면 치수에 비해 작다. 층(180)이 표면(110) 상에 실질적으로 균일하게 배치되기 때문에, 층(180)의 형광 재료는 표면(110)을 경유하여 나오는 광에 의해 실질적으로 균일하게 펌핑될 수 있다. 형광층(180)은 광 발생 영역(130)에 의해 방출된 광이 LED(100)의 전체 표면에 걸쳐 대략 균일하게 형광층(180) 내에서 낮은 파장의 광으로 전환되도록 LED(100)의 표면 치수에 비해 비교적 얇다. 따라서, 비교적 얇고 균일한 형광층(180)은 표면(110) 상의 위치의 함수로서 LED(100)로부터 방출된 백색 광의 균일한 스펙트럼을 생성시킨다.

<130> 일반적으로, LED(100)는 원하는 대로 제조될 수 있다. 통상, LED(100)의 제조는 다양한 증착, 레이저 처리, 리소그래피 및 식각 단계를 포함한다.

<131> 도 15를 참조하면, 사파이어 기판상에 증착된 재료의 LED 층 스택을 포함하는 LED 웨이퍼(500)는 쉽게 입수할 수 있으며, 상업적 판매자로부터 구매할 수 있다. 사파이어 기판(502)상에, 연속적으로, 베퍼층(504), n-도핑 Si:GaN층(506), 전류 분산층(508)을 제공하는 AlGaN/GaN 이질접합 또는 초격자, InGaN 다중 양자 웨尔 광 발생 영역(510) 및 p-도핑 Mg:GaN층(512)이 배치된다. 상업적으로 입수할 수 있는 LED 웨이퍼는 직경이 약 2-3in이고, 웨이퍼가 처리된 이후, 개별 디바이스를 형성하도록 웨이퍼로부터 다수의 LED 다이스가 절단될 수 있다. 웨이퍼 다이싱 이전에, 미러층(126)으로서 광 발생 영역(130)의 동일 측부상에 p-도핑층(128)을 위치시키기 위해

다수의 웨이퍼 스케일 처리 단계가 사용된다.

<132> 도 16을 참조하면, 비교적 얇은 니켈층(520)이 p-도핑층(512)상에 증착되어(예컨대, 전자-빔 증발을 사용하여) p-도핑층(512)에 대한 p-형 저항 콘택트를 형성한다. 실버층(522)이 (예컨대, 전자-빔 증발을 사용하여) 니켈층(520)상에 증착된다. 비교적 두꺼운 니켈층(524)이 (예컨대, 전자-빔 증발을 사용하여) 실버층(522)상에 증착된다. 층(524)은 실버층(522)으로의 오염물의 확산을 감소시키기 위한 확산 배리어로서 작용할 수 있다. 골드층(526)이 (예컨대, 저항 증발을 사용하여) 니켈층(524)상에 증착된다. 웨이퍼(500)는 그 후, 저항 콘택트를 달성하기 위해, 질소, 산소, 공기 또는 형성 가스내에서 30 내지 300초 동안 400 내지 600°C 사이의 온도에서 어닐링된다.

<133> 도 17을 참조하면, p-도핑 실리콘 웨이퍼(602)상에 연속적으로 알루미늄 콘택트층(604)을 (예컨대, 전자-빔 증발을 사용하여) 증착함으로써 서브마운트 웨이퍼(600)가 만들어진다. 골드층(608)이 층(604)상에 (예컨대, 열적 증발을 사용하여) 증착되고, AuSn 접합층(610)이 (예컨대, 열적 증발을 사용하여) 층(608)상에 증착된다. 서브마운트 웨이퍼(600)는 저항 콘택트를 달성하기 위해 질소, 산소, 공기 또는 형성 가스 내에서 30 내지 300초 동안 350 내지 500°C 사이의 온도에서 어닐링된다.

<134> 웨이퍼(500, 600)는 200 내지 400°C 범위의 온도와 0 내지 0.5MPa의 압력을 사용하여 (예컨대, 열 기계 프레스를 사용하여) 서마운트 웨이퍼(600)의 층(610)과 층(526)이 접촉하게 함으로써 함께 접합된다. 층(510) 및 층(610)은 공용 본드를 형성한다. 조합된 웨이퍼 샌드위치가 냉각되고, 접합된 샌드위치가 프레스로부터 제거된다.

<135> 접합 이후, 기판(502)은 레이저 리프트오프 프로세스에 의해 조합된 구조체로부터 제거된다. 레이저 리프트오프 프로세스는 예컨대, 미국 특허 제6,420,242호 및 제6,071,795호에 개시되어 있으며, 이들은 본 명세서에 참조로 인용되어 있다. 몇몇 실시예에서, 사파이어 기판(502)과의 그 계면 부근의 n-도핑 Si:GaN층(506)을 국부적으로 가열하여 n-도핑층(506)의 서브층을 분해시키도록 248nm 레이저 빔이 기판(502)을 통해 조사된다. 그 후, 사파이어 기판(502)이 (예컨대, 코تون 스왑을 사용하여) 그에 측방향 힘을 인가함으로써 샌드위치로부터 제거되는 용접으로, 갈륨의 용접을 초과하여 가열된다. 노출된 GaN 표면이 그후 (예컨대, 염화수소산 배스를 사용하여) 세정되어 표면으로부터 액체 갈륨을 제거한다. 종종 사파이어 기판(502)이 GaN 에피택셜층 스택으로부터 제거될 때, 스택 내에 존재하던 (예컨대, 기판(502)과 스택 사이의 격자 오정합으로 인한)변형이 스택으로부터 제거된다. 이는 기판(502)에 접합될 때 가질 수 있는 휘어지거나 굴곡된 형상으로부터 스택을 이완시킬 수 있으며, n-도핑층(506)의 노출된 표면상에 비교적 평탄한 형상을 취하게 한다. 레이저 리프트오프 프로세스에서 균열을 피하기 위해 서브마운트 선택시 열팽창 계수를 고려된다. 부가적으로, 이 단계 및 반복 프로세스에서 필드를 실질적으로 중첩시킴으로써 레이저 리프트오프 동안 균열이 감소될 수 있다.

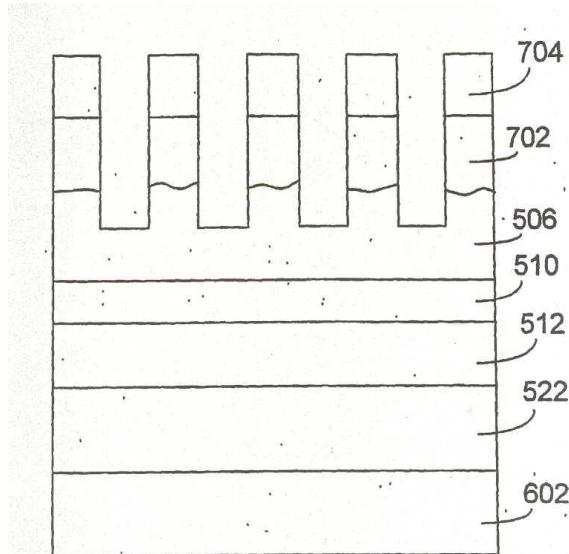

<136> 도 18을 참조하면, 최종 디바이스(도 19)에 사용될 층을 위한 원하는 두께를 달성하기 위해 n-도핑 Si:GaN층(506)의 노출된 표면이 (예컨대, 반응성 이온 식각 프로세스를 사용하여) 다시 식각된다. 식각 이후, 식각된 GaN 층(506)의 표면은 식각으로 인해 조면화된 표면 텍스처(700)를 갖는다. 조면화된 표면(700)은 약 5nm 평균 자승근(rms)보다 작은 표면 평활도 및 층(506)을 위한 최종 두께를 달성하기 위해 (예컨대, 화학 기계 프로세스를 사용하여) 평탄화 및 박막화될 수 있다. 또한, 조면화된 표면(700)은 디바이스(100)에 국지적 비평면 계면을 도입시킴으로써 디바이스의 추출 효율을 증가시키는 것을 돋기 위해 유지될 수 있다. 조면화된 표면은 극미세 평활 표면에 관하여, 다수회 표면(700)에 충돌하는 광선이 결국 스넬(Snell)의 법칙에 의해 주어진 임계 각도보다 작은 각도로 표면에 충돌하고, 표면(700)을 통해 추출될 가능성을 증가시킨다.

<137> 식각 이후, n-도핑층(506) 내에 유전체 기능 패턴을 준비하기 위해, 재료의 제 1평탄화층(702)이 n-도핑 GaN층(506)상에 (예컨대, 스판 코팅을 사용하여) 배치되고, 레지스트층(704)이 평탄화층(702) 상에 배치된다(예컨대, 스판 코팅된다). LED에 포토닉 격자를 형성하는 패턴이 그후 나노임프린트 리소그래피 및 식각 프로세스에 의해 n-도핑층(506) 내에 생성된다. 먼저, 원하는 패턴의 일부를 형성하는 몰드가 레지스트층(704) 내에 가압되고, 패턴(150)의 형상부를 인쇄하기 위해 부분 단위 방식으로 웨이퍼의 전체 표면을 가로질러 단계식으로 진행되어 프로세스 흐름상 추후에 n-콘택트를 증착하기 위한 영역을 남긴다. n-도핑층(506)의 표면은 프로세스의 이 부분동안 실질적으로 평탄해지는 것이 바람직하다. 예컨대, X-선 리소그래피 또는 원자외선 리소그래피가 레지스트층(704)내에 패턴을 생성하기 위해 사용될 수도 있다. 웨이퍼 상에 레지스트를 증착하고, 웨이퍼 상의 레지스트 내에 패턴을 생성하는 것에 대한 대안으로서, 미리 증착된 에치 마스크가 층(506)의 표면상에 놓여질 수 있다.

<138> 패턴화된 층(704)은 (예컨대, 반응성 이온 식각 프로세스를 사용하여) 패턴을 평탄화층(702)으로 전사하기 위한

마스크로서 사용된다. 평탄화층은 이후에, 패턴을 n-도핑층(506)으로 전사하기 위한 마스크로서 사용된다. GaN층(506)의 식각에 이어서, 평탄화층이 (예컨대, 산소 기반 반응성 이온 에치를 이용하여) 제거된다.

<139> 패턴이 n-도핑층(506)으로 전사된 이후, 형광 재료층이 선택적으로 n-도핑층(506)의 패턴화된 표면 상에 배치될 수 있다(예컨대, 스펜 코팅된다). 몇몇 실시예에서, 형광체는 패턴화된 표면을 정각으로 코팅할 수 있다(패턴화된 표면 내의 개구의 저면 및 측벽을 따라 실질적으로 어떠한 공극도 존재하지 않는 코팅). 또한, 밀봉 재료층이 패턴화된 n-도핑층(506)의 표면 상에 (예컨대, CVD, 스퍼터링, 추후 증발되는 액체 바인더에 의한 혼탁에 의해) 증착될 수 있다. 몇몇 실시예에서, 밀봉재는 하나 이상의 형광 재료를 포함할 수 있다. 몇몇 실시예에서, 형광체는 이 형광체 평균 두께의 20% 미만, 15% 미만, 10% 미만, 5% 미만 또는 2% 미만의 두께 균일도를 달성하도록 압축될 수 있다. 몇몇 실시예에서, 형광체 함유 밀봉재는 패턴화된 표면을 정각으로 코팅할 수 있다.

<140> 유전체 기능 패턴이 n-도핑층(506) 내에 생성된 이후, 개별 LED 다이스가 웨이퍼로부터 절단될 수 있다. 웨이퍼 처리 및 웨이퍼 시험이 완료되고 나서, 개별 LED 다이스가 분리되고, 패키징 및 테스팅을 위해 준비된다. 측벽 패시베이션 단계 및/또는 분리전 딥 메사 식각 단계가 사용되어 웨이퍼 절단 동안 유발되는 패턴화된 LED의 전기적 및/또는 광학적 특성에 대한 손상 가능성을 감소시킬 수 있다. 개별 LED는 웨이퍼 자체의 크기까지 임의의 크기로 이루어질 수 있지만, 개별 LED는 통상적으로, 약 0.5mm 내지 5mm 사이의 길이를 갖는 측부를 가지는 정사각형 또는 직사각형이다. 다이스를 생성하기 위해, 디바이스를 여기하기 위한 웨이퍼 상의 콘택 패드의 위치를 규정하도록 표준 리소그래피가 사용되고, (예컨대, 전자 빔 증발을 사용하여) 저항 콘택이 원하는 위치상으로 증착된다.

<141> LED 다이가 패키지되는 경우, 또한 패키지는 일반적으로 다이의 기계적 및 환경적인 보호를 제공하면서 집광을 용이하게 할 수 있다. 예컨대, 밀봉재가 사용되지 않을 때 506의 패턴화된 표면을 보호하기 위해 LED 다이 상에 투명 커버가 패키지될 수 있다. 커버 슬립은 노 내에서 용융되는 유리질 프리트를 사용하여 지지부(142)에 부착된다. 지지부의 양단은 예컨대, 에폭시 또는 캡 용접을 사용하여 연결된다. 지지부는 통상적으로 패키지의 Au 도금 표면에 대한 용접을 용이하게 하기 위해 Ni 도금된다. 밀봉재층의 부재는 패턴화된 표면 LED(100)의 단위 면적 당 보다 높은 전력 부하를 견딜 수 있게 하는 것으로 생각된다. 밀봉재의 열화는 표준 LED의 일반적인 손상 메카니즘이 될 수 있으며, 밀봉재층을 사용하지 않으면 피할 수 있다.

<142> LED가 큰 면적의 평탄한 웨이퍼로부터 절단되기 때문에, 면적당 그 광 출력은 면적과 함께 감소되지 않는다. 또한, 웨이퍼로부터 절단된 개별 LED의 단면이 LED의 발광 표면적 보다 단지 미소하게 크기 때문에, 다수의 독립적, 그리고, 개별적으로 어드레스할 수 있는 LED가 어레이 내에 함께 밀접 패킹될 수 있다. 하나의 LED가 (예컨대, 큰 결함으로 인해) 기능하지 않는 경우, 이는 어레이의 성능을 현저히 저하시키지 않으며, 그 이유는 개별 디바이스가 밀접 패킹되어 있기 때문이다.

<143> 특정 실시예를 설명하였지만, 다른 실시예가 가능하다.

<144> 예컨대, 발광 디바이스 및 관련된 층을 위한 특정 두께를 상술하였지만, 다른 두께도 가능하다. 일반적으로, 발광 디바이스는 임의의 원하는 두께를 가질 수 있으며, 발광 디바이스 내의 개별 층은 임의의 원하는 두께를 가질 수 있다. 통상적으로, 다중 층 스택(122) 내의 층의 두께는 영역(130) 내에서 발생되는 광으로부터의 출력을 증가시키기 위해, 광 발생 영역(130)과의 광학적 모드의 공간적 중첩을 증가시키도록 선택된다. 발광 디바이스 내의 특정 층을 위한 예시적 두께는 이하를 포함한다. 일부 실시예에서, 층(134)은 적어도 약 100nm(예컨대, 적어도 약 200nm, 적어도 약 300nm, 적어도 약 400nm, 적어도 약 500nm) 및/또는 최대 약 10미크론(예컨대, 최대 약 5 미크론, 최대 약 3 미크론, 최대 약 1 미크론)의 두께를 가질 수 있다. 특정 실시예에서, 층(128)은 적어도 약 10nm(예컨대, 적어도 약 25nm, 적어도 약 40nm) 및/또는 최대 약 1 미크론(예컨대, 최대 약 500nm, 최대 약 100nm)의 두께를 가진다. 몇몇 실시예에서, 층(126)은 적어도 약 10nm(예컨대, 적어도 약 50nm, 적어도 약 100nm) 및/또는 최대 약 1 미크론(예컨대, 최대 약 500nm, 최대 약 250nm)의 두께를 갖는다. 특정 실시예에서, 광 발생 영역(130)은 적어도 약 10nm(예컨대, 적어도 약 25nm, 적어도 약 50nm, 적어도 약 100nm) 및/또는 최대 약 500nm(예컨대, 최대 약 250nm, 최대 약 150nm)의 두께를 갖는다.

<145> 예컨대, 발광 다이오드를 설명하였지만, 상술된 특징(예컨대, 패턴, 프로세스)을 갖는 다른 발광 디바이스가 사용될 수 있다. 이런 발광 디바이스는 레이저 및 광 증폭기를 포함한다.

<146> 다른 예로서, n-도핑된 층(134)으로부터 분리된 층으로서 전류 확산층(132)을 설명하였지만, 일부 실시예에서, 전류 확산층은 층(134)과 일체가 될 수 있다(예컨대, 그 일부가 될 수 있다). 이런 실시예에서, 전류 확산층은

2D 전자 가스를 형성하기 위해, 층(134)의 비교적 높게 n-도핑된 부분 또는 사이의 이질접합부(예컨대, AlGaN/GaN)가 될 수 있다.

<147> 다른 예로서, 특정 반도체 재료를 설명하였지만, 다른 반도체 재료도 사용될 수 있다. 일반적으로, 발광 디바이스에 사용될 수 있는 임의의 반도체 재료(예컨대, III-V 반도체 재료, 유기 반도체 재료, 실리콘)가 사용될 수 있다. 다른 발광 재료의 예는 InGaAsP, AlInGaN, AlGaAs, InGaAlP를 포함한다. 유기 발광 재료는 알루미늄 트리-8-하이드록시퀴놀린(Alq3) 같은 작은 분자 및 폴리[2-메톡시-5-(2-에틸헥실옥시)-1,4-비닐렌페닐렌] 또는 MEH-PPV 같은 공역 폴리머를 포함한다.

<148> 추가적인 예로서, 큰 면적의 LED를 설명하였지만, LED는 또한 작은 면적의 LED일 수 있다(예컨대, 예지상에서 약 300미크론의 표준 보다 작은 LED).

<149> 다른 예로서, 패턴이 홀로 형성되는, 패턴에 따라 공간적으로 변하는 유전체 기능을 설명하였지만, 패턴은 또한 다른 방식으로 형성될 수도 있다. 예컨대, 패턴은 적절한 층내의 연속적 베인 및/또는 불연속 베인으로 형성될 수 있다. 또한, 가변 유전체 기능의 패턴은 홀 또는 베인을 사용하지 않고 달성될 수 있다. 예컨대, 서로 다른 유전체 기능을 갖는 재료가 적절한 층내에 패턴화될 수 있다. 이런 패턴의 조합도 사용될 수 있다.

<150> 추가 예로서, 층(126)이 은으로 형성되는 것으로 설명하였지만, 다른 재료도 사용될 수 있다. 일부 실시예에서, 층(126)은 반사성 재료의 층상에 충돌하는 광 발생 영역에 의해 발생되는 광의 적어도 약 50%를 반사할 수 있는 재료로 형성되며, 반사성 재료의 층은 재료의 다층 스택과 지지부 사이에 존재한다. 이런 재료의 예는 분산된 Bragg 리플렉터 스택 및 알루미늄과 알루미늄 함유 합금 같은 다양한 금속 및 합금을 포함한다.

<151> 다른 예로서, 다양한 재료로 지지부(120)를 형성할 수 있다. 지지부(120)를 형성할 수 있는 재료의 예로는 구리, 구리-텅스텐, 질화알루미늄, 탄화 규소, 산화 베릴륨, 다이아몬드, TEC 및 알루미늄이 있다.

<152> 추가적인 예로서, 히트 싱크 재료로 형성될 수 있는 층(126)을 설명하였지만, 몇몇 실시예에서, 발광 디바이스는 히트 싱크로서 기능하는 (예컨대, 층(126)과 서브마운트(120) 사이에 배치되는) 별개의 층을 포함할 수 있다. 그러한 실시예에서, 층(126)은 히트 싱크로서 기능할 수 있는 재료로 형성되거나 형성되지 않을 수 있다.

<153> 다른 예로서, 전체 광 발생 영역을 사용하게 하는 것외에 n-도핑층(134)(표면 재결합 담체의 손실 가능성을 실질적으로 줄일 수 있음)으로만 연장될 때 유전체 기능이 변하는 패턴을 설명하였지만, 몇몇 실시예에서, 유전체 기능이 변하는 패턴은 (예컨대, 전류 확산층(132), 광 발생 영역(130), 및/또는 p-도핑층(128)으로) n-도핑층을 지나서 연장될 수 있다.

<154> 또 다른 예로서, 공기가 표면(110)과 커버 슬립(140) 사이에 배치될 수 있는 실시예를 설명하였지만, 몇몇 실시예에서, 공기와 다른 재료 또는 공기에 추가하여 다른 재료가 표면(110)와 커버 슬립(140) 사이에 배치될 수 있다. 일반적으로, 그러한 재료의 굴절률은 적어도 약 1이고 약 1.5 미만(예컨대, 약 1.4 미만, 약 1.3 미만, 약 1.2 미만, 약 1.1 미만)이다. 그러한 재료의 예로는 질소, 공기 또는 열도전성이 높은 일부 가스이다. 그러한 실시예에서, 표면(110)은 패턴화되거나 되지 않을 수 있다. 예컨대, 표면(110)은 패턴화되지 않지만 조면화될 수 있다(즉,  $\lambda/5$  미만의 다양한 크기 및 형태가 임의로 분포된 특징부를 갖는다).

<155> 몇몇 실시예에서, 발광 디바이스는 표면(110) 상에 코팅된 형광 재료층, 커버층(140) 및 지지부(142)를 포함할 수 있다.

<156> 특정 실시예에서, 발광 디바이스는 내부에 형광 재료가 배치된 커버층(140)을 포함할 수 있다. 그러한 실시예에서, 표면(110)은 패턴화되거나 되지 않을 수 있다.

<157> 변형예에서, 광 발생 영역(130)에 의해 방출되는 광은 UV(또는 보라색 또는 청색)이고, 형광층(180)은 적색 형광 재료(예컨대,  $L_2O_2S:Eu^{3+}$ ), 녹색 형광 재료(예컨대, ZnS:Cu,Al,Mn) 및 청색 형광 재료(예컨대,  $(Sr,Ca,Ba,Mg)_{10}(PO_4)_6Cl:Eu^{2+}$ )의 혼합물을 포함한다.

## 도면의 간단한 설명

<6> 도 1은 패턴화된 표면을 갖는 측면도.

<7> 도 2는 도 1의 LED의 패턴화된 표면의 평면도.

- <8> 도 3은 패턴화된 표면을 갖는 LED의 추출 효율을 이조 파라미터의 함수로서 나타낸 그래프.

- <9> 도 4는 LED의 패턴화된 표면의 퓨리에 변환을 나타내는 개략도.

- <10> 도 5는 패턴화된 표면을 갖는 LED의 추출 효율을 최근접 거리의 함수로서 나타낸 그래프.

- <11> 도 6은 패턴화된 표면을 갖는 LED의 추출 효율을 충전 팩터의 함수로서 나타낸 그래프.

- <12> 도 7은 LED의 패턴화된 표면의 평면도.

- <13> 도 8은 상이한 표면 패턴을 갖는 LED들의 추출 효율의 그래프.

- <14> 도 9는 상이한 표면 패턴을 갖는 LED들의 추출 효율의 그래프.

- <15> 도 10은 상이한 표면 패턴을 갖는 LED들의 추출 효율의 그래프.

- <16> 도 11은 상이한 표면 패턴을 갖는 LED들의 추출 효율의 그래프.

- <17> 도 12는 LED의 복사 방출 스펙트럼에 비해 상이한 패턴화된 표면을 갖는 2개의 LED의 퓨리에 변환을 나타내는 개략도.

- <18> 도 13은 상이한 표면을 갖는 LED들의 추출 효율을 각도의 함수로서 나타낸 그래프.

- <19> 도 14는 패턴화된 표면과 이 패턴화된 표면 상의 형광층을 갖는 LED의 측면도.

- <20> 도 15는 패턴화된 표면을 갖는 LED에 대한 에피택설층 전구체의 측면도.

- <21> 도 16은 패턴화된 표면을 갖는 LED에 대한 에피택설층 전구체의 측면도.

- <22> 도 17은 패턴화된 표면을 갖는 LED에 대한 에피택설층 전구체의 측면도.

- <23> 도 18은 패턴화된 표면을 갖는 LED에 대한 에피택설층 전구체의 측면도.

- <24> 도 19는 패턴화된 표면을 갖는 LED에 대한 에피택설층 전구체의 측면도.

- <25> 여러 도면에서 동일한 참조 부호는 동일한 요소를 지시한다.

## 도면

### 도면1

도면2

도면3

## 도면4

## 도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12

도면13

도면14

도면15

도면16

도면17

도면18

도면19