(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第4398225号

(P4398225)

(45) 発行日 平成22年1月13日(2010.1.13)

(24) 登録日 平成21年10月30日(2009.10.30)

(51) Int.Cl.

F 1

H01L 25/065 (2006.01)

H01L 25/08

Z

H01L 25/07 (2006.01)

H01L 25/18 (2006.01)

請求項の数 10 (全 19 頁)

(21) 出願番号

特願2003-376415 (P2003-376415)

(22) 出願日

平成15年11月6日 (2003.11.6)

(65) 公開番号

特開2005-142312 (P2005-142312A)

(43) 公開日

平成17年6月2日 (2005.6.2)

審査請求日

平成18年11月2日 (2006.11.2)

前置審査

(73) 特許権者 503121103

株式会社ルネサステクノロジ

東京都千代田区大手町二丁目6番2号

(74) 代理人 100080001

弁理士 筒井 大和

(72) 発明者 林 義成

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72) 発明者 石川 智和

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72) 発明者 山本 健一

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

第1主面、前記第1主面に形成された複数の配線、前記第1主面に形成された複数のボンディングパッド、前記第1主面に形成された複数のフリップチップ電極、前記第1主面とは反対側の第1裏面、及び前記第1裏面に形成された複数の外部端子搭載電極を有し、6層の配線層から成る配線基板と、

第2主面、前記第2主面に形成された第1半導体素子、前記第2主面に形成された複数の第1電極、及び前記第2主面とは反対側の第2裏面を有し、前記第2主面が前記配線基板の前記第1主面と対向するように、複数のバンプ電極を介して前記配線基板の前記第1主面上にフリップチップ接続された第1半導体チップと、

第3主面、前記第3主面に形成された第2半導体素子、前記第3主面に形成された複数の第2電極、及び前記第3主面とは反対側の第3裏面を有し、前記第3裏面が前記第1半導体チップの前記第2裏面と対向するように、前記第1半導体チップの前記第2裏面上に配置された第2半導体チップと、

前記第2半導体チップの前記複数の第2電極と、これに対応する前記配線基板の前記複数のボンディングパッドとをそれぞれ電気的に接続する複数のワイヤと、

前記配線基板の前記複数の外部端子搭載電極にそれぞれ搭載された複数の外部端子と、を含み、

前記複数のボンディングパッドは、前記複数の配線層のうちの1層目に形成され、

前記複数の外部端子搭載電極は、前記複数の配線層のうちの6層目に形成され、

10

20

前記複数のボンディングパッドのそれぞれには、電解メッキの第1給電用配線が接続されており、

前記複数の外部端子搭載電極のそれぞれには、電解メッキの第2給電用配線が接続されており、

前記複数のボンディングパッド及び前記複数の外部端子搭載電極のそれぞれの表面には、ニッケル合金のメッキ膜が形成されており、

前記第1給電用配線は、前記複数の配線層のうちの1層目に形成されており、

前記第2給電用配線は、前記複数の配線層のうちの5層目及び6層目のそれぞれに形成されていることを特徴とする半導体装置。

【請求項2】

10

請求項1記載の半導体装置において、前記メッキ膜は、ニッケル・金合金の膜であることを特徴とする半導体装置。

【請求項3】

請求項1記載の半導体装置において、前記配線基板の前記複数のフリップチップ電極のそれぞれは、その側面が絶縁膜によって囲まれていることを特徴とする半導体装置。

【請求項4】

請求項1記載の半導体装置において、前記複数の外部端子のそれぞれは、はんだボールから成ることを特徴とする半導体装置。

【請求項5】

20

請求項1記載の半導体装置において、前記複数のバンプ電極のそれぞれは、金バンプ電極であることを特徴とする半導体装置。

【請求項6】

請求項1記載の半導体装置において、前記複数のワイヤのそれぞれは、金線であることを特徴とする半導体装置。

【請求項7】

請求項1記載の半導体装置において、前記第1半導体チップの前記第2裏面上に第3半導体チップが搭載されており、前記第3半導体チップの第4正面に形成された複数の第3電極と、これに対応する前記配線基板の前記複数のボンディングパッドとが、それぞれ複数のワイヤによって電気的に接続されていることを特徴とする半導体装置。

【請求項8】

30

請求項1記載の半導体装置において、前記複数のボンディングパッドは、前記複数のフリップチップ電極の外側に配置されていることを特徴とする半導体装置。

【請求項9】

請求項8記載の半導体装置において、前記配線基板の前記複数のフリップチップ電極には、前記メッキ膜が形成されていないことを特徴とする半導体装置。

【請求項10】

請求項9記載の半導体装置において、前記配線基板の正面の前記複数のフリップチップ電極には、前記第1及び第2給電用配線が接続されていないことを特徴とする半導体装置。

【発明の詳細な説明】

40

【技術分野】

【0001】

本発明は、半導体装置に関し、特に、複数の半導体チップを有したチップ積層型の半導体装置に適用して有効な技術に関する。

【背景技術】

【0002】

従来のチップ積層型の半導体装置（マルチチップモジュール）では、そのパッケージ基板の正面に実装された3個のチップのうち、DRAM（Dynamic Random Access Memory）が形成されたチップおよびフラッシュメモリが形成されたチップは、それぞれA u バンプを介してパッケージ基板の配線と電気的に接続されており、さらに2個のチップの上に

50

は高速マイクロプロセッサが形成されたチップが実装され、このチップはAuワイヤを介してパッケージ基板のボンディングパッドと電気的に接続されている（例えば、特許文献1参照）。

【特許文献1】国際公開番号WO 02/103793 A1号公報（図2）

【発明の開示】

【発明が解決しようとする課題】

【0003】

配線基板の主面上に半導体チップがフリップチップ接続され、さらにこの半導体チップ上に他の半導体チップが積層され、上段の半導体チップが配線基板に対してワイヤボンディングされる構造の半導体装置（マルチチップモジュールやマルチチップパッケージなど）では、配線基板の正面の周縁部にワイヤボンディング用パッド（金属細線接続用電極）が並んで設けられており、フリップチップ用ランド（フリップチップ電極）は、その内側に設けられている。

【0004】

このような構造のチップ積層型の半導体装置の組み立てにおいて、多数個取り基板の製品領域の外側に電解メッキの給電用配線が形成されている場合、フリップチップ用ランドと給電用配線を各々独立して接続する配線を設けるのは困難である。

【0005】

一方、マルチチップパッケージなどの積層型の半導体装置では、多機能で、かつ高密度実装の場合が多く、配線基板の裏面には外部端子接続用として多数のはんだボール接続用ランド（外部端子搭載電極）が狭いピッチで配置されている。

【0006】

本発明者は、チップ積層型の半導体装置において更なる多ピン化（狭ピッチ化）について検討した結果、以下のような問題点を見い出した。

【0007】

すなわち、多ピン化によって、はんだボール接続用ランドの直径をさらに小さくすると、はんだボールとランドの接続力のマージンが少なくなつて両者の接続不良を引き起こすという問題が発生する。

【0008】

また、はんだボールとランドの接続を強化するためにランドに電解メッキを形成しようと/orして、多ピン化によって、ランド間ピッチもさらに狭ピッチ化されるため、ランド間に配置可能な配線本数は非常に少なく、全てのランドに対して電解メッキの給電用配線を製品領域の外側に引き出すのは困難なことが問題である。

【0009】

本発明の目的は、多ピン化を図る半導体装置を提供することにある。

【0010】

また、本発明のその他の目的は、信頼性の向上を図る半導体装置を提供することにある。

【0011】

本発明の前記ならびにその他の目的と新規な特徴は、本明細書の記述および添付図面から明らかになるであろう。

【課題を解決するための手段】

【0012】

本願において開示される発明のうち、代表的なものの概要を簡単に説明すれば、以下のとおりである。

【0013】

すなわち、本発明は、第1正面、前記第1正面に形成された複数の配線、前記第1正面に形成された複数のボンディングパッド、前記第1正面に形成された複数のフリップチップ電極、前記第1正面とは反対側の第1裏面、及び前記第1裏面に形成された複数の外部端子搭載電極を有し、6層の配線層から成る配線基板と、第2正面、前記第2正面に形成

10

20

30

40

50

された第1半導体素子、前記第2主面に形成された複数の第1電極、及び前記第2主面とは反対側の第2裏面を有し、前記第2主面が前記配線基板の前記第1主面と対向するように、複数のバンプ電極を介して前記配線基板の前記第1主面上にフリップチップ接続された第1半導体チップと、第3主面、前記第3主面に形成された第2半導体素子、前記第3主面に形成された複数の第2電極、及び前記第3主面とは反対側の第3裏面を有し、前記第3裏面が前記第1半導体チップの前記第2裏面と対向するように、前記第1半導体チップの前記第2裏面上に配置された第2半導体チップと、前記第2半導体チップの前記複数の第2電極と、これに対応する前記配線基板の前記複数のボンディングパッドとをそれぞれ電気的に接続する複数のワイヤと、前記配線基板の前記複数の外部端子搭載電極にそれぞれ搭載された複数の外部端子と、を含み、前記複数のボンディングパッドは、前記複数の配線層のうちの1層目に形成され、前記複数の外部端子搭載電極は、前記複数の配線層のうちの6層目に形成され、前記複数のボンディングパッドのそれぞれには、電解メッキの第1給電用配線が接続されており、前記複数の外部端子搭載電極のそれぞれには、電解メッキの第2給電用配線が接続されており、前記複数のボンディングパッド及び前記複数の外部端子搭載電極のそれぞれの表面には、ニッケル合金のメッキ膜が形成されており、前記第1給電用配線は、前記複数の配線層のうちの1層目に形成されており、前記第2給電用配線は、前記複数の配線層のうちの5層目及び6層目のそれぞれに形成されているものである。

**【発明の効果】**

**【0016】**

本願において開示される発明のうち、代表的なものによって得られる効果を簡単に説明すれば、以下のとおりである。

**【0017】**

チップ積層型の半導体装置において、配線基板の主面の金属細線接続用電極と裏面の外部端子搭載電極のそれぞれの表面にニッケル合金のメッキ膜が形成され、外部端子搭載電極のメッキ膜に接続する電解メッキの給電用配線が配線基板の内層に形成されていることにより、配線基板の裏面において外部端子搭載電極を狭ピッチ化して配置させることができ、半導体装置の多ピン化を図ることができる。

**【発明を実施するための最良の形態】**

**【0018】**

以下の実施の形態では特に必要なとき以外は同一または同様な部分の説明を原則として繰り返さない。

**【0019】**

さらに、以下の実施の形態では便宜上その必要があるときは、複数のセクションまたは実施の形態に分割して説明するが、特に明示した場合を除き、それらはお互いに無関係なものではなく、一方は他方の一部または全部の変形例、詳細、補足説明などの関係にある。

**【0020】**

また、以下の実施の形態において、要素の数など（個数、数値、量、範囲などを含む）に言及する場合、特に明示した場合および原理的に明らかに特定の数に限定される場合などを除き、その特定の数に限定されるものではなく、特定の数以上でも以下でも良いものとする。

**【0021】**

以下、本発明の実施の形態を図面に基づいて詳細に説明する。なお、実施の形態を説明するための全図において、同一の機能を有する部材には同一の符号を付し、その繰り返しの説明は省略する。

**【0022】**

**(実施の形態)**

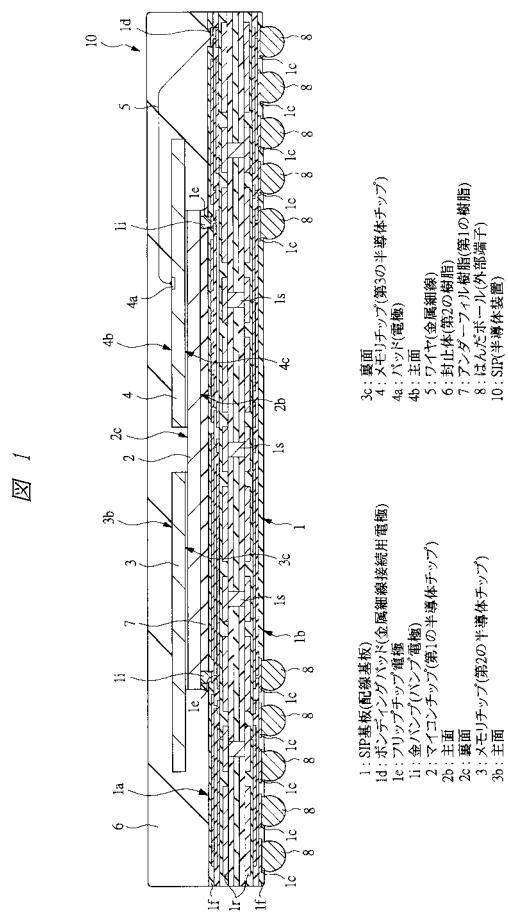

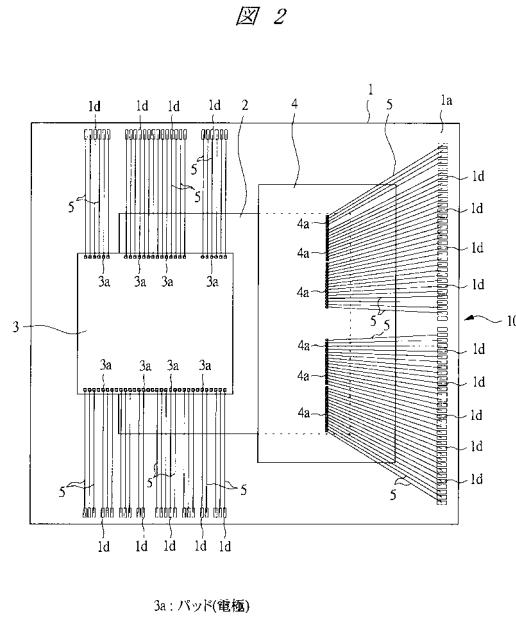

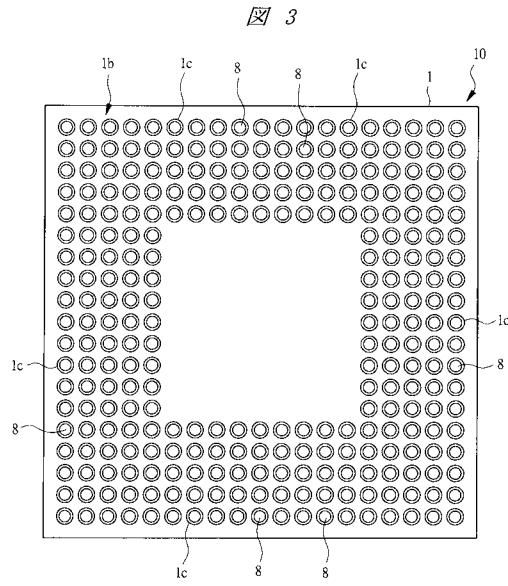

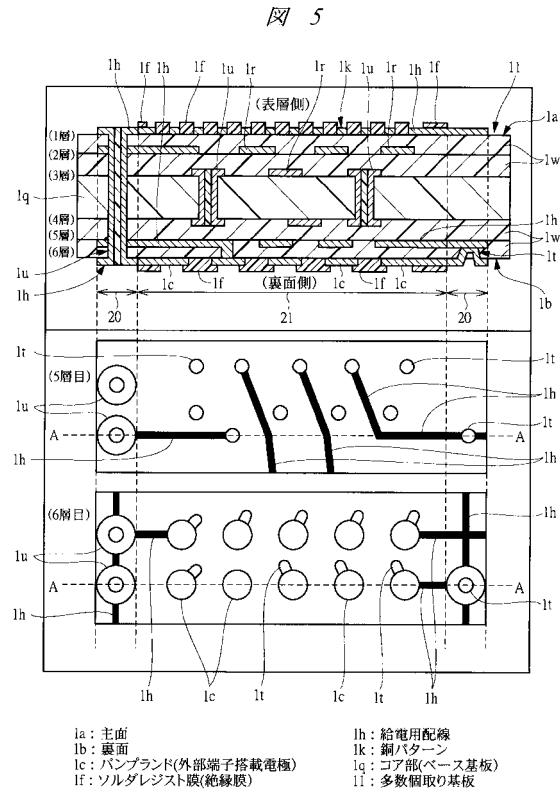

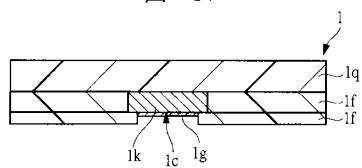

図1は本発明の実施の形態の半導体装置の構造の一例を示す断面図、図2は図1に示す半導体装置の構造を封止体を透過して示す平面図、図3は図1に示す半導体装置の構造を

10

20

30

40

50

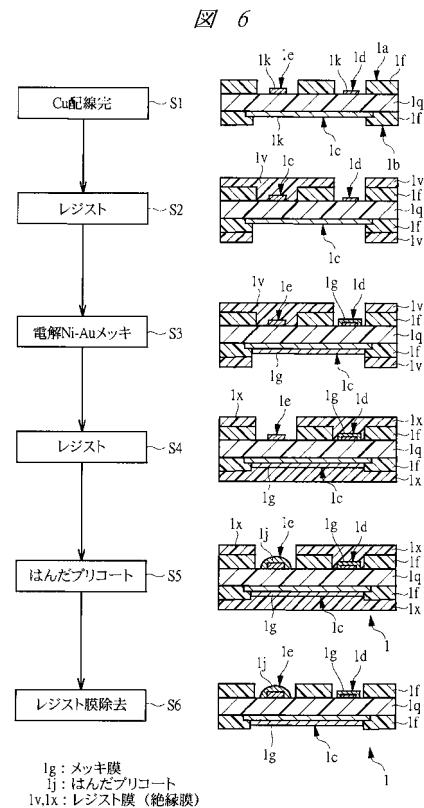

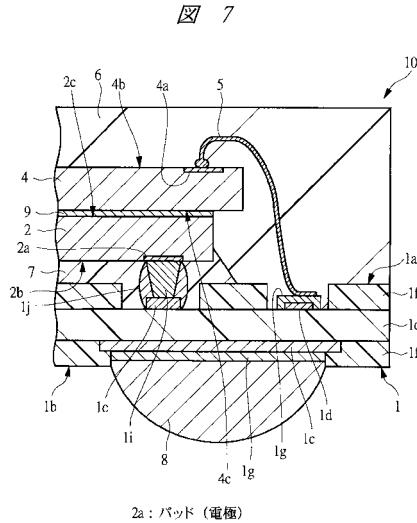

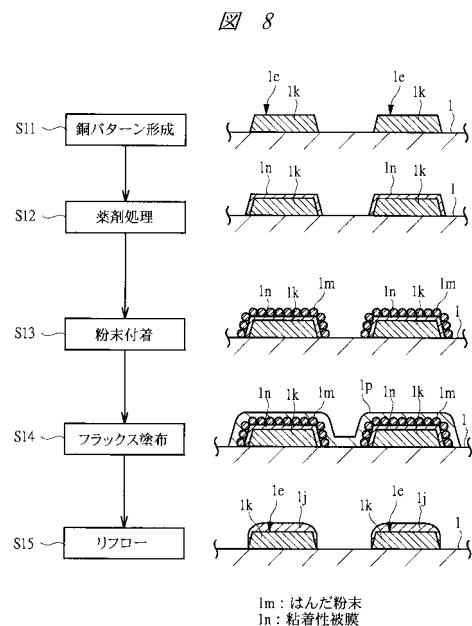

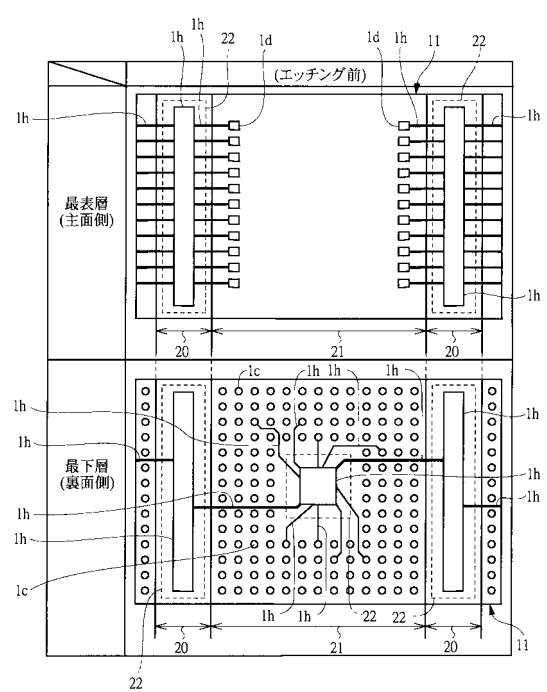

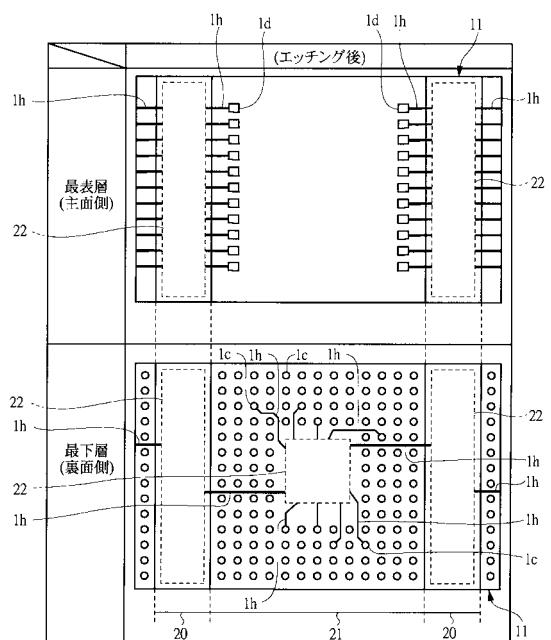

示す裏面図、図4は図1に示す半導体装置のシステムの一例を示すプロック構成図、図5は図1に示す半導体装置の組み立てに用いられる多数個取り基板（配線基板）の構造の一例を示す断面図と、5層目および6層目の平面図、図6は図5に示す配線基板の各電極の形成方法の一例を示す製造プロセスフロー図、図7は図1に示す半導体装置の構造の一例を模式化して示す部分拡大断面図、図8は図5に示す配線基板のフリップチップ電極における高精度プリコートの形成方法の一例を示す製造プロセスフロー図、図9は図1に示す半導体装置の配線基板におけるフリップチップ電極の構造の一例を示す部分拡大断面図、図10および図11はそれぞれ図1に示す半導体装置の配線基板における変形例のフリップチップ電極の構造を示す部分拡大断面図、図12は図1に示す半導体装置の配線基板における外部端子搭載電極の構造の一例を示す部分拡大断面図、図13および図14はそれぞれ図1に示す半導体装置の配線基板における変形例の外部端子搭載電極の構造を示す部分拡大断面図、図15は本発明の実施の形態の変形例の配線基板の給電用配線の除去方法におけるエッチバック前の最表層と最下層の構造を示す平面図、図16はエッチバック後の最表層と最下層の構造を示す平面図である。

#### 【0023】

図1～図3に示す本実施の形態の半導体装置は、配線基板上に3つの半導体チップ（第1、第2および第3の半導体チップ）が搭載されたチップ積層型のものである。なお、複数の半導体チップを同一の配線基板上に搭載した半導体装置をマルチチップモジュール（MCM）といい、半導体チップが積層された構造のMCMをスタック構造のMCMという。また、本実施の形態の半導体装置では、3つの半導体チップのうち、第1の半導体チップがマイコンチップ2であり、第2の半導体チップがFlash Memoryなどのメモリチップ3であり、第3の半導体チップがDRAM（Dynamic Random Access Memory）などのメモリチップ4であり、このように、メモリチップ3、4とこれらを制御するマイコンチップ2とを同一の配線基板上に搭載した半導体装置をシステムインパッケージ（SIP10）と呼ぶ。

#### 【0024】

図1～図3に示す本実施の形態のSIP10の詳細構造について説明すると、正面1aに複数の配線と複数の電極（ボンディングパッド1dやフリップチップ電極1e）を有し、かつ正面1aと反対側の裏面1bに複数のバンプランド（外部端子搭載電極）1cが形成された配線基板であるSIP基板1と、正面2bに半導体素子および複数のパッド（電極）2aを有し、かつSIP基板1の正面1a上に金バンプ（バンプ電極）1iを介してフリップチップ接続された第1の半導体チップであるマイコンチップ2と、正面3bに半導体素子および複数のパッド（電極）3aを有し、かつマイコンチップ2の裏面2c上にダイボンド材9（図7参照）を介して配置された第2の半導体チップであるメモリチップ3と、正面4bに半導体素子および複数のパッド（電極）4aを有し、かつマイコンチップ2の裏面2c上にダイボンド材9を介して配置された第3の半導体チップであるメモリチップ4と、メモリチップ3の正面3bの複数のパッド3aとこれに対応するSIP基板1の正面1aのボンディングパッド1dとをそれぞれ接続し、また、メモリチップ4の正面4bの複数のパッド4aとこれに対応するSIP基板1の正面1aのボンディングパッド1dとをそれぞれ接続する複数の金属細線であるワイヤ5と、マイコンチップ2、メモリチップ3、4および複数のワイヤ5を樹脂封止する封止体6と、SIP基板1の裏面1bのバンプランド1cに搭載された複数の外部端子であるはんだボール8とから成る。

#### 【0025】

さらに、SIP10では、図7に示すように、SIP基板1の正面1aの複数の電極におけるボンディングパッド（金属細線接続用電極）1dと、裏面1bのバンプランド（外部端子搭載電極）1cのそれぞれの表面にニッケル・金合金のメッキ膜1gが形成されており、裏面1bのバンプランド1cのメッキ膜1gに接続する電解メッキの給電用配線1hが、図5に示すように、SIP基板1（多数個取り基板11）の内層に形成されている。

#### 【0026】

10

20

30

40

50

すなわち、本実施の形態のSIP10は、図1および図2に示すように、配線基板であるSIP基板1に対してフリップチップ接続されるマイコンチップ2と、ワイヤボンディングされるメモリチップ3，4を有しており、マイコンチップ2の上にメモリチップ3，4が積層されたチップ積層型の半導体装置である。SIP10の裏面1bには、図3に示すように、外部端子として複数のはんだボール8がそれぞれバンブランド1cに設けられている。

#### 【0027】

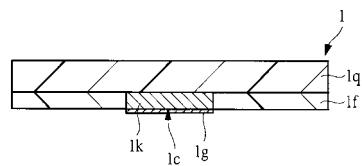

その際、SIP基板1において、裏面1bのバンブランド1c（下地は図6に示す銅パターント1k）の表面にニッケル-金合金のメッキ膜1gを形成しており、このメッキ膜1gを形成する際に用いられる電解メッキの給電用配線1hをSIP基板1の内層に形成したことにより、多ピン化のための裏面1bの空きスペースを確保することができる。10

#### 【0028】

さらに、各バンブランド1cの表面にニッケル-金合金のメッキ膜1gが形成されるため、バンブランド1cとはんだボール8との接続強度を高めることができ、その結果、バンブランド1cの直径をさらに小さくすることが可能になるとともに、バンブランド1cの配列の狭ピッチ化を図ることも可能になる。

#### 【0029】

これにより、SIP10の多ピン化を図ることができる。

#### 【0030】

次に、本実施の形態のSIP10におけるマイコンチップ2と、メモリチップ3，4との制御関係について説明する。20

#### 【0031】

メモリチップ3，4は、マイコンチップ2によって制御される。マイコンチップ2およびメモリチップ3，4の機能とそれに伴うピン構成について図4を参照しながら説明する。

#### 【0032】

ここでは、実施の形態に即し、フラッシュメモリが形成されたメモリチップ3とDRAMが形成されたメモリチップ4を有する場合について説明するが、メモリチップ3，4の数や種類については、この例に限られるものではない。

#### 【0033】

マイコンチップ2は、システムの外部に設けられた外部LSI（Large Scale Integrated circuit）とシステムの内部に設けられたメモリチップ3，4との間を仲介してデータの入出力を行う。そのために、マイコンチップ2は、外部インターフェース用の論理アドレス（外部アドレス）をフラッシュメモリまたはDRAM用のアドレスに変換する。30

#### 【0034】

マイコンチップ2がこのような役割を担う場合、マイコンチップ2には、マイコンチップ2とメモリチップ3，4の間のインターフェースに必要なピン数以外に、外部インターフェースを構成するピンが必要になる。したがって、マイコンチップ2は、外部インターフェースに必要なピン数の分、メモリチップ3，4に比較してピン数が多くなる。

#### 【0035】

本実施の形態のマイコンチップ2は、外部インターフェースとして、例えば、PCIバスやUSBバスを有している。このように、マイコンチップ2が複数種類の外部インターフェースを持つ場合は、マイコンチップ2の外部インターフェースが1種類の場合に比較してマイコンチップ2に必要なピン数が多くなる。40

#### 【0036】

メモリチップ3，4がフラッシュメモリやDRAMなど複数種類設けられている場合、マイコンチップ2のメモリインターフェースに必要なピン数は、それぞれのメモリチップのインターフェースが有するピン数に比較して多くなる。

#### 【0037】

このように、メモリチップ3，4として複数種類のメモリを有する場合には、マイコン50

チップ2のメモリインターフェースの構成としては、それぞれのメモリチップ3，4が有するインターフェースのピン数よりも多くなる場合がある。

#### 【0038】

また、マイコンチップ2には、MPU以外にさまざまな回路を有する場合があり、その場合は、それぞれの回路に対して安定した電源を供給するためにより多くのピン数が必要となる。例えば、本実施の形態のマイコンチップ2は、A/D、D/A変換回路やPLL回路を有している。このようなA/D、D/A変換回路やPLL回路は、自らが電源ノイズ源になり得るとともに、外部からの電源ノイズに弱い性質を持つため、MPUとは分離された電源供給ピンを持っており、これにより、マイコンチップ2のピン数はさらに増える。また、マイコンチップ2は、外部インターフェース回路を有しているが、外部インターフェース回路における安定した信号增幅を実現するためには、MPUなどの内部回路とは独立した電源供給ピンを必要とするので、これによってもマイコンチップ2のピン数は増える。10

#### 【0039】

したがって、例えば、メモリチップ4のパッド4aは、70個（端子、ピン）、メモリチップ3のパッド3aは、56個であり、その合計は126個程度であるのに対し、マイコンチップ2の金バンプ1iは、272個となっており、マイコンチップ2は、システム内部（メモリチップ3，4など）とのインターフェースに加えて、システム外部との各種インターフェースを備えた多ポート構造で構成されているため、ピン数はメモリチップ3，4に比べて遥かに多い。結果的に、本実施の形態のSIP10の場合、総合計で、400個前後の外部端子が必要になるが、各バンプランド1cの給電用配線1hをSIP基板1の内層で引き回しているため、多ピン化に対応することができ、さらに多ピン化が進んだ場合であっても、バンプランド1cの配置の狭ピッチ化にも対応することができる。20

#### 【0040】

なお、マイコンチップ2はSIP基板1に対してフリップチップ接続であり、SIP基板1の正面1aに多数のフリップチップ電極1eが形成されているが、ワイヤ5と接続するボンディングパッド1dが正面1aの周縁部に配置されているのに対して、フリップチップ電極1eはその内側の中央寄りに配置されており、裏面1bの各バンプランド1cに接続する給電用配線1hを正面1a側の各フリップチップ電極1eを介して正面1a側で外方に引き出すのは非常に困難である。したがって、本実施の形態のSIP10のように、給電用配線1hをSIP基板1の内層に形成することは非常に有効である。30

#### 【0041】

本実施の形態のSIP10に用いられるSIP基板1は、図5の断面図に示すように、ベース基板であるコア部1qの表裏両面に配線を形成し、さらにこの両側にビルドアップ製法などによって絶縁層1wと導電層（配線層）とを交互に積層して形成した多層配線基板である。図5に示す例の場合、6層の配線層を有した多数個取り基板（配線基板）11があり、この多数個取り基板11を用いて組み立てられたパッケージが6層の配線層を有するSIP基板1が組み込まれた図1に示すSIP10である。

#### 【0042】

SIP基板1において、コア部1qの表裏両側の端子は、図1に示すようにベースビア1sによって接続されている。また、各配線層には内部配線1rが形成されている。40

#### 【0043】

なお、本実施の形態のSIP10に組み込まれるSIP基板1は、図5に示す多数個取り基板11を用いて組み立てたものである。すなわち、製品領域21がSIP10の領域であり、その外側に個片化時に切断される切断部20が形成されている。したがって、多数個取り基板11の製品領域21がSIP基板1に相当するものであるが、その内層に裏面1bのバンプランド1cのニッケル-金合金のメッキ膜1gを形成するための給電用配線1hが形成されている。図5では、5層目の給電用配線1hを介して裏面1bのバンプランド1cと切断部20のスルーホール配線1uとが接続されている。あるいは、6層目の離れた位置のバンプランド1c同士が、6層目の切断部20のビア1tおよび5，6層

目の給電用配線 1 h を介して接続されている。

**【 0 0 4 4 】**

また、バンプランド列のうち、比較的中央寄りに配置されたバンプランド 1 c は、単独で給電用配線 1 h のみと接続しており、バンプランド 1 c と接続した単独の給電用配線 1 h が外側に引き出されているものもある。

**【 0 0 4 5 】**

このようにして多数個取り基板 1 1 の状態では、裏面 1 b の全てのバンプランド 1 c が単独、あるいは内層の給電用配線 1 h 、または切断部 2 0 の給電用配線 1 h および切断部 2 0 のスルーホール配線 1 u やビア 1 t を介して複数繋がった状態で外側の切断部 2 0 に引き出されており、この状態で各バンプランド 1 c のメッキ膜 1 g に対して給電が行われてニッケル - 金合金のメッキ膜 1 g が形成される。10

**【 0 0 4 6 】**

さらに、S I P 1 0 組み立て後の個片化時にダイシングなどによって切断部 2 0 を切断することにより、各バンプランド 1 c がそれぞれ絶縁されてランド間で電気的に接続されていない状態になる（ただし、G N D 用ランドなどの共通電極の場合は、接続されていてもよい）。

**【 0 0 4 7 】**

また、本実施の形態の S I P 1 0 の S I P 基板 1 では、図 7 に示すように、マイコンチップ 2 のフリップチップ接続は、金バンプ 1 i とはんだとの接続であるため、S I P 基板 1 の主面 1 a の複数のフリップチップ電極 1 e それぞれには電解メッキは施されていない。したがって、それぞれのフリップチップ電極 1 e には給電用配線 1 h は接続されていない。20

**【 0 0 4 8 】**

また、金属細線であるワイヤ 5 には、金線を用いているため、ワイヤ 5 が接続される S I P 基板 1 の主面 1 a 側のボンディングパッド 1 d の表面には、裏面 1 b のバンプランド 1 c と同様に、ニッケル - 金合金のメッキ膜 1 g が形成されており、金線のワイヤ 5 とボンディングパッド 1 d の接続強度を高めている。

**【 0 0 4 9 】**

なお、各ボンディングパッド 1 d は、図 2 に示すように、主面 1 a においてその周縁部に沿って並んで配置されているため、給電用配線 1 h を製品領域 2 1 の外側に引き出すのは容易である。30

**【 0 0 5 0 】**

また、マイコンチップ 2 と S I P 基板 1 の主面 1 a との間、すなわちフリップチップ接続部には、アンダーフィル樹脂 7 が注入されており、フリップチップ接続部を保護している。

**【 0 0 5 1 】**

本実施の形態の S I P 1 0 によれば、S I P 基板 1 の裏面 1 b の各バンプランド 1 c に接続する電解メッキの給電用配線 1 h を S I P 基板 1 の内層に形成したことにより、多ピン化のための裏面 1 b の空きスペースを確保することができる。

**【 0 0 5 2 】**

さらに、下地が銅パターン 1 k （図 6 参照）で形成された各バンプランド 1 c の表面にニッケル - 金合金のメッキ膜 1 g が形成されるため、ニッケル（N i ）と錫（S n ）、およびニッケルと銅（C u ）それぞれの界面の接着力は、錫と銅の界面の接着力に比較して強いことから、バンプランド 1 c とはんだボール 8 の接続強度を高めることができる。40

**【 0 0 5 3 】**

その結果、バンプランド 1 c の直径をさらに小さくすることが可能になるとともに、バンプランド 1 c の配列の狭ピッチ化を図ることも可能になり、S I P 1 0 の多ピン化を図ることができる。

**【 0 0 5 4 】**

また、S I P 基板 1 の裏面 1 b のバンプランド 1 c の表面にニッケル - 金合金のメッキ50

膜 1 g が形成されることにより、バンプランド 1 c とはんだボール 8 の接続強度を高めることができる。今後、はんだボール 8 のはんだが鉛フリー化された場合においても、バンプランド 1 c の表面にニッケル - 金合金のメッキ膜 1 g を形成してバンプランド 1 c とはんだボール 8 の接続強度を高めることはより効果的である。

#### 【 0 0 5 5 】

したがって、多ピン化によってランド面積が小さくなってもはんだボール 8 とバンプランド 1 c の接続不良の発生を低減することができる。その結果、チップ積層型の S I P 1 0 の信頼性の向上を図ることができる。

#### 【 0 0 5 6 】

さらに、はんだボール 8 とバンプランド 1 c の接続不良の発生を低減することができるため、S I P 1 0 の歩留りの向上を図ることができる。

10

#### 【 0 0 5 7 】

次に、図 6 に示す模式図を用いて、本実施の形態の S I P 1 0 の組み立てに用いられる S I P 基板 1 の各電極の形成方法について説明する。

#### 【 0 0 5 8 】

まず、S I P 基板 1 の正面 1 a に銅パターン 1 k によって複数のボンディングパッド 1 d、およびこのボンディングパッド 1 d に接続する電解メッキの給電用配線 1 h（図 5 参照）およびフリップチップ電極 1 e を形成し、さらに、S I P 基板 1 の裏面 1 b に銅パターン 1 k によって複数のバンプランド 1 c を形成するとともに、バンプランド 1 c に接続する電解メッキの給電用配線 1 h を内層に形成してステップ S 1 の C u 配線完を行う。

20

#### 【 0 0 5 9 】

その後、ステップ S 2 のレジストにより、複数のフリップチップ電極 1 e のみを絶縁膜であるレジスト膜 1 v によって覆う。その際、正面 1 a のボンディングパッド 1 d と裏面 1 b のバンプランド 1 c は露出させておく。

#### 【 0 0 6 0 】

その後、ステップ S 3 に示す電解 N i - A u (金) メッキを行って正面 1 a のボンディングパッド 1 d と裏面 1 b のバンプランド 1 c にニッケル - 金のメッキ膜 1 g を形成する。すなわち、フリップチップ電極 1 e をレジスト膜 1 v によって覆った状態で、それぞれの給電用配線 1 h を介して給電を行ってボンディングパッド 1 d およびバンプランド 1 c それぞれの表面にニッケル - 金のメッキ膜 1 g を形成する。

30

#### 【 0 0 6 1 】

その後、ステップ S 4 のレジストにより、フリップチップ電極 1 e のみを露出させてボンディングパッド 1 d およびバンプランド 1 c をレジスト膜 1 x によって覆う。

#### 【 0 0 6 2 】

その後、ステップ S 5 に示すはんだプリコートを行う。すなわち、ボンディングパッド 1 d およびバンプランド 1 c をレジスト膜 1 x によって覆った状態で、フリップチップ電極 1 e の表面にはんだプリコート 1 j を形成してフリップチップ電極 1 e の表面を薄いはんだ膜で覆う。

#### 【 0 0 6 3 】

その後、ステップ S 6 に示すレジスト膜 1 x の除去を行う。

40

#### 【 0 0 6 4 】

これによって、S I P 基板 1 の各電極が形成され、図 7 に示すように、S I P 1 0 の組み立てにおいて、フリップチップ電極 1 e は金バンプ 1 i を介してマイコンチップ 2 とフリップチップ接続し、また、ボンディングパッド 1 d は金線であるワイヤ 5 とワイヤボンディングによって接続し、さらにバンプランド 1 c は、はんだボール 8 とそれぞれ接続する。

#### 【 0 0 6 5 】

なお、フリップチップ電極 1 e の表面にはんだプリコート 1 j を形成する際には、フリップチップ電極 1 e の狭ピッチ化に対応するように高精度にはんだ膜を形成する必要がある。そこで、図 8 のステップ S 1 1 に示すように、まず、フリップチップ電極 1 e それぞ

50

れの銅パターン 1 k を形成し、その後、ステップ S 1 2 の薬剤処理を行う。すなわち、フリップチップ電極 1 e の銅パターン 1 k に接着剤となる粘着性被膜 1 n を形成する。

#### 【 0 0 6 6 】

その後、ステップ S 1 3 の粉末付着により、粘着性被膜 1 n 上にはんだ粉末 1 m を付着させ、はんだ粉末付着後、ステップ S 1 4 のフラックス塗布により、はんだ粉末 1 m 上にフラックス 1 p を塗布して覆い、その後、ステップ S 1 5 のリフローを行う。すなわち、はんだ粉末 1 m とフラックス 1 p で覆われた銅パターン 1 k を加熱することにより、はんだが溶融してはんだプリコート 1 j が形成される。このようにしてはんだプリコート 1 j を高精度に形成する。

#### 【 0 0 6 7 】

なお、はんだプリコート 1 j を高精度に形成する方法としては、はんだ成分を有した合金を銅 ( C u ) と置換反応させて形成する方法などを用いてもよい。

#### 【 0 0 6 8 】

次に、本実施の形態の S I P 1 0 の製造方法について説明する。

#### 【 0 0 6 9 】

まず、図 5 に示す製品領域 2 1において、図 6 に示すような主面 1 a に複数の配線と複数のボンディングパッド 1 d と複数のフリップチップ電極 1 e とを有しているとともに、裏面 1 b に複数のバンプランド 1 c を有しており、さらにボンディングパッド 1 d とバンプランド 1 c のそれぞれの表面にニッケル - 金合金の電解メッキのメッキ膜 1 g が形成され、かつ主面 1 a のフリップチップ電極 1 e の表面にはんだプリコート 1 j が形成された図 5 に示す多数個取り基板 ( 配線基板 ) 1 1 を準備する。

#### 【 0 0 7 0 】

なお、多数個取り基板 1 1においては、製品領域 2 1 の外側の切断部 2 0 に、複数のバンプランド 1 c 間を電気的に接続する給電用配線 1 h 、スルーホール配線 1 u およびビア 1 t などが形成されている。

#### 【 0 0 7 1 】

一方、主面 2 b に半導体素子および複数の金バンプ ( バンプ電極 ) 1 i が形成された第 1 の半導体チップであるマイコンチップ 2 と、主面 3 b に半導体素子および複数の電極が形成された第 2 の半導体チップであるメモリチップ 3 と、主面 4 b に半導体素子および複数の電極が形成された第 3 の半導体チップであるメモリチップ 4 とを準備する。なお、一例として、メモリチップ 3 がFlash Memory 、メモリチップ 4 がD R A M の場合を取り上げ、マイコンチップ 2 はメモリチップ 3 , 4 を制御するものである。

#### 【 0 0 7 2 】

その後、マイコンチップ 2 の主面 2 b と多数個取り基板 1 1 の製品領域 2 1 の主面 1 a とを対向させて、マイコンチップ 2 の複数の金バンプ 1 i を多数個取り基板 1 1 の製品領域 2 1 のフリップチップ電極 1 e に接続して多数個取り基板 1 1 の製品領域 2 1 の主面 1 a にマイコンチップ 2 をフリップチップ接続する。

#### 【 0 0 7 3 】

その際、熱圧着によってマイコンチップ 2 をフリップチップ接続する。すなわち、フリップチップ接続部を加熱することにより、図 7 に示すように、フリップチップ電極 1 e の表面のはんだプリコート 1 j を溶融して金 - はんだ接続でマイコンチップ 2 をフリップチップ接続する。

#### 【 0 0 7 4 】

その後、マイコンチップ 2 の主面 2 b と多数個取り基板 1 1 の主面 1 a との間に第 1 の樹脂であるアンダーフィル樹脂 7 を注入してアンダーフィル封止を行う。

#### 【 0 0 7 5 】

その後、マイコンチップ 2 の裏面 2 c とメモリチップ 3 の裏面 3 c とを対向させてマイコンチップ 2 上にメモリチップ 3 を積層する。その際、マイコンチップ 2 上にダイボンド材 9 を介してメモリチップ 3 を固定する。

#### 【 0 0 7 6 】

10

20

30

40

50

続いて、マイコンチップ2の裏面2cとメモリチップ4の裏面4cとを対向させてマイコンチップ2上にメモリチップ4を積層する。その際、マイコンチップ2上にダイボンド材9を介してメモリチップ4を固定する。

#### 【0077】

その後、メモリチップ3の複数のパッド3aとこれに対応する多数個取り基板11の製品領域21の複数のボンディングパッド1dそれぞれとをワイヤ(金線)5によって接続し、続いてメモリチップ4の複数のパッド4aとこれに対応する多数個取り基板11の製品領域21の複数のボンディングパッド1dそれぞれとをワイヤ5によって接続する。

#### 【0078】

その後、マイコンチップ2、メモリチップ3、メモリチップ4および複数のワイヤ5を第2の樹脂である封止用樹脂によって封止して封止体6を形成する。 10

#### 【0079】

その後、多数個取り基板11の製品領域21の複数のバンブランド1cに外部端子であるはんだボール8を搭載する。

#### 【0080】

外部端子搭載後、多数個取り基板11の切断部20をダイシングによって切断してそれぞれのSIP10に個片化する。これにより、SIP10の組み立て完了となる。 20

#### 【0081】

次に、本実施の形態のSIP10におけるSIP基板1のフリップチップ電極1eとバンブランド1cの構造について説明する。 20

#### 【0082】

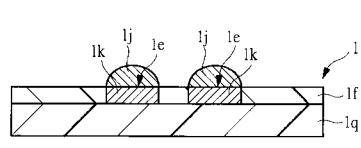

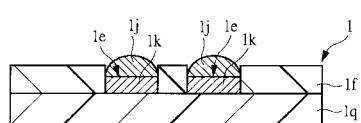

まず、図9、図10および図11は、それぞれSIP基板1のフリップチップ電極1eの構造について示したものであり、フリップチップ電極1eは、その側面が絶縁膜であるソルダレジスト膜1fによって囲まれていることが好ましい。

#### 【0083】

すなわち、フリップチップ電極1eの側面がソルダレジスト膜1fによって囲まれていることにより、フリップチップ電極1eの接続面に形成するはんだプリコート1jの量を少なくすることができ、その結果、隣接するフリップチップ電極1e間で発生するはんだショートを回避することができる。 30

#### 【0084】

これにより、チップ積層型のSIP10の信頼性の向上を図ることができるとともに、SIP10の歩留りの向上を図ることができる。

#### 【0085】

また、フリップチップ電極1eの狭ピッチ化を図ることができる。

#### 【0086】

なお、図10に示すように、フリップチップ電極1eよりこれを囲むソルダレジスト膜1fの高さを高くすることにより、フリップチップ電極1eの接続面に形成するはんだプリコート1jの量をより確実に少なくすることができ、その結果、フリップチップ電極1e間で発生するはんだショートをより確実に回避することができる。 40

#### 【0087】

また、図11に示すように、ソルダレジスト膜1fを2層構造として、上層のソルダレジスト膜1fをフリップチップ電極1eの接続面の周縁部に配置することにより、フリップチップ電極1eの接続面に形成するはんだプリコート1jの量をさらに少なくすることができ、その結果、フリップチップ電極1e間で発生するはんだショートをさらに回避することができる。

#### 【0088】

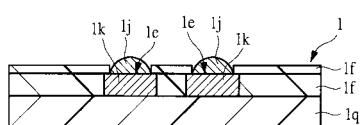

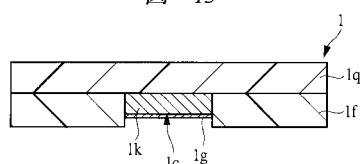

次に、図12、図13および図14は、それぞれSIP基板1のバンブランド1cの構造について示したものであり、バンブランド1cもフリップチップ電極1eと同様に、その側面が絶縁膜であるソルダレジスト膜1fによって囲まれていることが好ましい。

#### 【0089】

バンプランド 1 c の側面がソルダレジスト膜 1 f によって囲まれていることにより、バンプランド 1 c の接続面に形成するはんだボール 8 の量を抑制することができ、その結果、隣接するはんだボール 8 間で発生するはんだショートを低減することができる。

#### 【 0 0 9 0 】

なお、図 13 に示すように、バンプランド 1 c よりソルダレジスト膜 1 f の高さを高くすることにより、バンプランド 1 c の接続面に接続するはんだボール 8 の量をより確実に低減することができ、その結果、バンプランド 1 c 間で発生するはんだショートをより確実に低減することができる。

#### 【 0 0 9 1 】

また、図 14 に示すように、ソルダレジスト膜 1 f を 2 層構造として、上層のソルダレジスト膜 1 f をバンプランド 1 c の接続面の周縁部に配置することにより、バンプランド 1 c の接続面に接続するはんだボール 8 の量をさらに少なくすることができ、その結果、バンプランド 1 c 間で発生するはんだショートをさらに低減することができる。

#### 【 0 0 9 2 】

次に、本実施の形態の S I P 1 0 に組み込まれる S I P 基板 1 の変形例について説明する。

#### 【 0 0 9 3 】

図 15 は変形例の多数個取り基板 1 1 ( S I P 基板 1 ) の最表層 ( 主面 1 a ) と最下層 ( 裏面 1 b ) のそれぞれの配線パターンを示すものである。変形例の多数個取り基板 1 1 ( S I P 基板 1 ) では、裏面 1 b のバンプランド 1 c のニッケル - 金合金のメッキ膜 1 g を形成するための電解メッキの給電用配線 1 h が、裏面 1 b ( 最下層 ) にも形成されている。すなわち、図 15 の最下層に示すように、バンプランド 1 c の配置によるその内側の空きスペース ( 例えば、中央部 ) を利用し、この空きスペースと切断部 2 0 とに広面積パターンによる共通の給電用配線 1 h を配置し、それぞれをリード状の給電用配線 1 h によって接続している。この場合、裏面 1 b において外周部に配置されたバンプランド 1 c から中央部の広面積パターンによる共通の給電用配線 1 h に向かってリード状の給電用配線 1 h が延在している。さらに、中央部の広面積パターンの給電用配線 1 h と複数のバンプランド 1 c がそれぞれリード状の給電用配線 1 h によって接続されている。このようにして裏面 1 b の全てのバンプランド 1 c を、中央部もしくは切断部 2 0 の広面積パターンの共通の給電用配線 1 h にリード状の給電用配線 1 h を介して接続する。

#### 【 0 0 9 4 】

なお、最表層では、複数のボンディングパッド 1 d ( フリップチップ電極 1 e であってもよい ) がそれぞれ単独の給電用配線 1 h によって切断部 2 0 の共通の給電用配線 1 h と接続されている。

#### 【 0 0 9 5 】

図 15 に示すような配線基板において、給電用配線 1 h を用いて各バンプランド 1 c に給電を行ってニッケル - 金合金の電解メッキのメッキ膜 1 g を形成し、その後、基板の製造の最終行程にて、ボンディングパッド 1 d 、バンプランド 1 c およびフリップチップ電極 1 e をレジスト膜で覆った状態で、主面 1 a の切断部 2 0 の広面積パターンの給電用配線 1 h ( 図 15 に点線で示すエッチング部 2 2 ) と、裏面 1 b の中央部および切断部 2 0 の広面積パターンの給電用配線 1 h ( 点線で示すエッチング部 2 2 ) を、図 16 に示すようにエッチングによって除去する。これにより、主面 1 a の各ボンディングパッド 1 d および裏面 1 b の各バンプランド 1 c は、それぞれ共通の広面積パターンの給電用配線 1 h から独立した状態となる。

#### 【 0 0 9 6 】

このように、本実施の形態の S I P 1 0 は、給電後にエッチングにより共通の給電用配線 1 h を除去して製造された S I P 基板 1 を用いて組み立ててもよい。

#### 【 0 0 9 7 】

また、S I P 基板 1 としては、その裏面 1 b の各バンプランド 1 c の表面に、電解メッキによるニッケル - 金合金のメッキ膜 1 g を形成するのではなく、無電解メッキによる二

10

20

30

40

50

ツケル - 金合金の無電解メッキ膜を形成したものを用いてもよい。

**【0098】**

この無電解メッキを使用した場合、裏面1bの配線パターンの引き回しを簡略化することができるとともに、メッキ用の給電工程を無くすことができるため、SIP基板1の製造の簡素化を図ることができる。さらに、SIP基板1の低コスト化を図ることができる。

**【0099】**

以上、本発明者によってなされた発明を発明の実施の形態に基づき具体的に説明したが、本発明は前記発明の実施の形態に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることは言うまでもない。

10

**【0100】**

例えば、前記実施の形態では、SIP10が3つの半導体チップを有する場合を説明したが、SIP10は、SIP基板1に対してフリップチップ接続される半導体チップと、ワイヤボンディングされる半導体チップとの少なくとも2つの半導体チップを有し、さらに裏面1bに複数のバンブランド1cが形成されていれば他のSIP10またはマルチチップモジュールあるいはマルチチップパッケージなどであってもよい。

**【産業上の利用可能性】**

**【0101】**

本発明は、電子装置および半導体製造技術ならびに基板の製造技術に好適である。

**【図面の簡単な説明】**

20

**【0102】**

**【図1】**本発明の実施の形態の半導体装置の構造の一例を示す断面図である。

**【図2】**図1に示す半導体装置の構造を封止体を透過して示す平面図である。

**【図3】**図1に示す半導体装置の構造を示す裏面図である。

**【図4】**図1に示す半導体装置のシステムの一例を示すブロック構成図である。

**【図5】**図1に示す半導体装置の組み立てに用いられる多数個取り基板(配線基板)の構造の一例を示す断面図と、5層目および6層目の平面図である。

**【図6】**図5に示す配線基板の各電極の形成方法の一例を示す製造プロセスフロー図である。

**【図7】**図1に示す半導体装置の構造の一例を模式化して示す部分拡大断面図である。

30

**【図8】**図5に示す配線基板のフリップチップ電極における高精度プリコートの形成方法の一例を示す製造プロセスフロー図である。

**【図9】**図1に示す半導体装置の配線基板におけるフリップチップ電極の構造の一例を示す部分拡大断面図である。

**【図10】**図1に示す半導体装置の配線基板における変形例のフリップチップ電極の構造を示す部分拡大断面図である。

**【図11】**図1に示す半導体装置の配線基板における変形例のフリップチップ電極の構造を示す部分拡大断面図である。

**【図12】**図1に示す半導体装置の配線基板における外部端子搭載電極の構造の一例を示す部分拡大断面図である。

40

**【図13】**図1に示す半導体装置の配線基板における変形例の外部端子搭載電極の構造を示す部分拡大断面図である。

**【図14】**図1に示す半導体装置の配線基板における変形例の外部端子搭載電極の構造を示す部分拡大断面図である。

**【図15】**本発明の実施の形態の変形例の配線基板の給電用配線の除去方法におけるエッチバック前の最表層と最下層の構造を示す平面図である。

**【図16】**本発明の実施の形態の変形例の配線基板の給電用配線の除去方法におけるエッチバック後の最表層と最下層の構造を示す平面図である。

**【符号の説明】**

**【0103】**

50

- 1 S I P 基板 (配線基板)

1 a 主面

1 b 裏面

1 c バンブランド (外部端子搭載電極)

1 d ボンディングパッド (金属細線接続用電極)

1 e フリップチップ電極

1 f ソルダレジスト膜 (絶縁膜)

1 g メッキ膜

1 h 給電用配線

1 i 金バンプ (バンプ電極) 10

1 j はんだプリコート

1 k 銅パターン

1 m はんだ粉末

1 n 粘着性被膜

1 p フラックス

1 q コア部 (ベース基板)

1 r 内部配線

1 s ベースピア

1 t ピア

1 u スルーホール配線 20

1 v レジスト膜 (絶縁膜)

1 w 絶縁層

1 x レジスト膜 (絶縁膜)

2 マイコンチップ (第1の半導体チップ)

2 a パッド (電極)

2 b 主面

2 c 裏面

3 メモリチップ (第2の半導体チップ)

3 a パッド (電極)

3 b 主面 30

3 c 裏面

4 メモリチップ (第3の半導体チップ)

4 a パッド (電極)

4 b 主面

4 c 裏面

5 ワイヤ (金属細線)

6 封止体 (第2の樹脂)

7 アンダーフィル樹脂 (第1の樹脂)

8 はんだボール (外部端子)

9 ダイボンド材

1 0 S I P (半導体装置) 40

1 1 多数個取り基板 (配線基板)

2 0 切断部

2 1 製品領域

2 2 エッティング部

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

【図6】

【図7】

【図8】

【図 9】

図 9

【図 10】

図 10

【図 11】

図 11

【図 12】

図 12

【図 13】

図 13

【図 14】

図 14

【図 15】

図 15

【図16】

图 16

---

フロントページの続き

(72)発明者 木本 良輔

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

(72)発明者 内藤 孝洋

東京都千代田区丸の内二丁目4番1号 株式会社ルネサステクノロジ内

審査官 田中 永一

(56)参考文献 特開2002-343818(JP,A)

特開2003-007902(JP,A)

特開2001-284783(JP,A)

特開2002-373911(JP,A)

特開2001-344967(JP,A)

特開2002-359446(JP,A)

特開2003-234451(JP,A)

国際公開第02/103793(WO,A1)

特開2002-217361(JP,A)

特開平09-199630(JP,A)

特開2002-026174(JP,A)

特開2003-086735(JP,A)

特開2000-114412(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 25/065

H01L 25/07

H01L 25/18