(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2011-86941

(P2011-86941A)

(43) 公開日 平成23年4月28日(2011.4.28)

(51) Int.Cl.

**HO1L 27/108 (2006.01)**

**HO1L 21/8242 (2006.01)**

**HO1L 21/768 (2006.01)**

**HO1L 23/522 (2006.01)**

**HO1L 21/3205 (2006.01)**

F 1

HO1L 27/10 621C

HO1L 21/90 D

HO1L 27/10 671B

HO1L 21/88 Q

テーマコード(参考)

5FO33

5FO83

審査請求 未請求 請求項の数 45 O L (全 50 頁) 最終頁に続く

(21) 出願番号 特願2010-230439 (P2010-230439)

(22) 出願日 平成22年10月13日 (2010.10.13)

(31) 優先権主張番号 10-2009-0098742

(32) 優先日 平成21年10月16日 (2009.10.16)

(33) 優先権主張国 韓国 (KR)

(31) 優先権主張番号 12/836,081

(32) 優先日 平成22年7月14日 (2010.7.14)

(33) 優先権主張国 米国 (US)

(71) 出願人 390019839

三星電子株式会社

SAMSUNG ELECTRONICS

CO., LTD.

大韓民国京畿道水原市靈通区梅灘洞416

416, Maetan-dong, Yeongtong-gu, Suwon-si,

Gyeonggi-do 442-742

(KR)

(74) 代理人 100089037

弁理士 渡邊 隆

(74) 代理人 100110364

弁理士 実広 信哉

最終頁に続く

(54) 【発明の名称】半導体装置の配線構造物及び配線構造物の製造方法

## (57) 【要約】

【課題】半導体装置の配線構造物及び配線構造物の製造方法を提供すること。

【解決手段】半導体装置の配線構造物の形成方法において、セル領域及び周辺回路領域を有する基板上に第1絶縁膜を形成し、前記第1絶縁膜を貫通して延長する第1導電物質を含む第1コンタクトプラグを前記セル領域に形成する。前記第1コンタクトプラグをカバーして一体で形成され、前記第1導電物質を含む第1導電ラインを前記第1コンタクトプラグと実質的に同時に形成する。前記第1絶縁膜を貫通して延長して、前記第1導電物質を含む第2コンタクトプラグを前記第1コンタクトプラグと実質的に同時に前記周辺回路領域に形成する。前記第2コンタクトプラグをカバーして一体で形成され、前記第1導電物質を含む第2導電ラインを前記第2コンタクトプラグと実質的に同時に形成する。

【選択図】図1

## 【特許請求の範囲】

## 【請求項 1】

セル領域及び周辺回路領域を有する基板を設ける段階と、

前記基板上に第1絶縁膜を形成する段階と、

前記第1絶縁膜を貫通して延長する第1導電物質を含む第1コントラクトプラグを前記セル領域に形成する段階と、

前記第1コントラクトプラグをカバーして前記第1コントラクトプラグと一体で形成して、

第1導電物質を含む第1導電ラインを前記第1コントラクトプラグと同時に形成する段階と、

前記第1絶縁膜を貫通して延長して、第1導電物質を含む第2コントラクトプラグを前記第1コントラクトプラグと同時に前記周辺回路領域に形成する段階と、

前記第2コントラクトプラグをカバーして前記第2コントラクトプラグと一体で形成して、

第1導電物質を含む第2導電ラインを前記第2コントラクトプラグと同時に形成する段階と、

を含む半導体装置の配線構造物の製造方法。 10

## 【請求項 2】

前記第1導電ライン及び前記第2導電ラインは互いに平行したことを特徴とする請求項1に記載の半導体装置の配線構造物の製造方法。

## 【請求項 3】

前記第1絶縁膜、前記第1コントラクトプラグ及び前記第2コントラクトプラグは、それぞれ同じ平面に配置される上部表面を含むことを特徴とする請求項1に記載の半導体装置の配線構造物の製造方法。 20

## 【請求項 4】

少なくとも前記第1導電ライン及び前記第2導電ラインの側部を同時にシリサイド化する(Silicidating)段階をさらに含むことを特徴とする請求項1に記載の半導体装置の配線構造物の製造方法。

## 【請求項 5】

前記第1コントラクトプラグ、前記第1導電ライン、前記第2コントラクトプラグ、及び前記第2導電ラインを同時にシリサイド化する段階をさらに含むことを特徴とする請求項1に記載の半導体装置の配線構造物の製造方法。

## 【請求項 6】

前記基板内に少なくとも一つのトレンチを形成する段階をさらに含むことを特徴とする請求項1に記載の半導体装置の配線構造物の製造方法。 30

## 【請求項 7】

前記少なくとも一つのトレンチは前記第1導電ラインと平行するように配列されることを特徴とする請求項6に記載の半導体装置の配線構造物の製造方法。

## 【請求項 8】

前記第1コントラクトプラグに隣接する前記少なくとも一つのトレンチにゲート電極を形成する段階をさらに含むことを特徴とする請求項6に記載の半導体装置の配線構造物の製造方法。

## 【請求項 9】

前記第1コントラクトプラグに対して前記ゲート電極の対向する側壁上に配置される少なくとも一つの第3コントラクトプラグを前記第1絶縁膜を貫通して形成する段階をさらに含み、前記少なくとも一つの第3コントラクトプラグは前記第1導電ラインより高く延長することを特徴とする請求項8に記載の半導体装置の配線構造物の製造方法。 40

## 【請求項 10】

前記少なくとも一つの第3コントラクトプラグ上に直接キャパシタを形成する段階をさらに含むことを特徴とする請求項9に記載の半導体装置の配線構造物の製造方法。

## 【請求項 11】

セル領域と周辺回路領域を有する基板と、

前記基板上に配置される第1絶縁膜と、

10

20

30

40

50

前記セル領域に配置されて、前記第1絶縁膜を貫通して延長する第1導電物質を含む第1コンタクトプラグと、

前記セル領域に配置されて第1方向に沿って延長して、前記第1コンタクトプラグと一緒に形成されて前記第1コンタクトプラグを覆う第1導電物質を含む第1導電ラインと、

前記周辺回路領域に配置されて、前記第1絶縁膜を貫通して延長する第1導電物質を含む第2コンタクトプラグと、

前記周辺回路領域に配置されて第2方向に沿って延長して、前記第2コンタクトプラグと一緒に形成されて前記第2コンタクトプラグを覆う第1導電物質を含む第2導電ラインと、を備える半導体装置の配線構造物。

【請求項12】

前記第1絶縁膜及び前記第1コンタクトプラグはそれぞれ同じ平面に配置される上部表面を含むことを特徴とする請求項11に記載の半導体装置の配線構造物。

【請求項13】

前記第1絶縁膜及び前記第1コンタクトプラグは同じ厚さを有することを特徴とする請求項11に記載の半導体装置の配線構造物。

【請求項14】

前記第1導電ラインは前記第1絶縁膜上に直接配置されることを特徴とする請求項11に記載の半導体装置の配線構造物。

【請求項15】

前記第1コンタクトプラグ及び前記第1導電ラインはシリサイドを除けば同じ物質を含むことを特徴とする請求項11に記載の半導体装置の配線構造物。

【請求項16】

少なくとも前記第1導電ライン及び前記第2導電ラインの側部はシリサイドを含むことを特徴とする請求項11に記載の半導体装置の配線構造物。

【請求項17】

前記第1コンタクトプラグ、前記第1導電ライン、前記第2コンタクトプラグ、及び前記第2導電ラインは、全部シリサイドを含むことを特徴とする請求項11に記載の半導体装置の配線構造物。

【請求項18】

前記第1コンタクトプラグと前記第1導電ラインを含む前記セル領域に配置される第1ソース／ドレーン電極と、

前記第2コンタクトプラグと前記第2導電ラインを含む前記周辺回路領域に配置される第2ソース／ドレーン電極と、

前記第2ソース／ドレーン電極の少なくとも一つの側壁上に配置される垂直スペーサ(Spacer)をさらに含み、前記第2ソース／ドレーン電極は、ポリシリコンパターンを有する前記第2コンタクトプラグと金属シリサイドを有する前記第2導電ラインと、を含むことを特徴とする請求項11に記載の半導体装置の配線構造物。

【請求項19】

前記第1導電ラインに平行で前記第1コンタクトプラグに隣接するように配列されるゲート電極をさらに含むことを特徴とする請求項11に記載の半導体装置の配線構造物。

【請求項20】

前記第1絶縁膜を貫通して延長して、前記第1コンタクトプラグに対して前記ゲート電極の対向の側面上に配置されて、前記第1導電ラインより高く延長する少なくとも一つの第3コンタクトプラグと、

前記第3コンタクトプラグ上に直接配置されるキャパシタと、をさらに含むことを特徴とする請求項19に記載の半導体装置の配線構造物。

【請求項21】

基板上に第1絶縁膜を形成する段階と、

前記基板のアクティブ領域の前記第1絶縁膜に第1コンタクトホールを形成する段階と、

10

20

30

40

50

第1導電物質を使って前記第1コンタクトホールに第1コンタクトプラグを形成すると同時に前記第1コンタクトプラグと一緒に形成されて前記第1コンタクトプラグを覆う導電膜を形成する段階と、

前記第1コンタクトプラグを覆う前記導電膜上に第1方向に延長するキャッピング(capping)パターンを形成する段階と、

前記キャッピングパターンの外部で延長する部分の前記導電膜を除去して前記第1コンタクトプラグと一緒に形成されて前記第1コンタクトプラグを覆う第1導電ラインを形成する段階と、

前記第1方向に対して傾斜した第2方向に沿って延長するフォトレジストパターンを形成する段階と、を含む半導体装置の配線構造物の製造方法。 10

【請求項22】

前記第1方向及び前記第2方向は、互いに直交することを特徴とする請求項21に記載の半導体装置の配線構造物の製造方法。

【請求項23】

前記フォトレジストパターンは、前記キャッピングパターン上に直接配置されることを特徴とする請求項21に記載の半導体装置の配線構造物の製造方法。

【請求項24】

前記第1コンタクトプラグ及び前記第1絶縁膜の上部境界と前記第1導電ラインの下部境界は、同じ水平面に配置されることを特徴とする請求項21に記載の半導体装置の配線構造物の製造方法。 20

【請求項25】

前記第1導電ラインの少なくとも側部をシリサイド化する段階をさらに含むことを特徴とする請求項21に記載の半導体装置の配線構造物の製造方法。

【請求項26】

前記第1コンタクトプラグ及び前記第1導電ラインを同時にシリサイド化する段階をさらに含むことを特徴とする請求項21に記載の半導体装置の配線構造物の製造方法。

【請求項27】

前記第1コンタクトホールは前記基板のセル領域に配置されて、前記基板の周辺回路領域の前記第1絶縁膜に第2コンタクトホールを形成する段階と、

前記第1導電物質を使って、前記第2コンタクトホールに第2コンタクトプラグを形成すると同時に前記第2コンタクトプラグと一緒に形成されて前記第2コンタクトプラグを覆う前記導電膜を形成する段階と、をさらに含むことを特徴とする請求項21に記載の半導体装置の配線構造物の製造方法。 30

【請求項28】

前記基板内に前記第1導電ラインと平行するように配列される少なくとも一つのトレンチを形成する段階と、

前記第1コンタクトプラグに隣接するように配置される前記少なくとも一つのトレンチにゲート電極を形成する段階と、をさらに含むことを特徴とする請求項21に記載の半導体装置の配線構造物の製造方法。

【請求項29】

前記第1絶縁膜を通じて前記第1コンタクトプラグに対して前記ゲート電極の対向の側面に配置される少なくとも一つの第3コンタクトプラグを形成する段階をさらに含み、

前記少なくとも一つの第3コンタクトプラグは前記第1導電ラインより高く延長することを特徴とする請求項28に記載の半導体装置の配線構造物の製造方法。

【請求項30】

前記少なくとも一つの第3コンタクトプラグ上に直接キャパシタを形成する段階をさらに含むことを特徴とする請求項29に記載の半導体装置の配線構造物の製造方法。

【請求項31】

基板と、

前記基板上に配置される第1絶縁膜と、 50

前記第1絶縁膜を貫通して延長する第1導電物質を含む第1コンタクトプラグと、前記第1コンタクトプラグと一体で形成されて前記第1コンタクトプラグを覆う第1導電物質を含み、第1方向に延長する第1導電ラインと、

前記第1コンタクトプラグを覆う前記第1導電ライン上に配置されるキャッピングパターンと、を含む半導体装置の配線構造物。

【請求項32】

前記第1絶縁膜及び前記第1コンタクトプラグはそれぞれ同じ平面に配置される上部表面を含むことを特徴とする請求項31に記載の半導体装置の配線構造物。

【請求項33】

前記第1コンタクトプラグ及び前記第1絶縁膜の上部境界と前記第1導電ラインの下部境界は、水平する平面に配置されることを特徴とする請求項31に記載の半導体装置の配線構造物。

【請求項34】

前記第1絶縁膜及び前記第1コンタクトプラグは同じ厚さを有することを特徴とする請求項31に記載の半導体装置の配線構造物。

【請求項35】

前記第1導電ラインは前記第1絶縁膜上に直接配置されることを特徴とする請求項31に記載の半導体装置の配線構造物。

【請求項36】

前記第1コンタクトプラグ及び前記第1導電ラインはシリサイドを除けば、同じ物質を含むことを特徴とする請求項31に記載の半導体装置の配線構造物。

【請求項37】

少なくとも前記第1導電ラインの少なくとも側部はシリサイドを含むことを特徴とする請求項31に記載の半導体装置の配線構造物。

【請求項38】

前記第1コンタクトプラグ及び前記第1導電ラインは全部シリサイドを含むことを特徴とする請求項31に記載の半導体装置の配線構造物。

【請求項39】

前記第1コンタクトプラグ及び前記第1導電ラインを含む第1ソース／ドレーン電極をさらに含むことを特徴とする請求項31に記載の半導体装置の配線構造物。

【請求項40】

前記第1ソース／ドレーン電極の少なくとも一つの側面上に配置される少なくとも一つの垂直スペーサをさらに含むことを特徴とする請求項39に記載の半導体装置の配線構造物。

【請求項41】

前記第1コンタクトプラグは、ポリシリコンパターンを含み、前記第1導電ラインは金属シリサイドを含むことを特徴とする請求項31に記載の半導体装置の配線構造物。

【請求項42】

前記第1導電ラインに平行して、前記第1コンタクトプラグに隣接するゲート電極をさらに含むことを特徴とする請求項31に記載の半導体装置の配線構造物。

【請求項43】

前記第1絶縁膜を通じて延長して、前記第1コンタクトプラグに対して前記ゲート電極の対向の側面上に配置され、前記第1導電ラインより高く延長する少なくとも一つの第1コンタクトプラグと、

前記少なくとも一つの第3コンタクトプラグ上に直接配置されるキャパシタと、をさらに含むことを特徴とする請求項42に記載の半導体装置の配線構造物。

【請求項44】

前記ゲート電極は前記基板内に配置されることを特徴とする請求項42に記載の半導体装置の配線構造物。

【請求項45】

10

20

30

40

50

前記ゲート電極は前記第1絶縁膜内に配置されることを特徴とする請求項42に記載の半導体装置の配線構造物。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は概して半導体製造方法及びリソグラフィ(lithography)方法に関する。より詳細に、本発明は半導体装置の配線構造物及び半導体装置の配線構造物の製造方法に関する。

【背景技術】

【0002】

近来、半導体装置が高度に集積化されるということによって、半導体装置の配線の幅と配線の間の間隔も減少している。このような配線は狭い幅と間隔を有しながらも低い抵抗を有することが要求される。しかし、配線の幅が減少すればその抵抗は増加することになる。従って、半導体装置には低い抵抗を有する配線、減少された配線幅、隣接する配線の間の減少された幅などが要求される。

【0003】

半導体装置の配線が導電性ラインに連結されるコンタクトプラグ(contact plug)を含む場合、前記配線が全体的に低い抵抗を有するようにするために前記コンタクトプラグと前記導電性ライン間の接触抵抗が減少しなければならない。また、前記配線の幅が減少した程增加する抵抗を補償するために、前記配線の高さはより一層増加して前記配線の抵抗を減少させなければならない。一方、前記配線を低抵抗の導電物質を使って形成することによって前記配線の抵抗をより一層減少させることができる。

【0004】

しかし、前記配線の高さが増加する程前記コンタクトプラグと前記導電性ラインの間のアライメント(alignment)が難しくて、これに伴い、前記コンタクトプラグと前記導電性ラインの間の接触面積が減少する問題が発生する。また、低い抵抗を有する金属または金属シリサイドの大部分は写真エッチング(photo lithography)工程でパターニングすることが容易ではないため、実質的に金属や金属シリサイドを低い抵抗を有する配線の形成に適用することは難しいという問題がある。

【先行技術文献】

30

【特許文献】

【0005】

【特許文献1】特開2008-078381号公報

【特許文献2】特開平06-318680号公報

【特許文献3】特開2001-257525号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明の一目的は、低い抵抗を確保しながら低い高さを有する配線構造物を提供することである。

【0007】

40

本発明の他の目的は、前記配線構造物の製造方法を提供することである。

【0008】

本発明のまた他の目的は、前記配線構造物を含む半導体装置を提供することである。

【0009】

本発明のさらに他の目的は、前記配線構造物を具備する半導体装置の製造方法を提供することである。

【課題を解決するための手段】

【0010】

上述した目的を達成するために、本発明の実施例に係る半導体装置の配線構造物の製造

50

方法において、セル領域及び周辺回路領域を有する基板を備え、前記基板上に第1絶縁膜を形成する。前記第1絶縁膜を貫通して延長する第1導電物質を含む第1コンタクトプラグを前記セル領域に形成する。前記第1コンタクトプラグをカバーして前記第1コンタクトプラグと一体で形成して、第1導電物質を含む第1導電ラインを前記第1コンタクトプラグと実質的に同時に形成する。前記第1絶縁膜を貫通して延長して、第1導電物質を含む第2コンタクトプラグを前記第1コンタクトプラグと実質的に同時に前記周辺回路領域に形成する。前記第2コンタクトプラグをカバーして前記第2コンタクトプラグと一体で形成して、第1導電物質を含む第2導電ラインを前記第2コンタクトプラグと実質的に同時に形成する。

## 【0011】

10

上述の目的を達成するために、本発明の実施例に係る半導体装置の配線構造物は、セル領域と周辺回路領域を有する基板と、前記基板上に配置される第1絶縁膜と、前記セル領域に配置されて前記第1絶縁膜を貫通して延長する第1導電物質を含む第1コンタクトプラグと、前記セル領域に配置されて第1方向に沿って延長して、前記第1コンタクトプラグと一体で形成して前記第1コンタクトプラグを覆う第1導電物質を含む第1導電ラインと、前記周辺回路領域に配置して前記第1絶縁膜を貫通して延長する第1導電物質を含む第2コンタクトプラグと、前記周辺回路領域に配置されて第2方向に沿って延長し、前記第2コンタクトプラグと一体で形成されて前記第2コンタクトプラグを覆う第1導電物質を含む第2導電ラインとを具備する。

## 【0012】

20

本発明の他の実施例に係る半導体装置の配線構造物の製造方法において、基板上に第1絶縁膜を形成して、前記基板のアクティブ領域の前記第1絶縁膜に第1コンタクトホールを形成する。第1導電物質を使って前記第1コンタクトホールに第1コンタクトプラグを形成すると同時に前記第1コンタクトプラグと一体で形成されて前記第1コンタクトプラグを覆う導電膜を形成する。前記第1コンタクトプラグを覆う前記導電膜上に第1方向で延長するキャッピング(capping)パターンを形成する。前記キャッピングパターンの外部で延長する部分の前記導電膜を除去して前記第1コンタクトプラグと一体で形成されて前記第1コンタクトプラグを覆う第1導電ラインを形成する。前記第1方向に対して傾斜した第2方向に沿って延長するフォトレジストパターンを形成する。

## 【0013】

30

本発明のまた他の実施例に係る半導体装置の配線構造物は、基板と、前記基板上に配置される第1絶縁膜と、前記第1絶縁膜を貫通して延長する第1導電物質を含む第1コンタクトプラグと、前記第1コンタクトプラグと一体で形成されて前記第1コンタクトプラグを覆う第1導電物質を含んで第1方向で延長する第1導電ラインと、前記第1コンタクトプラグを覆う前記第1導電ライン上に配置されるキャッピングパターンと、を含む。

## 【発明の効果】

## 【0014】

40

本発明に係る配線構造物はコンタクトプラグと導電性ライン間の界面の接触抵抗が減少する。また、前記配線構造物は低抵抗を有する金属シリサイドを含んでいて、前記配線構造物の全体抵抗が減少して、前記配線構造物の高さが減少する。また、前記配線構造物は簡単な工程で形成されることがあるため、前記配線構造物を形成するのに必要とされる工程費用及び工程不良が減少する。

## 【図面の簡単な説明】

## 【0015】

【図1】本発明の実施例に係る配線構造物を示す斜視図である。

【図2】本発明の実施例に係る配線構造物を示す断面図である。

【図3】本発明の他の実施例に係る配線構造物を示す断面図である。

【図4】本発明のまた他の実施例に係る配線構造物を示す断面図である。

【図5】図2に示した配線構造物の形成方法を説明するための断面図である。

【図6】図2に示した配線構造物の形成方法を説明するための断面図である。

50

【図 7】図 2 に示した配線構造物の形成方法を説明するための断面図である。

【図 8】図 2 に示した配線構造物の形成方法を説明するための断面図である。

【図 9】図 2 に示した配線構造物の形成方法を説明するための断面図である。

【図 10】図 2 に示した配線構造物の形成方法を説明するための断面図である。

【図 11】図 2 に示した配線構造物の形成方法を説明するための斜視図である。

【図 12】図 2 に示した配線構造物の形成方法を説明するための断面図である。

【図 13】図 2 に示した配線構造物の形成方法を説明するための断面図である。

【図 14】本発明の実施例に係る半導体装置のセル領域の回路図である。

【図 15】図 1 に示した配線構造物を含む半導体装置の平面図である。

【図 16】図 15 に示した半導体装置の断面図である。

10

【図 17】本発明の実施例に係る半導体装置の製造方法を説明するための断面図である。

【図 18】本発明の実施例に係る半導体装置の製造方法を説明するための断面図である。

【図 19】本発明の実施例に係る半導体装置の製造方法を説明するための断面図である。

【図 20】本発明の実施例に係る半導体装置の製造方法を説明するための断面図である。

【図 21】本発明の実施例に係る半導体装置の製造方法を説明するための断面図である。

【図 22】本発明の他の実施例に係る半導体装置の製造方法を説明するための断面図である。

【図 23】本発明の実施例に係る半導体装置の製造方法を説明するための断面図である。

【図 24】本発明の他の実施例に係る半導体装置の製造方法を説明するための断面図である。

20

【図 25】本発明の実施例に係る半導体装置の製造方法を説明するための断面図である。

【図 26】本発明のまた他の実施例に係る半導体装置の断面図である。

【図 27】本発明のまた他の実施例に係る半導体装置の断面図である。

【図 28】本発明のまた他の実施例に係る半導体装置の断面図である。

【図 29】図 28 に示した半導体装置の製造方法を説明するための断面図である。

【図 30】図 28 に示した半導体装置の製造方法を説明するための断面図である。

【図 31】図 28 に示した半導体装置の製造方法を説明するための断面図である。

【図 32】本発明のまた他の実施例に係る半導体装置の断面図である。

【図 33】図 32 に示した半導体装置の製造方法を説明するための断面図である。

【図 34】図 32 に示した半導体装置の製造方法を説明するための断面図である。

【図 35】図 32 に示した半導体装置の製造方法を説明するための断面図である。

【図 36】図 32 に示した半導体装置の製造方法を説明するための断面図である。

【図 37】図 32 に示した半導体装置の製造方法を説明するための断面図である。

【図 38】図 32 に示した半導体装置の製造方法を説明するための断面図である。

【図 39】本発明のまた他の実施例に係る半導体装置の断面図である。

30

【図 40】図 39 に示した半導体装置の製造方法を説明するための断面図である。

【図 41】図 39 に示した半導体装置の製造方法を説明するための断面図である。

【図 42】図 39 に示した半導体装置の製造方法を説明するための断面図である。

【図 43】図 39 に示した半導体装置の製造方法を説明するための断面図である。

【図 44】本発明のまた他の実施例に係る配線構造物を示す斜視図である。

【図 45】図 44 に示した配線構造物を示す断面図である。

40

【図 46】図 45 に示した配線構造物の形成方法を説明するための断面図である。

【図 47】図 45 に示した配線構造物の形成方法を説明するための断面図である。

【図 48】図 45 に示した配線構造物の形成方法を説明するための断面図である。

【図 49】図 45 に示した配線構造物の形成方法を説明するための断面図である。

【図 50】図 45 に示した配線構造物の形成方法を説明するための断面図である。

【図 51】図 44 及び図 45 に示した配線構造物を含む半導体装置の断面図である。

【図 52】本発明のまた他の実施例に係る半導体装置を示す断面図である。

【図 53】本発明のまた他の実施例に係る半導体装置の断面図である。

【図 54】図 53 に示した半導体装置の製造方法を説明するための断面図である。

50

【図55】図53に示した半導体装置の製造方法を説明するための断面図である。

【図56】図53に示した半導体装置の製造方法を説明するための断面図である。

【図57】図53に示した半導体装置の製造方法を説明するための断面図である。

【図58】本発明の実施例に係る半導体装置を含むメモリシステムの概略的なブロック図である。

【図59】本発明に実施例に係る半導体チップが含まれたグラフィックシステムの概略的なブロック図である。

【図60】図59に示したグラフィックチップ及び半導体チップの概略的なブロック図である。

【発明を実施するための最良の形態】

10

【0016】

以下、添付した図面を参照して本発明の例示的な実施形態に係る半導体装置のパターン構造物と半導体装置のパターン構造物の形成方法を詳細に説明する。本明細書の各図面において、構成要素及び／または構造物のサイズは本発明の明確性を期するために実際より拡大して示した。

【0017】

本明細書において、第1、第2等の用語が多様な構成要素を説明するのに使われるが、構成要素はこのような用語によって限定されるのではなく、用語は一つの構成要素を他の構成要素から区別する目的で使われる。

【0018】

本明細書で使用する用語は単に特定の実施形態を説明するために使用するもので、本発明を限定しようとする意図ではない。単数の表現は文脈上明白に異なるように意味しない限り、複数の表現を含む。本明細書で、「含む」または「有する」等の用語は明細書上に記載された特徴、数字、段階、動作、構成要素、部品または、これを組み合わせたものが存在するということを指定しようとするものであって、一つまたは、それ以上の他の特徴や数字、段階、動作、構成要素、部品または、これを組み合わせたものの存在または、付加の可能性を、予め排除しない。

【0019】

本明細書において、各階（膜）、領域、電極、パターンまたは、構造物が対象物、基板、各階（膜）、領域、電極または、パターンの「上に」、「上部に」または「下部」に形成されると言及される場合には各階（膜）、領域、電極、パターンまたは、構造物が直接、基板、各階（膜）、領域、または、パターン上に形成されたり、下に位置することを意味したり、他の層（膜）、他の領域、他の電極、他のパターンまたは、他の構造物が対象物や基板上に追加的に形成することを意味する。

30

【0020】

本明細書に開示されている本発明の実施形態に対して、特定の構造的ないし機能的説明は単に本発明の実施形態を説明するための目的で例示されたもので、本発明の実施形態は多様な形態で実施可能で、本明細書に説明された実施形態に限定されるものではない。即ち、本発明は多様な変更を加えることができ、種々な形態を有することができるが、特定の実施形態を図面に例示し、本明細書に詳細に説明したものである。これは本発明を特定の開示形態に限定しようとするものではなく、本発明の思想及び技術範囲に含まれるすべての変更、均等物ないし代替物を含むと理解されるべきである。

40

【0021】

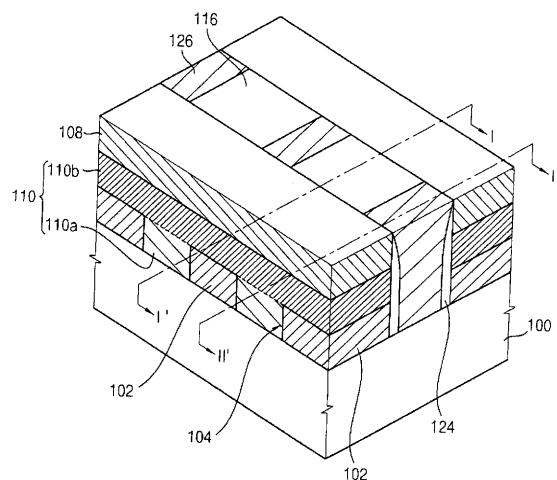

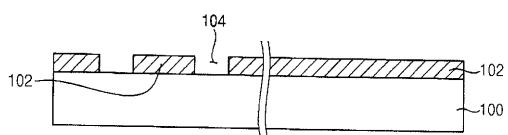

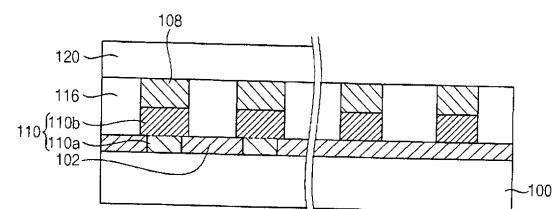

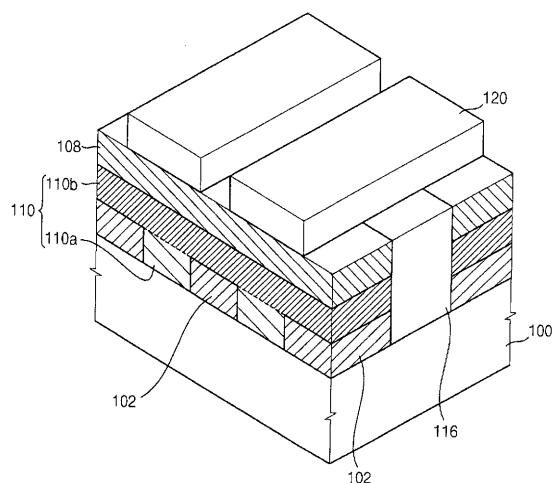

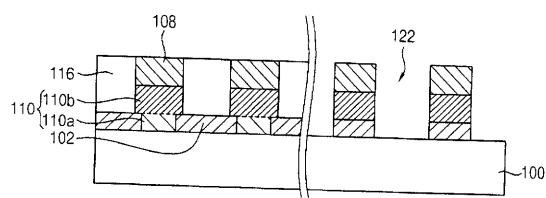

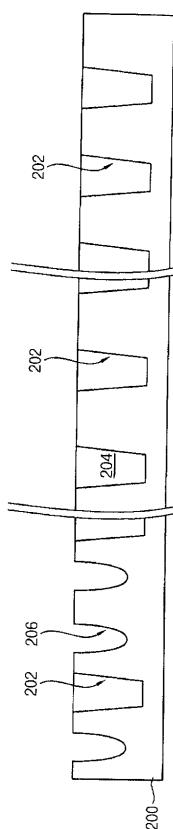

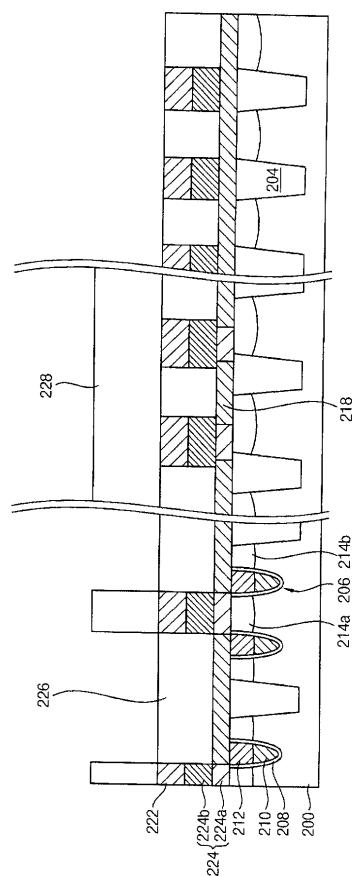

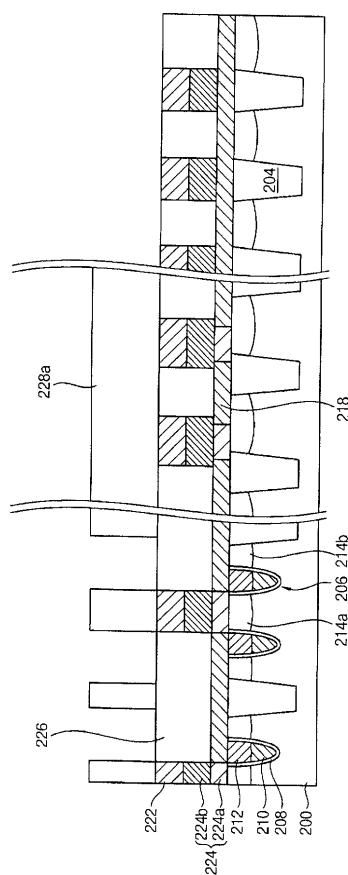

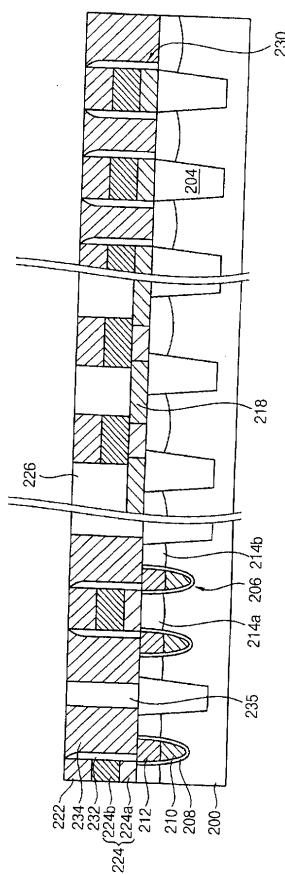

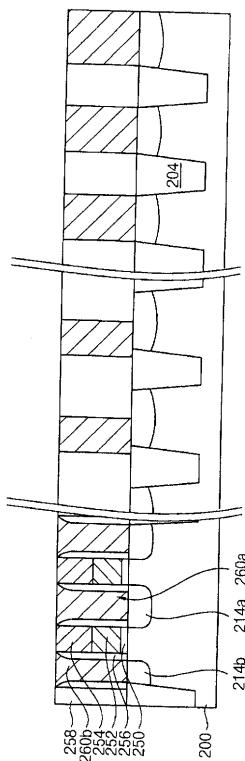

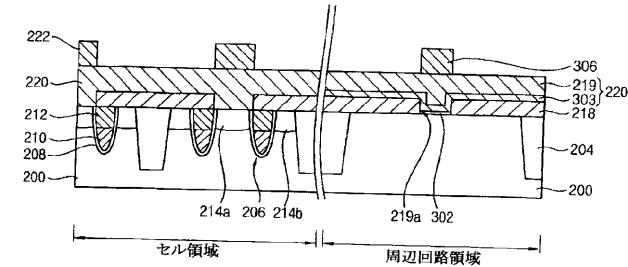

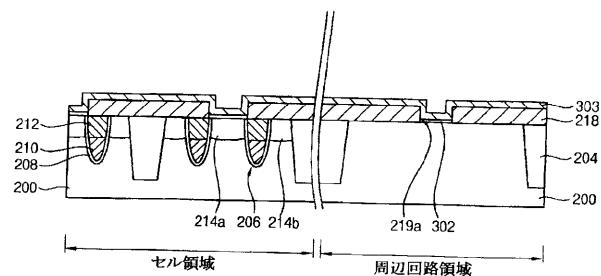

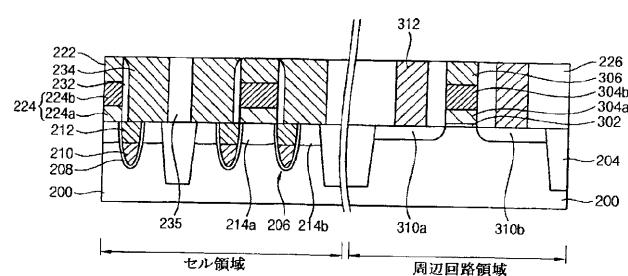

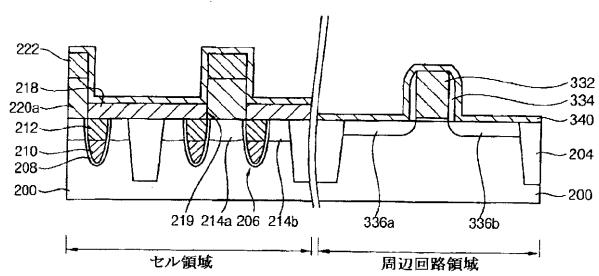

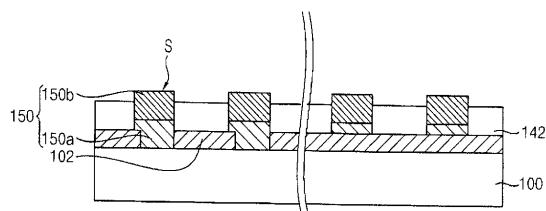

図1は、本発明の実施例に係る配線構造物を示す斜視図である。図2は本発明の実施例に係る配線構造物を示す断面図である。図2で左側部の断面図は図1のI-I'を切断した時の断面であり、右側部の断面図は図1のII-II'を切断した時の断図である。

【0022】

図1及び図2を参照すれば、基板100上に絶縁膜102が備えられる。前記絶縁膜102には第1コンタクトホール104が設けられる。図示はしなかったが、前記第1コンタクトホール104は、オーバーエッチ（over etch）により前記基板100表

50

面の一部が除去された形状を有することができる。

【0023】

前記絶縁膜102は層間絶縁膜116をエッチングする時、エッチング阻止膜として使われることができる。従って、前記絶縁膜102は層間絶縁膜116に対してエッチング選択比が高い物質からなることができる。例えば、前記絶縁膜102はシリコン窒化物からなることができる。前記絶縁膜102の上部面と第1コンタクトプラグの上部面は同じ高さに位置することができる。本発明の実施例において、前記絶縁膜102は、約100～300程度の薄い厚さを有することができる。

【0024】

前記第1コンタクトホール104内部には第1コンタクトプラグ110aが備えられる。前記第1コンタクトプラグ110aは別途の下部層間絶縁膜内に形成されるのではなく、エッチング阻止膜で使われる絶縁膜102内に備えられることができる。従って、前記第1コンタクトプラグ110aは非常に低い高さを有することができる。

【0025】

前記絶縁膜102の上部面には前記第1コンタクトプラグ110aと一体で備えられる導電性ライン110bが備えられる。前記第1コンタクトプラグ110a及び導電性ライン110bは1回の蒸着工程を通じて同時に形成されることができる。以下、前記第1コンタクトプラグ110a及び導電性ライン110bは、第1配線110とする。前記第1配線110の少なくとも一部分は低い抵抗を有する金属シリサイドSからなる。

【0026】

本発明の実施例において、図1及び図2に示したように、導電性ライン110bは金属シリサイドSからなって、前記第1コンタクトプラグ110aはポリシリコンからなることができる。しかし、これとは異なって、前記導電性ライン110bの一部分のみが金属シリサイドからなるか、または、前記導電性ライン110b及び第1コンタクトプラグ110aの全部が金属シリサイドからなることができる。

【0027】

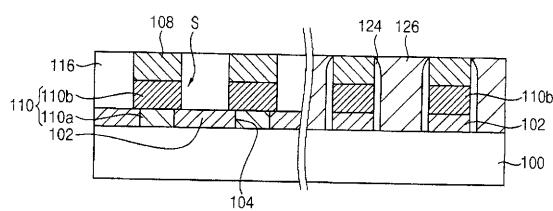

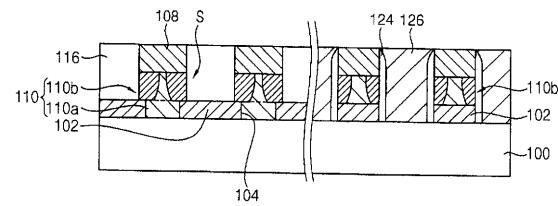

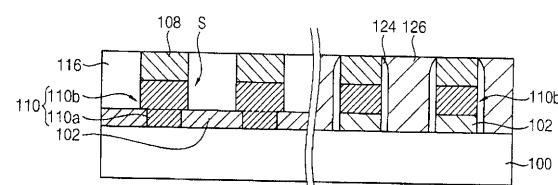

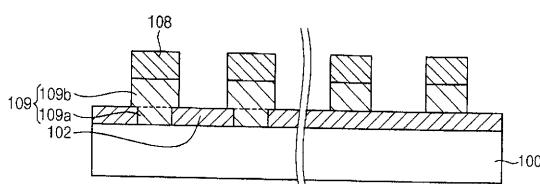

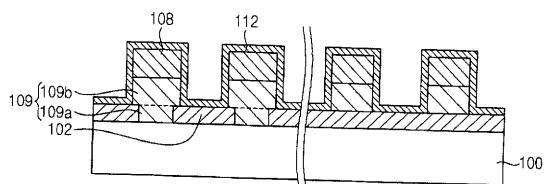

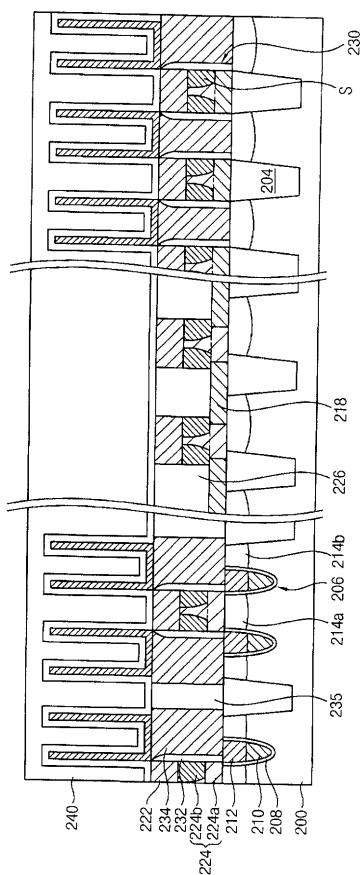

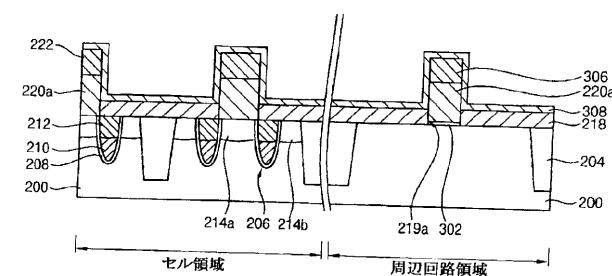

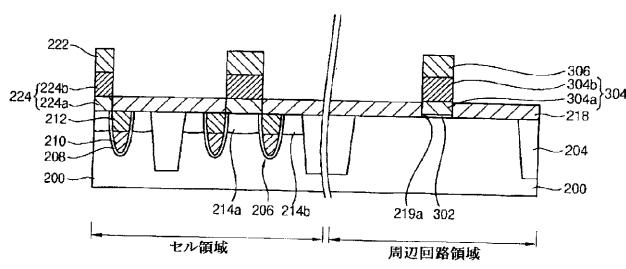

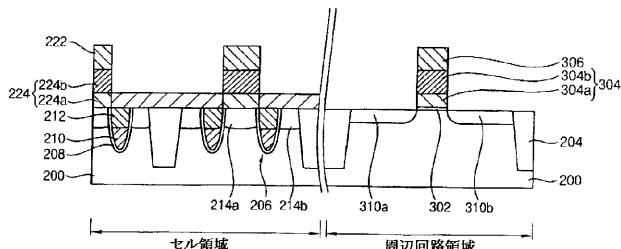

図3は本発明の他の実施例に係る金属シリサイドを含む配線構造物を示す断面図である。図4は本発明のまた他の実施例に係る金属シリサイドを含む配線構造物を示す断面図である。

【0028】

図3に示したように、前記導電性ライン110bの側壁表面部位は金属シリサイドSからなって、残り部位はポリシリコンからなることができる。これとは異なって、図4に示したように、前記導電性ライン110b及び第1コンタクトプラグ110a全体が金属シリサイドSからなることができる。

【0029】

上述のように、前記第1配線110が要求される抵抗を有しているように前記金属シリサイドSの厚さが変わることができる。また、前記金属シリサイドSが形成される部位が変わることができる。

【0030】

本発明の実施例において、前記金属シリサイドSはコバルトシリサイド(CoSi<sub>x</sub>)、チタンシリサイド(TiSi<sub>x</sub>)、タンタルシリサイド(TaSi<sub>x</sub>)、ニッケルシリサイド(NiSi<sub>x</sub>)、白金シリサイド(PtSi<sub>x</sub>)等からなることができる。これらは単独で形成されることができ、また2種類以上の金属シリサイドが積層されることもできる。前記第1配線110に含まれる前記金属シリサイドSはチタン窒化物と同じ金属窒化物であるが、タングステン、タングステンシリサイドに比べて低い抵抗を有することができる。本発明の一実施例において、前記金属シリサイドSは、低い抵抗を有しながらも半導体製造工程で使われるのに適したコバルトシリサイドからなることができる。前記第1配線110がコバルトシリサイドを含む場合、前記第1配線110が金属窒化物を含むことと比較する時、前記第1コンタクトプラグ110a及び導電性ライン110bの高さが減少しても十分に低い抵抗を有することができる。

10

20

30

40

50

## 【0031】

前記導電性ライン110bの上部面にはハードマスクパターン108が備えられる。前記ハードマスクパターン108は、層間絶縁膜116をエッティングするためのマスクにも提供されるため、前記ハードマスクパターン108は、シリコン酸化物に対して高いエッティング選択比を有する物質からなることができる。例えば、前記ハードマスクパターン108は、シリコン窒化物からなることができる。

## 【0032】

前記第1配線110間のギャップを埋め立てる層間絶縁膜116が備えられる。前記層間絶縁膜116の上部面は前記ハードマスクパターン108の上部面と同じ平面上に位置することができる。これとは異なって、前記層間絶縁膜116の上部面は前記ハードマスクパターン108の上部面より高く或いは低く位置することもできる。10

## 【0033】

前記層間絶縁膜116及び絶縁膜102を貫通して基板100と接触する第2コントラクトプラグ126が備えられる。前記第2コントラクトプラグ126は、前記第1配線110間に配置される。前記第2コントラクトプラグ126の側壁には内壁スペーサ124が位置する。従って、前記内壁スペーサ124により前記第1配線110及び第2コントラクトプラグ126が互いに電気的に絶縁されることができる。

## 【0034】

前記第2コントラクトプラグ126は前記基板100と接触する。従って、前記第2コントラクトプラグ126と前記基板100の接触特性を向上させるために、前記第2コントラクトプラグ126はポリシリコンからなることができる。この場合、前記内壁スペーサ124はシリコン酸化物或いはシリコン窒化物からなることができる。20

## 【0035】

上述のように、第1コントラクトプラグ110a及び導電性ライン110bは、1回の蒸着工程によって一体で形成されるために、前記第1コントラクトプラグ110aと導電性ライン110bとの間の界面接触抵抗が減少することができる。また、第1配線110は金属窒化物及びタンゲステンに比べて低い抵抗を有する金属シリサイドSを含むため、前記第1配線110の高さが低くなっても十分に低い抵抗を確保することができる。さらに、前記第1配線110上に備えられるハードマスクパターン108が、第2コントラクトプラグ126を形成するためのエッティングマスクとして使われることがあるため、前記第2コントラクトプラグ126を容易に形成することができる。30

## 【0036】

図5～図10、図12、及び図13は、図2に示した配線構造物の形成方法を説明するための断面図である。図11は図2に示した配線構造物の形成方法を説明するための斜視図である。

## 【0037】

図5～図13において、左側部の断面図は図1のI-I'線に沿って切断した図であり、右側部の断面図は図1のII-II'線に沿って切断した図である。

## 【0038】

図5を参照すれば、基板100上に絶縁膜102を形成する。前記絶縁膜102は、後続工程で層間絶縁膜をエッティングする時、エッティング阻止膜として使われる。従って、前記絶縁膜102は前記層間絶縁膜に対してエッティング選択比が高いシリコン窒化物からなることができる。また、前記絶縁膜102は、約100～約300程度の薄い厚さで形成することができる。40

## 【0039】

前記絶縁膜102の一部分を写真エッティング工程を通じて除去して基板100表面を露出させる第1コントラクトホール104を形成する。

## 【0040】

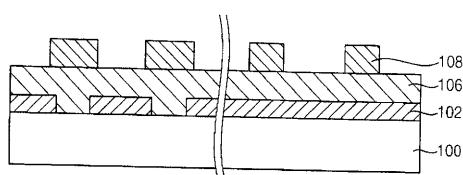

図6を参照すれば、前記第1コントラクトホール104を満たしながら前記絶縁膜102上にポリシリコン膜106を形成する。50

## 【0041】

前記ポリシリコン膜106上にハードマスク膜(図示せず)を形成する。前記ハードマスク膜はシリコン窒化物を蒸着させて形成することができる。前記ハードマスク膜を写真エッチング工程を通じてパターニングすることによって、第1方向で延長するライン形状を有するハードマスクパターン108を形成する。前記ハードマスクパターン108は前記第1コンタクトホール104上部と対向するように配置される。

## 【0042】

図7を参照すれば、前記ハードマスクパターン108をエッチングマスクで使って前記ポリシリコン膜106をパターニングすることによって、予備導電パターン109を形成する。

10

## 【0043】

前記予備導電パターン109は前記第1コンタクトホール104内部に満たされた予備コンタクトプラグ109a及び前記予備コンタクトプラグ109a上部面と一体で形成されながらライン形状を有する予備ラインパターン109bを含む。例えば、前記予備ラインパターン109bは前記第1コンタクトホール104に満たされた予備コンタクトプラグ109aの上部であるならば全体を覆う形状を有するように形成されることがある。この場合、前記予備ラインパターン109bは前記予備コンタクトプラグ109aの上部面と互いにくい違う部分がなくて、前記予備ラインパターン109bと前記予備コンタクトプラグ109aの間の接触面積が増加することができる。

20

## 【0044】

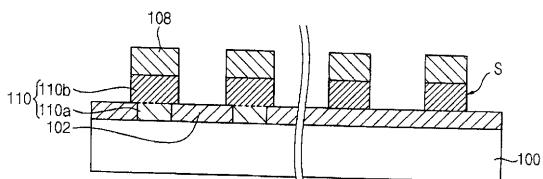

図8を参照すれば、前記予備導電パターン109、ハードマスクパターン108及び絶縁膜102上部面のプロファイルについて金属膜112を形成する。前記金属膜112は、シリサイデーション工程を通じてシリサイド化した時に低い抵抗を有することができる耐熱性金属を含むことができる。前記金属膜112で使用できる物質の例としてはコバルト、チタン、タンタル、ニッケル、白金などを挙げることができる。これらは単独またはこれらの合金物質を使うことができる。本発明の実施例において、前記金属膜112でシリサイド化した時に低い抵抗を有しながら熱的安全性が優秀なコバルト膜を形成することができる。一方、前記金属膜112でタンゲステンを使うこともできるが、タンゲステンシリサイドの場合、相対的に抵抗が高いから、前記金属膜112でタンゲステンを使う場合には十分に低い抵抗を有する配線構造物を実現することが容易でないこともある。

30

## 【0045】

本発明の他の実施例において、前記金属膜112上にキャッピング膜(図示せず)を形成する工程をさらに遂行できる。ここで、前記キャッピング膜はチタン窒化物またはタンタル窒化物を含むことができる。

## 【0046】

図9を参照すれば、前記金属膜112を熱処理して前記金属膜112と前記金属膜112と接触しているポリシリコンを反応させて、金属シリサイドSを形成する。すなわち、前記金属膜112及び予備導電パターン109の側壁が互いに反応して金属シリサイドSが形成される。次いで、反応しなかった金属膜112を除去する。

40

## 【0047】

上述したことによって、前記金属シリサイドSを含む第1配線110が形成される。前記第1配線110は第1コンタクトホール104内部に満たされた第1コンタクトプラグ110aと、前記第1コンタクトプラグ110aと一体で形成された導電性ライン110bを含む。

## 【0048】

本発明の実施例において、前記熱処理工程条件を調節して前記第1配線110に含まれる金属シリサイドSの量を調節することができる。例えば、図9及び図2に示したように、前記導電性ライン110bは、全体が金属シリサイドSになるようにして、前記第1コンタクトプラグ110aにはポリシリコンが残っているようにすることができる。これとは異なって、図3に示したように、前記導電性ライン110bの側壁表面部位のみに金属

50

シリサイドSが形成されるようにして、残り部位の導電性ライン110b及び第1コンタクトプラグ110aにはポリシリコンが残っているようにすることができる。また、図4に示したように、前記導電性ライン110b及び第1コンタクトプラグ110a全体が金属シリサイドSになるようにすることもできる。

【0049】

上述のように、前記第1配線110が要求される抵抗値を有しているように第1配線110内に前記金属シリサイドSが形成される量を調節することができる。

【0050】

本発明の実施例において、前記金属シリサイドSを形成するための熱処理工程は1回のみ遂行する事もでき、2回以上にわたって遂行することもできる。しかし、前記金属シリサイドSが低い抵抗を有するようにするためには前記金属シリサイドSを形成するための熱処理工程を2回遂行することが有利である。2回の熱処理工程を通じてコバルトシリサイドを形成する場合、先ず約250～約550程度の温度で前記金属膜、例えば、コバルト膜が形成された構造物を1次熱処理する。この後、反応せずに残っている金属膜をストリッピング(stripping)工程を通じて除去する。次に、約600～約900範囲の温度で2次熱処理する。これと共に、2回の熱処理工程を遂行して、低い抵抗を有するコバルトシリサイドを形成することができる。

10

【0051】

上述のように、本発明の実施例によれば、第1配線110に含まれる第1コンタクトプラグ110aと導電性ライン110bは1回の蒸着工程を通じて一体で形成されることができる。これに伴い、前記第1コンタクトプラグ110a及び導電性ライン110bが互いにくい違うミスアラインメント(mis-alignment)不良発生が減少する。また、前記第1コンタクトプラグ110aと導電性ライン110b間の接触面積が増加しながら接触抵抗は減少する。これによって、前記第1配線110の全体的な抵抗も減少する。

20

【0052】

本発明の実施例において、前記第1配線110の少なくとも一部分は低抵抗を有する金属シリサイドSを含むため前記第1配線110の抵抗が減少する。また、前記金属シリサイドSは前記ハードマスクパターン108をエッチングマスクとして予備導電性ライン109bを形成した後、前記予備導電性ライン109b側壁を反応させることによって形成される。これと共に、ダマシン(damascene)工程を利用せずに前記金属シリサイドを含むライン形状のパターンを形成することができる。特に、通常の写真エッチング工程を通じてほぼエッチングされない金属シリサイド(例えば、コバルトシリサイド)の場合でもダマシン工程を利用せずにライン形状のパターンを形成することができる。その結果、前記第1配線110を形成するための工程が簡単になり、工程費用が減少する。

30

【0053】

本発明の実施例によれば、前記第1配線110の上部面にはハードマスクパターン108が備えられる。前記ハードマスクパターン108は後続のエッチング工程時にエッチングマスクとして使うことができる。

40

【0054】

図10及び図11を参照すれば、前記第1配線110の間を満たしながら前記ハードマスクパターン108を覆う絶縁膜を形成する。前記絶縁膜は、シリコン酸化物と同じ酸化物を蒸着させて形成することができる。前記ハードマスクパターン108の上部面が露出するように前記絶縁膜を研磨して、前記第1配線110b間を埋め立てる層間絶縁膜116を形成する。

【0055】

前記層間絶縁膜116上にフォトレジストパターン120を形成する。図11に示したように、前記フォトレジストパターン120は前記第1方向と垂直な第2方向で延長するライン形状またはバー形状を有することができる。この場合、前記フォトレジストパターン120及び前記ハードマスクパターン108によってカバーされない前記層間絶縁膜1

50

16部位が選択的に露出する。

【0056】

図12を参照すれば、前記フォトレジストパターン120及びハードマスクパターン108により露出した部位の層間絶縁膜116をエッチングする。この時、底面に前記絶縁膜102が露出すれば前記層間絶縁膜116のエッチング工程を中断する。次いで、前記絶縁膜102を除去して前記シリコン基板100を露出させる。これに伴い、前記層間絶縁膜116に第2コンタクトホール122を形成する。

【0057】

本発明の実施例によれば、第1配線110上にハードマスクパターン108が形成されている。従って、前記フォトレジストパターン120をライン形状で形成すれば、図11に示したように、前記ハードマスクパターン108及びフォトレジストパターン120により孤立された部位の層間絶縁膜116が露出する。これに伴い、前記ライン形状のフォトレジストパターン120をエッチングマスクとして使ってエッチング工程を遂行することによって、前記第2コンタクトホール122を形成することができる。上述のように、前記ハードマスクパターン108によって自己整合(Self aligned)されて第2コンタクトホール122が形成されるため、前記第2コンタクトホール122のミスアラインメント不良が減少する。また、広い底部を有する第2コンタクトホール122を形成することができる。

10

【0058】

図13を参照すれば、前記第2コンタクトホール122の側壁に絶縁物質からなる内壁スペーサ124を形成する。本発明の実施例において、前記第2コンタクトホール122の側壁及び底面と前記ハードマスクパターン108及び層間絶縁膜116についてスペーサ用絶縁膜(図示せず)を形成する。次いで、前記第2コンタクトホール122の底面に基板が露出するように前記スペーサ用絶縁膜を異方性エッチング工程でエッチングすることによって、前記内壁スペーサ124を形成する。前記内壁スペーサ124はシリコン酸化物またはシリコン窒化物からなることができる。

20

【0059】

前記第2コンタクトホール122内部に導電物質を満たして、前記ハードマスクパターン108の上部面が露出するように研磨することによって、第2コンタクトプラグ126を形成する。前記第2コンタクトプラグ126は前記基板100と直接接触する。従って、前記第2コンタクトプラグ126に含まれる前記導電物質は前記基板100との接触特性を向上させるためにポリシリコンを含むことができる。これとは異なって、前記導電物質はバリア(barrier)金属膜及び/または金属膜を含むこともできる。

30

【0060】

上述の工程を遂行することによって、本発明による配線構造物を形成することができる。前記第1配線は第1コンタクトプラグと導電性ラインが一体からなるため、低い接触抵抗を有する。また、低抵抗を有する金属シリサイドが含まれるため、前記第1配線の高さが低くなても低い抵抗を有することができる。これと共に、前記第1配線は低い高さを有することができ、これによって、前記第1配線工程この後で進行される工程を容易に遂行できる。また、前記第1配線上に備えられるハードマスクパターンが第2コンタクトプラグを形成するためのエッチングマスクにも使うことがあるので、前記第2コンタクトプラグを形成する時にミスアラインメントの発生を減少させることができる。

40

【0061】

本発明の実施例に係る配線構造物はDRAM装置のような半導体装置のメモリセルに適する。

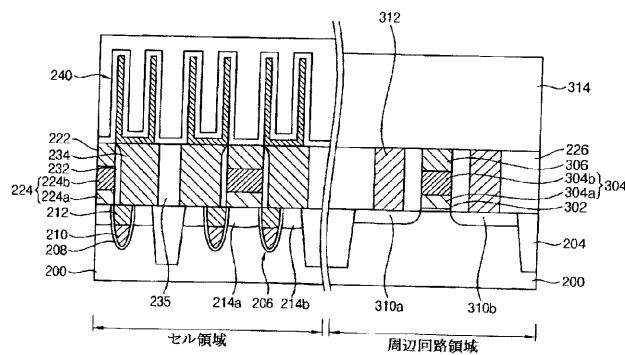

【0062】

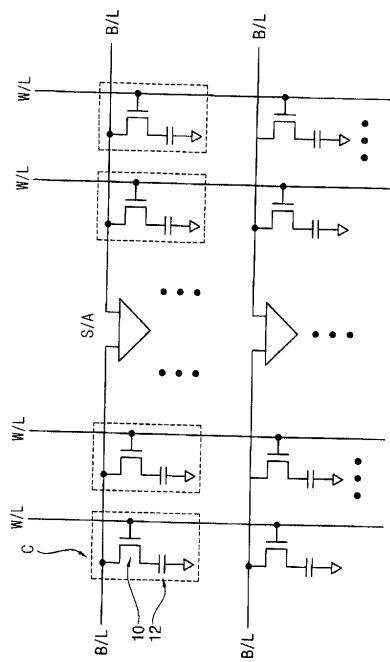

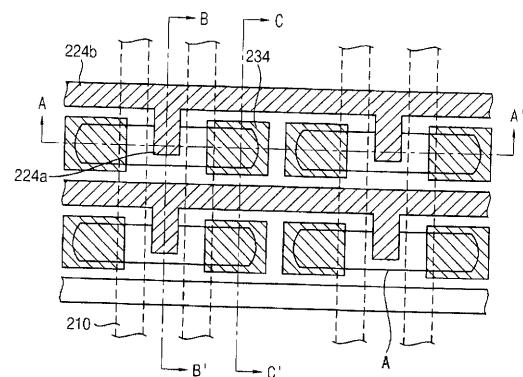

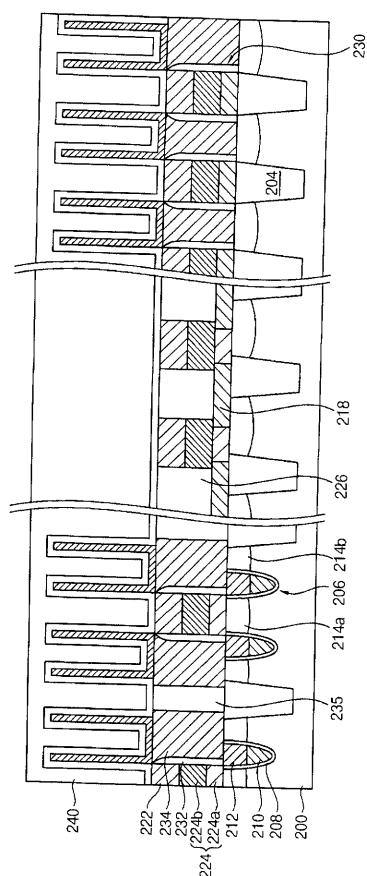

図14は半導体装置のメモリセルの部分の回路図であり、図15は図1に示した配線構造物を含む半導体装置の平面図である。図16は図15に示した半導体装置の断面図である。図14～図16において、半導体装置としてDRAM装置を例示的に図示する。図16の断面図は左側部から各々図15のA-A'線、B-B'線、及びC-C'線を切断した

50

図である。

【0063】

図14を参照すれば、DRAM装置のような半導体装置の単位セルCはワードラインW/Lによって調整される一つのNMOSトランジスタ10と前記NMOSトランジスタ10と連結されるキャパシタ12を含む。ここで、前記NMOSトランジスタ10の不純物領域の中の一つの端子はビットラインB/Lに連結され、前記NMOSトランジスタ10の不純物領域中残り一つの端子は前記キャパシタ12の下部電極と連結される。

【0064】

前記キャパシタ12の下部電極は電荷が保存されるストレージノードに該当する。前記キャパシタ12の上部電極は共通のセルプレートライン(図示せず)に連結され、前記プレートラインを通じてプレート電圧が印加される。また、ラッチ型ビットラインセンスアンプS/Aの両出力端子はビットラインB/L対に連結される。

10

【0065】

図14に示した半導体装置のメモリセルは、単結晶半導体基板に具現される。前記半導体装置のメモリセルでトランジスタ10の不純物領域とビットラインB/Lとキャパシタ12との間の電気的連結のために配線構造物が備えられなければならない。

【0066】

以下、図1に示した配線構造物を含む半導体装置に対して図15及び16を参照して詳細に説明する。

20

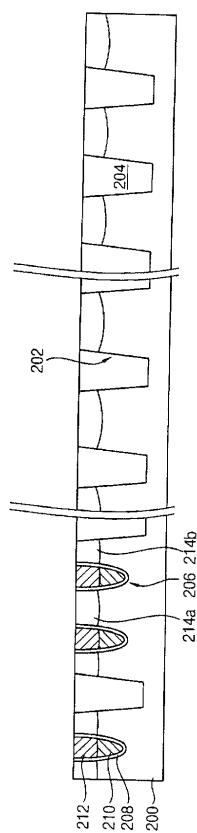

【0067】

図15及び図16を参照すれば、アクティブ領域A及び素子分離領域が区分される基板200が設けられる。前記基板200で素子分離領域は素子分離用トレンチが形成されていて、前記素子分離用トレンチ内部に素子分離膜204が満たされている。前記アクティブ領域Aは孤立された形状を有しながら規則的に配置される。

30

【0068】

前記アクティブ領域A及び素子分離領域には、第1方向に延長するライン形状を有するゲート電極用トレンチ206が生成されている。前記ゲート電極用トレンチ206は前記アクティブ領域Aを横切りながら延長する。一つの孤立されたアクティブ領域Aには2つのMOSトランジスタが備えられるため、前記一つの孤立されたアクティブ領域Aには2つのゲート電極用トレンチ206が互いに並んでいるように配置されることができる。

30

【0069】

前記アクティブ領域Aに位置する前記ゲート電極用トレンチ206の側壁にはゲート酸化膜208が備えられる。前記ゲート酸化膜208はシリコン酸化物または高誘電率を有する金属酸化物からなることができる。前記高誘電率を有する金属酸化物としてはアルミニウム酸化物(A<sub>2</sub>O<sub>3</sub>)、チタン酸化物(TiO<sub>2</sub>)、タンタル酸化物(Ta<sub>2</sub>O<sub>5</sub>)、ジルコニア酸化物(ZrO<sub>2</sub>)、ハフニウム酸化物(HfO<sub>2</sub>)等を挙げることができる。これらは単独または互いに混合して使うことができる。

40

【0070】

前記ゲート電極用トレンチ206の内部には導電膜パターン210及び第1ハードマスクパターン212を含むゲート構造物が埋め立てられている。前記ゲート構造物の上部面は前記基板200表面より高く突出せず、前記基板200の上部面と平坦であるかまたは前記基板200の上部面より低く位置する。前記導電膜パターン210は選択トランジスタのゲート電極として使われるのみならず、半導体装置のメモリセルのワードラインとしても使われる。

【0071】

前記導電膜パターン210はドーピングされたポリシリコンと同じシリコン、金属または、金属シリサイドからなることができる。これらは単独または互いに混合して使うことができる。前記導電膜パターン210に含まれる金属の例としてはタンゲステン、チタン窒化物、タンタル窒化物などを挙げることができる。前記第1ハードマスクパターン212はシリコン窒化物からなることができる。

50

## 【0072】

前記ゲート構造物両側のアクティブ領域の基板表面の下には第1及び第2不純物領域214a、214bが備えられる。前記第1及び第2不純物領域214a、214bは選択トランジスタのソース／ドレーンで使われる。

## 【0073】

前記基板200、素子分離膜パターン204、及び前記ゲート構造物の上部面にエッティング阻止膜218が備えられる。前記エッティング阻止膜218は層間絶縁膜226に対してエッティング選択比が高い物質からなり、例えば、シリコン窒化物からなることができる。前記エッティング阻止膜218には前記第1不純物領域214aが露出する第1コンタクトホールが生成されている。

10

## 【0074】

前記第1コンタクトホール内部にはピットラインコンタクト224aが備わり、前記エッティング阻止膜218上には前記ピットラインコンタクト224aと一体でピットライン224bが備えられる。以下、前記ピットラインコンタクト224a及びピットライン224bをピットライン構造物224とする。

## 【0075】

前記ピットライン構造物224の表面の少なくとも一部分は金属シリサイドからなる。本発明の実施例において、前記ピットライン構造物224の金属シリサイドはコバルトシリサイド、チタンシリサイド、タンタルシリサイド、ニッケルシリサイド、白金シリサイドなどからなることができる。これらは単独または2つ以上が混合して使われることができる。

20

## 【0076】

前記ピットライン構造物224は、図1及び図2を参照して説明した第1配線と実質的に同一であるか、または、類似の構成を有することができる。これとは異なって、前記ピットライン構造物224は、図3または図4を参照して説明した第1配線と実質的に同一であるかまたは類似の構成を有することもある。

## 【0077】

前記ピットライン構造物224上にはシリコン窒化物からなる第2ハードマスクパターン222が備えられる。

30

## 【0078】

本発明の実施例において、ピットラインコンタクト224aは層間絶縁膜226の間を貫通せずに、エッティング阻止膜218だけを貫通する形状を有することができる。すなわち、ピットラインコンタクト224aの両側には層間絶縁膜226が備えられないため、前記層間絶縁膜226に該当する高さほど高さが低くなるため前記ピットライン構造物224の全体の高さも非常に低くなることになる。このように、前記ピットライン構造物224の高さが低くなても前記ピットライン構造物224を構成する導電物質に低い抵抗の金属シリサイドが含まれているため、前記ピットライン構造物224は半導体装置で要求する低い抵抗を有することができる。

## 【0079】

前記エッティング阻止膜218上に前記ピットライン224bの間を埋め立てる層間絶縁膜226が備えられる。

40

## 【0080】

前記層間絶縁膜226及びエッティング阻止膜218を貫通して基板100の第2不純物領域214bと接触するストレージノード(storage node)コンタクト234が備えられる。前記ストレージノードコンタクト234の両側壁は絶縁物質からなることができる。本発明の実施例において、前記ストレージノードコンタクト234の側壁には内壁スペーサ232及び絶縁パターン235が備えられることができる。前記ストレージノードコンタクト234はポリシリコンからなることができる。

## 【0081】

前記ストレージノードコンタクト234上にキャパシタ240が備えられる。前記キャ

50

パシタ 240 は高い蓄積容量を有するシリンドラ型の構造を有することができるが、スタック型の構造を有することもできる。

【0082】

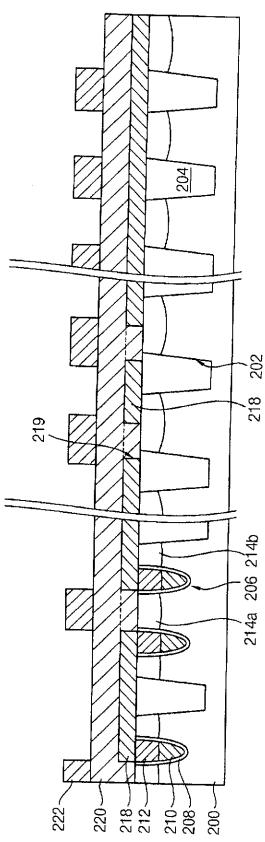

図17～図25は、図15に示した半導体装置の製造方法を説明するための断面図である。図17～図25に示した断面図は左側部から各々図15のA-A'線、B-B'線、及びC-C'線に沿って切断した図である。

【0083】

図17を参照すれば、単結晶シリコン基板200にパッド酸化膜(図示せず)を形成する。その後、前記パッド酸化膜上に素子分離用トレンチを形成する時にエッチングマスクで使われるハードマスクパターン(図示せず)を形成する。

10

【0084】

前記ハードマスクパターンをエッチングマスクで使って素子分離領域に位置する前記パッド酸化膜及び基板200を選択的にエッチングすることによって、基板200に素子分離用トレンチ202を形成する。前記素子分離用トレンチ202以外の基板200のアクティブ領域は孤立された形状を有して規則的に配列される。

【0085】

前記素子分離用トレンチ202の側面及び底面に露出したシリコンを熱酸化させてトレンチ内壁酸化膜(図示せず)を形成する。前記トレンチ内壁酸化膜及び前記ハードマスクパターンの表面上に窒化膜ライナ(図示せず)を形成する。

20

【0086】

前記素子分離用トレンチ202内を埋めたてしながら前記ハードマスクパターンを覆うようにシリコン酸化膜(図示せず)を形成する。例えば、前記シリコン酸化膜はHDP(high Density plasma)酸化物、TEOS(tetraethyl orthosilicate)、USG(undoped Silicate glass)、TOSZ(登録商標)(Tonen Silazane)等を含むことができる。本発明の実施例において、前記素子分離用トレンチ202内に窒化物膜または空気層がさらに含まれることもできる。

【0087】

前記ハードマスクパターンが露出するように前記シリコン酸化膜を化学機械的研磨(CMP)工程で研磨して前記素子分離用トレンチ202内部を埋め立てる素子分離膜パターン204を形成する。

30

【0088】

前記ハードマスクパターン及び前記素子分離膜パターン204上に有機反射防止膜(図示せず)を形成する。前記有機反射防止膜を写真エッチング工程を通じてパターニングして有機反射防止膜パターン(図示せず)を形成する。前記有機反射防止膜パターンはゲート構造物形成領域を選択的に露出する。

【0089】

前記有機反射防止膜パターンで前記ハードマスクパターンをエッチングして、次いで、前記パッド酸化膜をエッチングする。その後、アッシング(shining)工程及び/またはストリッピング工程を通じて前記有機反射防止膜パターンを除去する。

40

【0090】

前記ハードマスクパターンをエッチングマスクとして使って前記露出したアクティブ領域及び素子分離領域の基板200表面を異方性エッチング工程でエッチングすることによって、前記ゲート電極用トレンチ206を形成する。前記ゲート電極用トレンチ206は前記アクティブ領域を横切る方向に延長することができる。孤立した形状の前記アクティブパターン内には2つのゲート電極用トレンチ206が形成される。

【0091】

図18を参照すれば、前記ゲート電極用トレンチ206の内壁に露出した基板200表面にゲート酸化膜208を形成する。前記ゲート酸化膜208は前記基板200を熱酸化させて形成することができる。これとは異なって、前記ゲート酸化膜208は高誘電率を

50

有する金属酸化物を原子層積層（ALD）工程または化学気相蒸着（CVD）工程を通じて蒸着させて形成することができる。例えば、前記高誘電率を有する金属酸化物はアルミニウム酸化物（Al<sub>2</sub>O<sub>3</sub>）、チタン酸化物（TiO<sub>2</sub>）、タンタル酸化物（Ta<sub>2</sub>O<sub>5</sub>）、ジルコニア酸化物（ZrO<sub>2</sub>）、ハフニウム酸化物（HfO<sub>2</sub>）等を挙げができる。これらは単独または互いに混合して使われることができる。

【0092】

前記ゲート酸化膜208上にゲート電極用導電膜（図示せず）を形成する。前記ゲート電極用導電膜は前記ゲート電極用トレンチ206内部を完全に埋め立てるように形成する。前記ゲート電極用導電膜はドーピングされたポリシリコンと同じ半導体物質、金属シリサイド及び／または金属を使って形成することができる。これらは単独または互いに混合して使うことができる。例えば、前記ゲート電極用導電膜に含まれる金属としてはタングステン、チタン窒化物、タンタル窒化物などを挙げができる。

10

【0093】

前記ゲート電極用トレンチ206内部にだけ前記ゲート電極用導電膜が残っているように前記ゲート電極用導電膜を化学機械的研磨工程を通じて研磨する。その後、湿式エッティング工程または乾式エッティング工程を通じて前記ゲート電極用導電膜を部分的に除去することによって、導電膜パターン210を形成する。これに伴い、前記導電膜パターン210は前記ゲート電極用トレンチ206内部を部分的に埋め立てことになる。

【0094】

上述のように、前記導電膜パターン210は写真エッティング工程によってパターニングされるのではなく、ダマシン工程を通じて形成される。従って、前記導電膜パターン210は写真エッティング工程でパターニングすることが難しい金属を使って形成されることができる。

20

【0095】

前記導電膜パターン210上に前記ゲート電極用トレンチ206内部を完全に埋め立てるハードマスク膜（図示せず）を形成する。前記ハードマスク膜は化学気相蒸着工程を利用してシリコン窒化物を蒸着させて形成することができる。前記ゲート電極用トレンチ206内部にだけ前記ハードマスク膜が残っているように化学機械的研磨工程を行って、前記ハードマスク膜の一部を除去する。

30

【0096】

前記化学機械的研磨工程を行えば、前記ゲート電極用トレンチ206内部には導電膜パターン210及び第1ハードマスクパターン212が積層されたゲート構造物が完成される。前記第1ハードマスクパターン212はゲート電極及びワードラインに提供される前記導電膜パターン210を保護する。

【0097】

本発明の実施例において、前記ゲート酸化膜208、導電膜パターン210及び第1ハードマスクパターン212を含む前記ゲート構造物は前記ゲート電極用トレンチ206内部に位置して前記基板200上部面より高く突出しない。

【0098】

イオン注入工程を通じて前記アクティブ領域の基板200表面下へ不純物を注入することによって、第1及び第2不純物領域214a、214bをそれぞれ形成する。この時、前記ゲート構造物の第1ハードマスクパターン212はイオン注入マスクとして利用される。

40

【0099】

上述の工程を行えば、半導体装置のメモリセルに含まれる選択トランジスタが完成される。

【0100】

図19を参照すれば、前記選択トランジスタが形成されている前記基板200表面上にエッティング阻止膜218を形成する。前記エッティング阻止膜218はシリコン窒化物を蒸着させ形成することができる。

50

## 【0101】

前記エッチング阻止膜218を写真エッチング工程でエッチングして、前記基板200に形成された第1不純物領域214aを露出させる第1コンタクトホール219を形成する。前記第1コンタクトホール219を満たしながら前記エッチング阻止膜218上にポリシリコン膜220を形成する。

## 【0102】

前記ポリシリコン膜220上にビットラインを形成するためのマスクとして使われる第2ハードマスクパターン222を形成する。前記第2ハードマスクパターン222は前記アクティブ領域を横切るように第1方向に延長するライン形状を有することができる。前記第2ハードマスクパターン222は前記ゲート電極の延長方向と垂直な方向に延長する。また、前記第2ハードマスクパターン222は前記アクティブ領域の間の素子分離領域を過ぎて、前記アクティブ領域の第1不純物領域214aの上部を覆うように側傍に突出した形状を有することができる。

10

## 【0103】

図20を参照すれば、前記第2ハードマスクパターン222をエッチングマスクとして利用して前記ポリシリコン膜220をエッチングすることによって、前記第1コンタクトホール219内部を埋め立てながら前記エッチング阻止膜218の上部面で突出する予備導電パターン(図示せず)を形成する。前記予備導電パターンはポリシリコンからなることができる。

20

## 【0104】

前記予備導電パターン及びエッチング阻止膜218上に金属膜を形成して、前記金属膜を熱処理することによって前記予備導電パターン表面の少なくとも一部分をシリサイデーション(Silicidation)させる。それによって、少なくとも一部分に金属シリサイドを含み、ビットラインコンタクト224a及びビットライン224bが積層されたビットライン構造物224を形成する。前記ビットライン構造物224に含まれるビットラインコンタクト224a及びビットライン224bは1回の蒸着工程を通じて形成された一体形態の配線である。

20

## 【0105】

上述のように、前記第2ハードマスクパターン222が前記アクティブ領域の間の素子分離領域を過ぎながら、前記アクティブ領域の第1不純物領域214aの上部を覆うように側傍で突出した形状を有するため、図15に示したことと同じように前記ビットライン224bが前記アクティブ領域の第1不純物領域214aの上部を覆うように側傍に突出する。

30

## 【0106】

前記予備導電パターンの形成及びビットライン構造物224を形成する工程は図9～図11を参照して説明した工程と実質的に同一である。

## 【0107】

図21を参照すれば、前記ビットライン構造物224間のギャップを埋め立てる層間絶縁膜226を形成する。前記層間絶縁膜226を形成する工程は図10を参照して説明した工程と実質的に同一である。

40

## 【0108】

前記層間絶縁膜226上に前記第1方向に実質的に直交する第2方向に沿って延長するライン形状のフォトレジストパターン228を形成する。前記フォトレジストパターン228は前記第2不純物領域214b上部を露出しながら前記第2方向に延長する形状を有することができる。

## 【0109】

本発明の実施例において、前記フォトレジストパターン228が前記第1不純物領域214aの基板200をカバーする。従って、前記フォトレジストパターン228により隣接するアクティブ領域の間の素子分離領域も共に露出する。それによって、2つのアクティブ領域に各々形成された第2不純物領域214bの上部が同時に露出する。前記第2不

50

純物領域 214b の上部表面はストレージノードコンタクトが形成される領域である。

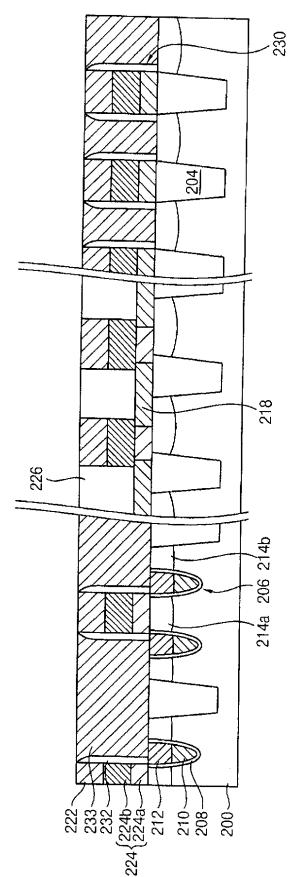

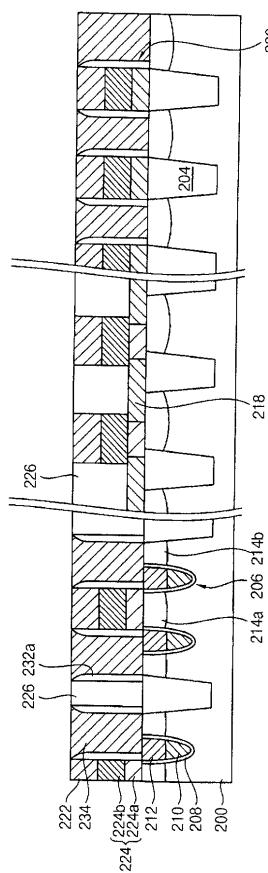

【0110】

図23を参照すれば、前記フォトレジストパターン228及び第2ハーデマスクパターン222によって露出された層間絶縁膜226をエッチングする。次いで、前記エッチング阻止膜218を除去して前記基板200を露出させる。それによって、前記層間絶縁膜226には第2コンタクトホール230が形成される。

【0111】

前記フォトレジストパターン228をエッチングマスクとして使って前記層間絶縁膜226及びエッチング阻止膜218をエッチングすると、互いに隣接する2つのストレージノードコンタクト領域及び前記ストレージノードコンタクト領域の間の素子分離領域を同時に露出させる第2コンタクトホール230を形成することができる。

10

【0112】

前記第2コンタクトホール230の側壁に絶縁物質からなる内壁スペーサ232を形成する。これで、前記ビットライン222と前記ストレージノードコンタクトが互いに絶縁される。

【0113】

前記第2コンタクトホール230内部に導電物質を埋め立てて、前記第2ハーデマスクパターン222の上部面が露出するように研磨することによって、予備ストレージノードコンタクト233を形成する。前記導電物質は乾式エッチング工程を通じて容易にエッチングできる物質ならば可能であり、ポリシリコンを含むことができる。

20

【0114】

本発明の実施例において、一つの予備ストレージノードコンタクト233は互いに異なるアクティブ領域に形成された2つの第2不純物領域214bの上部面と同時に接続されることができる。

【0115】

図25を参照すれば、前記予備ストレージノードコンタクト233が第2不純物領域214bと各々接觸することができるよう前記予備ストレージノードコンタクト233を2つに分離する。それによって、前記第2不純物領域214bと各々接觸するストレージノードコンタクト234を形成する。

30

【0116】

本発明の実施例によれば、前記予備ストレージノードコンタクト233及び層間絶縁膜226上にフォトレジストパターン(図示せず)を形成する。前記フォトレジストパターンは前記予備ストレージノードコンタクト233と接している素子分離領域を露出する形状を有することができる。例えば、前記フォトレジストパターンの露出部位はライン形状を有することができる。次に、前記フォトレジストパターンをエッチングマスクとして使って、前記素子分離領域が露出するよう前記予備ストレージノードコンタクト233をエッチングする。前記エッチング工程を行えば、前記予備ストレージノードコンタクト233が分離して前記素子分離領域の両側で2つのストレージノードコンタクト234が形成される。これと共に分離したそれぞれのストレージノードコンタクト234は互いに異なるアクティブ領域で第2不純物領域214bと接觸することになる。

40

【0117】

前記分離したそれぞれのストレージノードコンタクト234間に生成されたギャップを埋め立てるよう絶縁物質を蒸着し、これを平坦化することによって、絶縁パターン235を形成する。例えば、前記絶縁パターン235はシリコン酸化物からなることができる。

【0118】

上述の工程によれば、前記絶縁パターン235と接する前記ストレージノードコンタクト234の側壁部位には内壁スペーサ232が備えられず、残り部位のストレージノードコンタクト234の側壁部位には内壁スペーサ232が備えられる。すなわち、前記ビットライン構造物224と隣接するストレージノードコンタクト234の側壁部位には内壁

50

スペーサ 232 が備えられる。

【0119】

上述したこととは異なって、別途のストレージノードコンタクトの分離工程なしでストレージノードコンタクト 234 を形成することができる。これに対しては、図 22 及び図 24 を参照して説明する。

【0120】

図 22 及び図 24 は本発明の他の実施例によってストレージノードコンタクトを形成する方法を説明するための断面図である。

【0121】

図 17 ~ 図 20 を参照して説明した工程を行った後、図 22 に示したように、第 2 コンタクトホールを形成するためのフォトレジストパターン 228a を形成する。前記フォトレジストパターン 228a は前記第 1 不純物領域 214a の基板 200 のみならず、前記第 1 方向で互いに隣接するアクティブ領域間の素子分離領域をマスキング (masking) するように形成される。

【0122】

図 24 を参照すれば、前記フォトレジストパターン 228a をエッチングマスクとして使って前記層間絶縁膜 226 及びエッチング阻止膜 218 を次々とエッチングしたならば、第 2 不純物領域 214b を露出させる前記第 2 コンタクトホールが形成される。前記第 2 コンタクトホール内に内壁スペーサ 232a を形成する。

【0123】

前記内壁スペーサ 232a が形成された第 2 コンタクトホール内に導電物質を埋め立てて平坦化することによって、第 2 不純物領域 214b と電気的に接触するストレージノードコンタクト 234 を形成する。上述の工程を通じて形成されたストレージノードコンタクト 234 の側壁には内壁スペーサ 232a が備えられる。

【0124】

その後、図 16 に示したように、前記ストレージノードコンタクト 234 と接続するようにキャパシタ 240 を形成する。前記キャパシタ 240 はシリンドラ型構造を有することができ、スタッカ型構造を有することもできる。

【0125】

図 26 は本発明の他の実施例に係る配線構造物を含む半導体装置を示す断面図である。図 26 において、前記半導体装置はビットライン 224b に形成された金属シリサイド S の形状を除いては図 16 を参照して説明した半導体装置と実質的に同じ構成を有する。

【0126】

図 26 に示したように、前記半導体装置は少なくとも一部分に金属シリサイド S を含み、ビットライン 224b 及びビットラインコンタクト 224a を含むビットライン構造物 224 を含む。

【0127】

前記ビットライン 224b の側壁表面部位は、金属シリサイド S からなる。そして、前記ビットライン 224b の残り部分及びビットラインコンタクト 224a はポリシリコンからなる。

【0128】

図 26 に示した半導体装置は金属シリサイド S を形成するための工程を除いては、図 17 ~ 図 24 を参照して説明した工程と実質的に同じ工程を通じて形成されることができる。すなわち、図 20 を参照して説明した金属シリサイド S を含むビットライン 224b の形成工程において、予備導電パターンの側壁部位だけがシリサイデーション反応が起きるように金属膜蒸着条件及びシリサイデーションのための熱処理条件を調節することによって、図 26 に示した半導体装置を製造することができる。

【0129】

図 27 は本発明のまた他の実施例に係る配線構造物を含む半導体装置の断面図である。図 27 に示した半導体装置は、ビットライン構造物 224 全体が金属シリサイド S からな

10

20

30

40

50

ることを除いては図16を参照して説明した半導体装置と実質的に同じ構成を有する。

【0130】

図27に示したように、前記半導体装置はビットライン224b及びビットラインコンタクト224a全体が金属シリサイドSからなるビットライン構造物224を具備する。

【0131】

本発明のまた他の実施例によれば、前記半導体装置はビットライン全体及びビットラインコンタクトの上部が金属シリサイドからなるビットライン構造物を含むこともできる。

【0132】

図27に示した半導体装置の製造方法において、ビットライン構造物224に含まれる金属シリサイドSは前記金属膜形成工程及びシリサイデーション反応が起きるようにする熱処理条件を調節することによって多様な厚さと形状を有するようにすることができる。

10

【0133】

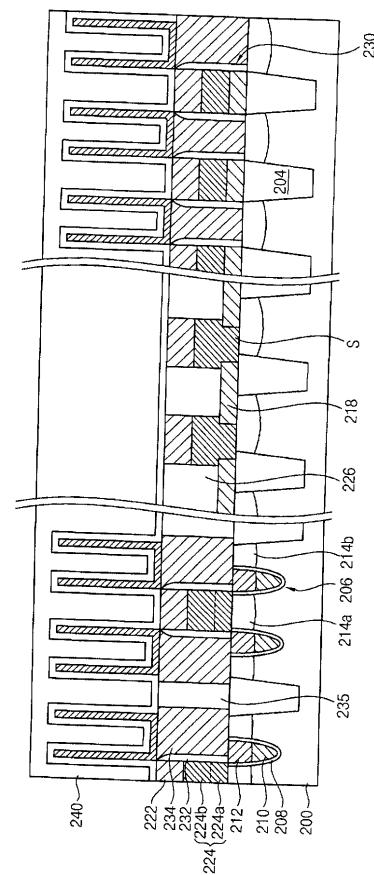

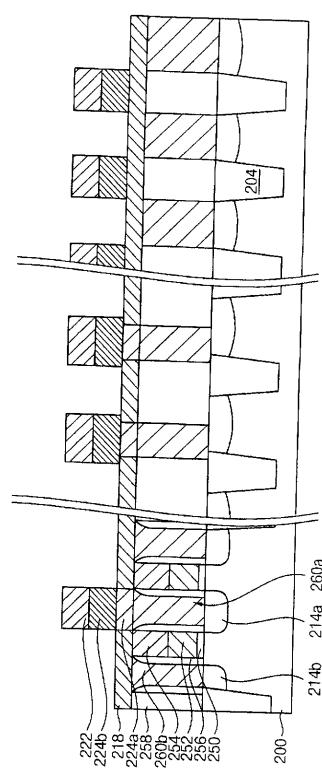

図28は本発明のまた他の実施例に係る配線構造物を含む半導体装置の断面図である。図28に示した半導体装置は図1を参照して説明した配線構造物と実質的に同じ構造を有する配線構造物を含む。

【0134】

図28を参照すれば、アクティブ領域及び素子分離領域が区分される基板200が設けられる。前記基板200の素子分離領域には素子分離用トレンチが生成されていて前記素子分離用トレンチ内部に素子分離膜パターン204が埋め立てられている。

20

【0135】

前記アクティブ領域及び素子分離領域を有する基板200上には第1方向に延長するライン形状を有するゲート構造物が備えられる。前記ゲート構造物は前記基板200上部面から突出する形状を有することができる。前記ゲート構造物はそれぞれゲート酸化膜250、導電膜パターン252、及び第1ハードマスクパターン254が積層された構造を有する。

【0136】

前記ゲート構造物の両側壁にはスペーサ256が備えられる。本発明の実施例において、前記ゲート構造物は前記基板200に含まれたりセス(recess)内部を埋め立てながら前記基板200表面上で突出するリセスゲートの形状を有することができる。

30

【0137】

前記ゲート構造物両側のアクティブ領域の基板200表面の下には第1及び第2不純物領域214a、214bが備えられる。

【0138】

前記ゲート構造物を覆いながら基板200上には下部層間絶縁膜258が備えられる。前記下部層間絶縁膜258の上部面は前記第1ハードマスクパターン254の上部面と同じ平面上に位置することができる。これとは異なって、前記下部層間絶縁膜258の上部面が前記第1ハードマスクパターン254の上部面より高く位置することもできる。

【0139】

前記下部層間絶縁膜258を貫通して前記第1及び第2不純物領域214a、214bと接触する第1及び第2コンタクトパッド260a、260bが各々備えられる。

40

【0140】

前記下部層間絶縁膜258、第1及び第2コンタクトパッド260a、260b上にはエッチング阻止膜218が備えられる。前記エッチング阻止膜218を貫通して前記第1パッドコンタクト260aと接触するビットラインコンタクト224aが備わって、前記エッチング阻止膜218上には前記ビットラインコンタクト224aと一体でビットライン224bが配置される。前記ビットライン224bの表面の少なくとも一部分は金属シリサイドからなる。

【0141】

前記ビットラインコンタクト224a及びビットライン224bからなるビットライン構造物224は図1を参照して説明した第1配線と実質的に同じ構成を有することができ

50

る。前記ピットライン構造物 224 上にはシリコン窒化物からなる第2ハーデマスクパターン 222 が備えられる。前記ピットライン 224b の間には層間絶縁膜 226 が備えられる。

【0142】

前記層間絶縁膜 226 及びエッチング阻止膜 218 を貫通して前記第2パッドコンタクト 260b の少なくとも一部分と接触するストレージノードコンタクト 234 が備えられる。前記ストレージノードコンタクト 234 の側壁には絶縁物質からなる内壁スペーサ 232 が備えられる。前記ストレージノードコンタクト 234 上にはキャパシタ 240 が備えられる。

【0143】

図29～図31は、図28に示した半導体装置の製造方法を説明するための断面図である。

【0144】

図29を参照すれば、単結晶シリコン基板 200 にシャロートレンチ (Shallow trench) 素子分離工程を行って素子分離膜パターン 204 を形成することによって、前記基板 200 をアクティブ領域及び素子分離領域で区分する。

【0145】

前記アクティブ領域の基板 200 上にゲート酸化膜 250 を形成する。前記ゲート酸化膜 250 上にゲート電極で形成される導電膜 (図示せず) を形成する。前記導電膜上に第1ハーデマスク膜 (図示せず) を形成する。前記第1ハーデマスク膜はシリコン窒化物を蒸着させ形成することができる。

【0146】

前記ハーデマスク膜を写真エッチング工程によってパターニングすることによって、前記アクティブ領域を横切るライン形状の第1ハーデマスクパターン 254 を形成する。一つのアクティブ領域上には2つの第1ハーデマスクパターン 254 が配置される。

【0147】

前記第1ハーデマスクパターン 254 をエッチングマスクとして使って、前記導電膜をエッチングすることによって導電膜パターン 252 を形成する。前記導電膜パターン 252 はゲート電極及びワードラインで使われる。以下、前記ゲート酸化膜 250 、導電膜パターン 252 及び第1ハーデマスクパターン 254 の積層構造をゲート構造物とする。

【0148】

前記導電膜パターン 252 、第1ハーデマスクパターン 254 、基板表面についてスペーサ用絶縁膜 (図示せず) を形成する。前記スペーサ用絶縁膜はシリコン窒化物からなることができる。前記スペーサ用絶縁膜を異方性でエッチングすることによって、前記ゲート構造物の側壁にスペーサ 256 を形成する。また、前記ゲート構造物両側の基板表面の下に不純物を注入することによって、第1及び第2不純物領域 214a 、 214b を形成する。

【0149】

前記ゲート構造物の間ギャップを埋め立てる下部層間絶縁膜 258 を形成する。前記下部層間絶縁膜 258 はシリコン酸化物を蒸着した後に前記第1ハーデマスクパターン 254 が上部面に露出するように前記シリコン酸化物の表面を平坦化することによって形成することができる。

【0150】

前記下部層間絶縁膜 258 の一部分を写真エッチング工程を通じてエッチングすることによって、第1及び第2不純物領域 214a 、 214b を各々露出するコンタクトホールを形成する。前記コンタクトホール内に導電物質を埋め立てて、平坦化することによってコンタクトパッド 260a 、 260b を形成する。

【0151】

上述の工程を行えば、前記下部層間絶縁膜 258 を貫通して前記第1不純物領域 214a と接触する第1コンタクトパッド 260a と前記下部層間絶縁膜 258 を貫通して前記

10

20

30

40

50

第2不純物領域214bと接触する第2コンタクトパッド260bが各々形成される。

【0152】

図30を参照すれば、前記下部層間絶縁膜258、第1及び第2コンタクトパッド260a、260b表面上にエッチング阻止膜218を形成する。

【0153】

前記エッチング阻止膜218の一部分を写真エッチングを通じて次々とエッチングすることによって、第1コンタクトホールを形成する。前記第1コンタクトホールの底面には第1コンタクトパッド260aの上部面が露出する。前記第1コンタクトホールを満たしながら前記エッチング阻止膜218上にポリシリコン膜(図示せず)を形成する。前記ポリシリコン膜上にピットラインを形成するためのマスクとして使われる第2ハードマスクパターン222を形成する。

10

【0154】

前記第2ハードマスクパターン222をエッチングマスクとして前記ポリシリコン膜をエッチングすることによって、予備導電パターン(図示せず)を形成する。その後、前記予備導電パターン、エッチング阻止膜218及び第2ハードマスクパターン222表面上に金属膜を蒸着し、これをシリサイド化して前記予備導電パターンの少なくとも一部分に金属シリサイドを形成する。それによって、金属シリサイドを含んで、ピットラインコンタクト224a及びピットライン224bで構成されるピットライン構造物を形成する。

20

【0155】

前述した予備導電パターン及びピットライン構造物を形成する工程は図20を参照して説明した工程と実質的に同一である。

30

【0156】

図30を参照すれば、前記ピットライン構造物224の間のギャップを埋め立てる層間絶縁膜226を形成する。

【0157】

前記層間絶縁膜226を部分的にエッチングした後、前記エッチング阻止膜218をエッチングすることによって、前記第2コンタクトパッド260b上部面の少なくとも一部分を露出する第2コンタクトホールを形成する。このような層間絶縁膜226形成及び前記第2コンタクトホールを形成する工程は図21～図24を参照して説明した工程と実質的に同一である。

30

【0158】

前記第2コンタクトホールの側壁上に内壁スペーサ232を形成した後、前記第2コンタクトホール内に導電物質を埋めたてさせてストレージノードコンタクト234を形成する。

【0159】

その後、図28に示したように、前記ストレージノードコンタクト234と接続するキャパシタ240を形成する。

【0160】

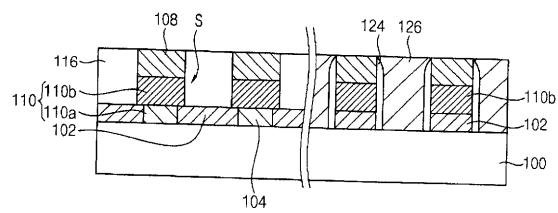

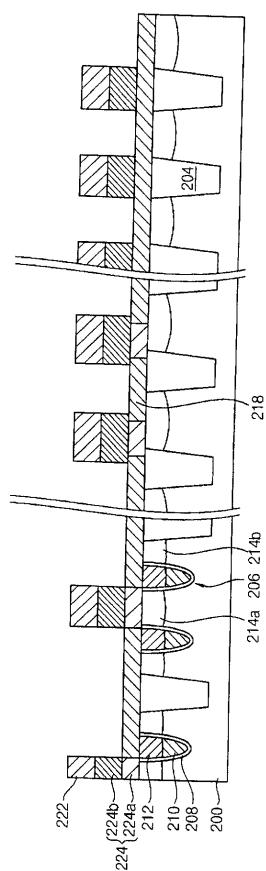

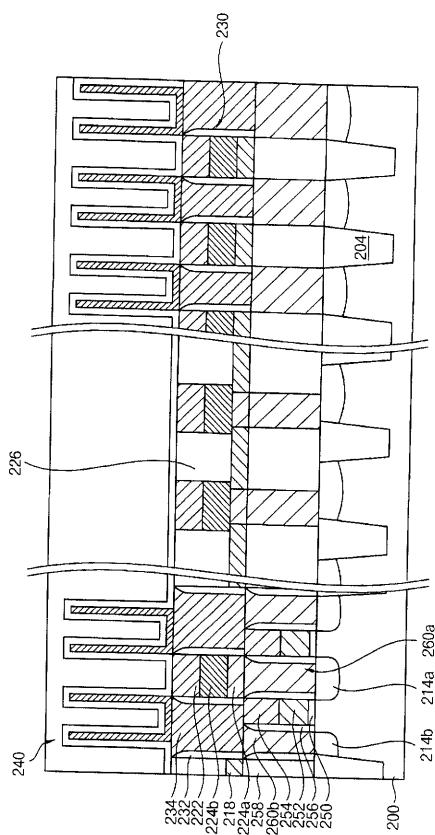

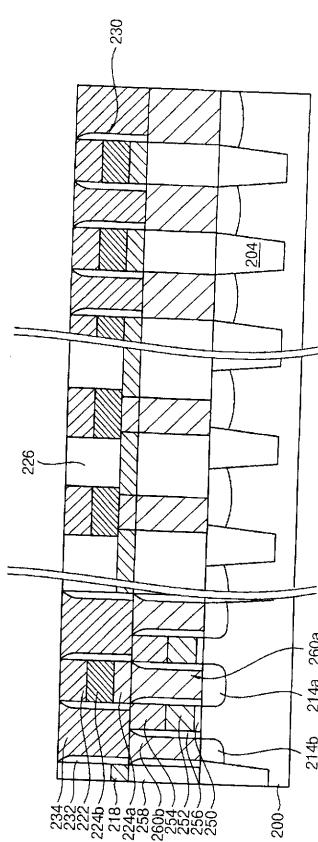

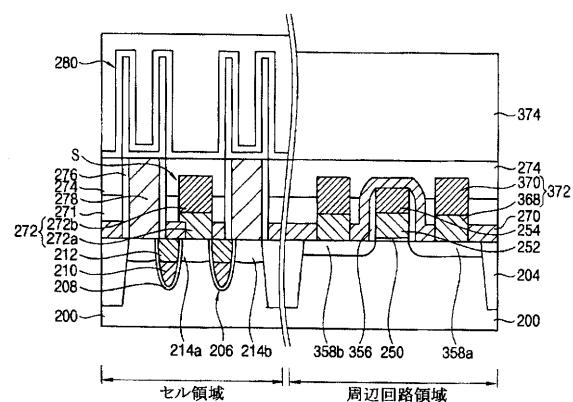

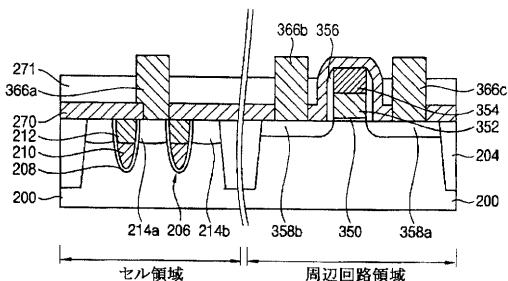

図32は、本発明のまた他の実施例に係る配線構造物を含む半導体装置を示す断面図である。図32に示した半導体装置において、メモリセル領域には図16を参照して説明したメモリセル領域と実質的に同じ構造のメモリセルが備えられる。また、前記半導体装置の周辺回路領域にはプランナー(planar)型のトランジスタが配置される。前記半導体装置のメモリセル領域には、図16を参照して説明したセルと実質的に同じ構造のメモリセルが備えられるので、以下においては前記半導体装置の周辺回路領域に備えられる素子を説明する。

40

【0161】

図32を参照すれば、周辺回路領域の基板200には素子分離領域及びアクティブ領域を区分する素子分離膜パターン204が備えられる。前記周辺回路領域の基板200表面上にはゲート絶縁膜302、第2ゲート電極304、及び第3ハードマスクパターン306が積層された第2ゲート構造物が備えられる。本発明の実施例において、前記第2ゲー

50

ト電極 304 は、ポリシリコン 304a 及び金属シリサイド 304b を含む。また、前記第2ゲート構造物両側の基板 200 表面下へソース／ドレーンで使われる第3及び第4不純物領域 310a、310b が備えられる。

【0162】

前記第2ゲート構造物は前記基板 200 表面上にゲート絶縁膜 302 が備えられるのを除いてはメモリセル領域に形成されたビットラインコンタクト 224a、ビットライン 224b 及び第2ハードマスクパターン 222 と実質的に同じ積層構造を有する。

【0163】

本発明の実施例によれば、前記第2ゲート構造物に含まれる第2ゲート電極 304 は前記ビットラインコンタクト 224a を構成する物質及びビットライン 224b を成し遂げる物質が積層された構造を有することができる。従って、前記第2ゲート電極 304 は表面の少なくとも一部分が金属シリサイドからなるから、前記第2ゲート電極 304 は低い抵抗を有することができる。前記第3ハードマスクパターン 306 は前記ビットライン 224b 上に備えられる第2ハードマスクパターン 222 と実質的に同じ物質からなって、例えば、シリコン窒化物からなることができる。前記第2及び第3ハードマスクパターン 222、306 の上部面は実質的に同じ平面上に位置することができる。

【0164】

前記第2ゲート構造物の間のギャップ部位に層間絶縁膜 226 が備えられる。前記層間絶縁膜 226 は前記セル領域に形成された層間絶縁膜 226 と同じ物質からなることができる。

【0165】

前記層間絶縁膜 226 を貫通して前記第3及び第4不純物領域 310a、310b と接触する第2コンタクトプラグ 312 が備えられる。互いに隣接する第2コンタクトプラグの間には絶縁パターン 235 が備えられる。前記第2コンタクトプラグ 312 及び層間絶縁膜 226 上には上部層間絶縁膜 314 が備えられる。

【0166】

図33～図38は、図32に示した半導体装置の製造方法を説明するための断面図である。

【0167】

図33を参照すれば、セル領域及び周辺回路領域が区分された基板 200 にシャロートレンチ素子分離工程を行って素子分離膜パターン 204 を形成する。

【0168】

図17及び図18を参照して説明した工程と実質的に同じ工程を行って、前記セル領域の基板 200 に埋め立てられたゲートを含む選択トランジスタを形成する。

【0169】

前記選択トランジスタが形成されている前記基板 200 表面上にエッチング阻止膜 218 を形成する。前記エッチング阻止膜 218 を写真エッチングして第1開口部 219a を形成する。具体的に、前記セル領域の基板には前記第1不純物領域 214a の基板 200 表面を露出させるコンタクトホールを形成する。また、前記周辺回路領域の基板 200 には、ゲート電極が形成される部位の基板 200 表面を露出させる開口部を形成する。

【0170】

前記第1開口部 219a 表面に露出している基板 200 を熱酸化させてゲート絶縁膜 302 を形成する。前記ゲート絶縁膜 302 上に前記ゲート絶縁膜 302 を保護するために予備ポリシリコン膜 303 を形成する。前記予備ポリシリコン膜 303 は、約 50 ～約 200 程度の厚さで形成されることがある。

【0171】

図34を参照すれば、前記予備ポリシリコン膜 303 上に前記セル領域を選択的に露出させるフォトレジストパターン（図示せず）を形成する。前記フォトレジストパターンをエッチングマスクで利用して前記セル領域に形成されている予備ポリシリコン膜及びゲート絶縁膜を全部除去する。それによって、前記セル領域に形成されているコンタクトホー

10

20

30

40

50

ルの底面には基板 200 表面が露出する。

【0172】

前記第1開口部 219a 内部を埋め立てながら前記セル領域及び周辺回路領域の前記エッチング阻止膜 218 表面を覆うように上部ポリシリコン膜 219 を形成する。以下、残っている予備ポリシリコン膜 303 と上部ポリシリコン膜 219 をポリシリコン膜 220 という。

【0173】

前記セル領域には前記第1開口部 219a 内に形成されているポリシリコン膜 220 が前記基板 200 表面と接触する。前記周辺回路領域には前記第1開口部 219a 内に形成されている予備ポリシリコン膜上に追加的に上部ポリシリコン膜 219 が形成される。それで、前記周辺回路領域に形成されるポリシリコン膜 220 は前記基板 200 表面と接触しないで、前記ゲート絶縁膜 302 表面と接触する。

10

【0174】

前記セル領域及び周辺回路領域に形成されている前記ポリシリコン膜 220 上にハードマスクパターン 222、306 を形成する。前記セル領域のハードマスクパターン 222 はビットラインを形成するためのエッチングマスクとして使われて、前記周辺回路領域のハードマスクパターン 306 はトランジスタのゲートを形成するためのエッチングマスクとして使われる。

20

【0175】

図 35 を参照すれば、前記ハードマスクパターン 222、306 をエッチングマスクとして使って前記ポリシリコン膜 220 をエッチングすることによって、第1開口部 219a 内部を埋め立てながら前記エッチング阻止膜 218 上部面より突出する予備導電パターン 220a を形成する。

20

【0176】

前記セル領域に形成されている予備導電パターン 220a はコンタクト及びラインパターンが積層された構造を有する。また、前記周辺回路領域に形成されている予備導電パターン 220a は、ライン形状または孤立した形状を有することができる。

30

【0177】

前記エッチング阻止膜 218、予備導電パターン 220a 及びハードマスクパターン 222、306 について金属膜 308 を形成する。前記金属膜 308 は、シリサイド化された時、金属窒化物より低い抵抗を有する物質で形成される。前記金属膜 308 で使われることができるもの例ではコバルト、チタン、タンタル、ニッケル、白金などをあげることができる。この時、前記金属膜 308 は前記予備導電パターン 220a の側壁一部と直接接触することになる。

30

【0178】

図 36 を参照すれば、前記金属膜 308 を熱処理することによって前記予備導電パターン 220a の少なくとも一部分をシリサイド化する。それによって、前記セル領域にはビットラインコンタクト 224a 及び前記ビットライン 224b が積層されて金属シリサイドを含むビットライン構造物 224 が形成される。また、前記周辺回路領域には金属シリサイド 304b を含む第2ゲート電極 304 が形成される。前記シリサイデーション工程条件を調節することによって、前記ビットライン構造物 224 及び第2ゲート電極 304 に含まれる金属シリサイドの厚さを調節することができる。また、前記金属シリサイドの厚さを調節して望む水準の低い抵抗を有するビットライン構造物 224 及びゲート電極 304 を得ることができる。

40

【0179】

その後、反応せずに残っている金属膜 308 を除去する。

【0180】

上述のように、本発明の実施例によれば、1回のシリサイデーション工程を通じて金属シリサイドを含むビットライン構造物 224 及びフェリー回路用トランジスタの第2ゲート電極 304 を同時に形成することができる。従って、前記半導体装置の製造工程が非常

50

に単純になることができる。

【0181】

図37を参照すれば、前記周辺回路領域の基板200に形成されているエッチング阻止膜218を選択的に除去する。このようなエッチング工程を行えば、セル領域の基板200表面上にだけエッチング阻止膜218が残っていることになる。

【0182】

その後、前記周辺回路領域の基板200に不純物を注入することによって、前記第2ゲート電極304両側の基板200表面の下に第3及び第4不純物領域310a、310bを形成する。前記第3及び第4不純物領域310a、310bは周辺回路用トランジスタのソース／ドレーンで提供される。

10

【0183】

本発明の他の実施例によれば、前記周辺回路領域の基板に不純物を注入する工程を遂行する前、後または、遂行中に、前記第2ゲート電極304の側壁にスペーサを形成する工程をさらに遂行することもできる。

【0184】

図38を参照すれば、前記ハードマスクパターン222、306を全部覆うように層間絶縁膜226を形成する。前記ハードマスクパターン222、306の上部面が露出するように前記層間絶縁膜226の上部面を研磨する。

20

【0185】

前記セル領域に形成されている層間絶縁膜226を貫通するストレージノードコンタクト234を形成する。前記ストレージノードコンタクト234を形成する工程は図21～図24を参照して説明した工程と実質的に同一である。

【0186】

前記周辺回路領域に形成されている層間絶縁膜226の一部をエッチングしてコンタクトホールを形成して、前記コンタクトホール内に導電物質を埋め立てて前記第3及び第4不純物領域310a、310bと接触する第3コンタクトプラグ312を形成する。

【0187】

再び、図32を参照すれば、前記周辺回路領域を覆う上部層間絶縁膜314を形成する。また、前記基板200のセル領域には前記ストレージノードコンタクト234と接続するようにキャパシタ240を形成する。前記キャパシタ240はシリンドラ型構造またはスタッカ型構造を有することができる。

30

【0188】

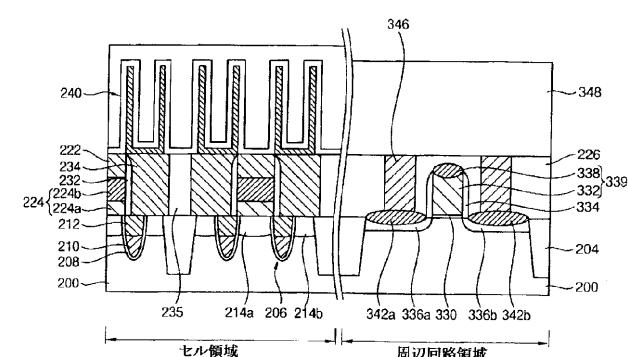

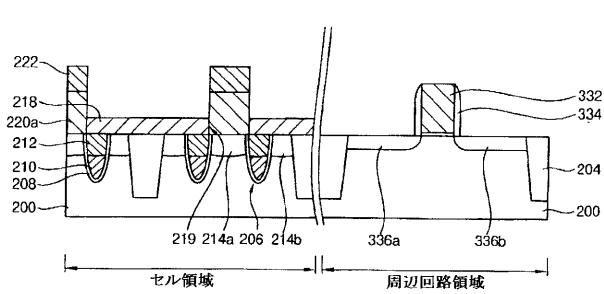

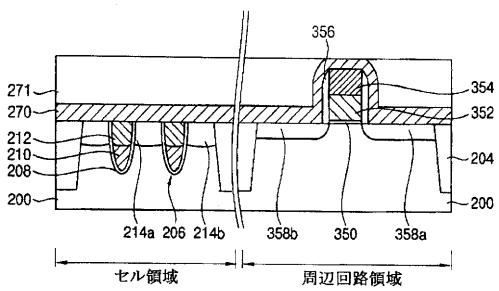

図39は本発明のまた他の実施例に係る配線構造物を有する半導体装置の断面図である。図39に示した半導体装置のセル領域には図16を参照して説明したものと実質的に同じ構造のセルが備えられる。また、前記半導体装置の周辺回路領域にはプランナー型のトランジスタが設けられる。従って、以下では前記半導体装置の周辺回路領域に備えられる素子を説明する。

【0189】

前記周辺回路領域の基板200には素子分離領域及びアクティブ領域を区分する素子分離膜パターン204が備えられる。前記周辺回路領域の基板200表面上にはゲート絶縁膜330及び第2ゲート電極339が積層された第2ゲート構造物が備えられる。すなわち、前記第2ゲート電極339上にはハードマスクパターンが備えられない。また、前記第2ゲート構造物両側の基板表面下にソース／ドレーンで使われる第3及び第4不純物領域336a、336bが備えられる。一方、前記第2ゲート構造物の両側壁にはスペーサ334が備えられる。

40

【0190】

前記第2ゲート電極339はポリシリコンパターン332及び金属シリサイド338が積層された形状を有する。また、前記スペーサ334両側に位置する前記第3及び第4不純物領域336a、336bの基板200上には前記金属シリサイド342a、342bが形成されている。前記金属シリサイド338、342a、342bは前記セル領域のビ

50

ットライン構造物に含まれる金属シリサイドと実質的に同じ物質からなる。

【0191】

前記基板200上において前記第2ゲート構造物の間のギャップ部位には層間絶縁膜226が備えられる。前記層間絶縁膜226は前記セル領域に形成された層間絶縁膜と実質的に同じ物質からなる。

【0192】

前記層間絶縁膜226を貫通して前記第3及び第4不純物領域336a、336b上の金属シリサイド342a、342bと接触する第3コントラクトプラグ346が備えられる。前記第3コントラクトプラグ346及び層間絶縁膜226上には上部層間絶縁膜348が備えられる。

10

【0193】

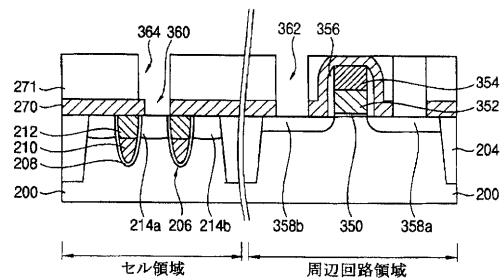

図40～図43は、図39に示した半導体装置の製造方法を説明するための断面図である。

【0194】

図40を参照すれば、セル領域及び周辺回路領域が区分された基板200にトレンチ素子分離工程を行って素子分離膜パターン204を形成する。次いで、図17及び図18を参照して説明した工程と実質的に同じ工程を行って、前記セル領域の基板200に埋め立てられたゲートを含む選択トランジスタを形成する。

【0195】

前記選択トランジスタを形成した後、前記周辺回路領域の基板200上にゲート絶縁膜330及びポリシリコン膜パターン332が積層された予備ゲート構造物を形成する。前記予備ゲート構造物両側壁にスペーサ334を形成する。

20

【0196】

前記予備ゲート構造物両側の基板表面下へ不純物を注入して第3及び第4不純物領域336a、336bを形成する。それによって、前記周辺回路領域の基板200には予備ゲート構造物、スペーサ334及び不純物領域336a、336bを含む予備トランジスタを形成する。

【0197】

前記セル領域及び周辺回路領域の基板200上にエッティング阻止膜218を形成する。すなわち、前記セル領域に形成されたエッティング阻止膜218は前記埋め立てられたゲートを含む選択トランジスタを覆う。また、前記周辺回路領域に形成されたエッティング阻止膜218は前記予備トランジスタを覆う。

30

【0198】

図41を参照すれば、前記エッティング阻止膜218を写真エッティング工程でエッティングして前記セル領域の第1不純物領域214aを露出させるコントラクトホール219を形成する。

【0199】

前記コントラクトホール219を埋め立てながら前記エッティング阻止膜218表面を覆うようにポリシリコン膜(図示せず)を形成する。前記セル領域に形成されている前記ポリシリコン膜上にハードマスクパターン222を形成する。この時、前記周辺回路領域には前記ハードマスクパターンが形成されない。前記セル領域のハードマスクパターン222はビットラインを形成するためのエッティングマスクとして使われる。

40

【0200】

前記ハードマスクパターン222をエッティングマスクとして使って前記ポリシリコン膜をエッティングする。それによって、前記セル領域の基板200には前記コントラクトホール219内部を埋め立てながら前記エッティング阻止膜218上部面より突出する予備導電パターン220aを形成する。また、前記周辺回路領域のエッティング阻止膜218上に形成されている前記ポリシリコン膜は全て除去される。

【0201】

写真エッティング工程を通じて、前記周辺回路領域の基板200に形成されているエッチ

50

ング阻止膜 218 を除去する。従って、前記周辺回路領域に形成された前記予備ゲート構造物の表面が露出する。また、前記予備ゲート構造物の両側では前記周辺回路領域の基板 200 表面が露出する。

【0202】

図 42 を参照すれば、前記セル領域及び周辺回路領域に形成された構造の表面について金属膜 340 を形成する。前記セル領域では前記エッチング阻止膜 218、予備導電パターン 220a、ハードマスクパターン 222 について金属膜を形成する。また、前記周辺回路領域では前記基板 200 表面及び予備ゲート構造物の表面について金属膜 340 を形成する。前記金属膜 340 はシリサイド化された時、金属窒化物より低い抵抗を有する物質で形成される。

10

【0203】

図 43 を参照すれば、前記金属膜 340 を熱処理することによって、前記セル領域の予備導電パターン 220a、フェリー回路領域のポリシリコンパターン 332、第 3 及び第 4 不純物領域 336a、336b の基板 200 表面の少なくとも一部分をシリサイデーションさせる。その結果、前記セル領域にはビットラインコンタクト 224a 及び前記ビットライン 224b が積層されて金属シリサイドを含むビットライン構造物が形成される。前記周辺回路領域には金属シリサイド 338 を含む第 2 ゲート電極 339 が形成される。また、前記第 3 及び第 4 不純物領域 336a、336b 表面にも金属シリサイド 342a、342b が形成される。

20

【0204】

次に、反応せずに残っている金属膜 340 を除去する。

【0205】

前記シリサイデーション工程条件を調節することによって、前記ビットライン構造物、第 2 ゲート電極 339 に含まれる金属シリサイド 224b、338 と第 3 及び第 4 不純物領域 336a、336b 表面に形成される金属シリサイド 342a、342b の厚さを調節することができる。また、前記金属シリサイドの厚さを調節して望む水準の低い抵抗を有するビットライン構造物及び第 2 ゲート電極 339 を得ることができる。また、周辺回路トランジスタのソース／ドレーンの抵抗も減少させることができる。

30

【0206】

上述のように、本発明の実施例によれば、1 回のシリサイデーション工程を通じて金属シリサイドを含むビットライン構造物、周辺回路用トランジスタの第 2 ゲート電極及びソース／ドレーンを同時に形成することができる。

【0207】

また、図 39 を参照すれば、前記ビットライン構造物及び第 2 ゲート電極 339 を覆う層間絶縁膜 226 を形成する。前記セル領域に形成されているハードマスクパターン 222 の上部面が露出するように前記層間絶縁膜 226 の上部面を研磨する。

30

【0208】

前記セル領域に形成されている層間絶縁膜 226 を貫通するストレージノードコンタクト 234 を形成する。前記ストレージノードコンタクト 234 を形成する工程は図 21～図 24 を参照して説明した工程と実質的に同一である。また、前記周辺回路領域に形成されている層間絶縁膜 226 の一部をエッチングしてコンタクトホールを形成して、このようなコンタクトホールを導電物質で埋め立てる。それによって、前記第 3 及び第 4 不純物領域 336a、336b 上に位置する金属シリサイド 342a、342b と接触する第 3 コンタクトプラグ 346 を形成する。

40

【0209】

前記周辺回路領域を覆う上部層間絶縁膜 348 を形成する。また、前記セル領域には前記ストレージノードコンタクト 234 と接続されるキャパシタ 240 を形成する。

【0210】

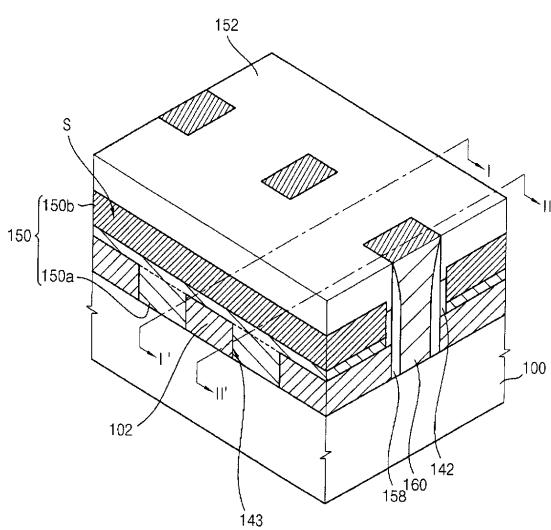

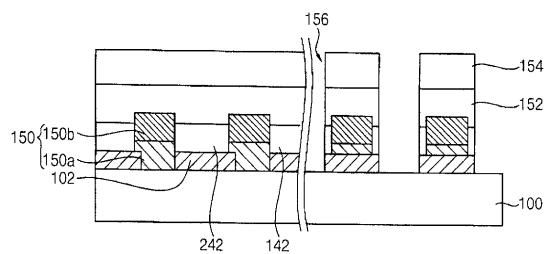

図 44 は本発明のまた他の実施例に係る配線構造物を示す斜視図であり、図 45 は図 40 に示した配線構造物を示す断面図である。図 45 において、左側部の断面図は図 44 の

50

I - I' 線に沿って切断した図であり、右側部の断面図は図44のII - II' 線に沿って切断した図である。図44及び図45に示した配線構造物は、図1及び図2を参照して説明した配線構造物とは異なって第1配線上にハードマスクパターンが備えられない。

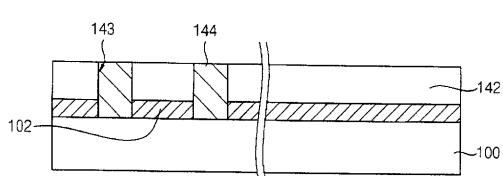

#### 【0211】

図44及び図45を参照すれば、基板100上にエッチング阻止膜102及び下部層間絶縁膜142が備えられる。前記エッチング阻止膜102には第1コンタクトホール143が用意されて、前記下部層間絶縁膜142には、前記第1コンタクトホール143と下面で延長するライン形状のトレンチ146が設けられる。

#### 【0212】

前記第1コンタクトホール143内部には第1コンタクトプラグ150aが備えられる。また、前記下部層間絶縁膜142に含まれたトレンチ146内には前記第1コンタクトプラグ150aと一体で備えられる導電性ライン150bが備えられる。

#### 【0213】

前記導電性ライン150bの上部面は、前記下部層間絶縁膜142の上部面より突出または前記下部層間絶縁膜142の上部面と同じ平面が位置することができる。前記第1コンタクトプラグ150a及び導電性ライン150bは第1配線150で提供される。前記第1配線150の少なくとも一部分は金属シリサイドSからなる。

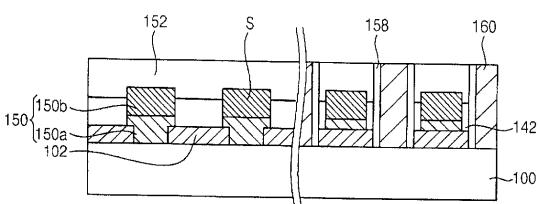

#### 【0214】

前記金属シリサイドSはコバルトシリサイド、チタンシリサイド、タンタルシリサイド、ニッケルシリサイド、白金シリサイドなどからなることができる。これらは単独で形成されることが望ましいが、2つ以上が混合されて積層されることができる。しかし、前記導電性ライン150bの上部面にはハードマスクパターンが備えられない。

#### 【0215】

前記導電性ライン150bが含まれた前記第1配線150と前記下部層間絶縁膜142を覆う層間絶縁膜152が備えられる。前記層間絶縁膜152の上部面は、前記導電性ライン150bの上部面より高く位置して前記導電性ライン150bを覆う。また、前記層間絶縁膜152は平坦な上部面を有することができる。

#### 【0216】

前記層間絶縁膜152、下部層間絶縁膜142及びエッチング阻止膜102を貫通して基板100と接触する第2コンタクトプラグ160が備えられる。前記第2コンタクトプラグ160の側壁には内壁スペーサ158が備えられることができる。前記内壁スペーサ158はシリコン酸化物またはシリコン窒化物からなることができる。

#### 【0217】

図46～図50は、図45に示した配線構造物の形成方法を説明するための断面図である。図46～図50において、左側部の断面図は図44のI - I' 線に沿って切断した図であり、右側部の断面図は図44のII - II' 線に沿って切断した図である。

#### 【0218】

図46を参照すれば、基板100上にエッチング阻止膜102及び下部層間絶縁膜142を形成する。前記下部層間絶縁膜142及びエッチング阻止膜102の一部を写真エッチング工程を通じて除去して基板100表面を露出する第1コンタクトホール143を形成する。

#### 【0219】

前記第1コンタクトホール143内部に炭素を含むポリマーからなる犠牲膜(図示せず)を埋め立てる。前記犠牲膜はアッシング工程及び/またはストリッピング工程を通じて容易に除去される物質で形成されることができる。

#### 【0220】

前記下部層間絶縁膜142の上部面が露出するように前記犠牲膜を化学機械研磨工程で研磨することによって、前記第1コンタクトホール143内に犠牲膜パターン144を形成する。

#### 【0221】

10

20

30

40

50

図47を参照すれば、前記下部層間絶縁膜142及び犠牲膜パターン144上にライン形状を有するフォトレジストパターン(図示せず)を形成する。前記フォトレジストパターンは下部に犠牲膜パターン144が露出するように形成される。

【0222】

前記フォトレジストパターンをエッチングマスクとして利用して前記下部層間絶縁膜142をエッチングすることによって、前記下部層間絶縁膜142にトレンチ146を形成する。

【0223】

前記フォトレジストパターンをアッシング工程及び/またはストリッピング工程を通じて除去する。前記フォトレジストパターンを除去する間前記犠牲膜パターン144も除去される。それによって、前記エッチング阻止膜102には前記第1コンタクトホール143が形成されて、前記下部層間絶縁膜142には前記第1コンタクトホール143と連係するトレンチ146が形成される。

10

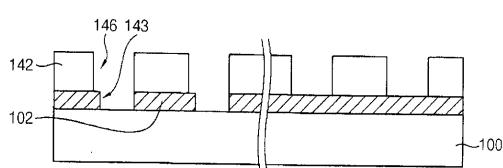

【0224】

図48を参照すれば、前記第1コンタクトホール143及びトレンチ146内部を埋め立てながら前記下部層間絶縁膜142上にポリシリコン膜(図示せず)を形成する。続いて、前記下部層間絶縁膜142の上部面が露出するように前記ポリシリコン膜をエッチバック(etch back)工程及び/または、化学機械的研磨工程で研磨する。このような工程によって、前記第1コンタクトホール143内部に満たされた予備コンタクトプラグと、前記予備コンタクトプラグ上部面と一体で形成しながらライン形状を有する予備ラインパターンを含む予備導電パターン148を形成する。

20

【0225】

前記下部層間絶縁膜142の上部面を所定の厚さ程除去する。前記下部層間絶縁膜142の部分的な除去はエッチバック工程を通じて遂行または湿式エッチング工程を通じて行われることができる。上述のように下部層間絶縁膜142を部分的に除去すれば、前記予備導電パターン148の上部が突出する。本発明の他の実施例によれば、前記下部層間絶縁膜142を追加で除去することができないこともあって、前記下部層間絶縁膜142を全部除去して上部面に前記エッチング阻止膜102が露出するようにすることもできる。

30

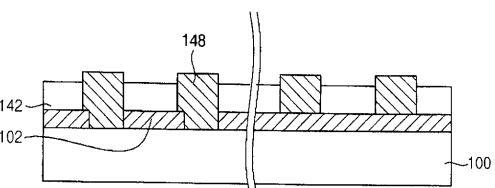

【0226】

図49を参照すれば、予備導電パターン148及び下部層間絶縁膜142上部面について金属膜(図示せず)を形成する。

30

【0227】

前記金属膜を熱処理して、前記金属膜及び前記金属膜と接触しているポリシリコンを反応させて金属シリサイドSを形成する。この時、前記金属膜及び予備導電パターン148が接触した部位が互いに反応して金属シリサイドSが形成される。その結果、前記金属シリサイドSを含む第1配線150が形成される。

40

【0228】

前記第1配線150は第1コンタクトホール143内部に満たされた第1コンタクトプラグ150aと、前記第1コンタクトプラグ150aと一体で形成された導電性ライン150bを含む。

【0229】

本発明の実施例において、前記下部層間絶縁膜142の上に突出している前記予備導電パターンの側壁及び上部面と前記金属膜が反応して金属シリサイドSが形成される。前記シリサイデーション工程条件を調節することによって前記金属シリサイドSの厚さを調節することができる。前記金属シリサイドSを形成するための熱処理工程は図9を参照して説明した工程と実質的に同一である。

【0230】

図50を参照すれば、前記第1配線150と前記下部層間絶縁膜142を覆う層間絶縁膜152を形成する。前記層間絶縁膜152はその上部面が前記第1配線150の上部ならばより高くなるように形成する。前記層間絶縁膜152を形成した後に、前記層間絶縁

50

膜 152 を平坦化させる工程が追加的に遂行されることがある。

【0231】

前記層間絶縁膜 152 上にフォトレジストパターン 154 を形成する。前記フォトレジストパターン 154 は第 2 コンタクトプラグが形成されなければならない部位のみを露出させる形状を有する。すなわち、前記フォトレジストパターン 154 はライン形状を有しない。

【0232】

前記フォトレジストパターン 154 により露出した部位の層間絶縁膜 152 をエッティングする。続いて、下部層間絶縁膜 142 及びエッティング阻止膜 102 をエッティングすることによって第 2 コンタクトホール 156 を形成する。その後、前記フォトレジストパターン 154 を除去する。

10

【0233】

再び、図 45 を参照すれば、前記第 2 コンタクトホール 156 の側壁に絶縁物質からなった内壁スペーサ 158 を形成する。前記第 2 コンタクトホール 156 内部に導電物質を埋め立てて、前記層間絶縁膜 152 の上部面が露出するように研磨することによって、第 2 コンタクトホール 156 に第 2 コンタクトプラグ 160 を形成する。

20

【0234】

上述した工程を行って、半導体装置の配線構造物を形成することができる。前記配線構造物は第 1 コンタクトプラグと導電性ラインが 1 回の蒸着工程及び研磨工程を通じて一体で形成されることがあるため、低い接触抵抗を有することができる。また、前記配線構造物に低抵抗を有する金属シリサイドが含まれているので、前記配線構造物の高さが低くなつても望む低い抵抗を確保することができる。

20

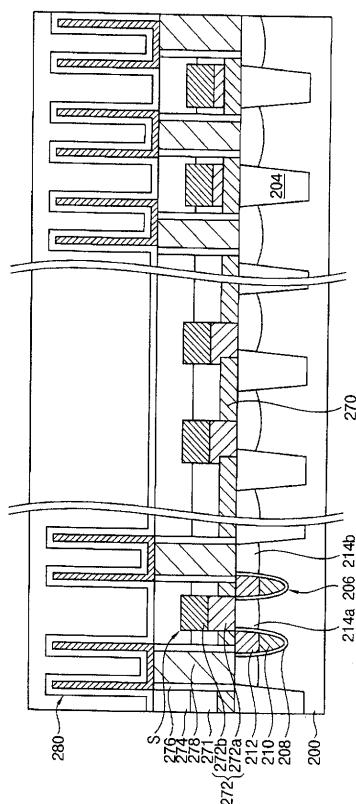

【0235】

図 51 は、図 44 及び図 45 に示した配線構造物を含む半導体装置の断面図である。

【0236】

図 51 を参照すれば、アクティブ領域及び素子分離領域が区分される基板 200 が設けられる。前記基板 200 には埋め立て型トランジスタが備えられる。前記埋め立て型トランジスタは、配線構造物を除けば図 16 を参照して説明した半導体装置と実質的に同じ構成を有する。

30

【0237】

前記基板 200、素子分離膜パターン 204 及び埋め立てゲート構造物の上部面にエッティング阻止膜 270 が備えられる。前記エッティング阻止膜 270 上には下部層間絶縁膜 271 が備えられる。前記エッティング阻止膜 270 には第 1 不純物領域 214a を露出する第 1 コンタクトホールが形成される。

30

【0238】

前記第 1 コンタクトホール内にはビットラインコンタクト 272a が備わって、前記ビットラインコンタクト 272a 上に前記ビットラインコンタクト 272a と一緒にビットライン 272b が備えられる。前記ビットライン 272b の少なくとも一部分は金属シリサイド S からなる。より具体的に、前記金属シリサイド S は、コバルトシリサイド、チタンシリサイド、タンタルシリサイド、ニッケルシリサイド、白金シリサイドなどからなることができる。これらは単独または 2 つ以上が混合されて使われることができる。また、前記ビットライン 272b 上にはハードマスクパターンが備えられない。

40

【0239】

前記ビットラインコンタクト 272a 及びビットライン 272b からなるビットライン構造物 272 は、図 44 を参照して説明した第 1 配線と実質的に同じ構成を有することができる。

【0240】

前記ビットライン構造物 272 の間を埋め立てながら、前記ビットライン構造物 272 を覆う層間絶縁膜 274 が備えられる。前記層間絶縁膜 274、下部層間絶縁膜 271 及びエッティング阻止膜 270 を貫通して基板 200 と接触するストレージノードコンタクト

50

278が配置される。前記ストレージノードコンタクト278の側壁には絶縁物質からなる内壁スペーサ276が備えられる。

【0241】

前記ストレージノードコンタクト278上にキャパシタ280が備えられる。前記キャパシタ280は高い蓄積容量を有するシリンドラ形状を有することができるが、スタック構造を有することもある。

【0242】

以下、図51に示した半導体装置の製造方法を説明する。

【0243】

先ず、図17及び図18を参照して説明した工程と実質的に同じ工程を行って基板200上に埋め立て型トランジスタを形成する。 10

【0244】

図46～図50を参照して説明した配線構造物を形成するための工程と実質的に同じ工程を行って、基板200上にビットライン構造物272及びストレージノードコンタクト278を形成する。 20

【0245】

前記ビットライン構造物272は前記配線構造物の第1配線を形成する工程を通じて形成される。この時、前記ビットライン構造物272は埋め立て型トランジスタの第1不純物領域214aと接触するように形成する。また、前記ストレージノードコンタクト278は前記配線構造物で第2コンタクトプラグを形成する工程を通じて形成される。この時、前記ストレージノードコンタクト278は第2不純物領域214bと接触するように形成される。 20

【0246】

その後、前記ストレージノードコンタクト278上にキャパシタ280を形成して図51に示した構成を有する半導体装置を製造する。

【0247】

図52は本発明のまた他の実施例に係る配線構造物を含む半導体装置を示す断面図である。図52に示した半導体装置は図45を参照して説明した配線構造物と実質的に同じ構造を有する配線構造物を含む。

【0248】

図52を参照すれば、アクティブ領域及び素子分離領域が区分される基板200を用意する。前記基板200にはプランナー型トランジスタが備えられる。前記プランナー型トランジスタは前述したプランナー型トランジスタと実質的に同じ構造を有する。 30

【0249】

前記基板200、素子分離膜パターン204及びゲート構造物を覆う第1下部層間絶縁膜258が備えられる。前記第1下部層間絶縁膜258を貫通して、前記第1及び第2不純物領域214a、214bと接触する第1及び第2コンタクトパッド260a、260bがそれぞれ形成される。

【0250】

前記第1下部層間絶縁膜258、第1及び第2コンタクトパッド260a、260b上にはエッチング阻止膜270及び第2下部層間絶縁膜271が備えられる。前記エッチング阻止膜270を貫通して前記第1コンタクトパッド260aの上部面を露出する第1コンタクトホールが形成されて、第2下部層間絶縁膜271には前記第1コンタクトホールと連係するライン形状のトレンチが形成される。 40

【0251】

前記第1コンタクトホール内部にはビットラインコンタクト272aが配置されて、前記ビットラインコンタクト272aと一体でビットライン272bが形成される。前記ビットラインコンタクト272aは前記第1コンタクトパッド260aの上部面と接触する。前記ビットライン272bは前記トレンチ内部を埋め立てながら、前記トレンチの上で突出することができる。これとは異なって、前記ビットライン272bは前記トレンチの 50

上に突出せずに、前記トレンチ上部と同じ上部面を有することもある。

【0252】

前記ビットライン272bの少なくとも一部分は金属シリサイドSからなる。例えば、前記金属シリサイドSはコバルトシリサイド、チタンシリサイド、タンタルシリサイド、ニッケルシリサイド、白金シリサイドなどからなることができる。これらは単独で形成または2つ以上が混合されて使われることができる。一方、前記ビットライン272b上にはハードマスクパターンが備えられない。

【0253】

前記ビットラインコンタクト272a及びビットライン272bからなるビットライン構造物272は図45を参照して説明した第1配線と実質的に同じ構成を有することができる。

10

【0254】

前記ビットライン構造物272aと下部層間絶縁膜271を覆う層間絶縁膜274が備えられる。前記層間絶縁膜274、下部層間絶縁膜271及びエッチング阻止膜270を貫通して前記第2コンタクトパッド260bに接触するストレージノードコンタクト278が備えられる。

【0255】

前記ストレージノードコンタクト278上にキャパシタ280が備えられる。前記キャパシタ280は高い蓄積容量を有するシリンドラ形状を有するかまたはスタック形状を有することができる。

20

【0256】

以下、図52に示した半導体装置の製造方法を説明する。

【0257】

先ず、図29を参照して説明した工程と実質的に同じ工程を行って基板200上にプランナー型のトランジスタを形成して、第1及び第2コンタクトパッドを形成する。

【0258】

図46～図50を参照して説明した配線構造物を形成するための工程と実質的に同じ工程を行って、基板200上にビットライン構造物272及びストレージノードコンタクト278を形成する。すなわち、前記ビットライン構造物272は前記配線構造物で第1配線を形成する工程を通じて形成される。この時、前記ビットライン構造物272は第1パッドコンタクト260aと接触するように形成する。また、前記ストレージノードコンタクト278は前記配線構造物で第2コンタクトプラグを形成する工程を通じて形成される。この時、前記ストレージノードコンタクト278は第2パッドコンタクト260bと接触するように形成する。

30

【0259】

その後、前記ストレージノードコンタクト278上にキャパシタ280を形成しても52に示した構成を有する半導体装置を製造する。

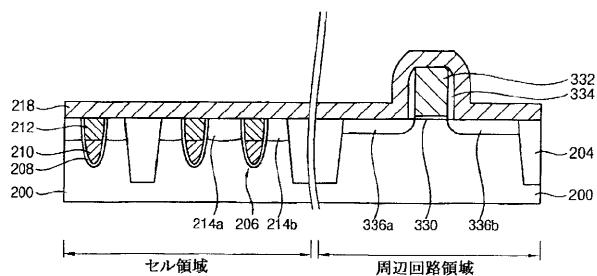

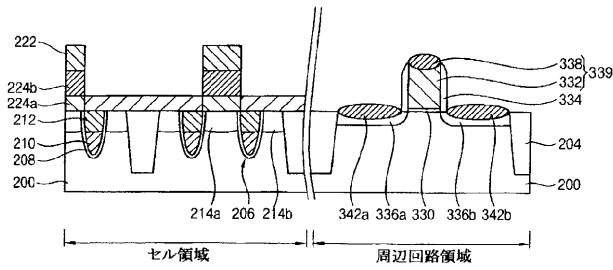

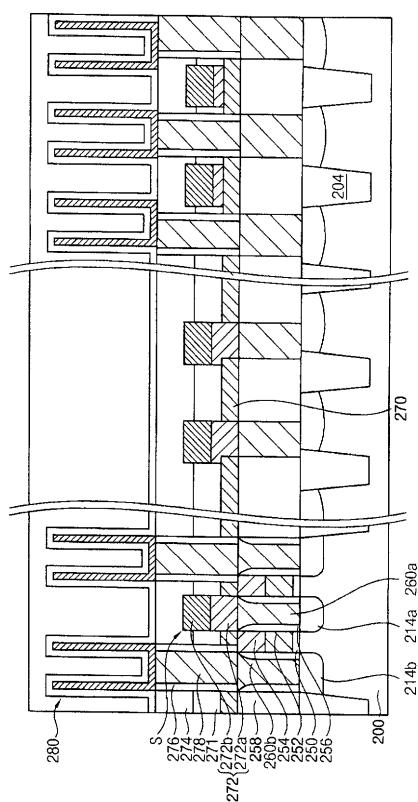

【0260】

上述したことにおいては、本発明の多様な実施例に係る配線構造物がDRAM装置のような半導体装置に適用することを例示したが、本発明の実施例に係る配線構造物はDRAM装置その他にもコンタクトプラグ及びラインパターンを含む多様な半導体装置の配線に適用することができる。

40

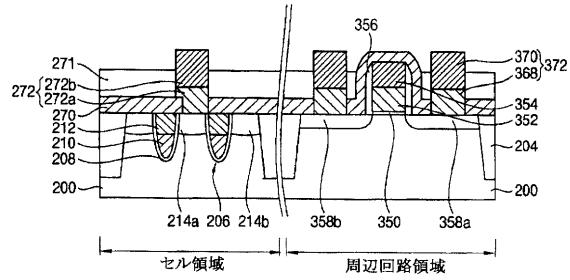

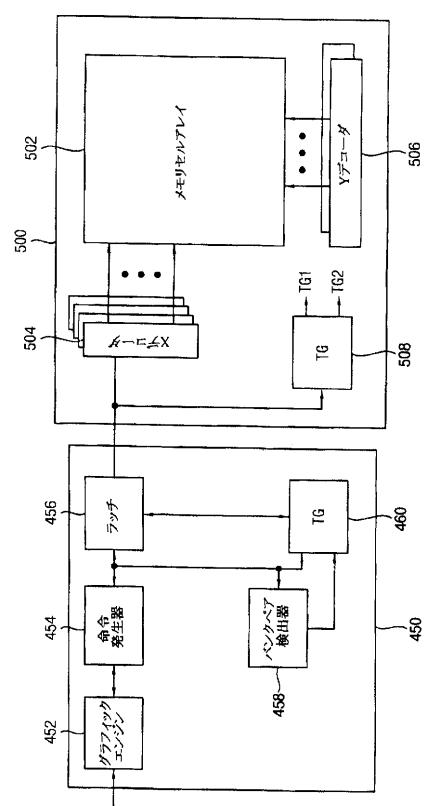

【0261】

図53は本発明のまた他の実施例に係る配線構造物を具備する半導体装置を示す断面図である。図53において、前記半導体装置のセル領域には図51に示したことと同じ構造のセルが配置される。また、前記半導体装置の周辺回路領域にはプランナー型のトランジスタが配置される。従って、前記半導体装置の周辺回路領域に備えられる素子を中心に説明する。

【0262】

前記周辺回路領域の基板200には素子分離領域及びアクティブ領域を区分する素子分

50

離膜パターン 204 が備えられる。前記アクティブ領域の基板 200 表面上にはゲート絶縁膜 250、第 2 ゲート電極 252 及びハードマスクパターン 254 が積層された第 2 ゲート構造物が備えられる。

【0263】

前記ゲート構造物側壁にはスペーサ 356 が備えられる。また、前記第 2 ゲート構造物両側の基板 200 表面下にソース / ドレーンで使われる第 3 及び第 4 不純物領域 358a、358b が備えられる。

【0264】

前記周辺回路領域の基板 200 表面、スペーサ 356 及び第 2 ゲート構造物上部面についてエッチング阻止膜 270 が備えられる。前記エッチング阻止膜 270 はセル領域に形成されたエッチング阻止膜と同じ物質からなることができる。

10

【0265】

前記セル領域と同一に前記周辺回路領域のエッチング阻止膜 270 上には下部層間絶縁膜 271 が備えられる。前記周辺回路領域には、前記下部層間絶縁膜 271 及びエッチング阻止膜 270 を貫通して前記第 3 及び第 4 不純物領域 358a、358b と接触するコンタクトパッド 372 が備えられる。

【0266】

前記コンタクトパッド 372 は前記下部層間絶縁膜 271 上部面で突出する形状を有する。これとは異なって、前記コンタクトパッド 372 の上部面が前記下部層間絶縁膜 271 の上部面と同じ平面にあることもできる。

20

【0267】

前記コンタクトパッド 372 は前記セル領域に形成されたピットラインコンタクト 272a 及びピットライン 272b と実質的に同じ積層構造を有する。すなわち、前記コンタクトパッド 372 は少なくとも一部分が金属シリサイド 370 からなる。図示したように、前記コンタクトパッド 372 はポリシリコン 368 及び金属シリサイド 370 が積層された形状を有することができる。これと共に、前記コンタクトパッド 372 に金属シリサイドが含まれることによって、前記コンタクトパッド 372 は低い抵抗を有することができる。

【0268】

前記セル領域と同一に前記下部層間絶縁膜 271 上には前記コンタクトパッド 372 を覆う層間絶縁膜 274 が備えられる。前記周辺回路領域の層間絶縁膜 274 上には上部層間絶縁膜 374 が備えられる。

30

【0269】

図 54 ~ 図 57 は、図 53 に示した半導体装置の製造方法を説明するための断面図である。

【0270】

図 54 を参照すれば、セル領域及び周辺回路領域が区分された基板 200 にトレンチ素子分離工程を行って素子分離膜パターン 204 を形成する。

【0271】

図 17 及び図 18 を参照して説明した工程と実質的に同じ工程を行って、前記セル領域の基板 200 に埋め立てされたゲートを含む選択トランジスタを形成する。

40

【0272】

前記選択トランジスタを形成した後、前記周辺回路領域の基板 200 上にゲート絶縁膜 350、ポリシリコン膜パターン 352 及びハードマスクパターン 354 が積層されたゲート構造物を形成する。前記ゲート構造物両側壁にスペーサ 356 を形成する。前記ゲート構造物両側の基板表面下へ不純物を注入して第 3 及び第 4 不純物領域 358a、358b を形成する。その結果、前記周辺回路領域の基板にはゲート構造物、スペーサ 356、第 3 及び第 4 不純物領域 358a、358b を含む周辺回路用トランジスタが形成される。

【0273】

50

前記セル領域及び周辺回路領域の基板上にエッチング阻止膜270を形成する。すなわち、前記セル領域に形成されたエッチング阻止膜270は前記埋め立てされたゲートを含む選択トランジスタを覆う。また、前記周辺回路領域に形成されたエッチング阻止膜270は前記予備トランジスタを覆う。

【0274】

前記エッチング阻止膜270上に下部層間絶縁膜271を形成する。前記下部層間絶縁膜271を形成した後前記下部層間絶縁膜271の表面を研磨して、前記周辺回路領域に形成された前記エッチング阻止膜270の上部面が露出するようにする。

【0275】

図55を参照すれば、前記下部層間絶縁膜271及びエッチング阻止膜270を写真工10

ッチング工程でエッチングして前記セル領域の第1不純物領域214aの基板を露出させる第1コンタクトホール360を形成する。

【0276】

前記第1コンタクトホール360を形成するためのエッチング工程において、前記周辺回路領域の第3及び第4不純物領域358a、358bを各々露出する第2コンタクトホール362が同時に形成される。また、前記第1及び第2コンタクトホール360、362内部に犠牲膜パターン(図示せず)を形成する。

【0277】

前記下部層間絶縁膜271を部分的にエッチングして前記第1コンタクトホール360と連通しながらライン形状で延長するトレンチ364を形成する。前記トレンチ364を形成した後、前記第1及び第2コンタクトホール360、362内部に位置する犠牲膜パターン(図示せず)を除去する。

【0278】

図56を参照すれば、前記第1コンタクトホール360、トレンチ364及び第2コンタクトホール362を埋め立てながら前記下部層間絶縁膜271の表面を覆うポリシリコン膜(図示せず)を形成する。前記ポリシリコン膜を研磨することによって、前記第1コンタクトホール360、トレンチ364及び第2コンタクトホール362内部に各々第1ないし第3ポリシリコンパターン366a、366b、366cを形成する。

【0279】

前記第1～第3ポリシリコンパターン366a、366b、366cの上部側壁の一部が外部に露出するように前記下部層間絶縁膜271の上部を除去する。このような除去工程は湿式エッチング工程を通じて遂行されることができる。

【0280】

図57を参照すれば、前記下部層間絶縁膜271の上部面、露出した第1～第3ポリシリコンパターン366a、366b、366c、及びエッチング阻止膜270について金属膜(図示せず)を形成する。

【0281】

前記金属膜を熱処理して前記セル領域及び周辺回路領域に形成された第1ないし第3ポリシリコンパターン366a、366b、366cの少なくとも一部分をシリサイデーションさせる。その結果、前記セル領域にはピットラインコンタクト272a及び前記ピットライン272bが積層されて金属シリサイドSを含むピットライン構造物272が形成される。一方、前記周辺回路領域には金属シリサイド370を含むコンタクトパッド372が形成される。前記シリサイデーション工程の工程条件を調節することによって、前記ピットライン構造物272及びコンタクトパッド372に形成される金属シリサイドの厚さを調節することができる。

【0282】

上述のように、本発明の実施例によれば、1回のシリサイデーション工程を通じて金属シリサイドSを含むピットライン構造物及び周辺回路用トランジスタのソース/ドレーンと電気的に連結されるコンタクトパッド372を同時に形成することができる。

【0283】

10

20

30

40

50

その後、反応せずに残っている金属膜を除去する。

【0284】

再び、図53を参照すれば、前記ビットライン構造物272及びコンタクトパッド372を覆う層間絶縁膜274を形成する。前記層間絶縁膜274を貫通して前記セル領域の第2不純物領域214bと電気的に連結されるコンタクトプラグ278を形成する。

【0285】

前記周辺回路領域を覆う上部層間絶縁膜374を形成する。また、前記セル領域には前記ストレージノードコンタクト234と接続するようキャパシタ240を形成する。キャパシタ204はシリンドラ構造または積層構造を有することができる。

【0286】

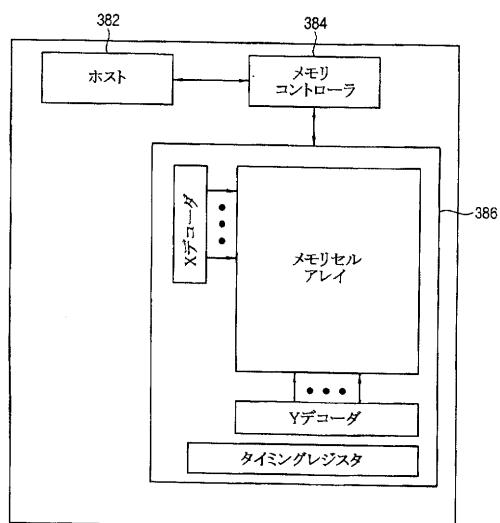

図58は本発明の実施例に係る半導体装置を含むメモリシステムの概略的なブロック図である。

【0287】

図58を参照すれば、前記メモリシステムは、ホスト(host)382、メモリコントローラ(memory controller)384、及びDRAM装置のような半導体装置386を具備する。

【0288】

前記メモリコントローラ384は、ホスト382と半導体装置386の間のインターフェースの役割をして、バッファメモリを含む。図示はしていないが、前記メモリコントローラ384は、CPU、ROM、RAM、及びインターフェースブロックをさらに含むことができる。

【0289】

前記半導体装置386はメモリセルアレイ(memory cell array)、Xデコーダ(Decoder)、Yデコーダ、及びタイミングレジスタ(timing resistor)を含む。

【0290】

前記ホスト382からデータ、アドレス信号、及び書き込み命令(write command)がメモリコントローラ384に入力され、前記メモリコントローラ384では入力された命令によってデータが半導体装置386のメモリセルアレイに使われるよう制御する。また、メモリコントローラ384は、ホスト382から入力される読み取り命令(read command)により、前記メモリセルアレイに保存されているデータが読まれるように半導体装置386を制御する。

【0291】

前記半導体装置386のメモリセルアレイは複数のメモリセルから構成される。前記Xデコーダは、ワードラインと連結されている。前記Yデコーダはビットラインと連結されている。前記Xデコーダはメモリコントローラ384からXアドレス(address)の入力を受けてこれをデコーディングして、1つのワードラインを選択し、前記Yデコーダはメモリコントローラ384からYアドレスの入力を受けてこれをデコーディングして1つのビットラインを選択する。

【0292】

前記メモリシステムに含まれる半導体装置386は前述した本発明の多様な実施例の中のいずれか一つと同じ構成を有することができる。上述のように、前記半導体装置386が高集積化され高性能化されることによって、前記メモリシステムが集積化され向上した性能を有することができる。

【0293】

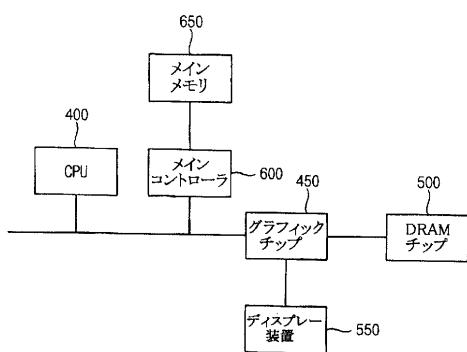

図59は本発明の実施例に係る半導体チップを含むグラフィックシステムの概略的なブロック図である。図60は図59に例示されたグラフィックチップ及び半導体チップの概略的なブロック図である。

【0294】

図59を参照すれば、前記グラフィックシステムはCPU400、グラフィックチップ

10

20

30

40

50

(graphic chip) 450、半導体チップ500、ディスプレー装置550、メモリ制御器(memory controller)600、及びメインメモリ(main memory)650を含む。

【0295】

CPU400は、グラフィックチップ450に対して原始的な命令(original command)を伝送する。グラフィックチップ450は原始的な命令を解釈して、DRAMチップ500に対して遠視命令に対応する命令及びデータビットを発行する。また、グラフィックチップ450は、ディスプレー装置550が前記半導体チップ500で判読されたデータをディスプレーするように制御する。

【0296】

図60に示したように、前記グラフィックチップ450は、グラフィックエンジン452、命令発生器454、ラッチ(latch)456、バンクペア検出器(bank-pair Detector)458、及びタイミング発生器460を含む。前記グラフィックチップ450が遠視命令を受信する時、グラフィックエンジン452は、グラフィックデータを発生させる。これに応じて、前記命令発生器454は、グラフィックデータによりデータを半導体チップ500に記入するための命令を発生させる。発生した命令は、ラッチ456、バンク-対検出器458、及びタイミング発生器460に伝達される。

【0297】

前記半導体チップ500は、Xデコーダ504、タイミング発生器508、メモリセルアレイ502、Yデコーダ506を含む。メモリセルアレイ502の各々はビットライン及びワードラインに接続された複数のセルを含む。Xデコーダ504は、前記ワードラインに結合される一方、Yデコーダ506は前記ビットラインに結合される。

【0298】

Xデコーダ504は、ラッチ456により発行された現在の命令をデコーディングし、次いで、それぞれのワードラインを活性化させる。Yデコーダ506は現在の命令をデコーディングし、それぞれのビットラインを活性化させる。タイミング発生器508は現在の命令に対応するバンクペアを明示し、タイミング信号を発生させる。

【0299】

前記グラフィックシステムに含まれる半導体チップ500は本発明の多様な実施例のうちのいずれか一つの半導体装置と同じ構成を有する。このように、前記半導体チップ500が高集積化され高性能化されることによって、前記半導体チップ500が含まれた前記グラフィックシステムが集積化され向上した性能を有することができる。

【産業上の利用可能性】

【0300】

上述のように、本発明の実施例に係る配線構造物はコンタクトプラグ及び前記コンタクトプラグと接触するラインパターンを含む。それによって、前述した構造の配線が要求される多様な半導体装置に適用することができる。

【符号の説明】

【0301】

- 10 トランジスタ

- 240、280 キャパシタ

- 100、200 基板

- 102 絶縁膜

- 104、143、219 第1コンタクトホール

- 106、220 ポリシリコン膜

- 108 ハードマスクパターン

- 109 予備導電パターン

- 109a 予備コンタクトプラグ

- 109b 予備ラインパターン

- 110、150 第1配線

10

20

30

40

50

1 1 0 a、1 5 0 a 第1コンタクトプラグ

1 1 0 b、1 5 0 b 第1導電性ライン

1 1 2、3 0 8、3 4 0 金属膜

1 1 6、2 2 6 層間絶縁膜

1 2 0、2 2 8 フォトレジストパターン

1 2 2、1 5 6、2 3 0 第2コンタクトホール

1 2 4、2 3 2 内壁スペーサ

1 2 6、1 6 0、3 1 2 第2コンタクトプラグ

2 0 2 素子分離用トレンチ

2 0 4 素子分離膜パターン

1 4 6、2 0 6 トレンチ

2 0 8、2 5 0 ゲート酸化膜

2 1 0、2 5 2 導電膜パターン

2 1 4 a、2 1 4 b 不純物領域

1 0 2、2 1 8、2 7 0 エッチング阻止膜

2 2 4 ビットライン構造物

2 2 4 a、2 7 2 a ビットラインコンタクト

2 2 2、2 2 4 b、2 7 2 b ビットライン

2 3 4、2 7 8 ストレージノードコンタクト

2 3 5 絶縁パターン

2 5 6、3 3 4 スペーサ

2 6 0 a 第1コンタクトパッド

2 6 0 b 第2コンタクトパッド

3 0 4、3 3 9 第2ゲート電極

3 3 6 a 第3不純物領域

3 3 6 b 第4不純物領域

3 3 8、3 4 2 a、3 4 2 b 金属シリサイド

A アクティブ領域

S 金属シリサイド

10

20

【図 1】

【図 2】

【図 3】

【図 4】

【図 5】

【図 6】

【図 9】

【図 7】

【図 10】

【図 8】

【図 1 1】

【図 1 3】

【図 1 2】

【図 1 4】

【図 1 5】

【図 16】

【図 17】

【図 18】

【図 19】

【図 2 0】

【図 2 1】

【図 2 2】

【図 2 3】

【図24】

【図25】

【図26】

【図27】

【 図 2 8 】

【 図 2 9 】

【図30】

【 図 3 1 】

【図 3 2】

【図 3 4】

【図 3 3】

【図 3 5】

【図 3 6】

【図 3 8】

【図 3 7】

【図 3 9】

【図 4 0】

【図 4 2】

【図 4 1】

【図 4 3】

【図 4 4】

【図 4 6】

【図 4 7】

【図 4 8】

【図 4 5】

【図 4 9】

【図 5 0】

【図 5 1】

【図 5 2】

【図 5 3】

【図 5 4】

【図 5 5】

【図 5 7】

【図 5 6】

【図 5 8】

【図 5 9】

【図 6 0】

## フロントページの続き

(51) Int.CI. F I テーマコード(参考)

H 01 L 23/52 (2006.01)

(72)発明者 李 殷沃

大韓民国京畿道華城市盤松洞(番地なし) 示範ハンビッマウルグムホオウリムアパート242棟

3004号

(72)発明者 金 大容

大韓民国京畿道龍仁市豊徳川洞(番地なし) ジンサンマウル518棟801号

(72)発明者 崔 吉鉉

大韓民国ソウル特別市江南区大峙1洞(番地なし) チョンシリアパート15棟802号

(72)発明者 金 秉熙

大韓民国ソウル特別市瑞草区方背4洞(番地なし) 方背現代アパート106棟901号

F ターム(参考) 5F033 HH04 HH25 HH27 HH30 JJ01 JJ04 JJ25 JJ27 JJ30 KK01

MM05 MM10 NN07 NN13 NN15 NN40 PP19 QQ08 QQ09 QQ21

QQ25 QQ28 QQ30 QQ37 QQ47 QQ48 QQ70 QQ84 RR04 RR06

SS10 TT07 VV16 XX09 XX10 XX15 XX33 XX34

5F083 AD04 AD24 AD48 AD49 GA02 JA02 JA35 JA39 JA40 KA01

KA05 LA21 MA06 MA17 MA20 PR10 PR40 ZA04