(19) 日本国特許庁(JP)

## (12) 公表特許公報(A)

(11) 特許出願公表番号

特表2004-500718

(P2004-500718A)

(43) 公表日 平成16年1月8日(2004.1.8)

(51) Int.Cl.<sup>7</sup>

H01L 23/50

F1

H01L 23/50

R

テーマコード(参考)

5FO67

審査請求 有 予備審査請求 有 (全 48 頁)

|               |                              |          |                                                                                               |

|---------------|------------------------------|----------|-----------------------------------------------------------------------------------------------|

| (21) 出願番号     | 特願2001-573521 (P2001-573521) | (71) 出願人 | 502354708<br>エイティーエス・サービス、カンパニー<br>アメリカ合衆国カリフォルニア州95050, サンタクララ, スイート・エイ, シビック・センター・ドライブ・1680 |

| (86) (22) 出願日 | 平成13年3月30日 (2001.3.30)       | (74) 代理人 | 100087642<br>弁理士 古谷 聰                                                                         |

| (85) 翻訳文提出日   | 平成14年9月30日 (2002.9.30)       | (74) 代理人 | 100063897<br>弁理士 古谷 韶                                                                         |

| (86) 國際出願番号   | PCT/US2001/010390            | (74) 代理人 | 100076680<br>弁理士 溝部 孝彦                                                                        |

| (87) 國際公開番号   | W02001/075938                | (74) 代理人 | 100121061<br>弁理士 西山 清春                                                                        |

| (87) 國際公開日    | 平成13年10月11日 (2001.10.11)     |          |                                                                                               |

| (31) 優先権主張番号  | 60/193,319                   |          |                                                                                               |

| (32) 優先日      | 平成12年3月30日 (2000.3.30)       |          |                                                                                               |

| (33) 優先権主張国   | 米国(US)                       |          |                                                                                               |

| (31) 優先権主張番号  | 09/668,423                   |          |                                                                                               |

| (32) 優先日      | 平成12年10月6日 (2000.10.6)       |          |                                                                                               |

| (33) 優先権主張国   | 米国(US)                       |          |                                                                                               |

最終頁に続く

(54) 【発明の名称】オプションで窓となる蓋を備えるリードレス半導体製品パッケージング装置とその組み立て方法

## (57) 【要約】

天然資源を保全し環境に優しくコスト効率が良いリードレス半導体パッケージング装置(1000)は、優れた機械的かつ電気的特性を持ち、また独特な密封と内部のパッケージされた半導体集積回路(チップ/ダイ)(40)を見る機構を与えており、オプションの窓のあるハウジングを持つ。特にスタンプされかつ/または曲げ加工されたリードフレーム(30, 41)は、モールドを使う独特の圧縮モールディング工程の間、重合体材料(12)によりパッケージされ、特に関連技術で共通の"オーバーパッケージング"問題を避けるために形作られる。特別に形作られたモールドは、外部ポーションがプリント回路基板上のパッドに接触する有効なはんだ付け領域として、リードフレームの外部ポーションから内部ポーションの輪郭描写を容易にする。それゆえに、困難で環境に優しくないマスキング段階とデフラッシング段階を回避し、デバイスパッケージング工程を簡略化する。圧縮成型は、効果的に圧縮力のある密封開口部を供給し、そこからリードフレームの有効なはんだ付け可能領域は拡張し露出する場合があり、このように、リード

**【特許請求の範囲】****【請求項 1】**

半導体回路をパッケージングするためのリードレス半導体製品パッケージング装置であつて、

a. リードフレームであつて、

前記リードフレームが内部リードポーションと外部リードポーションを持ち、電気的に前記半導体回路と接合し、リードフレーム材をスタンピングすることにより形成されるリードフレームと、

b. ハウジングメンバーであつて、

前記ハウジングメンバーがハウジング材を含み、前記ハウジング材は外部リードポーションがはんだ付け可能領域を与えるため露出されるように前記リードフレームを保護するハウジングメンバーとを含むリードレス半導体製品パッケージング装置。

**【請求項 2】**

前記半導体回路であつて、

a. 少なくとも 1 つのダイ取り付けパッドであつて、前記半導体回路が前記ダイ取り付けパッド上に実装されている、少なくとも 1 つのダイ取り付けパッドと、

b. 少なくとも 1 つのワイヤであつて、前記少なくとも 1 つのワイヤは、前記回路と前記内部リードポーション間の電気的接続をもたらすようにワイヤで結合され、前記少なくとも 1 つのワイヤは、実質的に銅、アルミニウム、金を含む電気伝導性物質のグループから選択された電気伝導性物質から形成される少なくとも 1 つのワイヤと、を含む半導体回路を含み、

ハウジング材が、前記ダイ取り付けパッド、前記少なくとも 1 つのワイヤ、及び前記内部リードポーションを取り囲んで更に圧縮成型され、

ハウジング材が、前記外部リードポーションを取り囲んで圧縮成型されておらず、

前記スタンプされたリードフレームが、チップサイズからチップサイズに近い範囲で、前記リードレス半導体製品パッケージング装置に適合しやすいうように所望の構造に機械的に曲げられる、請求項 1 に記載されたリードレス半導体製品パッケージング装置。

**【請求項 3】**

前記リードフレーム材の厚さが 6 ミル以下の範囲である、請求項 2 に記載のリードレス半導体製品パッケージング装置。

**【請求項 4】**

前記リードフレーム材の厚さが 6 ミル以下の範囲である、請求項 1 に記載のリードレス半導体製品パッケージング装置。

**【請求項 5】**

前記リードレス半導体製品であつて、

a. 少なくとも 1 つのダイ取り付けパッドであつて、前記半導体回路が前記ダイ取り付けパッド上に実装されている、少なくとも 1 つのダイ取り付けパッドと、

b. 少なくとも 1 つのワイヤであつて、前記少なくとも 1 つのワイヤは、前記回路と前記内部リードポーション間の電気的接続をもたらすようにワイヤで結合され、前記少なくとも 1 つのワイヤは、実質的に銅、アルミニウム、金を含む電気伝導性物質のグループから選択された電気伝導性物質から形成される少なくとも 1 つのワイヤと、を含むリードレス半導体製品を含み、

ハウジング材が、前記ダイ取り付けパッド、前記少なくとも 1 つのワイヤ、及び前記内部リードポーションを取り囲んで更に圧縮成型され、

ハウジング材が、前記外部リードポーションを取り囲んで圧縮成型されておらず、

前記スタンプされたリードフレームが、チップサイズからチップサイズに近い範囲で、前記リードレス半導体製品パッケージング装置に適合しやすいうように所望の構造に機械的に曲げられる、請求項 4 に記載されたリードレス半導体製品パッケージング装置。

**【請求項 6】**

a. 窓となる蓋のメンバーであつて、

10

20

30

40

50

前記窓となる蓋のメンバーが前記ハウジングメンバーの一部を形成し、前記窓となる蓋のメンバーが本質的にポリマーやガラスを含む視覚的に透明なグループから選択された、視覚的に透明な物質から形成される、窓となる蓋のメンバーと、

b . 密封剤と、

c . 密封シートであって、

前記密封シートが、より大きな密封された表面積を与るために前記ハウジングメンバーの上面に配置された少なくとも1つの溝を含み、汚染物質の入場を防止するため前記1つの溝の中のハウジングメンバーと前記窓となる蓋のメンバー間に密封剤が置かれる密封シートとを更に含む請求項1に記載のリードレス半導体製品パッケージング装置。

【請求項7】

ダイが、前記リードフレームの前記内部ポーションの各々に電気伝導性のないポリマーにより取り付け可能である請求項2に記載のリードレス半導体製品パッケージング装置。

【請求項8】

ダイが、前記リードフレームの前記内部ポーションの各々に電気伝導性のないポリマーにより取り付け可能である請求項5に記載のリードレス半導体製品パッケージング装置。

【請求項9】

前記ハウジング材は重合体のモールディング化合物を含み、前記ハウジングメンバーは圧縮成型された前記ハウジング材を含み、それによって前記外部リードポーションは露出され、それにより前記外部リードポーション上のはんだ付け可能部分は保護され、それにより前記外部リードポーションのディフラッシングを避けることができる、請求項1に記載のリードレス半導体製品パッケージング装置。

【請求項10】

前記リードフレームは、実質的に銅、アルミニウム、金を含む電気伝導性物質のグループから選択された少なくとも1つの電気伝導性物質から形成され、前記ハウジング材は、実質的にポリマーとセラミックを含むハウジング材のグループから選択された少なくとも1つの材料を含み、前記ポリマーは、実質的にエポキシ、ポリイミド、及びビスマレイミドを含むポリマーのグループから選択される、請求項1に記載のリードレス半導体製品パッケージング装置。

【請求項11】

半導体回路をパッケージングするためのリードレス半導体製品パッケージング装置を組み立てる方法であって、

a . リードフレームであって、

前記リードフレームは、内部リードポーションと外部リードポーションを持ち、前記リードフレームは、電気的に前記半導体回路と接合し、

前記リードフレームは、リードフレーム材をスタンピングすることにより形成される、リードフレームを供給する段階と、

b . ハウジングメンバーであって、

前記ハウジングメンバーは、ハウジング材を含み、

前記ハウジング材は、外部リードポーションがはんだ付け可能領域を与えるため露出されるように前記リードフレームを保護し、それにより前記リードレス半導体製品パッケージング装置を形成する、ハウジングメンバーを供給する段階とを含むリードレス半導体製品パッケージング装置を組み立てる方法。

【請求項12】

前記リードレス半導体回路であって、

a . 少なくとも1つのダイ取り付けパッドであって、前記半導体回路が前記ダイ取り付けパッド上に実装されている、少なくとも1つのダイ取り付けパッドと、

b . 少なくとも1つのワイヤであって、前記少なくとも1つのワイヤは、前記回路と前記内部リードポーション間の電気的接続をもたらすようにワイヤで結合され、前記少なくとも1つのワイヤは、実質的に銅、アルミニウム、金を含む電気伝導性物質のグループから選択された電気伝導性物質から形成される少なくとも1つのワイヤとを含むリードレス半

10

20

30

40

50

導体回路を含み、

ハウジング材が、前記ダイ取り付けパッド、前記少なくとも1つのワイヤ、及び前記内部リードポーションを取り囲んで更に圧縮成型され、

ハウジング材が、前記外部リードポーションを取り囲んで圧縮成型されておらず、前記スタンプされたリードフレームが、チップサイズからチップサイズに近い範囲で、前記リードレス半導体製品パッケージング装置に適合しやすいうように所望の構造に機械的に曲げられ、それゆえにリードレス半導体製品パッケージング装置を形成する、請求項11に記載のリードレス半導体製品パッケージング装置を組み立てる方法。

【請求項13】

リードフレーム材の厚さが6ミル以下の範囲である、請求項12に記載のリードレス半導体製品パッケージング装置を組み立てる方法。 10

【請求項14】

リードフレーム材の厚さが6ミル以下の範囲である、請求項11に記載のリードレス半導体製品パッケージング装置を組み立てる方法。

【請求項15】

前記リードレス半導体回路であって、

a. 少なくとも1つのダイ取り付けパッドであって、前記少なくとも1つの半導体回路が前記ダイ取り付けパッド上に実装されている、少なくとも1つのダイ取り付けパッドと、

b. 少なくとも1つのワイヤであって、前記少なくとも1つのワイヤは、前記回路と前記内部リードポーション間の電気的接続をもたらすようにワイヤで結合され、前記少なくとも1つのワイヤは、実質的に銅、アルミニウム、金を含む電気伝導性物質のグループから選択された電気伝導性物質から形成される少なくとも1つのワイヤとを含むリードレス半導体回路を含み、 20

ハウジング材が、前記ダイ取り付けパッド、前記少なくとも1つのワイヤ、及び前記内部リードポーションを取り囲んで更に圧縮成型され、

ハウジング材が、前記外部リードポーションを取り囲んで圧縮成型されておらず、前記リードフレームが、チップサイズからチップサイズに近い範囲で、前記リードレス半導体製品パッケージング装置に適合しやすいうように所望の構造に機械的に曲げられ、それゆえにリードレス半導体製品パッケージング装置を形成する、請求項14に記載のリードレス半導体製品パッケージング装置を組み立てる方法。 30

【請求項16】

a. 窓となる蓋のメンバーであって、

前記窓となる蓋のメンバーが前記ハウジングメンバーの一部を形成し、前記窓となる蓋のメンバーが本質的にポリマー ガラスを含む視覚的に透明なグループから選択された、視覚的に透明な物質から形成される窓となる蓋のメンバーを供給する段階と、

b. 密封剤を供給する段階と、

c. 密封シートであって、

より大きな密封された表面積を与えるために前記ハウジングメンバーの上面上に配置された少なくとも1つの溝を含み、汚染物質の入場を防止するため前記1つの溝の中のハウジングメンバーと前記窓となる蓋のメンバー間に密封剤が置かれ、それゆえに前記リードレス半導体製品パッケージング装置を形成する、密封シートを供給する段階とを更に含む請求項14に記載のリードレス半導体製品パッケージング装置を組み立てる方法。 40

【請求項17】

前記リードフレームの各々の前記内部ポーションに電気伝導性の無いポリマーによりダイが取り付け可能である請求項12に記載のリードレス半導体製品パッケージング装置を組み立てるための方法。

【請求項18】

前記リードフレームの各々の前記内部ポーションに電気伝導性の無いポリマーによりダイが取り付け可能である請求項15に記載のリードレス半導体製品パッケージング装置を組み立てるための方法。 50

## 【請求項 19】

前記ハウジング材は重合体のモールディング化合物を含み、前記ハウジングメンバーは圧縮成型された前記ハウジング材を含み、それによって前記外部リードポーションは露出され、それにより前記外部リードポーション上のはんだ付け可能部分は保護され、それにより前記外部リードポーションのディフラッシングを避けることができる、請求項 11 に記載のリードレス半導体製品パッケージング装置を組み立てるための方法。

## 【請求項 20】

前記リードフレームは電気伝導性物質から形成され、前記電気伝導性物質は銅を含み、前記ハウジング材は、実質的にポリマーとセラミックを含むハウジング材のグループから選択された少なくとも 1 つの材料を含み、前記ポリマーは、実質的にエポキシ、ポリイミド、及びビスマレイミドを含むポリマーのグループから選択される、請求項 11 に記載のリードレス半導体製品パッケージング装置を組み立てるための方法。

10

## 【請求項 21】

少なくとも 1 つの半導体回路をパッケージングするために少なくとも 1 つのリードレス半導体製品パッケーニング装置を組み立てるための方法で、

a . 少なくとも 1 つのスタンプされたリードフレームを供給するためにリードフレーム材をスタンピングし、前記リードフレームは 6 ミル以下の範囲の厚さを持ち、前記少なくとも 1 つのスタンプされたリードフレームは内部リードポーションと外部リードポーションを持つ段階と、

20

b . 前記少なくとも 1 つのリードフレームの各々に対して、前記ダイを前記内部リードポーションに取り付けるため、ダイと前記内部リードポーション間のインターフェースに電気伝導性の無い接着剤を供給する段階と、

c . 前記少なくとも 1 つのスタンプされたリードフレームの各々に対して、前記電気伝導性の無い接着剤を硬化する段階と、

d . 前記少なくとも 1 つのスタンプされたリードフレームの各々に対してワイヤを供給し、前記ワイヤは第 1 と第 2 の終端を持ち、前記第 1 のワイヤの終端は前記ダイに接合し、前記第 2 のワイヤの終端は前記リード内部ポーションに接合する段階と、

e . 前記少なくとも 1 つのスタンプされたリードフレームの各々に対して、ハウジングメンバーを形成するためにホットプレスを使って、モールド中の前記リード内部ポーションを取り囲むハウジング材を成型し、前記モールドは、上側ポーションと下側ポーションを有し、前記ホットプレスは、お互いに平行である上側のプラテンと下側のプラテンを有し、前記上側のモールドポーションは前記上側のプラテン上に内部へ配置され、前記下側のモールドポーションは前記下側のプラテン上に内部へ配置され、前記リード内部ポーションは前記ダイに取り付けられ、前記下側のモールドポーションに対して、前記上側のモールドポーションを、各々、圧縮している前記プラテンに垂直方向に前記上側のホットプレスプラテンと前記下側のホットプレスプラテンが一緒に変形され、それによって、外部リードポーション上にわずかに局所化された変形を発生させるため前記外部リードポーション上に前記モールドポーションにより圧縮力が加えられ、それによって、前記内部リードポーションと前記外部リードポーション間の密封が、前記圧縮力と前記わずかに局所化された変形を通してたらされ、それによって、前記ハウジング材は前記モールド内で硬化され、それによって、前記ハウジングメンバーを形成し、それによって、前記少なくとも 1 つのリードレス半導体製品パッケーニング装置を形成する段階と、

30

f . レーザーにより、前記少なくとも 1 つの形成されたリードレス半導体製品パッケージング装置の各々の前記外部リードポーションにマーキングする段階と、

g . お互いから、前記少なくとも 1 つの形成されたリードレス半導体製品パッケージング装置の各々の前記外部リードポーションをシンギュレートする段階と、h . 前記シンギュレートされた前記少なくとも 1 つのリードレス半導体製品パッケージング装置をパックする段階と、

i . パックされたリードレス半導体製品パッケージング装置を出荷する段階とを含む方法。

40

## 【請求項 2 2】

前記リードフレームが、チップサイズからチップサイズに近い範囲で、前記リードレス半導体製品パッケージング装置に適合しやすいうように所望の構造に機械的に曲げられる、請求項 2 1 に記載された少なくとも 1 つの半導体回路をパッケージングするための少なくとも 1 つのリードレス半導体製品パッケージング装置を組み立てる方法。

## 【請求項 2 3】

少なくとも 1 つの半導体回路をパッケージングするために少なくとも 1 つの窓のあるリードレス半導体製品パッケージング装置を組み立てるための方法で、

a . 少なくとも 1 つのスタンプされたリードフレームを供給するためにリードフレーム材をスタンピングし、前記リードフレームは 6 ミル以下の範囲の厚さを持ち、前記少なくとも 1 つのスタンプされたリードフレームは内部リードポーションと外部リードポーションを持つ段階と、

b . 前記少なくとも 1 つのスタンプされたリードフレームをプリプレーティングする段階と、

c . 前記少なくとも 1 つのスタンプされたリードフレームの各々に対して、ハウジングメンバーを形成するためにホットプレスを使って、モールド中の前記リード内部ポーションを取り囲むハウジング材を成型し、前記モールドは、上側ポーションと下側ポーションを有し、前記上側のモールドポーションは見える蓋を収容するためのモールドラインを持ち、前記ホットプレスは、お互いに平行である上側のプラテンと下側のプラテンを有し、前記上側のモールドポーションは前記上側のプラテン上に内部へ配置され、前記下側のモールドポーションは前記下側のプラテン上に内部へ配置され、前記リード内部ポーションは前記ダイに取り付けられ、前記下側のモールドポーションに対して、前記上側のモールドポーションを、各々、圧縮している前記プラテンに垂直方向に前記上側のホットプレスプラテンと前記下側のホットプレスプラテンが一緒に変形され、それによって、外部リードポーション上にわずかに局所化された変形を発生させるため前記外部リードポーション上に前記モールドポーションにより圧縮力が加えられ、それによって、前記内部リードポーションと前記外部リードポーション間の密封が、前記圧縮力と前記わずかに局所化された変形を通してたらされ、それによって、前記ハウジング材は前記モールド内で硬化され、それによって、前記ハウジングメンバーを形成し、それによって、前記少なくとも 1 つのリードレス半導体製品パッケージング装置を形成する段階と、

d . 前記少なくとも 1 つのリードフレームの各々に対して、前記ダイを前記内部リードポーションに取り付けるため、ダイと前記内部リードポーション間のインターフェースに電気伝導性の無い接着剤を供給する段階と、

e . 前記少なくとも 1 つのリードフレームの各々に対して、前記電気伝導性の無い接着剤を硬化する段階と、

f . 前記少なくとも 1 つのリードフレームの各々に対してワイヤを供給し、前記ワイヤは第 1 と第 2 の終端を持ち、前記第 1 のワイヤの終端は前記ダイに接合し、前記第 2 のワイヤの終端は前記リード内部ポーションに接合する段階と、

g . 少なくとも 1 つの溝を持つ密封シートへの密封剤を硬化させることにより前記ハウジングメンバー上に窓となる蓋のメンバーを取り付け、前記密封剤は前記窓と前記成型されたリードフレーム間に異種混合で配置され、前記密封剤は、前記見える蓋により圧縮され、前記密封剤の一部は、それゆえ前記少なくとも 1 つの溝へプレスされ、それにより密封がもたらされ、それにより前記窓となる蓋のメンバーを持つ前記少なくとも 1 つの窓のあるリードレス半導体製品パッケージング装置を形成する段階と、

h . レーザーにより、前記少なくとも 1 つの窓のある形成されたリードレス半導体製品パッケージング装置の前記外部リードポーションにマーキングする段階と、i . お互いから、前記少なくとも 1 つの窓のある形成されたリードレス半導体製品パッケージング装置の前記外部リードポーションをシンギュレートする段階と、j . 前記シンギュレートされた前記少なくとも 1 つの窓のあるリードレス半導体製品パッケージング装置をパックする段階と、

10

20

30

40

50

k . パックされた少なくとも 1 つの窓のあるリードレス半導体製品パッケージング装置を出荷する段階とを含む方法。

#### 【請求項 24】

前記リードフレームが、チップサイズからチップサイズに近い範囲で、前記リードレス半導体製品パッケージング装置に適合しやすいうように所望の構造に機械的に曲げられる、請求項 22 に記載された少なくとも 1 つの半導体回路をパッケージングするための少なくとも 1 つの窓のあるリードレス半導体製品パッケージング装置を組み立てる方法。

#### 【発明の詳細な説明】

本出願は、同じ出願者による同時係属中の米国暫定特許出願、第 60 / 193,319、題名「ガラスの窓となる蓋を持つリードレス半導体製品パッケージング装置とパッケージングするための方法」、2000 年 3 月 30 日提出、に関する。 10

#### 【0001】

##### 【発明の属する技術分野】

本発明は半導体製品のパッケージングとパッケージされた半導体製品を生産するための組み立て方法に関する。より詳細には、本発明は、リードレス半導体製品のパッケージングとリードレスパッケージされた半導体製品を生産するための組み立て方法に関する。更に詳細には、本発明は、リードレス半導体製品のパッケージングと、時間を浪費し環境に優しくない関連技術であるリードフレームエッチング、及びディフラッシング技術を使用しないパッケージされた半導体製品を量産するための組み立て方法に関する。

#### 【0002】

##### 【従来の技術】

必要な機能回路を持つ電子製品を設置したプリント回路基板に関連する製造コストの関心に応じて、半導体製品パッケージング産業はリードレス回路部品の生産を発展させた（それはまた表面実装可能な電子製品として知られている）。以下「リードレス製品」として言及する。その名が暗示しているように、リードレス製品は、パッケージされた電子製品で、それは、機械式の実装手段として、またはプレナー・ボード上の回路を形成している他の電子部品に対する電気的接続として、そのようなプレナー・ボード上に与えられる接合ホールへ差し込むための物理的なリードの使用を必要としない。一般に、リードレス製品は、プリント回路基板の製造を容易にし、それによりボードホールへの構成要素のリードの挿入、及びボードのはんだパッドへのこれらリードのはんだ付けが除かれる。リードレス技術は、1980 年の初期から電子部品のパッケージングのためのオプションとして十分に受け入れられてきた。例として、現在の関連技術の工業製品は「QFN」を含む。（Quad Flat No Lead, JEDEC STD MO 197, 198, 208, 209, and 220 として登録されている）。もちろん電子部品機能はまだ、リード型のパッケージング構造で利用できる場合がある。 30

#### 【0003】

関連したリードレス半導体製品のパッケージング技術で、「ハーフエッチング」技術はリードフレームを形成するため使われ、その時、かなり危険な物質を生成する。（すなわち、酸の廃棄物、金属の廃棄物、あるいは有機溶剤）。そして非絶縁状態でリードフレームの有効なはんだ付け可能領域を保護するために、成型プロセス中に加えられるパッケージング材料からリードフレームのそのような有効なはんだ可能領域（外部 I/O として知られている）を一時的にマスクするため、接着テープが使われ、過剰のテープや恐らくは有機溶剤の廃棄物を生成する。もう一つ別の関連した半導体製品のパッケージング技術において、リードフレームは完全に成型工程によってパッケージされ、そしてリードフレームの有効なはんだ付け可能領域は、次の工程で「バリ取り」を行う必要があり、ここでそのような部分は「オーバーパッケージング」を除くため、高圧の水性微粒子スラリー（すなわちウエットプラスティング）で吹き飛ばされる。従って、重合体廃棄物スラリーの形態で、かなり危険な材料を生成する。従って、天然資源の保全及びリードレス半導体製品をパッケージングするための環境に優しい方法と装置を供給する必要性がある。 40

#### 【0004】

20

30

40

50

## 本発明の開示

本発明は、すなわちリードレス半導体パッケージング装置は、優れた機械的、電気的、そして熱的特性を持ち、コスト効率が良い製品を与え、また独特な密封のみならず内部にパッケージされ集積化された半導体回路（チップ／ダイ）を見るための機構を与えるオプションの窓のある蓋の特徴（すなわち見える蓋（sight lid））を有している。コスト低減は、（a）デバイスをパッケージングするために伝統的な関連技術であるセラミック材料よりむしろエポキシのような重合体材料を任意に使う（b）パッケージング工程を簡略化し、それにより生産性を改善することにより成し遂げられる。

### 【0005】

本発明は、関連技術の「ハーフエッチされた」リードフレームと対照的に、成型工程中に重合体材料によりパッケージされる、独特の「スタンプされた」かつ／または「曲げ加工された」標準のソルダープレートされた、またはプリプレートされたリードフレームを使う。本発明の工程は独特な圧縮タイプの型を供給し、この型は特に、関連技術で共通の問題であるリードフレームの有効なはんだ付け可能領域の「オーバーパッケージング」を避けるように構成されることを含む。本出願者の発明は、デバイスの組み立てとパッケージング工程を簡略化したものである。特別に形作られた圧縮型は、リードフレームの外部ポーションから内部ポーションの輪郭描写を容易にする。ここで外部ポーションはプリント回路基板上のパッドに接触する有効なはんだ付け可能領域を有する。型は効果的に「圧縮力のある密封口」を供給し、そこから、リードフレームの有効なはんだ付け可能領域は拡張され露出される場合があり、このようにしてリードフレームの内部ポーションをパッケージングするために型により包含された重合体でコートされることを避け、それによって困難なマスキング段階と退屈なバリ取り段階を回避する。

### 【0006】

本発明はリードフレームの「スタンピング」かつ／または「曲げ加工」の独特な技術を供給し、それによって、それを独特な半導体製品の電気機械的要件に適合させる。所望の形状へリードフレーム材料をスタンピングかつ／または曲げ加工することにより、本発明は、パッケージされた半導体製品の電気機械的要件に適合させるためのリードの旧技術である「ハーフエッティング」を必要としない。例えば、関連技術のプロセスは必要な形状を作るためリードフレームを「ハーフエッティング」する（例えば、元が10ミルの導電体物質を約5ミル、エッティングすると、それによって大量の酸と導電体物質の危険な廃棄物を発生させる）。従って、6ミル以下の範囲にあるような薄いリードフレーム材料が本発明で使われる場合がある。本発明は、下記の幾つかの更に特色のある利点を提供している。（a）顧客仕様のパッケージサイズ（b）現存の表面実装技術（SMT）プロセスが適用可能（c）低コストで全体の性能を向上できる（d）危険な副産物を発生させずにフルスケールの生産が達成できる（環境に優しい、すなわち、酸の廃棄物を無くし、揮発性有機化合物の遊離を無くし、そして前記の固体重合体のスラリー廃棄物を無くす）。（e）より薄いリードフレーム材料（天然資源の保全）。

### 【0007】

#### 発明の実施の形態

本発明をよりよく理解するために、以下の参考添付図を用いて説明する。参考番号は、幾つかの図面を通して本発明の同じ部分、または等価な部分を指し示す。

### 【0008】

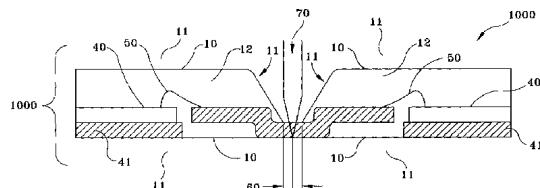

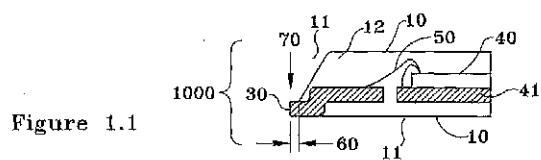

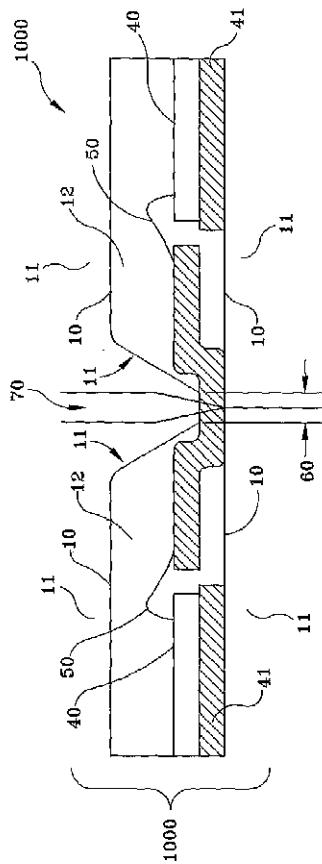

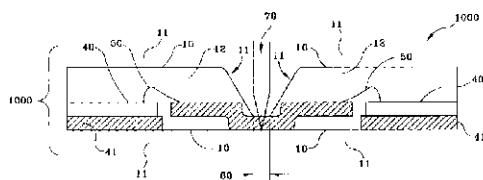

図1.1の断面図は、本発明による第1の具体例である「チップサイズに近い」リードレス半導体パッケージング装置1000（すなわち、ここではパッケージングと外部リード部分が、与えられたチップの平面図領域を越えて最小に拡張している）を例示しているが、それはパッケージングモールドライン10と銅のような導電性物質を「スタンピング」かつ「曲げ加工」することにより形成された、独特の「スタンプされた」かつ「曲げ加工された」リードフレーム30を持ち、効果的にはんだ付け可能な長さ60と有効な曲部34、すなわちモールド11（図示されず）により特に圧縮的に保持されている特にスタンプされ曲げ加工されたリードフレーム30、を備えている。そこに示されている他の

リードレス半導体デバイスの構成部品は、ダイ40、パッドメタルを形成する場合があるダイ取り付けパッド41、そして金のような導電性物質から形成される結合されたワイヤである。モールド11は(図示されていない)、独特かつ効果的に圧縮(例えばホットプレスを使う)により、スタンプされ曲げ加工されたリードフレーム30の内部ポーションのみを取り囲むために重合体モルディング化合物のような重合体物質12を保持し、それによりスタンプされ曲げ加工されたリードフレーム30上のきれいではんだ付け可能な領域を保護し、そしてそれにより過剰なパッケージング物質のバリ取りに対して環境に優しくない関連技術の必要性を回避する。スタンプされ曲げ加工されたリードフレーム30をトリミングするための方法は、矢印70により示された方向にソーイング(sawing)またはポンチカッティング(punch-cutting)することを含む場合がある。10

#### 【0009】

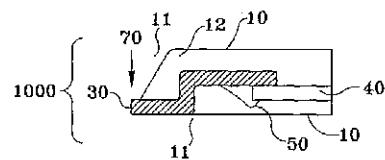

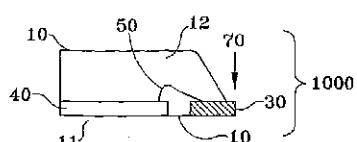

図1.2は、本発明による第2の具体例の断面図で、チップサイズに近いリードレス半導体パッケージング装置1000を示し、それは、パッケージングモールドライン10、銅のような導電性物質をスタンピングし、かつ曲げ加工することにより形成された独特のスタンプされかつ曲げ加工されたリードフレーム30、有効な曲部34、そしてそれらの間で下側で結合された金のような導電性物質により形成されたワイヤ50を備えるダイ40を持つ。これらの構成部品は、図1.1で述べられた方法で、特に圧縮成型される。

#### 【0010】

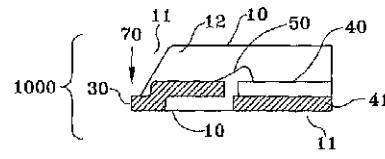

図1.3は、本発明による第3の具体例の断面図で、チップサイズに近い耐熱性の高いリードレス半導体パッケージング装置1000を示し、それは、パッケージングモールドライン10、銅のような導電性物質をスタンピングし、かつ曲げ加工することにより形成された独特のスタンプされかつ曲げ加工されたリードフレーム30、有効な曲部34、そしてそれらの間で上側で結合された金のような導電性物質により形成されたワイヤ50を備えるダイ40を持ち、そしてスタンプされかつ曲げ加工されたリードフレーム30とダイ40は、型からはみ出した(すなわち露出した)共通のダイ取り付けパッド41を共有している。これらの構成部品は、図1.1で述べられた方法で、特に圧縮成型される。20

#### 【0011】

図1.3aは、本発明による第4の具体例の断面図で、チップサイズに近い耐熱性の高いリードレス半導体パッケージング装置1000を示し、それは、パッケージングモールドライン10、銅のような導電性物質をスタンピングし、かつ曲げ加工することにより形成された独特のスタンプされかつ曲げ加工されたリードフレーム30、有効な曲部34、そしてそれらの間で上側で結合された金のような導電性物質により形成されたワイヤ50を備えるダイ40を持ち、そしてダイ取り付けパッド41の下面是、はみ出した(すなわち露出した)状態である。これらの構成部品は、図1.1で述べられた方法で、特に圧縮成型される。30

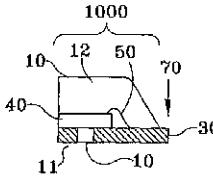

#### 【0012】

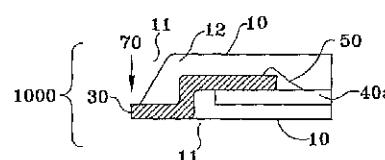

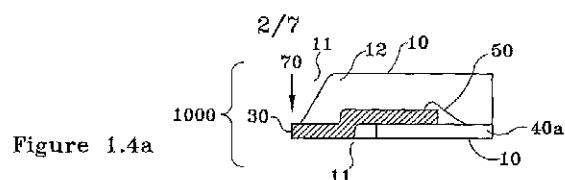

図1.4は、本発明による第5の具体例の断面図で、チップサイズに近いリードレス半導体パッケージング装置1000を示し、それは、パッケージングモールドライン10、銅のような導電性物質をスタンピングし、かつ曲げ加工することにより形成された独特のスタンプされかつ曲げ加工されたリードフレーム30、有効な曲部34、そしてそれらの間で上側で結合された金のような導電性物質により形成されたワイヤ50を備えるスタンプされかつ曲げ加工されたリードフレーム30の下側に置かれた中心パッド40aを持つ。これらの構成部品は、図1.1で述べられた方法で、特に圧縮成型される。40

#### 【0013】

図1.4aは、本発明による第6の具体例の断面図で、チップサイズに近いリードレス半導体パッケージング装置1000を示し、それは、パッケージングモールドライン10、銅のような導電性物質をスタンピングし、かつ曲げ加工することにより形成されたスタンプされかつ曲げ加工されたリードフレーム30、有効な曲部34、そしてそれらの間で上側で結合された金のような導電性物質により形成されたワイヤ50を備えるスタンプされ50

かつ曲げ加工されたリードフレーム 30 の下側に置かれた中心パッド 40a を持ち、そして中心パッド 40a の下面是、はみ出した（すなわち露出した）状態である。これらの構成部品は、図 1.1 で述べられた方法で、特に圧縮成型される。

【0014】

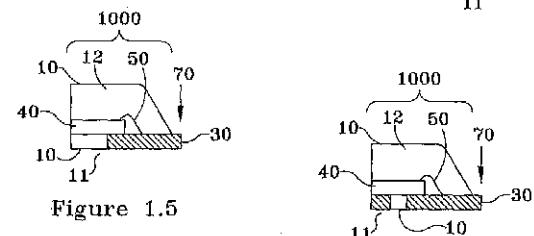

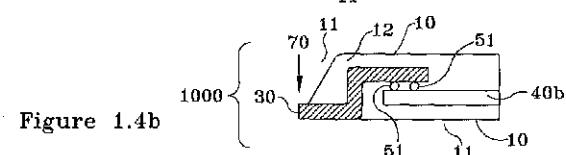

図 1.4b は、本発明による第 7 の具体例の断面図で、チップサイズに近いリードレス半導体パッケージング装置 1000 を示し、それは、パッケージングモールドライン、銅のような導電性物質をスタンピングし、かつ曲げ加工することにより形成された独特のスタンプされかつ曲げ加工されたリードフレーム 30、有効な曲部 34、及び、スタンプされかつ曲げ加工されたリードフレーム 30 とフリップチップ 40b 間に配置され接触している少なくとも 1 つの導電性パーティクル 51 を備えた、スタンプされかつ曲げ加工されたリードフレーム 30 の下側に置かれたフリップチップ 40b を持つ。これらの構成部品は、図 1.1 で述べられた方法で、特に圧縮成型される。

10

【0015】

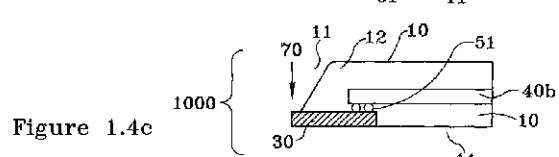

図 1.4c は、本発明による第 8 の具体例の断面図で、「チップサイズ」のリードレス半導体パッケージング装置 1000 を示し、それは、パッケージングモールドライン 10、銅のような導電性物質をスタンピングすることにより形成された独特のスタンプされたリードフレーム 30、及びスタンプされかつ曲げ加工されたリードフレーム 30 とフリップチップ 40b 間に配置され接触している少なくとも 1 つの導電性パーティクル 51 を備えた、スタンプされたリードフレーム 30 の上側に置かれたフリップチップ 40b を持つ。これらの構成部品は、図 1.1 で述べられた方法で、特に圧縮成型される。

20

【0016】

図 1.5 は、本発明による第 9 の具体例の断面図で、チップサイズのリードレス半導体パッケージング装置 1000（すなわち、ここではパッケージングと外部リードポーションが、与えられたチップの平面図領域を越えて最小限に拡張している。ここで平面図パッケージング領域はダイ平面図領域の 12 倍以下である）を示し、それは、パッケージングモールドライン 10、銅のような導電性物質をスタンピングし、かつ曲げ加工することにより形成された独特のスタンプされかつ曲げ加工されたリードフレーム 30 上に置かれたダイ 40、そして、それらの間で上側で結合された金のような導電性物質により形成されたワイヤ 50 を備える。これらの構成部品は、図 1.1 で述べられた方法で、特に圧縮成型される。

30

【0017】

図 1.6 は、本発明による第 10 の具体例の断面図で、チップサイズのリードレス半導体パッケージング装置 1000 を示し、それは、パッケージングモールドライン 10、銅のような導電性物質をスタンピングすることにより形成された少なくとも 1 つ以上の独特のスタンプされたリードフレーム 30 上に置かれたダイ 40、及びそれらの間で上側で結合された金のような導電性物質から形成されたワイヤ 50 を備える。これらの構成部品は、図 1.1 で述べられた方法で、特に圧縮成型される。

【0018】

図 1.7 は、本発明による第 11 の具体例の断面図で、リードレス半導体パッケージング装置 1000 を示し、それは、パッケージングモールドライン、銅のような導電性物質をスタンピングすることにより形成された独特のスタンプされたリードフレーム 30 に対して側面に置かれ露出したダイ 40、及びそれらの間で上側で結合された金のような導電性物質から形成されたワイヤ 50 を備える。これらの構成部品は、図 1.1 で述べられた方法で、特に圧縮成型される。

40

【0019】

図 1.8 の断面図は、第 3 の具体例と同等の本発明によるチップサイズに近いリードレス半導体パッケージング装置 1000 を例示しているが、それは、パッケージングモールドライン 10 と、銅のような導電性物質をスタンピングし、かつ曲げ加工することにより形成される場合がある少なくとも 1 つの独特的スタンプされ曲げ加工されたリードフレーム 30 と、有効な曲部 34 を持ち、製造工程中に生ずるであろうモールド 11（図示せず）

50

により保持されている有効はんだ付け可能長 60 を備えている。ここに図示される他のリードレス半導体デバイスの構成部品は、少なくとも 1 つのダイ 40 と、パッドメタルを形成する場合がある少なくとも 1 つのダイ取り付けパッド 41 と、金のような導電性物質により形成される少なくとも 1 つの結合したワイヤ 50 である。複数のリードレス半導体デバイスをパッケージングするとき、アセンブリライン形式で大量生産されパッケージされたデバイスを分離するための方法は、矢印 70 で示された方向にソーイング (sawing) やポンチカッティング (punch-cutting) を行うことを含む場合がある。モールド 11 (図示せず) は、圧縮力を通して、少なくとも 1 つの独特的なスタンプされ曲げ加工されたリードフレーム 30 (すなわち外部ポーションへの漏れが無い、少なくとも 1 つのスタンプされたリードフレーム) の内部ポーションのみを取り囲むために少なくとも 1 つの重合体物質 12 を独特かつ効果的に保持する。従って、少なくとも 1 つの独特にスタンプされ曲げ加工されたリードフレーム 30 の外部ポーション上のきれいではんだ付け可能な領域を保護し、それにより過剰なパッケージング物質のバリ取りのための関連技術の必要性を回避する。

10

20

30

40

50

## 【0020】

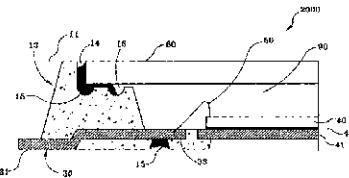

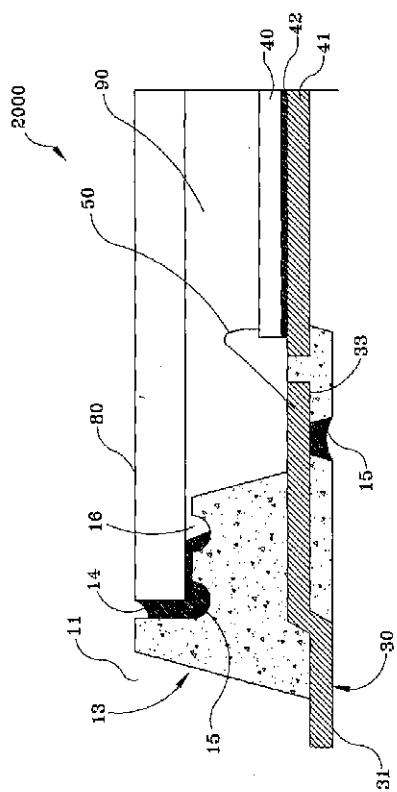

図 20 の断面図は、本発明のもう 1 つ別の具体例である、本発明による窓のあるリードレス半導体パッケージング装置 2000 を例示しているが、それは銅のような導電性物質をスタンピングし、かつ曲げ加工することにより形成される独特的なスタンプされ曲げ加工されたリードフレーム 30 を含むリードレス半導体デバイスと、有効な曲部 34 と、電気伝導性が無い接着剤 42 によりダイ取り付けパッド 41 に接着されたダイ 40 と、金のような物質から形成されるワイヤ 50 を持ち、それらは、ガラスや高温ポリマのような視覚的に透明な物質から作られた見える蓋 (サイトリッド) 80 によりパッケージされ、紫外線で硬化可能なエポキシ樹脂のような密封剤 14 により硬化重合体物質 13 に対して独特に密封されている。密封剤 14 は、汚染物質の入場に対して、独特のより大きな密封表面積とより良い密封性を与えるため、密封剤 14 の一部が内側の溝 16 に流れ込むように、独特な 2 つの部分からなる溝の密封シートの外側の溝 15 の中に入れられ、見える蓋 80 により圧縮される。しかしながら本発明は、2 つの部分からなる溝の使用に限定されず、パッケージされる与えられた半導体回路により要求される少なくとも 1 つの溝を利用する場合がある。硬化重合体物質 13 は、スタンプされたリードフレーム 30 の外部ポーション 31 と内部ポーション 32 の両方に置かれた重なった先細りのモールドラインを持ち、またダイ取り付けパッド 41 とスタンプされたリードフレーム 30 の内部ポーション 33 間に置かれた同じ高さのモールドラインを持つ。強化された充填物質 15 は、内部ポーション 33 が以前にモールド 11 (図示せず) により独特な圧縮力で保持されたように、スタンプされたリードフレーム 30 の内部ポーション 33 の下面まで硬化される。

## 【0021】

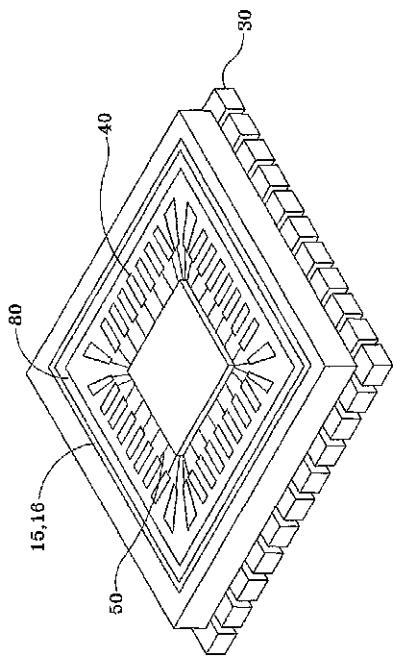

図 3.0 の斜視図は、本発明による窓のあるリードレス半導体パッケージング装置 2000 を例示しているが、それは、銅のような導電性物質をスタンピングかつ/または曲げ加工することにより形成されたスタンプかつ/または曲げ加工されたリードフレーム 30 を持ち、この独特的なスタンプ加工は空所 35 により示されたように、リードフレーム材を効果的に除去して、硬化重合体 13 に形成された少なくとも 1 つの溝を持つ独特的な密封シート 15, 16 に対して密封された見える蓋 80 を通して見られるようにそれらの間でワイヤ 50 を結合することにより共通のダイ 40 を共有し、重合体 13 は、前記の独特的な圧縮成型技術により形成される。

## 【0022】

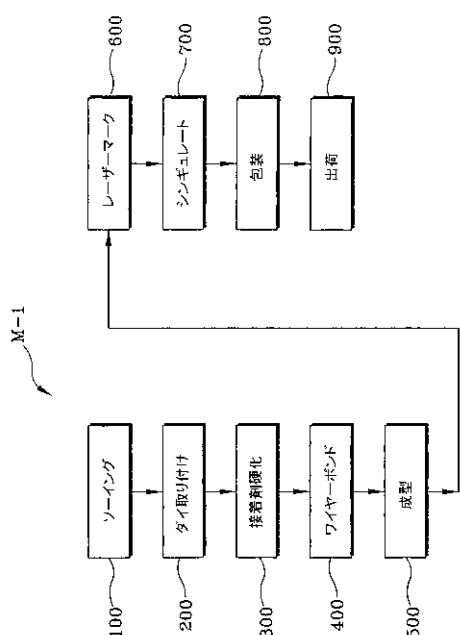

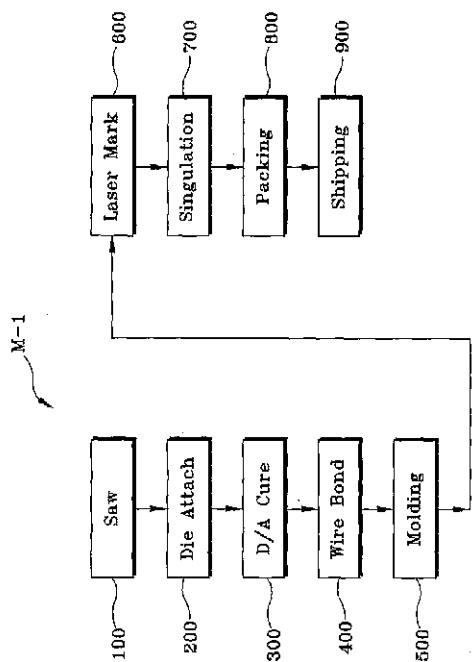

図 4.0 は、本発明による、少なくとも 1 つのリードレス半導体パッケージング装置 1000 をパッケージするための一般的な組み立て方法 M-1 の流れ図を示す。方法 M-1 は次のステップから成る。(a) 工程ブロック 100 に示されたように、リードフレーム材料をソーイング (sawing) またはポンチカッティング (punch-cutting) することにより少なくとも 1 つのリードを持つ少なくとも 1 つのスタンプされたリードフレームを供給する。(b) 工程ブロック 200 に示されたように、電気伝導性が無

い接着剤（ダイ取り付け）を供給し少なくとも1つのリードフレームにダイを接着する。（c）工程ブロック300に示されたように、電気伝導性が無い接着剤を硬化させる。（d）工程ブロック400に示されたように、少なくとも1つのリードのそれぞれにダイからワイヤを接続する。（e）工程ブロック500に示されたように、上側プラテンと下側プラテンを持つホットプレスを使う加熱圧縮成型のような技術により重合体モールディング化合物のようなもう一つ別の重合体物質で半導体デバイス構成要素を成型し、それは独特な密封開口部をもたらし、そこから外部リードポーションが圧縮力とわずかに局所化された変形によって拡張し、それにより少なくとも1つのリードレス半導体パッケージング装置1000を形成する。（f）工程ブロック600に示されたように、レーザーにより少なくとも1つの形成されたリードレス半導体パッケージング装置1000をマークリングする。（g）工程ブロック700に示されたように、少なくとも1つのレーザーマークされたリードレス半導体パッケージング装置1000をシンギュレートする。（h）工程ブロック800に示されたように、少なくとも1つのシンギュレートされたリードレス半導体パッケージング装置1000をパックする。（i）工程ブロック900に示されたように、少なくとも1つのパックされたリードレス半導体パッケージング装置1000を出荷する。

10

20

30

40

#### 【0023】

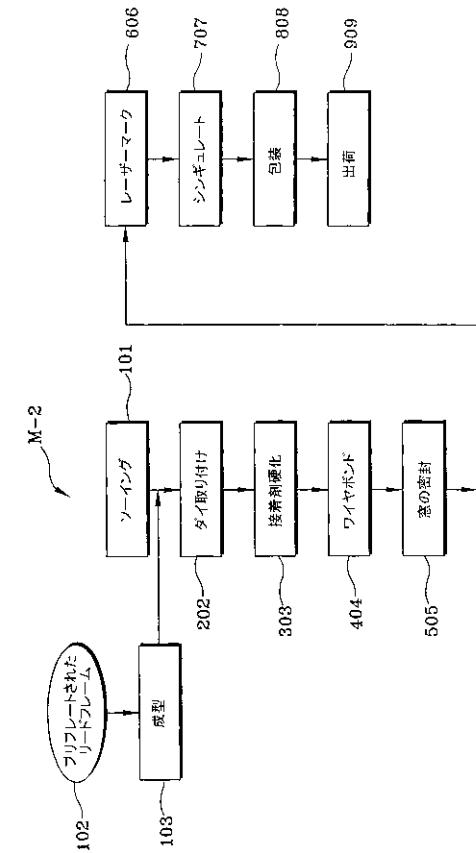

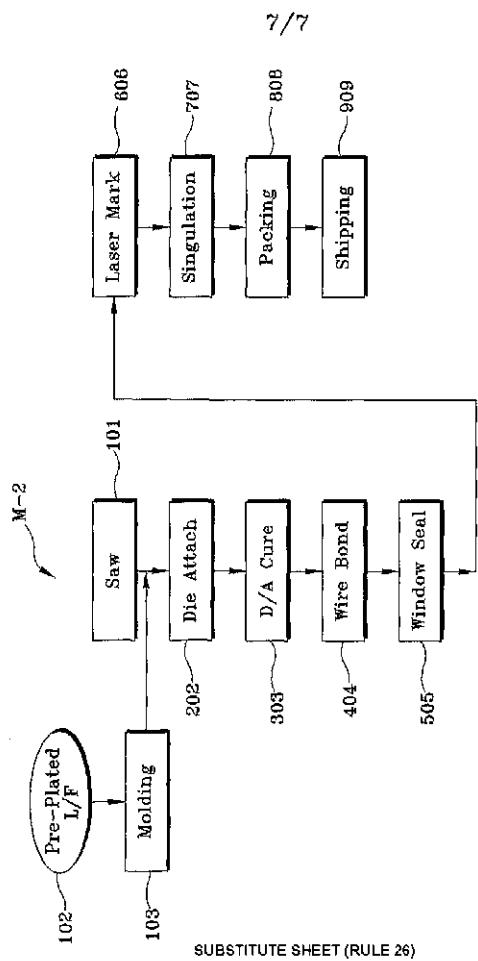

図5.0は、本発明による、少なくとも1つの窓のあるリードレス半導体パッケージング装置2000をパッケージングするための一般的な組み立て方法M-2の流れ図を示す。方法M-2は次のステップから成る。（a）工程ブロック102に示されたように、リードフレーム材料をプリプレーティングすることにより、少なくとも1つのリードを持つ少なくとも1つのスタンプされたリードフレームを供給する。（b）工程ブロック103に示されたように、上側プラテンと下側プラテンを持つホットプレスを使う加熱圧縮成型のような技術により重合体モールディング化合物のような重合体物質で少なくとも1つのスタンプされプリプレートされたリードフレームを成型し、それは独特な密封開口部もたらし、そこから外部リードポーションが圧縮力とわずかに局所化された変形によって拡張している。（c）工程ブロック101に示されたように、リードフレーム材をソーイング（sawing）またはポンチカッティング（punch-cutting）する。（d）工程ブロック202に示されたように、少なくとも1つのリードフレーム（ダイ取り付け）にダイを取り付ける。（e）工程ブロック303に示されたように、電気伝導性の無い接着剤を硬化させる。（f）工程ブロック404に示されたように、少なくとも1つのリードにダイからワイヤを接合する。（g）工程ブロック505に示されたように、紫外線で硬化可能なエポキシのような密封剤を供給することにより成型されたリードフレーム上に窓を取り付け、それにより、少なくとも1つのリードレス半導体パッケージング装置2000を形成する。（h）工程ブロック606に示されたように、レーザー技術により、少なくとも1つの形成された窓のあるリードレス半導体パッケージング装置2000をマークリングする。（i）工程ブロック707に示されたように、少なくとも1つのレーザーマークされた窓のあるリードレス半導体パッケージング装置2000をシンギュレートする。（j）工程ブロック808に示されたように、少なくとも1つのシンギュレートされた窓のあるリードレス半導体パッケージング装置2000をパックする。（k）工程ブロック909に示されたように、少なくとも1つのパックされた窓のあるリードレス半導体パッケージング装置2000を出荷する。

#### 【0024】

ここに示された情報及び詳細は、現在の好ましい発明の具体例として、つまり本発明により広く考えられる属する代表的なものとして、その発明の上述された目的を達成することが十分に可能である。本発明の範囲は、当業者に明らかになるであろう他の具体例も十分に包含し、従って添付された本請求項以外の何物によっても制限されない。ここで単数の要素に言及したときは、明白に述べていない限り、それは「1つまたは1つのみ」ではなく「1つまたは1つ以上」を意味することを意図している。一般的の当業者に知られた上述の好ましい具体例及び追加的な具体例の要素と、構造的、機能的に同等なものすべては、

50

これにより明白に参照により組み込まれ、本請求項により包含されるものであることが意図されている。更に、本請求項により包含されるそのようなものに対して、本発明により解決を求める各々の、そしてあらゆる問題を処理するためのデバイスまたは方法に対する要件は存在しない。更に、要素、構成要素、または方法の段階が明白に本請求項に列挙されているかどうかに關係なく、本発明で公開された要素、構成要素、または方法は、公衆に奉げられると言う意図は持たない。しかしながら、様々な形状、半導体材料、及び組み立て材料の詳細な変更や修正は添付された請求項に述べられているような発明の精神と範囲から逸脱することなく成されることは普通の当業者なら容易に理解されるだろう。語句「～のための手段」を使って要素が明白に列挙されていないなら、35 U.S.C 112、第6項の規定により解釈される請求項は、ここには無い。

10

【図面の簡単な説明】

【図1.1】本発明による、ワイヤがスタンプされたリードフレームに結合し、もう一つ別のワイヤがダイ取り付けパッドに結合した状態で、「上側」の位置に置かれたダイを持つリードレス半導体デバイス形状について示されたパッケージングモールドラインを持つチップサイズに近い基本リードレス半導体パッケージング装置の断面図である。

【図1.2】本発明による、スタンプされたリードフレームと「下側」の位置に、それらの間で結合したワイヤを備えるダイを持つリードレス半導体デバイス形状について示されたパッケージングモールドラインを持つチップサイズに近いリードレス半導体パッケージング装置の断面図である。

【図1.3】本発明による、スタンプされたリードフレームと、「上側」の位置に、それらの間で結合したワイヤを備え、かつ、共通のダイ取り付けパッドを共有するダイを備えるリードレス半導体デバイス形状について示されたパッケージングモールドラインを持つチップサイズに近く耐熱性の高いリードレス半導体パッケージング装置の断面図である。

【図1.3a】本発明による、スタンプされたリードフレームと「上側」の位置に、それらの間で結合したワイヤを備え、かつ、型からはみ出した（すなわち露出された）ダイ取り付けパッドの下面を備えるダイを持つリードレス半導体デバイス形状について示されたパッケージングモールドラインを持つチップサイズに近く耐熱性の高いリードレス半導体パッケージング装置の断面図である。

【図1.4】本発明による、スタンプされたリードフレームと「上側」の位置に、それらの間で結合したワイヤを備え、かつ、スタンプされたリードフレームの下側に置かれた中心パッドを持つリードレス半導体デバイス形状について示されたパッケージングモールドラインを持つチップサイズに近いリードレス半導体パッケージング装置の断面図である。

【図1.4a】本発明による、スタンプされたリードフレームと、「上側」の位置にそれらの間で結合したワイヤを備え、かつ中心パッドの下面が型からはみだしている、スタンプされたリードフレームの下側に置かれた中心パッドを持つリードレス半導体デバイス形状について示されたパッケージングモールドラインを持つチップサイズに近いリードレス半導体パッケージング装置の断面図である。

【図1.4b】本発明による、スタンプされたリードフレームと、少なくとも1つの伝導性パーティクルと接触し、かつ、それがリードフレームとフリップチップ間に配置されている、スタンプされたリードフレームの下側に置かれたフリップチップを持つリードレス半導体デバイス形状について示されたパッケージングモールドラインを持つチップサイズに近いリードレス半導体パッケージング装置の断面図である。

【図1.4c】本発明による、スタンプされたリードフレームと、少なくとも1つの伝導性パーティクルと接触し、かつ、それがリードフレームとフリップチップ間に配置されているスタンプされたリードフレームの上側に置かれたフリップチップを持つリードレス半導体デバイス形状について示されたパッケージングモールドラインを持つチップサイズに近いリードレス半導体パッケージング装置の断面図である。

【図1.5】本発明による、リードフレーム上に置かれたダイと、「上側」の位置に、それらの間で結合したワイヤを備えたリードレス半導体デバイス形状について示されたパッケージングモールドラインを持つチップサイズに近いリードレス半導体パッケージング装

20

30

40

50

置の断面図である。

【図1.6】本発明による、少なくとも1つのリードフレーム上に置かれたダイと、「上側」の位置に、それらの間で結合したワイヤを備えたリードレス半導体デバイス形状について示されたパッケージングモールドラインを持つチップサイズに近いリードレス半導体パッケージング装置の断面図である。

【図1.7】本発明による、リードフレームに対して横に置かれて露出されたダイと、「上側」の位置に、それらの間で結合したワイヤを備えたリードレス半導体デバイス形状について示されたパッケージングモールドラインを持つチップサイズに近いリードレス半導体パッケージング装置の断面図である。

【図1.8】本発明による、製造工程中に産出されるであろう少なくとも1つのリードレス半導体デバイスについて示されたパッケージングモールドラインを持つリードレス半導体パッケージング装置の断面図である。 10

【図2】本発明による、スタンプされたリードフレームの内部ポーションに置かれた平らなモールドラインを持つ硬化した重合体材料に対して密封された見える蓋によりパッケージされているスタンプされたリードフレーム、ダイ、及び結合したワイヤを持つリードレス半導体デバイス形状を有する窓を取り付けたリードレス半導体パッケージング装置の断面図である。

【図3】本発明による、見える蓋を通して見られるように、それらの間のワイヤを結合することにより、共通のダイを共有する複数のリードを持つスタンプされたリードフレームを持つ窓を取り付けたリードレス半導体パッケージング装置の斜視図である。 20

【図4】本発明による、リードレス半導体パッケージング装置をパッケージするための組み立て方法のフローチャートである。

【図5】本発明による、窓のあるリードレス半導体パッケージング装置をパッケージングするための組み立て方法のフローチャートである。 20

【図4】

【図5】

## 【国際公開パンフレット】

(12) INTERNATIONAL APPLICATION PUBLISHED UNDER THE PATENT COOPERATION TREATY (PCT)

(19) World Intellectual Property Organization

International Bureau(43) International Publication Date

11 October 2001 (11.10.2001)

PCT

(10) International Publication Number

WO 01/75938 A2

- (51) International Patent Classification<sup>7</sup>: H01L

- (81) Designated States (*initials*): AE, AG, AI, AM, AT, AU, AZ, BA, BB, BG, BR, BY, BZ, CA, CL, CN, CR, CU, CZ, DE, DK, DM, DZ, IL, IS, FL, GB, GD, GE, GI, GM, HR, HU, ID, IL, IN, IS, IP, KH, KG, KP, KR, KZ, LC, LK, LR, LS, LU, LV, MA, MD, MG, MK, MN, MW, MX, MZ, NO, NZ, PL, PT, RO, RU, SD, SE, SG, SL, SK, SL, TJ, TM, TR, TT, TZ, UA, UG, UZ, VN, YU, ZA, ZW

- (21) International Application Number: PCT/US01/0390

- (22) International Filing Date: 30 March 2001 (30.03.2001)

- (25) Filing Language: English

- (26) Publication Language: English

- (30) Priority Data: 60/193,319 30 March 2000 (30.03.2000) US

09/668,425 6 October 2000 (06.10.2000) US

- (71) Applicant: ATS SERVICES COMPANY (US) (US), 1680 Civic Center Drive, Suite A, Santa Clara, CA 95051 (US).

- (72) Inventors: CHUN, Dosung 900 North Rural Road, #2055, Chandler, AZ 85226 (US); CHANG, Sung 415-112 North Mary Avenue, Sunnyvale, CA 94086 (US)

- (74) Agent: FLORES, Victor; Lariviere, Grubman & Payne LLP, P.O. Box 3140, Monterey, CA 93942 (US).

- Published: *without international search report and to be republished upon receipt of that report*

- For two-letter codes and other abbreviations, refer to the "Guidance Notes on Codes and Abbreviations" appearing at the beginning of each regular issue of the PCT Gazette

(54) Title: LEADLESS SEMICONDUCTOR PRODUCT PACKAGING APPARATUS HAVING A WINDOW LID AND METHOD FOR PACKAGING

WO 01/75938 A2

(57) Abstract: A novel, resource-conservative, environmentally friendly, cost effective, leadless semiconductor packaging apparatus, having superior mechanical and electrical properties, and having an optional windowed housing which uniquely seals and provides a mechanism for viewing the internally packaged integrated semiconductor circuits (chips/lines). A uniquely stamped and/or bent lead-frame is packaged by a polymeric material during a unique compression-molding process using a mold, specially contoured to avoid the common "over packaging" problem in related art techniques. The specially contoured mold facilitates delineation of the internal portions from the external portions of the lead-frame, as the external portions are the effective solderable areas that contact pads on a printed circuit board, thereby avoiding a laborious, environmentally-unfriendly masking step and de-flashing step, streamlining the device packaging process. The compression-mold effectively provides a compressive sealing office from which the effective solderable areas of the lead frame may extend and be exposed and, thus, avoid being coated with the polymer which is uniquely contained by the mold for packaging the internal portions of the lead-frame. The lead-frame is uniquely stamped and/or bent, conforming it to electro-mechanical requirements of a particular semiconductor product. By uniquely stamping and/or bending, the related art "half-etching" of the lead for conforming it to electro-mechanical requirements of the packaged semiconductor product is no longer required. Environmental enhancement is achieved by conserving natural resources and by eliminating hazardous material by products otherwise liberated in related art packaging techniques.

WO 01/75938

PCT/US01/10390

LEADLESS SEMICONDUCTOR PRODUCT PACKAGING APPARATUS

HAVING A WINDOW LID AND METHOD FOR PACKAGING

## RELATED APPLICATION

This application is related to co-pending U.S. Provisional Patent Application, Ser. No. 60/193,319, filed March 30, 2000 and U.S. Non-Provisional Patent Application, Ser. No. 09/668,423, filed September 22, 2000, both entitled "LEADLESS SEMICONDUCTOR PRODUCT PACKAGING APPARATUS HAVING GLASS WINDOW LID AND METHOD FOR PACKAGING," by the same Applicants.

## TECHNICAL FIELD

The present invention relates to semiconductor product packaging and methods of fabrication for producing a packaged semiconductor product. More particularly, the present invention relates to leadless semiconductor product packaging and methods of fabrication for producing leadless packaged semiconductor product. Even more particularly, the present invention relates to leadless semiconductor product packaging and methods of fabrication for mass-producing packaged semiconductor product without employing time-consuming, environmentally-unfriendly related art lead-frame etching and de-flashing techniques.

10

## BACKGROUND ART

In response to manufacturing cost concerns relating to populating printed circuit boards with electronic product having the requisite functional circuits, the semiconductor product packaging industry has developed a leadless circuit component product (also known as a surface mountable electronic product), hereinafter referred to as a "leadless product." The leadless product, as the name implies, is a packaged electronic product that does not require the use of physical leads for being inserted into mating holes provided on a planar board as a mechanical mounting means nor as an electrical connection with other electronic components forming the circuit on such a planar board. In general, the leadless product facilitates manufacturing of a printed circuit card, thereby eliminating the inserting of component leads into the board holes and the soldering of these leads to the board's solder pads. The leadless technology has been well accepted as an option for packaging electronic components since early 1980. By example, a current related art industrial product includes "QFN" (Quad Flat No Lead, registered as JEDEC STD MO 197, 198, 208, 209, and 220). Of course, the electronic component function may still be available in a lead-type packaging structure.

WO 01/75938

PCT/US01/10390

In the related leadless semiconductor product packaging art, "half-etching" techniques are used for forming the lead-frame, generating considerable hazardous material (e.g., acid waste, metals waste, and possibly organic solvent waste); and an adhesive tape is used to temporarily mask effective solderable areas of the lead-frame (also known as the "outer I/O") from the packaging material to be applied during the molding process in order to preserve such effective solderable areas of the lead-frame in an un-insulated state, generating undue tape and possibly organic solvent waste. In another related semiconductor product packaging art technique, the lead-frame is completely packaged by a molding process; and the effective solderable areas of the lead-frame must be subsequently "de-flashed" in a process wherein such portions are blasted with a highly pressurized aqueous slurry of particulates (i.e., wet-blasting) to remove the "over-packaging," thereby generating considerable hazardous material in the form of polymeric waste slurry. Therefore, a need exists for providing a natural resource-conservative and environmentally-friendly method and apparatus for packaging a leadless semiconductor product.

15

## DISCLOSURE OF INVENTION

The present invention, a leadless semiconductor packaging apparatus, provides a cost-effective product, having superior mechanical, electrical, and thermal properties, and having an optional window lid feature (i.e., a sight lid) which not only uniquely seals, but also provides a mechanism for viewing the internally packaged integrated semiconductor circuits (chips/die). Cost reduction is achieved by (a) optionally using polymeric materials, such as epoxies, rather than conventional related art ceramic materials for packaging devices, and (b) simplifying the packaging process, thereby improving productivity.

The present invention employs a unique "stamped" and/or "bent" standard solder-plated or pre-plated lead-frame which is packaged by a polymeric material during a molding process, in contrast to the related art "half-etched" lead-frame. The process of the present invention involves providing a unique compression-type mold, specially contoured to avoid "over-packaging," of the effective solderable areas of the lead-frame which is a common problem in the related art techniques. Applicants' invention results in streamlining the device fabrication and packaging process. The specially contoured compression-mold facilitates delineation of the internal portions from the external portions of the lead-frame, where the external portions have the effective solderable areas that contact pads on a printed circuit board. The mold effectively provides a

WO 01/75938

PCT/US01/10390

"compressive sealing orifice" from which the effective solderable areas of the lead-frame may extend and be exposed and, thus, avoid being coated with the polymer which is contained by the mold for packaging the internal portions of the lead-frame, thereby avoiding a laborious masking step and a tedious de-flashing step.

5 The present invention applies the unique technique of "stamping" and/or "bending" of the lead-frame, thereby conforming it to electro-mechanical requirements of a particular semiconductor product. By stamping and/or bending the lead-frame material into the desired configuration, the present invention does not require old art "half-etching" of the lead for conforming it to electro-mechanical requirements of the packaged semiconductor product. By 10 example, the related art process "half-etches" the lead-frame (e.g., 10 mils of raw conducting material are etched to about 5 mils, thereby generating a large volume of acid and conducting material hazardous waste) in order to create the requisite shape. Thus, thinner lead-frame material, such as that in a range of 6 mils or less, may be used with the present invention. The 15 present invention offers several more distinctive advantages: (a) customer-specifiable package size, (b) applicable existing surface mount technology (SMT) processes, (c) overall improved performance at a lower cost, (d) complete absence of hazardous material by-products in full-scale production (environmentally-friendly, i.e., no acid waste, no metals waste, no liberation of volatile organic compounds, and no solid polymeric slurry waste), and (e) thinner lead-frame material (natural-resource-conservative).

20

#### BRIEF DESCRIPTION OF DRAWINGS

For a better understanding of the present invention, reference is made to the below-referenced accompanying drawings.

25 Figure 1.1 is a cross-sectional view of a near chip-size basic leadless semiconductor packaging apparatus having packaging mold-lines shown with respect to a leadless semiconductor device configuration having a die located in the "up" position with a wire bonded to a stamped lead frame and another wire bonded to a die attach pad, in accordance with the present invention.

30 Figure 1.2 is a cross-sectional view of a near chip-size leadless semiconductor packaging apparatus having packaging mold-lines shown with respect to a leadless semiconductor device configuration having a stamped lead-frame and a die with a wire therebetween bonded in the "down" position, in accordance with the present invention.

Figure 1.3 is a cross-sectional view of a near chip-size thermal leadless semiconductor

WO 01/75938

PCT/US01/10190

packaging apparatus having packaging mold-lines shown with respect to a leadless semiconductor device configuration having a stamped lead-frame and a die with a wire therebetween bonded in the "up" position and with the die sharing a common die attach pad, in accordance with the present invention.

5 Figure 1.3a is a cross-sectional view of a near chip-size thermal leadless semiconductor packaging apparatus having packaging mold-lines shown with respect to a leadless semiconductor device configuration having a stamped lead-frame and a die with a wire therebetween bonded in the "up" position and with a lower surface of the die attach pad being unmolded (i.e., exposed), in accordance with the present invention.

10 Figure 1.4 is a cross-sectional view of a near chip-size leadless semiconductor packaging apparatus having packaging mold-lines shown with respect to a leadless semiconductor device configuration having a stamped lead-frame and a center pad located beneath the stamped lead-frame with a wire bonded therebetween in the "up" position, in accordance with the present invention.

15 Figure 1.4a is a cross-sectional view of a near chip-size leadless semiconductor packaging apparatus having packaging mold-lines shown with respect to a leadless semiconductor device configuration having a stamped lead-frame and a center pad located beneath the stamped lead-frame with a wire bonded therebetween in the "up" position and a lower surface of the center pad being unmolded, in accordance with the present invention.

20 Figure 1.4b is a cross-sectional view of a near chip-size leadless semiconductor packaging apparatus having packaging mold-lines shown with respect to a leadless semiconductor device configuration having a stamped lead-frame and a flip chip located beneath the stamped lead-frame with at least one conducting particle contacting and being disposed between the lead-frame and the flip chip, in accordance with the present invention.

25 Figure 1.4c is a cross-sectional view of a chip-size leadless semiconductor packaging apparatus having packaging mold-lines shown with respect to a leadless semiconductor device configuration having a stamped lead-frame and a flip chip located above the stamped lead-frame with at least one conducting particle contacting and being disposed between the lead-frame and the flip chip, in accordance with the present invention.

30 Figure 1.5 is a cross-sectional view of a chip-size leadless semiconductor packaging apparatus having packaging mold-lines shown with respect to a leadless semiconductor device configuration having a die located on a lead-frame and a wire bonded therebetween in the "up"

WO 01/75938

PCT/US01/10390

position, in accordance with the present invention.

Figure 1.6 is a cross-sectional view of a chip-size leadless semiconductor packaging apparatus having packaging mold-lines shown with respect to a leadless semiconductor device configuration having a die located on at least one lead-frame and a wire bonded therebetween in the "up" position, in accordance with the present invention.

Figure 1.7 is a cross-sectional view of a chip-size leadless semiconductor packaging apparatus having packaging mold-lines shown with respect to a leadless semiconductor device configuration having an exposed die laterally located with regard to the lead-frame and a wire bonded therebetween in the "up" position, in accordance with the present invention.

10 Figure 1.8 is a cross-sectional view of a leadless semiconductor packaging apparatus having packaging mold-lines shown with respect to at least one leadless semiconductor device, as would occur during a manufacturing process, in accordance with the present invention.

15 Figure 2.0 is a cross-sectional view of a windowed leadless semiconductor packaging apparatus with a leadless semiconductor device configuration having a stamped lead frame, a die, and a bonded wire being packaged by a sight lid sealed against a cured polymeric material having a flush mold-line located at the interior portion of the stamped lead frame, in accordance with the present invention.

20 Figure 3.0 is a perspective view of a windowed leadless semiconductor packaging apparatus having a stamped lead-frame having a plurality of leads sharing a common die by bonding a wire therebetween as viewed through a sight lid, in accordance with the present invention.

Figure 4.0 is a flow-chart of a fabrication method for packaging a leadless semiconductor packaging apparatus, in accordance with the present invention.

25 Figure 5.0 is a flow-chart of a fabrication method for packaging a windowed leadless semiconductor packaging apparatus, in accordance with the present invention.

Reference numbers refer to the same or equivalent parts of the present invention throughout the several figures of the drawings.

#### MODE FOR CARRYING OUT THE INVENTION

30 Figure 1.1 illustrates, in cross-section, a first embodiment, a "near chip-size" leadless semiconductor packaging apparatus 1000 (i.e., where the packaging and external lead portions extend minimally beyond the plan-form area of a given chip) having packaging mold-lines 10 and

WO 01/75938

PCT/US01/10390

a unique "stamped" and "bent" lead-frame 30 formed by "stamping" and "bending" a conductive material such as copper, with an effective solderable length 60 and effecting a bend 34, the unique stamped and bent lead-frame 30 being uniquely compressively retained by a mold 11 (not shown), in accordance with the present invention. Other leadless semiconductor device components therein shown are a die 40, a die attach pad 41 which may be formed of a pad metal, and a bonded wire 50 formed from a conductive material such as gold. The mold 11 (not shown) uniquely effectively retains, by compression (e.g., using a hot-press), a polymeric material 12, such as a polymeric molding compound, for surrounding only the interior portion of the stamped and bent lead-frame 30, thereby uniquely preserving a clean solderable area on the stamped and bent lead-frame 30, and thereby avoiding the environmentally-unfriendly related art need for de-flashing of excess packaging material. A method for trimming the stamped and bent lead-frame 30 may include sawing or punch-cutting in the direction indicated by arrow 70.

Figure 1.2 is a cross-sectional view of a second embodiment, a near chip-size leadless semiconductor packaging apparatus 1000, having packaging mold-lines 10, a unique stamped and bent lead-frame 30 formed by stamping and bending a conductive material such as copper, effecting a bend 34, and a die 40 with a wire 50, formed from a conductive material such as gold, therebetween bonded in the "down" position, in accordance with the present invention. These components are uniquely compression-molded in the manner discussed with respect to Figure 1.1.

Figure 1.3 is a cross-sectional view of a third embodiment, a near chip-size thermal leadless semiconductor packaging apparatus 1000 having packaging mold-lines 10, a unique stamped and bent lead-frame 30 formed by stamping and bending a conductive material such as copper, effecting a bend 34, and a die 40 with a wire 50 formed from a conductive material such as gold, therebetween bonded in the "up" position and with the stamped and bent lead-frame 30 and the die 40 sharing a common die attach pad 41 being unmolded (i.e., exposed), in accordance with the present invention. These components are uniquely compression-molded in the manner discussed with respect to Figure 1.1.

Figure 1.3a is a cross-sectional view of a fourth embodiment, a near chip-size thermal leadless semiconductor packaging apparatus 1000 having packaging mold-lines 10, a unique stamped and bent lead-frame 30 formed by stamping and bending a conductive material such as copper, effecting a bend 34, and a die 40 with a wire 50 formed from a conductive material such as gold, therebetween bonded in the "up" position and with a lower surface of the die attach pad 41 being unmolded (i.e., exposed), in accordance with the present invention. These components

WO 01/75938

PCT/US01/10390

are uniquely compression-molded in the manner discussed with respect to Figure 1.1.

5 Figure 1.4 is a cross-sectional view of a fifth embodiment, a near chip-size leadless semiconductor packaging apparatus 1000 having packaging mold-lines 10, a unique stamped and bent lead-frame 30 formed by stamping and bending a conductive material such as copper, effecting a bend 34, and a center pad 40a located beneath the stamped and bent lead-frame 30 with a wire 50 formed from a conductive material such as gold, bonded therebetween in the "up" position, in accordance with the present invention. These components are uniquely compression-molded in the manner discussed with respect to Figure 1.1.

10 Figure 1.4a is a cross-sectional view of a sixth embodiment, a near chip-size leadless semiconductor packaging apparatus 1000 having packaging mold-lines 10, a stamped and bent lead-frame 30 formed by stamping and bending a conductive material such as copper, effecting a bend 34, and a center pad 40a located beneath the stamped and bent lead-frame 30 with a wire 50 formed from a conductive material such as gold, bonded therebetween in the "up" position and a lower surface of the center pad 40a being unmolded (i.e., exposed), in accordance with the 15 present invention. These components are uniquely compression-molded in the manner discussed with respect to Figure 1.1.

20 Figure 1.4b is a cross-sectional view of a seventh embodiment, a near chip-size leadless semiconductor packaging apparatus 1000 having packaging mold-lines, a unique stamped and bent lead-frame 30 formed by stamping and bending a conductive material such as copper, effecting a bend 34, and a flip chip 40b located beneath the stamped and bent lead-frame 30 with at least one conducting particle 51 contacting and being disposed between the stamped and bent lead-frame 30 and the flip chip 40b, in accordance with the present invention. These components are uniquely compression-molded in the manner discussed with respect to Figure 1.1.

25 Figure 1.4c is a cross-sectional view of an eighth embodiment, a "chip-size" leadless semiconductor packaging apparatus 1000 having packaging mold-lines 10, a unique stamped lead-frame 30 formed by stamping a conductive material such as copper, and a flip chip 40b located above the stamped lead-frame 30 with at least one conducting particle 51 contacting and being disposed between the stamped lead-frame 30 and the flip chip 40b, in accordance with the present invention. These components are uniquely compression-molded in the manner discussed with 30 respect to Figure 1.1.

Figure 1.5 is a cross-sectional view of a ninth embodiment, a chip-size leadless semiconductor packaging apparatus 1000 (i.e., where the packaging and external lead portions

WO 01/75938

PCT/US01/10190

extend very minimally beyond the plan-form area of a given chip, where the plan-form package area is less than or equal to 1.2 times the die plan-form area) having packaging mold-lines 10, a die 40 located on a unique stamped lead-frame 30 formed by stamping a conductive material such as copper, and a wire 50 formed from a conductive material such as gold, bonded therebetween in the "up" position, in accordance with the present invention. These components are uniquely compression-molded in the manner discussed with respect to Figure 1.1.

Figure 1.6 is a cross-sectional view of a tenth embodiment, a chip-size leadless semiconductor packaging apparatus 1000 having packaging mold-lines 10, a die 40 located on at least one unique stamped lead-frame 30 formed by stamping a conductive material such as copper, and a wire 50 formed from a conductive material such as gold, bonded therebetween in the "up" position, in accordance with the present invention. These components are uniquely compression-molded in the manner discussed with respect to Figure 1.1.

Figure 1.7 is a cross-sectional view of an eleventh embodiment, a leadless semiconductor packaging apparatus 1000 having packaging mold-lines, an exposed die 40 laterally located with regard to the unique stamped lead-frame 30 formed by stamping a conductive material such as copper, and a wire 50 formed from a conductive material such as gold, bonded therebetween in the "up" position, in accordance with the present invention. These components are uniquely compression-molded in the manner discussed with respect to Figure 1.1.

Figure 1.8 illustrates, in cross-section, a near chip-size leadless semiconductor packaging apparatus 1000, consistent with the third embodiment, having packaging mold-lines 10, at least one unique stamped and bent lead-frame 30 which may be formed by stamping and bending a conductive material such as copper, effecting a bend 34, with an effective solderable length 60, being retained by a mold 11 (not shown) as would occur during a manufacturing process, in accordance with the present invention. Other leadless semiconductor device components therein shown are at least one die 40, at least one die attach pad 41 which may be formed of a pad metal, and at least one bonded wire 50 formed from a conductive material such as gold. In packaging a plurality of leadless semiconductor devices, a method for separating the mass-produced packaged devices in an assembly line fashion may include sawing or punch-cutting in the direction indicated by arrow 70. The mold 11 (not shown) uniquely and effectively retains, via compressive forces, at least one polymeric material 12 for surrounding only the interior portion of the at least one unique stamped and bent lead-frame 30 (i.e., without leakage to an exterior portion the at least one stamped lead-frame), thereby preserving clean solderable areas on an external portion of the at

WO 01/75938

PCT/US01/10390

least one unique stamped and bent lead-frame 30, and thereby avoiding the related art need for de-flashing of excess packaging material.

Figure 2.0 illustrates, in cross-section, another embodiment of the present invention, a windowed leadless semiconductor packaging apparatus 2000 having a leadless semiconductor device comprising a unique stamped and bent lead-frame 30 formed by stamping and bending a conductive material such as copper, effecting a bend 34, a die 40 adhered to a die attach pad 41 by a non-electrically conductive adhesive material 42, and a wire 50 formed from a material such as gold, being packaged by a sight lid 80, formed from a visually transparent material such as a glass or a high temperature polymer, uniquely sealed against a cured polymeric material body 13 by a sealant material 14 such as a UV-curable epoxy resin, in accordance with the present invention. Sealant material 14 is compressed by the sight lid 80 into an outboard channel 15 of a unique dual channel sealant seat such that a portion of the sealant material 14 flows into an inboard channel 16 for providing a uniquely larger sealing surface area and better sealing against contaminant entry. The present invention, however, is not limited to the use of dual channels, but may utilize at least one channel as required by the given semiconductor circuit to be packaged. The cured polymeric material body 13 has an overlapping tapered mold line located at both the exterior portion 31 and the interior portion 32 of the stamped lead-frame 30 and a flush mold line located between the die attach pad 41 and the interior portion 33 of stamped lead-frame 30. A reinforced fill material 15 is cured unto a lower surface of the interior portion 33 of the stamped lead-frame 30, such interior portion 33 formerly being uniquely compressively retained by the mold 11 (not shown).

Figure 3.0 illustrates, in perspective view, a windowed leadless semiconductor packaging apparatus 2000 having a stamped and/or bent lead-frame 30 formed by stamping and/or bending a conductive material such as copper, such unique stamping effecting removal of lead-frame material as indicated by void 35, sharing a common die 40 by bonding a wire 50 therebetween as viewed through the sight lid 80 sealed against a unique sealant seat 15, 16 having at least one channel formed in the cured polymeric body 13, the polymeric body 13 being formed by the foregoing unique compression-molding technique, in accordance with the present invention.

Figure 4.0 flow-charts the general fabrication method M-1 for packaging at least one leadless semiconductor packaging apparatus 1000, in accordance with the present invention. Method M-1 comprises the steps of: (a) providing at least one stamped lead-frame having at least one lead, by sawing or punch-cutting a lead-frame material as indicated by process block 100, (b)

WO 01/75938

PCT/US01/10390

attaching a die to the at least one lead-frame by applying a non-electrically conductive adhesive material (die attach) as indicated by process block 200, (c) curing the non-electrically conductive adhesive material as indicated by process block 300, (d) bonding a wire from the die to each of the at least one lead as indicated by process block 400, (e) molding the semiconductor device components in another polymeric material, such as a polymeric molding compound, by a technique such as hot compression-molding using a hot-press having an upper platen and a lower platen, effecting a unique sealing orifice from which the external lead portion extends via a compressive force and a nominally localized deformation, thereby forming the at least one leadless semiconductor packaging apparatus 1000, as indicated by process block 500, (f) marking, by 5

lasing, the at least one formed leadless semiconductor packaging apparatus 1000 as indicated by process block 600, (g) singulating, the at least one laser-marked leadless semiconductor packaging apparatus 1000, as indicated by process block 700, (h) packing the at least one singulated leadless semiconductor packaging apparatus 1000 as indicated by process block 800, and (i) shipping the 10

at least one packed leadless semiconductor packaging apparatus 1000 as indicated by process block 900.

15 Figure 5.0 flow-charts the general fabrication method M-2 for packaging at least one windowed leadless semiconductor packaging apparatus 2000, in accordance with the present invention. Method M-2 comprises the steps of: (a) providing at least one stamped lead-frame having at least one lead, by pre-plating a lead-frame material as indicated by process block 102, (b) molding the at least one stamped pre-plated lead-frame in a polymeric material, such as a 20

polymeric molding compound, by a technique such as hot compression-molding using a hot-press having an upper platen and a lower platen, effecting a unique sealing orifice from which the external lead portion extends via a compressive force and a nominally localized deformation, as indicated by process block 103, (c) sawing or punch-cutting the lead-frame material as indicated by process block 101, (d) attaching a die to the at least one lead-frame (die attach) as indicated by process block 202, (e) curing the non-electrically conductive adhesive material as indicated by process block 303, (f) bonding a wire from the die to the at least one lead as indicated by process block 404, (g) installing a window onto the molded lead-frame by applying a sealant such as a UV-curable epoxy as indicated by process block 505, thereby forming the at least one leadless 25

semiconductor packaging apparatus 2000, (h) marking, by laser techniques, the at least one formed windowed leadless semiconductor packaging apparatus 2000 as indicated by process block 606, (i) singulating the at least one laser-marked windowed leadless semiconductor packaging apparatus 30

WO 01/75938

PCT/US01/10390

2000, as indicated by process block 707, (j) packing the at least one singulated windowed leadless semiconductor packaging apparatus 2000 as indicated by process block 808, and (k) shipping the at least one packed windowed leadless semiconductor packaging apparatus 2000 as indicated by process block 909.

5 Information as herein shown and described in detail is fully capable of attaining the above-described object of the invention, the presently preferred embodiment of the invention, and is, thus, representative of the subject matter which is broadly contemplated by the present invention. The scope of the present invention fully encompasses other embodiments which may become obvious to those skilled in the art, and is to be limited, accordingly, by nothing other than the appended

10 claims, wherein reference to an element in the singular is not intended to mean "one and only one" unless explicitly so stated, but rather "one or more." All structural and functional equivalents to the elements of the above-described preferred embodiment and additional embodiments that are known to those of ordinary skill in the art are hereby expressly incorporated by reference and are intended to be encompassed by the present claims. Moreover, no requirement exists for a device or method

15 to address each and every problem sought to be resolved by the present invention, for such to be encompassed by the present claims. Furthermore, no element, component, or method step in the present disclosure is intended to be dedicated to the public regardless of whether the element, component, or method step is explicitly recited in the claims. However, it should be readily apparent to those of ordinary skill in the art that various changes and modifications in form, semiconductor

20 material, and fabrication material detail may be made without departing from the spirit and scope of the inventions as set forth in the appended claims. No claim herein is to be construed under the provisions of 35 U.S.C. 112, sixth paragraph, unless the element is expressly recited using the phrase

"means for."

WO 01/75938

PCT/US01/10390

## CLAIMS

What is claimed:

1. A leadless semiconductor product packaging apparatus for packaging a semiconductor circuit, comprising:

- a. a lead-frame,

said lead-frame having an internal lead portion and an external lead portion,

said lead-frame being in electrical contact with said semiconductor circuit, and

said lead-frame being formed by stamping a lead frame material; and

- b. a housing member,

said housing member comprising a housing material, and

said housing material encapsulating said lead-frame such that said external lead

10 portions are exposed to provide solderable regions.

2. The leadless semiconductor product packaging apparatus, as recited in claim 1,

wherein said semiconductor circuit comprises:

- a. at least one die attach pad,

wherein said semiconductor circuit is mounted on said die attach pad; and

- b. at least one wire,

wherein said at least one wire is wire-bonded to effect an electrical connection

5 between said circuit and said internal lead portion,

wherein said at least one wire is formed from an electrically conducting material

selected from a group of electrically conducting materials consisting

essentially of copper, aluminum, and gold,

10 wherein said housing material is further compression-molded around said die attach pad,

said at least one wire, and said internal lead portion,

wherein said housing material is not compression-molded around said lead external

portion, and

15 wherein said stamped lead-frame is mechanically bent into a desired configuration for

facilitating fit of said leadless semiconductor product packaging apparatus to a size

in a range of chip-size to near chip-size.

WO 01/75938

PCT/US01/10390

- 20 3. The leadless semiconductor product packaging apparatus, as recited in claim 2, wherein

said lead frame material has a thickness in a range of 6 mils or less.

4. The leadless semiconductor product packaging apparatus, as recited in claim 1, wherein

said lead frame material has a thickness in a range of 6 mils or less.

5. The leadless semiconductor product packaging apparatus, as recited in claim 4, wherein

said leadless semiconductor product comprises:

a. at least one die attach pad,

wherein said semiconductor circuit is mounted on said die attach pad; and

b. at least one wire,

wherein said at least one wire is wire-bonded to effect an electrical connection

between said circuit and said internal lead portion,

wherein said at least one wire is formed from an electrically conducting material

selected from a group of electrically conducting materials consisting

essentially of copper, aluminum, and gold,

10 wherein said housing material is further compression-molded around said die attach pad,

said at least one wire, and said internal lead portion,

wherein said housing material is not compression-molded around said lead external

portion, and

15 wherein said stamped lead-frame is mechanically bent into a desired configuration for

facilitating fit of said leadless semiconductor product packaging apparatus to a size

in a range of chip-size to near chip-size.

6. The leadless semiconductor product packaging apparatus, as recited in claim 1, further

comprising:

a. a window lid member,

5 wherein said window lid member forms a portion of said housing member, and

wherein said window lid member is formed from a visually transparent material

selected from a group of visually transparent materials consisting essentially

of a polymer and a glass;

b. a sealant material;

WO 01/75938

PCT/US01/10390

- 10        c.     a sealant seat,

said sealant seat comprising at least one channel disposed on an upper surface of

said housing member for providing a larger sealing surface area, and

said sealant material being disposed between said housing member and said

window lid member within said at least one channel for preventing

15            contaminant entry.

7.     The leadless semiconductor product packaging apparatus, as recited in claim 2, wherein

a die is attachable, by a non-electrically conductive polymer, to each said internal portion

of said lead-frame.

8.     The leadless semiconductor product packaging apparatus, as recited in claim 5, wherein

a die is attachable, by a non-electrically conductive polymer, to each said internal portion

of said lead-frame.

9.     The leadless semiconductor product packaging apparatus, as recited in claim 1,

wherein said housing material comprises a polymeric molding compound,

wherein said housing member comprises said housing material being compression-molded,

whereby said external lead portion is exposed,

5            thereby preserving a solderable area on said external lead portion, and

thereby avoiding de-flashing of said external lead portion.

10.    The leadless semiconductor product packaging apparatus, as recited in claim 1,

wherein said lead-frame is formed from at least one electrically conducting material

selected from a group of electrically conducting materials consisting essentially of

copper, aluminum, and gold,

5            wherein said housing material comprises at least one material selected from a group of

housing materials consisting essentially of a polymer and a ceramic, and

wherein said polymer is selected from a group of polymers consisting essentially of an

epoxy, a polyimide, and a bismaleimide.

WO 01/75938

PCT/US01/10390

11. A method for fabricating a leadless semiconductor product packaging apparatus for packaging a semiconductor circuit, comprising the steps of:

- a. providing a lead-frame,

said lead-frame having an internal lead portion and an external lead portion,

said lead-frame being in electrical contact with said semiconductor circuit, and

said lead-frame being formed by stamping a lead-frame material; and

- b. providing a housing member,

said housing member comprising a housing material, and

said housing material encapsulating said lead-frame such that said external lead

portions are exposed to provide solderable regions, and

thereby forming said leadless semiconductor product packaging apparatus.

- 10

12. The method for fabricating a leadless semiconductor product packaging apparatus, as recited in claim 11, wherein said leadless semiconductor circuit comprises:

- a. at least one die attach pad,

wherein said semiconductor circuit is mounted on said die attach pad; and

- b. at least one wire,

wherein said at least one wire is wire-bonded to effect an electrical connection

between said circuit and said internal lead portion,

wherein said at least one wire is formed from an electrically conducting material

selected from a group of electrically conducting materials consisting

essentially of copper, aluminum, and gold,

wherein said housing material is further compression-molded around said die attach pad,

said at least one wire, and said internal lead portion,

wherein said housing material is not compression-molded around said lead external

portion, and

- 10

15. wherein said lead-frame is mechanically bent into a desired configuration for facilitating

fit of said leadless semiconductor product packaging apparatus to a size in a range

of chip-size to near chip-size, and

thereby forming said leadless semiconductor product packaging apparatus.

- 15

- 20 13. The method for fabricating a leadless semiconductor product packaging apparatus, as

WO 01/75938

PCT/US01/10390

recited in claim 12, wherein said lead frame material has a thickness in a range of 6 mils or less.

14. The method for fabricating a leadless semiconductor product packaging apparatus, as recited in claim 11, wherein said lead frame material has a thickness in a range of 6 mils or less.

15. The method for fabricating a leadless semiconductor product packaging apparatus, as recited in claim 14, wherein said leadless semiconductor product comprises:

a. at least one die attach pad,

wherein said at least one semiconductor circuit is mounted on said die attach pad;

5 and

b. at least one wire,

wherein said at least one wire is wire-bonded to effect an electrical connection between said circuit and said internal lead portion,

10 wherein said at least one wire is formed from an electrically conducting material selected from a group of electrically conducting materials consisting essentially of copper, aluminum, and gold,

wherein said housing material is further compression-molded around said die attach pad,

said at least one wire, and said internal lead portion,

wherein said housing material is not compression-molded around said lead external 15 portion, and

wherein said lead-frame is mechanically bent into a desired configuration for facilitating fit of said leadless semiconductor product packaging apparatus to a size in a range of chip-size to near chip-size, and

thereby forming said leadless semiconductor product packaging apparatus.

16. The method for fabricating a leadless semiconductor product packaging apparatus, as recited in claim 14, further comprising the steps of:

a. providing a window lid member,

wherein said window lid member forms a portion of said housing member, and

5 wherein said window lid member is formed from a visually transparent material

WO 01/75938

PCT/US01/10390

- selected from a group of visually transparent materials consisting essentially of a polymer and a glass;

- b. providing a sealant material;

- c. providing a sealant seat,

- 10 said sealant seat comprising at least one channel disposed on an upper surface of said housing member for providing a larger sealing surface area, and said sealant material being disposed between said housing member and said window lid member within said at least one channel for preventing contaminant entry, and

- 15 thereby forming said leadless semiconductor product packaging apparatus.

17. The method for fabricating a leadless semiconductor product packaging apparatus, as recited in claim 12, wherein a die is attachable, by a non-electrically conductive polymer, to each said internal portion of said lead-frame.

18. The method for fabricating a leadless semiconductor product packaging apparatus, as recited in claim 15, wherein a die is attachable, by a non-electrically conductive polymer, to each said internal portion of said lead-frame.

19. The method for fabricating a leadless semiconductor product packaging apparatus, as recited in claim 11, wherein said housing material comprises a polymeric molding compound, wherein said housing member comprises said housing material being compression-molded, 5 whereby said external lead portion is exposed, thereby preserving a solderable area on said external lead portion, and thereby avoiding de-flashing of said external lead portion.

20. The method for fabricating a leadless semiconductor product packaging apparatus, as recited in claim 11, wherein said lead-frame is formed from an electrically conducting material, said electrically conducting material comprising copper,

WO 01/75938

PCT/US01/10390

- 5 wherein said housing material comprises at least one material selected from a group of housing materials consisting essentially of a polymer and a ceramic, and wherein said polymer is selected from a group of polymers consisting essentially of an epoxy, a polyimide, and a bismaleimide.

21. A method for fabricating at least one leadless semiconductor product packaging apparatus for packaging at least one semiconductor circuit, comprising the steps of:

- a. stamping a lead-frame material for providing at least one stamped lead-frame, said lead-frame material having a thickness in a range of less than 6 mils, said at least one stamped lead-frame having an internal lead portion and an external lead portion;

- b. applying a non-electrically conductive adhesive material to an interface between a die and said internal lead portion for attaching said die to said internal lead portion for each of said at least one lead frame;

- c. curing said non-electrically conductive adhesive material for each of said at least one stamped lead-frame;

- d. providing a wire for each of said at least one stamped lead-frame, said wire having a first end and a second end, wherein said first wire end is bonded to said die, and wherein said second wire end is bonded to said lead internal portion;

- e. molding a housing material around said lead internal portion in a mold using a hot-press to form a housing member for each of said at least one stamped lead-frame, said mold having an upper portion and a lower portion, said hot-press having an upper platen and a lower platen being parallel to one another, said upper mold portion being inwardly disposed on said upper platen, said lower mold portion being inwardly disposed on said lower platen, said lead internal portion being attached to said die, said upper hot-press platen and said lower hot-press platen being translated together in a direction normal to said platens respectively compressing said upper mold portion against said lower mold portion, whereby a compressive force is exerted by said mold portions on said external lead

WO 01/75938

PCT/US01/10390

- portion to create a nominally localized deformation on said external lead portion,

- 30 whereby a leak-proof seal, between said internal lead portion and said external lead portion, is effected via said compressive force and said nominally localized deformation, and

- whereby said housing material is cured within said mold,

- 35 thereby forming said housing member, and

- thereby forming said at least one leadless semiconductor product packaging apparatus,

- f. marking, by lasing, said external lead portion of each of said at least one formed leadless semiconductor product packaging apparatus;

- 40 g. singulating said external lead portion of each of said at least one formed leadless semiconductor product packaging apparatus from one another;

- h. packing said singulated said at least one leadless semiconductor product packaging apparatus; and

- i. shipping said packed leadless semiconductor product packaging apparatus.

22. The method for fabricating at least one leadless semiconductor product packaging apparatus for packaging at least one semiconductor circuit, as recited in claim 21, wherein said lead-frame is mechanically bent into a desired configuration for facilitating fit of said leadless semiconductor product packaging apparatus to a size in a range of chip-size to near chip-size.

- 5 23. A method for fabricating at least one windowed leadless semiconductor product packaging apparatus for packaging at least one semiconductor circuit, comprising the steps of:

- a. stamping a lead-frame material for providing at least one stamped lead-frame, said lead-frame material having a thickness in a range of less than 6 mils, said at least one stamped lead-frame having an internal lead portion and an external lead portion;

- b. pre-plating said at least one stamped lead-frame;

- 5 c. molding a housing material around said lead internal portion in a mold using a hot-press to form a housing member for each of said at least one stamped lead-frame,

WO 01/75938

PCT/US01/10390

- 10        said mold having an upper portion and a lower portion,

said upper mold portion having a mold-line for accommodating a sight lid,

said hot-press having an upper platen and a lower platen being parallel to one

another,

said upper mold portion being inwardly disposed on said upper platen,

15        said lower mold portion being inwardly disposed on said lower platen,

said lead internal portion being attached to said die,

said upper hot-press platen and said lower hot-press platen being translated

together in a direction normal to said platens respectively compressing said

upper mold portion against said lower mold portion,

20        whereby a compressive force is exerted by said mold portions on said external lead

portion to create a nominally localized deformation on said external lead

portion,

whereby a leak-proof seal, between said internal lead portion and said external lead

25        portion, is effected via said compressive force and said nominally localized

deformation, and

whereby said housing material is cured within said mold,

thereby forming said housing member, and

thereby forming said at least one leadless semiconductor product packaging

apparatus,

30        d. applying a non-electrically conductive adhesive material to an interface between a

die and said internal lead portion for attaching said die to said internal lead portion

for each of said at least one lead frame;

e. curing the non-electrically conductive adhesive material for each of said at least one

lead frame;

35        f. providing a wire for each of said at least one lead frame,

said wire having a first end and a second end,

wherein said first wire end is bonded to said die, and

wherein said second wire end is bonded to said lead internal portion;

40        g. installing a window lid member onto said housing member by curing a sealant

material into a sealant seat having at least one channel,

said sealant being interracially disposed between said window and said molded

WO 01/75938

PCT/US01/10390

- lead-frame,

said sealant being compressed by said sight lid, a portion of said sealant material

being thereby pressed into said at least one channel,

45 whereby seal is effected, and

thereby forming said at least one windowed leadless semiconductor product

packaging apparatus having said window lid member;

h. marking, by lasing, said external lead portion of said at least one windowed formed

leadless semiconductor product packaging apparatus;

50 i. singulating said external lead portion of said at least one windowed formed leadless

semiconductor product packaging apparatus from one another;

j. packing said singulated at least one windowed leadless semiconductor product

packaging apparatus; and

k. shipping said packed at least one windowed leadless semiconductor product

packaging apparatus.

- 55

24. The method for fabricating at least one windowed leadless semiconductor product

packaging apparatus for packaging at least one semiconductor circuit, as recited in claim

22, wherein said lead-frame is mechanically bent into a desired configuration for

facilitating fit of said leadless semiconductor product packaging apparatus to a size in a

range of chip-size to near chip-size.

- 5

1/7

Figure 1.1

Figure 1.2

Figure 1.3a

Figure 1.4

SUBSTITUTE SHEET (RULE 26)

WO 01/75938