(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5174355号

(P5174355)

(45) 発行日 平成25年4月3日(2013.4.3)

(24) 登録日 平成25年1月11日(2013.1.11)

(51) Int.Cl.

H05K 3/46 (2006.01)

H01L 23/12 (2006.01)

F 1

H05K 3/46

H01L 23/12 501B

請求項の数 8 (全 15 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2007-24228 (P2007-24228)    |

| (22) 出願日  | 平成19年2月2日 (2007.2.2)          |

| (65) 公開番号 | 特開2008-192740 (P2008-192740A) |

| (43) 公開日  | 平成20年8月21日 (2008.8.21)        |

| 審査請求日     | 平成21年12月16日 (2009.12.16)      |

|           |                                           |

|-----------|-------------------------------------------|

| (73) 特許権者 | 000190688<br>新光電気工業株式会社<br>長野県長野市小島田町80番地 |

| (74) 代理人  | 100091672<br>弁理士 岡本 啓三                    |

| (72) 発明者  | 荒井 直<br>長野県長野市小島田町80番地 新光電気<br>工業株式会社内    |

審査官 中田 誠二郎

最終頁に続く

(54) 【発明の名称】配線基板及びその製造方法と半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

基板と、前記基板の少なくとも上面に形成され、垂直方向に立設する層間接続部が一体的に設けられた第1配線パターンとにより構成される第1ユニット配線板と、

前記第1ユニット配線板の上に形成され、上下側を導通可能にする第2配線パターンを備えた第2ユニット配線板と、

前記第1ユニット配線板と前記第2ユニット配線板の間に充填された樹脂部とを有し、

前記第1配線パターンは電源プレーン及びグラントプレーンを含み、前記第2配線パターンは前記第1ユニット配線板の前記層間接続部に接続され、

前記第1配線パターン及びそれに繋がって立設する前記層間接続部は、リードフレームが加工されて一体的に形成され、前記第1配線パターンの厚みは前記第2配線パターンの厚みより厚いことを特徴とする配線基板。 10

## 【請求項 2】

前記第1ユニット配線板の前記基板は貫通電極を備えており、

前記第1ユニット配線板は、前記基板の両面側に、前記貫通電極に接続されて外側に前記層間接続部が立設した前記第1配線パターンがそれぞれ形成されて構成され、

前記第2ユニット配線板が前記第1ユニット配線板の両面側の第1配線パターンの前記層間接続部にそれぞれ接続されて配置されており、

前記樹脂部は、前記第1ユニット配線板とその両面側に配置された前記第2ユニット配線板との間にそれぞれ充填されていることを特徴とする請求項1に記載の配線基板。

10

20

**【請求項 3】**

請求項 1 又は 2 の配線基板と、

前記配線基板における前記第 2 ユニット配線板の外面側の前記第 2 配線パターンにフリップチップ接続された半導体チップとを有することを特徴とする半導体装置。

**【請求項 4】**

前記第 1 ユニット配線板の上に前記樹脂部に埋設された状態で実装され、前記第 1 配線パターンに接続された電子部品をさらに有することを特徴とする請求項 3 に記載の半導体装置。

**【請求項 5】**

基板と、垂直方向に立設する層間接続部が設けられて、連結部によって相互に繋がって形成された第 1 配線パターンを備えたリードフレームとを用意する工程と、10

前記基板の少なくとも上面に、前記第 1 配線パターンの前記層間接続部が外側に配置されるように前記リードフレームを接着する工程と、

前記リードフレームの前記連結部を除去して前記第 1 配線パターンを相互に分離することにより、前記基板と前記第 1 配線パターンにより構成される第 1 ユニット配線板を得る工程と、

上下側を導通可能にする第 2 配線パターンを備えた第 2 ユニット配線板を用意し、前記第 1 ユニット配線板の前記第 1 配線パターンの前記層間接続部に、前記第 2 ユニット配線板の前記第 2 配線パターンを接続する工程と、

真空トランスファモールド法によって、前記第 1 ユニット配線板と前記第 2 ユニット配線板の間に樹脂を充填することにより、前記第 1 ユニット配線板及び前記第 2 ユニット配線板を一体化する樹脂部を形成する工程とを有し、20

前記リードフレームを用意する工程は、

金属薄板の上に形成されたマスク材をマスクにして、前記金属薄板を厚みの途中までウエットエッティングすることにより前記層間接続部を形成する工程と、

前記層間接続部を形成する工程の前又は後に、前記金属薄板を貫通加工することにより前記第 1 配線パターンを形成する工程とを含むことを特徴とする配線基板の製造方法。

**【請求項 6】**

前記基板を用意する工程において、前記基板は半硬化状態のプリプレグからなり、

前記リードフレームを前記基板に接着する工程において、前記プリプレグを熱処理して硬化させることによって前記基板を得ると共に、前記基板の上に前記リードフレームを接着させることを特徴とする請求項 5 に記載の配線基板の製造方法。30

**【請求項 7】**

前記基板は貫通電極を備えており、

前記リードフレームを前記基板に接着する工程において、前記基板の両面側に、前記貫通電極に接続される前記リードフレームをそれぞれ接着し、

第 1 ユニット配線板を得る工程、及び前記第 2 ユニット配線板を前記第 1 ユニット配線板に接続する工程は、前記基板の両面側で行われ、

前記樹脂部は、前記第 1 ユニット配線板とその両面側に配置された前記第 2 ユニット配線板の間に充填されることを特徴とする請求項 5 に記載の配線基板の製造方法。40

**【請求項 8】**

前記第 1 ユニット配線板を得る工程の後に、第 1 ユニット配線板の上に、電子部品を前記第 1 配線パターンに接続して実装する工程をさらに有し、

樹脂部を形成する工程において、前記電子部品が樹脂部に埋設されることを特徴とする請求項 5 に記載の配線基板の製造方法。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は配線基板及びその製造方法と半導体装置に係り、さらに詳しくは、半導体チップが実装される多層配線を有する配線基板及びその製造方法と半導体装置に関する。50

**【背景技術】****【0002】**

従来、C P Uなどの半導体チップが配線基板の上に実装されて構成される半導体装置がある。半導体チップを実装するための配線基板としては、配線が多層化されて形成されたビルドアップ配線板が一般的に使用されている。

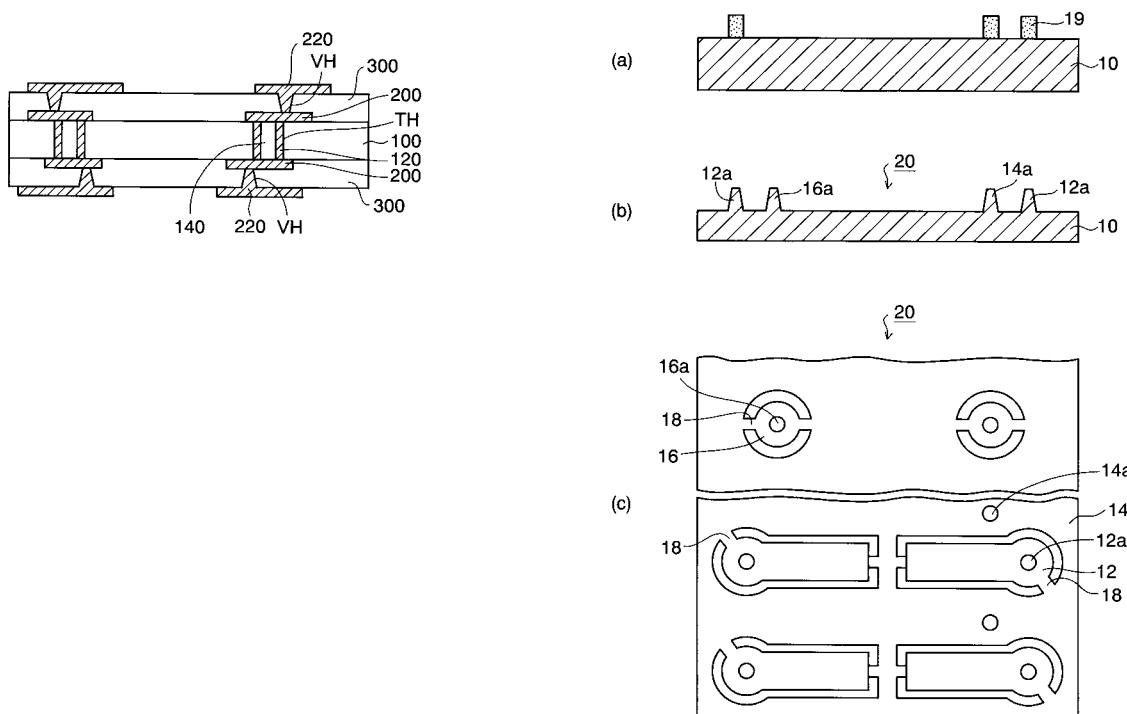

**【0003】**

図1に示すように、従来技術のビルドアップ配線板では、コア基板100にスルーホールTHが設けられており、そのスルーホールTHの内面にスルーホールめっき層120が形成されている。コア基板100の両面にはスルーホールめっき層120を介して相互接続された第1配線パターン200がそれぞれ形成されている。スルーホールTHの孔は樹脂140で埋め込まれている。

10

**【0004】**

また、コア基板100の両面側には、第1配線パターン200を被覆する層間絶縁層300がそれぞれ形成されており、層間絶縁層300には第1配線パターン200に到達する深さのビアホールVHがそれぞれ形成されている。

**【0005】**

さらに、コア基板100の両面側の層間絶縁層300の上には、ビアホールVHを介して第1配線パターン200に接続される第2配線パターン220がそれぞれ形成されている。

**【0006】**

このように、従来技術のビルドアップ配線板では、コア基板100の両面側にセミアディティブ法などによって配線パターンが繰り返し形成されて相互接続された所要の多層配線が形成される。

20

**【0007】**

そのような配線基板に関連する技術としては、特許文献1には、半導体チップ内の配線層数を減らすために半導体チップ内の配線の機能をインターポーザに移し、配線基板の上にインターポーザを介して半導体チップを実装することが記載されている。

**【0008】**

また、特許文献2には、外部接続端子を備えた第1の配線基板に半導体素子が実装された上部装置部と、接続用電極を備えた第2の配線基板に半導体素子が実装された下部装置部との間に、インターポーザ基板を配設することが記載されている。

30

【特許文献1】特開2001-102479号公報

【特許文献2】特開2004-273938号公報

**【発明の開示】****【発明が解決しようとする課題】****【0009】**

ところで、近年では半導体チップの高性能化に伴って配線基板の配線パターンのさらなるファインピッチ化や多層化が要求されている。図1に示した従来技術のビルドアップ配線板では、半導体チップの高性能化に対応させて配線パターンのさらなる多層化を行うとき、片面側の配線パターンの追加のみで対応できる場合であっても、反りの発生を防止するためにはコア基板の両面側に配線パターンを対称に形成する必要があり、無駄なコストがかかる問題がある。

40

**【0010】**

特に、C P Uなどの高性能な半導体チップが実装される配線基板では、厚膜化が要求される電源ラインやグラウンドラインが多く、形成に手間がかかる配線パターンの層数が膨大になるケースが想定され、コスト上昇や歩留りの低下が懸念される。

**【0011】**

本発明は以上の課題を鑑みて創作されたものであり、製造工程が簡略化されて低コスト・高歩留りで製造される信頼性の高い配線基板及びその製造方法と半導体装置を提供することを目的とする。

50

**【課題を解決するための手段】****【0012】**

上記課題を解決するため、本発明は配線基板に係り、基板と、前記基板の少なくとも上面に形成され、垂直方向に立設する層間接続部が一体的に設けられた第1配線パターンにより構成される第1ユニット配線板と、前記第1ユニット配線板の上に形成され、上下側を導通可能にする第2配線パターンを備えた第2ユニット配線板と、前記第1ユニット配線板と前記第2ユニット配線板の間に充填された樹脂部とを有し、前記第1配線パターンは電源プレーン及びグランドプレーンを含み、前記第2配線パターンは前記第1ユニット配線板の前記層間接続部に接続され、前記第1配線パターン及びそれに繋がって立設する前記層間接続部は、リードフレームが加工されて一体的に形成され、前記第1配線パターンの厚みは前記第2配線パターンの厚みより厚いことを特徴とする。 10

**【0013】**

本発明の配線基板では、基板の少なくとも上面にリードフレームから形成された第1配線パターンが接着されており、第1配線パターンはそれと一体的に形成されて垂直方向に立設する層間接続部を備えている。そして、基板と第1配線パターンとにより第1ユニット配線板が構成されている。

**【0014】**

また、第1ユニット配線板の上には、上下側を導通可能にする第2配線パターンを備えた第2ユニット配線板が配置されており、第2ユニット配線板の第2配線パターンが第1ユニット配線板の層間接続部に接続されている。 20

**【0015】**

さらに、第1ユニット配線板と第2ユニット配線板の間に樹脂部が充填されており、樹脂部は第1、第2ユニット配線板を一体化する基板として機能すると共に、第1、第2ユニット配線板を絶縁する層間絶縁部として機能する。

**【0016】**

本発明の配線基板では、厚みの厚いリードフレームから形成された第1配線パターンを備えた第1ユニット配線板の上に第2ユニット配線板50が積層されて多層配線構造を構成している。このため、従来技術のような銅箔やめっきによって配線を形成する場合よりも、低コストで容易に厚膜（例えば100μm以上）の電源プレーンやグランドプレーンを形成することができる。これにより、配線基板の電源プレーンやグランドプレーンの低抵抗化を図ることで電源系を強化することができ、高性能な半導体チップ搭載用の配線基板として対応できるようになる。 30

**【0017】**

また、従来技術の基板上に配線を順次作り込んでいくビルトアップ配線板の製造方法と違って、ユニット配線板を積層し、その間に樹脂を充填して配線基板を構成するので、短手番で配線基板を製造することができ、製造効率を向上させることができる。しかも、良品のユニット配線板を選別して多層化できるので、従来技術よりも製造歩留りを格段に向上させることができる。

**【0018】**

また、本発明の好適な態様では、樹脂部として、フィラーが85～90%含有された樹脂を使用することにより、半導体チップ（シリコンLSIチップ）の熱膨張係数に近似させることができると共に、基板の強度を向上させることができる。これにより、配線基板に半導体チップを実装して半導体装置を構成する際に、高い信頼性が得られるようになる。

**【0019】**

上記した発明において、第1ユニット配線板の基板が貫通電極を備えており、第1ユニット配線板が、基板の両面側に、貫通電極を介して相互接続された前記第1配線パターンがそれぞれ形成されて構成されるようにしてもよい。この態様では、第2ユニット配線板が第1ユニット配線板の両面側の第1配線パターンの層間接続部にそれぞれ接続されて配置され、樹脂部は、第1ユニット配線板と、その両面側に配置された第2ユニット配線板 50

との間にそれぞれ充填される。

**【0020】**

上記課題を解決するため、本発明は配線基板の製造方法に係り、基板と、垂直方向に立設する層間接続部が設けられて、連結部によって相互に繋がって形成された第1配線パターンを備えたリードフレームとを用意する工程と、前記基板の少なくとも上面に、前記第1配線パターンの前記層間接続部が外側に配置されるように前記リードフレームを接着する工程と、前記リードフレームの前記連結部を除去して前記第1配線パターンを相互に分離することにより、前記基板と前記第1配線パターンにより構成される第1ユニット配線板を得る工程と、上下側を導通可能にする第2配線パターンを備えた第2ユニット配線板を用意し、前記第1ユニット配線板の前記第1配線パターンの前記層間接続部に、前記第2ユニット配線板の前記第2配線パターンを接続する工程と、真空トランスマーレル法によって、前記第1ユニット配線板と前記第2ユニット配線板の間に樹脂を充填することにより、前記第1ユニット配線板及び前記第2ユニット配線板を一体化する樹脂部を形成する工程とを有し、前記リードフレームを用意する工程は、金属薄板の上に形成されたマスク材をマスクにして、前記金属薄板を厚みの途中までウェットエッチングすることにより前記層間接続部を形成する工程と、前記層間接続部を形成する工程の前又は後に、前記金属薄板を貫通加工することにより前記第1配線パターンを形成する工程とを含むことを特徴とする。

10

**【0021】**

本発明の配線基板の製造方法を使用することにより、上記した配線基板を容易に製造することができる。

20

**【0022】**

本発明の好適な態様では、リードフレームが接着される基板はプリプレグから形成され、プリプレグが硬化して基板になる際の接着作用によってリードフレームが基板に固着される。また、真空トランスマーレル法によって第1、第2ユニット配線板の間に樹脂を充填するので、それらの隙間が狭い場合であってもフィラーを多量に含む樹脂を信頼性よく充填することができる。

**【発明の効果】**

**【0023】**

以上説明したように、本発明の配線基板は、製造工程が簡略化されて低コスト・高歩留りで製造される。

30

**【発明を実施するための最良の形態】**

**【0024】**

以下、本発明の実施の形態について、添付の図面を参照して説明する。

**【0025】**

(第1の実施の形態)

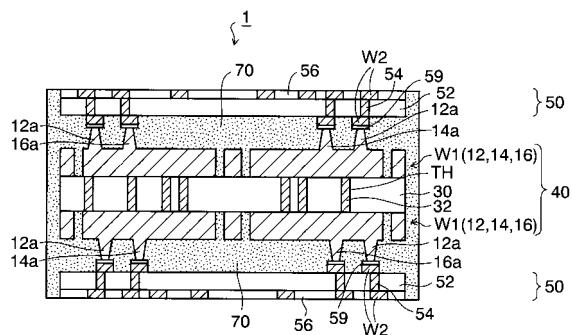

図2～図8は本発明の第1実施形態の配線基板の製造方法を示す断面図、図9は本発明の第1実施形態の配線基板を示す断面図、図10は同じく半導体装置を示す断面図である。

40

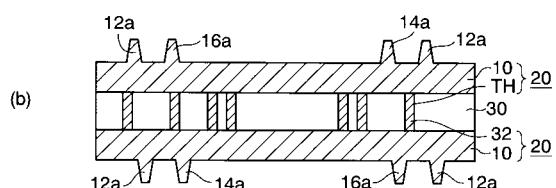

**【0026】**

本実施形態の配線基板の製造方法では、図2(a)に示すように、まず、リードフレームを製造するための厚みが100～200μmの銅合金材からなる金属薄板10を用意する。金属薄板10の材料としては銅合金や銅が好適に使用される。さらに、金属薄板10の上にレジスト19(マスク材)をフォトリソグラフィによってパターニングする。レジスト19は、金属薄板10上の層間接続部が形成される部分に配置される。

**【0027】**

続いて、レジスト19をマスクにして、塩化第二鉄水溶液又は塩化第二銅水溶液を使用するウェットエッチングにより、金属薄膜10を厚みの途中までエッチングする。その後に、レジスト19が除去される。

**【0028】**

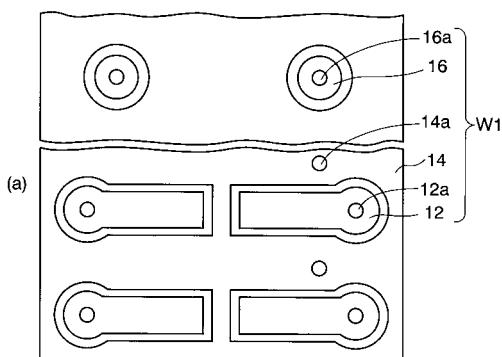

これにより、図2(b)に示すように、金属薄板10に繋がって垂直方向に立設する電源ライン用の層間接続部12a、グランドライン用の層間接続部14a及び信号ライン用の層間接続部16aが形成される。各層間接続部12a, 14a, 16aの高さは例えば30~50μmに設定され、それらの径が0.5mm程度(ピッチ: 1mm程度)の設計ルールで形成することが可能である。

#### 【0029】

次いで、図2(c)に示すように、金型を使用するプレス加工によって層間接続部12a, 14a, 16aが設けられた金属薄板10を打ち抜くことにより、電源プレーン12、グランドプレーン14及び信号線パッド16が画定されてリードフレーム20が得られる。

10

#### 【0030】

このとき、電源プレーン12、グランドプレーン14及び信号線パッド16は連結部18によって繋がった状態となって画定され、グランドプレーン14はリードフレーム20の枠部としても機能する。

#### 【0031】

またこのとき、電源プレーン12、グランドプレーン14及び信号線パッド16は、それらに繋がって立設する電源ライン用の層間接続部12a、グランドライン用の層間接続部14a及び信号ライン用の層間接続部16aがそれぞれ設けられた状態となる。

#### 【0032】

なお、層間接続部12a, 14a, 16aが設けられた金属薄板10の上にレジストをパターニングした後に、金属薄板をウェットエッチングにより貫通加工することにより、電源プレーン12、グランドプレーン14及び信号線パッド16を形成してもよい。

20

#### 【0033】

金属薄板10は長尺状に引き出された状態で加工され、層間接続部12a, 14a, 16aがそれぞれ設けられた電源プレーン12、グランドプレーン14及び信号線パッド16を備えたリードフレーム20が順次形成される。そして、個々のリードフレーム20が得られるように金属薄板10が切断される。

#### 【0034】

後に説明するように、リードフレーム20の連結部18が除去されることにより、電源プレーン12、グランドプレーン14及び信号線パッド16が独立した正規の配線となる。なお、金属薄板10をプレス加工して電源プレーン12、グランドプレーン14及び信号線パッド16を画定した後に、金属薄板10を厚みの途中までエッチングして層間接続部12a, 14a, 16aを形成してもよい。

30

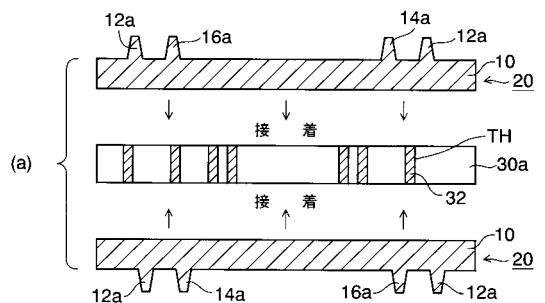

#### 【0035】

次いで、図3(a)に示すように、ガラスクロスやアラミド繊維などにエポキシ樹脂などの樹脂を含侵させたプリプレグ(prepreg)30aを用意する。プリプレグ30aはB-ステージ(半硬化状態)のものが使用される。さらに、プリプレグ30aにスルーホールTHを形成し、スルーホールTHの中にめっき被膜を形成するか又は導電性ペーストを埋め込むなどして貫通電極32を形成する。

#### 【0036】

続いて、同じく図3(a)に示すように、前述した図2(c)で作成した2枚のリードフレーム20を用意し、プリプレグ30aの両面側にリードフレーム20をそれぞれ配置する。各リードフレーム20は、プリプレグ30aの外側に層間接続部12a, 14a, 16aが立設するようにしてそれぞれ配置される。

40

#### 【0037】

さらに、リードフレーム20を加熱した状態でプリプレグ30a側に押圧することにより(熱プレス)、プリプレグ30aを硬化させると共に、2枚のリードフレーム20をプリプレグ30aの両面にそれぞれ接着させる。

#### 【0038】

このようにして、図3(b)に示すように、プリプレグ30aが硬化することによりコ

50

ア基板30が得られる。プレプレグ30aは硬化するときに接着機能を有するので、接着剤を特別に使用することなく、コア基板30の両面側にリードフレーム20がそれぞれ固定される。

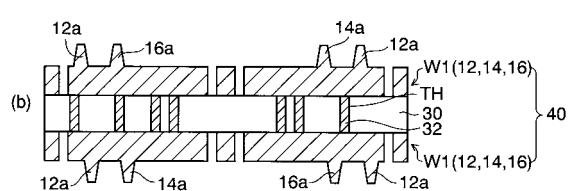

#### 【0039】

次いで、図4(a)に示すように、リードフレーム20の連結部18(図2(c)参照)を除去することにより、電源プレーン12、グランドプレーン14及び信号線パッド16が独立して相互に電気絶縁された状態とする。つまり、図3(b)のコア基板30の両面側のリードフレーム20の連結部18の上に開口部が設けられたレジスト(不図示)がそれぞれ形成された後に、レジストの開口部の連結部18がウェットエッチングにより除去される。リードフレーム20は、コア基板30に接着されているので、連結部18を除去しても、電源プレーン12、グランドプレーン14及び信号線パッド16はコア基板30の両面に固定された状態で残される。

#### 【0040】

このようにして、図4(b)に示すように、コア基板30の両面側に、正規の配線として機能する電源プレーン12、グランドプレーン14及び信号線パッド16から構成される第1配線パターンW1が形成される。コア基板30の両面側の電源プレーン12は、コア基板30内の電源ライン用の貫通電極32を介して相互接続される。また、同様に、コア基板30の両面側のグランドプレーン14は、コア基板30内のグランドライン用の貫通電極32を介して相互接続される。また、同様に、コア基板30の両面側の信号線パッド16は、コア基板30内の信号ライン用の貫通電極32を介して相互接続される。

#### 【0041】

以上により、コア基板30の両面側に、リードフレーム20から形成された第1配線パターンW1がそれぞれ形成された構造の第1ユニット配線板40が得られる。

#### 【0042】

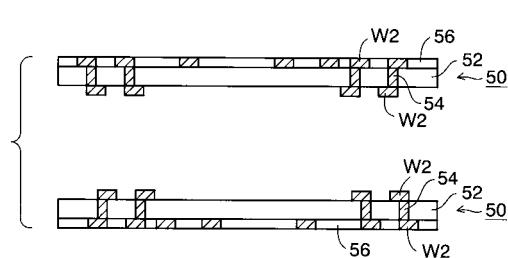

次いで、図5に示すように、2枚の第2ユニット配線板50を用意する。図5の上図に示すように、第2ユニット配線板50では、プリプレグなどから形成された絶縁性の基板52に貫通電極54が設けられており、基板52の両面側に貫通電極54を介して相互接続された第2配線パターンW2がそれぞれ形成されている。基板52の上面には第2配線パターンW2の接続部上に開口部が設けられたソルダレジスト56が形成されている。図5の下図には上図の第2ユニット配線板50が上下左右反転したものが示されている。

#### 【0043】

第2ユニット配線板50は半導体チップが実装されるものであり、その第2配線パターンW2は、第1ユニット配線板50の第1配線パターンW1より薄膜(例えば $30\mu m$ 程度)でかつファインピッチで形成される。このような観点から、第2ユニット配線板50の絶縁性の基板52の代わりにシリコン基板を使用し、第2ユニット配線板50が上下側を導通可能するより微細な配線パターンを両面に備えたシリコンインターポーザから構成されるようにしてもよい。

#### 【0044】

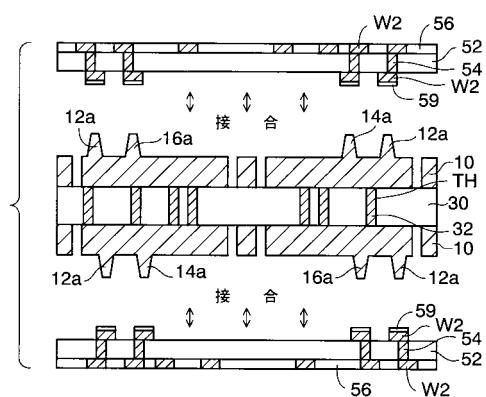

続いて、図6に示すように、2枚の第2ユニット配線板50のソルダレジスト56が設けられていない側の第2配線パターンW2に導電性ペースト59をそれぞれ塗布する。さらに、2枚の第2ユニット配線板50の導電性ペースト59が設けられた第2配線パターンW2を第1ユニット配線板40の両面側の電源プレーン12、グランドプレーン14及び信号線パッド16の各層間接続部12a, 14a, 16aに導電性ペースト59を介してそれぞれ接合する。

#### 【0045】

これにより、図7に示すように、第1ユニット配線板40の両面側の層間接続部12a, 14a, 16aに第2ユニット配線板50の配線パターン56がそれぞれ接続された構造の配線立体構造体5が得られる。この配線立体構造体5では、コア基板30の両面側において、第1ユニット配線板40の電源プレーン12、グランドプレーン14及び信号線パッド16(第1配線パターンW1)はそれらの層間接続部12a, 14a, 16aを介

10

20

30

40

50

して第2ユニット配線板50の電源ライン用、グランドライン用及び信号ライン用の第2配線パターンW2にそれぞれ接続される。そして、コア基板30の両面側の第1、第2配線パターンW1, W2は、コア基板30の貫通電極32を介してそれぞれ相互接続される。

#### 【0046】

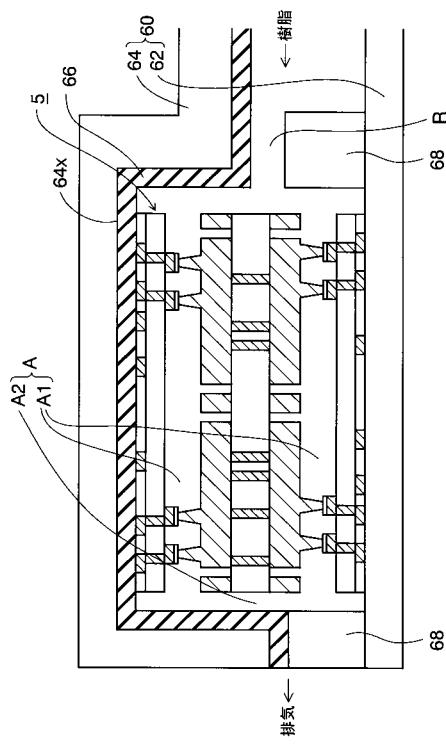

次いで、図8に示すように、下型62及び上型64から基本構成されるモールド金型60を用意する。そして、下型62の上に図7の配線立体構造体5を配置する。

#### 【0047】

さらに、下面側に凹部64xを備えた上型64を配線立体構造体5の上に配置する。上型64の下面にはリリースフィルム66が設けられており、配線立体構造体5の上面はリリースフィルム66で押えられた状態となる。リリースフィルム66は、配線立体構造体5を保護すると共に、樹脂を充填した後に上型64を樹脂から容易に分離するための剥離層として機能する。

#### 【0048】

また、下型62の周縁部上には配線立体構造体5を取り囲むようにスペーサ68が配置されており、配線立体構造体5の一辺の領域にはスペーサ68と上型64によって樹脂流入部Rが構成されている。また、樹脂流入部R以外の領域に配置されるスペーサ68は上型64の下に配置されたリリースフィルム66に接触しており、樹脂流入がそこでストップするようになっている。なお、下型62の表面（配線立体構造体5との当接面）にもリリースフィルムを介在させてもよい。

#### 【0049】

このようにして、配線立体構造体5を下型62と上型64とによって挟むことにより、樹脂流入部Rとそれに繋がって樹脂が充填される空間Aが構成される。樹脂が充填される空間Aは、第1ユニット配線板40と第2ユニット配線板50の隙間A1と、配線立体構造体5の外面と金型60との隙間A2などである。

#### 【0050】

次いで、同じく図8に示すように、溶融された樹脂を樹脂流入部Rを通してモールド金型60によって構成される空間Aに流し込む。このとき、空間Aを減圧して（又は真空にして）エアを排気した状態で樹脂が流入される。このようにして、樹脂が樹脂流入部Rからモールド金型60の中の空間Aに流入し、第1ユニット配線板40と第2ユニット配線板50の隙間A1と、配線立体構造体5の外側の隙間A2などに樹脂が充填される。

#### 【0051】

さらに、空間Aに押し込まれた樹脂を熱処理して硬化させた後に、配線立体構造体5からモールド金型60を取り外して樹脂を露出させる。このとき、上型64の下面にはリリースフィルム66が存在するので、上型64を樹脂から容易に取り外すことができる。その後に、樹脂流入部Rに形成された樹脂を折り取って廃棄する。

#### 【0052】

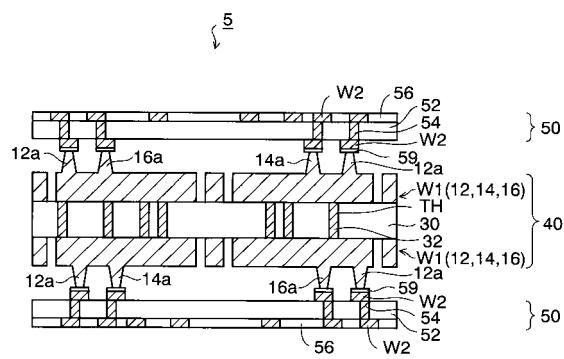

これにより、図9に示すように、第1ユニット配線板40と第2ユニット配線板50の隙間A1に樹脂が充填されて、第1、第2ユニット配線板40, 50を一体化する樹脂部70が形成される。なお、第1ユニット配線板40と第2ユニット配線板50隙間A1が比較的広い（100μm程度）場合は、空間Aを減圧することなく大気の状態で樹脂を充填することも可能である。

#### 【0053】

樹脂部70の材料としては、径が30μm程度以下のシリカフィラーが85～90%含有されたエポキシ樹脂（モールドコンパウンド樹脂）が好適に使用され、その熱膨張係数は7～20ppm/°Cであり、弾性率は15～25GPaである。樹脂部70は第1、第4ユニット配線板40, 50を一体化する基板として機能し、上記した特性の樹脂材料を採用することにより、十分な剛性を有すると共に、後述するように反りの発生を抑制することができる。

#### 【0054】

10

20

30

40

50

また、一般的に、毛細管現象を利用して液状樹脂を隙間に充填する方法では、フィラーを多量に含む樹脂を狭い隙間に充填することは困難を極める。本実施形態では、第1ユニット配線板40と第2ユニット配線板50の隙間A1がかなり狭い（例えば30μm）場合であっても、真空トランスマールド法によって樹脂を充填するので、フィラーを多量に含む樹脂を狭い隙間に信頼性よく充填することが可能である。

#### 【0055】

以上により、本実施形態の配線基板1が得られる。

#### 【0056】

図9に示すように、本実施形態の配線基板1では、第1ユニット配線板40の両面側に第2ユニット配線板50がそれぞれ接続され、第1ユニット配線板40と第2ユニット配線板50の間に樹脂部70が充填されて基本構成される。

10

#### 【0057】

第1ユニット配線板40では、コア基板30に貫通電極32が設けられており、コア基板30の両面側に貫通電極32を介して相互接続された第1配線パターンW1がそれぞれ接着されている。第1配線パターンW1は、リードフレーム20から形成され、電源プレーン12、グランドプレーン14及び信号線パッド16（図4（a）参照）から構成されている。そして、コア基板30の両面側の電源プレーン12、グランドプレーン14、及び信号線パッド16には、それらと一体的に形成されて垂直方向（コア基板30の外側）に立設する層間接続部12a、14a、16aがそれぞれ設けられている。

#### 【0058】

また、第2ユニット配線基板50では、絶縁性の基板52に貫通電極54が設けられており、基板52の両面側には貫通電極54を介して相互接続された第2配線パターンW2がそれぞれ形成されている。さらに、第1ユニット配線板40の両面側に配置された第2ユニット配線基板50の各外面には、第2配線パターンW2の接続部上に開口部が設けられたソルダレジスト56が形成されている。第2ユニット配線板50の第2配線パターンW2の積層数はn層（nは2以上の整数）で任意に設定することができる。

20

#### 【0059】

第1ユニット配線板40の両面側において、第1ユニット配線板40の電源プレーン12の層間接続部12a、グランドプレーン14の層間接続部14a及び信号線パッド16の層間接続部16aに、導電性ペースト59によって第2ユニット配線板50の第2配線パターンW2の電源ライン、グランドライン及び信号ラインがそれぞれ接続されている。

30

#### 【0060】

このようにして、コア基板30の両面側の電源ライン（電源プレーン12とそれに接続された第2配線パターンW2）がコア基板30の貫通電極32を介して相互接続されている。また同様に、コア基板30の両面側のグランドライン（グランドプレーン12とそれに接続された第2配線パターンW2）がコア基板30の貫通電極32を介して相互接続されている。また同様に、コア基板30の両面側の信号ライン（信号線パッド16とそれに接続された第2配線パターンW2）がコア基板30の貫通電極32を介して相互接続されている。

#### 【0061】

さらに、第1ユニット配線板40と第2ユニット配線板50の間には樹脂部70が充填されている。第1、第2ユニット配線板40、50は樹脂部70によって一体化されており、樹脂部70は配線基板1の基板として機能すると共に、第1、第2ユニット配線板40、50を絶縁する層間絶縁部として機能する。

40

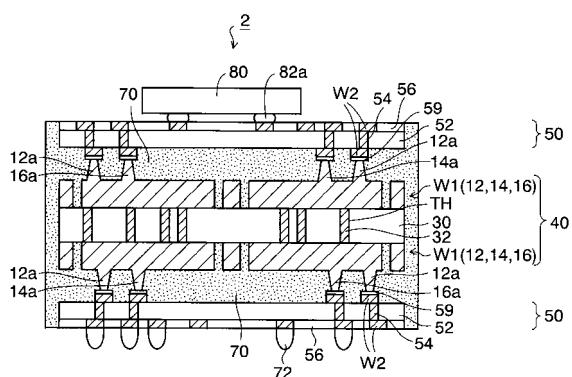

#### 【0062】

そして、図10に示すように、本実施形態の配線基板1では、上側の第2ユニット配線板50の第2配線パターンW2に半導体チップ80（シリコンLSIチップ）のバンプ80aがフリップチップ接続される。さらに、下側の第2ユニット配線板50の第2配線パターンW2にはんだボールが搭載されるなどして外部接続端子72が設けられる。以上により、本実施形態の半導体装置2が構成される。

50

**【 0 0 6 3 】**

外部接続方式を B G A (Ball Grid Array) 型とする例を示したが、 L G A (Land Grid Array) 型とする場合は、外部接続端子 7 2 が省略されて最下の第 2 配線パターン W 2 の接続部がランドとして使用される。あるいは、 P G A (Pin Grid Array) 型として使用する場合は、最下の第 2 配線パターン W 2 の接続部にリードピンが設けられる。

**【 0 0 6 4 】**

なお、第 1 ユニット配線板 4 0 のコア基板 3 0 の片面のみに第 1 配線パターン W 1 とそれに接続される第 2 ユニット配線板 5 0 が形成された形態としてもよい。この場合、コア基板 3 0 の貫通電極 3 2 の下面に外部接続端子が設けられる。

**【 0 0 6 5 】**

本実施形態では、樹脂部 7 0 の材料として、前述したように、反りの発生を防止するために熱膨張係数が 7 ~ 20 ppm / の樹脂が使用される。半導体チップ 8 0 (シリコン L S I チップ) の熱膨張係数が 3 ppm / 程度であり、一般的な樹脂材料 (熱膨張係数 : 40 ~ 100 ppm / ) を使用する場合よりも、半導体チップ 8 0 と配線基板 1 との間で熱膨張係数を近似させることができる。これにより、半導体チップを配線基板に実装する際に反りの発生を抑制できるので、半導体装置の信頼性を向上させることができる。

**【 0 0 6 6 】**

また、真空トランスマーキュリーフ法によって、第 1 ユニット配線板 4 0 と第 2 ユニット配線板 5 0 の隙間 A 1 に樹脂が信頼性よく充填されて樹脂部 7 0 が形成される。しかも、樹脂部 7 0 は、高い弾性率を有する樹脂材料から形成されるので、第 1 、 2 ユニット配線板 4 0 , 5 0 を一体的に支持する剛性の高い基板として機能する。

**【 0 0 6 7 】**

さらには、本実施形態では、層間接続部 1 2 a , 1 4 a , 1 6 a がそれぞれ立設する電源プレーン 1 2 、グランドプレーン 1 4 及び信号線パッド 1 6 を厚みの厚いリードフレーム 2 0 から形成し、その上に第 2 ユニット配線板 5 0 を積層して配線基板 1 を構成している。これにより、従来技術のような銅箔やめっきによって配線を形成する場合よりも、低コストで容易に第 2 ユニット配線板 5 0 の第 2 配線パターン W 2 よりもかなり厚い (100 μm 以上) の電源プレーン 1 2 やグランドプレーン 1 4 を形成することができる。

**【 0 0 6 8 】**

従って、配線基板 1 の電源プレーン 1 2 やグランドプレーン 1 4 の低抵抗化を図ることで電源系を強化することができ、高性能な半導体チップ搭載用の配線基板として対応できるようになる。

**【 0 0 6 9 】**

また、従来技術の基板上に配線を順次作り込んでいくビルトアップ配線板の製造方法と違って、ユニット配線板を積層し、その間に樹脂を充填して配線基板を構成するので、短手番で配線基板を製造することができ、製造効率を向上させることができる。しかも、良品のユニット配線板を選別して多層化できるので、従来技術 (ビルトアップ配線板) よりも製造歩留りを格段に向上させることができる。

**【 0 0 7 0 】**

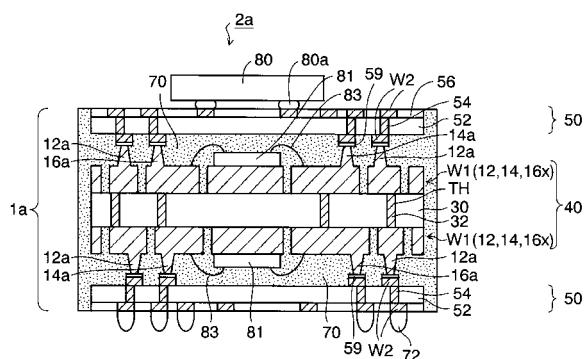

(第 2 の実施の形態)

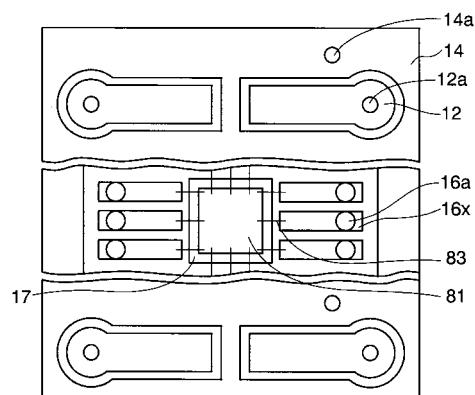

図 1 1 は本発明の第 2 実施形態の半導体装置を示す断面図、図 1 2 は本発明の第 2 実施形態に係るリードフレームから形成された第 1 配線パターンに半導体チップが接続されて実装された様子を示す平面図である。

**【 0 0 7 1 】**

第 2 実施形態の特徴は、リードフレームから形成された第 1 配線パターンに電子部品を実装して配線基板の内部に電子部品を内蔵せることにある。第 2 実施形態では、第 1 実施形態と同一要素については、同一符号を付してその説明を省略する。

**【 0 0 7 2 】**

図 1 1 及び図 1 2 に示すように、第 2 実施形態の半導体装置 2 a では、配線基板 1 の第 1 ユニット配線板 4 0 の第 1 配線パターン W 1 は、電源プレーン 1 2 、グランドプレーン

10

20

30

40

50

14、信号配線 $16\times$ 及びダイパッド17から構成される。そして、電源プレーン12、グランドプレーン14及び信号配線 $16\times$ には、それらに繋がって立設する電源ライン用の層間接続部12a、グランドライン用の層間接続部14a及び信号ライン用の層間接続部16aがそれぞれ設けられている。第2実施形態では、信号配線 $16\times$ が第1実施形態の信号線パッド16として機能する共に、半導体チップがワイヤボンディングされるリードとして機能する。

#### 【0073】

第2実施形態では、第1実施形態と同様に、まず、金属薄板10が加工されて、層間接続部12a, 14a, 16aがそれぞれ立設した電源プレーン12、グランドプレーン14及び信号配線 $16\times$ と、ダイパッド17とが連結部で繋がったリードフレームが形成される。さらに、そのリードフレームがコア基板30の両面に接着された後に、連結部がエッチングされて除去される。これにより、図12に示すように、相互に電気絶縁された電源プレーン12、グランドプレーン14、信号配線 $16\times$ 及びダイパッド17がコア基板30の両面に形成される。10

#### 【0074】

そして、同じく図12に示すように、ダイパッド17の上に半導体チップ81がフェイスアップで固着され、ワイヤボンディング法によるワイヤ83によって半導体チップ81の接続パッドが電源プレーン12、グランドプレーン14及び信号配線 $16\times$ に接続される。図12には、半導体チップ81がワイヤ83で信号配線 $16\times$ に接続された部分が示されている。20

#### 【0075】

コア基板20の下面側のダイパッド17上にも半導体チップ81が実装され、同様に半導体チップ81の接続パッドがワイヤ83によって信号配線 $16\times$ などに接続される。

#### 【0076】

これにより、半導体チップ81が両面側に実装された第1ユニット配線板40が得られる。続いて、第1実施形態と同様に、第1ユニット配線板40の両面の各層間接続部12a, 14a, 16aに第2ユニット配線板50の第2配線パターンW2を導電性ペースト59を介してそれぞれ接続する。

#### 【0077】

さらに、第1ユニット配線板40と第2ユニット配線板50の間に樹脂部70が充填されることで半導体チップ81が封止される。これにより、半導体チップ81が内蔵された配線基板1aが得られる。なお、配線基板1aに内蔵される電子部品としては、半導体チップ81の他にキャパシタや抵抗などの受動素子があり、半導体チップ81及び受動部品のいずれか又は両方を第1ユニット配線板40と第2ユニット配線板50の間に実装し、樹脂部70で埋設してもよい。30

#### 【0078】

さらに、第1実施形態と同様に、配線基板1の上面の第2配線パターンW2に半導体チップ80のバンプ80aがフリップチップ接続され、下面の第2配線パターンW2に外部接続端子72が設けられる。これにより、第2実施形態の半導体装置2aが得られる。

#### 【0079】

第2実施形態の半導体装置2aは第1実施形態と同様な効果を奏する。これに加えて、第1、第2ユニット配線板40, 50の間に半導体チップや受動部品を内蔵させたようにしたので、より高性能な半導体装置を構成することができる。

#### 【図面の簡単な説明】

#### 【0080】

【図1】図1は従来技術のビルドアップ配線板を示す断面図である。

【図2】図2(a)～(c)は本発明の第1実施形態の配線基板の製造方法を示す断面図(その1)である。

【図3】図3(a)及び(b)は本発明の第1実施形態の配線基板の製造方法を示す断面図(その2)である。40

50

20

30

40

50

【図4】図4(a)及び(b)は本発明の第1実施形態の配線基板の製造方法を示す断面図(その3)である。

【図5】図5は本発明の第1実施形態の配線基板の製造方法を示す断面図(その4)である。

【図6】図6は本発明の第1実施形態の配線基板の製造方法を示す断面図(その5)である。

【図7】図7は本発明の第1実施形態の配線基板の製造方法を示す断面図(その6)である。

【図8】図8は本発明の第1実施形態の配線基板の製造方法を示す断面図(その7)である。

10

【図9】図9は本発明の第1実施形態の配線基板を示す断面図である。

【図10】図10は本発明の第1実施形態の半導体装置を示す断面図である。

【図11】図11は本発明の第2実施形態の半導体装置を示す断面図である。

【図12】図12は本発明の第2実施形態に係るリードフレームから形成された第1配線パターンに半導体チップが接続されて実装された様子を示す平面図である。

#### 【符号の説明】

#### 【0081】

1, 1a...配線基板、2, 2a...半導体装置、10...金属薄板、12...電源プレーン、12a, 14a, 16a...層間接続部、14...グランドプレーン、16...信号線パッド、16x...信号配線、18...連結部、20...リードフレーム、30...コア基板、30a...ブリプレグ、32, 54...貫通電極、40...第1ユニット配線板、50...第2ユニット配線板、52...基板、56...ソルダレジスト、60...モールド金型、62...下型、64...上型、64x...凹部、66...リリースフィルム、68...スペーサ、70...樹脂部、72...外部接続端子、80, 81...半導体チップ、80a...バンプ、83...ワイヤ、A...空間、A1, A2...隙間、W1...第1配線パターン、W2...第2配線パターン、R...樹脂流入部。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

---

フロントページの続き

(56)参考文献 特開2004-014679(JP,A)

特開2002-290051(JP,A)

特開平08-181417(JP,A)

特開平03-083396(JP,A)

(58)調査した分野(Int.Cl., DB名)

H 05 K 3 / 4 6