(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第4822791号

(P4822791)

(45) 発行日 平成23年11月24日(2011.11.24)

(24) 登録日 平成23年9月16日(2011.9.16)

|                          |                   |

|--------------------------|-------------------|

| (51) Int.Cl.             | F 1               |

| HO 1 L 27/11 (2006.01)   | HO 1 L 27/10 381  |

| HO 1 L 21/8244 (2006.01) | G 11 C 11/40 301  |

| G 11 C 11/412 (2006.01)  | HO 1 L 27/10 481  |

| HO 1 L 27/10 (2006.01)   | HO 1 L 29/78 613B |

| HO 1 L 29/786 (2006.01)  | HO 1 L 29/78 617N |

請求項の数 14 (全 24 頁)

|           |                               |

|-----------|-------------------------------|

| (21) 出願番号 | 特願2005-290889 (P2005-290889)  |

| (22) 出願日  | 平成17年10月4日 (2005.10.4)        |

| (65) 公開番号 | 特開2007-103629 (P2007-103629A) |

| (43) 公開日  | 平成19年4月19日 (2007.4.19)        |

| 審査請求日     | 平成20年9月9日 (2008.9.9)          |

|           |                                                      |

|-----------|------------------------------------------------------|

| (73) 特許権者 | 302062931<br>ルネサスエレクトロニクス株式会社<br>神奈川県川崎市中原区下沼部1753番地 |

| (74) 代理人  | 110000350<br>ポレール特許業務法人                              |

| (72) 発明者  | 山岡 雅直<br>東京都国分寺市東恋ヶ窪一丁目280番地<br>株式会社日立製作所 中央研究所内     |

| (72) 発明者  | 河原 尊之<br>東京都国分寺市東恋ヶ窪一丁目280番地<br>株式会社日立製作所 中央研究所内     |

審査官 吉田 安子

最終頁に続く

(54) 【発明の名称】半導体記憶装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ワード線と、前記ワード線と交差する方向に延伸するピット線と、データを記憶するラッチ部と、前記データを転送する転送部と、を具備してなるスタティック型のメモリセルを有し、

前記ラッチ部および前記転送部は、チャネル部分が絶縁膜から成るBOX層によって基板部分と絶縁されたS01層を有するトランジスタを含み、

前記メモリセルのデータの書き込み動作時とデータの読み出し動作時に前記BOX層下に設けられた導電層からなるウエル層に適宜電圧を印加するための第2の電源線を有し、

前記ラッチ部は、接地電位線にそのソース電極が接続された第1の導電型チャネルを有する駆動トランジスタ対と、前記接地電位線の電位よりも高い電位となる第1の電源線にそのソース電極が接続された第2の導電型チャネルを有する負荷トランジスタ対とを含んで構成され、

前記転送部は、前記メモリセルにアクセスするための前記ピット線と情報を保持する記憶ノードとの間に接続された第1の導電型チャネルを有する転送トランジスタ対を含んで構成され、

前記駆動トランジスタ対の一方と、前記転送トランジスタ対の一方とが第1ウエル層上に設けられ、

前記駆動トランジスタ対の他方と、前記転送トランジスタ対の他方とが前記第1ウエル層と電気的に分離された前記第2ウエル層上に設けられ、

10

20

前記第1ウエル層上に設けられた駆動トランジスタと転送トランジスタ、および前記第2ウエル層上に設けられた駆動トランジスタと転送トランジスタのそれぞれのウエル電位が電気的に接続され、

前記第1ウエル層に印加する第2の電源線と前記第2ウエル層に印加する第2の電源線とは、電気的に独立に設けられ、

前記第2の電源線が前記ビット線に並行する方向に設けられ、

前記メモリセルからのデータの読み出し動作時において前記BOX層下に設けられたウエル層に供給される電圧は、前記メモリセルへの書き込み時において前記ウエル層に供給される電圧と異なることを特徴とする半導体記憶装置。

【請求項2】

10

請求項1において、

前記メモリを構成するトランジスタの少なくとも一つは、S01層が完全に空乏化したFD-S01構造を有することを特徴とする半導体記憶装置。

【請求項3】

請求項1において、

前記ラッチ部を構成するトランジスタ対のしきい値電圧を変化させることを特徴とする半導体記憶装置。

【請求項4】

請求項1において、

前記転送部を構成するトランジスタ対のしきい値電圧を変化させることを特徴とする半導体記憶装置。

20

【請求項5】

請求項1において、

前記メモリセルは、書き込み時における前記負荷トランジスタのしきい値電圧が読み出し時のしきい値電圧よりも高い値に制御されることを特徴とする半導体記憶装置。

【請求項6】

請求項1において、

前記メモリセルは、書き込み時における前記転送トランジスタのしきい値電圧が読み出し時のしきい値電圧よりも低い値に制御されることを特徴とする半導体記憶装置。

【請求項7】

30

請求項1において、

前記メモリセルは、書き込み時における前記駆動トランジスタのしきい値電圧が読み出し時のしきい値電圧よりも低い値に制御されることを特徴とする半導体記憶装置。

【請求項8】

請求項1において、

前記メモリセルは、書き込み時の負荷トランジスタのウエル電位が、読み出し時の前記負荷トランジスタのウエル電位よりも高い電圧に制御されることを特徴とする半導体記憶装置。

【請求項9】

40

請求項1において、

前記メモリセルは、書き込み時の転送トランジスタのウエル電位が、読み出し時の前記転送トランジスタのウエル電位よりも高い電圧に制御されることを特徴とする半導体記憶装置。

【請求項10】

請求項1において、

前記メモリセルは、書き込み時の駆動トランジスタのウエル電位が、読み出し時の前記駆動トランジスタのウエル電位よりも高い電圧に制御されることを特徴とする半導体記憶装置。

【請求項11】

請求項1において、

50

データ保持状態にあるメモリセルへのアクセスがないスタンバイ状態で、前記負荷トランジスタのウエル電位は、前記第1の電源線の電位よりも高い電位に制御されることを特徴とする半導体記憶装置。

【請求項12】

請求項1において、

データ保持状態にあるメモリセルへのアクセスがないスタンバイ状態で、前記駆動及び転送トランジスタのウエル電位は、接地線の電位よりも低い負の電位に制御されることを特徴とする半導体記憶装置。

【請求項13】

半導体基板に形成された導電層からなるウエル層と、 10

前記ウエル層上に形成された絶縁膜からなるBOX層と、

前記BOX層上に形成されたソース層、ドレイン層および前記ソース層とドレイン層に挟まれて形成されたチャネル層と、

前記チャネル層上にゲート絶縁膜を介して形成されたゲート電極とを有するSOI型トランジスタを複数備えてなり、スタティック型メモリセルとして機能する半導体記憶装置であって、

接地電位線にそのソース電極が接続され、前記SOI型トランジスタからなる第1の導電型チャネルを有する駆動トランジスタ対と、

前記接地線の電位よりも高い電位となる第1の電源線にそのソース電極が接続され、ドレイン電極を介して前記駆動トランジスタと接続された前記SOI型トランジスタからなる第2の導電型チャネルを有する負荷トランジスタ対と、 20

前記メモリセルにアクセスするためのピット線と情報を保持する記憶ノードとの間に接続され、前記SOI型トランジスタからなる第1の導電型チャネルを有する転送トランジスタ対とを有し、

前記駆動トランジスタ対の一方と、前記転送トランジスタ対の一方とが第1ウエル層上に設けられ、

前記駆動トランジスタ対の他方と、前記転送トランジスタ対の他方とが前記第1ウエル層と電気的に分離された前記第2ウエル層上に設けられ、

前記第1ウエル層上に設けられた駆動トランジスタと転送トランジスタ、および前記第2ウエル層上に設けられた駆動トランジスタと転送トランジスタのそれぞれのウエル電位が電気的に接続され、 30

前記第1ウエル層に印加する第2の電源線と前記第2ウエル層に印加する第2の電源線とは、電気的に独立に設けられ、

前記負荷トランジスタ対の一方と、前記負荷トランジスタ対の他方とが共通の第3ウエル層上に設けられ、

前記第1および第2ウエル層と前記第3ウエル層とが互いに電気的に分離され、

前記第1および第2ウエル層への電圧印加と前記第3ウエル層への電圧印加が独立に制御可能な手段を有することを特徴とする半導体記憶装置。

【請求項14】

請求項13において、

前記負荷トランジスタ対の一方と、前記負荷トランジスタ対の他方とが、異なるウエル層内に形成され、

前記異なるウエル層のそれぞれへの電圧印加が独立に制御可能な手段を有することを特徴とする半導体記憶装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、スタティックメモリ(SRAM)回路が半導体チップ上に集積された半導体集積回路に関し、特に、SRAM集積回路装置の動作に必要な動作マージンを広げる構成に関する。 50

**【背景技術】****【0002】**

近年、半導体装置、例えばSRAM回路などの半導体装置に対しては、高速化および低消費電力化が強く求められている。

**【0003】**

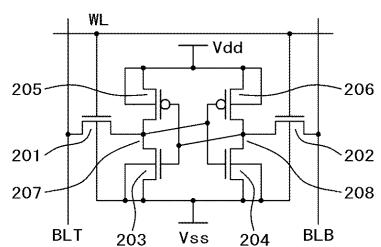

図32に従来のSRAMメモリセル回路を示す。ここで、BLTおよびBLBはビット線、WLはワード線、Vddはハイレベルの電源線、Vssは接地電位線、201および202はメモリセルにアクセスするための転送トランジスタ、203および204はメモリセルのデータを保持するため記憶ノードを駆動する駆動トランジスタ、205および206はメモリセルデータを保持するため電荷を供給する負荷トランジスタ、207および208は記憶ノードである。

10

**【0004】**

SRAM回路の消費電力を低減するには電源電圧を低下させることがもっとも単純で効果が大きい方法である。

**【0005】**

しかし、低い電源電圧ではトランジスタの動作に必要な動作マージンが低下し、動作が不安定となる。この問題の解決を狙った技術として、特許文献1（特開平11-39879号）では、SRAMセルを構成するトランジスタの基板電位を制御して、書き込み時の高速化と読み出し時の消費電力を低減する技術が開示されている。また、特許文献2（特開2003-151277号）では、1つのメモリセルに2種類のVthをもつトランジスタを用いて、高速・低電圧動作を可能とする回路技術が開示されている。さらに、特許文献3（特開2003-86713号）では、SRAMメモリセルを構成するトランジスタのゲート幅を左右の記憶ノードに接続されるトランジスタで非対称にすることで、動作時のデータ破壊を防ぎ低電圧動作を可能とする技術が開示されている。

20

**【0006】**

【特許文献1】特開平11-39879号公報

【特許文献2】特開2003-151277号公報

【特許文献3】特開2003-86713号公報

**【発明の開示】****【発明が解決しようとする課題】****【0007】**

30

LSI(Large Scale Integrated circuit:大規模集積回路)の低消費電力化およびLSI中のトランジスタの微細化により、LSIの電源電圧が低下している。たとえば、90nmプロセスでは、電源電圧1.2Vで動作するLSIが製造される。電源電圧が下がると、SRAM回路においては書き込み・読み出しの動作時の動作安定性が低下し、動作が難しくなる。メモリセルを構成する各トランジスタの駆動力すなわち電流が変化すると書き込み、読み出しの安定性、および動作速度の各性能が変化する。

**【0008】**

よって、メモリセルを構成する各トランジスタの性能を適切に制御することができれば、それぞれの性能を向上することができる。また電源電圧を低下させるとトランジスタの駆動電流が下がるため、回路の動作速度が低下する。この動作速度の低下を抑えるためには、トランジスタのしきい値電圧(Vth)を低くして電源電圧が低下しても動作電流の低下を抑える方法が取られる。

40

**【0009】**

しかし、トランジスタのVthを低下させるとサブスレショルドリーク電流とよばれるオフしているトランジスタのソース-ドレイン間を流れるリーク電流が増加し、非動作状態での消費電力が増加するという問題がある。特許文献1の例では、SRAMメモリセル中の適切なトランジスタの基板電位を制御することでトランジスタの性能を制御し、非動作時の低電力を実現する技術が開示されている、nチャネル型バルクCMOSトランジスタのバックゲートにソース電極よりも低い電圧を印加するとトランジスタのVthを高く制御することで可能であり、トランジスタのサブスレショルドリークを抑えることができる。

50

## 【0010】

しかし、製造プロセス90nm以下の微細化されたバルクCMOSトランジスタのバックゲートを制御すると、接合リーケ電流と呼ばれるドレイン電極から基板電極へ流れるリーケ電流が増加し、サブスレショルドリーケ電流は低下しているものの、トランジスタ全体でみたリーケ電流は増加し回路全体の消費電力が低減できないという課題がある。

## 【0011】

特許文献2の例では、1つのメモリセルを構成するトランジスタの数を増加させるとともに2種類のV<sub>th</sub>をもつトランジスタを用いることで、メモリセル内のトランジスタの駆動力を適切に設定し、メモリセルの書き込み・読み出し時の動作安定性を向上させている。

10

## 【0012】

しかし、メモリセルの素子数が増えることから大きくメモリセル面積が増加してしまう。メモリ回路はできるだけ多くの容量を搭載するという要求があるため、面積が増加するメモリセルを用いるのは難しいという課題がある。

## 【0013】

特許文献3の例では、本来対称であるべきメモリセル内のトランジスタのゲート幅に非対称性を持たせることで、メモリセル内のトランジスタの駆動力を適切に設定し、これによってメモリセルのもつ書き込み・読み出し時の動作安定性を向上させている。

## 【0014】

しかし、ゲート幅を左右で変化させるためメモリセルの対称性が失われる。メモリセルを製造する際には、同じメモリセルを大量に繰り返し配置できるという規則性の高さと対称的なメモリセルを用いるという対称性の高さで精度の高いメモリセルを作っているが、対称性が崩れてしまうとこの製造精度が低下してしまい、性能が低下してしまうという課題がある。また異なったゲート幅を用いるということはメモリセル面積が増大するという問題もかかえており、これは特許文献2の例と同様の面積増加という課題に行き着く。

20

## 【0015】

本発明が解決しようとする課題は、微細化されたトランジスタを用いた低消費電力SRAMにおいて、ドレイン電極から基板電極へ流れるリーケ電流およびサブスレショルドリーケ電流を低減することによりLSI回路全体の消費電力を低減する技術を提供する点にある。

30

また、メモリセルの書き込み・読み出し時の動作安定性を向上させる技術の提供にある。

さらに、トランジスタの数を増加等によるメモリセルの増加を抑制し、チップ面積の増大を抑制する技術の提供にある。

## 【課題を解決するための手段】

## 【0016】

本発明の代表的なものの一例を示せば、以下の通りである。すなわち、本発明の半導体記憶装置は、データを記憶するラッチ部と、データを転送する転送部とを具備してなるスタティック型のメモリセルを有し、そのラッチ部および転送部は、チャネル部分が絶縁膜から成るBOX層によって基板部分と絶縁されたSOI層を有するトランジスタを含み、メモリセルのデータの書き込み動作時とデータの読み出し動作時に、メモリセル内の少なくとも一つのトランジスタのしきい値電圧を変化させることを特徴とするものである。

40

## 【0017】

これにより、スタティック型のメモリセルをSOIトランジスタで構成し、各トランジスタの埋め込み酸化膜(BOX: Buried Oxide)層の下側のウエル層の電位を適切に制御することで各トランジスタの電流を変化させSRAMの各性能を向上させることが可能となる。ウエル層はBOX層によりトランジスタが形成されているSOI層とは電気的に絶縁されているため余分なリーケ電流は増加しない。

## 【0018】

また、本発明の半導体記憶装置は、半導体基板に形成された導電層からなるウエル層と

50

、そのウエル層上に形成された絶縁膜からなるBOX層と、BOX層上に形成されたソース層、ドレイン層およびソース層とドレイン層に挟まれて形成されたチャネル層と、そのチャネル層上にゲート絶縁膜を介して形成されたゲート電極とを有するSOI型トランジスタを複数備えてなり、スタティック型メモリセルとして機能する半導体記憶装置であつて、接地電位線にそのソース電極が接続され、SOI型トランジスタからなる第1の導電型チャネルを有する駆動トランジスタ対と、接地線の電位よりも高い電位となる第1の電源線にそのソース電極が接続され、ドレイン電極を介して前記駆動トランジスタと接続されたSOI型トランジスタからなる第2の導電型チャネルを有する負荷トランジスタ対と、メモリセルにアクセスするためのビット線と情報を保持する記憶ノードとの間に接続され、SOI型トランジスタからなる第1の導電型チャネルを有する転送トランジスタ対とを有し、駆動トランジスタ対の一方が形成されているウエル層と、転送トランジスタ対の一方が形成されているウエル層とが、共通の第1ウエル層上に設けられ、負荷トランジスタ対の一方と、前記負荷トランジスタ対の他方とが共通の第2ウエル層上に設けられ、第1ウエル層と第2ウエル層とが互いに電気的に分離されていることを特徴とするものである。10

これにより、適切にウエルコントクトを形成すれば、メモリセル面積も増加しない。

#### 【0019】

さらに、本発明の半導体記憶装置は、複数のトランジスタからなるスタティック型メモリセルが列方向および行方向に配列されてなり、メモリセルアレイとして機能する半導体記憶装置であつて、

メモリセルにアクセスするためのビット線を複数有し、複数のビット線の一つに接続された複数のメモリセルを構成する同一の列内に形成された各々のトランジスタが共通して設けられている第1ウエル層と、複数のビット線の他の線に接続された複数のメモリセルを構成する同一の列内に形成された各々のトランジスタが共通して設けられた第2ウエル層とを有し、第1ウエル層の電位が前記第2ウエル層の電位と異なる電位に制御されることを特徴とするものである。20

#### 【0020】

これにより、2種類の電圧の電源をメモリ内の特定のノードに選択的に印加することで、トランジスタの電流を変化させて各性能を向上させることが可能となる。

#### 【発明の効果】

#### 【0021】

本発明によれば、トランジスタ動作の高速化とリーク電流の低減とが可能となるため、SRAM回路の動作特性の向上が可能となる。

#### 【発明を実施するための最良の形態】

#### 【0022】

以下に、本発明を、図面を用いて詳細に説明する。

#### <実施例1>

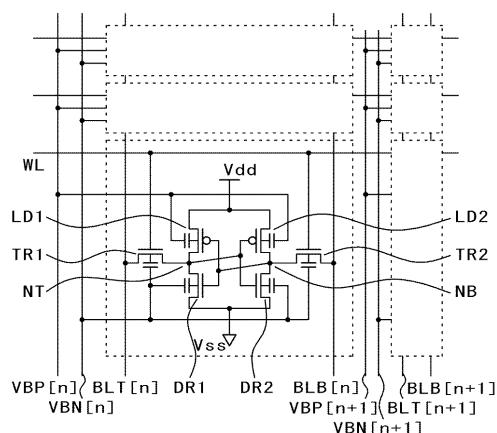

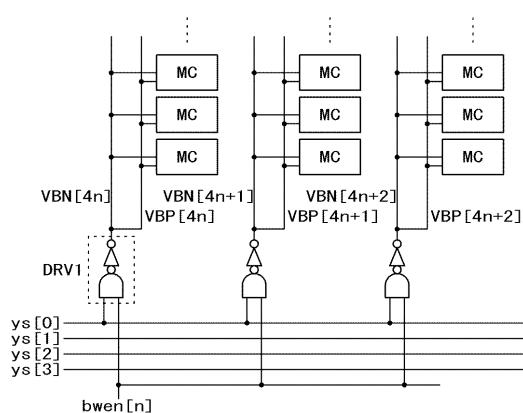

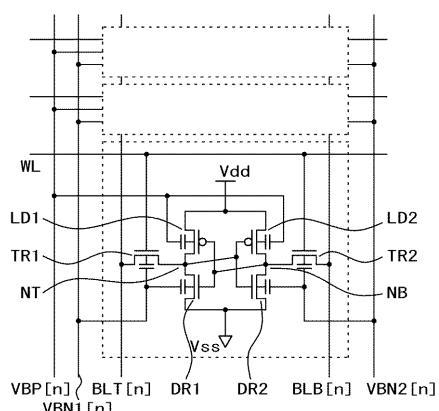

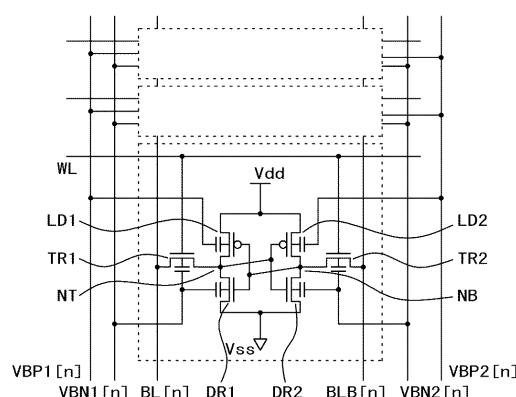

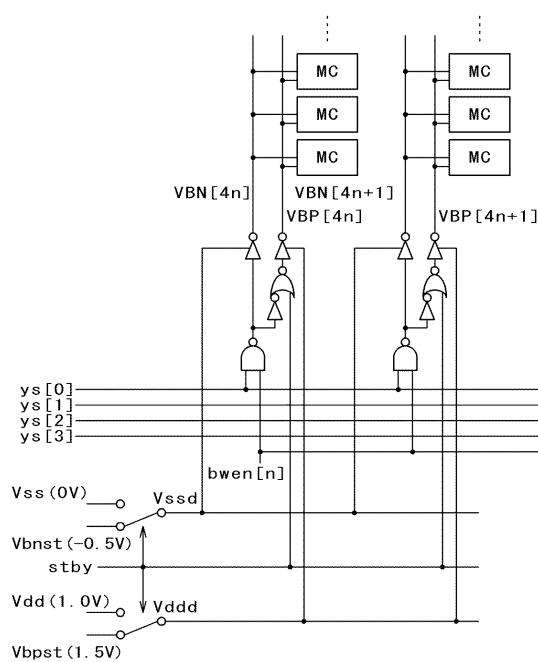

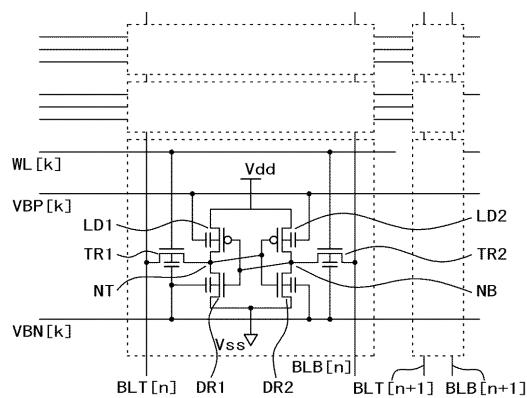

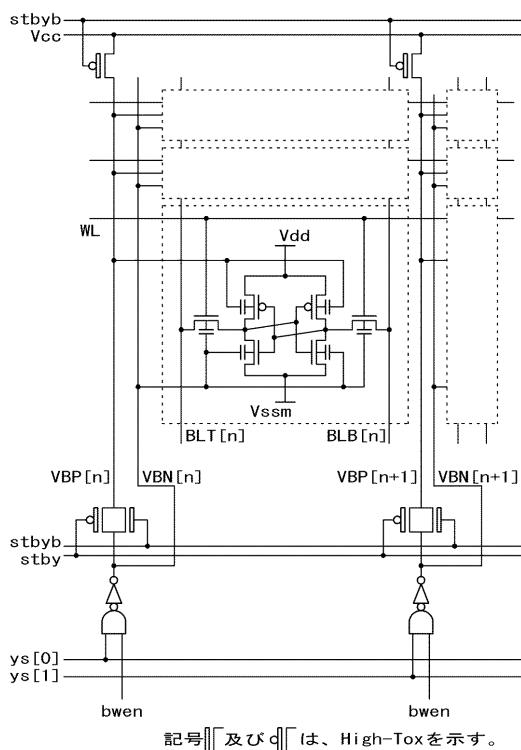

図1に本発明を用いたSRAM回路の回路図を示す。図1において、[n]はn列目で共通になっていることを表し、同様に[n+1]はn+1列目で共通になっていることを表す。今後、列によって特に区別する必要のない場合は[ ]を除いて表し、列毎に特徴がある点については[ ]をつけて説明を行う。図1において、BLTおよびBLBはビット線、WLはワード線、Vddはハイレベルの電源線、Vssは接地電位線、NTおよびNBはデータを記憶するデータ保持ノード、TR1およびTR2はビット線とデータ保持ノードを接続する転送トランジスタ、DR1およびDR2はデータ保持ノードをロウレベルに駆動する駆動トランジスタ、LD1およびLD2はデータ保持ノードに電荷を供給する負荷トランジスタ、VBN[n]はn列目のメモリセル内のnMOSトランジスタのウエルノードが全て接続されたノード、VBP[n]はn列目のメモリセル内のpMOSトランジスタのウエルノードが全て接続されたノードである。たとえば、Vddは1.2V、Vssは0Vの電位となっている。本実施例は、一般に横長セルと呼ばれるワード線方向に長い長方形のメモリセルを用いたSRAM回路に最適な回路構成の例である。横長セルは、ワード線と垂直方向に長いnウエルとpウエルとが交互にワード線方向に繰り返して並ぶことによりメモリセルの形状がワード線方向に長い長方形となるものである。そのセル形状304050

に起因して、VBN[k]およびVBP[k]は、WLに垂直、すなわちビット線に平行に延伸するよう配置される。

【0023】

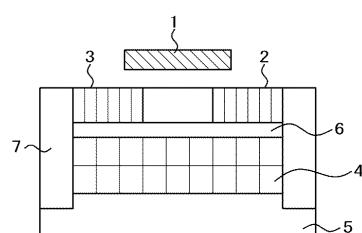

図1の回路中で用いられているトランジスタの断面の概略図を図3に示す。ここで用いられているトランジスタは、チャネル部分がBOX層によって基板部分と絶縁されているSOIトランジスタである。図3中で、1はゲート、2はドレイン、3はソース、4はBOX層下のウエル層、5は支持基板、6は埋め込み酸化膜(BOX)層、7は素子分離領域である。本トランジスタは完全空乏型SOI(FD-SOI:Fully Depleted SOI)トランジスタ構造となっており、ウエル層の電位を制御することによって、パルクCMOSトランジスタのバックゲート電位を制御した時と同様にトランジスタのVthを制御することが可能である。特にBOX層の厚さが薄ければ薄い程、ウエル層の電位を変えた時のVthの変化も大きくなる。本発明では、特に埋め込み酸化膜の膜厚が20nm以下の10nm程度を想定している。しかし、埋め込み酸化膜の膜厚が20nm以上のSOIトランジスタでも、ウエル層の電位を変えた時のVthの変化の程度は小さくなるものの、同様のVth制御の効果が得られる。またウエル層は、トランジスタのソースおよびドレインなどの拡散層とは絶縁膜であるBOX層により分離されているため、ウエルの電位を変化させてもウエルと拡散層間に電流は流れない。

【0024】

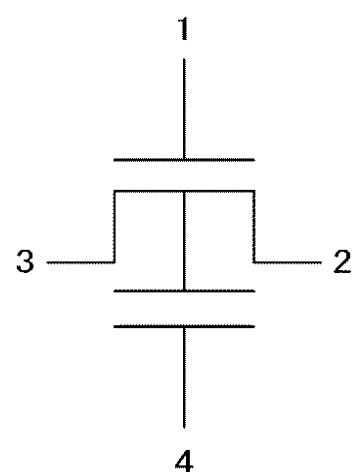

図4に、図3のトランジスタ構造の等価回路を示す。1はゲート、2はドレイン、3はソース、4はウエルを示しており、ウエルとトランジスタのバックゲートはBOX層による容量によって分離されている。図1ではこの構造のトランジスタが用いられている。

【0025】

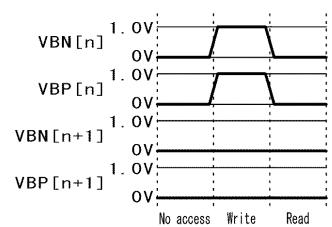

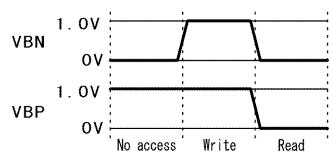

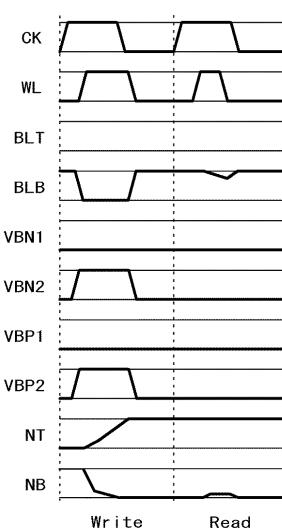

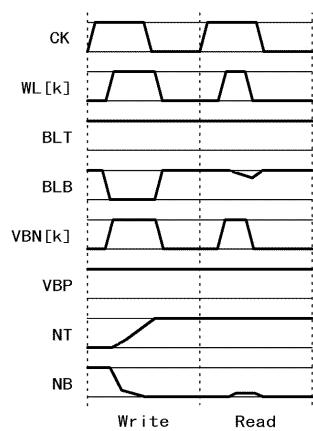

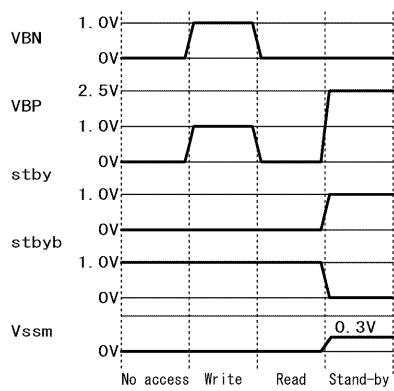

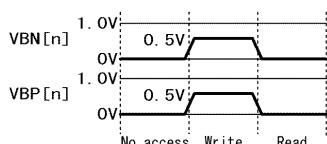

図2に、それぞれの列のウエル電位の変化を示す。VBN[n]およびVBP[n]はアクセスされている列のウエルノードの電位を表し、VBN[n+1]およびVBP[n+1]はアクセスされていない列のウエルノードの電位を示している。SRAMでは列選択アクセスが行われることが一般的であるため、ここではアクセスされる列とアクセスされない列の電位を示している。列選択アクセスが行われず、すべての列がアクセスされる場合は、すべての列のウエルノードの電位がVBN[n]およびVBP[n]であらわされている電位と同様となる。読み出しが行われる場合およびアクセスされていない場合にはnMOSのウエルノードおよびpMOSのウエルノード電位共にロウレベルに制御される。また、書き込みが行われる場合には、nMOSおよびpMOSのウエルノードの電位がハイレベルに制御される。

【0026】

図3のメモリセルにおいて、記憶ノード207にロウのデータが、記憶ノード208にハイのデータが記憶されている場合の読み出し動作について説明する。読み出しを行う場合には、ビット線BLTおよびBLBがハイ電位にプリチャージされる。プリチャージ完了後にワード線WLがハイ電位になることで転送トランジスタ201および202がオンになり、ハイになっているビット線BLTの電荷が転送トランジスタ201から記憶ノード207、駆動トランジスタ203を通してディスチャージされ、BLTの電位がセンスアンプによって増幅できるレベルになった時点で、図には示されていないがビット線に接続されているセンスアンプを起動することで、メモリセルのデータが増幅され出力される。ここでビット線の電荷がディスチャージされる経路に着目すると、記憶ノード207は読み出し動作開始直前まではロウレベルである0Vであるが、読み出し動作が開始されると記憶ノード207はビット線BLTとVss間を転送トランジスタ201と駆動トランジスタ203によって抵抗分割した状態となるため、記憶ノード207の電位は0.3Vなど正の電位となる。ここでこの電位が高くなると、記憶ノード207がゲートに接続されているnMOSトランジスタのコンダクタンスが高くなるとともに、記憶ノード207がゲートに接続されているpMOSトランジスタのコンダクタンスが低下するためハイレベルであった記憶ノード208の電位が低下する。さらにこの記憶ノード208の電位上昇は記憶ノード207にフィードバックされこの繰り返しによってメモリセルに記憶されているデータが破壊される。通常メモリセルでは駆動トランジスタのコンダクタンスと転送トランジスタのコンダクタンスの比が1.5などの大きな値をとるように設計され、メモリセルに記憶されているデータが破壊されるまで記憶ノード207の電位が上昇するこ

10

20

30

40

50

とはい。

【0027】

しかし、近年のトランジスタ製造プロセスの微細化によってトランジスタ性能のばらつきが大きくなる傾向にあり、設計時のコンダクタンス比を下回るメモリセルが製造され、読み出し時の動作安定性が低下する傾向にある。また、低消費電力化のために電源電圧を下げる記憶ノード207がゲートに接続されているnMOSトランジスタおよびpMOSトランジスタで構成されるインバータの論理しきい値電圧が低下し、データを破壊するフィードバックが起き易くなり、これによつても読み出し時の動作安定性が低下する。

【0028】

図1の本発明の回路において同様に記憶ノードNTにロウのデータ、記憶ノードNBにハイのデータが記憶されている場合の読み出し動作を考えると、図32とほぼ同様の動作を行う。この中で、負荷トランジスタLD1およびLD2のウエル電位はロウ電位となつてゐるため、従来のトランジスタの状態と比較するとLD1およびLD2のV<sub>th</sub>が低い状態となつてゐる。負荷トランジスタの駆動力つまりコンダクタンスは大きくなつてゐる。駆動トランジスタDR2のウエル電位はソース電位と同等となつてゐるため、負荷トランジスタLD2と駆動トランジスタDR2で構成されるインバータの論理しきい値電圧は、負荷トランジスタLD2のウエル電位がハイの状態と比較すると高い状態となつてゐる。よつて、記憶ノードNTの電位が上昇した場合にもデータを破壊するフィードバックが起きにくく状態となつてゐる。

【0029】

このように、負荷トランジスタのウエル電位がロウとなつてゐる状態は読み出し時の動作安定性が高い、つまり読み出し動作のマージンが高い状態となつてゐる。ばらつきに強くまた低電圧での動作に適してゐる。さらに本発明では、pMOSトランジスタのウエル電位にロウの電位を印加した場合にも絶縁膜によってウエルから拡散層に電流が流れないと、0.5V以上のPN接合をオンさせるような高い電圧でも消費電力の増加なく適用することが可能となる。

【0030】

図32のメモリセルにおいて、記憶ノード207にハイのデータが、記憶ノード208にロウのデータが記憶されている場合に逆のデータを書き込む場合の動作について説明する。ビット線BLTをロウレベルに、ビット線BLBをハイレベルにするとともにワード線電位を"H"レベルにし、転送トランジスタをオンさせる。記憶ノード207の電荷は転送トランジスタ201を通してディスチャージされ、記憶ノード207の電位はハイレベルから低下する。207の電位が負荷トランジスタ206と駆動トランジスタ204で構成されるインバータの論理しきい値よりも低くなると、ロウレベルであった記憶ノード208の電位が上昇し、記憶ノード間のフィードバックも作用して、新しいデータがメモリセルに書き込まれる。

【0031】

このようにSRAMメモリセルではハイレベルの記憶ノードの電荷を転送トランジスタによってディスチャージすることによって書き込みが行われるが、転送トランジスタによって電荷がディスチャージされると同時に負荷トランジスタから電荷が供給されているため、書き込み動作を終えるには、転送トランジスタが負荷トランジスタが供給する以上に電荷を引き抜く必要がある。よつて、負荷トランジスタのコンダクタンスが大きくなると書き込みに必要な時間が長くなり、またばらつき等の原因で設計値を超えて大きくなるような場合には書き込みが出来なくなる場合がある。これらを補償するためには、負荷トランジスタのコンダクタンスを小さくするか、転送トランジスタのコンダクタンスを大きくする必要がある。

【0032】

本実施例では、従来と同様の動作でメモリセルに新しいデータの書き込みが行われる。図1の回路で書き込みが行われる列では、負荷トランジスタLD1およびLD2のウエル電位がハイに制御され、アクセスされていない場合または読み出しが行われる場合と比較して負荷トランジスタのV<sub>th</sub>は上昇し、駆動力は低下する。同時にメモリセル中のnMOSトランジスタのウエル電位がハイに制御されnMOSトランジスタのV<sub>th</sub>は低くなり駆動力が高くなる

10

20

30

40

50

。よって、書き込み前の状態でハイのレベルであった記憶保持ノードの電位を低下させる電流を転送トランジスタの駆動力が高くなるとともにハイレベルを維持しようとする負荷トランジスタの駆動力が低くなり、よって書き込み動作が行われ易くなる。つまり書き込み時の動作マージンが増加し、ばらつきに強くまた低電圧での動作に適している。さらに本発明では、nMOSトランジスタのウエル電位にハイの電位を印加した場合にも絶縁膜によってウエルから拡散層に電流が流れないと、0.5V以上のPN接合をオンさせるような高い電圧でも消費電力の増加なく適用することが可能となる。

#### 【 0 0 3 3 】

以上のように、書き込みおよび読み出しのそれぞれの動作でメモリセルを構成するトランジスタのウエル電位を適切に変化させることで、書き込みおよび読み出しのそれぞれの動作の動作マージンを増加させることが出来、ばらつきに強く低電圧での動作に適したメモリセル動作を行うことが出来る。

#### 【 0 0 3 4 】

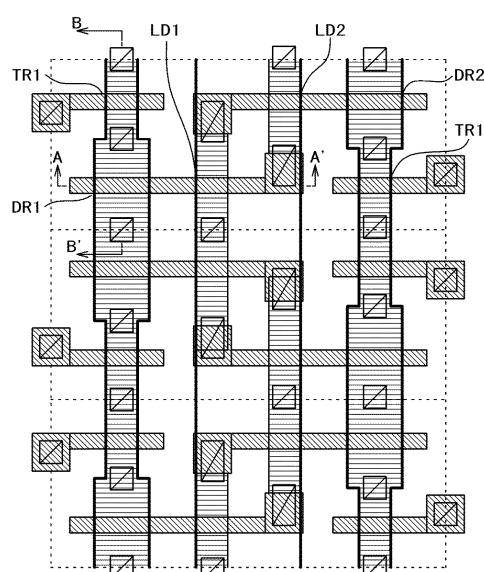

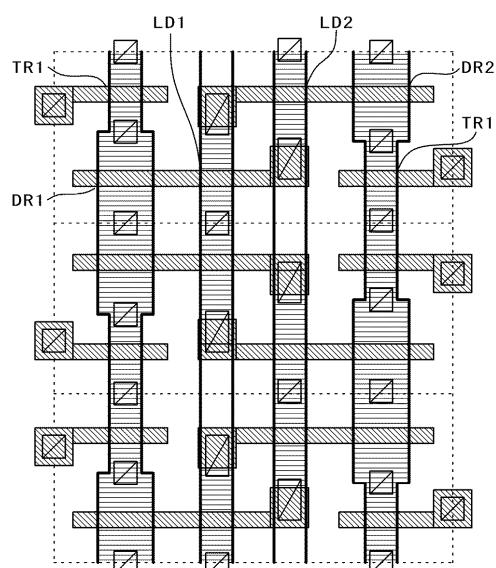

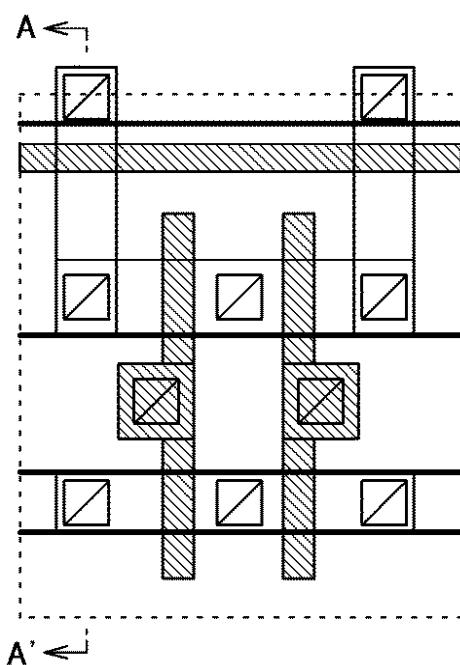

図5に本メモリセルのレイアウト図を示す。図5において、TR1およびTR2は転送トランジスタ、DR1およびDR2は駆動トランジスタ、LD1およびLD2は負荷トランジスタ、Gateはトランジスタのゲート電極を構成するポリシリコン層、Diffusionは拡散層、Contactは拡散層およびポリシリコン層とメタル配線を接続するためのコンタクト、Wellがトランジスタのウエル層であり、点線で囲まれた範囲が1つのメモリセルである。図5中には同一列に並ぶ3つのメモリセルが描かれている。同一列にならぶメモリセルのnMOSおよびpMOSトランジスタのウエル層が接続されており、同電位に制御されることがわかる。またさらに隣の列のトランジスタとはウエル層が分離され別電位に制御されていることもわかる。このメモリセルは、一般に横長セルと呼ばれるワード線方向に長い長方形の形状を持つメモリセルである。横長セルは、ワード線と垂直方向に長いnウエルとpウエルとが交互にワード線方向に繰り返して並ぶことによりメモリセルの形状がワード線方向に長い長方形となるものである。このセル形状に起因して、横長セルのSRAM回路図は図1に示すようにVBN[k]およびVBP[k]がワード線WLに垂直、すなわちビット線に平行に延伸する構成となる。

#### 【 0 0 3 5 】

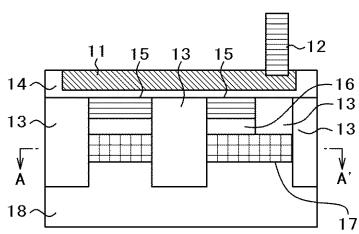

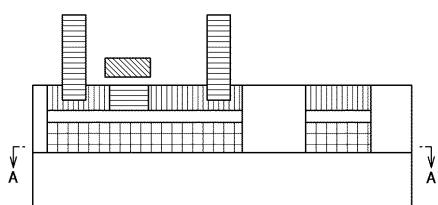

図6に図5中のA-A'で切断した場合の断面の概略を示す。図6において、11はゲート電極、12はコンタクト、13は素子分離層、14はゲート絶縁膜層、15はSOI層、16はBOX膜、17はウエル層、18は支持基板である。チャネルが形成されるSOI層は埋め込み酸化膜によってウエル層から絶縁されている。これによって、ウエル層にバルクCMOSトランジスタでの順方向バイアスが印加されてもウエルからソース電極に電流が流れることはない。また、素子分離層によって、SOI層およびウエル層は隣りのトランジスタとは分離されている。

#### 【 0 0 3 6 】

図7に図5中のB-B'で切断した場合の断面の概略を示す。図7において、11はゲート電極、12はコンタクト、13は素子分離層、15はSOI層、16はBOX膜、17はウエル層、18は支持基板、19は拡散層である。同一列上に並ぶトランジスタのウエルが接続されて同電位に制御される構造となっていることがわかる。

#### 【 0 0 3 7 】

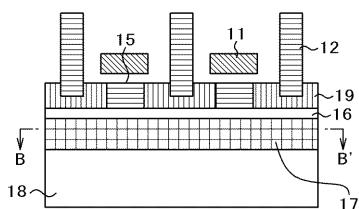

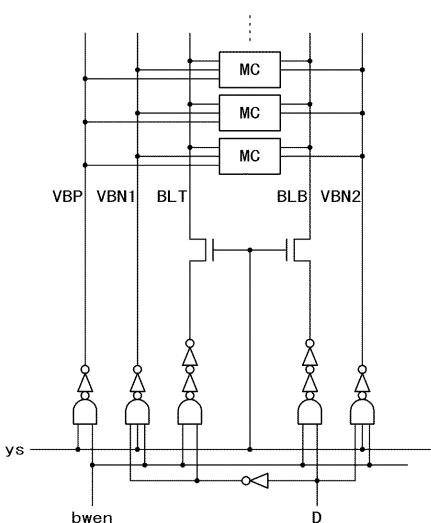

図8に図2に記載したウエル電位の制御を行うための回路図を示す。図8において、VN[4n]からVBN[4n+2]はそれぞれの列のnMOSトランジスタのウエル電極、VBP[4n]からVBP[4n+2]はそれぞれの列のpMOSトランジスタのウエル電極、DRV1はウエル電位を駆動する駆動回路、ys[0]からys[3]は列を選択するための列選択信号、bwen[n]はそのカラムに書き込みが行われることを示す書き込み信号である。列選択信号および書き込み信号によって選択された列に書き込みが行われ、図8の回路ではそれぞれの信号の論理積がウエルノードに入力され、書き込みが行われる場合にはnMOSおよびpMOSのウエル電位がハイに、書き込みが行われない場合には、nMOSおよびpMOSのウエル電位がロウに制御され、図2に記載した電位制御が可能となる。

#### 【 0 0 3 8 】

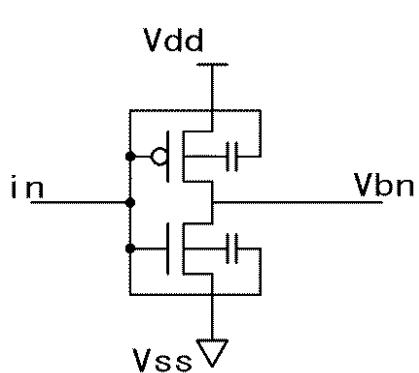

図9にウエルノードを駆動する回路DRV1の最終段のインバータ回路の一例を示す。図9

10

20

30

40

50

において、VddおよびVssは電源ノード、inは入力信号、Vbnは本インバータ回路の出力を示している。本実施例において該当する列が選択されていない場合には、inにハイの電位が印加されており、該当する列に書き込みが行われる場合にinの電位がロウとなる。これによって、出力Vbnはハイとなって、書き込み特性を向上させる。図9の回路中のpMOSトランジスタのウエルノードはゲートと接続されており、inの電位がハイからロウに変化するとpMOSトランジスタのウエルノード電位がロウとなってVthが低下して駆動力が向上し、駆動するメモリセル列のウエルノードの電位を素早くハイに変化させることが可能となる。

#### 【0039】

また、nMOSトランジスタのウエルノードもゲート電極と接続されており、該当メモリセル列のウエル電位を素早くロウ電位に変化させることが可能となる。動作速度が重要でない場合には、それぞれのウエル電位をソース電位に接続することも可能である。また、サブスレショルドリーク電流が問題にならない場合には、nMOSトランジスタのウエルをVddに、pMOSトランジスタのウエルをVssに接続して常にそれぞれのトランジスタのVthを低い状態としておき動作速度を向上させることも出来る。また、出力つまりメモリセル内のウエルノードをハイにする速度のみが重要であり、ロウにする速度は遅くてもよい場合には、pMOSのウエルノードのみゲート電極やVssに接続して高速化を実現することも可能である。

#### 【0040】

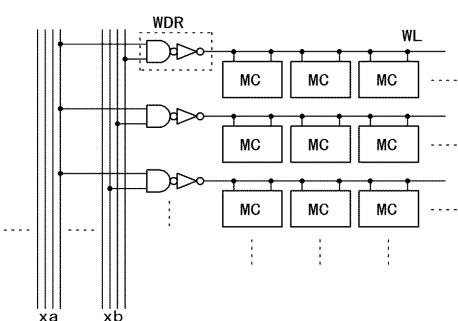

図10に本SRAM回路のワード線を制御する回路の一例を示す。図10において、MCはメモリセル、WLはワード線、WDRはワード線ドライバ、xaおよびxbはアドレスをデコードした信号を表す。本回路構成では、xaおよびxbで選択された1本のワード線がワードドライバ回路によってハイとなり、メモリセルにアクセスされる。

#### 【0041】

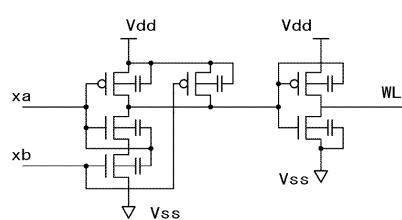

図11に図10中のワードドライバ回路の一例を示す。この回路はxaおよびxbが入力されるNAND回路と、その出力の反転信号をワード線電位として出力するインバータ回路で構成されており、xaおよびxbの双方がハイとなった場合にワード線電位をハイとする。通常、メモリセルの動作速度はワード線の立ち上がる時間に大きく影響される。よって、ワード線をロウからハイにする経路を早くすれば大きくメモリの動作速度を向上することが出来る。本回路では、NAND回路中のnMOSトランジスタとインバータ回路中のpMOSトランジスタのウエルノードがそれぞれゲート電極に接続されている。よって、それぞれのトランジスタはオンとなる時にVthが低下し、駆動力が増加し動作速度が大きくなる。ワード線電位がロウからハイになる場合には、NAND回路中のnMOSトランジスタが両方オンし、さらにインバータ回路のpMOSトランジスタがオンする場合であるため、このようにウエルノードとゲートノードを接続することで、ワード線電位を変化させる速度が向上し、メモリ全体の高速化に寄与する。また、動作速度の向上が重要でない場合には、それぞれのウエル電位をソース電位に接続することも可能である。また、サブスレショルドリーク電流が問題にならない場合には、nMOSトランジスタのウエルをVddに、pMOSトランジスタのウエルをVssに接続して常にそれぞれのトランジスタのVthを低い状態としておき動作速度を向上させることも出来る。

#### 【0042】

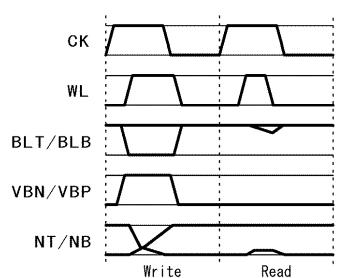

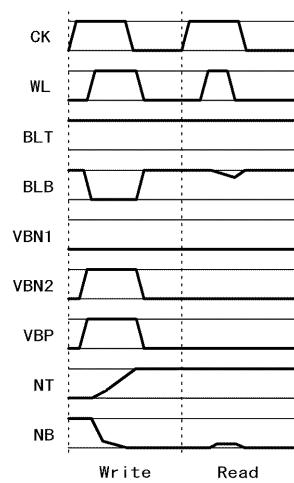

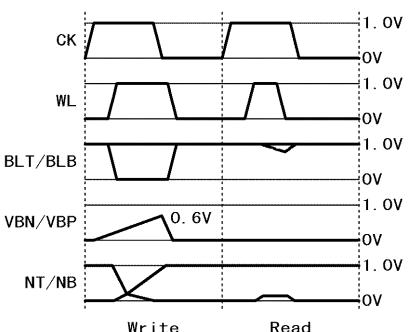

図12に本実施例の回路を用いた場合の回路各部分の動作電圧の変化を示す。図12中で、CKはクロック信号、WLはワード線、BLTおよびBLBはビット線、VBNおよびVBPはアクセスされるメモリセル内のトランジスタのウエルノード、NTおよびNBはアクセスされるメモリセル内の記憶保持ノードであり、WriteおよびReadが書き込みおよび読み出し動作を表す。書き込み時は、クロック信号の立ち上がりとともにメモリセルに書き込まれるデータがビット線上に入力される。また、ほぼ同時にウエルの電位が書き込み動作に最適な電位に制御される。ここで、ワード線電位がロウからハイに立ち上がり、メモリセル内の記憶ノード電位が反転し、新しいデータがメモリセルに書き込まれる。読み出し時にはクロック信号の立ち上がりによりワード線電位がハイとなる。これによってデータ保持ノードの

10

20

30

40

50

データがビット線に出力されて読み出しが行われる。

【0043】

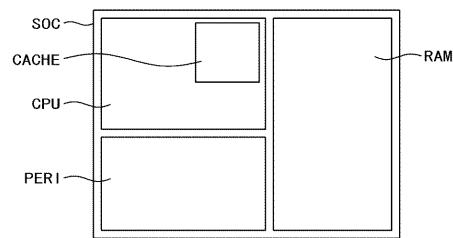

図33に、本発明のSRAMメモリを用いたSoC(System-on-a Chip)の例を示す。SoCは、CPUコアであるCPUとその他の特定の機能を持った回路ブロックPERI、およびさまざまな回路からアクセスされる比較的大容量のメモリRAMで構成されている。またCPUコアの中には、キャッシュメモリCACHEが搭載されている。本発明のSRAMメモリは、SoC中の大容量メモリおよびキャッシュメモリとして用いることが可能である。

【0044】

<実施例2>

図13に本発明を用いたSRAMメモリセルウエル電位の制御方法の一例を示す。なお以降の実施例において、第1の実施例と等しいものに関しては同一の記号を用い、異なるものに関してのみ説明する。本メモリセルのトランジスタレベルの回路構成は図1と同等の回路となっている。図13中で、図2のウエル状態と異なるのは、メモリにアクセスのないNo accessの状態で、pMOSのウエル電位がハイレベルとなっていることである。アクセスされていない状態、特にスタンバイ状態といわれるメモリセルがデータは保持しているがアクセスはされないという状態では、メモリセルのリーク電流が問題になる場合がある。この場合に、pMOSのウエル電位がロウとなっているとpMOSのVthが下がった状態となり、大きいリーク電流が流れる。図13の状態ではpMOSのウエル電位がハイとなり、pMOSのVthが下がっておらずリーク電流が低く抑えられる。

【0045】

<実施例3>

図14に本発明を用いたSRAM回路の回路図を示す。本実施例では、実施例1と異なり、メモリセル内のnMOSトランジスタのウエルノードが、メモリセル内の左側つまりビット線BLTからVSSまで直列に接続されているnMOSと、メモリセル内の右側つまりビット線BLBからVSSまで直列に接続されているnMOSとで別々のノードVBN1とVBN2となっていることである。メモリセルのレイアウトは図5と同様であるがすでに左右のnMOSのウエルノードは別々に接続されているためメモリセルのレイアウトを変更する必要はない。

【0046】

図15に本実施例の回路を用いた場合の回路各部の動作波形を示す。実施例1と異なるのは、書き込み時にVBN1とVBN2が別々の電位に制御されていることである。図15中で、書き込み時にVBN1はロウ電位のままであり、VBN2はハイ電位に制御される。これは、書き込みデータが入力されているビット線電位と関係があり、BLTにハイのデータが、BLBにロウのデータが入力されている場合は、図15の電位関係となりVBN1はロウ電位に、VBN2はハイ電位に制御される。ここでSRAMメモリセルにデータを書き込む際の動作を考える。実施例1の説明で書いた通り、SRAMにデータを書き込む動作はハイのデータを保持している記憶保持ノードの電位を、転送トランジスタを通して電流を流してロウ電位にすることで実現される。BLBにロウのデータが入力された場合には、転送トランジスタTR2を通して大きな電流が流せれば書き込み特性を改善できる。ここで、TR2のウエルノードはVBN2であり、よってVBN2の電位をハイに制御すれば、転送トランジスタTR2の駆動力を高めて書き込み特性が改善する。ここでは図示していないが、BLTにロウのデータが入力された場合には当然VBN1がハイに制御されて書き込み特性が改善される。

【0047】

図16に、図15の波形を実現するための制御回路の回路図を示す。Dは書き込むために入力されたデータ信号である。Dの値がビット線BLTおよびBLBに入力されるとともに、ウエル電位VBN1とVBN2が別々の電位に制御できることがわかる。この構成を取れば、制御されるウエルが減少するため充放電される電荷の量が減少し、書き込み時の動作特性を同等レベルに保ったまま、消費電力を低減することが可能となる。

【0048】

<実施例4>

図17に本発明を用いたSRAM回路の回路図を示す。本実施例では、実施例3からさらに

10

20

30

40

50

メモリセル内の左右のpMOSのウエルノードの制御も別々に分割した構成である。

【0049】

図18に本実施例の回路を用いた場合の回路各部の動作波形を示す。実施例3と異なり、書き込み時にVBN1とVBN2に加えて、VBP1とVBP2が別々の電位に制御されている。図18中で、書き込み時にVBN1およびVBP1はロウ電位のままであり、VBN2およびVBP2はハイ電位に制御される。これは、書き込みデータが入力されているビット線電位と関係があり、BLTにハイのデータが、BLBにロウのデータが入力されている場合は、図18の電位関係となりVBN1およびVBP1はロウ電位に、VBN2およびVBP2はハイ電位に制御される。

【0050】

ここで、SRAMメモリセルにデータを書き込む際の動作を考える。実施例1の説明で書いた通り、SRAMにデータを書き込む動作はハイのデータを保持している記憶保持ノードの電位を、転送トランジスタを通して電流を流してロウ電位にすることで実現される。BLBにロウのデータが入力された場合には、転送トランジスタTR2を通して大きな電流を流すとともに、記憶保持ノードNBへの電荷を供給している負荷トランジスタLD2の駆動能力を低減すれば、記憶保持ノードNBの電位がハイからロウに変化しやすくなり、書き込み特性は改善する。ここで、TR2のウエルノードはVBN2であり、よってVBN2の電位をハイに制御すれば、転送トランジスタTR2の駆動力を高めて書き込み特性が改善する。またLD2のウエルノードはVBP2であり、よってVBP2の電位をハイに制御すれば、負荷トランジスタLD2の駆動力が下がり書き込み特性が改善する。ここでは図示していないが、BLTにロウのデータが入力された場合には当然VBN1およびVBP1の電位がハイに制御されることによって書き込み特性が改善される。

【0051】

図19に本実施例の制御を可能とするメモリセルレイアウトを示す。実施例1で用いられるメモリセルレイアウトを表す図5と異なっているのは、負荷トランジスタのウエルノードが2つに分割されて別々の制御が可能となっていることである。

【0052】

この構成を取れば、制御されるウエルが減少するため充放電される電荷の量が減少し、書き込み時の動作特性を同等レベルに保ったまま、消費電力を低減することが可能となる。さらに、書き込み動作は、ハイの記憶ノード電位をロウにすることによって実行されるが、この時ロウ電位であった記憶保持ノードの電位はハイにチャージされる必要がある。この記憶保持ノードをハイにチャージするのはそのノードにドレイン電極が接続されている負荷トランジスタの役割である。

【0053】

つまり、上記のように記憶保持ノードNBの電位をハイからロウにする書き込みを行う場合には、記憶保持ノードNTの電位をロウからハイにチャージする必要があり、これは負荷トランジスタLD1の電流によって実行される。LD1およびLD2のウエル電位が同じ電位に制御されている場合にはLD1の駆動力も低下しているため、記憶保持ノードNTの電位をハイにするために時間がかかることになる。これは、書き込み時間が厳しい条件下では、動作速度を低下させる要因となる可能性がある。しかし、図17の構成とすれば、負荷トランジスタLD1のVthは低下しており、ロウ電位の記憶保持ノードの電位をハイにするために必要な時間も短縮され、動作速度を向上させることが可能となる。

【0054】

<実施例5>

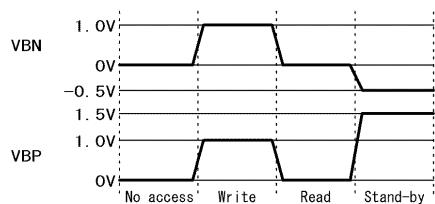

図20に本発明を用いたSRAMメモリセルウエル電位の制御方法の一例を示す。図20では実施例1と異なり、Stand-byというスタンバイモードの状態が追加されている。この状態では、メモリセルではデータを保持する必要があるがアクセスされない状態であり、トランジスタのリーク電流を低減することが全体の電力を減らすために必要となる。スタンバイ状態では、nMOSのウエル電位が負の電位である-0.5Vに、pMOSのウエル電位がハイの電源電圧Vddよりも高い1.5Vに制御される。この状態では、nMOSおよびpMOSのVthが、それぞれのウエル電位がソース電位と同等の電位に制御される場合よりも高く制御されサブス

10

20

30

40

50

レショルドリークと呼ばれるソース-ドレイン間に流れるリーク電流が大きく低減できる。ここでは、nMOSのウエル電位として-0.5Vを、pMOSのウエル電位として1.5Vの例をあげているが、さらにV<sub>th</sub>を変動させるようにnMOSのウエル電位を-0.5Vより低い電位に、またpMOSのウエル電位を1.5Vよりも高い電位にすることも可能である。

#### 【0055】

図21に図20の電位状態を実現するためのSRAM回路構成の回路図を示す。図21中で、V<sub>ssd</sub>はメモリセル内のトランジスタのウエル電位を制御する駆動回路のロウ側の電源線、V<sub>ddd</sub>はメモリセル内のトランジスタのウエル電位を制御する駆動回路のハイ側の電源線、V<sub>bns</sub>はスタンバイ時のnMOSのウエル電位であり本実施例では-0.5V、V<sub>bps</sub>はスタンバイ時のpMOSのウエル電位であり本実施例では1.5V、stbyはスタンバイ時にハイとなるスタンバイ信号である。スタンバイ状態ではない場合には、V<sub>ssd</sub>およびV<sub>ddd</sub>には通常の電源電位である0Vと1.0Vが印加されており、実施例1と同等の動作をする。スタンバイ信号stbyがハイとなり、スタンバイ状態になるとV<sub>ssd</sub>およびV<sub>ddd</sub>には、それぞれ-0.5V、1.5Vが印加され、メモリセル内のnMOSおよびpMOSトランジスタのウエル電位はそれぞれ-0.5Vおよび1.5Vに制御され、それぞれのトランジスタのV<sub>th</sub>が上昇しサブスレショルドリーク電流が低減される。

10

#### 【0056】

＜実施例6＞

図22に本発明を用いたSRAM回路の回路図を示す。実施例1は、一般に横長セルと呼ばれるワード線方向に長い長方形のメモリセルを用いたSRAM回路に最適な回路構成の例であった。横長セルは、ワード線と垂直方向に長いnウエルとpウエルとが交互にワード線方向に繰り返して並ぶことによりメモリセルの形状がワード線方向に長い長方形となるものである。これに対し、本実施例では、一般に縦長セルと呼ばれるメモリセルを用いた場合に最適となる回路構成に関して例示する。縦長セルは、ピット線と垂直方向に長いnウエルとpウエルとが交互にピット線方向に繰り返して並ぶことによりメモリセルの形状がピット線方向に長い長方形となるものである。図22中で、WL[k]はk行目のワード線、VBN[k]はk行目のメモリセルで共通なnMOSトランジスタのウエルノード、VBP[k]はk行目のメモリセルで共通なpMOSトランジスタのウエルノードである。実施例1の図1が示す横長セルのSRAM回路図と異なる点は、VBN[k]およびVBP[k]がWL[k]に平行に延伸するように配置される点である。

20

30

#### 【0057】

図23に回路各部の電位の変化を示す。ワード線が立ち上がった時に同時にnMOSトランジスタのウエルノード電位であるVBNもハイ電位となり、nMOSトランジスタのV<sub>th</sub>が低下して駆動力が増加する。これによって、nMOSトランジスタの電流が増加し、書き込み特性が向上する。また、読み出し時にもnMOSトランジスタの電流が増加するため高速動作が可能となる。またpMOSトランジスタのウエル電位であるVBPは常にハイ電位となっている。これは書き込み時に電流が増加してしまうと書き込み特性を悪化させてしまうためである。

#### 【0058】

図24にメモリセルのレイアウト図を示す。図中の太線で囲まれた部分がウエルとなっており、図5とは異なり、nウエルとpウエルとが交互にピット線方向に繰り返して並ぶ縦長メモリセルとなっている。このセル形状に起因して、縦長セルのSRAM回路図は図22に示すようにVBN[k]およびVBP[k]がWL[k]に平行に延伸する構成となる。

40

#### 【0059】

本レイアウト中をA-A'で切断した場合の断面図を図25に示す。nMOSトランジスタおよびpMOSトランジスタのウエルノードが接続されて形成されていることがわかる。

#### 【0060】

＜実施例7＞

図26に本発明を用いたSRAM回路の回路図を示す。図26中で、V<sub>ssm</sub>はメモリセル内の駆動トランジスタのソース電極を接続したノード、V<sub>cc</sub>はV<sub>dd</sub>より高い電位の電源、stbyおよびstbybはスタンバイ時に入力されるスタンバイ信号である。回路図中で、ゲート電極

が接続されている部分が線ではなく長方形で表現されており、図下方にHigh-Toxと表示されたトランジスタ記号がある。これは、それ以外のトランジスタよりもゲート酸化膜厚( $T_{ox}$ )が厚いトランジスタで、 $V_{dd}$ よりも高い電圧をゲート電極等に印加してもトランジスタが破壊されない、厚膜トランジスタをあらわしている。このトランジスタは通常のLSIではLSI外部との入出力回路で用いられている。 $V_{cc}$ は通常のLSIでの入出力回路に用いられる電源をあらわしており現在1.8Vや2.5V、3.3Vの電圧が使用されている。本実施例では2.5Vであるとして説明を行うが、それ以外の電位であっても同様の効果が得られる。 $stby$ および $stbyb$ はスタンバイ状態を表す信号で、 $stby$ はスタンバイ時にハイ、 $stbyb$ はスタンバイ時にロウに制御される。

## 【0061】

10

図27に回路各部の動作状態毎の電位状態を示す。スタンバイ状態以外は、実施例1と同様になっている。スタンバイ状態には、 $V_{BN}$ は実施例1と同様0Vとなるが、 $V_{BP}$ および $V_{sm}$ の電位が異なる。 $V_{ssm}$ の電位は、約0.3V程度に制御されて、nMOSトランジスタがバックバイアスが印加されたのと同様の状態となり、サブスレショルドリーク電流が大きく低減される。具体的には、1/10以下に低減可能である。また、nMOSおよびpMOSトランジスタのゲート電極からチャネルに流れるゲートリリーク電流も、電界が緩和されることから大きく低減される。 $V_{ssm}$ の電位が制御された場合、pMOSトランジスタに関してはソース-ドレン間の電圧が約2/3になった程度であるためリリーク電流もそれにほぼ比例して低減されるのみで約2/3程度にしかさがらない。本回路では、pMOSトランジスタのウエルノードに2.5Vの電位が印加される。これによって、pMOSトランジスタの $V_{th}$ が200mV程度上昇しサブスレショルドリーク電流は1/100以下に低減できる。これにより、スタンバイ状態でのリリーク電流を大きく低減することが可能となる。

20

## 【0062】

また、本発明の構成では、ウエルノードをSRAMで用いられている電源の電圧よりも高い電圧に制御する際に、LSIの入出力回路に用いられている電源がウエルノードに印加される構成を取っている。よって、高い電圧を発生する回路を余分に持つ必要がなく、回路面積および消費電力の点で有利となる。

## 【0063】

30

一方では、pMOSトランジスタのウエルノードに印加する高い電圧はSRAM回路で用いられる電源電圧よりも高い電圧であれば、LSIの入出力回路に用いられる電源の電圧と異なる電圧であっても同じ効果が得られる。よって、同一LSI内に電源を生成する回路を持って高い電圧を発生させることも可能である。また、外部からSRAMに印加される電源電圧よりも高い電圧を供給し、これをpMOSトランジスタのウエルノードに印加することも可能である。

## 【0064】

40

図31に、ゲート酸化膜厚( $Tox$ )と埋め込み酸化膜厚( $T_{box}$ )、電源電圧( $V_{dd}$ )とpMOSトランジスタのウエル電位( $V_{BP}$ )の関係の例を示す。Pattern1は、本実施例で想定している膜厚と電圧の関係を示している。Pattern2は、pMOSトランジスタにかけることの出来る最大の電圧を印加して、リリーク電流を低減する効果を最大にした場合の例を示している。Pattern3は、ゲート酸化膜の厚さが薄くなり、それにともなって電源電圧が低下している関係を表している。Pattern4は、埋め込み酸化膜の厚さを厚くすることによってウエルノードの電位を変化させた時に $V_{th}$ が変動する効果が小さくなるが、その分ウエルノードに印加する電圧を高めることで、同等の性能を達成する構成の例を示している。Pattern5は、埋め込み酸化膜の膜厚を薄くした場合の例を示している。pMOSトランジスタのウエルノードには入出力回路で用いられるのと同じ電圧が印加されているが、埋め込み酸化膜厚が薄いために $V_{th}$ が変動する効果が大きく、Pattern2とほぼ同等の性能が得られると考えられる。Pattern6は、酸化膜の膜厚はPattern5と同様で、ウエルノードにさらに高い電圧を印加した例を示している。この例では、さらに高いリリーク電流削減効果が得られる。Pattern7では、埋め込み酸化膜の厚さをさらに薄くした例が示されている。ウエルノードの電位はそれほど大きくなりがPattern2よりもリリーク電流を低減する効果は大きいと考えられる。

50

## 【0065】

## &lt;実施例8&gt;

図28に本発明を用いたSRAMメモリセル内のトランジスタの電位の状態を示す。本実施例では、書き込み時に0Vから上昇するウエル電位が0.5Vとなっている。これにより、VBNおよびVBPを制御することにより消費される電力が低減できる。また、VBNおよびVBPの電位を制御するのにかかる時間を短くすることが出来、高速化の効果もある。

## 【0066】

## &lt;実施例9&gt;

図29に本発明を用いたSRAM回路各部分の電位の変化を示す。本実施例では、実施例1とは異なり、制御されるべきVBNおよびVBPの電位がフルスイングせずに0.6V程度ましか上昇していない。これによって、実施例8と同様にVBNおよびVBPを制御することで消費される消費電力を抑える効果がある。

10

## 【0067】

本実施例は、実施例1と同様の回路構成で実現することが可能である。1点異なるのは、VBNおよびVBPを駆動する駆動回路の駆動力を小さくすることである。実施例1では、VBNおよびVBPの電位を急速に変化させるため駆動力の大きな駆動回路が必要であったが、本実施例の回路はその駆動回路の駆動力を小さくすることで実現できる。実際には、VBNおよびVBPを駆動するトランジスタのゲート幅を小さくすればよい。これによって、実施例1と比較して回路面積も小さくすることが可能となる。

## 【0068】

20

従来のバルクトランジスタのゲート電極を駆動する場合には、信号の電位変化が遅いとホットキャリアが発生してLSIの信頼性が劣化する等の問題があったが、本回路で変化するのはウエルの電位であるためホットキャリア等信頼性の問題も発生しない。

## 【0069】

## &lt;実施例10&gt;

図30に、本発明を用いたSRAM回路内のメモリセルのウエル電位であるVBNおよびVBPが、書き込み、読み出しおよびスタンバイ状態においてとりうる電位の関係を表す。Pattern1は実施例1の例を示している。

## 【0070】

Pattern2では、実施例1とは異なり読み出し時にもVbnの電位を1.0Vに制御している。これによって、読み出し時のnMOSトランジスタの電流が増加し高速な読み出し動作が可能となる。

30

## 【0071】

Pattern3では、スタンバイ状態にVBPを2.5Vに制御することでpMOSトランジスタのVthを上昇させリーク電流を大きく低減することが可能となる。

## 【0072】

Pattern4では、スタンバイ状態でPattern3よりもVBNの電位をマイナスの電位としている。これによってnMOSトランジスタのVthが上昇し、リーク電流をさらに低減することが可能となる。

## 【0073】

40

Pattern5では、書き込み時にVBNの電位を2.5Vまで昇圧し、これによってnMOSトランジスタのVthを大きく低下させている。よって、nMOSトランジスタの電流がPattern1等と比較してさらに大きくなり、書き込み特性がさらに改善されるとともに動作速度が高速化する。

## 【0074】

Pattern6では、さらに読み出し時のVBNの電位を2.5Vまで昇圧し、これによってnMOSトランジスタのVthを大きく低下させている。よって、nMOSトランジスタの電流がPattern2と比較してさらに大きくなり、読み出しメモリセル電流が大きく改善し、動作速度が高速化する。

## 【0075】

50

以上の各実施例によれば、トランジスタ動作の高速化とリーク電流の低減とが可能となる。また、SRAM回路の動作に必要な動作マージンが改善し動作特性が向上する。さらに、メモリセル面積の増大を抑制できる。

【図面の簡単な説明】

【0076】

【図1】本発明が適用されたSRAMメモリセルの回路構成の概略図。

【図2】本発明が適用されたSRAM内のウエルノードの電圧関係を表す図。

【図3】本発明で使用されるトランジスタ構造の断面の概略図。

【図4】本発明で使用されるトランジスタの等価回路を示す図。

【図5】本発明が適用されたSRAMメモリセルのレイアウトの概略図。 10

【図6】本発明が適用されたSRAMメモリセルの断面図。

【図7】本発明が適用されたSRAMメモリセルの断面図。

【図8】本発明が適用されたSRAMのウエルノードを制御する回路の概略図。

【図9】本発明が適用されたSRAMの制御回路の概略図。

【図10】本発明が適用されたSRAMのワード線ドライバの概略図。

【図11】本発明が適用されたSRAMのワード線ドライバの概略図。

【図12】本発明が適用されたSRAM内の各ノードの電位変化を表す図。

【図13】本発明が適用されたSRAM内のウエルノードの電圧関係を表す図。

【図14】本発明が適用されたSRAMメモリセルの回路構成の概略図。

【図15】本発明が適用されたSRAM内の各ノードの電位変化を表す図。 20

【図16】本発明が適用されたSRAM内の各ノードの電位変化を表す図。

【図17】本発明が適用されたSRAMメモリセルの回路構成の概略図。

【図18】本発明が適用されたSRAM内の各ノードの電位変化を表す図。

【図19】本発明が適用されたSRAMメモリセルのレイアウトの概略図。

【図20】本発明が適用されたSRAM内のウエルノードの電圧関係を表す図。

【図21】本発明が適用されたSRAMのウエルノードを制御する回路の概略図。

【図22】本発明が適用されたSRAMメモリセルの回路構成の概略図。

【図23】本発明が適用されたSRAM内の各ノードの電位変化を表す図。

【図24】本発明が適用されたSRAMメモリセルのレイアウトの概略図。

【図25】本発明が適用されたSRAMメモリセルの断面図。 30

【図26】本発明が適用されたSRAMのウエルノードを制御する回路の概略図。

【図27】本発明が適用されたSRAM内の各ノードの電圧関係を表す図。

【図28】本発明が適用されたSRAM内のウエルノードの電圧関係を表す図。

【図29】本発明が適用されたSRAM内の各ノードの電位変化を表す図。

【図30】本発明が適用されたSRAM内のウエルノードの電圧関係を表す図。

【図31】膜厚とウエルノードへの印加電圧の関係を表す図。

【図32】従来のSRAMメモリセルの回路構成の概略図。

【図33】本発明が適用されたSRAMを搭載するシステムLSIの概略図。

【符号の説明】

【0077】

TR1,TR2,201,202...転送トランジスタ、DR1,DR2,203,204...駆動トランジスタ、LD1,LD2,205,206...負荷トランジスタ、NT,NB,207,208...メモリセル内のデータ記憶ノード、WL...ワード線、Vdd...電源線、Vss...接地電位、LT,BLB,BLT[n],BLB[n],BLT[n+1],BLB[n+1]...ピット線、VBN,VBN[n],VBN[n+1],VBN1,VBN2,VBN[4n],VBN[4n+1],VBN[4n+2],VBN[k],VBN1[n],VBN2[n]...nMOSウエルノード、VBP,VBP[n],VBP[n+1],VBP1,VBP2,VBP[4n],VBP[4n+1],VBP[4n+2],VBP[k],VBP1[n],VBP2[n]...pMOSウエルノード、1,11...ゲート電極、2...ドレイン電極、3...ソース電極、4,17,Well...ウエル、5,18...支持基板、6,16...埋め込み酸化膜層、7,13...素子分離層、12,Contact...コンタクト、19,Diffusion...拡散層、14...ゲート絶縁膜、15...SOI層、MC...メモリセル、ys,ys[0]~ys[3]...カラム選択信号、DRV1...ウエルノードドライバ、in...入力信号、WDR...ワード線ドライバ、xa,xb...アドレスデコード信号、CK...クロック 50

ク信号、bwen...書き込み信号、D...入力データ、Vssd...ウエルノードドライバのVss線、Vd dd...ウエルノードドライバのVdd線、Vbnst, Vbst...スタンバイ用ウエルノード電位線、st by, stbyb...スタンバイ状態制御信号、Vssm...メモリセル内駆動トランジスタソース線、Vc...Vddより高い電位の電源線、SOC...システムLSIのチップ、CPU...CPUコア、CACHE...キャッシュメモリ、RAM...ワークメモリ、PERI...システムLSI中のCPUコア外の論理回路。

【図1】

図1

【図2】

図2

【図3】

図3

【図4】

図4

【図5】

図5

■ Gate

□ Contact

▨ Diffusion

■ Well

【図6】

図6

【図7】

図7

【図8】

図8

【図9】

図9

【図10】

図10

【図 1 1】

図 1 1

【図 1 2】

図 1 2

【図 1 3】

図 1 3

【図 1 5】

図 1 5

【図 1 4】

図 1 4

【図 1 6】

図 1 6

【図17】

図17

【図18】

図18

【図19】

図19

Gate

Diffusion

Contact

Well

【図20】

図20

【図21】

図21

【図22】

図22

【図23】

図23

【図24】

図24

【図25】

図25

【図26】

図26

【図27】

図27

【図29】

図29

【図30】

図30

【図28】

図28

|          | read |     | write |      | stand-by |      |

|----------|------|-----|-------|------|----------|------|

|          | Vbn  | Vbn | Vbn   | Vbn  | Vbn      | Vbn  |

| Pattern1 | 0V   | 0V  | 1.0V  | 1.0V | 0V       | 1.0V |

| Pattern2 | 1.0V | 0V  | 1.0V  | 1.0V | 0V       | 1.0V |

| Pattern3 | 0V   | 0V  | 1.0V  | 1.0V | 0V       | 2.5V |

| Pattern4 | 0V   | 0V  | 1.0V  | 1.0V | -1.0V    | 2.5V |

| Pattern5 | 0V   | 0V  | 2.5V  | 1.0V | 0V       | 1.0V |

| Pattern6 | 2.5V | 0V  | 2.5V  | 1.0V | 0V       | 1.0V |

【図31】

図31

|          | Tox   | Tbox  | Vdd  | VBP   |

|----------|-------|-------|------|-------|

| Pattern1 | 2.0nm | 10nm  | 1.2V | 2.5V  |

| Pattern2 | 2.0nm | 10nm  | 1.2V | 6.0V  |

| Pattern3 | 1.2nm | 10nm  | 1.0V | 6.0V  |

| Pattern4 | 1.2nm | 20nm  | 1.0V | 12.0V |

| Pattern5 | 1.2nm | 5.0nm | 1.0V | 2.5V  |

| Pattern6 | 1.2nm | 5.0nm | 1.0V | 4.0V  |

| Pattern7 | 1.2nm | 2.4nm | 1.0V | 1.8V  |

【図33】

図33

【図32】

図32

---

フロントページの続き

(56)参考文献 特開2001-053168(JP,A)

特開2005-251776(JP,A)

特開平11-016363(JP,A)

特開平06-089574(JP,A)

特開2005-085349(JP,A)

特開2001-338993(JP,A)

(58)調査した分野(Int.Cl., DB名)

H01L 21/8244

G11C 11/412

H01L 27/10

H01L 27/11

H01L 29/786