(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2013-225045

(P2013-225045A)

(43) 公開日 平成25年10月31日(2013.10.31)

(51) Int.Cl.

**G09G 3/36 (2006.01)**

**G09G 3/20 (2006.01)**

**G02F 1/133 (2006.01)**

F 1

GO9G 3/36

GO9G 3/20 622E

GO9G 3/20 623G

GO9G 3/20 623H

GO9G 3/20 622D

テーマコード(参考)

2H193

5C006

5C080

審査請求 未請求 請求項の数 8 O L (全 18 頁) 最終頁に続く

(21) 出願番号

特願2012-97444 (P2012-97444)

(22) 出願日

平成24年4月23日 (2012.4.23)

(71) 出願人

000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74) 代理人

100088672

弁理士 吉竹 英俊

(74) 代理人

100088845

弁理士 有田 貴弘

(72) 発明者

立花 裕史

東京都千代田区丸の内二丁目7番3号 三

菱電機株式会社内

F ターム(参考) 2H193 ZC30 ZD38 ZF23

|            |      |      |      |      |

|------------|------|------|------|------|

| 5C006 AB01 | BC03 | BC14 | BF03 | BF04 |

| BF06       | BF22 | BF24 | FA42 | FA51 |

| 5C080 AA10 | DD23 | DD27 | EE23 | JJ02 |

| JJ04       |      |      |      |      |

(54) 【発明の名称】表示パネルの駆動回路および表示装置

## (57) 【要約】

【課題】表示装置の走査線または画像信号線の駆動回路において、出力信号の数を任意に設定可能にし、上下反転表示や左右反転表示を容易に行うことを可能にする。

【解決手段】走査線駆動回路DRVは、出力させる信号数を指定する出力数制御信号OECNTに対する演算処理により、出力信号OUTVi<sub>i</sub>を出力させる単位レジスタSR<sub>i</sub>を特定する演算結果OUTC<sub>i</sub>を生成する演算回路20を備える。各単位レジスタSR<sub>i</sub>の入力段には、演算結果OUTC<sub>i</sub>に基づいて当該単位レジスタSR<sub>i</sub>に出力信号OUTVi<sub>i</sub>を出力させるか否かを制御する信号制御回路SCが設けられる。

【選択図】図2

**【特許請求の範囲】****【請求項 1】**

表示パネルの複数の走査線または複数の画像信号線に信号を出力する複数の単位駆動回路と、

出力させる信号数を指定する第1の制御信号を受け、当該第1の制御信号に対する演算処理により、前記複数の単位駆動回路のうち信号を出力する単位駆動回路を特定する第2の制御信号を生成する演算回路とを備え、

前記複数の単位駆動回路の各々は、

前記第2の制御信号に基づいて当該単位駆動回路に信号を出力させるか否かを制御する信号制御回路を備える

ことを特徴とする表示パネルの駆動回路。

**【請求項 2】**

前記第1の制御信号は、パルス幅によって前記信号数を指定するパルス信号である請求項1記載の表示パネルの駆動回路。

**【請求項 3】**

前記演算回路は、

前記パルス幅をカウントするカウンタと、

前記カウンタのカウント値に対する演算処理により前記第2の制御信号を生成する演算部とを備える

請求項2記載の表示パネルの駆動回路。

**【請求項 4】**

前記複数の単位駆動回路は、従属接続しており、

最前段の単位駆動回路から、前記第1の制御信号が指定する前記信号数と同数の単位駆動回路に信号を出力させる

請求項1から請求項3のいずれか一項記載の表示パネルの駆動回路。

**【請求項 5】**

前記複数の単位駆動回路は、従属接続しており、

最後段の単位駆動回路から、前記第1の制御信号が指定する前記信号数と同数の単位駆動回路に信号を出力させる

請求項1から請求項3のいずれか一項記載の表示パネルの駆動回路。

**【請求項 6】**

前記複数の単位駆動回路は、従属接続しており、

最前段から所定数の単位駆動回路と、最後段から所定数の単位駆動回路とに信号を出力させることにより、合計で前記第1の制御信号が指定する前記信号数と同数の単位駆動回路に信号を出力させる

請求項1から請求項3のいずれか一項記載の表示パネルの駆動回路。

**【請求項 7】**

請求項1から請求項6のいずれか一項記載の表示パネルの駆動回路と、

前記駆動回路の動作タイミングを規定するタイミングコントローラとを備え、

前記第1の制御信号は、前記タイミングコントローラから供給されていることを特徴とする表示装置。

**【請求項 8】**

前記タイミングコントローラは、前記複数の単位駆動回路に動作を開始させるスタート信号および当該動作を停止させるエンド信号に基づいて、前記第1の制御信号を生成する請求項7記載の表示装置。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、表示パネルの走査線または画像信号線を駆動する駆動回路およびその駆動方法に関するものである。

**【背景技術】****【0002】**

例えば液晶表示装置等において、表示パネル（液晶パネル）の走査線を駆動する駆動回路（走査線駆動回路）は、その液晶表示パネルの走査線の数に応じた数の信号を出力するように構成される。同様に、液晶表示パネルの画像信号線を駆動する駆動回路（画像信号線駆動回路）は、画像信号線の数に応じた数の信号を出力するように構成される。

**【0003】**

一般に、表示パネルの走査線および画像信号線の数は、1つの駆動回路（集積回路）が出力可能な信号の数（出力端子の数）よりも多いため、走査線および画像信号線は、それぞれ従属接続した複数の駆動回路を用いて駆動されている。液晶表示装置のコスト低減の観点からは、使用する駆動回路の数は少ない方が好ましいので、近年の微細加工技術の向上に伴い、1つの駆動回路に設けられる出力端子の数は増加傾向にある。10

**【0004】**

また、駆動回路が有する出力端子の全てを使用することが最も効率がよいが、表示パネルの解像度（走査線および画像信号線の数）は様々であるため、必要とされる信号数と、駆動回路の出力端子数とが一致することは限らない。駆動回路の出力端子数が増加した昨今では、これまで以上に、表示パネルの解像度と駆動回路の出力端子数とを合わせることが難しくなっている。そのため、駆動回路の一部の出力端子が不使用とされる場合も多い。

**【0005】**

表示パネルの標準的な解像度に合うように、出力信号の数を切り替えできる（つまり、一部の出力端子を不使用にできる）機能を有する駆動回路も提案されている（例えば特許文献1）。

20

**【先行技術文献】****【特許文献】****【0006】****【特許文献1】特開2009-128776号公報****【発明の概要】****【発明が解決しようとする課題】****【0007】**

特許文献1の技術では、出力信号数の切り替えは、標準的な解像度を想定した数種類の中から選択するものであり、あらゆる解像度に対応できるほどの充分な汎用性があるとは言えない。また、特殊な解像度の表示パネルに対応させることは困難である。

30

**【0008】**

また、表示パネルの解像度と駆動回路が出力する信号の数が一致しない場合、表示装置の上下反転表示機能や左右反転表示機能にも大きな影響を与える。上下反転表示や左右反転表示にかかる動作は、画像信号処理部の回路で制御されるが、駆動回路の出力信号数が表示パネルの解像度と一致しない場合は、画像信号を駆動回路の端子数に合わせて処理するために多くのメモリと、画像信号の表示位置を把握してその表示位置に画像を出力させるための制御回路が必要になり、コストの上昇を招く。また、画像信号処理部がそのような制御回路を有しなければ、上下反転表示や左右反転表示を行うことができず、表示装置の機能が制限される。

40

**【0009】**

本発明は以上のような課題を解決するためになされたものであり、表示装置の走査線または画像信号線の駆動回路において、出力信号の数を任意に設定可能にし、上下反転表示や左右反転表示を容易に行うことを行ふことを目的とする。

**【課題を解決するための手段】****【0010】**

本発明に係る表示パネルの駆動回路は、表示パネルの複数の走査線または複数の画像信号線に信号を出力する複数の単位駆動回路と、出力させる信号数を指定する第1の制御信号を受け、当該第1の制御信号に対する演算処理により、前記複数の単位駆動回路のうち

50

信号を出力する単位駆動回路を特定する第2の制御信号を生成する演算回路とを備え、前記複数の単位駆動回路の各々は、前記第2の制御信号に基づいて当該単位駆動回路に信号を出力させるか否かを制御する信号制御回路を備えるものである。

**【発明の効果】**

**【0011】**

本発明によれば、駆動回路が出力する信号数を任意に設定できるため、解像度による駆動回路の選別が不要となり、駆動回路の部材共有化が図れ、表示装置のコストを低減させることができる。また、駆動回路が出力する信号数と走査線（または画像信号線）の数を確実に一致させることができるので、上下反転表示や左右反転表示を処理が容易に（画像信号処理部の回路を複雑にさせることなく）実現できる。また、演算回路による演算処理によって、信号を出力させる単位駆動回路を任意に指定できるので、配線の自由度が向上し、駆動回路と液晶パネルとの結線がしやすくなるという利点も得られる。

10

**【0012】**

また、駆動回路の出力端子本数を外部から任意に設定することで多くの解像度に対応することが可能であり、解像度による駆動回路の出力選択が不要となり、駆動回路の部材共有化が図れ、コスト低減も可能となる。

**【図面の簡単な説明】**

**【0013】**

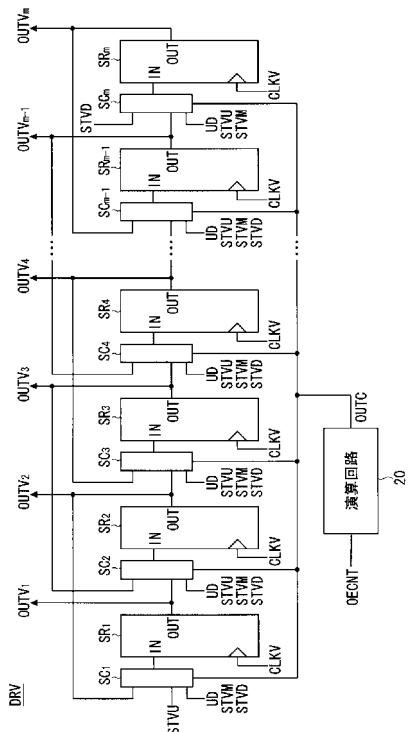

**【図1】**実施の形態1に係る液晶表示装置の主要構成を示す図である。

20

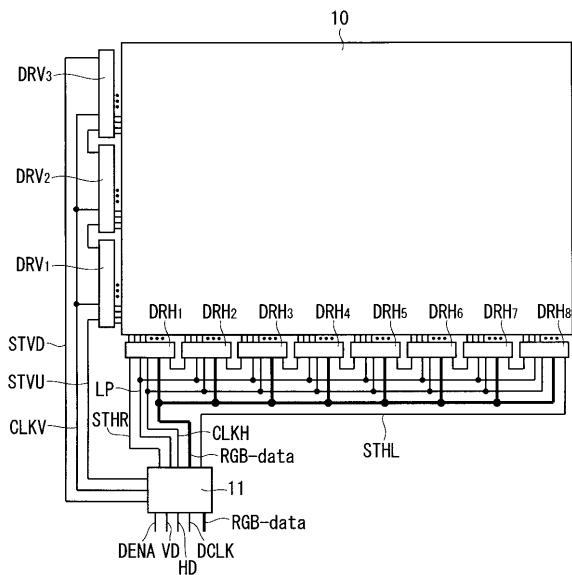

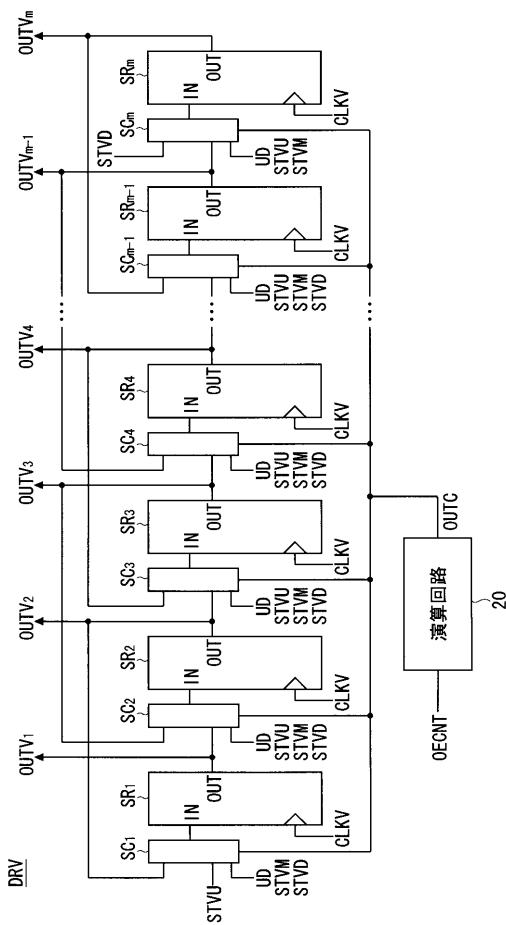

**【図2】**実施の形態1に係る走査線駆動回路のブロック図である。

**【図3】**実施の形態1に係る走査線駆動回路が備える信号制御回路の各動作モードを説明するための図である。

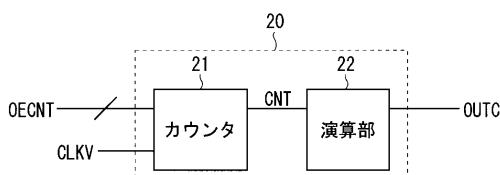

**【図4】**実施の形態1に係る走査線駆動回路が備える演算回路のブロック図である。

**【図5】**実施の形態1に係る走査線駆動回路が備える演算回路の動作を示す図である。

**【図6】**実施の形態1に係る走査線駆動回路と液晶パネルとの接続状態の一例を示す図である。

**【図7】**実施の形態1に係る走査線駆動回路の順方向走査時の動作を説明するためのタイミング図である。

**【図8】**実施の形態1に係る走査線駆動回路の逆方向走査時の動作を説明するためのタイミング図である。

30

**【図9】**実施の形態1に係る走査線駆動回路と液晶パネルとの接続状態の一例を示す図である。

**【図10】**実施の形態1に係る走査線駆動回路の順方向走査時の動作を説明するためのタイミング図である。

**【図11】**実施の形態2に係る走査線駆動回路と液晶パネルとの接続状態の一例を示す図である。

**【図12】**実施の形態3に係る走査線駆動回路の順方向走査時の動作を説明するためのタイミング図である。

**【図13】**実施の形態4に係る走査線駆動回路と液晶パネルとの接続状態の一例を示す図である。

40

**【図14】**実施の形態4に係る走査線駆動回路の順方向走査時の動作を説明するためのタイミング図である。

**【発明を実施するための形態】**

**【0014】**

<実施の形態1>

図1は、本発明の実施の形態1に係る液晶表示装置の主要構成を示す図である。図1の如く、当該液晶表示装置は、表示パネルとしての液晶パネル10、タイミングコントローラ11、画像信号線駆動回路D RH<sub>1</sub> ~ D RH<sub>8</sub>および走査線駆動回路D RV<sub>1</sub> ~ D RV<sub>3</sub>、を備えている。

**【0015】**

50

図示は省略するが、液晶パネル10には、複数の走査線と、複数の画像信号線とが互いに直行して配設されており、その各交点近傍に画素が形成されている。各画素には、走査線により制御され、画像信号線を通して画素に画像信号を供給するスイッチング素子が設けられている。

#### 【0016】

走査線駆動回路DRV<sub>1</sub> ~ DRV<sub>3</sub>は、走査線を駆動する集積回路である。走査線駆動回路DRV<sub>1</sub> ~ DRV<sub>3</sub>の各々には、個々の走査線を駆動する駆動回路が複数個集積されており、それら複数の駆動回路は、走査線駆動回路DRV<sub>1</sub> ~ DRV<sub>3</sub>それぞれの内部で縦続接続してシフトレジスタを構成している。また図1のように、3つの走査線駆動回路DRV<sub>1</sub> ~ DRV<sub>3</sub>も縦続接続される。これにより、走査線駆動回路DRV<sub>1</sub> ~ DRV<sub>3</sub>に集積されている駆動回路は全て縦続接続されて、シフトレジスタを構成することになる。以下、シフトレジスタの各段に相当する駆動回路を「単位レジスタ」と称する。10

#### 【0017】

画像信号線駆動回路DRH<sub>1</sub> ~ DRH<sub>8</sub>は、画像信号線に画像データを送り出すための集積回路である。画像信号線駆動回路DRH<sub>1</sub> ~ DRH<sub>8</sub>の各々には、個々の画像信号線に画像データを送り出す駆動回路が複数個集積されており、各駆動回路は、画像データを保持すると共に、その画像データを後述のラッチパルスLPに応じて画像信号線へ出力するラッチ回路を含んでいる。また、画像信号線駆動回路DRH<sub>1</sub> ~ DRH<sub>8</sub>の各々には、各ラッチ回路が画像データを取り込むタイミングを規定するシフトレジスタも集積されており、その単位レジスタは、画像信号線駆動回路DRH<sub>1</sub> ~ DRH<sub>8</sub>それぞれの内部で縦続接続している。また図1のように、8つの画像信号線駆動回路DRH<sub>1</sub> ~ DRH<sub>8</sub>も縦続接続される。これにより、画像信号線駆動回路DRH<sub>1</sub> ~ DRH<sub>8</sub>内の単位レジスタは全て縦続接続されることとなる。20

#### 【0018】

タイミングコントローラ11には、赤、緑、青の各画像データを含むRGBデータ(RGB-data)と共に、画像信号線駆動回路DRH<sub>1</sub> ~ DRH<sub>8</sub>および走査線駆動回路DRV<sub>1</sub> ~ DRV<sub>3</sub>の制御の基準となる信号(制御基準信号)として、データタイネーブル信号DENA、水平同期信号HD、垂直同期信号VD、クロックDCLKが入力される。データタイネーブル信号DENAは、RGBデータが有効である期間を示す信号である。水平同期信号HDは、液晶パネル10の水平方向の同期をとるための信号であり、垂直同期信号VDは垂直方向の同期をとるための信号である。クロックDCLKは、タイミングコントローラ11の動作タイミングを規定する基準クロックとなる。30

#### 【0019】

タイミングコントローラ11は、これらの制御基準信号に基づいて、画像信号線駆動回路DRH<sub>1</sub> ~ DRH<sub>8</sub>および走査線駆動回路DRV<sub>1</sub> ~ DRV<sub>3</sub>の動作を制御するための制御信号を生成する。

#### 【0020】

画像信号線駆動回路DRH<sub>1</sub> ~ DRH<sub>8</sub>の制御信号には、クロックCLKH(以下「水平クロック」)、順方向走査用のスタート信号STHR(以下「順方向水平スタート信号」)、逆方向走査用のスタート信号STHL(以下「逆方向水平スタート信号」)、ラッチパルスLPなどが含まれる。水平クロックCLKHは、画像信号線駆動回路DRH<sub>1</sub> ~ DRH<sub>8</sub>の動作の基準クロックである。なお、水平方向の走査については、液晶パネル10の画面の左から右への走査を「順方向走査」、右から左への走査を「逆方向走査」と定義している。40

#### 【0021】

順方向水平スタート信号STHRは、順方向走査時のRGBデータにおける各ラインの先頭を表すパルス信号である。順方向水平スタート信号STHRは、画像信号線駆動回路DRH<sub>1</sub>のシフトレジスタに入力され、順方向走査における各駆動回路の画像データの取り込みタイミングは、これにより規定される。画像信号線駆動回路DRH<sub>1</sub> ~ DRH<sub>8</sub>内の単位レジスタは全て縦続接続されているので、順方向水平スタート信号STHRが画像50

信号線駆動回路 D R H<sub>1</sub> に入力されることにより、画像信号線駆動回路 D R H<sub>1</sub> ~ D R H<sub>8</sub> 内の全てのラッチ回路が、シリアルに送信されてくる R G B データを順番に取り込むことができる。

#### 【 0 0 2 2 】

逆方向水平スタート信号 S T H L は、逆方向走査時の R G B データにおける各ラインの先頭を表すパルス信号である。逆方向水平スタート信号 S T H L は、画像信号線駆動回路 D R H<sub>8</sub> のシフトレジスタに入力され、逆方向走査における各駆動回路の画像データの取り込みタイミングは、これにより規定される。逆方向水平スタート信号 S T H L が画像信号線駆動回路 D R H<sub>8</sub> に入力されることにより、画像信号線駆動回路 D R H<sub>1</sub> ~ D R H<sub>8</sub> 内の全てのラッチ回路は、順方向走査時とは逆の順番で、R G B データを取り込むことができる。10

#### 【 0 0 2 3 】

ラッチパルス L P は、画像信号線駆動回路 D R H<sub>1</sub> ~ D R H<sub>8</sub> の各ラッチ回路が取り込んで保持している R G B データを、液晶パネル 1 0 の画像信号線に出力するタイミングを規定する信号である。

#### 【 0 0 2 4 】

その他、画像信号線駆動回路 D R H<sub>1</sub> ~ D R H<sub>8</sub> の制御信号には、液晶駆動の極性を反転するための極性反転信号なども含まれる。タイミングコントローラ 1 1 は、これらの制御信号を R G B データと共に画像信号線駆動回路 D R H<sub>1</sub> ~ D R H<sub>8</sub> に送信する。20

#### 【 0 0 2 5 】

一方、走査線駆動回路 D R V<sub>1</sub> ~ D R V<sub>3</sub> の制御信号には、クロック C L K V (以下「垂直クロック」)、順方向走査用のスタート信号 S T V U (以下「順方向垂直スタート信号」)、逆方向走査用のスタート信号 S T V D (以下「逆方向垂直スタート信号」)などが含まれる。垂直クロック C L K V は、走査線駆動回路 D R V<sub>1</sub> ~ D R V<sub>3</sub> の動作の基準クロックである。なお、垂直方向の走査については、液晶パネル 1 0 の画面の下から上への走査を「順方向走査」、上から下への走査を「逆方向走査」と定義している。20

#### 【 0 0 2 6 】

順方向垂直スタート信号 S T V U は、順方向走査時において、各フレームの先頭を表すパルス信号となる。順方向垂直スタート信号 S T V U は、走査線駆動回路 D R V<sub>1</sub> のシフトレジスタに入力され、順方向走査における各走査線の駆動タイミングはこれにより規定される。走査線駆動回路 D R V<sub>1</sub> ~ D R V<sub>3</sub> 内の単位レジスタは全て継続接続されているので、順方向垂直スタート信号 S T V U が走査線駆動回路 D R V<sub>1</sub> に入力されることにより、走査線駆動回路 D R V<sub>1</sub> ~ D R V<sub>3</sub> で構成されるシフトレジスタは、液晶パネル 1 0 の各走査線を下から上へ順番にアクティブ状態にする。アクティブ状態となった走査線に接続した画素では、スイッチング素子がオンになり、当該画素は書き込み可能な状態となる。30

#### 【 0 0 2 7 】

逆方向垂直スタート信号 S T V D は、逆方向走査時において、各フレームの先頭を表すパルス信号となる。逆方向垂直スタート信号 S T V D は、走査線駆動回路 D R V<sub>3</sub> のシフトレジスタに入力され、逆方向走査における各走査線の駆動タイミングはこれにより規定される。逆方向垂直スタート信号 S T V D が走査線駆動回路 D R V<sub>3</sub> に入力されることにより、走査線駆動回路 D R V<sub>1</sub> ~ D R V<sub>3</sub> で構成されるシフトレジスタは、液晶パネル 1 0 の各走査線を上から下へ順番にアクティブ状態にする。40

#### 【 0 0 2 8 】

走査線駆動回路 D R V<sub>1</sub> ~ D R V<sub>3</sub> が、液晶パネル 1 0 の走査線を順番にアクティブ状態にして各ラインの画素を書き込み可能な状態にし、画像信号線駆動回路 D R H<sub>1</sub> ~ D R H<sub>8</sub> が、ラインごとの R G B データを、画像信号線を通して各画素に書き込んでいく。この動作を繰り返すことにより、液晶パネル 1 0 全体に画像が表示される。

#### 【 0 0 2 9 】

図 2 は、実施の形態 1 に係る走査線駆動回路のブロック図である。図 1 では 3 つの走査

線駆動回路  $D R V_1 \sim D R V_3$  が従属接続した構成を示したが、ここではそれらのうちの1つを代表的に示す。

#### 【0030】

走査線駆動回路  $D R V$  は、複数 ( $m$  個) の単位レジスタ  $S R_i$  ( $i = 1, 2, \dots, m$ ) が従属接続して成るシフトレジスタである。但し、各単位レジスタ  $S R_i$  は、その入力段に信号制御回路  $S C_i$  を有している。また走査線駆動回路  $D R V$  には、信号制御回路  $S C_i$  の制御回路としての演算回路 20 が設けられている。各単位レジスタ  $S R_i$  に設けられた信号制御回路  $S C_i$  は、演算回路 20 が出力する演算結果  $O U T_c$  に基づいて、単位レジスタ  $S R_i$  に出力信号  $O U T V_i$  信号を出力させるか否かを制御する。

#### 【0031】

単位レジスタ  $S R_i$  の出力信号  $O U T V_i$  は、走査線の駆動に用いられる。図示は省略するが、各単位レジスタ  $S R_i$  の出力端子  $O U T$  には、出力信号  $O U T V_i$  を、走査線を駆動可能な電圧レベルにする電圧変換回路 (レベルシフタ) が設けられる。また、単位レジスタ  $S R_i$  は、タイミングコントローラ 11 から入力されるアウトプットイネーブル信号により、出力信号  $O U T V_i$  の出力の可否を制御できるように構成されている。

10

#### 【0032】

各信号制御回路  $S C_i$  には、前段の出力信号  $O U T V_{i-1}$  と、次段の出力信号  $O U T V_{i+1}$  と、順方向垂直スタート信号  $S T V U$  および逆方向垂直スタート信号  $S T V D$  と、走査方向を制御するための走査方向制御信号  $U D$  と、後述する再スタート信号  $S T V M$  とが入力される (再スタート信号  $S T V M$  は実施の形態 3 で使用する)。

20

#### 【0033】

なお、走査線駆動回路  $D R V$  が 1 つの場合には、最前段の単位レジスタ  $S R_1$  に設けられる信号制御回路  $S C_1$  には、前段の出力信号  $O U T V_{i-1}$  は入力されないが、前段に他の走査線駆動回路  $D R V$  が従属接続される場合には、代わりに前段の走査線駆動回路  $D R V$  からの信号が入力される。同様に、走査線駆動回路  $D R V$  が 1 つの場合には、最後段の単位レジスタ  $S R_m$  に設けられる信号制御回路  $S C_m$  には、次段の出力信号  $O U T V_{i+1}$  は入力されないが、後段に他の走査線駆動回路  $D R V$  が従属接続される場合には、次段の出力信号  $O U T V_{i+1}$  として、次段の走査線駆動回路  $D R V$  からの信号が入力される。

30

#### 【0034】

各信号制御回路  $S C_i$  は、演算回路 20 が出力する演算結果  $O U T C$  が入力されるデコーダを有しており、その演算結果  $O U T C$  に応じて動作モードが切り替わる。信号制御回路  $S C_i$  の動作モードは、図 3 に示す 4 つがある。

#### 【0035】

第 1 の動作モードでは、信号制御回路  $S C_i$  は、順方向垂直スタート信号  $S T V U$  および逆方向垂直スタート信号  $S T V D$  のみを受け付け、それを単位レジスタ  $S R_i$  の入力端子  $I N$  に入力する。

40

#### 【0036】

第 2 の動作モードでは、信号制御回路  $S C_i$  は、再スタート信号  $S T V M$  のみを受け付け、それを単位レジスタ  $S R_i$  の入力端子  $I N$  に入力する (第 2 の動作モードは実施の形態 3 で用いられる)。

#### 【0037】

第 3 の動作モードでは、信号制御回路  $S C_i$  は、全ての信号を無視し、単位レジスタ  $S R_i$  の入力端子  $I N$  に何も入力しない。

#### 【0038】

第 4 の動作モードでは、信号制御回路  $S C_i$  は、前段の出力信号  $O U T V_{i-1}$  および次段の出力信号  $O U T V_{i+1}$  を受け付け、そのいずれかを単位レジスタ  $S R_i$  の入力端子  $I N$  に入力する。

#### 【0039】

第 4 の動作モードにおいて、信号制御回路  $S C_i$  が、前段の出力信号  $O U T V_{i-1}$  と

50

次段の出力信号 OUTV<sub>i+1</sub> のどちらを単位レジスタ SR<sub>i</sub> の入力端子 IN に入力するかは、走査方向制御信号 UD によって切り替わる。単位レジスタ SR<sub>i</sub> の入力端子 IN に前段の出力信号 OUTV<sub>i-1</sub> が入力される場合は順方向走査が行われ、次段の出力信号 OUTV<sub>i+1</sub> が入力される場合は逆方向走査が行われる。

#### 【0040】

つまり、走査方向制御信号 UD は、走査方向を切り替えるための信号として機能する。本実施の形態では、走査方向制御信号 UD が L (Low) レベルのときは、単位レジスタ SR<sub>i</sub> の入力端子 IN に前段の出力信号 OUTV<sub>i-1</sub> が入力されて、順方向走査が行われるものとする。逆に、走査方向制御信号 UD が H (High) レベルのときは、単位レジスタ SR<sub>i</sub> の入力端子 IN に次段の出力信号 OUTV<sub>i+1</sub> が入力されて、逆方向走査が行われるものとする。図 1 では省略したが、走査方向制御信号 UD は、タイミングコントローラ 11 から出力される。

10

#### 【0041】

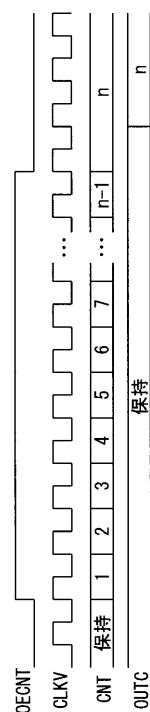

図 4 は、演算回路 20 の構成を示すブロック図である。演算回路 20 は、カウンタ 21 と演算部 22 とから構成される。カウンタ 21 には、走査線駆動回路 DRV に出力させる信号（出力信号 OUTV<sub>i</sub>）の数を指定するための出力数制御信号 OECNT（第 1 の制御信号）が入力される。本実施の形態において、出力数制御信号 OECNT は、走査線駆動回路 DRV に出力させる信号数に応じたパルス幅を有するパルス信号である。カウンタ 21 は、出力数制御信号 OECNT のパルス幅を、垂直クロック CLKV を用いてカウントする。

20

#### 【0042】

例えば、走査線駆動回路 DRV に n 個の信号を出力させる場合、出力数制御信号 OECNT のパルス幅は、垂直クロック CLKV の n 周期分の長さに設定される。本実施の形態では、出力数制御信号 OECNT のパルス幅（走査線駆動回路 DRV に出力させる信号数）は、タイミングコントローラ 11 に予め記憶されているものとする。

#### 【0043】

演算部 22 は、カウンタ 21 が出力数制御信号 OECNT のパルス幅をカウントした結果であるカウント数 CNT に対し、所定の演算処理を行い、その演算結果 OUTC（第 2 の制御信号）を各信号制御回路 SC<sub>i</sub> へ出力する。各信号制御回路 SC<sub>i</sub> は、演算結果 OUTC の値に基づいて、単位レジスタ SR<sub>1</sub> ~ SR<sub>m</sub> のうちのどれが信号を出力するかを特定し、それに応じて動作モードが切り替わる。

30

#### 【0044】

本実施の形態では、演算部 22 が、カウント数 CNT と同じ値の演算結果 OUTC を出力するものとする。図 5 は、この場合の演算回路 20 の動作を示す図である。カウンタ 21 は、出力数制御信号 OECNT が H レベルとなる期間に、垂直クロック CLKV の立ち上がり（L レベルから H レベルへの遷移）をカウントすることにより、出力数制御信号 OECNT のパルス幅をカウントする。演算部 22 は、出力数制御信号 OECNT が立ち下がったとき（H レベルから L レベルへ遷移したとき）のカウント数 CNT を取得して、それを演算結果 OUTC として出力する。

40

#### 【0045】

なお、演算部 22 は、出力数制御信号 OECNT の立ち下がりが検出されるまでは、前回の演算結果 OUTC の値を保持する。また、カウント数 CNT が 0 の場合、すなわち出力数制御信号 OECNT が入力されない場合は、演算結果 OUTC の初期設定値として、走査線駆動回路 DRV が出力できる信号数の最大値（出力端子数）を出力するものとする。図 2 の例では、演算結果 OUTC の初期設定値は m となる。

#### 【0046】

ここで、実施の形態 1 における、演算回路 20 が出力する演算結果 OUTC と信号制御回路 SC<sub>i</sub> の動作モードとの関係を説明する。

#### 【0047】

順方向走査時において、演算結果 OUTC の値が n の場合は、単位レジスタ SR<sub>1</sub> ~ S

50

$R_m$  にそれぞれ設けられた信号制御回路  $SC_1 \sim SC_m$  のうち、第 1 段目の信号制御回路  $SC_1$  が第 1 動作モードとなり、第 2 段目から第  $n$  段目までの信号制御回路  $SC_2 \sim SC_n$  は第 4 動作モードとなり、信号制御回路  $SC_n$  よりも後段の信号制御回路  $SC_{n+1} \sim SC_m$  は第 3 動作モードとなる。

#### 【0048】

また逆方向走査時において、演算結果 OUTC の値が  $n$  の場合は、第  $n$  段目の信号制御回路  $SC_n$  が第 1 動作モードとなり、第 1 段目から第  $n-1$  段目までの信号制御回路  $SC_1 \sim SC_{n-1}$  は第 4 動作モードとなり、信号制御回路  $SC_n$  よりも後段の信号制御回路  $SC_{n+1} \sim SC_m$  は第 3 動作モードとなる。

#### 【0049】

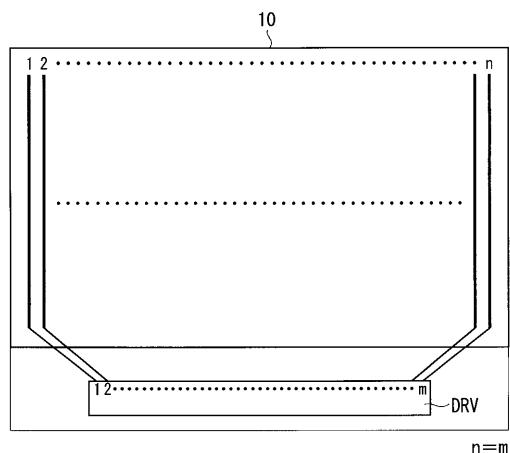

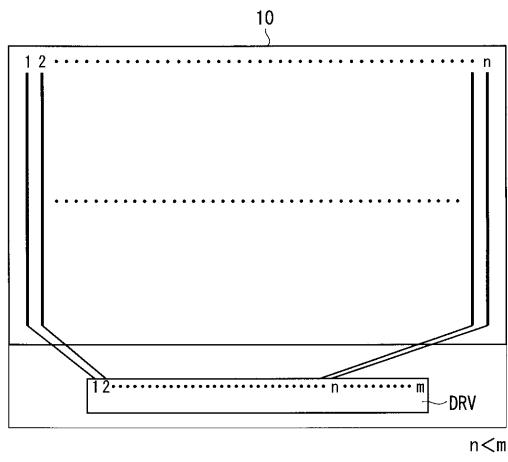

図 6 は、実施の形態 1 に係る走査線駆動回路 DRV と液晶パネル 10 との接続状態の一例を示す図である。図 1 においては、3 つの走査線駆動回路  $DRV_1 \sim DRV_3$  が従属接続して用いられる例を示したが、ここでは説明の簡単のため、1 つの走査線駆動回路 DRV が液晶パネル 10 の  $n$  本の走査線を駆動させる例を示す。微細加工技術が向上した近年では、1 つの走査線駆動回路が出力できる信号数は増えており、実際に 1 つの走査線駆動回路のみで液晶パネルを駆動させるケースもある。

#### 【0050】

図 6 は、液晶パネル 10 の走査線数  $n$  が、走査線駆動回路 DRV の出力端子数  $m$  と等しい場合を示している ( $n = m$ )。走査線駆動回路 DRV の出力端子を余すことなく液晶パネル 10 の走査線へ全端子を接続でき、最も効率がよい。

10

20

#### 【0051】

この場合、走査線駆動回路 DRV は全ての出力端子を使って  $m$  個の信号を出力する必要がある。よって、出力数制御信号 OECNT のパルス幅は、垂直クロック CLKV の  $m$  周期分の長さに設定され、演算回路 20 が出力する演算結果 OUTC の値は  $m$  となる。もし  $k$  は、出力数制御信号 OECNT を演算回路 20 に入力せずに、演算結果 OUTC として初期設定値の  $m$  を出力してもよい。つまり図 6 のケースでは、出力数制御信号 OECNT の出力機能を有しないタイミングコントローラ 11 を用いることもできる。

#### 【0052】

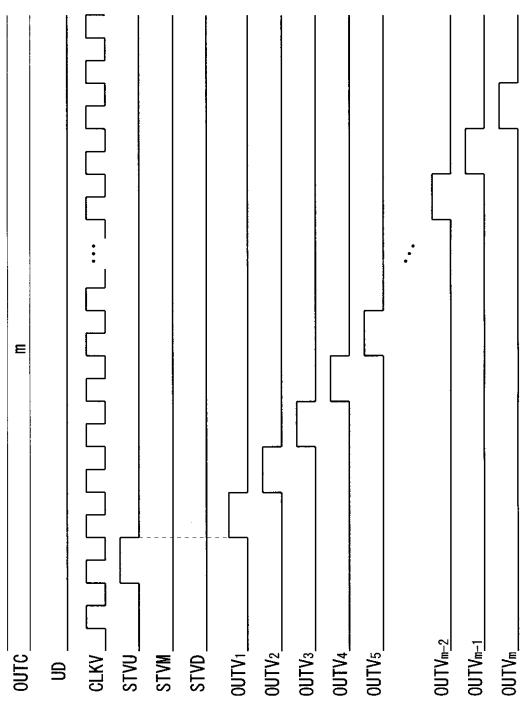

図 7 は、図 6 の構成における走査線駆動回路 DRV の動作を示すタイミング図であり、順方向走査が行われる場合（走査方向制御信号 UD が L レベルの場合）を示している。ここでは演算結果 OUTC の値が  $m$  であるので、信号制御回路  $SC_1$  が第 1 動作モードとなり、他の信号制御回路  $SC_2 \sim SC_m$  は第 4 動作モードとなる。

30

#### 【0053】

この場合、順方向垂直スタート信号 STVU が H レベルになるのに応じて、出力信号 OUTV<sub>1</sub>, OUTV<sub>2</sub>, …, OUTV<sub>m</sub> が、この順番で、垂直クロック CLKV に同期して H レベルになる。これにより、液晶パネル 10 の  $n$  本の走査線が順番にアクティブ状態にされる。

#### 【0054】

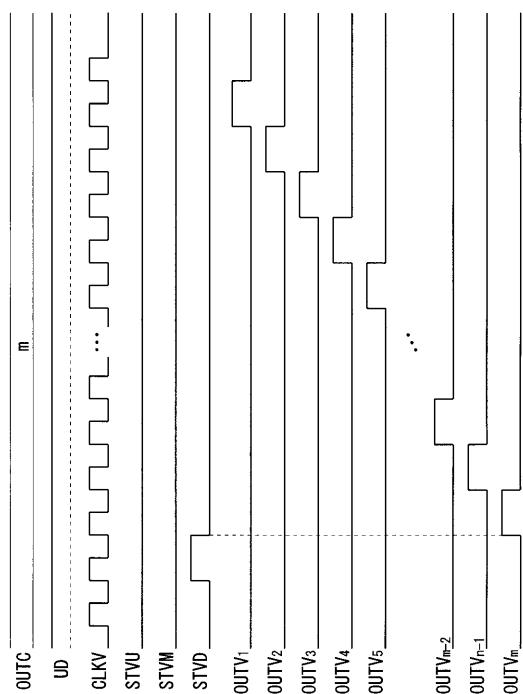

また図 8 は、図 6 の構成における走査線駆動回路 DRV の動作を示すタイミング図であり、逆方向走査が行われる場合（走査方向制御信号 UD が H レベルの場合）を示している。ここでは演算結果 OUTC の値が  $m$  であるので、信号制御回路  $SC_m$  が第 1 動作モードとなり、他の信号制御回路  $SC_1 \sim SC_{m-1}$  は第 4 動作モードとなる。

40

#### 【0055】

この場合、逆方向垂直スタート信号 STVD が H レベルになるのに応じて、出力信号 OUTV<sub>m</sub>, OUTV<sub>m-1</sub>, …, OUTV<sub>1</sub> が、この順番で、垂直クロック CLKV に同期して H レベルになる。これにより、液晶パネル 10 の  $n$  本の走査線が、順方向走査時は逆の順番でアクティブ状態にされる。

#### 【0056】

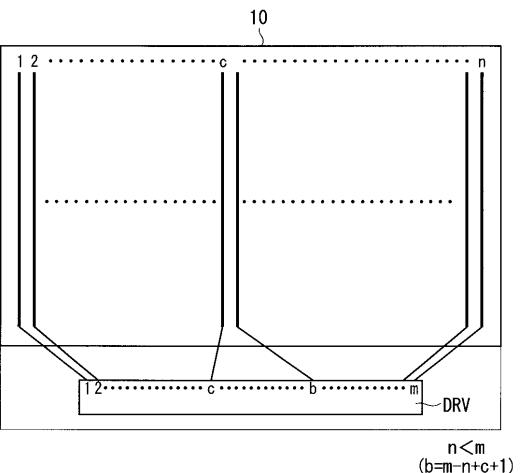

図 9 は、実施の形態 1 に係る走査線駆動回路 DRV と液晶パネル 10 との接続状態の他の一例を示す図であり、液晶パネル 10 の走査線数  $n$  が、走査線駆動回路 DRV の出力端

50

子数  $m$  よりも少ない場合を示している ( $n < m$ )。同図のように、 $n$  本の走査線は、走査線駆動回路  $D R V$  の 1 ~  $n$  番目の出力端子に接続される。

#### 【0057】

この場合、走査線駆動回路  $D R V$  が出力する信号の数を  $n$  個に減らす必要がある。具体的には、出力信号  $O U T V_1 \sim O U T V_n$  を出力させ、出力信号  $O U T V_{n+1} \sim O U T V_m$  の出力を停止させる。よって、出力数制御信号  $O E C N T$  のパルス幅は、垂直クロック  $C L K V$  の  $n$  周期分の長さに設定され、演算回路 20 が出力する演算結果  $O U T C$  の値は  $n$  となる。

#### 【0058】

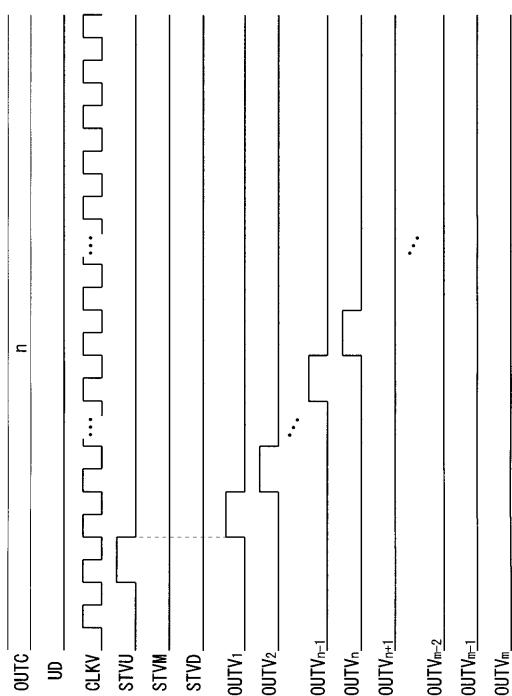

図 10 は、図 9 の構成における走査線駆動回路  $D R V$  の動作を示すタイミング図であり、順方向走査が行われる場合を示している。ここでは演算結果  $O U T C$  の値が  $n$  であるので、信号制御回路  $S C_1$  が第 1 動作モードとなり、信号制御回路  $S C_2 \sim S C_n$  が第 4 動作モードとなる。また、信号制御回路  $S C_n$  よりも後段の信号制御回路  $S C_{n+1} \sim S C_m$  は第 3 動作モードとなる。

10

#### 【0059】

この場合、順方向垂直スタート信号  $S T V U$  が H レベルになるのに応じて、出力信号  $O U T V_1, O U T V_2, \dots, O U T V_n$  が、この順番で、垂直クロック  $C L K V$  に同期して H レベルになる。これにより、液晶パネル 10 の  $n$  本の走査線が順番にアクティブ状態にされる。なお、出力信号  $O U T V_{n+1} \sim O U T V_m$  は L レベルに維持される。

20

#### 【0060】

タイミング図は省略するが、図 10 の構成において、逆方向走査時には、信号制御回路  $S C_n$  が第 1 動作モードとなり、信号制御回路  $S C_1 \sim S C_{n-1}$  が第 4 動作モードとなり、信号制御回路  $S C_{n+1} \sim S C_m$  が第 3 動作モードとなる。よって、逆方向垂直スタート信号  $S T V D$  が H レベルになるのに応じて、出力信号  $O U T V_n, O U T V_{n-1}, \dots, O U T V_1$  が、この順番で、垂直クロック  $C L K V$  に同期して H レベルになる。

20

#### 【0061】

このように本実施の形態によれば、走査線駆動回路  $D R V$  が出力する信号の数を、出力数制御信号  $O E C N T$  を用いて任意に設定できるので、特殊な解像度を含めた様々な解像度に対応することが可能である。解像度によって使用する駆動回路を変更する必要がなくなり、部品の共有化によるコスト低減が期待できる。また、容易に走査方向を切り替えることも可能であるので、画像処理部の回路を複雑にすることなく、上下反転表示が可能になる。

30

#### 【0062】

また、走査線駆動回路  $D R V$  に出力させる信号の数を、出力数制御信号  $O E C N T$  のパルス幅を用いて指定するようにしたことにより、その信号線を 1 本にすることが可能である。よって、出力数制御信号  $O E C N T$  のための配線エリアを最小限に抑えることができる。また、配線の自由度が上がる所以、駆動回路と液晶パネルとの結線がしやすくなると共に、表示装置のデザイン性がアップにも寄与できる。

30

#### 【0063】

< 実施の形態 2 >

40

実施の形態 1 では、走査線駆動回路  $D R V$  の出力端子数  $m$  が液晶パネル 10 の走査線数  $n$  より少ないと、走査線駆動回路  $D R V$  の第 1 番目の出力端子から数えて  $n$  個の出力端子 (つまり第 1 ~  $n$  番目の出力端子) を用いて走査線を駆動したが (図 9、図 10)、走査線駆動回路  $D R V$  のどの端子を使用するかは任意でよい。使用する出力端子は、演算部 22 による演算と信号制御回路  $S C_i$  のモード設定により決めることがある。

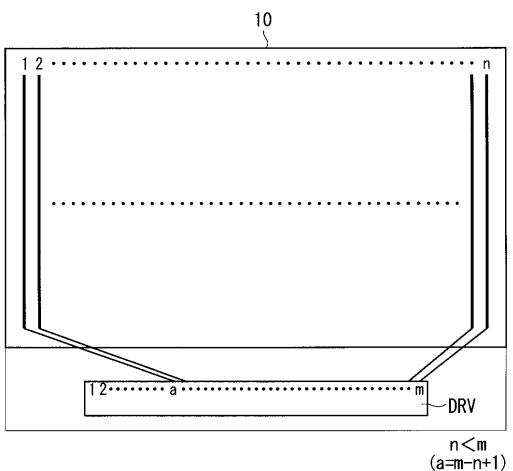

#### 【0064】

実施の形態 2 では、図 11 に示すように、第  $m$  番目の出力端子から逆に数えて  $n$  個の出力端子を用いる例を示す。図 11 では、第  $a$  番目 ~ 第  $m$  番目の出力端子が使用されているが、 $a = m - n + 1$  と定めれば、 $n$  個の出力端子が使用されることとなる。

#### 【0065】

50

本実施の形態では、演算回路 20 の演算部 22 が、 $a = m - n + 1$  の演算を行い、演算結果 OUTC として a の値を出力する。各信号制御回路 SC<sub>i</sub> の動作モードは、この a の値に基づいて決定する。

#### 【0066】

走査線駆動回路DRVが順方向走査を行う場合には、第 a 段目の信号制御回路 SC<sub>a</sub> が第 1 動作モードとなり、第 a + 1 段目から第 m 段目までの信号制御回路 SC<sub>a+1</sub> ~ SC<sub>m</sub> は第 4 動作モードとなり、信号制御回路 SC<sub>a</sub> よりも前段の信号制御回路 SC<sub>1</sub> ~ SC<sub>a-1</sub> は第 3 動作モードとなる。

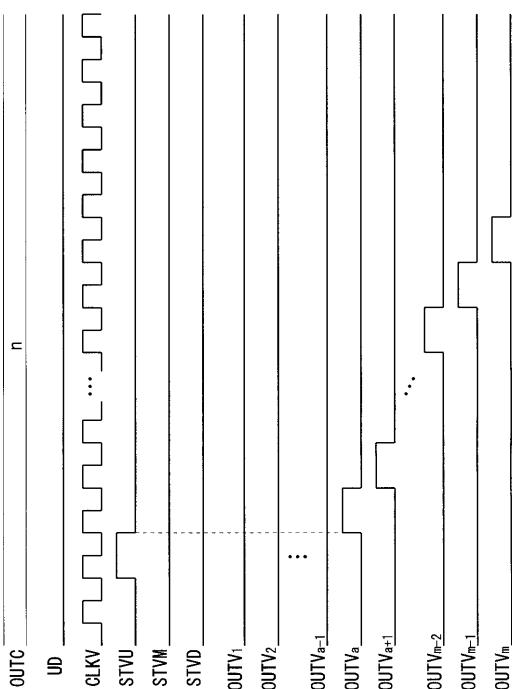

#### 【0067】

図 12 は、この場合の走査線駆動回路 DRV の動作を示すタイミング図である。この場合、順方向垂直スタート信号 STVU が H レベルになるのに応じて、出力信号 OUTVa, OUTV<sub>a+1</sub>, …, OUTVm が、この順番で、垂直クロック CLKV に同期して H レベルになる。これにより、液晶パネル 10 の n 本の走査線が順番にアクティブ状態にされる。なお、出力信号 OUTV<sub>1</sub> ~ OUTV<sub>a-1</sub> は L レベルに維持される。

10

#### 【0068】

また、走査線駆動回路 DRV が逆方向走査を行う場合には、第 m 段目の信号制御回路 SC<sub>m</sub> が第 1 動作モードとなり、第 a 段目から第 m - 1 段目までの信号制御回路 SC<sub>a</sub> ~ SC<sub>m-1</sub> は第 4 動作モードとなり、信号制御回路 SC<sub>a</sub> よりも前段の信号制御回路 SC<sub>1</sub> ~ SC<sub>a-1</sub> は第 3 動作モードとなる。

20

#### 【0069】

タイミング図は省略するが、この場合には、逆方向垂直スタート信号 STVD が H レベルになるのに応じて、出力信号 OUTVm, OUTVm-1, …, OUTVa が、この順番で、垂直クロック CLKV に同期して H レベルになる。

#### 【0070】

本実施の形態においても、実施の形態 1 と同様の効果が得られる。また、本発明では、本実施の形態や次の実施の形態 3 のように、演算部 22 の演算および信号制御回路 SC<sub>i</sub> の動作モードの設定により、使用する出力端子の位置を自由に変更できる。よって、配線の自由度が向上し、走査線駆動回路 DRV と液晶パネル 10 との結線がしやすくなるという利点も得られる。

30

#### 【0071】

##### <実施の形態 3>

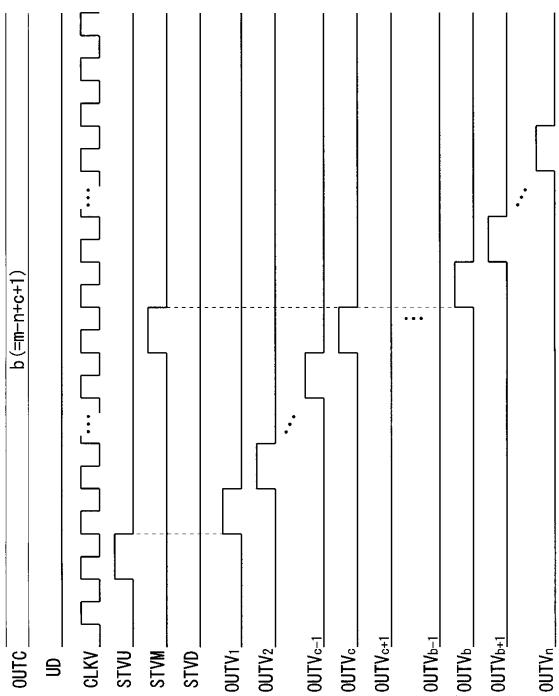

実施の形態 3 では、図 13 に示すように、走査線駆動回路 DRV の中央部の出力端子を不使用にして、両端の n 個の出力端子を用いる例を示す。図 13 では、第 1 番目 ~ 第 c 番目の出力端子と、第 b 番目 ~ 第 m 番目の出力端子が使用されている。c を固定値とすると、 $b = m - n + c + 1$  と定めれば、n 個の出力端子が使用されることとなる。

#### 【0072】

本実施の形態では、演算回路 20 の演算部 22 が、 $b = m - n + c + 1$  の演算を行い、演算結果 OUTC として b の値を出力する。

#### 【0073】

走査線駆動回路 DRV が順方向走査を行う場合には、第 1 段目の信号制御回路 SC<sub>1</sub> が第 1 動作モードとなり、第 2 段目から第 c 段目までの信号制御回路 SC<sub>2</sub> ~ SC<sub>c</sub> は第 4 動作モードとなる。また、第 c + 1 段目から第 b - 1 段目までの信号制御回路 SC<sub>c+1</sub> ~ SC<sub>b-1</sub> は第 3 動作モードとなる。さらに、第 b 段目の信号制御回路 SC<sub>b</sub> は第 2 動作モードとなり、第 b + 1 段目から第 m 段目までの信号制御回路 SC<sub>b+1</sub> ~ SC<sub>m</sub> は第 4 動作モードとなる。

40

#### 【0074】

図 14 は、この場合の走査線駆動回路 DRV の動作を示すタイミング図である。この場合、まず、順方向垂直スタート信号 STVU が H レベルになるのに応じて、出力信号 OUTV<sub>1</sub>, OUTV<sub>2</sub>, …, OUTV<sub>c</sub> が、この順番で、垂直クロック CLKV に同期して H レベルになる。その後、タイミングコントローラ 11 は、再スタート信号 STVM を、

50

出力信号 OUTV<sub>c</sub> が H レベルになるのと同じタイミングで H レベルにする。この再スタート信号 STVM は、第 2 動作モードの信号制御回路 SC<sub>b</sub> が接続した単位レジスタ SR<sub>b</sub> の入力端子 IN に入力されるので、出力信号 OUTV<sub>b</sub>, OUTV<sub>b+1</sub>, …, OUTV<sub>m</sub> が、出力信号 OUTV<sub>c</sub> に続いて順次活性化する。これにより、液晶パネル 10 の n 本の走査線が順番にアクティブ状態にされる。なお、出力信号 OUTV<sub>c+1</sub> ~ OUTV<sub>b-1</sub> は L レベルに維持される。

#### 【 0075 】

走査線駆動回路 DRV が逆方向走査を行う場合には、第 m 段目の信号制御回路 SC<sub>m</sub> が第 1 動作モードとなり、第 b 段目から第 m - 1 段目までの信号制御回路 SC<sub>b</sub> ~ SC<sub>m-1</sub> は第 4 動作モードとなる。また、第 c + 1 段目から第 b - 1 段目までの信号制御回路 SC<sub>c+1</sub> ~ SC<sub>b-1</sub> は第 3 動作モードとなる。さらに、第 c 段目の信号制御回路 SC<sub>c</sub> は第 2 動作モードとなり、第 1 段目から第 c - 1 段目までの信号制御回路 SC<sub>1</sub> ~ SC<sub>c-1</sub> は第 4 動作モードとなる。

10

#### 【 0076 】

タイミング図は省略するが、この場合には、逆方向垂直スタート信号 STVD が H レベルになるのに応じて、出力信号 OUTV<sub>m</sub>, OUTV<sub>m-1</sub>, …, OUTV<sub>b</sub> が、この順番で、垂直クロック CLKV に同期して H レベルになる。そしてタイミングコントローラ 11 は、再スタート信号 STVM を、出力信号 OUTV<sub>b</sub> と同じタイミングで H レベルにする。この再スタート信号 STVM は、第 2 動作モードの信号制御回路 SC<sub>c</sub> が接続した単位レジスタ SR<sub>c</sub> の入力端子 IN に入力されるので、出力信号 OUTV<sub>c</sub>, OUTV<sub>c-1</sub>, …, OUTV<sub>1</sub> が、出力信号 OUTV<sub>b</sub> に続いて順次活性化する。これにより、液晶パネル 10 の n 本の走査線が、順方向走査時とは逆の順番にアクティブ状態にされる。なお、出力信号 OUTV<sub>c+1</sub> ~ OUTV<sub>b-1</sub> は L レベルに維持される。

20

#### 【 0077 】

本実施の形態においても、実施の形態 1 と同様の効果が得られる。また、走査線駆動回路 DRV の両端の出力端子が必ず使用されるため、図 1 のように走査線駆動回路 DRV を複数個従属接続させて使用することが容易になるというメリットもある。

#### 【 0078 】

##### < 実施の形態 4 >

実施の形態 1 では、出力数制御信号 OECNT のパルス幅（走査線駆動回路 DRV に出力させる信号の数）は、タイミングコントローラ 11 が予め記憶しているものとしたが、出力数制御信号 OECNT は他の制御信号に基づいて生成させることができる場合がある。

30

#### 【 0079 】

例えば、タイミングコントローラ 11 の種類によっては、スタート信号（STVU または STVD）を出力した後、各フレームの終わりのタイミング（最終行の走査線がアクティブ状態にされるのと同じタイミング）で、走査線駆動回路 DRV の動作を一時的に停止させるエンド信号を出力するものがある。このスタート信号の立ち上がりからエンド信号の立ち上がりまでの期間は、垂直クロック CLKV の n 周期分の長さ（n は走査線数）に相当し、実施の形態 1 で用いた出力数制御信号 OECNT のパルス幅と同等である。よって、出力数制御信号 OECNT は、スタート信号の立ち上がりに応じて H レベルになり、エンド信号の立ち上がりに応じて L レベルになるパルス信号として、生成することができる。

40

#### 【 0080 】

この構成によれば、タイミングコントローラ 11 に、出力数制御信号 OECNT のパルス幅の情報を予め記憶されることなく、液晶パネル 10 の解像度に合った出力数制御信号 OECNT を生成できる。

#### 【 0081 】

##### < 変更例 >

実施の形態 1 ~ 4 では、本発明を走査線駆動回路 DRV のシフトレジスタに適用した例

50

を示したが、先に説明したように、画像信号線駆動回路 D R H も画像信号線の数に対応した数の信号を出力するシフトレジスタを備えている。本発明は、画像信号線駆動回路 D R H のシフトレジスタに適用することもできる。

#### 【 0 0 8 2 】

また、上の説明では出力数制御信号 O E C N T のパルス幅は、走査線駆動回路 D R V に出力させる信号の数、つまり使用する出力端子の数 ( n ) に対応する長さとしたが、不使用とする出力端子の数 ( m - n ) に対応する長さとしてもよい。その場合でも、演算部 2 2 が演算により、使用する出力端子の数を求めることができる。

#### 【 0 0 8 3 】

効率の観点から、不使用の出力端子は少なくするのが通常であるため、出力数制御信号 O E C N T のパルス幅を不使用の出力端子の数に対応させると、そのパルス幅を短くできる。これにより、走査線駆動回路 D R V で使用する出力端子の数を演算回路 2 0 が判断するのに要する時間が短縮される。

#### 【 0 0 8 4 】

さらに、上の説明では、カウンタ 2 1 が垂直クロック C L K V の立ち上がりをカウントする構成としたが、もちろん立ち下がりをカウントするように構成してもよい。また出力数制御信号 O E C N T のパルス幅は、その H レベル期間としたが、 L レベル期間をパルス幅として規定してもよい。

#### 【 0 0 8 5 】

また、上述の実施の形態 1 乃至 4 においては、液晶表示装置を例示して本発明を説明したが、例えば、有機 E L や L E D 素子を表示デバイスとした表示装置の画像信号線を駆動する駆動回路においても、同様に本発明を適用することができる。

#### 【 0 0 8 6 】

なお、本発明は、その発明の範囲内において、各実施の形態を自由に組み合わせたり、各実施の形態を適宜、変形、省略することが可能である。

#### 【 符号の説明 】

#### 【 0 0 8 7 】

D R H 画像信号線駆動回路、 D R V 走査線駆動回路、 1 0 液晶パネル、 1 1 タイミングコントローラ、 2 0 演算回路、 S R 単位レジスタ、 S C 信号制御回路、 2 1 カウンタ、 2 2 演算部。

10

20

30

【図1】

【図2】

【図3】

|         |                      |

|---------|----------------------|

| 第1動作モード | STVUおよびSTVDのみを受け付ける  |

| 第2動作モード | STVMのみを受け付ける         |

| 第3動作モード | 全ての入力を無視する           |

| 第4動作モード | 前段または後段の出力信号のみを受け付ける |

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図 14】

---

フロントページの続き

| (51) Int.Cl. | F I     | テーマコード(参考)   |

|--------------|---------|--------------|

|              | G 0 9 G | 3/20 6 2 3 D |

|              | G 0 9 G | 3/20 6 2 3 B |

|              | G 0 9 G | 3/20 6 2 2 C |

|              | G 0 9 G | 3/20 6 2 3 C |

|              | G 0 9 G | 3/20 6 2 2 B |

|              | G 0 2 F | 1/133 5 0 5  |