## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2006-310661 (P2006-310661A)

(43) 公開日 平成18年11月9日 (2006.11.9)

| (51) Int.C1. | F I                          |           |                     | テーマコード(参考)     |       |      |      |       |  |

|--------------|------------------------------|-----------|---------------------|----------------|-------|------|------|-------|--|

| HO1L 27/12   | <b>(2006.01)</b> HO1         | L = 27/12 | $\mathbf{E}$        |                | 5 F ( | 032  |      |       |  |

| HO1L 21/02   | <b>(2006.01)</b> HO 1        | L = 27/12 | В                   |                |       |      |      |       |  |

| HO1L 21/76   | <b>(2006.01)</b> HO 1        | L 27/12   | $\mathbf{F}$        |                |       |      |      |       |  |

| HO1L 21/762  | <b>(2006.01)</b> HO 1        | L = 21/76 | D                   |                |       |      |      |       |  |

|              | HO1                          | L = 21/76 | R                   |                |       |      |      |       |  |

|              |                              | 審査請求<br>  | 未請求                 | 請求項            | の数 5  | OL   | 全    | 14 頁) |  |

| (21) 出願番号    | 特願2005-133623 (P2005-133623) | (71) 出願人  | 0000030             | )78            |       |      |      |       |  |

| (22) 出願日     | 平成17年4月28日 (2005.4.28)       |           | 株式会                 | 株式会社東芝         |       |      |      |       |  |

|              |                              |           | 東京都                 | 東京都港区芝浦一丁目1番1号 |       |      |      |       |  |

|              |                              | (74)代理人   | 1001099             | 100109900      |       |      |      |       |  |

|              |                              |           | 弁理士                 | 堀口             | 浩     |      |      |       |  |

|              |                              | (72) 発明者  | 浜本 毅司               |                |       |      |      |       |  |

|              |                              |           | 神奈川県横浜市磯子区新杉田町8番地 株 |                |       |      |      |       |  |

|              |                              |           | 式会社東芝横浜事業所内         |                |       |      |      |       |  |

|              |                              | Fターム (参   | 多考) 5F03            | 32 AA03        | AA06  | AA07 | AA09 | BA03  |  |

|              |                              |           |                     | BA06           | CA09  | CA17 | DA12 | DA23  |  |

|              |                              |           |                     | DA24           | DA25  | DA43 | DA54 | DA55  |  |

|              |                              |           |                     | DA60           | DA71  | DA74 | DA78 |       |  |

|              |                              |           |                     |                |       |      |      |       |  |

## (54) 【発明の名称】半導体基板および製造方法

## (57)【要約】

【課題】埋め込み酸化膜の厚い部分と薄い部分における 基板表面の段差を減少させる。

【解決手段】薄い酸化膜20の表面部分に第一のマスク40を形成した状態で高温酸化熱

処理を加え、薄い酸化膜20のない領域に厚い酸化膜を 形成した状態で第一のマスク40

を除去し、再度酸素雰囲気中で第二の熱処理を行う。この第二の熱処理により薄い酸化膜

20の表面部分にも第二の熱酸化膜が形成され、このとき第一の熱酸化膜及び第二の熱酸

化膜の基板との界面が等しく条件を選択することによって、第一の熱酸化膜と第二の熱酸

化膜を除去した後には表面には段差のない平坦な基板を 形成することが可能となる。

【選択図】図1

10

20

30

40

50

#### 【特許請求の範囲】

## 【請求項1】

基板と、

前記基板の内部に第一の埋め込み酸化膜を有する領域と、

前記基板の内部に前記第一の埋め込み酸化膜とは異なる膜厚を備える第二の埋め込み酸化膜を有する領域とを備え、

前記基板の表面が平坦であることを特徴とする半導体基板。

### 【請求項2】

前記第一の埋め込み酸化膜の膜厚が50nm以上200nm以下であり、

前記第二の埋め込み酸化膜の膜厚が10nm以上かつ前記第一の埋め込み酸化膜の膜厚未満であることを特徴とする請求項1記載の半導体基板。

#### 【請求項3】

前記第一の埋め込み酸化膜を有する領域と前記第二の埋め込み酸化膜を有する領域の表面の水平方向における高低差が100nm以下の平坦さであることを特徴とする請求項1記載の半導体基板。

#### 【請求項4】

5 0 n m 以下の埋め込み酸化膜層を備える基板と、

前記基板上にマスクを堆積する工程と、

前記マスクの一部を選択的に除去し、窓部を形成する工程と、

前記マスクの前記窓部を介して前記基板に酸化種となるイオンを注入する工程と、

酸化雰囲気中で第一の熱処理を行い、前記酸化種との反応を用いて前記基板中に部分的に酸化膜を形成し、前記基板の表面に第一の熱酸化膜を形成する工程と、

前記マスクを除去する工程と、

酸化雰囲気中で第二の熱処理を行い、前記基板の表面に第二の熱酸化膜を形成する工程と

前記基板の表面に形成された前記第一の熱酸化膜と前記第二の熱酸化膜を除去する工程とを備えることを特徴とする半導体基板の製造方法。

#### 【請求項5】

前記マスクが耐酸化特性を有することを特徴とする請求項4記載の半導体基板の製造方法

【発明の詳細な説明】

## 【技術分野】

#### [0001]

本発明は基板中に膜厚の異なる埋め込み酸化膜を有し、表面に段差がない半導体基板および製造方法に関する。

## 【背景技術】

### [00002]

従来、シリコンの基板内部に埋め込み酸化膜を有するSOI(Silicon On Insulator)基板は、素子動作の高速化、低消費電力化、ソフトエラー耐性の向 上など多くのメリットがあることが知られている。

## [ 0 0 0 3 ]

アナログ・ロジック・メモリ等の複数の素子を同一基板上に混載するシステムLSIでは、シリコン基板の一部をマスクで覆い、SIMOX(Separation by Implantation of Oxygen)を部分的行うことよってSOIを形成する技術(以下部分SOIと呼ぶ)が用いられている。この場合、ロジック回路等を形成する部分SOIの埋め込み酸化膜の膜厚は、約100から約200nm程度の膜厚が用いられてきた。また、DRAMを代表とするメモリは、部分SOIのない領域の基板に形成されてきた。

## [0004]

最近、FBC(Floating Body Cell)に代表されるようなキャパシ

タのないDRAMメモリセルとロジック回路等をSOI上に混載する方法などが検討されている。この場合、FBCはSOI基板中の埋め込み酸化膜厚が薄いほど信号強度が高くなり特性が向上する。このため、FBCを搭載する領域にはロジック回路等を形成する領域よりも薄い埋め込み酸化膜を形成する必要がでてきた。

## [0005]

しかし、従来の部分SIMOXを複数回行うことによって異なる埋め込み酸化膜を形成する方法には問題があった。原因は、高温アニール時に埋め込み酸化膜厚に比例して基板が体積膨張するため、厚い埋め込み酸化膜の領域と薄い埋め込み酸化膜の領域の境界付近の基板表面には段差すなわち水平方向の高低差が生じるためである。これにより、デバイス形成時のリソグラフィー工程や加工工程のマージンが劣化し、歩留まり低下が懸念される。

[0006]

部分SOIの場合にもSOIのある領域とない領域の境界部分で表面に段差ができるという同様の問題があり、これを解決するための手法がある。(例えば特許文献 1 参照。)

[0007]

しかし、膜厚の異なる埋め込み酸化膜を有するSOI基板の場合には、高温アニール時に基板の内部酸化によって薄い埋め込み酸化膜が酸化されるという問題があり、薄い埋め込み酸化膜の膜厚を制御することが困難になる。すなわち、膜厚の異なる埋め込み酸化膜を有するSOI基板の場合には、薄い埋め込み酸化膜の膜厚を制御しつつ、表面の段差をなくす手法が必要である。

【 特 許 文 献 1 】 特 開 2 0 0 4 - 3 0 4 5 5 5 号 公 報

【発明の開示】

【発明が解決しようとする課題】

[0008]

本発明は、基板中に異なる膜厚の埋め込み酸化膜を有し、表面に段差のない半導体基板および製造方法を提供する。

【課題を解決するための手段】

[0009]

本発明の一態様は、基板と、前記基板の内部に第一の埋め込み酸化膜を有する領域と、前記基板の内部に前記第一の埋め込み酸化膜とは異なる膜厚を備える第二の埋め込み酸化膜を有する領域とを備え、前記基板の表面が平坦であることを特徴とする。

[0010]

また、本発明の一態様は、50nm以下の埋め込み酸化膜層を備える基板と、前記基板上にマスクを堆積する工程と、前記マスクの一部を選択的に除去し、窓部を形成する工程と、前記マスクの前記窓部を介して前記基板に酸化種となるイオンを注入する工程と、酸化雰囲気中で第一の熱処理を行い、前記酸化種との反応を用いて前記基板中に部分的に酸化膜を形成し、前記基板の表面に第一の熱酸化膜を形成する工程と、前記マスクを除去する工程と、酸化雰囲気中で第二の熱処理を行い、前記基板の表面に第二の熱酸化膜を形成する工程と、前記基板の表面に形成された前記第一の熱酸化膜と前記第二の熱酸化膜を除去する工程とを備えることを特徴とする。

【発明の効果】

[0011]

本発明によれば、基板中に異なる膜厚の埋め込み酸化膜を備え、基板表面の水平方向の段差が100nm以下の平坦なSOI基板表面を提供することができる。

【発明を実施するための最良の形態】

[0012]

以下、図面を参照しながら本発明の実施の形態を説明する。

【実施例1】

[0013]

20

30

40

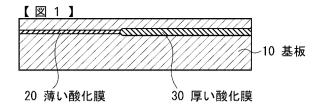

図1は、本発明の実施例1に係る半導体基板を示す断面図である。ただし、図面は模式的なものであり、厚みと平面寸法との関係、各層の厚みや比率等は現実のものとは異なることに留意すべきである。

### [0014]

基板10中には基板の一定の深さ(たとえば約50 n m)の領域に、たとえば膜厚が約10 n m程度の埋め込みの薄い酸化膜20を有する部分と、たとえば膜厚が約100 n m程度の埋め込みの厚い酸化膜30を有する部分がある。基板10としては、単結晶シリコンのほかに、多結晶シリコン、シリコンゲルマニウム(SiGe)、およびシリコンカーバイド(SiC)等のSiを含む材料が使用可能である。

#### [ 0 0 1 5 ]

このとき、薄い酸化膜 2 0 の領域には、たとえば F B C が形成可能であり、厚い酸化膜 3 0 の領域には M O S トランジスタで構成されるロジック回路等が形成可能である。薄い酸化膜 2 0 と厚い酸化膜 3 0 の膜厚は、用途によって最適化することができる。たとえば、4 5 n m 世代のロジック用としては、厚い酸化膜 3 0 の厚さは約 5 0 n m から約 2 0 0 n m 程度が望ましい。これは、約 5 0 n m 以下の厚さでは基板容量が無視できなくなることと、約 2 0 0 n m 以上の厚さではシリコン酸化膜の低い熱伝導率により動作中の放熱が劣化し、素子の動作特性を劣化するためである。

## [0016]

また、薄い酸化膜 2 0 の膜厚に F B C を形成する場合には約 1 0 n m 以上であることが望ましい。これは、例えば F B C では酸化膜はできるだけ薄いほうが信号強度が高くとれる一方で、熱酸化膜が約 1 0 n m 以下では上部単結晶シリコンが十分に絶縁されない可能性があるためである。

## [0017]

また、薄い酸化膜 2 0 、厚い酸化膜 3 0 ともに、基板表面からの深さにはとくに規定はなく、約 5 0 n m より深くても浅くてもよい。これは S O I 基板を形成後、基板表面を酸化した後に表面酸化膜を剥離し、埋め込み酸化膜上のシリコン単結晶を薄膜化することによって最適化することができる。この深さは、用途合わせて設定される最適値があり、たとえば 4 5 n m 世代のロジック用としては約 4 0 n m から約 1 0 0 n m 程度である。

## [0018]

また、薄い酸化膜 2 0 および厚い酸化膜 3 0 を有する基板 1 0 の表面には段差がなく平坦である。ここで段差がないは、薄い酸化膜 2 0 を埋め込んだ領域の基板表面及び厚い酸化膜 3 0 を埋め込んだ領域の基板の表面の水平方向にステップ状の段差や突起形状の段差がなく、表面凹凸の高低差によるリソグラフィー工程や加工工程でマージンが劣化しないことを意味する。このマージンはデザインルールが小さくなるにしたがって厳しくなる。たとえばデザインルールが 1 3 0 n m の世代では、表面の水平レベルの高低差が約 1 0 0 n m 以下であれば好ましく、デザインルールが 4 5 n m の世代では高低差は約 2 0 n m 以下であれば好ましい。

## [0019]

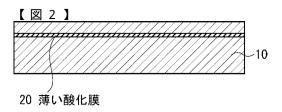

次に、実施例1に係る半導体基板の製造工程を図2から図4の工程断面図を用いて説明する。

## [0020]

まず、図2(a)に示すように、張り合わせ方式を用い、埋め込み酸化膜が基板全面に約10nm程度の厚さで形成されたSOI基板10を用いる。このSOI基板の製造方法には、例えば次のようなものがある。

#### [0021]

まず、シード基板上に陽極酸化によって多孔質シリコン層を形成し、その上に単結晶シリコンをエピタキシャル成長させる。次に、単結晶シリコンの表面を酸化し、この酸化膜をハンドル基板に張り合わせる。次に、張り合わせた基板の多孔質シリコン層の部分を水ジェットを用いて分離し、ハンドル基板に残る多孔質シリコン層をエッチングにより除去する。最後に水素を含む雰囲気中で熱処理を行うことにより、表面を平坦にする。

10

20

30

40

20

30

40

50

[0022]

このとき、薄い酸化膜 2 0 は基板 1 0 の表面から約 5 0 n m 程度の深さに形成されているが、この深さは 5 0 n m である必要はない。また、この基板 1 0 の表面と薄い酸化膜 2 0 は水平レベルがほぼ等しく形成されている。

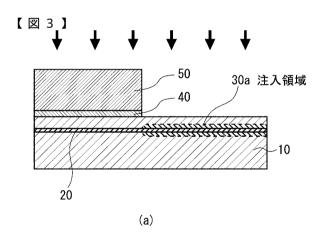

[ 0 0 2 3 ]

次に、基板10上に第一のマスク40と、その上に第二のマスク50を堆積する。第一のマスク40は、たとえば約150nm程度のシリコン窒化膜、第二のマスク50は、たとえば約1μm程度のシリコン酸化膜とする。このとき第一のマスクの厚さは、後の工程で酸素雰囲気中において熱処理を行う際にマスク下の基板部分が酸化されないために十分な厚さが必要であり、また第一のマスクと第二のマスクは、後の工程で酸化種をイオン注入する際に酸化種が基板まで到達することのない十分な厚さが必要である。

[0024]

次に、第二のマスク50上にレジストを塗布し、レジストをパターニングする。次に、レジストをマスクとして、RIE(Reactive Ion Etching)により第二のマスク50と第一のマスク40の一部を除去し、図2(b)に示すような領域70を形成する。図2(b)では領域70は基板10に達しているが、かならずしも基板10の表面が露出する必要はなく、第二のマスク50あるいは第一のマスク40の一部が残っていてもよい。

[0025]

次に、加工された第一のマスク40および第二のマスク50をマスクとして、酸化種をイオン注入により注入する。条件は、たとえば酸化種としてO+イオンを約150KeVから約200KeVのエネルギーで約4×1017cm-2から約6×1017cm-2程度のドーズ量で注入する。このとき、基板10中の領域70の領域には酸化種がイオン注入されるが、第一のマスク50および第二のマスク60により覆われた領域は、酸化種が第一のマスク50または第二のマスク60により、基板10には到達しない(図3(a)参照)。

[0026]

次に、第二のマスク 5 0 をフッ素あるいはフッ化アンモニウムなどによるウェットエッチング法、または H F V a p e r などのドライエッチング法を用いて除去する。

[0027]

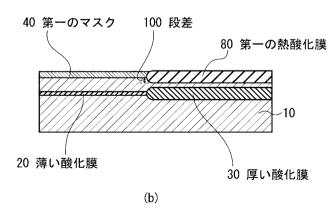

この後、酸素を含む雰囲気中で第一の熱処理をする。第一の熱処理の条件として、たとえば、まず約1%程度の酸素を含むアルゴンガス中で、約1300 から約1400 の温度で約4時間程度の熱処理を加え、その後同じ約1300 から約1400 で約100%程度の酸素ガス中において、約4時間程度の熱処理を加える。ここで、第一の熱処理は、注入された酸化種が基板10中のシリコンと反応して、酸化膜を形成する効果がある。第一の熱処理条件は、基板10の第一のマスクで覆われている領域には、熱酸化膜ががよいが形成されない条件を選択することが好ましい。このような条件を選択することが好ましい。このような条件を選択することが好ましい。このような条件を選択するので、第一の熱処理時における内部酸化によって薄い酸化膜20の膜厚が増加するのを抑制することが可能となり、薄い酸化膜20の膜厚制御を容易にする効果がある。このため、第一のマスクは耐酸化特性をもつ膜であることが望ましい。また第一のマスク材料として、多結晶シリコンのように、それ自身が酸化されることによって下地の基板10を酸化しないマスクを用いることもできる。

[0028]

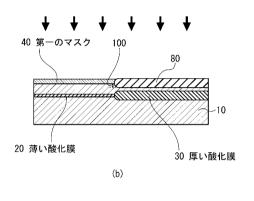

第一のマスクで覆われていない領域の表面には、この第一の熱処理により約800nm程度の第一の熱酸化膜80が形成される。また、基板10中では、イオン注入された酸素原子とシリコンとが反応し、約100nm程度の厚い酸化膜30を形成する。このとき、酸化膜は消費したシリコンに対して約2.2倍の体積をもつため、厚い酸化膜30が形成された領域では表面が膨張し押し上げられる。これにより、図3(b)に示すように、薄い酸化膜20の領域および厚い酸化膜30の領域の基板表面の水平方向には、約200nm程度の高低差を有する段差100が生じる。

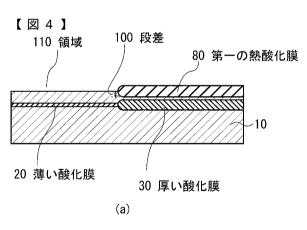

[0029]

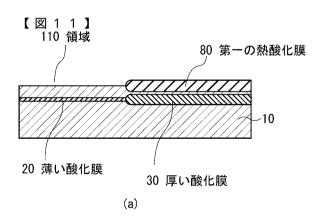

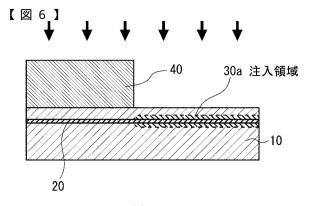

次に、第一のマスク40をウェットエッチング法またはドライエッチング法を用いて除去する。この結果、基板表面には、ほとんど熱酸化膜が形成されていない領域110と、約800mm程度の第一の熱酸化膜80が形成された領域が存在する(図4(a)参照)

[0030]

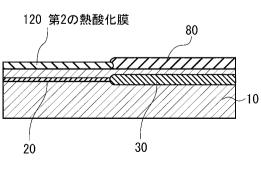

次に、酸化雰囲気中で第二の熱処理を行う。第二の熱処理条件としては、たとえば約900 の約100%程度の酸素雰囲気中で約1時間程度行う。この第二の熱処理では、厚い熱酸化膜80で覆われている領域は酸化速度が遅く、熱酸化膜はほとんど増加しないのに対し、酸化膜で覆われていない領域110には第二の熱酸化膜120が形成される。このとき、第一の熱酸化膜80及び第二の熱酸化膜120と基板との界面がほぼ等しくなるような第二の熱処理条件を選択することが好ましい。この第二の熱処理条件の最適化によって、後で形成される基板10の表面の水平方向の段差の量が制御されることになる(図4(b)参照)。

[0031]

次に、第一の熱酸化膜 8 0 および第二の熱酸化膜 1 2 0 をウェットエッチングまたはドライエッチングにより除去する。これにより、第一の熱酸化膜 8 0 と第二の熱酸化膜 1 2 0 は除去され、基板中の薄い酸化膜 2 0 の領域と厚い酸化膜 3 0 の領域で、基板表面の水平方向において、段差による高低差が少ない平坦な表面をもつ基板が形成される。

[0032]

本実施例によれば、基板表面の段差が約20nm以下の平坦な基板を提供することが可能となる。また、薄い酸化膜20は後の熱工程によって内部酸化による膜厚増加の影響を抑えることが可能になり、薄い酸化膜20の膜厚を制御することがきわめて容易になる。

[ 0 0 3 3 ]

なお、本発明は以上の構成に限定されるものではなく、種々の変形が可能である。例えば、本実施例でははじめに張り合わせ法によるSOI基板を用いたが、これを堆積膜結晶法によって形成してもよく、あるいはエピタキシャル成長法など他の方法で形成してもよい。

- 【実施例2】

- [0034]

実施例 1 では耐酸化性を有する第一のマスクと酸化種を基板まで到達することを防ぐための第二のマスクの二層膜を有していた。本実施例では両者の役割をひとつのマスクで兼ねている点で実施例 1 と異なる。

[0035]

実施例 2 に係る半導体基板を示す断面図は実施例 1 における図 1 と同様である。基板 1 0 中には基板の一定の深さ(たとえば約 5 0 n m ) の領域に、たとえば膜厚が約 1 0 n m 程度の埋め込みの薄い酸化膜 2 0 を有する部分と、たとえば膜厚が約 1 0 0 n m 程度の埋め込みの厚い酸化膜 3 0 を有する部分がある。基板 1 0 としては、単結晶シリコンのほかに、多結晶シリコン、シリコンゲルマニウム(SiGe)、およびシリコンカーバイド(SiC)等のSiを含む材料が使用可能である。

[ 0 0 3 6 ]

次に、実施例2に係る半導体基板の製造工程を図5から図7の工程断面図を用いて説明する。

[0037]

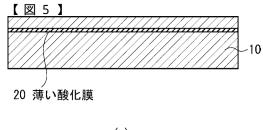

まず、図5(a)に示すように、実施例1と同様に張り合わせ方式を用い、埋め込み酸化膜が基板全面に約10nm程度の厚さで形成されたSOI基板10を用いる。

[0038]

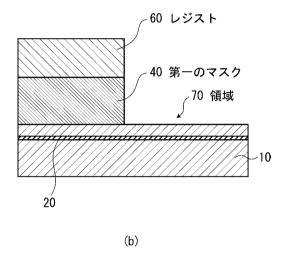

次に、基板10上に第一のマスク40を堆積する。本実施例のマスク材としては例えば シリコン窒化膜を用い、膜厚としては例えば約1μmとする。

[0039]

50

40

20

10

20

30

40

50

このとき第一のマスクの厚さは、後の工程で酸素雰囲気中において熱処理を行う際にマスク下の基板部分が酸化されないために十分な厚さが必要であり、また後の工程で酸化種を イオン注入する際に酸化種が基板まで到達することのない十分な厚さが必要である。

### [0040]

次に、第一のマスク40上にレジストを塗布し、レジストをパターニングする。次に、レジストをマスクとして、RIE(Reactive Ion Etching)により第一のマスク40の一部を除去し、図5(b)に示すような領域70を形成する。図5(b)では領域70は基板10に達しているが、かならずしも基板10の表面が露出する必要はなく、第一のマスク40の一部が残っていてもよい。

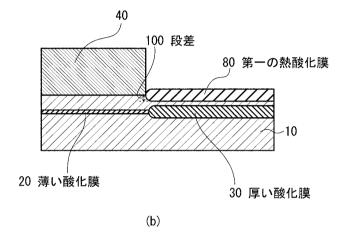

#### [0041]

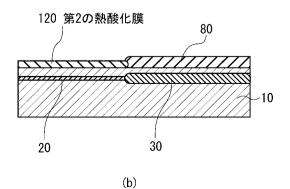

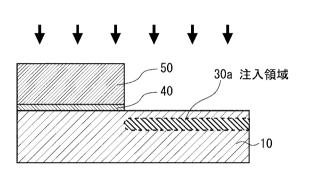

次に、加工された第一のマスク40をマスクとして、酸化種をイオン注入により注入する。条件は、たとえば酸化種として〇+イオンを約150KeVから約200KeVのエネルギーで約4×1017cm-2から約6×1017cm-2程度のドーズ量で注入する。このとき、基板10中の領域70の領域には酸化種がイオン注入されるが、第一のマスク40により覆われた領域は、酸化種が第一のマスク40により、基板10には到達しない(図6(a)参照)。

## [0042]

以下の工程は実施例1と同様である。

## [0043]

まず、酸素を含む雰囲気中で第一の熱処理をする。第一の熱処理の条件として、たとえば、まず約1%程度の酸素を含むアルゴンガス中で、約1300 から約1400 で約100%程度の酸素がス中において、約4時間程度の熱処理を加える。ここで、第一の熱処理を放った酸化種が基板10中のシリコンと反応して、酸化膜を形成する効果がある。第一の熱処理条件は、基板10の第一のマスクで覆われている領域には、熱酸化膜がほるのを形成されない条件を選択することが好ましい。このような条件を選択することによって、第一の熱処理時における内部酸化によって薄い酸化膜20の膜厚が増加するのを抑制することが可能となり、薄い酸化膜20の膜厚制御を容易にする効果がある。このため、第一のマスクは耐酸化特性をもつ膜であることが望ましい。また第一のマスク材料として、多結晶シリコンのように、それ自身が酸化されることによって下地の基板10を酸化しないマスクを用いることもできる。

## [0044]

第一のマスクで覆われていない領域の表面には、この第一の熱処理により約800nm程度の第一の熱酸化膜80が形成される。また、基板10中では、イオン注入された酸素原子とシリコンとが反応し、約100nm程度の厚い酸化膜30を形成する。このとき、酸化膜は消費したシリコンに対して約2.2倍の体積をもつため、厚い酸化膜30が形成された領域では表面が膨張し押し上げられる。これにより、図6(b)に示すように、薄い酸化膜20の領域および厚い酸化膜30の領域の基板表面の水平方向には、約200nm程度の高低差を有する段差100が生じる。

#### [0045]

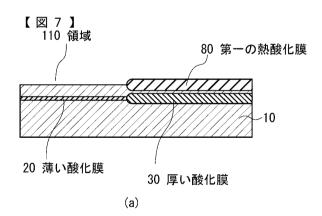

次に、第一のマスク40をウェットエッチング法またはドライエッチング法を用いて除去する。この結果、基板表面には、ほとんど熱酸化膜が形成されていない領域110と、約800mm程度の第一の熱酸化膜80が形成された領域が存在する(図7(a)参照)

## [0046]

次に、酸化雰囲気中で第二の熱処理を行う。第二の熱処理条件としては、たとえば約900 の約100%程度の酸素雰囲気中で約1時間程度行う。この第二の熱処理では、厚い熱酸化膜80で覆われている領域は酸化速度が遅く、熱酸化膜はほとんど増加しないのに対し、酸化膜で覆われていない領域110には第二の熱酸化膜120が形成される。このとき、第一の熱酸化膜80及び第二の熱酸化膜120と基板との界面がほぼ等しくなる

ような第二の熱処理条件を選択することが好ましい。この第二の熱処理条件の最適化によって、後で形成される基板10の表面の水平方向の段差の量が制御されることになる(図7(b)参照)。

### [0047]

次に、第一の熱酸化膜 8 0 および第二の熱酸化膜 1 2 0 をウェットエッチングまたはドライエッチングにより除去する。これにより、第一の熱酸化膜 8 0 と第二の熱酸化膜 1 2 0 は除去され、基板中の薄い酸化膜 2 0 の領域と厚い酸化膜 3 0 の領域で、基板表面の水平方向において、段差による高低差が少ない平坦な表面をもつ基板が形成される。

#### [0048]

本実施例によれば、基板表面の段差が約20nm以下の平坦な基板を提供することが可能となる。また、薄い酸化膜20は後の熱工程によって内部酸化による膜厚増加の影響を抑えることが可能になり、薄い酸化膜20の膜厚を制御することがきわめて容易になる。

#### [0049]

本実施例に拠れば、基板表面の段差が約20nm以下の平坦な基板を第一の実施例よりも 少ない工程数で実現することが可能となる。

#### 【実施例3】

## [0050]

実施例 1 および実施例 2 では、薄い埋め込み酸化膜も厚い酸化膜もイオン注入を用いた SIMOX法を用いることにより、この形成順序を入れ替えることが可能な点で実施例 1 および実施例 2 と異なる。

#### [0051]

図8は、本発明の実施例3に係る半導体基板を示す断面図である。以下の図面の記載において、同一の部分には同一の符号を付している。

#### [0052]

基板10中には基板の一定の深さの領域に、膜厚がたとえば約10nm程度の薄い酸化膜20を有する部分と、膜厚がたとえば約100nm程度の厚い酸化膜30を有する部分がある。

#### [0053]

次に、実施例3に係る半導体基板の製造工程を図9から図11の工程断面図を用いて説明する。

## [ 0 0 5 4 ]

実施例1および実施例2と同様に、基板10として単結晶シリコン、多結晶シリコン、 SiGe,SiC等のSiを含む材料を用いることができる。

## [0055]

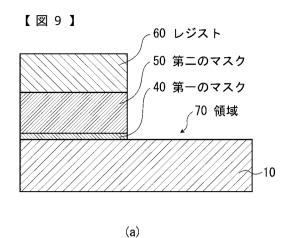

まず、基板 1 0 の表面に第一のマスク 4 0 および第二のマスク 5 0 を堆積し、レジスト 6 0 を塗布した後にフォトリソグラフィーを用いて領域 7 0 を形成する(図 9 ( a ) 参照)。

## [0056]

ここでレジストを剥離し、領域70に第一のイオン注入により酸化種を注入する。注入の条件としては、たとえば酸素原子を約180KeVのエネルギーで約4×1017cm-2程度のドーズ量を用いる。このとき、領域70には酸化種がイオン注入され、第一のマスク40および第二のマスク50で覆われた領域には酸化種が注入されない条件を選択する。このときの第一のイオン注入の条件によって、厚い酸化膜30の厚さと深さを制御することができる(図9(b)参照)。

#### [0057]

次に、約1300 から約1400 程度の酸素を含む雰囲気中で第一の熱処理を加える。この第一の熱処理により、注入された酸化種は基板中のシリコンと結合し約100n m程度のシリコン酸化膜を形成する。これにより厚い酸化膜30が形成される。また、領域70にあたる基板表面には約800nm程度の第一の熱酸化膜80が形成される。

## [0058]

50

40

20

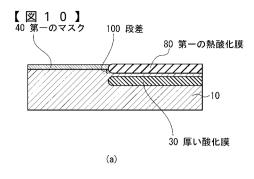

次に第二のマスク 5 0 を除去する(図 1 0 (a)参照)。

## [0059]

次に、全面に第二のイオン注入を行う。厚い酸化膜30の領域の表面には約800mm程度の酸化膜があるため、これがイオン注入時のマスクとして機能する。この第二のイオン注入はたとえば酸素原子を約180KeVから約200KeVのエネルギーで約1x1017cm-2から約3×1017cm-2程度のドーズ量で行う。このときのエネルギー条件の選択によって、薄い酸化膜20を形成する基板中の深さを選択することが可能であり、厚い酸化膜30と同じ深さにすることも、厚い酸化膜30よりも深い領域に形成することが可能となる。また、ドーズ量条件の選択によって、薄い酸化膜20の膜厚を制御することが可能となる(図10(b)参照)。

[0060]

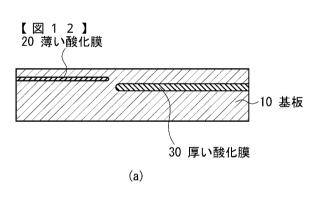

次に、第一のマスク40を除去する(図11(a)参照)。

#### [0061]

ここで、第一の熱処理と同じ条件で第二の熱処理を加える。ただし、第一の熱処理を行わずに第一の熱処理と第二の熱処理を兼ねてここで一度の熱処理を加えてもよい。その場合には、厚い酸化膜30の表面領域には第一の熱酸化膜80が形成される前に第二のイオン注入を行うことになる。このため、第一のマスクが覆う領域では薄い酸化膜20が形成されると同時に、厚い酸化膜30の領域にも再度酸化種が注入されることになる。このとき、第二のイオン注入の条件によって厚い酸化膜30の膜厚が増加する場合もあるし、厚い酸化膜30とは異なる深さの領域に薄い酸化膜領域が形成される場合もある。

[0062]

次に、約900 程度の酸素雰囲気中における第三の熱処理を行う。この第三の熱処理により、第一の熱酸化膜80のある領域はほとんど酸化されないのに対し、第一のマスク40を除去した領域の表面は、熱処理により表面が酸化され第二の熱酸化膜が形成される(図11(b)参照)。ここで、第一の熱酸化膜及び第二の熱酸化膜の基板との界面がほぼ一致するような第三の熱処理条件を選択することが好ましい。

[0063]

次に第一の熱酸化膜および第二の熱酸化膜をウェットエッチングまたはドライエッチング等の方法により除去する。

[0064]

この結果、薄い酸化膜20と厚い酸化膜30の領域の境界部分の段差は約20nm以下となり、表面が平坦な基板を提供することが可能となる(図8参照)。

[0065]

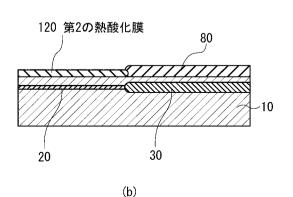

なお、本発明は以上の構成に限定されるものではなく、種々の変形が可能である。例えば、先に薄い酸化膜 2 0 を形成するためのイオン注入を行ってもよい。また、基板表面の一部にマスクを形成してから薄い酸化膜 2 0 を形成するためのイオン注入を行ってもよい。また、本実施例では、厚い酸化膜 3 0 と薄い酸化膜 2 0 がほぼ等しい深さに形成される場合について説明したが、本発明はこのような相対関係に限定されるものではなく、図 1 2 ( a ) のように厚い酸化膜 3 0 の方が薄い酸化膜 2 0 よりも深い領域に形成された構造でもよいし、図 1 2 ( b ) のように厚い酸化膜 3 0 のほうが浅い領域に形成された構造でもよい。

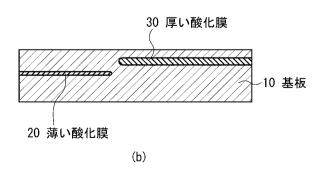

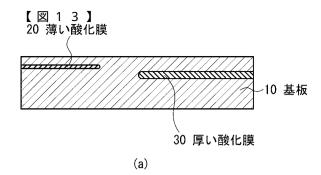

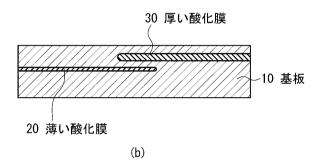

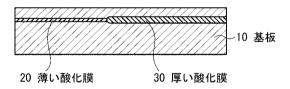

[0066]

また、本発明は以上の構成に限定されるものではなく、図13(a)のように一部に埋め込み酸化膜のない領域があってもよいし、図13(b)のように薄い酸化膜20と厚い酸化膜30が一部の領域でオーバーラップする領域があってもよい。

## [0067]

さらに、基板中に埋め込まれる酸化膜の厚さは 2 種類以上あってもよい。たとえば、酸化膜の厚さが 3 種類ある場合には、もっとも薄い領域に F B C を形成し、厚い方の 2 種類の膜厚の領域に部分空乏型のロジック回路と完全空乏型のロジック回路をそれぞれ形成することも可能であるし、あるいは一部に S R A M を形成することも可能である。また、酸

10

20

30

40

化膜のない領域にはDRAMに代表されるようなメモリや周辺回路を形成することも可能 である。

## 【図面の簡単な説明】

- [0068]

- 【図1】実施例1に係る半導体基板の断面構造を示す図。

- 【図2】実施例1に係る半導体基板の製造工程を示す図。

- 【図3】実施例1に係る半導体基板の製造工程を示す図。

- 【図4】実施例1に係る半導体基板の製造工程を示す図。

- 【図5】実施例2に係る半導体基板の製造工程を示す図。

- 【図6】実施例2に係る半導体基板の製造工程を示す図。

- 【図7】実施例2に係る半導体基板の製造工程を示す図。

- 【図8】実施例3に係る半導体基板の断面構造を示す図。

- 【図9】実施例3に係る半導体基板の製造工程を示す図。

- 【図10】実施例3に係る半導体基板の製造工程を示す図。

- 【図11】実施例3に係る半導体基板の製造工程を示す図。

- 【図12】実施例3に係る半導体基板の断面構造を示す図。

- 【図13】実施例3に係る半導体基板の断面構造を示す図。

## 【符号の説明】

- [0069]

- 1 0 基 板

- 2 0 薄い酸化膜

- 3 0 厚い酸化膜

- 3 0 a 注入領域

- 4 0 第一のマスク

- 5 0 第二のマスク

- 6 0 レジスト

- 7 0 領 域

- 8 0 第一の熱酸化膜

- 1 0 0 段差

- 1 1 0 領 域

- 1 2 0 第二の熱酸化膜

10

20

(a)

(b)

(b)

(a)

(a)

(b)