(12)发明专利

(10)授权公告号 CN 104022148 B

(45)授权公告日 2020.03.20

(21)申请号 201410059960.5

(51)Int.Cl.

(22)申请日 2014.02.21

H01L 29/737(2006.01)

(65)同一申请的已公布的文献号

申请公布号 CN 104022148 A

(56)对比文件

CN 102723358 A, 2012.10.10,

(43)申请公布日 2014.09.03

CN 102484067 A, 2012.05.30,

(30)优先权数据

US 2012/0319169 A1, 2012.12.20,

13/780,192 2013.02.28 US

US 2012/0319169 A1, 2012.12.20,

(73)专利权人 电力集成公司

审查员 裴亚芳

地址 美国加利福尼亚州

(72)发明人 J·拉姆德尼 M·墨菲

J·P·爱德华兹

(74)专利代理机构 北京林达刘知识产权代理事

务所(普通合伙) 11277

代理人 刘新宇

权利要求书2页 说明书9页 附图5页

(54)发明名称

具有AlSiN钝化层的异质结构功率晶体管

100

(57)摘要

一种异质结构半导体器件，包含第一活性层和布置在该第一活性层上的第二活性层。二维电子气层被形成在该第一活性层与该第二活性层之间。AlSiN钝化层被布置在该第二活性层上。第一欧姆接触点和第二欧姆接触点电学连接到该第二活性层。该第一欧姆接触点和该第二欧姆接触点横向间隔开，栅极被布置在该第一欧姆接触点与该第二欧姆接触点之间。

1. 一种异质结构功率晶体管,包括:

第一活性层;

第二活性层,被布置在该第一活性层上,二维电子气层形成在该第一活性层与该第二活性层之间;

包括氮化铝硅、即AlSiN的钝化和栅极电介质层,被布置在该第二活性层上;在所述钝化和栅极电介质层上的AlN籽晶层;

包括氧化铝、即Al<sub>2</sub>O<sub>3</sub>的第二栅极电介质层,所述第二栅极电介质层被布置在所述AlN籽晶层上;

栅极,被竖向布置在所述第二栅极电介质层上并且所述钝化和栅极电介质层将所述栅极与所述第二活性层竖向分隔;

第一欧姆接触点和第二欧姆接触点,该第一欧姆接触点和第二欧姆接触点电学连接到该第二活性层,该第一欧姆接触点和该第二欧姆接触点横向间隔开,该栅极被布置在该第一欧姆接触点与该第二欧姆接触点之间。

2. 根据权利要求1所述的异质结构功率晶体管,进一步包括被布置在该第二栅极电介质层之上的上钝化层,该栅极竖向延伸穿过该上钝化层,以接触该第二栅极电介质层。

3. 根据权利要求1所述的异质结构功率晶体管,其中该钝化和栅极电介质层具有第一厚度,且该第二栅极电介质层具有第二厚度,该第二厚度大于该第一厚度。

4. 根据权利要求1所述的异质结构功率晶体管,其中该第一欧姆接触点和该第二欧姆接触点竖向延伸穿过该第二栅极电介质层和该钝化和栅极电介质层。

5. 根据权利要求2所述的异质结构功率晶体管,其中该第一欧姆接触点和该第二欧姆接触点竖向延伸穿过该上钝化层、该第二栅极电介质层和该钝化和栅极电介质层。

6. 根据权利要求1所述的异质结构功率晶体管,其中该钝化和栅极电介质层具有在1-5纳米厚的范围内的第一厚度,并且该第二栅极电介质层具有在10-20纳米厚的范围内的第二厚度。

7. 根据权利要求1所述的异质结构功率晶体管,其中该第一欧姆接触点和该第二欧姆接触点分别包括源极欧姆接触点和漏极欧姆接触点。

8. 根据权利要求2所述的异质结构功率晶体管,其中该上钝化层包括SiN。

9. 根据权利要求1所述的异质结构功率晶体管,其中该第一活性层包括氮化镓、即GaN。

10. 根据权利要求1所述的异质结构功率晶体管,其中该第二活性层包括氮化铝镓、即AlGaN。

11. 根据权利要求1所述的异质结构功率晶体管,其中该第一活性层和该第二活性层被限定为隔离台面。

12. 根据权利要求1所述的异质结构功率晶体管,其中该钝化和栅极电介质层是5-10%的铝对氮化硅。

13. 一种用于制造异质结构半导体器件的方法,包括:

在衬底上形成第一活性层;

在该第一活性层上形成第二活性层,该第一活性层和该第二活性层具有不同的带隙,以使得在它们之间形成二维电子气层;

在该第二活性层上形成包括氮化铝硅、即AlSiN的钝化和栅极电介质层,该钝化和栅极

电介质层具有第一厚度；

在该钝化和栅极电介质层之上与该钝化和栅极电介质层原位生长AlN籽晶层；将AlN层用作籽晶层以形成第二栅极电介质层，将包括氧化铝的第二栅极电介质层沉积在该钝化和栅极电介质层之上；

形成第一欧姆接触点和第二欧姆接触点，该第一欧姆接触点和第二欧姆接触点各自竖向延伸穿过该钝化和栅极电介质层，该第一欧姆接触点和该第二欧姆接触点横向间隔开，且电学连接到该第二活性层；以及

在该第一欧姆接触点与该第二欧姆接触点之间的横向位置处形成栅极，其中所述钝化和栅极电介质层将所述栅极与所述第二活性层竖向分隔。

14. 根据权利要求13所述的方法，其中该第二栅极电介质层具有大于该第一厚度的第二厚度。

15. 根据权利要求14所述的方法，进一步包括：将上钝化层沉积在该第二栅极电介质层之上。

16. 根据权利要求13所述的方法，其中该第一活性层包括氮化镓。

17. 根据权利要求13所述的方法，其中该第二活性层包括氮化铝镓。

18. 根据权利要求13所述的方法，其中该钝化和栅极电介质层是与该第一活性层和该第二活性层原位形成的。

19. 根据权利要求14所述的方法，其中该第一厚度在1-5纳米厚的范围内，并且其中该第二厚度在10-20纳米厚的范围内。

20. 根据权利要求13所述的方法，其中形成该钝化和栅极电介质层包括：以MOCVD技术生长AlSiN，使用硅烷、氨和三甲基铝作为用于AlSiN的前体，其中氨流被维持，以使得综合的N成分被维持在Si<sub>3</sub>N<sub>4</sub>与AlN之间的化学定量关系。

21. 根据权利要求13所述的方法，其中该钝化和栅极电介质层是5-10%的铝对氮化硅。

## 具有AlSiN钝化层的异质结构功率晶体管

### 技术领域

[0001] 本发明总体涉及高电压场效应晶体管(FET)，更具体地涉及高电子迁移率晶体管(HEMT)和异质结构场效应晶体管(HFET)，且涉及制造这样的功率晶体管器件的方法。

### 背景技术

[0002] 一个类型的高电压FET是异质结构FET(HFET)，也被称为异质结或高电子迁移率晶体管(HEMT)。基于氮化镓(GaN)及其他宽带隙III-IV直接跃迁半导体材料的HFET，诸如碳化硅(SiC)，因它们超越硅基器件的优越物理性质而被有利地用在某些电子器件中。例如，GaN和AlGaN/GaN晶体管一般因由GaN基材料和器件结构提供的高的电子迁移率、高的击穿电压、和高的饱和电子速率特性而被用在高速切换和高功率应用中(例如功率开关和功率转换器)。由于HFET的物理性质，HFET可以以远快于在相同电压传导相同电流的其他半导体开关的方式改变状态，且宽带隙可以改善HFET在高温的性能。

[0003] GaN基HFET器件典型地通过外延生长(epitaxial growth)被制造在形成为薄盘(thin disk)或晶圆(wafer)的衬底半导体材料(诸如硅、蓝宝石和碳化硅)上。用于直接在该半导体材料中形成电子器件(例如晶体管)的制造步骤常常被称为前道工序(FEOL)处理。在HFET的FEOL处理过程中，该晶圆可以被从多种机器移动，以建立该器件结构的各种材料层。但因为GaN是压电材料，所以GaN基HFET器件在FEOL处理期间易于发生电荷累积(正的或负的)。例如，电荷累积可以是由在半导体的表面上涉及沉积或生长电介质层的钝化工艺导致的。可以通过将该晶圆的表面与环境中的电学和化学状况隔离来利用钝化提供电学稳定性。比如，在HFET制造期间曝露到空气可以造成发生表面反应(诸如氧化)，这可以影响该HFET器件的总体性能。

### 发明内容

[0004] 本发明的目的是通过下述1的异质结构功率晶体管以及18的方法来实现的，2-17和19-28是本发明的优选方案：

[0005] 1. 一种异质结构功率晶体管，包括：

[0006] 第一活性层；

[0007] 第二活性层，被布置在该第一活性层上，二维电子气层形成在该第一活性层与该第二活性层之间；

[0008] 包括氮化铝硅(AlSiN)的钝化层，被布置在该第二活性层上；

[0009] 栅极；

[0010] 第一欧姆接触点和第二欧姆接触点，它们电学连接到该第二活性层，该第一欧姆接触点和该第二欧姆接触点横向间隔开，该栅极被布置在该第一欧姆接触点与该第二欧姆接触点之间。

[0011] 2. 根据1所述的异质结构功率晶体管，进一步包括被布置在该钝化层上的第二栅极电介质层，该栅极被布置在该第二栅极电介质层上方。

[0012] 3. 根据2所述的异质结构功率晶体管,其中所述第二栅极电介质层包括氧化铝( $\text{Al}_2\text{O}_3$ )。

[0013] 4. 根据2所述的异质结构功率晶体管,进一步包括被布置在该第二栅极电介质层之上的上钝化层,该栅极竖向延伸穿过该上钝化层,以接触该第二栅极电介质层。

[0014] 5. 根据2所述的异质结构功率晶体管,其中该钝化层具有第一厚度,且该第二栅极电介质层具有第二厚度,该第二厚度大于该第一厚度。

[0015] 6. 根据2所述的异质结构功率晶体管,其中该第一欧姆接触点和该第二欧姆接触点竖向延伸穿过该第二栅极电介质层和该钝化层。

[0016] 7. 根据4所述的异质结构功率晶体管,其中该第一欧姆接触点和该第二欧姆接触点竖向延伸穿过该上钝化层、该第二栅极电介质层和该钝化层。

[0017] 8. 根据1所述的异质结构功率晶体管,其中该钝化层具有在约1-5纳米厚的范围内的第一厚度。

[0018] 9. 根据2所述的异质结构功率晶体管,其中该第二栅极电介质具有在约10-20纳米厚的范围内的第二厚度。

[0019] 10. 根据1所述的异质结构功率晶体管,其中该第一欧姆接触点和该第二欧姆接触点分别包括源极欧姆接触点和漏极欧姆接触点。

[0020] 11. 根据4所述的异质结构功率晶体管,其中该上钝化层包括SiN。

[0021] 12. 根据1所述的异质结构功率晶体管,其中该第一活性层包括氮化镓(GaN)。

[0022] 13. 根据1所述的异质结构功率晶体管,其中该第二活性层包括氮化铝镓(AlGaN)。

[0023] 14. 根据1所述的异质结构功率晶体管,其中该第一活性层和该第二活性层被限定为隔离台面。

[0024] 15. 根据1所述的异质结构功率晶体管,其中该栅极包括镍金(NiAu)合金。

[0025] 16. 根据10所述的异质结构功率晶体管,其中该栅极包含朝着该漏极欧姆接触点延伸的栅极场板。

[0026] 17. 根据1所述的异质结构半导体器件,其中该栅极包括钛金(TiAu)合金或钼金(MoAu)合金。

[0027] 18. 一种用于制造异质结构半导体器件的方法,包括:

[0028] 在衬底上形成第一活性层;

[0029] 在该第一活性层上形成第二活性层,该第一活性层和该第二活性层具有不同的带隙,以使得在它们之间形成二维电子气层;

[0030] 在该第二活性层上形成包括氮化铝硅(AlSiN)的钝化层,该钝化层具有第一厚度;

[0031] 形成第一欧姆接触点和第二欧姆接触点,它们各自都竖向延伸穿过该钝化层,该第一欧姆接触点和该第二欧姆接触点横向间隔开,且电学连接到该第二活性层;以及

[0032] 在该第一欧姆接触点与该第二欧姆接触点之间的横向位置处形成栅极。

[0033] 19. 根据19所述的方法,进一步包括:将第二栅极电介质层沉积在该钝化层之上,该第二栅极电介质层具有大于该第一厚度的第二厚度。

[0034] 20. 根据19所述的方法,进一步包括:将上钝化层沉积在该第二栅极电介质层之上。

[0035] 21. 根据19所述的方法,进一步包括:将该第二栅极电介质层退火。

- [0036] 22. 根据19所述的方法，其中该第二栅极电介质层包括氧化铝。

- [0037] 23. 根据18所述的方法，其中该第一活性层包括氮化镓。

- [0038] 24. 根据18所述的方法，其中该第二活性层包括氮化铝镓。

- [0039] 25. 根据18所述的方法，其中该钝化层是与该第一活性层和该第二活性层原位形成的。

- [0040] 26. 根据18所述的方法，进一步包括：在该钝化层之上与该钝化层原位生长AlN层。

- [0041] 27. 根据18所述的方法，其中该第一厚度在约1-5纳米厚的范围内。

- [0042] 28. 根据19所述的方法，其中该第二厚度在约10-20纳米厚的范围内。

## 附图说明

[0043] 参照下列图描述本发明的非限制性和非穷举性实施方案，其中在各个视图中，相同的参考数字指代相同的部分，除非另有规定。

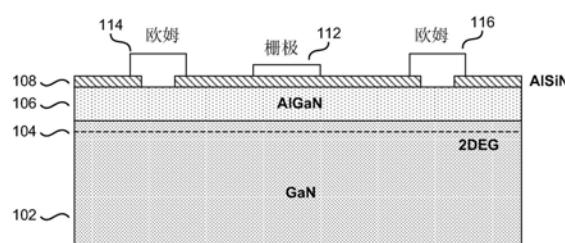

- [0044] 图1是具有一个钝化结构的示例性半导体器件的截面侧视图。

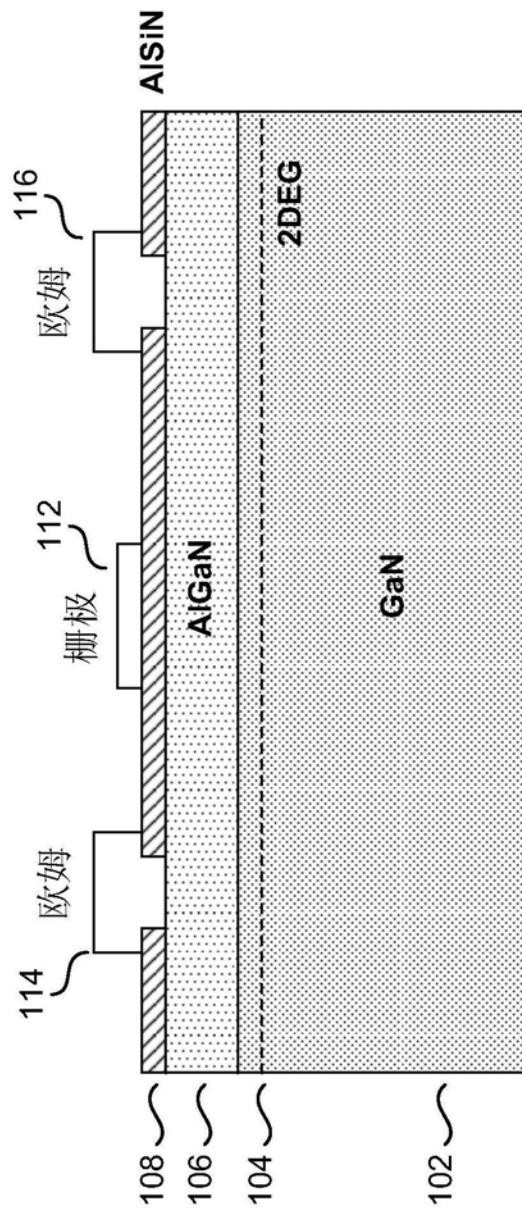

- [0045] 图2是具有另一个钝化结构的示例性半导体器件的截面侧视图。

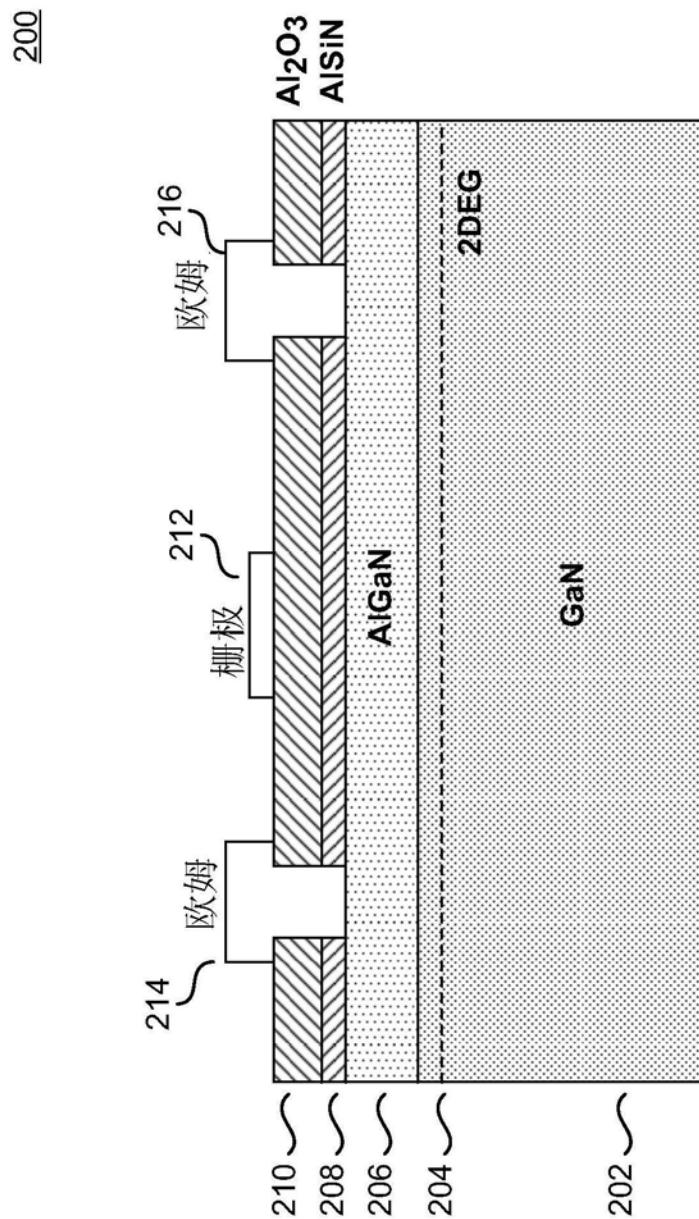

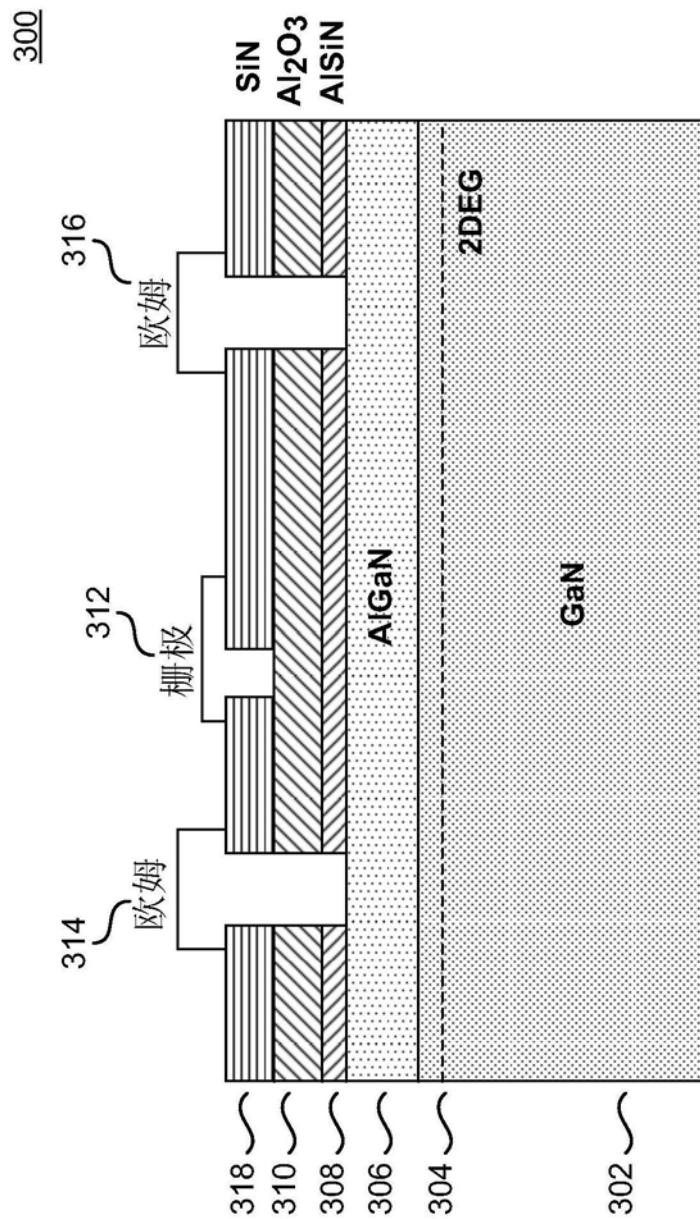

- [0046] 图3是具有又一个钝化结构的示例性半导体器件的截面侧视图。

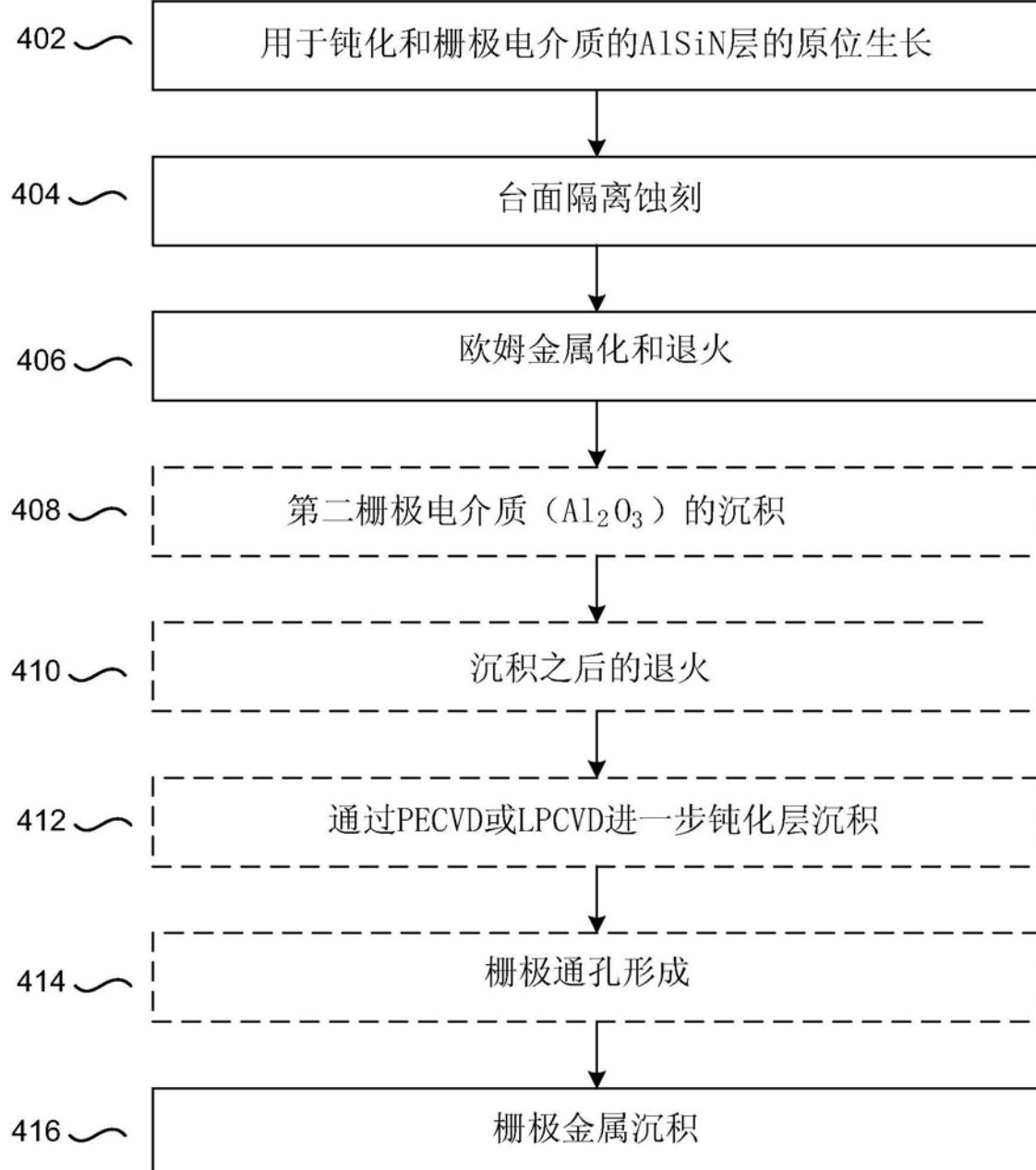

- [0047] 图4是例示了用于制造半导体器件结构的一个示例性处理流程的流程图。

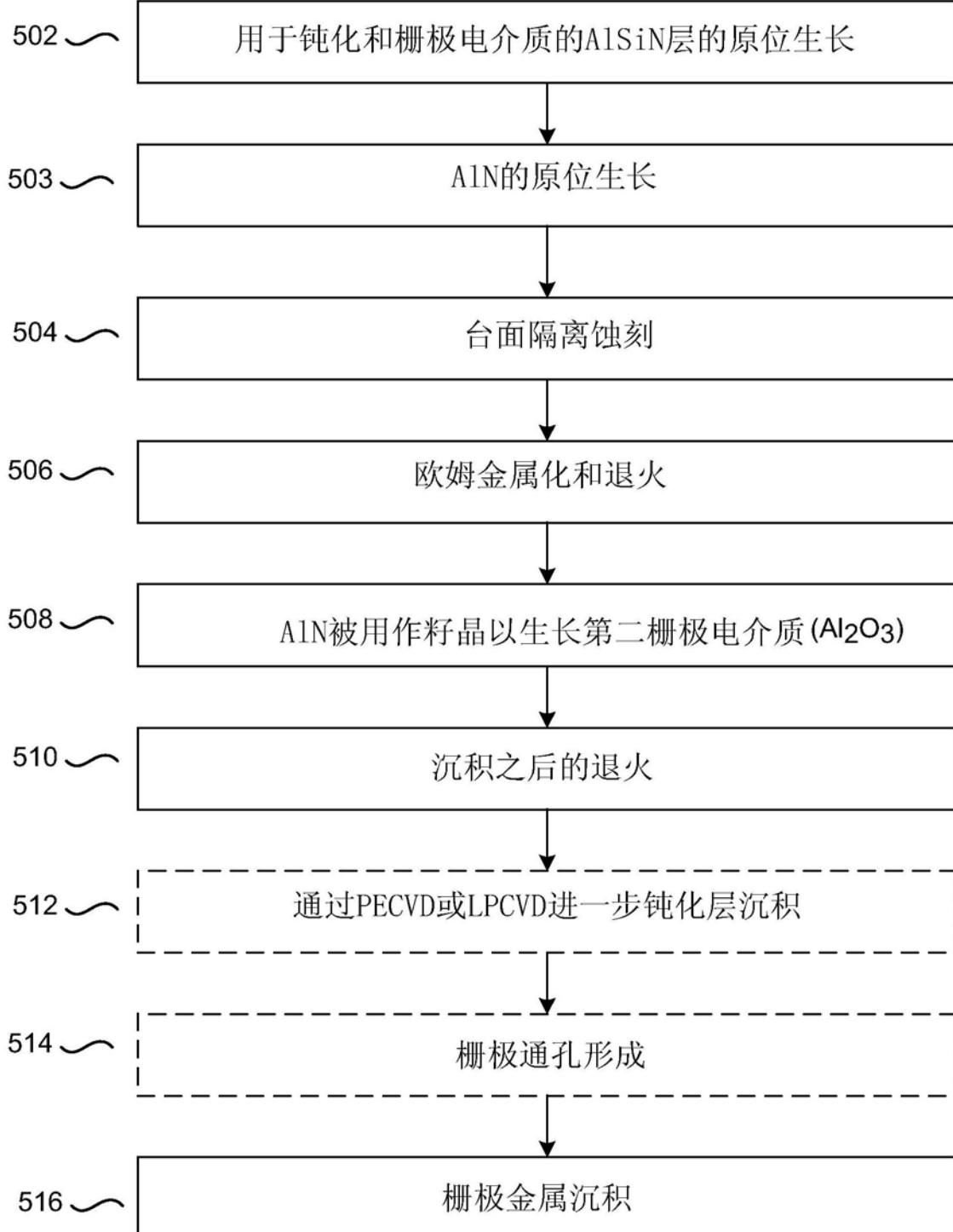

- [0048] 图5是例示了用于制造半导体器件结构的另一个示例性处理流程的流程图。

- [0049] 在这些附图的所有几个视图中，对应的参考字符指示对应的部件。技术人员应意识到，这些图中的元件是为了简化和清楚而例示的，且不必然按比例绘制。例如，这些图中的一些元件的尺寸相对于其他元件可以被夸大，以帮助增进对本发明的多种实施方案的理解。而且，经常没有描绘在商业上可行的实施方案中有用或必要的普通但广为理解的元件，以免妨碍观看本发明的这些多种实施方案。

## 具体实施方式

[0050] 在下列描述中，阐述了众多具体细节，以提供对本发明的透彻理解。然而应明了，对于本领域普通技术人员，无需采用该具体细节来实践本发明。在其他情况下，没有详细描述广为知晓的材料或方法，以免模糊本发明。

[0051] 本说明书通篇提及“一个实施方案”、“一实施方案”、“一个实施例”或“一实施例”意指，结合该实施方案或实施例描述的特定特征、结构或特性被包含在本发明的至少一个实施方案中。因而，在本说明书通篇各个地方出现的短语“在一个实施方案中”、“在一实施方案中”、“一个实施例”或“一实施例”不必然全都指代相同的实施方案或实施例。此外，该特定特征、结构或特性可以以任何合适的组合和/或子组合被结合在一个或更多个实施方案或实施例中。该特定特征、结构或特性可以被包含在集成电路、电子电路、组合逻辑电路或提供所描述的功能的其他合适的部件中。另外，应意识到，随此提供的这些图是为了向本领域普通人员解释，且绘图不必然按比例绘制。

[0052] 在下面的描述中，为了解释而使用一个示例性HFET。然而，应意识到，本发明的实施方案可以与其他类型的FET(诸如金属氧化物半导体FET(MOSFET)或金属绝缘栅半导体FET(MISFET)器件)一起使用。

[0053] 如上面提及的，在制造过程期间，表层电荷(sheet charge)可以积累在HFET器件

的晶圆上。为了对抗所积累的表面电荷(surface charge)的作用,且为了保护该HFET器件不受其他环境状况影响,一个或更多个电介质材料层可以被用作保护该HFET的表面的钝化层。

[0054] 根据本发明的一些实施方案,公开了一种GaN基HFET器件结构及其制造方法,它利用一种基于氮化铝硅(AlSiN)的新材料组合来钝化HFET器件的GaN表面。在一个实施方案中,该AlSiN层在该HFET器件中用作钝化层和栅极电介质。与传统的钝化材料相比,当用在本文描述的HFET结构中时,AlSiN的较宽带隙可以使切换期间的电流崩塌最小化、减少栅极泄漏以及提供增强的栅极可靠性和稳定性。

[0055] 在一个实施方案中,该HFET器件具有第一活性层和第二活性层,它们之间形成有二维电子气层(two-dimensional electron gas layer)。AlSiN(例如Al<sub>3</sub>N<sub>4</sub>)的钝化层被布置在该第二活性层上。该AlSiN钝化层也可以用作第一栅极电介质层。(在本公开内容中,这个双功能层也被称为钝化/第一栅极电介质层。)在又一个实施方案中,第二栅极电介质层被布置在该第一栅极电介质层上。在一个实施例中,氧化铝(Al<sub>2</sub>O<sub>3</sub>)被用于第二栅极电介质层。在另一些实施方案中,一个或多个附加的层被形成在该第二栅极电介质层之上。栅极构件被布置在该AlSiN钝化层上方。该器件的欧姆接触点(ohmic contact)(源极和漏极)向下延伸到该第二活性层。

[0056] 图1例示了示例性半导体器件(即HFET器件)100的截面侧视图,半导体器件100包含:第一活性层102,也被称为通道层;第二活性层106,也被称为阻挡层(barrier layer)或施主层(donor layer);钝化层108;栅极112;以及各自的源极欧姆接触点114和漏极欧姆接触点116。各自的源极欧姆接触点114和漏极欧姆接触点116被示出为竖向向下延伸穿过钝化层108,以电学连接到第二活性层106。如示出的,源极欧姆接触点114和漏极欧姆接触点116横向间隔开,且栅极112被布置在源极欧姆接触点114与漏极欧姆接触点116之间。

[0057] 图1中进一步示出了电荷层104,它形成在第一活性层102与第二活性层106之间。电荷层104有时被称为二维电子气(2DEG)层104。2DEG层104限定了用于该HFET器件的横向导电通道。2DEG层104是因这两个活性层之间的带隙差异而形成的。尤其,2DEG层104是因这两个活性层之间的自发和压电的极化作用的变化而形成的。因而,被捕获在由各自的第一活性层102与第二活性层106之间的带隙差异造成的量子阱中的电子在两个(水平)维度上自由地横向移动,但被紧紧限制在第三(竖直)维度中。

[0058] 在本公开内容的上下文中,术语“原位(in-situ)”是指在单个工具或反应腔内执行的处理,而不将该晶圆暴露到该工具或腔外部的环境。进一步,术语“非原位(ex-situ)”可以指不在单个工具中执行的处理。在另一个实施方案中,在分别形成第一活性层102和第二活性层106之后,可以使用金属-有机化学气相分解(MOCVD)来形成钝化层108。换言之,钝化层108可以分别与第一活性层102和第二活性层106原位沉积。

[0059] 应意识到,第一活性层102典型地被布置在由若干不同材料(诸如蓝宝石(Al<sub>2</sub>O<sub>3</sub>)、硅(Si)、GaN或碳化硅(SiC))之中的任何一种形成的衬底(未示出)之上。在一个实施方案中,第一活性层102包括外延GaN层。为了避免可能的晶格失配和/或热膨胀系数差异的问题,一个或多个附加的层可以被布置在第一活性层102与下面的衬底之间。例如,可选的薄成核层可以被形成在该衬底与第一活性层102之间。在另一些实施例中,第一活性层102可以包括含有其他III族元素的多种氮化物的不同半导体材料。另外,在形成第二活性层106

之前,可以在第一活性层102顶上形成AlN薄(约1nm)层。第一活性层102可以被生长或沉积在该衬底上。

[0060] 第二活性层106被布置在第一活性层102上。在图1的实施例中,第二活性层106包括氮化铝镓(AlGaN)。在另一些实施例中,不同的III族氮化物半导体材料(诸如氮化铝铟(AlInN)和氮化铝铟镓(AlInGaN))可以被用于第二活性层106。在另一些实施方案中,第二活性层106的材料可以是非化学计量化合物(non-stoichiometric compound)。在这样的材料中,各元素的比例不容易用普通整数来表达。例如,第二活性层106可以是III族非化学计量氮化物半导体材料,诸如 $Al_xGa_{1-x}N$ ,其中 $0 < X < 1$ 。在一个实施方式中,第二活性层106包括具有约20纳米(nm)厚的厚度的AlGaN(A125%)。在形成钝化层108之前,可以可选地在第二活性层106顶上形成薄的(约1nm)GaN终止层。第二活性层106可以被生长或沉积在第一活性层102上。

[0061] 如图1中示出的,钝化层108被布置在第二活性层106上。如上面讨论的,在一个实施方案中,钝化层108包括氮化铝硅(AlSiN)。在一个实施例中,钝化层108的厚度可以在1-10纳米(nm)厚的近似范围内。进一步,在一个实施方式中,钝化层108是基本5-10%的铝(Al)对氮化硅(SiN),且被形成为1-10nm厚。如先前讨论的,钝化层108可以分别与第一活性层102和第二活性层106原位沉积,且被用来钝化这些GaN基活性层。在一个实施例中,钝化层108具有与使用MOCVD原位生长的层相似的纯度、密度和强度特性。例如,与非原位生长的层相比,原位生长的层通常具有更高的纯度、更高的强度和更高的密度。进一步,钝化层108也可以被用作栅极电介质层。

[0062] 钝化层108将栅极112与第二活性层106分隔。如示出的,栅极112被布置在钝化层108顶上。在一个实施方案中,栅极112包括金镍(NiAu)合金。在另一个实施方案中,栅极112包括钛金(TiAu)合金或钼金(MoAu)合金。在另一些实施例中,栅极112可以包括栅极电极和栅极场板。在运行中,栅极112控制各自的源极欧姆接触点114和漏极欧姆接触点116之间的向前导通路径。在图1的实施例中,在钝化层108上方且朝着欧姆漏极接触点116横向延伸的栅极112的部分用作栅极场板,它用以减轻边缘(最靠近欧姆漏极接触点116)处的电场强度。

[0063] 欧姆接触点114和116被布置为穿过钝化电介质层108,以接触第二活性层106。欧姆接触点114是源极接触点的一个实例,而欧姆接触点116是漏极接触点的一个实例。在一个实施方案中,欧姆接触点114和116可以是通过在钝化层108中蚀刻开口然后进行金属沉积和退火步骤而形成的。

[0064] 如示出的,图1例示了制造过程中刚刚在栅极112以及欧姆金属接触点114和116形成之后的一点处的器件结构,该器件结构分别包括GaN HFET器件100的源极电极和漏极电极。图1示出了直接形成在钝化层108上的欧姆金属接触点114和116。在另一些实施方案中,欧姆金属接触点114和116可以被形成在竖向向下延伸到第二活性层106中的凹陷中。在又一些实施方案中,欧姆金属接触点114和116可以被形成在竖向向下延伸穿过第二活性层106的凹陷中,以接触第一活性层102。

[0065] 当半导体器件100被配置为用作功率开关时,栅极112以及欧姆接触点114和116典型地通过端子被联结,以形成到外部电路的电学连接。在运行中,2DEG层104中的电荷在欧姆接触点114与116之间横向流动,以成为外部电路中的电流。该电荷流,从而该电流,可以

被来自电学连接在栅极112与欧姆接触点114之间的外部电路的电压控制。

[0066] 如本公开内容中使用的,电学连接是欧姆连接。欧姆连接是这样的连接,其中电压与电流之间的关系是基本线性的,且在该电流的两个方向上是对称的。例如,仅通过金属彼此接触的两个金属图案被电学连接。相对比,欧姆接触点114和116在半导体器件100中没有电学连接到彼此,因为这两个接触之间的任何连接都是通过该半导体材料中的通道进行的,该传导路径被栅极112控制。相似地,栅极112没有电学连接到第二活性层106,因为钝化层108将栅极112与下面的活性层隔离。

[0067] 如上面讨论的,利用AlSiN作为钝化层108帮助减轻在制造和/或操纵器件100期间积累的表面电荷的不利效应。另外,利用AlSiN作为本文描述的HFET结构中的钝化层108可以使切换期间的电流崩塌最小化、减少栅极泄漏以及提供增强的栅极可靠性和稳定性。进一步,钝化层108也可以被用作栅极电介质层。

[0068] 图2例示了示例性半导体器件(HFET器件)200的截面侧视图,半导体器件200包含第一活性层202、第二活性层206以及形成在它们之间的2DEG层204。也示出了钝化/第一栅极电介质层208、第二栅极电介质210、栅极212以及各自的源极欧姆接触点214和漏极欧姆接触点216。图2中示出的半导体器件200与图1的半导体器件100相似,除了HFET器件200包含了钝化层218顶上的第二栅极电介质层210。第二栅极电介质层210被布置在钝化/第一栅极电介质层208上,且横向包围各自的源极欧姆接触点114和漏极欧姆接触点116,以及栅极112。此外,钝化/第一栅极电介质层208与钝化层108相似,然而被称为“钝化/第一栅极电介质层”,以强调钝化层208也可以被用作多个栅极电介质层的一个层。

[0069] 如示出的,第二栅极电介质层210被布置在钝化/第一栅极电介质层208上。在一个实施例中,第二栅极电介质层210包括氧化铝(Al<sub>2</sub>O<sub>3</sub>)。在又一个实施方案中,其他氧化物材料,诸如ZrO、HfO、SiO<sub>2</sub>和GdO,可以被用于第二栅极电介质层210。在一个实施方案中,第二栅极电介质层210具有近似10–20nm厚的范围内的厚度。在一个实施方案中,第二栅极电介质层210厚于钝化/第一栅极电介质层208。例如,钝化/第一栅极电介质层208的厚度可以在近似1–10nm的范围内。在一个示例性制造过程中,可以利用原子层沉积(ALD)将第二栅极电介质层210与各自的第一活性层202和第二活性层206非原位沉积。

[0070] 如示出的,钝化/第一栅极电介质层208和第二栅极电介质层210将栅极212与第二活性层206竖向分隔。在某些实施方案中,栅极212可以包括栅极电极和栅极场板构件。在图2的实施例中,在第二钝化层218上方且朝着漏极欧姆接触点216横向延伸的栅极212的部分用作栅极场板构件,它用以减轻边缘(最接近漏极欧姆接触点216)处的电场强度。

[0071] 如示出的,源极欧姆接触点214和漏极欧姆接触点216分别被布置在栅极212的对立的横向侧上。欧姆接触点214和216竖向延伸第二栅极电介质层210和钝化/第一栅极电介质层208,以接触第二活性层206。在一个实施方案中,欧姆接触点214和216可以是通过在第二栅极电介质层210和钝化/第一栅极电介质层208中蚀刻开口然后进行金属沉积和退火步骤而形成的。在另一个示例性制造过程中,欧姆接触点214和216可以在沉积第二栅极电介质层210之前被形成。

[0072] 进一步,钝化/第一栅极电介质层208可以连同第二栅极电介质层210被用作一个栅极电介质层。本领域从业者应意识到,以本文描述的方式利用多个栅极电介质层可以有利地产生所得到的HFET器件的更高的临界电压运行。该临界电压V<sub>CRIT</sub>被定义为栅极-源极

电压 $V_{GS}$ ,在该电压处栅极泄漏电流中存在相对急剧的上升。另外,与仅仅利用单个栅极电介质层的器件相比,多个栅极电介质层的使用可以改进半导体器件200的热稳定性。热稳定性与该器件的栅极泄漏电流随着温度而增大多少有关。

[0073] 图3例示了示例性半导体器件(HFET器件)300的截面侧视图,该半导体器件300包含第一活性层302、第二活性层306以及形成在它们之间的2DEG层304。也示出了钝化/第一栅极电介质层308、第二栅极电介质310、上钝化层318、栅极312以及各自的源极欧姆接触点314和漏极欧姆接触点316。图3中示出的半导体器件300与图1的半导体器件100和图2的半导体器件200相似,除了HFET器件300包含上钝化层318。上钝化层318被布置在第二栅极电介质310上,且横向围绕各自的源极欧姆接触点314和漏极欧姆接触点316以及栅极312。进一步,钝化/第一栅极电介质层308与钝化层108相似,然而被称为“钝化/第一栅极电介质层”,以强调钝化层/第一栅极电介质层308也可以被用作多个栅极电介质层的一个层。

[0074] 在一个实施方案中,上钝化层318可以包括电介质材料,诸如氮化硅(SiN)。在另一些实施方案中,上钝化层318可以包括多个材料层。应意识到,上钝化层318通过将HFET器件300的表面与周围环境中的电学和化学污染物隔离,提供了该HFET器件300的电学特性的稳定性。上钝化层318可以通过化学气相沉积——诸如低压化学气相沉积(LPCVD)或等离子体增强化学气相沉积(PECVD)——被沉积。

[0075] 如示出的,上钝化层318、钝化/第一栅极电介质层308和第二栅极电介质层310将栅极312与第二活性层306竖向分隔。在某些实施方案中,栅极312可以包括栅极电极和栅极场板构件。如示出的,栅极312竖向延伸穿过上钝化层318中形成的开口,以接触第二栅极电介质层310。在一个示例性制造过程中,栅极312可以是通过在上钝化层318中蚀刻开口然后进行栅极金属沉积而形成的。在图3的实施例中,在上钝化层318上方且朝着漏极欧姆接触点316横向延伸的栅极312的部分充当栅极场板构件,它用以减轻边缘(最靠近漏极欧姆接触点316)处的电场强度。

[0076] 如示出的,源极欧姆接触点314和漏极欧姆接触点316分别被布置在栅极312的对立的横向侧上。欧姆接触点314和316竖向延伸穿过上钝化层318、第二栅极电介质层310和钝化/第一栅极电介质层308,以接触第二活性层306。在一个实施方案中,欧姆接触点314和316可以是通过在上钝化层318、第二栅极电介质层310和钝化/第一栅极电介质层308中蚀刻开口然后进行金属沉积和退火步骤而形成的。在另一个示例性制造过程中,欧姆接触点314和316可以是在沉积第二栅极电介质层310和上钝化层318之前形成的。

[0077] 图4例示了用于建构半导体器件(诸如图1、图2和图3中分别示出的HFET器件100、200或300)的示例性处理流程400。在所示出的实施例中,该处理在完成第一活性层和第二活性层在该衬底上的外延生长或沉积之后开始。包括AlSiN的层(在上文也被称为钝化/第一栅极电介质层)的形成,在GaN/AlGaN活性层的生长之后被原位执行(框402)。在一个实施方案中,该钝化层是使用在800-900°C之间范围的温度以约100托的反应器压力执行的MOCVD技术来沉积的。在一个实施方案中,包括AlSiN的钝化层是以MOCVD技术生长的,使用硅烷(SiH<sub>4</sub>)、氨(NH<sub>3</sub>)和三甲基铝(TMAI)作为用于AlSiN的前体。氢(H<sub>2</sub>)和氮(N<sub>2</sub>)可以被用作载气(carrier gas)。约501/min.的总流,具有1-101/min.范围内的NH<sub>3</sub>流、约11/min.的SiH<sub>4</sub>和约5-20sccm范围内的TMAI流。该NH<sub>3</sub>流被维持,以使得综合的N成分被维持在如该AlSiN膜的总体折射率和密度监测的Si<sub>3</sub>N<sub>4</sub>与AlN之间的化学定量关系(stoichiometry)。

[0078] 该钝化层被形成到近似1-10nm的范围内的厚度,且在该晶圆的表面之上是连续的。在一个实施方案中,该钝化层的厚度是约5nm。在再另一个实施方案中,该钝化层是与该第一活性层和该第二活性层原位形成的。例如,被用来形成该第一活性层和该第二活性层的相同的MOCVD机器也可以被用来形成该钝化/第一栅极电介质层。在一个实施例中,该钝化层/第一栅极电介质层至使用MOCVD原位生长的层具有纯度、密度和强度特性。例如,原位生长的层通常具有比非原位生长的层更高的纯度、更高的强度以及更高的密度。

[0079] 在该钝化层的生长之后,该钝化层的表面经历台面隔离蚀刻,以限定该欧姆接触点的活性区(框404)。该台面隔离可以是利用反应离子蚀刻(RIE)系统来执行的。在另一些制造方法中,该台面隔离可以是使用电感耦合等离子体(ICP)RIE来执行。在该处理流程中的这一点,可以可选地穿过该钝化层形成欧姆通孔开口,然后进行欧姆金属化和退火(框306)。一种示例性欧姆接触金属是TiAlMoAu。该金属欧姆接触点可以利用RTA工具在近似600-900°C的温度范围被退火长达大约一分钟。

[0080] 接下来,第二栅极电介质层(可以由Al<sub>2</sub>O<sub>3</sub>构成)可以被可选地布置在该钝化层上(框408)。该第二栅极电介质层也可以被沉积在该源极欧姆接触点和该漏极欧姆接触点之上。在一个实施方案中,该第二栅极电介质层在300°C使用ALD被沉积在晶圆表面上。该第二栅极电介质层可以被生长到近似10-20nm范围内的厚度。

[0081] 在一个实施方案中,该第二栅极电介质层的形成的沉积,可以是与该第一活性层和该第二活性层以及该钝化/第一栅极电介质层非原位执行的。例如,该钝化/第一和第二栅极电介质层可以使用相同的ALD腔或者其他机器或系统被沉积在晶圆表面上。

[0082] 在已经沉积该第二栅极电介质层之后可以执行高温退火(框410),以改善该第二栅极电介质层的膜和界面品质。例如,该退火步骤可以在炉子中在450-750°C的温度范围被执行长达近似5-10分钟。也可以使用若干不同工具(诸如快速温度退火(RTA)工具)来执行退火。应意识到,框408和框410被认为是可选的,因为这些框应用到图2和图3中示出的HFET器件(例示了第二栅极电介质层)。

[0083] 在退火之后,可以可选地在该第二栅极电介质层之上沉积上钝化层(框412)。在一个实施方案中,该上钝化层可以使用PECVD被沉积。该上钝化层也可以使用LPCVD被沉积。该上钝化层典型地被形成到在近似100-150nm范围内的厚度。如上文讨论的,该上钝化层可以包括氮化硅(SiN)或具有相似性质的其他材料。

[0084] 栅极通孔形成,在框314中被示出。这个步骤可选地当上钝化层已经被形成在多个栅极电介质层的堆叠之上时被执行。栅极通孔形成包括对该上钝化层进行掩模和蚀刻,以使得穿过该上钝化层形成开口,由此曝露下面的第二栅极电介质层。在一个实施方案中,可以用气体(诸如CF<sub>4</sub>或SF<sub>6</sub>)利用干蚀刻,以蚀刻穿过该上钝化层。在该蚀刻处理曝露该第二栅极电介质层之后,栅极金属或金属合金沉积(框316)被执行,以填充所蚀刻的开口。在一个实施例中,NiAu被用作该栅极金属。如图1、图2和图3中示出的,可以通过对该栅极金属进行掩模或蚀刻来形成该栅极的场板部分,以使得顶部部分在该上钝化层之上朝着最远的(漏极)欧姆接触点横向延伸。应意识到,框412和414被认为是可选的,因为这些框应用到图3中示出的HFET器件300(例示了上钝化层)。

[0085] 半导体领域普通技术人员应理解,可以执行其他标准的制造后(post-fabrication)或后道(back-end)处理步骤,包含:在该晶圆的表面上形成金属(例如有图案

的线路或迹线);晶圆背磨(backgrinding),也被称为背研磨(backlapping)或晶圆打薄(wafer thinning);芯粒分离;以及封装。

[0086] 图5是例示了用于构建HFET器件(诸如图2和图3中示出的半导体器件200或300)的另一个示例性处理流程400的图表。图5中示出的处理与参照图4讨论的相同,其中相同编号的步骤与上文描述的相同,除了处理流程500包含插在框502与框504之间的附加的框503。在该AlSiN钝化/第一栅极电介质层的原位生长之后,氮化铝(AlN)被生长在该AlSiN层的顶上(框503)。在一个实施方案中,该AlN层与该AlSiN钝化/第一栅极电介质层以及该第一活性层和该第二活性层原位生长。该AlN层的厚度可以是约1nm厚。在框504和506中的台面隔离蚀刻以及欧姆金属化和退火之后,该AlN层被有效地用作籽晶层,以形成该Al2O3第二栅极电介质层(框508)。

[0087] 上面对所例示的示例性实施方案的描述,包含摘要中的描述,不旨在是穷举性的或限于所公开的精确形式。尽管本文描述的主题的具体实施方案和实施例是为了例示目的,但在不脱离本发明的较宽泛的精神和范围的前提下,多种等同修改是可能的。事实上,应意识到,具体的示例性的厚度、材料类型、温度、电压、时间等等是为了解释目的而提供的,且在根据本发明的教导的其他实施方案和实施例中也可以采用其他值。

100

图1

图3

400

图4

500

图5