(19) 日本国特許庁(JP)

## (12) 特 許 公 報(B2)

(11) 特許番号

特許第6085644号

(P6085644)

(45) 発行日 平成29年2月22日(2017.2.22)

(24) 登録日 平成29年2月3日(2017.2.3)

(51) Int.Cl.

F 1

G02F 1/1368 (2006.01)

G09F 9/30 (2006.01)G02F 1/1368

G09F 9/30 338

請求項の数 2 (全 63 頁)

(21) 出願番号 特願2015-128741 (P2015-128741)

(22) 出願日 平成27年6月26日 (2015.6.26)

(62) 分割の表示 特願2014-95924 (P2014-95924)

の分割

原出願日 平成18年12月13日 (2006.12.13)

(65) 公開番号 特開2015-232713 (P2015-232713A)

(43) 公開日 平成27年12月24日 (2015.12.24)

審査請求日 平成27年7月22日 (2015.7.22)

(31) 優先権主張番号 特願2005-372586 (P2005-372586)

(32) 優先日 平成17年12月26日 (2005.12.26)

(33) 優先権主張国 日本国 (JP)

(73) 特許権者 000153878

株式会社半導体エネルギー研究所

神奈川県厚木市長谷398番地

(72) 発明者 細谷 邦雄

神奈川県厚木市長谷398番地 株式会社

半導体エネルギー研究所内

審査官 佐藤 洋允

最終頁に続く

(54) 【発明の名称】半導体装置

## (57) 【特許請求の範囲】

## 【請求項 1】

ゲート配線と、

補助容量線と、

ゲート絶縁膜を介して、前記ゲート配線と重なる領域を有する半導体層と、

前記半導体層と電気的に接続されたソース配線と、

前記半導体層と電気的に接続されたドレイン電極と、

前記ゲート配線上、前記補助容量線上、前記半導体層上、前記ソース配線上、及び前記

ドレイン電極上の絶縁膜と、

前記絶縁膜上に設けられ、前記ドレイン電極と電気的に接続された画素電極と、 10

補助容量と、を有し、

前記ゲート配線と、前記補助容量線とは、同じ層に設けられ、且つ同じ材料で形成され

ており、

前記補助容量は、前記補助容量線の一部と前記画素電極の一部とが重なる領域に形成さ

れており、

前記絶縁膜は、少なくとも前記半導体層を覆う領域と、前記ソース配線を覆う領域とを

有し、

前記絶縁膜は開口を有し、

前記開口は、前記補助容量と重なる領域を有し、

前記ゲート配線は、Cuを含む第1の層と、Mo、Ti、Ta、W、又はCrを含む第 20

2の層と、を有し、

前記ゲート絶縁膜は、窒化珪素を含むことを特徴とする半導体装置。

**【請求項 2】**

ゲート配線と、

補助容量線と、

ゲート絶縁膜を介して、前記ゲート配線と重なる領域を有する半導体層と、

前記半導体層と電気的に接続されたソース配線と、

前記半導体層と電気的に接続されたドレイン電極と、

前記ゲート配線上、前記補助容量線上、前記半導体層上、前記ソース配線上、及び前記ドレイン電極上の絶縁膜と、

10

前記絶縁膜上に設けられ、前記ドレイン電極と電気的に接続された画素電極と、

補助容量と、を有し、

前記ゲート配線と、前記補助容量線とは、同じ層に設けられ、且つ同じ材料で形成され

ており、

前記補助容量は、前記補助容量線の一部と前記画素電極の一部とが重なる領域に形成さ

れており、

前記絶縁膜は、少なくとも前記半導体層を覆う領域と、前記ソース配線を覆う領域とを

有し、

前記絶縁膜は開口を有し、

前記開口は、前記補助容量と重なる領域を有し、

前記ゲート配線は、Cuを含む第1の層と、Mo、Ti、Ta、W、又はCrを含む第

2の層と、を有し、

20

前記ゲート絶縁膜は、第1の窒化珪素膜と、第2の窒化珪素膜とを有することを特徴と

する半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は、基板に設けられた非晶質半導体膜を用いたボトムゲート型の薄膜トランジスタ(Thin Film Transistor(以下、TFTと略記する))、TFTにより構成された回路、及びTFTにより構成された回路を有する装置、及びその作製方法に関するものである。

30

**【0002】**

特に本発明は、液晶表示装置に代表される電気光学装置、及びそのような電気光学装置を搭載した電子機器に好適に利用できる技術に関する。

**【背景技術】**

**【0003】**

現在、ノート型のパーソナルコンピュータやデスクトップ型のパーソナルコンピュータ用のモニタ、携帯電話、音楽再生装置、テレビ、携帯端末、デジタルスチルカメラ、ビデオカメラ、画像・動画閲覧専用のビューワ等の電子機器に、画像や文字情報を表示するために直視型の液晶表示装置が幅広く用いられている。

40

**【0004】**

特にパッシブ型液晶表示装置に比べ、アクティブマトリクス型液晶表示装置は高精細な画像が得られることから、広く用いられている。

**【0005】**

アクティブマトリクス型液晶表示装置は、表示領域となる画素部において能動素子(例えば薄膜トランジスタ)を個々の画素に対応してマトリクス状に配置して構成している。TFTはスイッチング素子として液晶に印加する電圧を画素毎に制御し所望の画像表示を行っている(特許文献1参照)。

**【0006】**

アクティブマトリクス型液晶表示装置は、フォトリソグラフィ技術により、複数のフォ

50

トマスクを使用して、基板上に TFT、配線、電極、絶縁膜中のコンタクトホール等を形成している。

【0007】

配線や電極を、アルミニウム (Al) やタンゲステン (W)、チタン (Ti) などの金属を用いて形成する場合には、乾式エッチング (ドライエッチング)、湿式エッチング (ウェットエッチング) いずれかのエッチングを行うことにより所望のパターンを形成することができる。

【0008】

また透過型液晶表示装置の画素電極の材料などに用いられる透光性導電膜 (本明細書では「透明導電膜」ともいう) についても、乾式エッチング (ドライエッチング)、湿式エッ 10 チング (ウェットエッチング) いずれかのエッチングを行うことにより所望のパターンを形成することができる。

【0009】

このような透明導電膜として、インジウム錫酸化物 (Indium Tin Oxide (以下「ITO」ともいう))、酸化亜鉛、酸化インジウム酸化亜鉛 (Indium Zinc Oxide (以下「IZO」ともいう)) 等の金属酸化物や半導体酸化物が用いられる。

【0010】

特に、透明導電膜のエッチングについてはウェットエッチングが主流である。

【0011】

しかしながら上記に例示した透明導電膜は、アルミニウム (Al) 等の金属と比較して残渣が生じ易いという欠点がある。従って残渣が発生し最終的に基板上に残渣が残留した場合には、画素電極間で電流リークを引き起こす恐れがある。

【0012】

また上述した透明導電膜と同様に、窒化珪素膜や酸化珪素膜などの絶縁膜においては、ウェットエッチングにより発生する残渣が導電体間の接続部に残留するという欠点がある。そのため接触不良やコンタクト抵抗の増大などを引き起こす恐れがある。

【0013】

また、従来のTFTを用いた液晶表示装置においては、スイッチング機能の核となる半導体膜、或いはTFT全体を汚染物から保護するために、窒化珪素膜や、窒素を含む酸化珪素膜や、酸素を含む窒化珪素膜からなる保護膜 (「パシベーション膜」ともいう) で覆うことで保護している。

【0014】

ここでいう汚染物とは、半導体のスイッチングとしての機能を劣化させる効果をもつ、リチウム (Li) やナトリウム (Na)、カリウム (K) などのアルカリ金属である。

【0015】

ところが、透過型液晶表示装置あるいは半透過型液晶表示装置の場合、この保護膜は TFT の上部だけでなく、バックライトの光を透過させ、表示画像を形成する開口部にも形成される。

【0016】

バックライトの光は開口部においても保護膜を透過するが、保護膜内部で光は反射、屈折や吸収などの影響を受け、最終的な透過光の強度は減少してしまう。このため液晶表示装置の輝度がバックライト光源自体に対し低減した値となってしまう恐れがある。加えて、同様の理由から保護膜を透過した後の光の波長が光源の波長から変化し、実際に表示される色と目的とする色との間にずれが生じてしまう恐れがある。

【0017】

また、従来のアクティブマトリクス型の液晶表示装置は行と列からなるマトリクス状の画素からなり、線順次駆動により走査線 (ゲート配線) を選択し画像を表示領域 (画素部) に表示させる方式をとることが主流である。

【0018】

10

20

30

40

50

各走査信号線は 60 Hz 等の周期で選択されるが、任意の行への書き込みを終了した後、次の周期で書き込みが行われるまでの期間、画素電極の電位を保持するために、各画素に補助容量 (Cs) を設けている。

#### 【0019】

従来の非晶質半導体膜を用いたアクティブマトリクス型の液晶表示装置においては、補助容量の形成方法として、次の二つの方法が考えられる。すなわち、隣接する画素のゲート配線（走査線）もしくはゲート配線と同じ材料及び同じ層に形成した配線を一方の電極とし、画素電極を他方の電極とし、二つの電極との間に、ゲート絶縁膜と保護膜の二層を挟んで補助容量を形成する方法（以下「第1の方法」という）と、ゲート配線とは別に形成され、かつゲート配線と同様の材料及び同じ層に形成された補助容量線を一方の電極とし、画素電極と接続し、ドレイン電極と同様の材料及び同じ層に形成された電極を他方の電極とし、二つの電極との間に、ゲート絶縁膜を挟んで補助容量を形成する方法（以下「第2の方法」という）が挙げられる。10

#### 【0020】

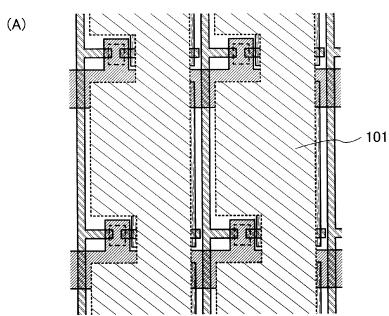

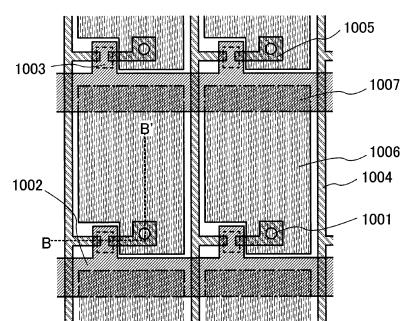

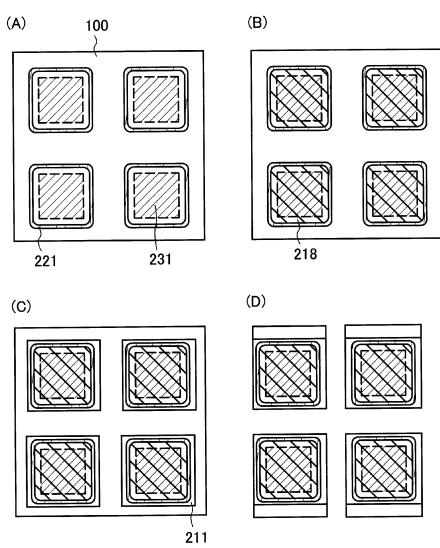

従来のアクティブマトリクス型液晶表示装置の画素の上面図を図2に示す。図2の液晶表示装置は、ゲート電極及びゲート配線（「ゲート配線」を「走査線」ともいう）1002、TFTの半導体膜1003、ソース電極及びソース配線（「ソース配線」を「信号線」ともいう）1004、ドレイン電極1005、画素電極1006、補助容量1007を有している。補助容量1007は、ゲート配線1002、画素電極1006、及びゲート配線1002と画素電極1006の間に形成された絶縁膜（誘電体膜）によって形成されている。20

#### 【0021】

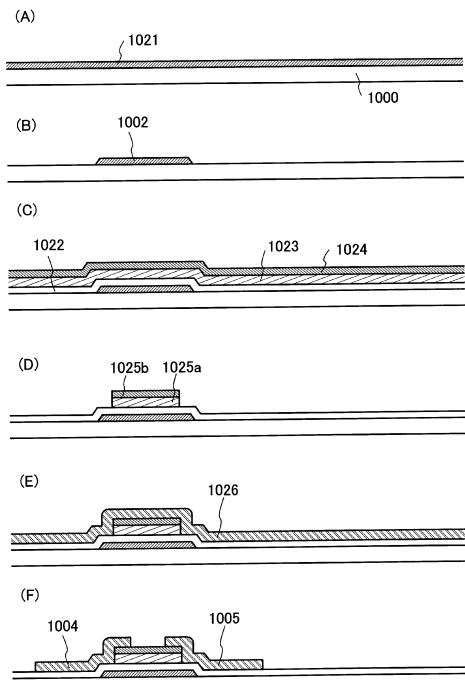

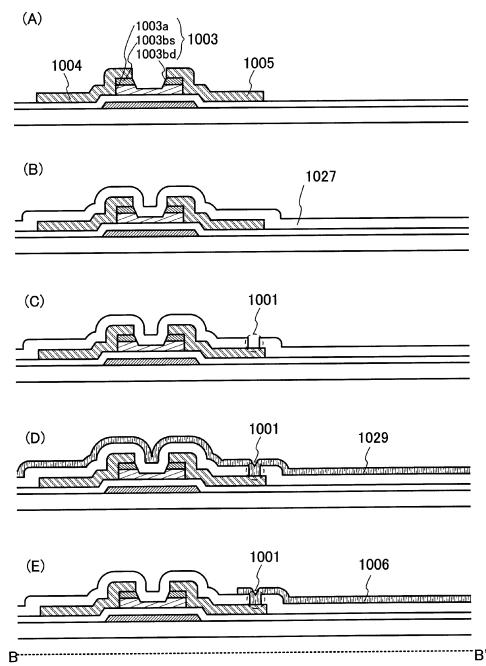

図2に示す従来のアクティブマトリクス型液晶表示装置の作製工程を、図12(A)～図12(F)及び図13(A)～図13(D)を用いて説明する。なお図12(A)～図12(F)及び図13(A)～図13(D)は、図2のB-B'線に沿った断面に対応する。

#### 【0022】

まず基板1000上に第1の導電膜1021を成膜する（図12(A)参照）。次いで第1のフォトリソグラフィ工程を行い、レジストマスクを形成し、第1の導電膜1021の不要な部分をエッティングにより除去して、ゲート電極及びゲート配線1002を形成する（図12(B)参照）。30

#### 【0023】

基板1000、ゲート電極及びゲート配線1002上に、ゲート絶縁膜1022、非晶質半導体膜1023、一導電型を付与する不純物を含む非晶質半導体膜1024を成膜する（図12(C)参照）。次いで第2のフォトリソグラフィ工程を行い、レジストマスクを形成して、非晶質半導体膜1023、一導電型を付与する不純物を含む非晶質半導体膜1024の不要な部分をエッティングにて除去し、島状半導体膜1025aと島状不純物半導体膜1025bを形成する（図12(D)参照）。

#### 【0024】

次いで、ゲート絶縁膜1022、島状半導体膜1025a、島状不純物半導体膜1025b上に、第2の導電膜1026を成膜する（図12(E)参照）。さらに第3のフォトリソグラフィ工程を行い、レジストマスクを形成して、第2の導電膜1026の不要な部分をエッティングして、ソース電極及びソース配線1004、ドレイン電極1005を形成する（図12(F)参照）。40

#### 【0025】

さらにソース電極及びソース配線1004、ドレイン電極1005をマスクとして、島状半導体膜1025aと島状不純物半導体膜1025bを自己整合的にエッティングする。島状不純物半導体膜1025bをソース領域1003b s及びドレイン領域1003b dに分離する。また島状半導体膜1025aもエッティングされ島状半導体膜1003aとなる（図13(A)参照）。

## 【0026】

ソース電極及びソース配線 1004、ドレイン電極 1005、ソース領域 1003b<sub>s</sub> 及びドレイン領域 1003b<sub>d</sub>、及び島状半導体膜 1003a 上に、保護膜 1027 を成膜する（図 13（B）参照）。第 4 のフォトリソグラフィ工程によりレジストマスクを形成し、保護膜 1027 をエッチングして、ドレイン電極 1005 に達するコンタクトホール 1001 を形成する（図 13（C）参照）。

## 【0027】

さらに保護膜 1027 及びコンタクトホール 1001 を覆って、第 3 の導電膜 1029 を成膜する（図 13（D）参照）。第 5 のフォトリソグラフィ工程によりレジストマスクを形成し、第 3 の導電膜 1029 をエッチングして、画素電極 1006 を形成する（図 13（E）参照）。

10

## 【0028】

このように、図 2 に示す従来のアクティブマトリクス型液晶表示装置の画素は、5 回のフォトリソグラフィ工程により、5 枚のフォトマスクを使用して形成される。

## 【0029】

また、補助容量を上記第 1 の方法で形成した例を図 2 及び図 11 に示す。図 2 の液晶表示装置は、隣接する画素のゲート配線（走査線）を一方の電極とし、画素電極を他方の電極とした例である。図 2 において、ゲート電極及びゲート配線 1002、TFT の半導体膜 1003、ソース電極及びソース配線 1004、ドレイン電極 1005、画素電極 1006 である。補助容量 1007 は、ゲート配線 1002、画素電極 1006、及びゲート配線 1002 と画素電極 1006 の間に形成されたゲート絶縁膜と保護膜を誘電体膜として用いることにより形成されている。

20

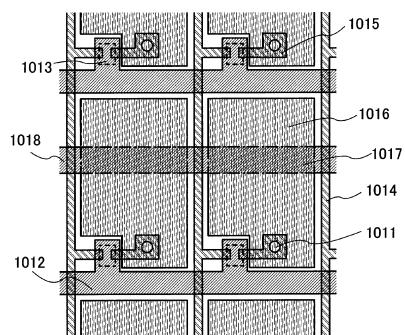

## 【0030】

また図 11 の液晶表示装置は、ゲート配線と同じ材料及び同じ層に形成した配線を一方の電極とし、画素電極を他方の電極とした例である。図 11 において、ゲート電極及びゲート配線 1012、TFT の半導体膜 1013、ソース電極及びソース配線 1014、ドレイン電極 1015、画素電極 1016、補助容量 1017、補助容量線 1018 である。ドレイン電極 1015 と画素電極 1016 はコンタクトホール 1011 で接続されている。補助容量線 1018 は、ゲート電極及びゲート配線 1012 と同様の材料及び同じ層に形成されている。

30

## 【0031】

補助容量 1017 は、補助容量線 1018、画素電極 1016、及び補助容量線 1018 と画素電極 1016 の間に形成されたゲート絶縁膜と保護膜を誘電体膜として用いることにより形成されている。

## 【0032】

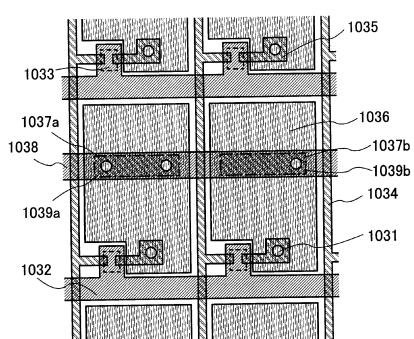

第 2 の方法で補助容量を形成した例は図 50 に示される。図 50 において、ゲート電極及びゲート配線 1032、TFT の半導体膜 1033、ソース電極及びソース配線 1034、ドレイン電極 1035、画素電極 1036、補助容量 1037a 及び 1037b、下層補助容量線 1038、上層補助容量電極 1039a 及び 1039b である。ドレイン電極 1035 はコンタクトホール 1031 を介して画素電極 1036 と接続されている。

40

## 【0033】

上層補助容量電極 1039a は、ソース電極及びソース配線 1034、並びにドレイン電極 1035 と、同じ材料及び同じ層に形成されており、コンタクトホールを介して画素電極 1036 と接続されている。補助容量 1037a は、下層補助容量線 1038 を一方の電極、上層補助容量電極 1039a を他方の電極、ゲート絶縁膜を電極間の誘電体として形成される。

## 【0034】

また上層補助容量電極 1039b も、ソース電極及びソース配線 1034、並びにドレイン電極 1035 と、同じ材料及び同じ層に形成され、コンタクトホールを介して画素電極 1036 と接続されている。補助容量 1037b は、下層補助容量線 1038 を一方の

50

電極、上層補助容量電極 1039b を他方の電極、ゲート絶縁膜を電極間の誘電体として形成される。

【0035】

第2の方法では、二つの電極間の誘電体膜がゲート絶縁膜一層分で良いことから膜厚を薄くできるので容量を増加させることができる。従って第2の方法は、第1の方法に比べ補助容量を形成するのに大きな面積を必要としない。

【0036】

しかし逆に第2の方法では、一方の電極として補助容量線を走査線（ゲート配線）と別に設けるために電極を形成するための面積が必要となり、開口率が低下すること、また他方の電極としてドレイン電極と同様の材料及び同じ層に形成された電極を形成することから、歩留まりの低下が問題となる。

【0037】

これに対し第1の方法では、誘電体膜にゲート絶縁膜と保護膜の二層を用いるため、容量が第2の方法と比較して小さく、そのため電極を形成するためにより大きな面積が必要となる。このため走査線自体を太い配線としなくてはならない、画素電極と走査線との重なり部分を設計上広くとらなければならないなどの問題が起こってしまう。

【0038】

またさらに、図2及び図11に示すように従来のアクティブ型液晶表示装置では、TFTに接続されたソース電極又はドレイン電極と画素電極は、円形のコンタクトホール 1001又は1011を介して接続され、それにより TFTと画素電極とを電気的に接続させている。

【0039】

しかしこのコンタクトホールそのものまたはコンタクトホール近傍の形状が、凹状となって配向膜に凹部が生じてしまうため、理想的なラビングが困難である。このためコンタクトホール上部近辺に位置する液晶は配向乱れを起こしてしまうという欠点がある。このためコンタクトホール上部近辺において光漏れが生じるため、表示の質が損なわれてしまうという問題がある。

【0040】

このような問題を防ぐ方法として、TFTが形成される基板と対向する対向基板側にブラックマトリクスを設け、コンタクトホールとその近傍を遮光するという方法がある。しかしこのことは開口率を低減させる要因の一つになっている。

【0041】

また保護膜は、保護膜材料をドライエッティング方法を用いてエッティングし、所定の形状にすることによって作成される。この時エッティングにより生じた保護膜材料の一部や、保護膜材料とエッティングガス成分との反応生成物等、不要な物質が残渣として被処理面に残留する。例えばこの残渣が画素電極と接続する配線との間に生じた場合、画素電極と配線との間の接触抵抗の原因となったり、あるいは電気的な接触が妨げられる恐れがあり、ひいては液晶表示装置としての機能を著しく損ねたり、機能自体を不可能なものにしてしまう。

【0042】

そのため残渣が残留するのを回避する目的で、フッ酸系の薬液やアルカリ洗浄剤、界面活性剤、純水、あるいはこれらと超音波洗浄との組合せ（以下洗浄剤と呼ぶ）により被処理面を洗浄する。

【0043】

しかし、従来の液晶表示装置の構造では、画素電極とドレイン電極との接触部分に径の小さい円形のコンタクトホールを用いていたが、洗浄後において洗浄剤から被処理面を有する基板を引き上げた際、円形のコンタクトホール内壁や底部に残渣や洗浄液が残留する恐れがあった。

【0044】

またこのような従来の径の小さいコンタクトホールでは、画素電極とドレイン電極が段

10

20

30

40

50

差により断線してしまい、接続不良が起こるという恐れがあった。

【0045】

また、液晶表示装置には、表示装置の背後に設けられたバックライトからの光を透過させ表示を行う透過型液晶表示装置と、外光を基板中に設けられた反射電極で反射させ表示を行う反射型液晶表示装置がある。

【0046】

透過型液晶表示装置は屋内等の暗所でも視認性に優れ、反射型液晶表示装置は屋外の明るい場所で優れる。また携帯電話のように屋内、屋外と場所を選ばず使用される表示装置に対しては、透過型と反射型との機能を併せた半透過型（透過領域と反射領域がほぼ同程度の割合で形成）液晶表示装置や、微反射型（反射領域が透過領域よりも小さい）液晶表示装置がある。10

【先行技術文献】

【特許文献】

【0047】

【特許文献1】特開2002-116712号公報

【発明の概要】

【発明が解決しようとする課題】

【0048】

上記のような液晶表示装置を含む製品を市場に供給するには、生産性の向上及び低コスト化と、高信頼性を同時に推進することが課題となる。20

【課題を解決するための手段】

【0049】

本発明は、アクティブマトリクス型の液晶表示装置に代表される電気光学装置ならびに半導体装置において、上記課題を解決するものであって、その目的とするところは、歩留まりの高い量産工程を可能とし、且つ、輝度の高い、高開口率の液晶表示装置及びその作製方法を提供することにある。

【0050】

本発明では、画素における開口部中の保護膜およびゲート配線上の保護膜を除去することにより、前記課題を解決し上記目的を達成する。

【0051】

本発明は、絶縁性基板と、前記絶縁性基板より上に設けられた薄膜トランジスタ（Thin Film Transistor (TFT)）と、前記絶縁性基板より上に設けられたゲート配線と、前記絶縁性基板より上に設けられたソース配線と、前記絶縁性基板より上に設けられた補助容量と、前記薄膜トランジスタに接続された画素電極と、前記ゲート配線および前記ソース配線とで囲まれた開口部とを有し、前記薄膜トランジスタおよび前記ソース配線は絶縁性材料を含む保護膜に覆われ、前記開口部の一部と前記補助容量は保護膜に覆われていないことを特徴とする半導体装置に関するものである。30

【0052】

なお、本明細書では「ソース配線」及び「ソース線」を「信号線」ともいう。また本明細書では、便宜上薄膜トランジスタの一対の不純物領域をソース領域及びドレイン領域としている。しかしソース領域及びドレイン領域が反転する場合は、それぞれ逆の働きをするのはいうまでもなく、またソース電極及びドレイン電極についても同様である。40

【0053】

TFTのスイッチング機能を行う中核となるのが、半導体膜である。半導体膜にはシリコンを用いることが多い。また半導体膜の結晶状態から液晶表示装置を大きく二つに分類することができる。即ち、半導体膜の結晶状態が非晶質（アモルファス状態）である非晶質半導体膜を用いた液晶表示装置と、結晶質（多結晶状態）である結晶性半導体膜を用いた液晶表示装置である。

【0054】

結晶性半導体膜を用いた液晶表示装置では、半導体膜中のキャリアの移動度が高いなど50

の理由から、表示領域周辺にTFTを用いて駆動回路を一体形成することが可能である。しかしその反面、製造工程の複雑さによる歩留まり低下や、製造コストの増大などが問題となる。

#### 【0055】

また、結晶性半導体膜を作製する場合には、結晶化のためにXeClやKrF等の気体レーザーの一種であるエキシマレーザを線状のレーザビームに加工し、非晶質半導体膜上を走査するのが一般的である。

#### 【0056】

しかし現状では線状レーザビームの長さに限界があるため、コスト低減に有利な大型ガラス基板に対応することができない等の問題がある。

10

#### 【0057】

一方、非晶質半導体膜を用いた液晶表示装置は、結晶性半導体膜を用いた液晶表示装置と比較して、製造工程が簡易であるため、製造コストが安価となるという利点がある。

#### 【0058】

本発明は、基板と、前記基板上に設けられ、チャネル形成領域、ソース領域、ドレイン領域、ゲート絶縁膜と、ゲート電極を有する薄膜トランジスタと、前記ソース領域に接続されるソース配線と、前記ドレイン領域に接続されるドレイン電極と、前記基板上に設けられた補助容量と、前記ドレイン電極に接続される画素電極と、前記薄膜トランジスタ及び前記ソース配線を覆い、前記画素電極の周辺部と重なる保護膜とを有し、前記保護膜は、前記ゲート配線および前記ソース配線とで囲まれた開口部を有し、前記補助容量は前記保護膜に覆われていないことを特徴とする半導体装置に関するものである。

20

#### 【0059】

また本発明は、基板と、前記基板上に設けられ、一対の一導電型の不純物領域とチャネル形成領域を含む薄膜トランジスタと、前記一対の一導電型の不純物領域の一方と電気的に接続する第1の配線と、前記一対の一導電型の不純物領域の他方と電気的に接続する第1の電極と、前記第1の電極と接続する画素電極と、前記基板上に設けられた補助容量と、前記画素電極と前記補助容量上に開口部を有し、前記薄膜トランジスタ及び前記ソース配線を覆う保護膜と、を有することを特徴とする半導体装置に関するものである。

#### 【0060】

また本発明は、基板と、前記基板上に設けられ、ゲート配線と、ゲート絶縁膜と、チャネル形成領域と、ソース領域と、ドレイン領域を有する薄膜トランジスタと、前記ソース領域に接続されたソース配線と、前記基板上に設けられ、前記ドレイン領域に接続されたドレイン電極と、前記基板上に設けられた補助容量と、前記ドレイン電極に接続された画素電極と、前記薄膜トランジスタ及び前記ソース配線上に形成された保護膜と、前記ゲート配線および前記ソース配線とで囲まれた開口部と、前記薄膜トランジスタ、前記画素電極、前記保護膜上に形成された第1の配向膜と、前記基板に対向する対向基板と、前記対向基板上に形成された対向電極と、前記対向電極上に形成された第2の配向膜と、前記基板と前記対向基板との間に保持された液晶とを有し、前記薄膜トランジスタ及び前記ソース配線は保護膜に覆われ、前記開口部の一部と前記補助容量は前記保護膜に覆われていないことを特徴とする半導体装置に関するものである。

30

#### 【0061】

又本発明は、基板と、前記基板上に設けられ、ゲート配線と、ゲート絶縁膜と、チャネル形成領域と、ソース領域と、ドレイン領域を有する薄膜トランジスタと、前記基板上に設けられ、前記ソース領域に接続されたソース配線と、前記基板上に設けられ、前記ドレイン領域に接続されたドレイン電極と、前記基板上に設けられた補助容量と、前記ドレイン電極に接続された画素電極と、前記薄膜トランジスタ及び前記ソース配線上に形成された保護膜と、前記ゲート配線および前記ソース配線とで囲まれた開口部を有し、前記薄膜トランジスタ及び前記ソース配線は保護膜に覆われ、前記開口部の一部と前記補助容量は前記保護膜に覆われておらず、前記画素電極は透明電極であり、前記画素電極の一部に重なって、反射電極が形成されていることを特徴とする半導体装置に関するものある。

40

50

**【 0 0 6 2 】**

本発明において、前記反射電極は、アルミニウム（A1）、銀（Ag）、クロム（Cr）のいずれか1つを含んでもよい。

**【 0 0 6 3 】**

また本発明は、基板と、前記基板上に設けられ、ゲート配線と、ゲート絶縁膜と、チャネル形成領域と、ソース領域と、ドレイン領域を有する薄膜トランジスタと、前記基板上に設けられ、前記ソース領域に接続されたソース配線と、前記基板上に設けられ、前記ドレイン領域に接続されたドレイン電極と、前記基板上に設けられた補助容量と、前記ドレイン電極に接続された画素電極と、前記薄膜トランジスタ及び前記ソース配線上に形成された保護膜と、前記ゲート配線および前記ソース配線とで囲まれた開口部と、前記基板上に形成され、前記ゲート配線と同じ材料及び同じ層に形成されたコモン配線と、前記基板上に形成され、前記画素電極と同じ材料及び同じ層に形成され、前記コモン配線に接続された、複数のコモン電極と、前記基板に対向する対向基板と、前記基板と前記対向基板との間に保持された液晶とを有し、前記薄膜トランジスタ及び前記ソース配線は保護膜に覆われ、前記開口部の一部と前記補助容量は前記保護膜に覆われていないことを特徴とする半導体装置に関するものである。 10

**【 0 0 6 4 】**

また本発明は、基板と、前記基板上に設けられた薄膜トランジスタと、前記薄膜トランジスタは、ゲート配線と、ゲート絶縁膜と、チャネル形成領域と、ソース領域と、ドレイン領域を有し、前記基板上に設けられ、前記ソース領域に接続されたソース配線と、前記基板上に設けられ、前記ドレイン領域に接続されたドレイン電極と、前記基板上に設けられた補助容量と、前記ドレイン電極に接続された画素電極と、前記薄膜トランジスタ及び前記ソース配線上に形成された保護膜と、前記ゲート配線および前記ソース配線とで囲まれた開口部と、前記画素電極に設けられた複数の溝と、前記薄膜トランジスタ、前記画素電極、前記保護膜上に形成された第1の配向膜と、前記基板に対向する対向基板と、前記対向基板上に形成された対向電極と、前記対向電極上に設けられた複数の突起と、前記対向電極及び前記複数の突起上に形成された第2の配向膜と、前記基板と前記対向基板との間に保持された液晶とを有し、前記薄膜トランジスタ及び前記ソース配線は保護膜に覆われ、前記開口部の一部と前記補助容量は前記保護膜に覆われていないことを特徴とする半導体装置に関するものである。 20

**【 0 0 6 5 】**

また本発明は、基板と、前記基板上に設けられ、ゲート配線と、ゲート絶縁膜と、チャネル形成領域と、ソース領域と、ドレイン領域を有する薄膜トランジスタと、前記基板上に設けられ、前記ソース領域に接続されたソース配線と、前記基板上に設けられ、前記ドレイン領域に接続されたドレイン電極と、前記基板上に設けられた補助容量と、前記ドレイン電極に接続された画素電極と、前記薄膜トランジスタ及び前記ソース配線上に形成された保護膜と、前記ゲート配線および前記ソース配線とで囲まれた開口部と、前記画素電極に設けられた複数の第1の溝と、前記薄膜トランジスタ、前記画素電極、前記保護膜上に形成された第1の配向膜と、前記基板に対向する対向基板と、前記対向基板上に形成された対向電極と、前記対向電極に設けられた複数の第2の溝と、前記対向電極及び前記複数の溝上に形成された第2の配向膜と、前記基板と前記対向基板との間に保持された液晶とを有し、前記薄膜トランジスタ及び前記ソース配線は保護膜に覆われ、前記開口部の一部と前記補助容量は前記保護膜に覆われておらず、前記第1の溝と前記第2の溝は重ならないように配置されることを特徴とする半導体装置に関するものである。 40

**【 0 0 6 6 】**

また本発明は、基板と、前記基板上に設けられ、第1のゲート配線と、ゲート絶縁膜と、第1のチャネル形成領域と、第1のソース領域と、第1のドレイン領域を有する第1の薄膜トランジスタ、及び第2のゲート配線と、前記ゲート絶縁膜と、第2のチャネル形成領域と、第2のソース領域と、第2のドレイン領域を有する第2の薄膜トランジスタと、前記基板上に設けられ、前記第1のソース領域及び前記第2のソース領域と接続されたソ 50

ース配線と、前記基板上に設けられ、前記第1のドレイン領域に接続された第1のドレイン電極と、前記基板上に設けられ、前記第2のドレイン領域に接続された第2のドレイン電極と、前記基板上に設けられた補助容量と、前記第1のドレイン電極に接続された第1の画素電極と、前記第2のドレイン電極に接続された第2の画素電極と、前記第1のゲート配線及び第2のゲート配線と同じ材料及び同じ層に形成された補助容量線と、前記第1の画素電極の一部と前記補助容量線が重なる領域に、第1の補助容量が形成され、前記第2の画素電極の一部と前記補助容量線が重なる領域に、第2の補助容量が形成され、前記第1の薄膜トランジスタ、前記第2の薄膜トランジスタ及び前記ソース配線上に形成された保護膜と、前記第1のゲート配線、前記第2のゲート配線および前記ソース配線とで囲まれた開口部と、前記第1の薄膜トランジスタ、前記第2の薄膜トランジスタ及び前記ソース配線は前記保護膜に覆われ、前記開口部の一部、前記第1の補助容量及び前記第2の補助容量は、前記保護膜に覆われておらず、前記第1の薄膜トランジスタ、前記第2の薄膜トランジスタ、前記第1の画素電極、前記第2の画素電極及び前記保護膜上に形成された第1の配向膜と、前記基板に対向する対向基板と、前記対向基板上に形成された対向電極と、前記対向電極上に形成された第2の配向膜と、前記基板と前記対向基板との間に保持された液晶とを有することを特徴とする半導体装置に関するものである。

10

#### 【0067】

本発明において、前記第1の画素電極と前記第2の画素電極の面積が同じであるものである。

#### 【0068】

本発明において、前記第1の画素電極と前記第2の画素電極の面積が異なるものである。

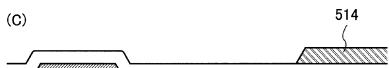

20

#### 【0069】

本発明は、基板上にゲート配線を形成し、前記ゲート配線上にゲート絶縁膜を形成し、前記ゲート配線上に、前記ゲート絶縁膜を介して、島状半導体膜及び島状不純物半導体膜を形成し、前記ゲート絶縁膜、前記島状半導体膜、前記島状不純物半導体膜上に、ソース配線及びドレイン電極を形成し、前記ソース配線及び前記ドレイン電極をマスクとして、前記島状半導体膜及び前記島状不純物半導体膜をエッチングして、前記島状不純物半導体膜からソース領域及びドレイン領域を、前記島状半導体膜からチャネル形成領域を形成し、前記ソース配線、前記ドレイン電極、前記ソース領域、前記ドレイン領域及び前記チャネル形成領域上に絶縁膜を形成し、前記絶縁膜の一部を除去して、前記ドレイン電極の一部の領域を露出させ、前記ドレイン電極の露出した領域に接して、画素電極を形成し、前記ソース配線、前記ソース領域、前記ドレイン領域及び前記チャネル形成領域上の絶縁膜は除去されず、前記除去されない絶縁膜は保護膜として機能することを特徴とする半導体装置の作製方法に関するものである。

30

#### 【0070】

本発明において、前記薄膜トランジスタは、ボトムゲート型薄膜トランジスタである。

#### 【0071】

本発明において、前記薄膜トランジスタは、逆スタガ型薄膜トランジスタである。

40

#### 【0072】

本発明において、前記ソース領域、ドレイン領域及びチャネル形成領域のそれぞれは、非晶質半導体膜を用いて形成されているものである。

#### 【0073】

本発明において、前記ドレイン電極は、上層ドレイン電極と下層ドレイン電極を有し、前記開口部において、前記上層ドレイン電極は除去されており、前記画素電極は、前記下層ドレイン電極のみに接するものである。

#### 【0074】

本発明において、前記ドレイン電極は、上層ドレイン電極、中層ドレイン電極及び下層ドレイン電極を有し、前記画素電極は、前記上層ドレイン電極のみに接するものである。

50

#### 【0075】

本発明において、前記ゲート配線の一部と、前記ゲート絶縁膜と、前記画素電極の一部により、補助容量が形成されているものである。

【0076】

本発明において、前記補助容量は、前記ゲート配線と同一材料で形成された補助容量線と、前記ゲート絶縁膜と、前記画素電極と電気的に接続するドレイン電極と同一材料で形成された導電膜の一部とにより形成されているものである。

【0077】

本発明において、前記島状半導体膜及び島状不純物半導体膜のそれぞれは、非晶質半導体膜を用いて形成されているものである。

【0078】

本発明において、前記画素電極は透明電極であり、前記画素電極の一部に重なって、反射電極が形成されているものである。

10

【0079】

本発明において、前記反射電極は、アルミニウム(A1)、銀(Ag)、クロム(Cr)のいずれか1つを有するものである。

【0080】

本発明において、前記保護膜は、窒化珪素膜、酸素を含む窒化珪素膜、窒素を含む酸化珪素膜、酸化珪素膜、またはこれらを組み合わせた積層膜のうちの1つである。

【0081】

本発明において、前記基板は、絶縁性基板である。

20

【0082】

本発明において、前記基板は、ガラス基板又は石英基板である。

【0083】

本発明において、前記画素電極は、酸化インジウム、インジウム錫酸化物、酸化インジウム酸化亜鉛合金のいずれか1つを有するものである。

【0084】

本発明において、前記保護膜と前記ゲート絶縁膜の材料は異なっていても良い。

【0085】

本発明において、前記開口部は、隣の開口部とソース配線に沿って連なっているものである。

30

【0086】

本発明において、前記半導体装置は、テレビ受像器、携帯電話、液晶ディスプレイ、コンピュータ、ゲーム機、画像再生装置、ビデオカメラ、ナビゲーションシステム、音楽再生装置及びデジタルスチルカメラのうちの1つである。

【0087】

なお本明細書において、半導体装置とは、半導体を利用することで機能する素子及び装置全般を指し、上記液晶表示装置を含む電気光学装置およびその電気光学装置を搭載した電子機器をその範疇とする。

【0088】

また、本明細書において、透明導電膜、透明電極、透明導電材料、透明な電極というのは、それぞれ、透光性を有している導電膜、透光性を有している電極、透光性を有している導電材料、透光性を有している電極であればよく、多少曇っていたり、色が付いていたりしても構わない。光を通すのに十分な透明度を有していれば、本明細書では透明であるとみなすこととする。

40

【発明の効果】

【0089】

本発明では、保護膜を開口部になるべく重ならないように形成することで開口部を増大させ、また開口部をソース配線に平行に列方向に延在させることにより、保護膜形成のための絶縁膜のエッチングの際に発生する残渣を低減し、残渣に由来する画素電極とドレン電極とのコンタクト不良を抑制することができる。

50

**【0090】**

また同様に、画素電極形成に用いる透明導電材料のエッチングの際に発生する残渣を低減し、残渣に由来するリーク電流や導通を低減することができる。

**【0091】**

また本発明により、従来生じていた保護膜のコンタクトホール形状に起因するコンタクトホール上部近傍における液晶の配向乱れ（「ディスクリネーション」ともいう）を無くすことができる。

**【0092】**

さらに本発明により、画素電極とドレイン電極との接触面積を増大させることにより、コンタクト抵抗を低減することができる。

10

**【0093】**

また、開口部の全域では保護膜が除去されており、開口部において光源からの光の透過率が向上する。

**【0094】**

また本発明では、フォトマスクの数を従来より増やさないことができ、作製工程や製造コストを増加させることなく、品質の良い液晶表示装置を作製することが可能となる。

**【0095】**

以上本発明により、信頼性・歩留まりの高く、高輝度、開口率の液晶表示装置が提供できる。

**【図面の簡単な説明】**

20

**【0096】**

【図1】本発明の液晶表示装置における画素の上面図。

【図2】従来の液晶表示装置における画素の上面図。

【図3】本発明の液晶表示装置における画素の上面図。

【図4】本発明の液晶表示装置の作製方法を示す上面図。

【図5】本発明の液晶表示装置の作製方法を示す上面図。

【図6】本発明の液晶表示装置の作製方法を示す上面図。

【図7】本発明の液晶表示装置の作製方法を示す断面図。

【図8】本発明の液晶表示装置の断面図。

【図9】本発明の液晶表示装置の上面図。

30

【図10】本発明の液晶表示装置の作製方法を示す上面図。

【図11】従来の液晶表示装置における画素の上面図。

【図12】従来の液晶表示装置の作製方法を示す断面図。

【図13】従来の液晶表示装置の作製方法を示す断面図。

【図14】本発明の液晶表示装置の作製方法を示す断面図。

【図15】本発明の液晶表示装置の作製方法を示す断面図。

【図16】本発明の液晶表示装置の作製方法を示す断面図。

【図17】本発明の液晶表示装置の作製方法を示す断面図。

【図18】本発明の液晶表示装置の作製方法を示す上面図。

【図19】本発明の液晶表示装置の作製方法を示す上面図。

40

【図20】本発明の液晶表示装置の作製方法を示す断面図。

【図21】本発明の液晶表示装置の作製方法を示す断面図。

【図22】本発明の液晶表示装置の作製方法を示す上面図。

【図23】本発明の液晶表示装置の作製方法を示す上面図。

【図24】本発明の液晶表示装置の作製方法を示す断面図。

【図25】本発明の液晶表示装置の作製方法を示す断面図。

【図26】本発明の液晶表示装置の作製方法を示す断面図。

【図27】本発明の液晶表示装置の作製方法を示す上面図。

【図28】本発明の液晶表示装置における画素の上面図。

【図29】本発明の液晶表示装置の作製方法を示す断面図。

50

- 【図30】本発明の液晶表示装置における画素の上面図。

- 【図31】本発明の液晶表示装置の作製方法を示す断面図。

- 【図32】本発明の液晶表示装置の液晶分子の動きを表す図。

- 【図33】本発明の液晶表示装置における画素の上面図。

- 【図34】本発明の液晶表示装置の作製方法を示す断面図。

- 【図35】本発明の液晶表示装置の液晶分子の動きを表す図。

- 【図36】本発明の液晶表示装置における画素の上面図。

- 【図37】本発明の液晶表示装置の作製方法を示す断面図。

- 【図38】本発明の液晶表示装置の作製方法を示す断面図。

- 【図39】本発明の液晶滴下方法を用いた液晶表示装置の作製工程を示す図。 10

- 【図40】本発明の液晶滴下方法を用いた液晶表示装置の作製工程を示す図。

- 【図41】本発明の液晶滴下方法を用いた液晶表示装置の作製工程を示す図。

- 【図42】本発明の液晶滴下方法を用いた液晶表示装置の作製工程を示す図。

- 【図43】本発明が適用される電子機器の例を示す図。

- 【図44】本発明が適用される電子機器の例を示す図。

- 【図45】本発明が適用される電子機器の例を示す図。

- 【図46】本発明が適用される電子機器の例を示す図。

- 【図47】本発明が適用される電子機器の例を示す図。

- 【図48】本発明が適用される電子機器の例を示す図。

- 【図49】本発明が適用される電子機器の例を示す図。 20

- 【図50】従来の液晶表示装置における画素の上面図。

**【発明を実施するための形態】**

**【0097】**

本実施の形態では、本発明の液晶表示装置及びその作製方法について、図1(A)～図1(B)、図3、図4(A)～図4(B)、図5(A)～図5(B)、図6(A)～図6(B)、図7(A)～図7(F)、図8、図9、図10(A)～図10(D)を用いて説明する。

**【0098】**

ただし、本発明は多くの異なる態様で実施することが可能であり、本発明の主旨及びその範囲から逸脱することなくその形態及び詳細を変更することは可能である。従って、本実施の形態の記載内容に限定して解釈されるものではない。 30

**【0099】**

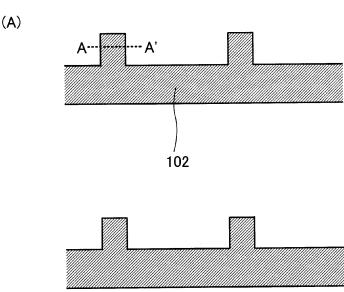

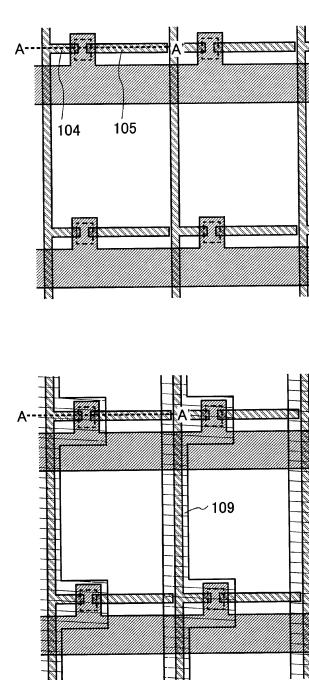

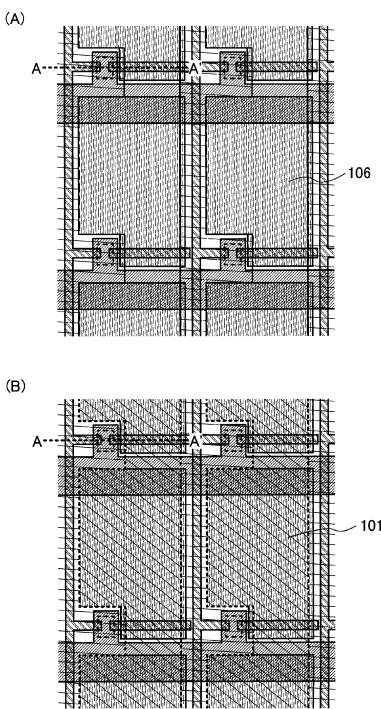

本実施の形態の液晶表示装置について、基板上に形成された透過型の画素部の概要を図1(A)～図1(B)及び図3に示す。画素部には複数の画素が形成されており、各画素には能動素子である画素TFTが形成される。図3は画素の実際の上面図であり、図1(B)は図3から保護膜109を除いたものである。そして図1(A)は開口部101の位置を明確に記載したものである。

**【0100】**

本実施の形態では、画素TFT201として、ボトムゲート型TFT、例えば逆スタガ型TFTが形成される。画素TFT201は、ゲート電極102、島状半導体膜103、ソース電極104、ドレイン電極105を有している。また画素TFT201に接続する補助容量(保持容量ともいう)107、画素電極106とドレイン電極105を接続するコンタクトホールでもある開口部101が形成されている。 40

**【0101】**

開口部101は、ゲート電極及びゲート配線102、並びに、ソース電極及びソース配線104で囲まれた領域に設けられる。

**【0102】**

ここで図4(A)～図4(B)、図5(A)～図5(B)、図6(A)～図6(B)は本実施の形態の液晶表示装置の画素の作製工程の過程を示す上面図である。また、図4(A)、図4(B)、図5(A)、図5(B)、図6(A)、図6(B)において、それぞ 50

れ A - A' 線に沿った断面図を、図 7 (A)、図 7 (B)、図 7 (C)、図 7 (D)、図 7 (E)、図 7 (F) に示す。

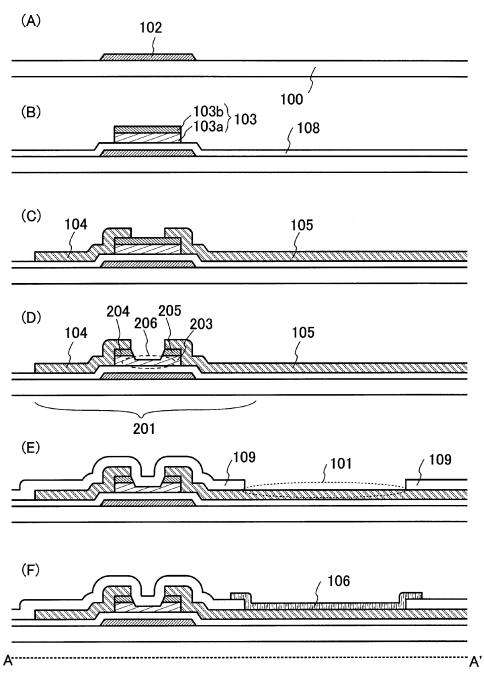

#### 【0103】

上面図である図 4 (A) 及びその断面図である図 7 (A) に示すように、基板 100 上にゲート電極及びゲート配線 102 が形成される。基板 100 は絶縁性基板を用い、例えば基板 100 として、コーニング社の 7059 や 1737、EAGLE 2000 などに代表されるバリウムホウケイ酸ガラス、アルミニノホウケイ酸ガラス、アルミニノシリケートガラスなどの透光性のガラス基板を用いることができる。その他に透光性を有する石英基板などを使用しても良い。

#### 【0104】

ゲート電極およびゲート配線 (走査線) 102 は、アルミニウム (Al)、などの低抵抗導電性材料で形成することが望ましいが、アルミニウム単体では耐熱性が劣り、また腐食しやすい等の問題があることから耐熱性導電性材料と組み合わせて積層膜を形成することが望ましい。

#### 【0105】

耐熱性導電性材料としては、モリブデン (Mo)、チタン (Ti)、タンタル (Ta)、タンゲステン (W)、クロム (Cr) から選ばれた元素、または前記元素を成分とする合金膜、または前記元素を成分とする窒化物で形成する。或いは、このような耐熱性導電性材料をのみを組み合わせて用いても良い。

#### 【0106】

またアルミニウムは純アルミニウムの他に、0.01 ~ 5 atomic % のスカンジウム (Sc)、チタン (Ti)、シリコン (Si)、銅 (Cu)、クロム (Cr)、ネオジム (Nd)、モリブデン (Mo) 等を含有するアルミニウムを使用してもよい。アルミニウムよりも質量の重い原子を添加することで、熱処理時のアルミニウム原子の移動を制限しヒロックを発生するのを防ぐ効果がある。

#### 【0107】

上記のアルミニウムと耐熱性導電性材料との組合せの例として、クロム (Cr) を含む膜及びアルミニウム (Al) を含む膜の積層膜、クロム (Cr) を含む膜及びネオジムを含有するアルミニウム (Al-Nd) を含む膜との積層膜、チタン (Ti) を含む膜、アルミニウム (Al) を含む膜及びチタン (Ti) を含む膜の積層膜、チタン (Ti) を含む膜、ネオジムを含有するアルミニウム (Al-Nd) を含む膜及びチタン (Ti) を含む膜の積層膜、モリブデン (Mo) を含む膜、アルミニウム (Al) を含む膜及びモリブデン (Mo) を含む膜の積層膜、モリブデン (Mo) を含む膜、ネオジムを含有するアルミニウム (Al-Nd) を含む膜及びモリブデン (Mo) を含む膜の積層膜、モリブデン (Mo) を含む膜及びアルミニウム (Al) を含む膜の積層膜、モリブデン (Mo) を含む膜及びネオジムを含有するアルミニウム (Al-Nd) を含む膜の積層膜などを用いることができる。

#### 【0108】

上述のように積層膜をスパッタにより基板 100 全面に成膜し、第 1 のフォトリソグラフィ工程を行い、第 1 のレジストマスクを形成し、エッチングにより不要な部分を除去して、ゲート電極及びゲート配線 102 を形成する。

#### 【0109】

この際図 7 (A) に示すように、ゲート電極 102 の端部がテーパー状に形成されるようエッチングする。テーパー状のゲート電極 102 を設けることで、ゲート電極 102 端部においてゲート絶縁膜 108 の被覆性を向上させ、ゲート絶縁膜 108 の耐圧を上げることができる。またテーパー状のゲート電極 102 を設けることにより、ゲート電極 102 により島状半導体膜 103 に印加される電界を緩和する効果がある。

#### 【0110】

ゲート電極及びゲート配線 102 の膜厚は、好ましくは 40 ~ 400 nm とする。ただし液晶表示装置の基板サイズや配線として使用する材質によって決定されるものであり、

10

20

30

40

50

必要に応じて膜厚を変えることはできるのはもちろんである。

**【0111】**

こうして、ゲート電極およびゲート配線（走査線）102を形成した後、ゲート絶縁膜108を形成する。ゲート絶縁膜108はプラズマCVD法またはスパッタ法を用い、350～450nmの膜厚で形成する。ゲート絶縁膜108は窒化珪素膜、酸化珪素膜、酸素を含む窒化珪素膜、窒素を含む酸化珪素膜などの絶縁膜を用い、これらの材料からなる単層又は積層構造として形成しても良い。

**【0112】**

例えはゲート絶縁膜108として、窒化珪素膜200nm積層した後、さらに窒化珪素膜200nmを積層してもよい。窒化珪素膜を二層成膜してゲート絶縁膜108を形成すると、下層の窒化珪素膜の成膜中にピンホールが生じても、上層の窒化珪素膜を成膜することでピンホールの成長を途切れさせ、これによりTFTの絶縁耐圧を向上させることができるという効果を得られる。10

**【0113】**

また窒化珪素膜二層でゲート絶縁膜108を成膜することにより、CVD等の装置内壁に生じる不要生成物からなるフリーエクが、ゲート絶縁膜108そのものやその他の膜の成膜中に混入してくるのを防ぐという効果も得られる。

**【0114】**

さらに生成ガスの組成比等の成膜条件を変えることにより、ゲート絶縁膜108の上部と下部で接する膜、例えはゲート絶縁膜108と上部で接する非晶質半導体膜、と密着性等の相性の良い膜質を選択できるなどの効果がある。20

**【0115】**

また後述するが、後の工程で行われる保護膜（パシベーション膜）109のエッチング時に、ゲート絶縁膜108のエッチングを防ぐため、ゲート絶縁膜108として緻密な膜質となるように絶縁膜を成膜して、保護膜109のエッチングストップとなるようにしても良い。

**【0116】**

またゲート絶縁膜108として上述した窒化珪素膜を選択した場合、ガラス基板に含まれるリチウム(Li)やナトリウム(Na)、カリウム(K)などのアルカリ金属の進入を妨げることができる。またゲート絶縁膜108に酸化珪素膜と窒化珪素膜の積層膜や、酸素を含む窒化珪素膜、窒素を含む酸化珪素膜を用いた場合にも同様の効果がある。特にこれら膜中に弗素(F)等のハロゲン元素が含有される場合には、Fによりアルカリ金属が固定され可動性を失わせることが可能である。30

**【0117】**

次に、ゲート絶縁膜108上に100～200nmの厚さで非晶質構造を有する非晶質半導体膜を、プラズマCVD法やスパッタ法などの方法で基板全面に形成する。

**【0118】**

非晶質構造は電子線回折分析によって確認できる。代表的には、プラズマCVD法で水素化非晶質珪素膜(a-Si:H膜)を100nmの厚さに形成する。その他、非晶質を有する半導体膜には、非晶質シリコンゲルマニウム(Si<sub>x</sub>Ge<sub>y</sub>)膜などの非晶質構造を有する半導体膜を適用することもできる。40

**【0119】**

また非晶質半導体膜の代わりに微結晶半導体膜（セミアモルファス半導体膜）を成膜してもよい。セミアモルファスシリコン膜に代表されるセミアモルファス半導体膜とは、非晶質半導体と結晶構造を有する半導体（単結晶、多結晶を含む）の中間的な構造の半導体（セミアモルファス半導体）を含む膜である。セミアモルファス半導体は、自由エネルギー的に安定な第3の状態を有する半導体であって、短距離秩序を持ち格子歪みを有する結晶質なものであり、その粒径を0.5～20nmとして非単結晶半導体中に分散させて存在せしめることが可能である。セミアモルファス半導体は、そのラマンスペクトルが520cm<sup>-1</sup>よりも低波数側にシフトしており、またX線回折ではSi結晶格子に由来する50

とされる(111)、(220)の回折ピークが観測される。また、未結合手(ダングリングボンド)の終端化するために、水素またはハロゲンを少なくとも1原子%またはそれ以上含ませている。ここでは便宜上、このような半導体をセミアモルファス半導体(SAS)と呼ぶ。さらに、ヘリウム、アルゴン、クリプトン、ネオンなどの希ガス元素を含ませて格子歪みをさらに助長させることで安定性が増し良好なセミアモルファス半導体が得られる。

#### 【0120】

またSASは珪素を含む気体をグロー放電分解することにより得ることができる。代表的な珪素を含む気体としては、SiH<sub>4</sub>であり、その他にもSi<sub>2</sub>H<sub>6</sub>、SiH<sub>2</sub>C<sub>1</sub><sub>2</sub>、SiHC<sub>1</sub><sub>3</sub>、SiC<sub>1</sub><sub>4</sub>、SiF<sub>4</sub>などを用いることができる。また水素や、水素にヘリウム、アルゴン、クリプトン、ネオンから選ばれた一種または複数種の希ガス元素を加えたガスで、この珪素を含む気体を希釈して用いることで、SASの形成を容易なものとすることができます。希釈率は2倍～1000倍の範囲で珪素を含む気体を希釈することが好み。

#### 【0121】

さらに一導電型を付与する不純物元素を含有する半導体膜として、n型半導体膜を20～80nmの厚さで成膜する。例えば、n型の水素化非晶質珪素膜を形成すればよい。n型の水素化非晶質珪素膜を形成するには、シラン(SiH<sub>4</sub>)に対して0.1～5%の濃度でフォスフィン(PH<sub>3</sub>)を添加すればよい。これによりリン(P)が水素化非晶質珪素膜中に含有される。

#### 【0122】

また一導電型を付与する不純物を含有する半導体膜として、p型半導体膜を用いる場合には、シラン(SiH<sub>4</sub>)に対してジボラン(B<sub>2</sub>H<sub>6</sub>)を添加すれば、p型の不純物元素であるホウ素(B)を含有する水素化非晶質珪素膜を得ることが可能である。

#### 【0123】

上述のゲート絶縁膜、非晶質半導体膜、一導電型の不純物元素を含有する半導体膜はいずれもプラズマCVDや、スパッタ法で作製することができる。そしてこれらの膜はプラズマCVD法であれば反応ガスを適宜切り換えることにより、またスパッタ法であればスパッタガスを適宜切り換えることにより連続して成膜することができる。

#### 【0124】

即ち、プラズマCVD装置或いはスパッタ装置において、同一の反応室または複数の反応室(いわゆるマルチチャンバ)を用いることで、これらの膜を大気に晒すことなく連続して積層することもできる。連続成膜を利用することで、大気に晒されないため、汚染源が混入する可能性が著しく低減される他、作製工程にかかる時間を短縮するなどの大きな効果を有する。

#### 【0125】

そして、このように積層して半導体膜を形成し、第2のフォトリソグラフィ工程によって第2のレジストマスクを形成し、上面図図4(B)及び断面図図7(B)に示すようにゲート電極102に重なるように島状半導体膜103を形成する。島状半導体膜103は、図7(B)に示すように、島状非晶質半導体膜103aと島状不純物半導体膜103bであるn型の島状半導体膜との積層で構成されている。

#### 【0126】

次に、導電膜をスパッタ法や真空蒸着法、MOCVD法(有機金属気相成長法)等で形成し、第3のフォトリソグラフィ工程により第3のレジストマスクを形成し、エッチング処理を施し、図7(C)に示すようにソース電極及びソース配線(「ソース配線」を「データ信号線」または「信号線」ともいう)104、ドレイン電極105を形成する。

#### 【0127】

本実施の形態ではソース電極及びソース配線104およびドレイン電極105を形成するための導電膜として金属膜を用いる。具体的にはソース電極及びソース配線104およびドレイン電極105を、モリブデン(Mo)、アルミニウム(Al)及びモリブデン(

10

20

30

40

50

M<sub>o</sub>)を積層した積層膜を用いて形成する。

**【0128】**

まず、モリブデン(M<sub>o</sub>)膜を20~80nmの厚さで形成し、島状不純物半導体膜103bとオーミック接続を形成し、そのモリブデン(M<sub>o</sub>)膜の上に重ねてアルミニウム(A1)膜を150~300nmの厚さで形成し、さらにその上にモリブデン(M<sub>o</sub>)膜を40~120nmの厚さで形成する。ここで用いられる金属層としては例示するモリブデン、アルミニウム及びモリブデンの積層膜の他に、ゲート電極およびゲート配線102、同様にモリブデン(M<sub>o</sub>)、チタン(Ti)、タンタル(Ta)、タングステン(W)、クロム(Cr)から選ばれた元素を含む膜、または前記元素を成分とする合金を含む膜、または前記元素を成分とする窒化物を含む膜、あるいはクロム(Cr)を含む膜及びアルミニウム(A1)を含む膜の積層膜、クロム(Cr)を含む膜及びネオジムを含有するアルミニウム(A1-Nd)を含む膜との積層膜、チタン(Ti)を含む膜、アルミニウム(A1)を含む膜及びチタン(Ti)を含む膜の積層膜、チタン(Ti)を含む膜、ネオジムを含有するアルミニウム(A1-Nd)を含む膜及びチタン(Ti)を含む膜の積層膜、モリブデン(M<sub>o</sub>)を含む膜、アルミニウム(A1)を含む膜及びモリブデン(M<sub>o</sub>)を含む膜の積層膜、モリブデン(M<sub>o</sub>)を含む膜、ネオジムを含有するアルミニウム(A1-Nd)を含む膜及びモリブデン(M<sub>o</sub>)を含む膜の積層膜、モリブデン(M<sub>o</sub>)を含む膜及びアルミニウム(A1)を含む膜の積層膜、モリブデン(M<sub>o</sub>)を含む膜及びネオジムを含有するアルミニウム(A1-Nd)を含む膜などを用いることができる。10 20

**【0129】**

ソース電極104及びドレイン電極105をマスクとして、上面図図5(A)及び断面図図7(D)に示すように島状非晶質半導体膜103aと島状不純物半導体膜103bの一部をドライエッチングにより除去して、島状不純物半導体膜103bをソース領域204とドレイン領域205に分離する。またこのエッチングにより島状非晶質半導体膜103aは自己整合的にエッチングされ、チャネル形成領域206を有する島状半導体膜203となる。30

**【0130】**

以上のようにして、本実施の形態のボトムゲート型TFT201が形成される。なお、本実施の形態では、チャネルエッチ型のボトムゲート型TFTを作製したが、可能であればチャネルストップ型のボトムゲート型TFTを作製してもよい。30

**【0131】**

その後、島状半導体膜203、ソース領域204、ドレイン領域205、ソース電極及びソース配線104及びドレイン電極105上に、無機材料からなる絶縁膜を形成する。

**【0132】**

無機材料からなる絶縁膜は、窒化珪素膜、酸素を含む窒化珪素膜、窒素を含む酸化珪素膜、酸化珪素膜、またはこれらを組み合わせた積層膜で形成し、厚さは200~450nmとする。本実施の形態では、プラズマCVD法でSiH<sub>4</sub>、NH<sub>3</sub>を原料ガスとして窒化珪素膜を成膜する。

**【0133】**

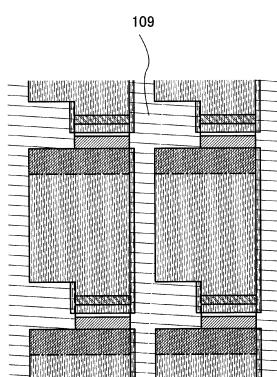

その後、第4のフォトリソグラフィ工程によって、第4のレジストマスクを形成し、無機材料からなる絶縁膜をドライエッチングして保護膜109を形成する(上面図図5(B)及び断面図図7(E))。保護膜109はTFTを覆うが、画素部の開口部101においてはドライエッチング工程により無機材料からなる絶縁膜が除去されているのでドレイン電極等が露出される。40

**【0134】**

保護膜109を形成することで、TFT201を外部の汚染から保護することができる。特に島状半導体膜203、ソース領域204及びドレイン領域205に接して保護膜109を形成することで、スイッチング機能の中核をなす島状半導体膜203へ汚染源が進入することを防ぐことができる。50

## 【0135】

また図5(B)及び図7(E)に示すように、前記ゲート配線102の、保護膜109が形成されず露出した領域には、後に形成される画素電極106の一部とゲート配線102とによって、補助容量107が形成される。また無機材料からなる絶縁膜が除去され、保護膜109が形成されないため、TFT201から延在するドレイン電極の大部分は露出する。

## 【0136】

なお、実施の形態では、第4のフォトリソグラフィ工程において、所定の形状のレジストマスクを形成する際に、ハーフトーン露光技術を用いて段差のあるレジストマスクを形成する。

10

## 【0137】

また、図1及び図5(B)に示すように、開口部101をソース配線104に平行な方向に延在させることにより、前記第4のドライエッチング工程によって生じる保護膜109の残渣および後述する画素電極106を形成する際に生じる透明導電材料の残渣を低減することが可能となる。開口部101がソース配線104に平行な方向に延在させるということは、言い換えると、1つの画素の開口部は隣り合う画素の開口部とソース配線104に沿って隣接しているということである。

## 【0138】

窒化珪素膜に代表される保護膜材料は、前述のとおりドライエッチング方法を用いて所定の箇所をエッチングして除去される。この時エッチングにより生じた保護膜材料の一部や、保護膜材料とエッチングガス成分との反応生成物等、不要な物質が残渣として被処理面に残留する。例えばこの残渣が後に画素電極106と接続する配線上に生じた場合、画素電極106と配線との接触抵抗として機能する、あるいは電気的な接触が妨げられる恐れがあり、ひいては液晶表示装置としての機能を著しく損ねたり、機能自体を不可能なものにしてしまう。

20

## 【0139】

残渣が残留するのを回避するため、フッ酸系の薬液やアルカリ洗浄剤、界面活性剤、純水、あるいはこれらと超音波洗浄との組合せ(以下洗浄剤と呼ぶ)により被処理面を洗浄する。

## 【0140】

30

しかし従来の液晶表示装置の構造では、画素電極とドレイン電極との接触部分に円形のコンタクトホール1001(例えば5~10μm径)を用いていた(図2参照)。このような円形のコンタクトホール1001では、洗浄後において洗浄剤から被処理面を有する基板を引き上げた際、コンタクトホール内壁や底部に残渣や洗浄液が残留する恐れがあった。

## 【0141】

従来のコンタクトホール1001を画素の開口部全体にまで広げることで、残渣の残留を防ぐとともに、洗浄剤から被処理面を有する基板を引き上げる際、信号線に並行な方向に延在する開口部101を洗浄剤の流れ落ちる通路として利用し、特に段差部に残渣が残留することを妨ぐことができる。また上記の洗浄やガスのブロー等の洗浄工程においてもこの通路を利用することができる。

40

## 【0142】

そして、透明導電膜をスパッタ法や真空蒸着法、スプレー法、ディップ法、CVD法で30~120nmの厚さに成膜し、第5のフォトリソグラフィ工程を行い第5のレジストマスクを形成し、上面図図6(A)及び断面図7(F)に示すように、画素電極106を形成する。また図6(B)は図6(A)における開口部101を示すものである。画素電極106は開口部101でドレイン電極105と接続する。

## 【0143】

本発明では、図2に示す従来の液晶表示装置に比べて、コンタクトホール1001をさらに拡大することにより、ドレイン電極105と画素電極106との接続している領域が

50

開口部 101 となる。このためドレン電極 105 と画素電極 106 との接続している領域が飛躍的に増大する。これによって、従来発生していたコンタクト不良が低減する他、接触抵抗が低減するといった効果が得られる。

#### 【 0144 】

透明導電膜の材料は、酸化インジウム ( $In_2O_3$ )、酸化インジウム酸化錫合金 (インジウム錫酸化物ともいう。 $In_2O_3 - SnO_2$ 、ITOと略記する。)、酸化インジウム酸化亜鉛合金 ( $In_2O_3 - ZnO$ )などをスパッタ法や真空蒸着法などを用いて形成する。またインジウム自体が希少であることから、酸化錫 ( $SnO$ )等、インジウムを含有しない透明導電膜材料を用いても良い。

#### 【 0145 】

一般的に透明導電膜は、塩酸、硝酸、塩化鉄、高純度塩化鉄、臭化水素、あるいはこれらの組合せなどからなる酸化性の酸性水溶液によりエッチングされる。この時エッチングにより生じた透明導電膜材料の一部が残渣となって被処理面に残留する場合がある。

#### 【 0146 】

例えはこの残渣が形成された画素電極の間をつなぐことによって、小規模のリーク電流や導通がおこり、画質が低下あるいは表示自体が困難になるなどの可能性がある。

#### 【 0147 】

本発明においてはこれを防止するために、ドレン電極 105 と画素電極 106 を接続するコンタクトホール開口部 101 全体にまで広げることで、残渣の残留を防ぐとともに、洗浄剤から被処理面を有する基板を引き上げた際、信号線に並行な方向に延在する開口部 101 を洗浄剤の流れ落ちる通路として利用し、特に段差部に残渣が残留することを妨ぐことができる。

#### 【 0148 】

こうして 5 回のフォトリソグラフィ工程により、5 枚のフォトマスクを使用して、逆スタガ型の n チャネル型 TFT 201、補助容量 107、開口部を有する画素を完成させることができる。そして、これらの画素をマトリクス状に配置した画像表示部を構成することにより、能動素子である TFT を用いたアクティブマトリクス型の液晶表示装置を作製するための一方の基板とすることができます。本明細書では便宜上、このような基板を TFT 基板と呼ぶ。

#### 【 0149 】

本実施の形態で作製した TFT 基板において、画素部の補助容量 107 は、ゲート配線 102、画素電極 106、及びその間にゲート絶縁膜 108 のみを誘電体膜として挟んで構成してもよい。この構成は、本発明におけるソース配線 104 に平行に列方向に延在する開口部 101 を形成することで可能となったものである。

#### 【 0150 】

「背景技術」で述べた第 2 の方法では、補助容量はゲート絶縁膜および保護膜を誘電体膜としていた。一方本実施の形態の補助容量 107 は、ゲート絶縁膜 108 のみから構成されることで誘電体膜の薄膜化が可能となり、補助容量 107 の容量を増大させることができる。

#### 【 0151 】

また逆に考えれば、容量が増大するため、従来のように画素電極とゲート配線との重なり部分を広く設ける必要がなくなる。そのためゲート配線 102 の幅を細く設計することが可能となる。それにより開口率の増大につながるといった効果がある。

#### 【 0152 】

ただしゲート配線 102 の幅を細くすることは、配線自体の抵抗を増大させることにも繋がるため、適正にゲート配線 102 の幅を選択する必要がある。

#### 【 0153 】

また本実施の形態によれば、「背景技術」で述べた第 1 の方法で説明した、画素電極と接続し、かつドレン電極と同様の材料及び同じ層に形成された電極を、容量電極として別途設ける必要がない。よって歩留まり低下の要因となる恐れを除外することができる。

10

20

30

40

50

**【0154】**

また本実施の形態で作製したTFT基板において、ドレン電極105と画素電極106が接続する開口部101は、図2に示す従来のコンタクトホール1001に比べて十分広がっている。さらにコンタクトホールの端は、画素中の開口部に沿うように形成される。

**【0155】**

このため、従来発生していた、コンタクトホール上方並びにその近傍における液晶の配向の乱れ(ディスクリネーションともいう)が発生することが無くなる。即ち、従来におけるディスクリネーションによる光漏れを防ぐために必要なブラックマトリクスの面積を低減することができるため、開口率を向上することができる。

10

**【0156】**

また本実施の形態で作製したTFT基板において、従来形成されてきたコンタクトホール1001を、開口部101の全域にまで広げている。開口部101はバックライト光源から発せられる光を透過させ、さらに上部に設けられる液晶を通して画像を形成する部分である。

**【0157】**

従来では図13(E)に示されるように、保護膜1027が開口部101にも形成されていたが、本発明では開口部に形成されていた保護膜を除去している。

**【0158】**

すなわち、従来では保護膜1027を開口部にも形成することにより、光を吸収する、光を反射する、あるいは光を散乱して、光強度を減少させる要因となっていたが、本発明では開口部の保護膜を除去することにより、開口部における光源からの光の透過率が向上するという効果を得ることができる。

20

**【0159】**

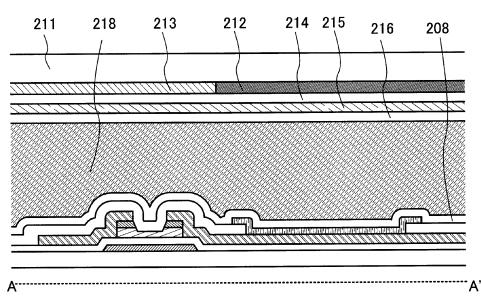

TFT基板を作成後、液晶表示装置を完成させるまでの作製工程を図8、図9、図10(A)~図10(D)を用いて以下に説明する。

**【0160】**

TFT基板上の保護膜109及び画素電極106を覆うように、配向膜208を形成する。なお、配向膜208は、液滴吐出法やスクリーン印刷法やオフセット印刷法を用いればよい。その後、配向膜208の表面にラビング処理を行う。

30

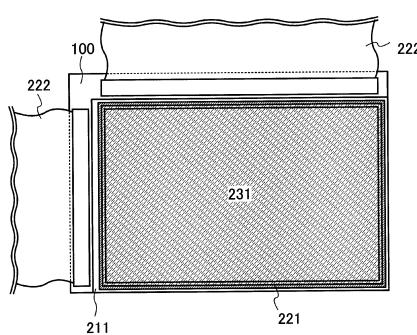

**【0161】**

そして、対向基板211には、着色層212、遮光層(ブラックマトリクス)213、及びオーバーコート層214からなるカラーフィルタを設け、さらに透明電極からなる対向電極215と、その上に配向膜216を形成する(図8参照)。対向電極215が透明電極で形成されることにより、本液晶表示装置は透過型液晶表示装置となる。なお対向電極215を反射電極で形成すると、本実施の形態の液晶表示装置は反射型液晶表示装置となる。

**【0162】**

そして、閉パタークであるシール材221をディスペンサにより画素部231と重なる領域を囲むように描画する。ここでは液晶218を滴下するため、閉パタークのシール材を描画する例を示すが、開口部を有するシールパターンを設け、TFT基板を貼りあわせた後に毛細管現象を用いて液晶を注入するディップ式(汲み上げ式)を用いてもよい(図10(A)参照)。

40

**【0163】**

次いで、気泡が入らないように減圧下で液晶218の滴下を行い(図10(B)参照)、基板100及び対向基板211を貼り合わせる(図10(C)参照)。閉ループのシールパターン内に液晶218を1回若しくは複数回滴下する。

**【0164】**

液晶218の配向モードとしては、液晶分子の配列が光の入射から射出に向かって90°ツイスト配向したTNモードを用いる場合が多い。TNモードの液晶表示装置を作製す

50

る場合には、基板のラビング方向が直交するように貼り合わせる。

【0165】

なお、一対の基板間隔は、球状のスペーサを散布する、樹脂からなる柱状のスペーサを形成する、あるいは、シール材221にフィラーを含ませることによって維持すればよい。上記柱状のスペーサは、アクリル、ポリイミド、ポリイミドアミド、エポキシの少なくとも1つを主成分とする有機樹脂材料、もしくは酸化珪素、窒化珪素、窒素を含む酸化珪素のいずれか一種の材料、或いはこれらの積層膜からなる無機材料であることを特徴としている。

【0166】

次いで、基板の分断を行う。多面取りの場合、それぞれのパネルを分断する。また、1面取りの場合、予めカットされている対向基板を貼り合わせることによって、分断工程を省略することもできる(図10(D)参照)。

【0167】

そして、異方性導電体層を介し、公知の技術を用いてFPC(Flexible Printed Circuit)222を貼りつける(図9参照)。以上の工程で液晶表示装置が完成する。また、必要があれば光学フィルムを貼り付ける。透過型液晶表示装置とする場合、偏光板は、アクティブマトリクス基板と対向基板の両方に貼り付ける。以上により本実施の形態の液晶表示装置が作製される。

【0168】

以上述べたように、本発明により、保護膜(パシベーション膜)形成の工程において、絶縁膜をエッチングする際に発生する残渣の残留を防ぐことができ、画素電極106とドレイン電極105とのコンタクト不良を低減させることができる。

【0169】

また本発明により、画素電極106の形成の工程において、透明導電膜材料をエッチングする際に発生する残渣の残留を防ぐことができる。これにより画素電極間の導通を防ぐことが可能となる。

【0170】

また本発明により、画素電極106とドレイン電極105との接触面積を従来に比べて飛躍的に増大させることができる。これにより画素電極106とドレイン電極105との接触抵抗の低減が可能となる。

【0171】

またさらに本発明では、従来の液晶表示装置に見られた、画素電極内に設けられたコンタクトホール形状に由来する液晶の配向乱れ(ディスクリネーション)を低減させることができる。

【0172】

また本発明では、補助容量107の誘電体膜をゲート絶縁膜108のみから構成されるので、誘電体膜の薄膜化が可能となり、補助容量107の容量を増大させることができる。また補助容量107の容量を増大するためゲート配線102の幅を細く設計することができ補助容量107の面積を低減させることができる。

【0173】

また、開口部101の全域にまで広げるように保護膜材料からなる絶縁膜を除去して保護膜109を形成することにより、開口部101における光源からの光の透過率が向上し輝度が増大する。

【0174】

また本発明では、フォトリソグラフィ工程で用いるフォトマスクの数を従来より増やさないことができ、作製工程や製造コストを増加させることなく、品質の良い液晶表示装置を作製することが可能となる。

【実施例1】

【0175】

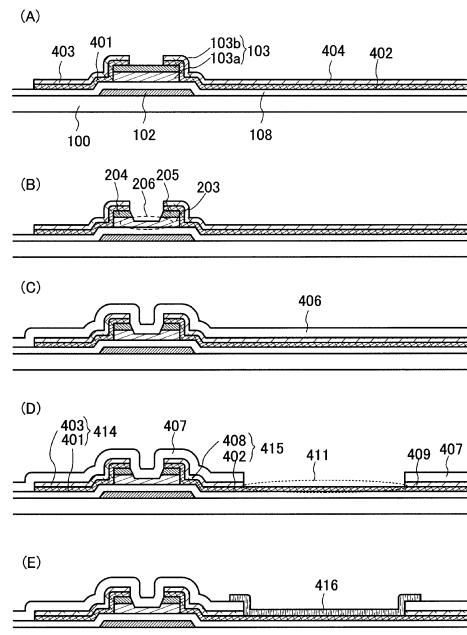

本実施例では、図14(A)～図14(D)、図15(A)～図15(B)、図18(

10

20

30

40

50

A)～図18(B)を用いて、ソース電極及びソース配線、並びにドレイン電極を形成する際に用いたレジストマスクを利用して、半導体膜をエッティングして島状半導体膜を形成する例について説明する。なお本実施例において、説明のない部分は実施の形態の記載を援用する。

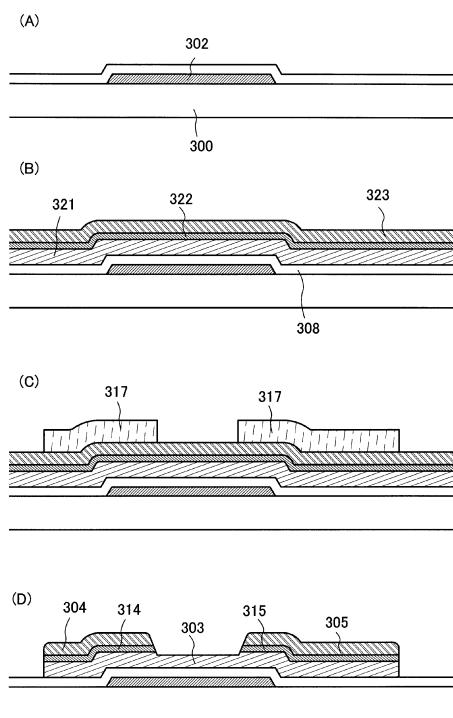

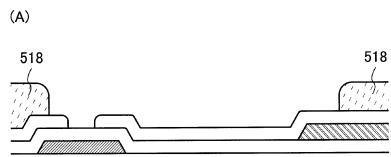

#### 【0176】

まず基板300上にゲート電極及びゲート配線302を形成する(図14(A)参照)。基板300は実施の形態の基板100と同様のものを用いればよい。またゲート電極及びゲート配線302は、実施の形態のゲート電極及びゲート配線102と同様の材料及び同様の作製工程で形成すればよい。

#### 【0177】

次いで基板300及びゲート電極及びゲート配線302上に、ゲート絶縁膜308、非晶質半導体膜321、一導電型を付与する不純物を含有する半導体膜322、及び導電膜323を成膜する(図14(B)参照)。

#### 【0178】

ゲート絶縁膜308は、実施の形態のゲート絶縁膜108と同様の材料及び同様の工程で形成すればよい。また非晶質半導体膜321は、島状半導体膜103を形成するための非晶質半導体膜と同様の材料及び工程で成膜すればよい。また、一導電型を付与する不純物を含有する半導体膜322は、ソース領域204及びドレイン領域205を形成するための半導体膜と同様の材料及び工程で成膜すればよい。

#### 【0179】

導電膜323として、実施の形態で述べたのと同様に、スパッタ法や真空蒸着法、MOCVD法(有機金属気相成長法)等で、金属膜を成膜すればよい。金属膜としては、モリブデン(Mo)、チタン(Ti)、タンタル(Ta)、タングステン(W)、クロム(Cr)から選ばれた元素を含む膜、または前記元素を成分とする合金を含む膜、または前記元素を成分とする窒化物を含む膜、あるいはモリブデン(Mo)を含む膜、アルミニウム(Al)を含む膜及びモリブデン(Mo)を含む膜を積層した積層膜、クロム(Cr)を含む膜及びネオジムを含有するアルミニウム(Al-Nd)を含む膜との積層膜、チタン(Ti)を含む膜、アルミニウム(Al)を含む膜及びチタン(Ti)を含む膜の積層膜、チタン(Ti)を含む膜、ネオジムを含有するアルミニウム(Al-Nd)を含む膜及びチタン(Ti)を含む膜の積層膜、モリブデン(Mo)を含む膜、アルミニウム(Al)を含む膜及びモリブデン(Mo)を含む膜の積層膜、モリブデン(Mo)を含む膜、ネオジムを含有するアルミニウム(Al-Nd)を含む膜及びモリブデン(Mo)を含む膜の積層膜、モリブデン(Mo)を含む膜及びアルミニウム(Al)を含む膜の積層膜、モリブデン(Mo)を含む膜の積層膜などを用いることができる。

#### 【0180】

次いで実施の形態の第3のフォトリソグラフィ工程と同様の工程を用いてレジストマスク317を形成する(図14(C)参照)。レジストマスク317により導電膜323をウェットエッティングによりエッティングしてソース電極及びソース配線304、及びドレイン電極305を形成する。

#### 【0181】

そしてレジストマスク317を除去せず、非晶質半導体膜321及び一導電型を付与する不純物を含有する半導体膜322をエッティングするマスクとして再度利用する。非晶質半導体膜321及び一導電型を付与する不純物を含有する半導体膜322をドライエッティングによりエッティングして、一導電型を付与する不純物を含有する半導体膜322をソース領域314及びドレイン領域315に分離し、非晶質半導体膜321からチャネル形成領域を有する島状半導体膜303を形成する(図14(D)参照)。

#### 【0182】

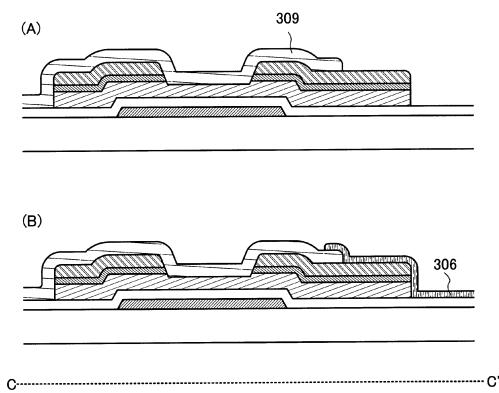

次いで保護膜309を保護膜109と同様の材料及び工程で形成する。実施の形態で述

10

20

30

40

50

べたように、保護膜材料からなる絶縁膜を第4のフォトリソグラフィ工程によりエッチングして、保護膜309を形成する(図15(A)参照)。

【0183】

保護膜309の端部は、ドレイン電極305の端部より内側になるように形成されており、これによりドレイン電極305が露出する。

【0184】

次いで保護膜309、ドレイン電極305の露出した領域、ゲート絶縁膜308上に、画素電極306を形成する(図15(B)参照)。保護膜309の端部とドレイン電極305の端部が同じ位置にそろっているのではなく、別々の位置に離れて存在するように形成されているため、画素電極306のカバレッジはよくなり断線を起こすことが少なくなる。

10

【0185】

以上のようにして形成された液晶表示装置の画素の上面図を図18(A)～図18(B)に示す。図18(A)のC-C'線で示される断面図が、図15(B)である。図18(A)は画素の実際の上面図であるが、図18(B)は開口部301の位置を強調して表した図である。

【0186】

補助容量307は、ゲート電極及びゲート配線302と、画素電極306と、その間に形成されているゲート絶縁膜308により形成されている。開口部の保護膜材料からなる絶縁膜が除去され、保護膜309が形成されないので、補助容量307の誘電体膜を、ゲート絶縁膜308のみにすることができる。したがってより容量の大きい補助容量307を作成することが可能となる。

20

【0187】

本実施例の液晶表示装置においても、実施の形態と同様に従来のコンタクトホール1001を画素の開口部全体にまで広げることにより、以下の効果が得ることができる。

【0188】

すなわち本実施例により、保護膜309形成の工程において、絶縁膜をエッチングする際に発生する残渣の残留を防ぐことができ、画素電極306とドレイン電極305とのコンタクト不良を低減させることができる。

30

【0189】

また本実施例により、画素電極306の形成の工程において、透明導電膜材料をエッチングする際に発生する残渣の残留を防ぐことができる。これにより画素電極間の導通を防ぐことが可能となる。

【0190】

また本実施例により、画素電極306とドレイン電極305との接触面積を従来に比べて飛躍的に増大させることができる。これにより画素電極306とドレイン電極305との接触抵抗の低減が可能となる。

【0191】

さらに本実施例においては、保護膜309の端部がドレイン電極305の端部の内側にあることから、画素電極306のカバレッジがよくなつて、画素電極306の断線を防ぐことができる。

40

【0192】

またさらに本実施例では、従来の液晶表示装置に見られた、画素電極内に設けられたコンタクトホール形状に由来する液晶の配向乱れ(ディスクリネーション)を低減させることができる。

【0193】

また本発明では、補助容量307の誘電体膜がほぼゲート絶縁膜308のみから構成されるので、誘電体膜の薄膜化が可能となり、補助容量307の容量を増大させることができる。また補助容量307の容量を増大するためゲート配線302の幅を細く設計することができ補助容量307の面積を低減させることができる。

50

**【 0 1 9 4 】**

また、開口部 301 の全域にまで広げるように保護膜材料からなる絶縁膜を除去して保護膜 309 を形成することにより、開口部 301 における光源からの光の透過率が向上し輝度が増大する。

**【 0 1 9 5 】**

また本発明では、フォトリソグラフィ工程で用いるフォトマスクの数を従来より増やさないことができ、作製工程や製造コストを増加させることなく、品質の良い液晶表示装置を作製することが可能となる。

**【 0 1 9 6 】**

なお本実施例は、必要であれば実施の形態の構成全てあるいはその一部と組み合わせることが可能である。 10

**【 実施例 2 】****【 0 1 9 7 】**

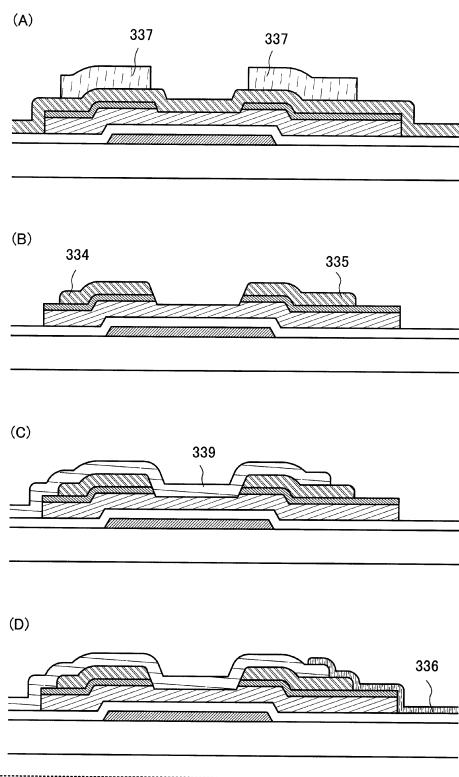

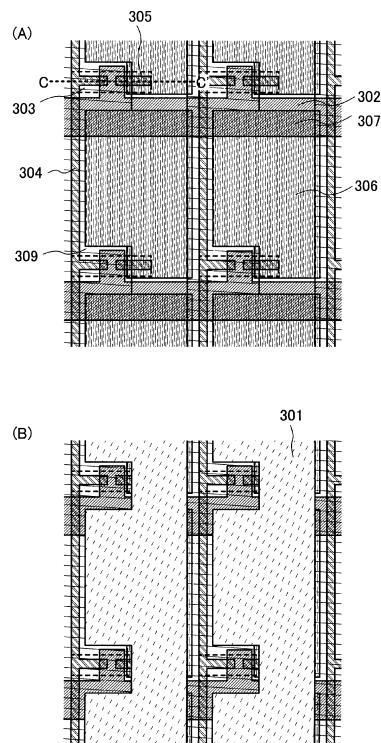

本実施例では、図 16 (A) ~ 図 16 (D)、図 17 (A) ~ 図 17 (D)、図 19 (A) ~ 図 19 (B) を用いて、ソース電極及びソース配線、並びにドレイン電極を形成する際に用いたレジストマスクを利用して、半導体膜をエッチングして島状半導体膜を形成する方法において、実施例 1 とは別の例について説明する。なお本実施例において、特に説明のない部分は実施の形態及び実施例 1 の記載を援用する。

**【 0 1 9 8 】**

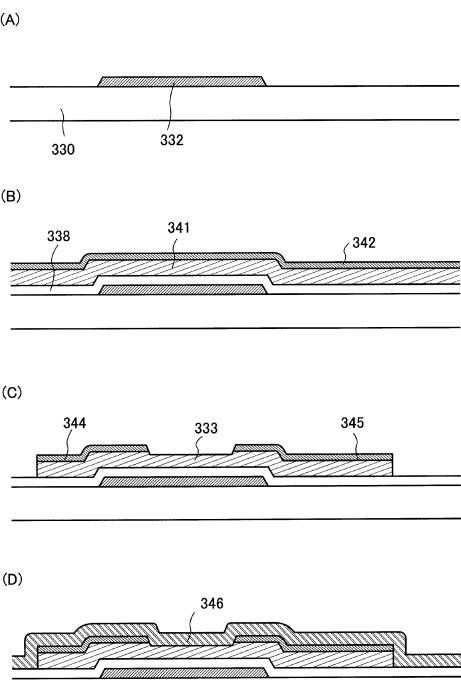

まず実施の形態又は実施例 1 と同様の工程で、基板 330 上にゲート電極及びゲート配線 332 を形成し(図 16 (A) 参照)、その上にゲート絶縁膜 338、非晶質半導体膜 341、一導電型を付与する不純物を含有する半導体膜 342 を成膜する(図 16 (B) 参照)。 20

**【 0 1 9 9 】**

次にフォトリソグラフィ工程を行い、レジストマスクを形成して、非晶質半導体膜 341 及び一導電型を付与する不純物を含有する半導体膜 342 をエッチングして、一導電型を付与する不純物を含有する半導体膜 342 をソース領域 344 及びドレイン領域 345 に分離し、また非晶質半導体膜 341 からチャネル形成領域を含む島状半導体膜 333 を形成する(図 16 (C) 参照)。

**【 0 2 0 0 】**

次いでゲート絶縁膜 338、島状半導体膜 333、ソース領域 344 及びドレイン領域 345 上に、導電膜 346 を成膜する(図 16 (D) 参照)。導電膜 346 は、ソース電極及びソース配線 104 並びにドレイン電極 105 を形成するための導電膜、並びに導電膜 323 と同様に成膜すればよい。 30

**【 0 2 0 1 】**

次にフォトリソグラフィ工程を行い、レジストマスク 337 を形成し、導電膜 346 をエッチングする(図 17 (A) 参照)。このエッチングにより導電膜 346 から、ソース電極及びソース配線 334、並びにドレイン電極 335 を形成する(図 17 (B) 参照)。

。

**【 0 2 0 2 】**

図 17 (B) において、ソース電極及びソース配線 334 の端部はソース領域 344 の端部より内側になるように形成されている。またドレイン電極 335 の端部はドレイン領域 345 の端部より内側になるように形成されている。特にドレイン領域 345 の端部がドレイン電極 335 の端部より、開口部内部へ突出した形状にすることにより、後述する画素電極 336 の作製工程において、段差を緩和することができる所以有用である。 40

**【 0 2 0 3 】**

さらに保護膜 339 を、保護膜 109 又は保護膜 309 と同様の材料及び工程で形成する。実施の形態又は実施例 1 で述べたように、保護膜材料からなる絶縁膜をフォトリソグラフィ工程によりエッチングして、保護膜 339 を形成する(図 17 (C) 参照)。

**【 0 2 0 4 】**

50

保護膜339の端部は、ドレイン電極335の端部より内側になるように形成されており、これによりドレイン電極335が露出する。

#### 【0205】

次いで保護膜339、ドレイン電極335の露出した領域、ゲート絶縁膜338上に、画素電極336を形成する(図17(D)参照)。保護膜339の端部、ドレイン電極335の端部及びドレイン領域345が同じ位置にそろっているのではなく、別々の位置に離れて存在するように形成されているため、画素電極336の段差が緩和され、カバレッジがよくなり断線を起こすことが少なくなる。

#### 【0206】

以上のようにして形成された液晶表示装置の画素の上面図を図19(A)～図19(B)に示す。図19(A)のD-D'線で示される断面図が、図17(D)である。図19(A)は画素の実際の上面図であるが、図19(B)は開口部331の位置を強調して表した図である。

#### 【0207】

本実施例では、実施例1に記載された効果に加えて、さらに保護膜339の端部、ドレイン電極335の端部及びドレイン領域345が異なる位置に離れて存在しているため、画素電極336の段差が緩和され、カバレッジがよくなり断線を防ぐことが可能となる。

#### 【0208】

なお本実施例は、必要であれば実施の形態及び実施例1の構成全てあるいはその一部と組み合わせることが可能である。

#### 【実施例3】

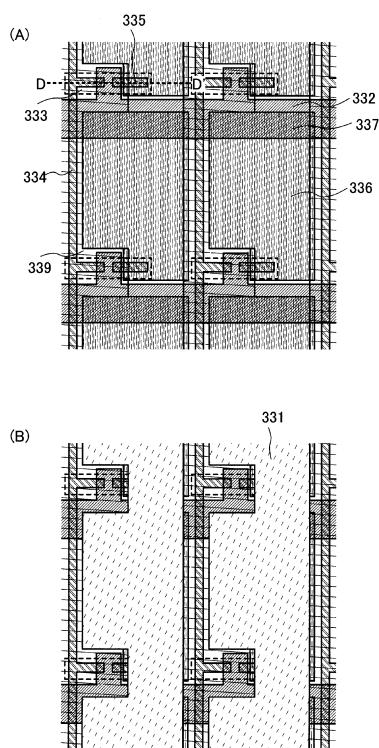

#### 【0209】

本実施例では、ドレイン電極を積層膜で形成することにより、保護膜材料からなる絶縁膜をエッチングして保護膜を形成する際にドレイン電極がダメージを受けるのを防止する例について、図20(A)～図20(E)、図21(A)～図21(E)を用いて説明する。

#### 【0210】

実施の形態において、第4のフォトリソグラフィ工程によりドライエッチング方法を用いて保護膜材料からなる絶縁膜をエッチングしている。ドライエッチングに用いるエッチングガス種や反応圧、基板温度や高周波数などの作製条件によっては、絶縁膜の下に形成されているドレイン電極105が露出した際に、大きなダメージを受けかねないという可能性がある。

#### 【0211】

ドレイン電極105がダメージを受けてしまうと、ドレイン電極105と画素電極106との電気的な接続に悪影響が出る恐れが生じてしまう。

#### 【0212】

従って本実施例では、ドレイン電極を複数の層で構成される積層膜で形成することにより、ドレイン電極へのダメージを防止する。

#### 【0213】

まず実施の形態の記載を基にして、図7(B)に示す構造までを作成する。なお本実施例においては、特に記載のないものについては実施の形態、実施例1及び実施例2の記載を援用する。

#### 【0214】

次いで、ゲート絶縁膜108、島状非晶質半導体膜103aと島状不純物半導体膜103bからなる島状半導体膜103上に、第1の導電膜を成膜し、さらにその上に第2の導電膜を成膜する。

#### 【0215】

第1の導電膜と第2の導電膜との組み合せは、クロム(Cr)を含む膜とアルミニウム(Al)を含む膜の積層膜や、クロム(Cr)を含む膜とネオジムを含むアルミニウム(Al-Nd)を含む膜などの積層膜等が挙げられる。

10

20

30

40

50

## 【0216】

次にフォトレジスト工程を行い、レジストマスクを形成して、第1の導電膜と第2の導電膜にエッティングを行い、第1の導電膜を下層ソース電極及びソース配線401、並びに下層ドレイン電極402とする。第2の導電膜は、上層ソース電極及びソース配線403、並びに電極404を形成する(図20(A)参照)。

## 【0217】

次いで実施の形態と同様に、下層ソース電極及びソース配線401、上層ソース電極及びソース配線403、下層ドレイン電極402及び電極404をマスクとして、島状非晶質半導体膜103aと島状不純物半導体膜103bの一部をドライエッティングにより除去して、島状不純物半導体膜103bをソース領域204とドレイン領域205に分離する。またこのエッティングにより島状非晶質半導体膜103aは自己整合的にエッティングされ、チャネル形成領域206を有する島状半導体膜203となる(図20(B)参照)。

10

## 【0218】

次いで基板全面を覆って、無機材料からなる絶縁膜406を形成する(図20(C)参照)。

## 【0219】

無機材料からなる絶縁膜406は、窒化珪素膜、酸素を含む窒化珪素膜、窒素を含む酸化珪素膜、酸化珪素膜、またはこれらを組み合わせた積層膜で形成し、厚さは200~450nmとする。本実施例では、プラズマCVD法でSiH<sub>4</sub>、NH<sub>3</sub>を原料ガスとして窒化珪素膜を成膜する。

20

## 【0220】

その後、フォトリソグラフィ工程によって、レジストマスクを形成し、無機材料からなる絶縁膜406をドライエッティングして保護膜407を形成する。保護膜407はTFTを覆うが、画素部の開口部411はドライエッティング工程により無機材料からなる絶縁膜が除去されているので露出する(図20(D)参照)。

## 【0221】

ここで絶縁膜406をドライエッティングする際に、下層ドレイン電極402の上部に形成されている電極404を、意図的に絶縁膜406と共にエッティングにより除去することにより、下層ドレイン電極402を開口部411にて露出させる。また電極404は、上層ドレイン電極408と電極409に分離される。

30

## 【0222】

よってソース電極及びソース配線414は、下層ソース電極及びソース配線401及び上層ソース電極及びソース配線403から構成され、ドレイン電極415は下層ドレイン電極402及び上層ドレイン電極408から構成されることとなる。

## 【0223】

次いで透明導電膜を保護膜407、開口部411にて露出した下層ドレイン電極402上に形成し、エッティングして画素電極416を形成する(図20(E)参照)。透明導電膜がインジウム錫酸化物(ITO)などの酸化物で形成されると、酸化物は多量に酸素を含有しているため、アルミニウムを含む膜と接触していると、アルミニウム(A1)との電気的、または物理的な接続性の劣化、あるいは形成後の電蝕による信頼性が劣化してしまう恐れがある。下層ドレイン電極402を形成するための第2の導電膜がアルミニウム膜、もしくはアルミニウムを含む膜で構成されるため、保護膜407形成のための絶縁膜406エッティングの際に、上層ドレイン電極408となる電極404と一緒にエッティングすることにより、アルミニウム(A1)と透明導電膜との接続を回避することが可能である。

40

## 【0224】

図21(A)~図21(E)では、ドレイン電極を三層の積層膜で形成した例を示す。

## 【0225】

まず実施の形態の記載を基にして、図7(B)に示す構造までを作成する。

## 【0226】

50

次いで、ゲート絶縁膜 108、島状非晶質半導体膜 103a と島状不純物半導体膜 103b からなる島状半導体膜 103 上に、第 3 の導電膜、第 4 の導電膜及び第 5 の導電膜を順に積層して成膜する。

#### 【0227】

第 3 の導電膜及び第 5 の導電膜の例としては、モリブデン (Mo) などの耐熱性導電性材料膜であり、第 4 の導電膜の材料の例としては、純アルミニウム膜 (Al) やネオジムを含むアルミニウム (Al-Nd) 膜など他の元素を含有するアルミニウム (Al) 膜である。

#### 【0228】

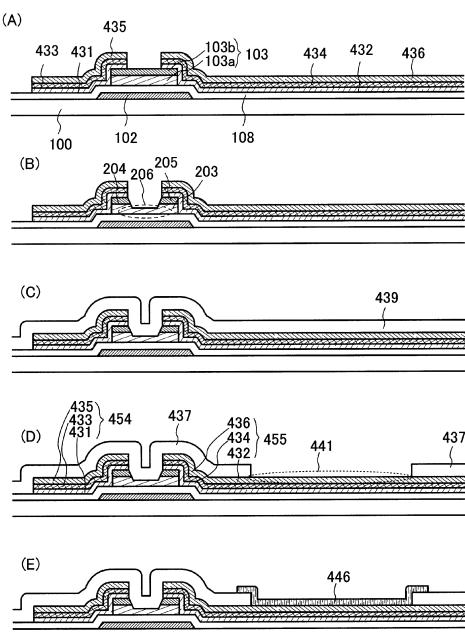

次にフォトレジスト工程を行い、レジストマスクを形成して、第 3 の導電膜、第 4 の導電膜及び第 5 の導電膜にエッチングを行い。第 3 の導電膜を下層ソース電極及びソース配線 431、並びに下層ドレイン電極 432 とする。第 4 の導電膜は、中層ソース電極及びソース配線 433、並びに中層ドレイン電極 434 とする。また第 5 の導電膜から、上層ソース電極及びソース配線 435、上層ドレイン電極 436 を形成する (図 21 (A) 参照)。なお下層ソース電極及びソース配線 431、中層ソース電極及びソース配線 433 並びに上層ソース電極及びソース配線 435 は、ソース電極及びソース配線 454 を構成しており、下層ドレイン電極 432、中層ドレイン電極 434 並びに上層ドレイン電極 436 はドレイン電極 455 を構成している。

#### 【0229】

次いで実施の形態と同様に、ソース電極及びソース配線 454 並びにドレイン電極 455 をマスクとして、島状非晶質半導体膜 103a と島状不純物半導体膜 103b の一部をドライエッティングにより除去して、島状不純物半導体膜 103b をソース領域 204 とドレイン領域 205 に分離する。またこのエッティングにより島状非晶質半導体膜 103a は自己整合的にエッティングされ、チャネル形成領域 206 を有する島状半導体膜 203 となる (図 21 (B) 参照)。

#### 【0230】

次いで基板全面を覆って、無機材料からなる絶縁膜 439 を形成する (図 21 (C) 参照)。なお絶縁膜 439 は絶縁膜 406 と同様の材料及び同様の工程で作成すればよい。

#### 【0231】

その後、フォトリソグラフィ工程によって、レジストマスクを形成し、無機材料からなる絶縁膜 439 をドライエッティングして保護膜 437 を形成する。保護膜 437 は TFT を覆うが、画素部の開口部 441 はドライエッティング工程により無機材料からなる絶縁膜が除去されているので露出する (図 21 (D) 参照)。

#### 【0232】

絶縁膜 439 のエッティング時に、ドレイン電極 455 にダメージの加わる恐れがある。しかし上層ドレイン電極 436 及び中層ドレイン電極 434 が存在しているので、耐熱性導電性材料からなる下層ドレイン電極 432 はダメージを受けないという利点を有する。すなわちドレイン電極を三層構造にすることで、エッティングによる膜減りによる影響を抑制することが可能となる。

#### 【0233】

次いで透明導電膜を保護膜 437、開口部 441 にて露出した上層ドレイン電極 436 上に形成し、エッティングして画素電極 446 を形成する (図 21 (E) 参照)。

#### 【0234】

図 21 (E) においては、画素電極がインジウム錫酸化物 (ITO) などの酸化物を含んでいたとしても、アルミニウムを含む中層ドレイン電極 434 上に、耐熱性導電性材料膜からなる上層ドレイン電極 436 が存在してゐるため、アルミニウム (Al) と透明導電膜との接続を回避することが可能である。

#### 【0235】

本実施例では、実施例 1 に記載された効果に加えて、さらに保護膜材料からなる絶縁膜のエッティングの際に、ドレイン電極にダメージを受けるのを抑制することができるとい

10

20

30

40

50

効果を有する。

**【0236】**

なお本実施例は、必要であれば実施の形態及び実施例1～実施例2の構成全てあるいはその一部と組み合わせることが可能である。

**【実施例4】**

**【0237】**

実施の形態及び実施例1～実施例3では透過型液晶表示装置及びその作製方法を説明したが、本実施例では半透過型液晶表示装置や微透過型液晶表示装置について、図22(A)～図22(B)、図23を用いて説明する。

**【0238】**

10

半透過型液晶表示装置や微透過型液晶表示装置いずれを作製する場合においても、実施の形態及び実施例1～実施例3で述べた透過型のTFT基板の作製後、アルミニウム(A1)、銀(Ag)、クロム(Cr)など反射率の高い金属膜を用いて反射電極を、透明な画素電極上に少なくとも一部が重なり電気的に接触するように形成する。

**【0239】**

反射電極を作製した部分が反射領域となり、その他の開口部分が透過領域となる。反射領域と透過領域との面積比率をほぼ等価にすることで半透過型となり、反射領域の面積を透過領域よりも小さくすることで微透過型液晶表示装置を作製することができる。

**【0240】**

20

実施の形態及び実施例1～実施例3で述べた透過型液晶表示装置を仮に全透過型液晶表示装置とすると、全透過型液晶表示装置ではバックライトの光を透過することにより画像を映し出す。一方微透過型液晶表示装置や半透過型液晶表示装置は、反射電極を有しているので外光を利用することが可能となり、消費電力を抑えることができる。

**【0241】**

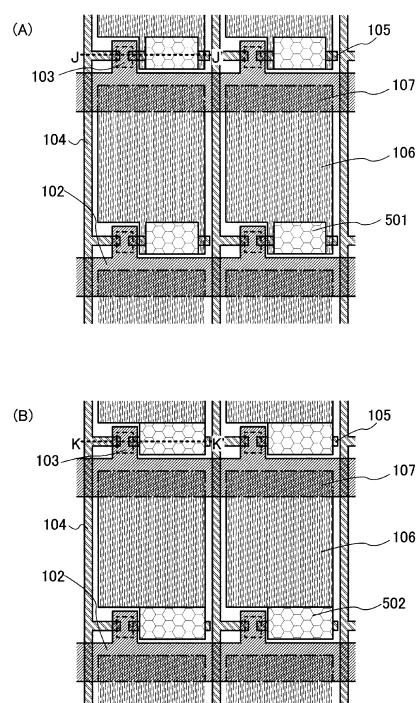

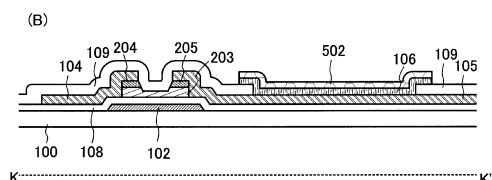

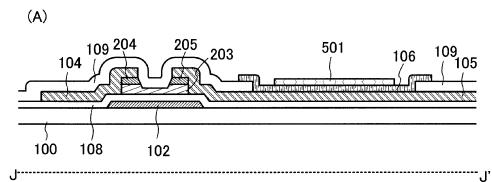

図22(A)は、実施の形態の図1(B)に、反射電極501を形成したものである。なお保護膜109は画面を見やすくするために省略してある。反射電極501が透明電極である画素電極106の面積よりもかなり小さく、反射領域が透過領域よりかなり小さくなっている。従って図22(A)の画素構造を有する液晶表示装置は、微透過型液晶表示装置となる。

**【0242】**

30

また図22(B)の液晶表示装置も、実施の形態の図1(B)に、反射電極502を形成したものであり、反射電極502の面積が画素電極106の面積よりもかなり小さく、微透過型液晶表示装置となっている。

**【0243】**

図22(A)の液晶表示装置の画素のJ-J'線に沿った断面図を図24(A)に、図22(B)の液晶表示装置の画素のK-K'線に沿った断面図を図24(B)に示す。

**【0244】**

図22(A)の反射電極501の端部は画素電極106の端部よりも内側に位置するように形成されている。一方図22(B)の液晶表示装置では、反射電極502の端部が画素電極106の端部と一致するように形成されている。

40

**【0245】**

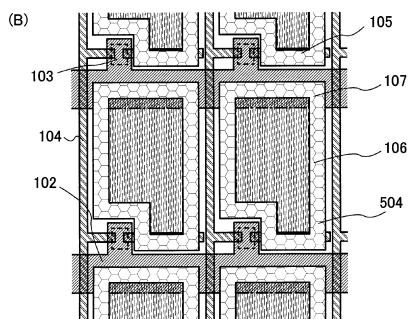

図23(A)も実施の形態の図1(B)に、反射電極503を形成したものであるが、反射電極503が透明電極である画素電極106の面積とほぼ半分になるように形成されている。すなわち反射部分の面積と透過部分の面積がほぼ等価であるので、図23(A)の画素構造を有する液晶表示装置は、半透過型液晶表示装置となる。

**【0246】**

図23(B)は、半透過型液晶表示装置の別の例である。反射電極504は画素電極106の縁に沿って、画素電極106の外周をなぞるように形成されている。この形状では透過領域と反射領域が偏らないので、より見やすい液晶表示装置を得ることができる。

**【0247】**

50

すなわち本実施例では、実施例1に記載された効果に加えて、さらに外光を利用するこ

とが可能となり、消費電力を抑えることができるという利点を持つ。

#### 【0248】

なお本実施例は、必要であれば実施の形態及び実施例1～実施例3の構成全てあるいは

その一部と組み合わせることが可能である。

#### 【実施例5】

#### 【0249】

本実施例では、画素部以外の領域例えば周辺部で、ゲート配線材料からなる配線とソース

配線材料からなる配線との接続方法について、図25(A)～図25(E)、図26(A)

～図26(C)、図27を用いて説明する。なお特に記載のないものについては、実

施の形態の記載を援用する。

10

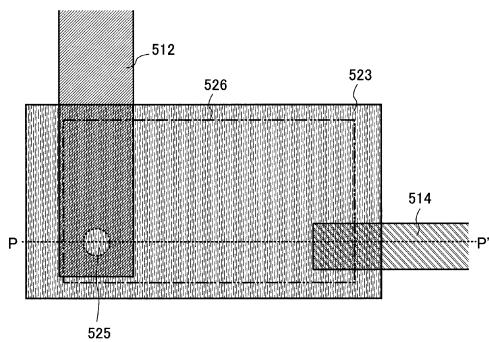

#### 【0250】

図27はゲート配線材料からなる配線とソース配線材料からなる配線との接続構造を上

面図で示したものである。図25(A)～図25(E)、図26(A)～図26(C)は

図27の上面図に示す接続構造を形成するための手順を示す断面図であり、図26(C)

は図27中のP-P'で示される部分の断面図である。

#### 【0251】

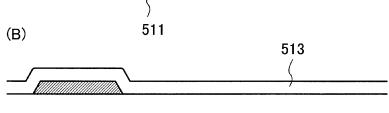

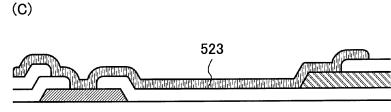

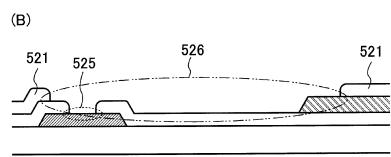

図27において、ゲート配線材料からなる配線512とソース配線材料からなる配線5

14がそれぞれ透明導電材料からなる導電膜523を介して接続されている。

#### 【0252】

まず図25(A)に示すように、基板511上に、実施の形態に記載された方法に基づき、

ゲート配線材料からなる配線512を形成する。その後、図25(B)に示すように

、ゲート絶縁膜513を基板511の全面に成膜する。

20

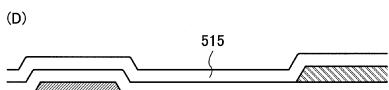

#### 【0253】

次に図25(B)に示すように、実施の形態で述べた方法に基づき、ソース配線材料から

なる配線514を形成する。さらに図25(D)に示すように、ゲート絶縁膜513及び

配線514上に保護膜515を成膜する。

#### 【0254】

次に実施の形態で述べた第4のフォトリソグラフィ工程において、ハーフトーンマスク

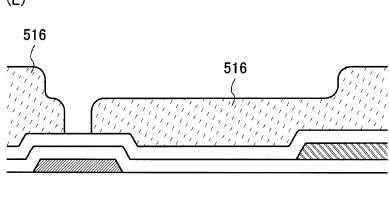

を用いたハーフトーン露光技術を用いて、段差状のレジストマスク516を形成する(図

25(E)参照)。レジストマスク516を用いてエッチングを行うことで、図26(A)

のようにゲート配線材料からなる配線512の真上の絶縁膜にコンタクトホール525

を形成する。ただしコンタクトホール525が形成される絶縁膜は好ましくは保護膜51

5のみとし、ゲート絶縁膜513は残存するようにエッチングする。このエッチングによ

り保護膜515は、コンタクトホール525が形成された保護膜517となる。

30

#### 【0255】

次に図26(A)のように、ラジカル状態の酸素などを用いてアッシング処理を行い、

レジストマスク516を一部除去して、レジストマスク516をレジストマスク518の

ように変形させる。

#### 【0256】

変形させたレジストマスク518を用いて、保護膜517を再度エッチングして、保護

膜521とする。図26(B)に示すように、このエッチングによりゲート配線材料から

なる配線512上のコンタクトホール525が形成され、かつ、ゲート配線材料からなる

配線512上のコンタクトホール525とソース配線材料からなる配線514の一部を含

んだ開口部526が形成される。

40

#### 【0257】

本実施例において、コンタクトホール525はゲート配線材料からなる配線512よりも幅を狭く形成しているが、ゲート配線材料からなる配線512の両端を含んだ広いコン

タクトホールを形成しても良い。

#### 【0258】

10

20

30

40

50

次いで図26(C)に示すように、透明導電材料からなる導電膜523を、コンタクトホール525および開口部526上に形成することで、透明導電材料からなる導電膜523を介して、ゲート配線材料からなる配線512とソース配線材料からなる配線514を接続することができる。

#### 【0259】

上述した周辺部のゲート配線材料からなる配線512は、実施の形態で述べた画素部におけるゲート電極及びゲート配線102と同一の構成であり、同一の材料である。またゲート絶縁膜513は画素部におけるゲート絶縁膜108と同一の構成であり、同一の材料である。またソース配線材料からなる配線514は、画素部におけるソース電極及びソース配線104、並びにドレイン電極105と同一の構成であり、同一の材料である。また保護膜521および透明導電材料からなる導電膜523はそれぞれ、画素部における保護膜109、画素電極106とそれぞれ同一の構成であり、同一の材料である。10

#### 【0260】

従って、周辺部での配線の形成も、画素部と同様の方法で、且つ同時に形成することができる。従って、TFT基板をマスク数を増やすことなく作製することが可能である。

#### 【0261】

本実施例は、実施の形態で述べられた効果を奏すると共に、マスク数を増やすことなく周辺の配線も形成することができるという利点を得ることができる。

#### 【0262】

なお本実施例は、必要であれば実施の形態及び実施例1～実施例4の構成全てあるいはその一部と組み合わせることが可能である。20

#### 【実施例6】

#### 【0263】

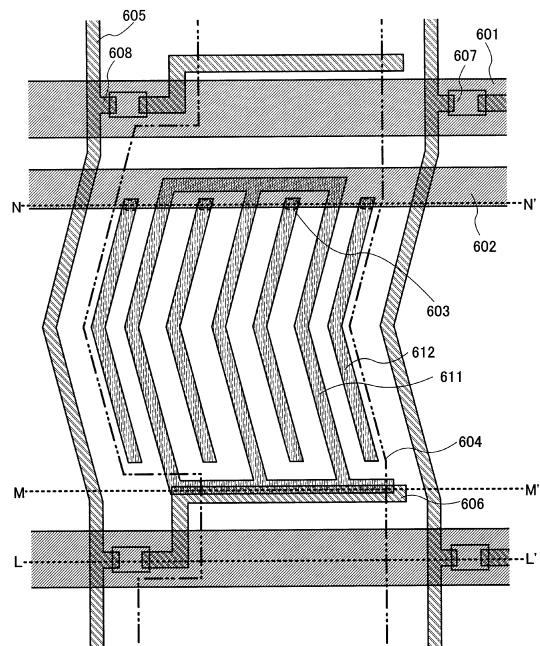

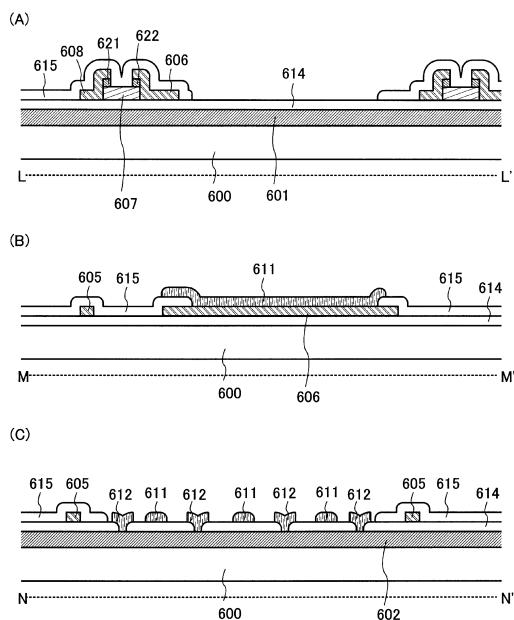

本実施例では、IPS(In-Plane Switching)モードの液晶表示装置について、図28、図29(A)～図29(C)を用いて説明する。

#### 【0264】

図28は、本実施例のIPSモードの液晶表示装置において、任意の一画素の上面図である。また図29(A)、図29(B)及び図29(C)は、それぞれ図28中のL-L'線、M-M'線及びN-N'線に沿った断面図である。

#### 【0265】

図28、図29(A)～図29(C)において、基板600上に、ゲート配線601及びコモン配線602が形成されている。ゲート配線601及びコモン配線602は、同一の材料、同一の層及び同一の工程で形成されている。ゲート配線601及びコモン配線602上には、ゲート絶縁膜614が形成されている。30

#### 【0266】

なお、基板600は実施の形態で述べた基板100と同様の材料を用いればよい。またゲート配線601及びコモン配線602は、実施の形態のゲート電極及びゲート配線102と同様の材料及び同様の作製工程で形成すればよい。さらにゲート絶縁膜614は、実施の形態のゲート絶縁膜108と同様の材料及び同様の作製工程で形成すればよい。

#### 【0267】

画素のスイッチング素子となるTFTは、ゲート配線601、ゲート絶縁膜614、島状半導体膜607、ソース領域621、ドレイン領域622、ソース電極608及びドレイン電極606を有している(図29(A)参照)。

#### 【0268】

なおTFTの島状半導体膜607、ソース領域621、ドレイン領域622は、それぞれ実施の形態の島状半導体膜203、ソース領域204、ドレイン領域205の形成方法を基に形成すればよい。

#### 【0269】

ソース電極608とソース配線605は便宜上分けているが、同一の導電膜から形成され互いに接続されている。またドレイン電極606も、ソース電極608とソース配線640

05と同一の材料及び同じ工程で形成される。

**【0270】**

保護膜615は、実施の形態で述べた保護膜109と同じ材料及び同じ作製工程で形成すればよい。また保護膜615は、二点鎖線で示される開口部604では除去されており、開口部604に形成されている絶縁膜はゲート絶縁膜614のみとなっている。

**【0271】**

ドレイン電極606と画素電極611は、開口部604において接することにより電気的にも接続されている（図29（B）参照）。

**【0272】**

ソース電極608及びソース配線605は、実施の形態のソース電極及びソース配線104、またドレイン電極606は、実施の形態のドレイン電極105と同様の材料及び同じ工程で形成すればよい。

**【0273】**

画素電極611と、複数のコモン電極612のそれぞれは、同一の材料及び同じ工程で形成される。コモン電極612は、ゲート絶縁膜614中のコンタクトホール603を介して、コモン配線602と電気的に接続されている（図29（C）参照）。

**【0274】**

なお、画素電極611及びコモン電極612は、実施の形態で述べた画素電極106と同様の材料及び同様の作製工程で形成すればよい。

**【0275】**

画素電極611とコモン電極612との間で、基板600に平行な横方向電界が発生し、液晶を制御する。

**【0276】**

IPSモードの液晶表示装置は、液晶分子が斜めに立ち上がるがないため、見る角度による光学特性の変化が少なく、広視野特性を得ることができる。本実施例は、実施例1に記載された効果に加えて、広視野特性をえることができるという利点を有する。

**【0277】**

なお本実施例は、必要であれば実施の形態、実施例1～実施例5の構成全てあるいはその一部と組み合わせることが可能である。

**【実施例7】**

**【0278】**

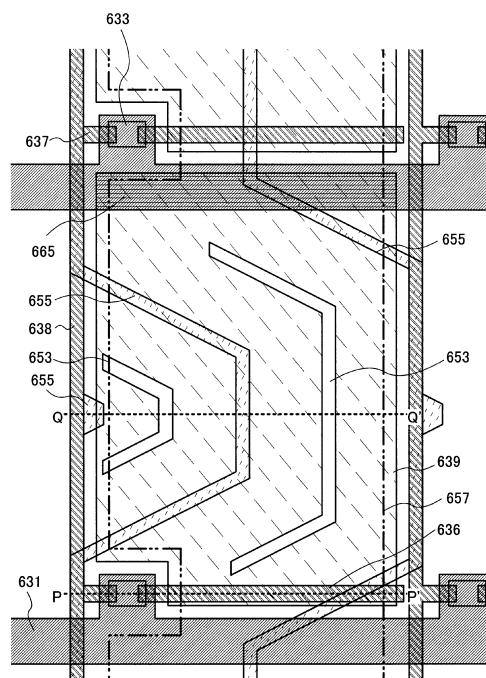

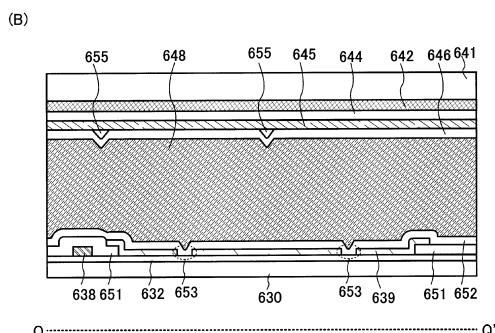

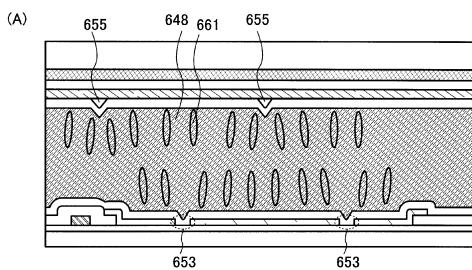

本実施例では、MVA（Multi-domain Vertically Aligned）モードの液晶表示装置について、図30、図31（A）～図31（B）、図32（A）～図32（B）を用いて説明する。

**【0279】**

図30は、本実施例のMVAモードの液晶表示装置において、任意の一画素の上面図である。また図31（A）及び図31（B）は、それぞれ図30中のP-P'線及びQ-Q'線に沿った断面図である。

**【0280】**

図30、図31（A）～図31（B）において、基板630上に、ゲート配線631、及び、ゲート配線631上にゲート絶縁膜632が形成されている。

**【0281】**

なお、基板630は実施の形態で述べた基板100と同様の材料を用いればよい。またゲート配線631は、実施の形態のゲート電極及びゲート配線102と同様の材料及び同様の作製工程で形成すればよい。さらにゲート絶縁膜632は、実施の形態のゲート絶縁膜108と同様の材料及び同様の作製工程で形成すればよい。

**【0282】**

画素のスイッチング素子となるTFTは、ゲート配線631、ゲート絶縁膜632、島状半導体膜633、ソース領域634、ドレイン領域635、ソース電極637及びドレイン電極636を有している（図31（A）参照）。

10

20

30

40

50

**【0283】**

なお TFT の島状半導体膜 633、ソース領域 634、ドレイン領域 635 は、それぞれ実施の形態の島状半導体膜 203、ソース領域 204、ドレイン領域 205 の形成方法を基に形成すればよい。

**【0284】**

ソース電極 637 とソース配線 638 は便宜上分けているが、同一の導電膜から形成され互いに接続されている。またドレイン電極 636 も、ソース電極 637 とソース配線 638 と同一の材料及び同じ工程で形成される。

**【0285】**

保護膜 651 は、実施の形態で述べた保護膜 109 と同じ材料及び同じ作製工程で形成すればよい。また保護膜 651 は、二点鎖線で示される開口部 657 では除去されており、開口部 657 に形成されている絶縁膜はゲート絶縁膜 632 のみとなっている。

**【0286】**

ソース電極 637 及びソース配線 638 は、実施の形態のソース電極及びソース配線 104、またドレイン電極 636 は、実施の形態のドレイン電極 105 と同様の材料及び同じ工程で形成すればよい。

**【0287】**

なお、画素電極 639 は、実施の形態で述べた画素電極 106 と同様の材料及び同様の作製工程で形成すればよい。

**【0288】**

画素電極 639 には、複数の溝 653 が形成されている。

**【0289】**

またゲート配線 631 と画素電極 639 が重なる領域には、ゲート絶縁膜 632 を誘電体として、補助容量 665 が形成される。

**【0290】**

保護膜 651 及び画素電極 639 上には、配向膜 652 を形成する。配向膜 652 は、液滴吐出法やスクリーン印刷法やオフセット印刷法を用いて形成すればよい。

**【0291】**

また、対向基板 641 には、着色層 642、遮光層（ブラックマトリクス）643、及びオーバーコート層 644 からなるカラーフィルタを設け、さらに透明電極からなる対向電極 645 と、その上に配向膜 646 が形成されている。

**【0292】**

対向電極 645 上方の配向膜 646 上には、複数の突起（リブともいう）655 が形成されている。突起 655 は、アクリル等の樹脂で形成すればよい。突起 655 は左右対称、望ましくは四面体であればよい。

**【0293】**

液晶 648 は、実施の形態の記載に基づいて、基板 630 及び対向基板 641 の間に形成される。

**【0294】**

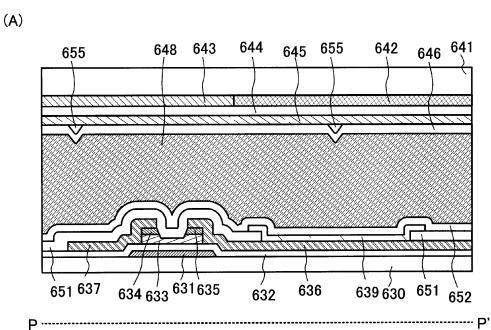

図 32(A)～図 32(B) は、図 31(B) において、液晶分子 661 の動きを表した図である。

**【0295】**

MVA 方式では、突起 655 に対して、液晶 648 中の液晶分子 661 が左右対称に傾くように駆動される。これにより左右方向から見た色の差をおさえられる。画素内で液晶分子 661 の傾く方向を変えるとどの目線からも色のムラがでない。

**【0296】**

図 32(A) は印加電圧が印加されない状態、すなわち印加電圧 0V であるときの図を示している。印加電圧が 0V のとき、液晶分子 661 は基板 630 及び 641 に対して垂直に配向している。このため基板 630 又は基板 641 に設けられた偏光板から入った入射光はそのまま液晶分子 661 を透過するため、出力側の偏光板の透過軸と入射光の振動

10

20

30

40

50

面が直交する。よって光は出力されないことから暗状態となる。

**【0297】**

図32(B)は印加電圧が印加された状態の図を示している。印加電圧を印加すると、図32(B)のように電界663がかかることにより液晶分子661は突起655の傾斜方向に倒れる。これにより液晶分子661の長軸が偏光板の吸収軸に交わるので、光が出力側の偏光板を透過することから、明状態となる。

**【0298】**

突起655を設けることにより、液晶分子661が突起655の傾斜面に垂直な方向に倒れるように駆動され、対称性があり視角特性のよい表示を得ることができる。

**【0299】**

またMVA方式においては、配向膜646及び652にラビングをしなくてよいので、作製工程を減らすことができる。またラビング工程がないので、ラビングによる液晶648への混入物をなくすことができる。これにより配向不良や表示品位の低下を抑制することが可能となる。

**【0300】**

以上から、本実施例のMVA方式の液晶表示装置では、実施例1に記載された効果に加えて、さらに、対称性があり視角特性のよい表示を得ることができる。

**【0301】**

なお本実施例は、必要であれば実施の形態、実施例1～実施例6の構成全てあるいはその一部と組み合わせることが可能である。

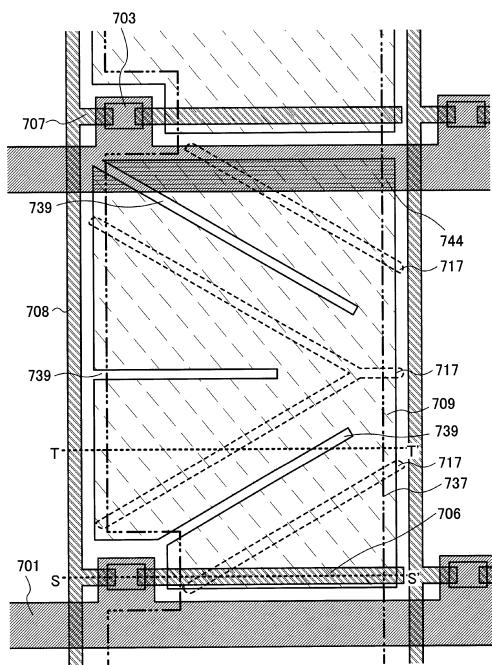

**【実施例8】**

**【0302】**

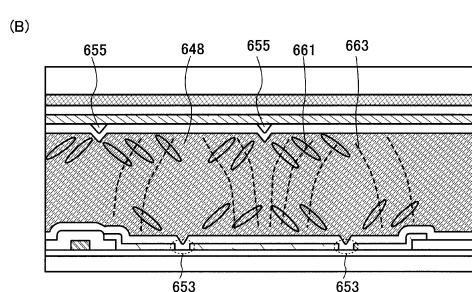

本実施例では、PVA(Patterned Vertical Alignment)方式の液晶表示装置について、図33、図34(A)～図34(B)、図35(A)～図35(B)を用いて説明する。

**【0303】**

図33は、本実施例のPVAモードの液晶表示装置において、任意の一画素の上面図である。また図34(A)及び図34(B)は、それぞれ図33中のS-S'線及びT-T'線に沿った断面図である。

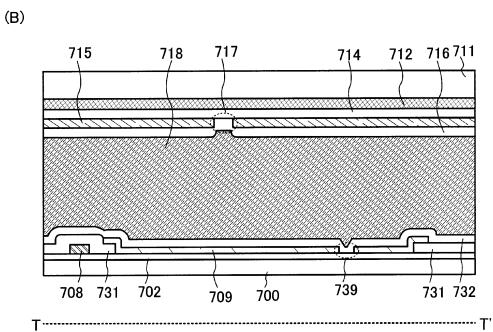

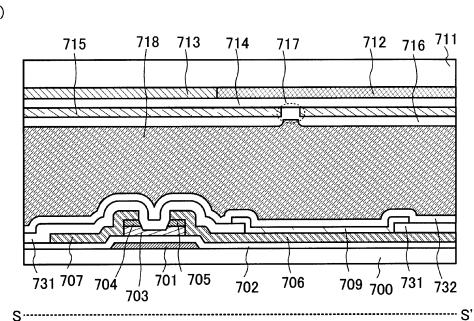

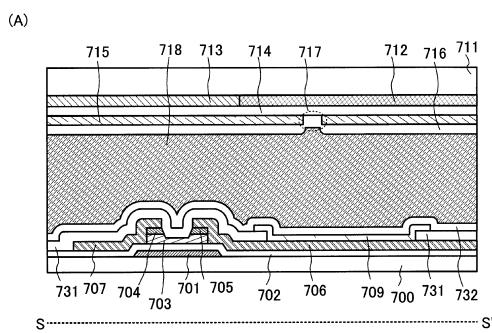

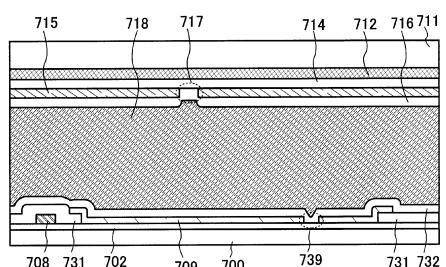

**【0304】**

図33、図34(A)～図34(B)において、基板700上に、ゲート配線701、及び、ゲート配線701上にゲート絶縁膜702が形成されている。

**【0305】**

なお、基板700は実施の形態で述べた基板100と同様の材料を用いればよい。またゲート配線701は、実施の形態のゲート電極及びゲート配線102と同様の材料及び同様の作製工程で形成すればよい。さらにゲート絶縁膜702は、実施の形態のゲート絶縁膜108と同様の材料及び同様の作製工程で形成すればよい。

**【0306】**

画素のスイッチング素子となるTFTは、ゲート配線701、ゲート絶縁膜702、島状半導体膜703、ソース領域704、ドレイン領域705、ソース電極707及びドレイン電極706を有している(図34(A)参照)。

**【0307】**

なおTFTの島状半導体膜703、ソース領域704、ドレイン領域705は、それぞれ実施の形態の島状半導体膜203、ソース領域204、ドレイン領域205の形成方法を基に形成すればよい。

**【0308】**

ソース電極707とソース配線708は便宜上分けているが、同一の導電膜から形成され互いに接続されている。またドレイン電極706も、ソース電極707とソース配線708と同一の材料及び同じ工程で形成される。

**【0309】**

10

20

30

40

50

保護膜 731 は、実施の形態で述べた保護膜 109 と同じ材料及び同じ作製工程で形成すればよい。また保護膜 731 は、二点鎖線で示される開口部 737 では除去されており、開口部 737 に形成されている絶縁膜はゲート絶縁膜 702 のみとなっている。

#### 【0310】

ソース電極 707 及びソース配線 708 は、実施の形態のソース電極及びソース配線 104、またドレイン電極 706 は、実施の形態のドレイン電極 105 と同様の材料及び同じ工程で形成すればよい。

#### 【0311】

なお、画素電極 709 は、実施の形態で述べた画素電極 106 と同様の材料及び同様の作製工程で形成すればよい。

10

#### 【0312】

画素電極 709 には、複数の溝 739 が形成されている。

#### 【0313】

また画素電極 709 とゲート配線 701 が重なる領域には、ゲート絶縁膜 702 を挟んで、補助容量 744 が形成される。

#### 【0314】

保護膜 731 及び画素電極 709 上には、配向膜 732 を形成する。配向膜 732 は、液滴吐出法やスクリーン印刷法やオフセット印刷法を用いて形成すればよい。

#### 【0315】

また、対向基板 711 には、着色層 712、遮光層（ブラックマトリクス）713、及びオーバーコート層 714 からなるカラーフィルタを設け、さらに透明電極からなる対向電極 715 と、その上に配向膜 716 が形成されている。

20

#### 【0316】

対向電極 715 には、複数の溝 717 が形成されている。対向電極 715 の溝 717 は、画素電極 709 の溝 739 と重ならないように配置されている（図 33 参照）。

#### 【0317】

液晶 718 は、実施の形態の記載に基づいて、基板 700 及び対向基板 711 の間に形成される。

#### 【0318】

図 35 (A) ~ 図 35 (B) は、図 34 (B) において、液晶分子 741 の動きを表した図である。

30

#### 【0319】

PVA 方式では、対向電極 715 の溝 717 と画素電極 709 の溝 739 が互いに重ならないように配置されており、液晶 718 中の液晶分子 741 が、お互いに重ならないように配置された溝 717 及び 739 に向かって配向することで、光が透過する。

#### 【0320】

図 35 (A) は印加電圧が印加されない状態、すなわち印加電圧 0V であるときの図を示している。印加電圧が 0V のとき、液晶分子 741 は基板 700 に対して垂直に配向しているため、基板 700 又は基板 711 に設けられた偏光板から入った入射光はそのまま液晶分子 741 を透過し、入射光の振動方向と出力側の偏光板の透過軸とが直交する。よって光は出力されないことから暗状態となる。

40

#### 【0321】

図 35 (B) は印加電圧が印加された状態の図を示している。印加電圧を印加すると、図 35 (B) のように斜めに電界 742 がかかることにより液晶分子 741 は斜めに傾くこととなる。これにより液晶分子 741 の長軸が偏光板の吸収軸に交わるので、光が出力側の偏光板を透過することから、明状態となる。

#### 【0322】

対向電極 715 に溝 717、及び、画素電極 709 に溝 739 を設けることにより、溝 717 及び 739 に向かう斜めの電界 742 によって、液晶分子 741 が斜めに駆動され、上下方向や左右方向だけでなく斜め方向にも対称性があり視角特性のよい表示を得ること

50

とができる。

**【0323】**

またPVA方式においては、配向膜716及び732にラビングをしなくてよいので、作製工程を減らすことができる。またラビング工程がないので、ラビングによる液晶718への混入物をなくすことができる。これにより配向不良や表示品位の低下を抑制することが可能となる。

**【0324】**

以上から、本実施例のPVA方式の液晶表示装置では、実施例1に記載された効果に加えて、さらに、対称性があり視角特性のよい表示を得ることができる。

**【0325】**

なお本実施例は、必要であれば実施の形態、実施例1～実施例7の構成全てあるいはその一部と組み合わせることが可能である。

**【実施例9】**

**【0326】**

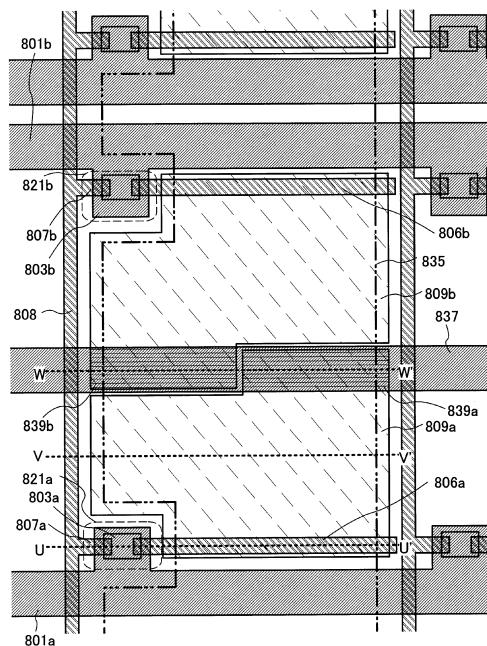

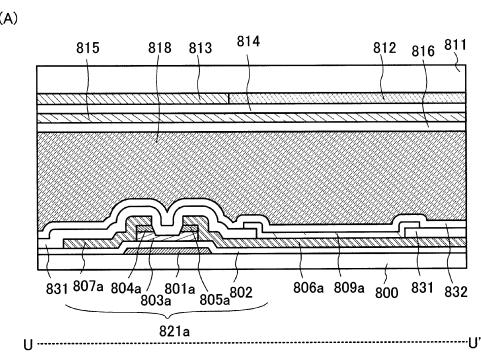

本実施例では、サブピクセル分割駆動方式の液晶表示装置について、図36、図37(A)～図37(B)、図38を用いて説明する。

**【0327】**

サブピクセル分割駆動方式では、一画素を複数のサブピクセルに分割して駆動する。

**【0328】**

図36は、本実施例のサブピクセル分割駆動方式の液晶表示装置において、任意の一画素の上面図である。また図37(A)～図37(B)及び図38は、それぞれ図36中のU-U'線、V-V'線及びW-W'線に沿った断面図である。

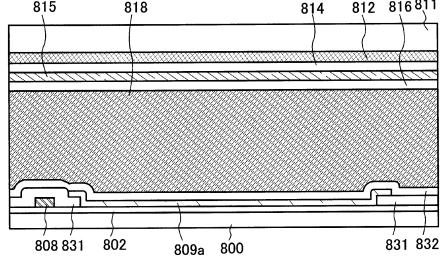

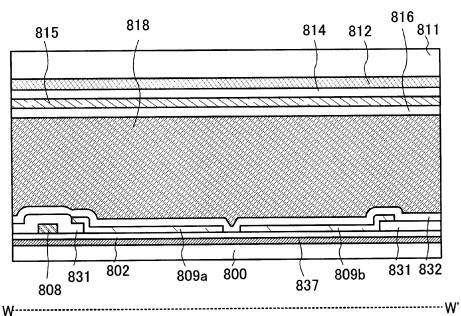

**【0329】**

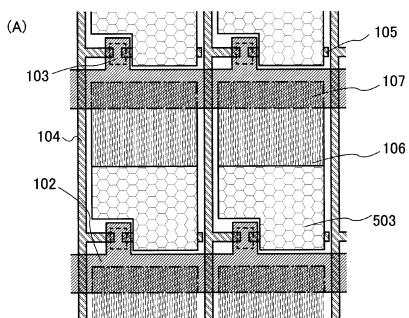

図36、図37(A)～図37(B)、図38において、基板800上に、ゲート配線801(801a、801b)、及び、ゲート配線801上にゲート絶縁膜802が形成されている。

**【0330】**

なお、基板800は実施の形態で述べた基板100と同様の材料を用いればよい。またゲート配線801(801a、801b)は、実施の形態のゲート電極及びゲート配線102と同様の材料及び同様の作製工程で形成すればよい。さらにゲート絶縁膜802は、実施の形態のゲート絶縁膜108と同様の材料及び同様の作製工程で形成すればよい。

**【0331】**

サブピクセル分割駆動方式の液晶表示装置においては、一画素につきスイッチング素子である画素TFTが複数形成される。本実施例では、一画素につき2つの画素TFTであるTFT821aとTFT821bが形成されている。

**【0332】**

TFT821aには、ゲート配線801a、ゲート絶縁膜802、島状半導体膜803a、ソース領域804a、ドレイン領域805a、ソース電極807a及びドレイン電極806aを有している(図37(A)参照)。なおTFT821bはTFT821aと同じ構造であり、ゲート配線801b、ゲート絶縁膜802、島状半導体膜803b、ソース領域804b(図示せず)、ドレイン領域805b(図示せず)、ソース電極807b及びドレイン電極806bを有している。

**【0333】**

なおTFT821aの島状半導体膜803a及びTFT821bの島状半導体膜803b、ソース領域804a及び804b、ドレイン領域805a及び805bは、それぞれ実施の形態の島状半導体膜203、ソース領域204、ドレイン領域205の形成方法を基に形成すればよい。

**【0334】**

ソース電極807a及び807b、並びにソース配線808は便宜上分けてあるが、同一の導電膜から形成され互いに接続されている。またドレイン電極806a及び806b

10

20

30

40

50

も、ソース電極 807a 及び 807b 並びにソース配線 808 と同一の材料及び同じ工程で形成される。

【0335】

保護膜 831 は、実施の形態で述べた保護膜 109 と同じ材料及び同じ作製工程で形成すればよい。また保護膜 831 は、二点鎖線で示される開口部 835 では除去されており、開口部 835 に形成されている絶縁膜はゲート絶縁膜 802 のみとなっている。

【0336】

ソース電極 807a 及び 807b、並びにソース配線 808 は、実施の形態のソース電極及びソース配線 104、またドレン電極 806a 及び 806b は、実施の形態のドレン電極 105 と同様の材料及び同じ工程で形成すればよい。

10

【0337】

TFT821a には画素電極 809a が設けられており、画素電極 809a はドレン電極 806a と開口部 835 において直接接続されている。同様に、TFT821b には画素電極 809b が設けられており、画素電極 809b はドレン電極 806b と開口部 835 において直接接続されている。

【0338】

なお、画素電極 809a 及び 809b は、実施の形態で述べた画素電極 106 と同様の材料及び同様の作製工程で形成すればよい。

【0339】

画素電極 809a と画素電極 809b の面積は、同じでもよいし、違っていてもよい。画素電極 809a と画素電極 809b の面積比は、必要に応じて適宜変更すればよい。例えば、画素電極 809a と画素電極 809b の面積比を 5 : 5 や、1 : 9 や、3 : 7 や、6 : 4 や、8 : 2 等にすることが可能である。

20

【0340】

また画素電極 809a と補助容量線 837 が重なる領域には、ゲート絶縁膜 802 を挟んで、補助容量 839a が形成される。同様に、画素電極 809b と補助容量線 837 が重なる領域には、ゲート絶縁膜 802 を挟んで、補助容量 839b が形成される。

【0341】

補助容量線 837 は、ゲート電極及びゲート配線 801a 及び 801b と同じ材料及び同じ層に形成すればよい。

30

【0342】

保護膜 831 並びに画素電極 809a 及び 809b 上には、配向膜 832 を形成する。配向膜 832 は、液滴吐出法やスクリーン印刷法やオフセット印刷法を用いて形成すればよい。

【0343】

また、対向基板 811 には、着色層 812、遮光層（ブラックマトリクス）813、及びオーバーコート層 814 からなるカラーフィルタを設け、さらに透明電極からなる対向電極 815 と、その上に配向膜 816 が形成されている。

【0344】

液晶 818 は、実施の形態の記載に基づいて、基板 800 及び対向基板 811 の間に形成される。

40

【0345】

本実施例に示すように、一画素を複数のサブピクセルに分割することにより、階調表示の向上が可能となる。

【0346】

以上から、本実施例のサブピクセル分割方式の液晶表示装置では、実施例 1 に記載された効果に加えて、さらに、階調表示が向上した液晶表示装置を得ることができる。

【0347】

なお本実施例は、必要であれば実施の形態、実施例 1 ~ 実施例 8 の構成全てあるいはその一部と組み合わせることが可能である。

50

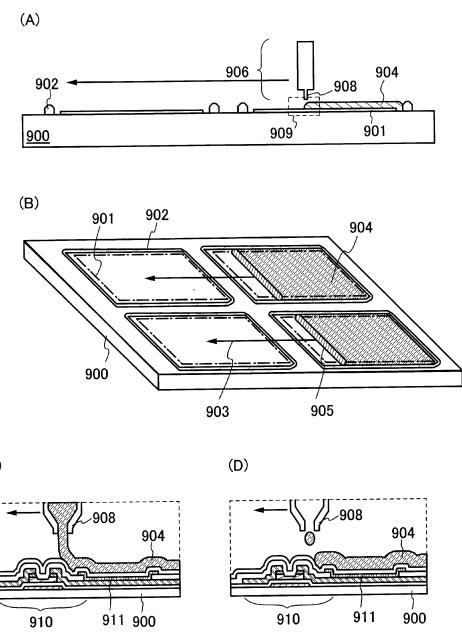

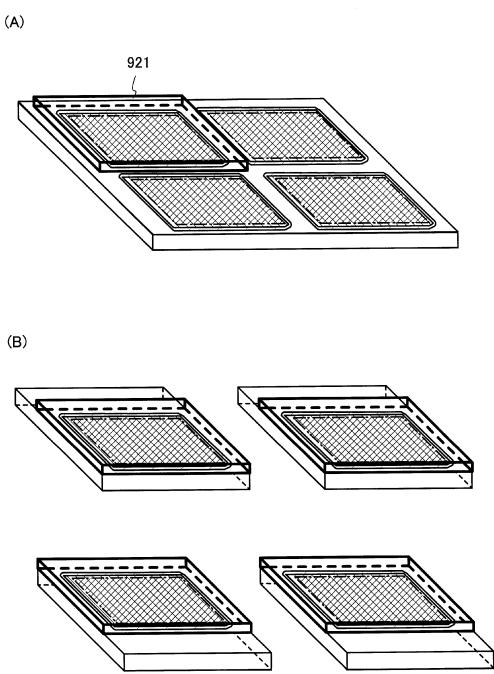

**【実施例 10】****【0348】**

本実施例では、液晶滴下に液滴吐出法を用いる例を示す。本実施例では、大面積基板からパネルを4枚取る例を、図39(A)～図39(D)、図40(A)～図40(B)、図41(A)～図41(B)及び図42(A)～図42(B)を用いて説明する。

**【0349】**

図39(A)は、ディスペンサ(またはインクジェット)による液晶層形成の途中の断面図を示しており、シール材902で囲まれた画素部901を覆うように液晶材料904を液滴吐出装置906のノズル908から吐出、噴射、または滴下させている。液滴吐出装置906は、図39(A)中の矢印で示す移動方向903に移動させる。なお、ここではノズル908を移動させた例を示したが、ノズルを固定し、基板900を移動させることによって液晶層を形成してもよい。

**【0350】**

また、図39(B)には斜視図を示している。シール材902で囲まれた領域のみに選択的に液晶材料904を吐出、噴射、または滴下させ、ノズル走査方向903に合わせて滴下面905が移動している様子を示している。

**【0351】**

また、図39(A)の点線で囲まれた部分909を拡大した断面図が図39(C)及び図39(D)である。液晶材料904の粘性が高い場合は、連続的に吐出され、図39(C)のように繋がったまま付着される。一方、液晶材料904の粘性が低い場合には、間欠的に吐出され、図39(D)に示すようにドット状に液滴が滴下される。

**【0352】**

なお、図39(C)及び図39(D)中、900は基板、910はTFT、911は画素電極をそれぞれ指している。画素部901は、マトリクス状に配置された画素電極911と、画素電極911と接続されているスイッチング素子、ここでは実施の形態及び実施例1の記載に基づいて作製されたTFT910と、保持容量とで構成されている。

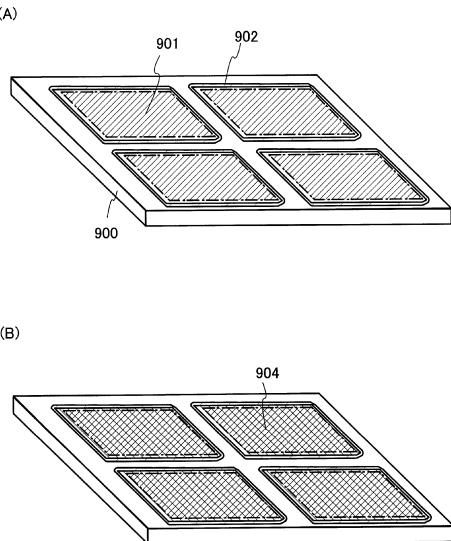

**【0353】**

ここで、図40(A)～図40(B)及び図41(A)～図41(B)を用いて、パネル作製の流れを以下に説明する。

**【0354】**

まず、絶縁表面に画素部901が形成された第1の基板900を用意する。第1の基板900は、予め、配向膜の形成、ラビング処理、球状スペーサ散布、或いは柱状スペーサ形成、またはカラーフィルタの形成などを行っておく。次いで、図40(A)に示すように、不活性気体雰囲気または減圧下で第1の基板900上にディスペンサ装置またはインクジェット装置でシール材902を画素部901を囲む位置に形成する。半透明なシール材902としてはフィラー(直径 $6\text{ }\mu\text{m}$ ～ $24\text{ }\mu\text{m}$ )を含み、且つ、粘度40～400Pa·sのものを用いる。なお、後に接する液晶に溶解しないシール材料を選択することが好ましい。シール材としては、アクリル系光硬化樹脂やアクリル系熱硬化樹脂を用いればよい。また、簡単なシールパターンであるのでシール材902は、印刷法で形成することもできる。

**【0355】**

次いで、シール材902に囲まれた領域に液晶材料904をインクジェット法により滴下する(図40(B))。液晶材料904としては、インクジェット法によって吐出可能な粘度を有する公知の液晶材料を用いればよい。また、液晶材料904は温度を調節することによって粘度を設定することができるため、インクジェット法に適している。インクジェット法により無駄なく必要な量だけの液晶材料904をシール材902に囲まれた領域に保持することができる。

**【0356】**

次いで、画素部901が設けられた第1の基板900と、対向電極や配向膜が設けられ

10

20

30

40

50

た第2の基板921とを気泡が入らないように減圧下で貼りあわせる(図41(A))。ここでは、貼りあわせると同時に紫外線照射や熱処理を行って、シール材902を硬化させる。なお、紫外線照射に加えて、熱処理を行ってもよい。

#### 【0357】

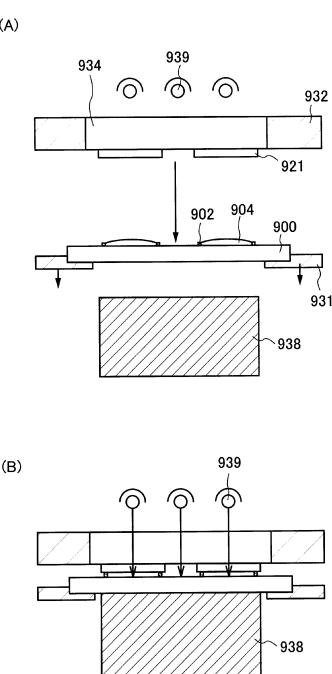

また、図42(A)～図42(B)に貼り合わせ時または貼り合わせ後に紫外線照射や熱処理が可能な貼り合わせ装置の例を示す。

#### 【0358】

図42(A)～図42(B)中、931は第1基板支持台、932は第2基板支持台、934は窓、938は下側定盤、939は光源である。なお、図42(A)～図42(B)において、図39(A)～図39(D)、図40(A)～図40(B)、図41(A)～図41(B)と対応する部分は同一の符号を用いている。10

#### 【0359】

下側定盤938は加熱ヒータが内蔵されており、シール材902を硬化させる。また、第2基板支持台932には窓934が設けられており、光源939からの紫外光などの光を通過させるようになっている。ここでは図示していないが窓934を通して基板の位置アライメントを行う。また、対向基板となる第2の基板921は予め、所望のサイズに切断しておき、第2基板支持台932に真空チャックなどで固定しておく。図42(A)は貼り合わせ前の状態を示している。

#### 【0360】

貼り合わせ時には、第1基板支持台931と第2基板支持台932とを下降させた後、20

圧力をかけて第1の基板900と第2の基板921を貼り合わせ、そのまま紫外光を照射することによって硬化させる。貼り合わせ後の状態を図42(B)に示す。

#### 【0361】

次いで、スクライバー装置、ブレイカー装置、ロールカッターなどの切断装置を用いて第1の基板900を切断する(図41(B)参照)。こうして、1枚の基板から4つのパネルを作製することができる。そして、公知の技術を用いてFPCを貼りつける。

#### 【0362】

以上の工程によって大面積基板を用いた液晶表示装置が作製される。

#### 【0363】

また、本実施例は、必要であれば実施の形態、実施例1～実施例9の構成全てあるいはその一部と自由に組み合わせることが可能である。30

#### 【実施例11】

#### 【0364】

本発明が適用される電子機器として、テレビ、ビデオカメラ、デジタルカメラ、ゴーグル型ディスプレイ、ナビゲーションシステム、音響再生装置(カーオーディオコンポ等)、コンピュータ、ゲーム機器、携帯情報端末(モバイルコンピュータ、携帯電話、携帯型ゲーム機または電子書籍等)、記録媒体を備えた画像再生装置(具体的にはDigital Versatile Disc(DVD)等の記録媒体を再生し、その画像を表示しうるディスプレイを備えた装置)などが挙げられる。それらの電子機器の具体例を、図43、図44、図45(A)～図45(B)、図46(A)～図46(B)、図47、図48(A)～図48(E)、図49(A)～図49(B)に示す。40

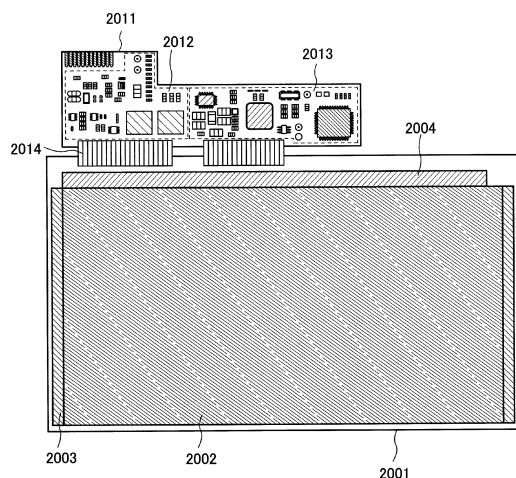

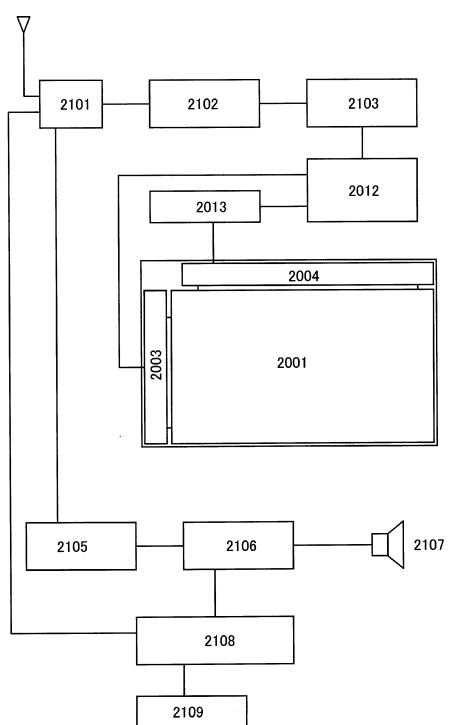

#### 【0365】

図43は液晶表示パネル2001と、回路基板2011を組み合わせた液晶モジュールを示している。回路基板2011には、コントロール回路2012や信号分割回路2013などが形成されており、接続配線2014によって本発明を用いて形成された液晶表示パネル2001と電気的に接続されている。

#### 【0366】

この液晶表示パネル2001には、複数の画素が設けられた画素部2002と、走査線駆動回路2003、選択された画素にビデオ信号を供給する信号線駆動回路2004を備えている。液晶表示パネル2001は、実施の形態及び実施例1～実施例10に基づいて50

作製すればよい。

**【0367】**

図43に示す液晶モジュールにより液晶テレビ受像器を完成させることができる。図44は、液晶テレビ受像機の主要な構成を示すブロック図である。チューナ2101は映像信号と音声信号を受信する。映像信号は、映像信号增幅回路2102と、そこから出力される信号を赤、緑、青の各色に対応した色信号に変換する映像信号処理回路2103と、その映像信号をドライバICの入力仕様に変換するためのコントロール回路2012により処理される。コントロール回路2012は、走査線側と信号線側にそれぞれ信号が出力する。デジタル駆動する場合には、信号線側に信号分割回路2013を設け、入力デジタル信号をm個に分割して供給する構成としても良い。

10

**【0368】**

チューナ2101で受信した信号のうち、音声信号は音声信号增幅回路2105に送られ、その出力は音声信号処理回路2106を経てスピーカ2107に供給される。制御回路2108は受信局(受信周波数)や音量の制御情報を入力部2109から受け、チューナ2101や音声信号処理回路2106に信号を送出する。

**【0369】**

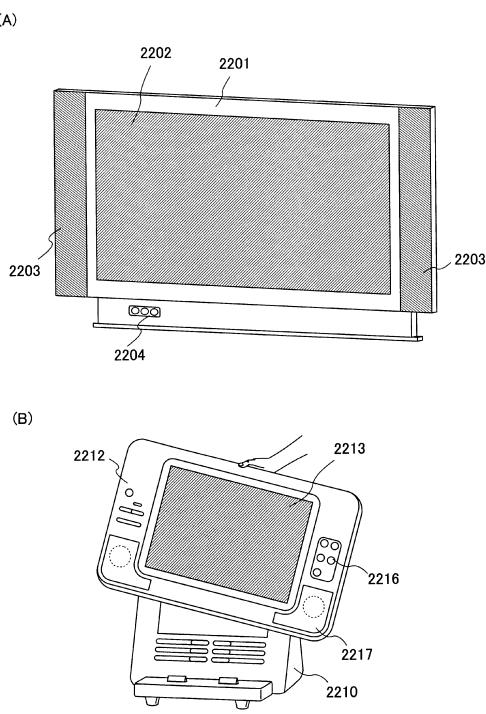

図45(A)に示すように、液晶モジュールを筐体2201に組みこんで、テレビ受像機を完成させることができる。液晶モジュールにより、表示画面2202が形成される。また、スピーカ2203、操作スイッチ2204などが適宜備えられている。

**【0370】**

また図45(B)に、ワイヤレスでディスプレイのみを持ち運び可能なテレビ受像器を示す。筐体2212にはバッテリー及び信号受信器が内蔵されており、そのバッテリーで表示部2213やスピーカ部2217を駆動させる。バッテリーは充電器2210で繰り返し充電が可能となっている。また、充電器2210は映像信号を送受信することができる、その映像信号をディスプレイの信号受信器に送信することができる。筐体2212は操作キー2216によって制御する。また、図45(B)に示す装置は、操作キー2216を操作することによって、筐体2212から充電器2210に信号を送ることも可能であるため映像音声双方向通信装置とも言える。また、操作キー2216を操作することによって、筐体2212から充電器2210に信号を送り、さらに充電器2210が送信できる信号を他の電子機器に受信させることによって、他の電子機器の通信制御も可能であり、汎用遠隔制御装置とも言える。本発明は表示部2213に適用することができる。

20

**【0371】**

本発明を図43、図44、図45(A)~図45(B)に示すテレビ受像器使用することにより、品質のよい表示装置を備えたテレビ受像器を得ることが可能となる。

**【0372】**

勿論、本発明はテレビ受像機に限定されず、パソコンコンピュータのモニタをはじめ、鉄道の駅や空港などにおける情報表示盤や、街頭における広告表示盤など特に大面積の表示媒体として様々な用途に適用することができる。

**【0373】**

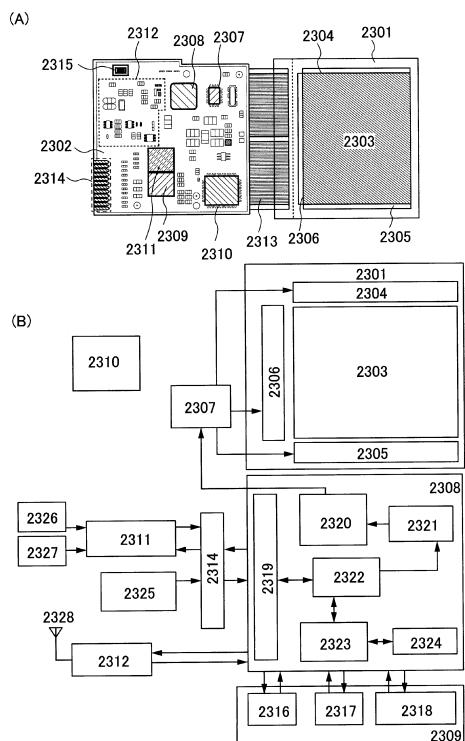

図46(A)は本発明を用いて形成された液晶表示パネル2301とプリント配線基板2302を組み合わせたモジュールを示している。液晶表示パネル2301は、複数の画素が設けられた画素部2303と、第1の走査線駆動回路2304、第2の走査線駆動回路2305と、選択された画素にビデオ信号を供給する信号線駆動回路2306を備えている。

30

**【0374】**

プリント配線基板2302には、コントローラ2307、中央処理装置(CPU)2308、メモリ2309、電源回路2310、音声処理回路2311及び送受信回路2312などが備えられている。プリント配線基板2302と液晶表示パネル2301は、フレキシブル・プリント・サーキット(FPC)2313により接続されている。プリント配線基板2302には、容量素子、バッファ回路などを設け、電源電圧や信号にノイズがの

40

50

ったり、信号の立ち上がりが鈍ったりすることを防ぐ構成としても良い。また、コントローラ 2307、音声処理回路 2311、メモリ 2309、CPU 2308、電源回路 2310などは、COG (Chip On Glass) 方式を用いて液晶表示パネル 2301に実装することもできる。COG 方式により、プリント配線基板 2302 の規模を縮小することができる。

#### 【0375】

プリント配線基板 2302 に備えられたインターフェース (I/F) 2314 を介して、各種制御信号の入出力が行われる。また、アンテナとの間の信号の送受信を行なうためのアンテナ用ポート 2315 が、プリント配線基板 2302 に設けられている。

#### 【0376】

図 46 (B) は、図 46 (A) に示したモジュールのブロック図を示す。このモジュールは、メモリ 2309 として VRAM 2316、DRAM 2317、フラッシュメモリ 2318 などが含まれている。VRAM 2316 にはパネルに表示する画像のデータが、DRAM 2317 には画像データまたは音声データが、フラッシュメモリには各種プログラムが記憶されている。

#### 【0377】

電源回路 2310 は、液晶表示パネル 2301、コントローラ 2307、CPU 2308、音声処理回路 2311、メモリ 2309、送受信回路 2312 を動作させる電力を供給する。またパネルの仕様によっては、電源回路 2310 に電流源が備えられている場合もある。

#### 【0378】

CPU 2308 は、制御信号生成回路 2320、デコーダ 2321、レジスタ 2322、演算回路 2323、RAM 2324、CPU 2308 用のインターフェース 2319 などを有している。インターフェース 2319 を介して CPU 2308 に入力された各種信号は、一旦レジスタ 2322 に保持された後、演算回路 2323、デコーダ 2321 などに入力される。演算回路 2323 では、入力された信号に基づき演算を行ない、各種命令を送る場所を指定する。一方デコーダ 2321 に入力された信号はデコードされ、制御信号生成回路 2320 に入力される。制御信号生成回路 2320 は入力された信号に基づき、各種命令を含む信号を生成し、演算回路 2323 において指定された場所、具体的にはメモリ 2309、送受信回路 2312、音声処理回路 2311、コントローラ 2307 などに送る。

#### 【0379】

メモリ 2309、送受信回路 2312、音声処理回路 2311、コントローラ 2307 は、それぞれ受けた命令に従って動作する。以下その動作について簡単に説明する。

#### 【0380】

入力手段 2325 から入力された信号は、インターフェース 2314 を介してプリント配線基板 2302 に実装された CPU 2308 に送られる。制御信号生成回路 2320 は、ポインティングデバイスやキーボードなどの入力手段 2325 から送られてきた信号に従い、VRAM 2316 に格納してある画像データを所定のフォーマットに変換し、コントローラ 2307 に送付する。

#### 【0381】

コントローラ 2307 は、パネルの仕様に合わせて CPU 2308 から送られてきた画像データを含む信号にデータ処理を施し、液晶表示パネル 2301 に供給する。またコントローラ 2307 は、電源回路 2310 から入力された電源電圧や CPU 2308 から入力された各種信号をもとに、H sync 信号、V sync 信号、クロック信号 CLK、交流電圧 (AC Cont)、切り替え信号 L/R を生成し、液晶表示パネル 2301 に供給する。

#### 【0382】

送受信回路 2312 では、アンテナ 2328 において電波として送受信される信号が処理されており、具体的にはアイソレータ、バンドパスフィルタ、VCO (Voltage

10

20

30

40

50

Controlled Oscillator)、LPF (Low Pass Filter)、カプラ、バランなどの高周波回路を含んでいる。送受信回路2312において送受信される信号のうち音声情報を含む信号が、CPU2308からの命令に従って、音声処理回路2311に送られる。

【0383】

CPU2308の命令に従って送られてきた音声情報を含む信号は、音声処理回路2311において音声信号に復調され、スピーカ2327に送られる。またマイク2326から送られてきた音声信号は、音声処理回路2311において変調され、CPU2308からの命令に従って、送受信回路2312に送られる。

【0384】

コントローラ2307、CPU2308、電源回路2310、音声処理回路2311、メモリ2309を、本実施例のパッケージとして実装することができる。本実施例は、アイソレータ、バンドパスフィルタ、VCO (Voltage Controlled Oscillator)、LPF (Low Pass Filter)、カプラ、バランなどの高周波回路以外であれば、どのような回路にも応用することができる。

【0385】

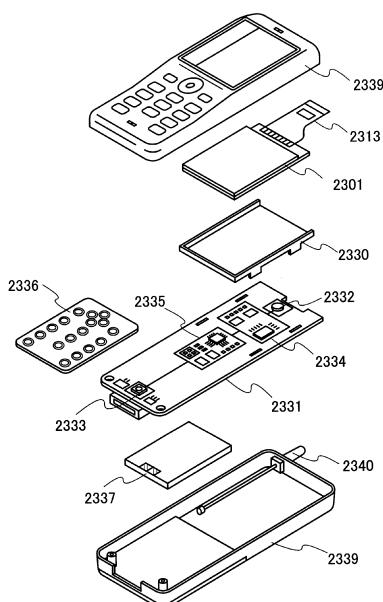

図47は、図46(A)～図46(B)に示すモジュールを含む携帯電話機の一態様を示している。液晶表示パネル2301はハウジング2330に脱着自在に組み込まれる。ハウジング2330は液晶表示パネル2301のサイズに合わせて、形状や寸法を適宜変更することができる。液晶表示パネル2301を固定したハウジング2330はプリント基板2331に嵌着されモジュールとして組み立てられる。

【0386】

液晶表示パネル2301はFPC2313を介してプリント基板2331に接続される。プリント基板2331には、スピーカ2332、マイクロフォン2333、送受信回路2334、CPU及びコントローラなどを含む信号処理回路2335が形成されている。このようなモジュールと、入力手段2336、バッテリ2337、アンテナ2340を組み合わせ、筐体2339に収納する。液晶表示パネル2301の画素部は筐体2339に形成された開口窓から視認できよう配置する。

【0387】

本実施例に係る携帯電話機は、その機能や用途に応じてさまざまな態様に変容し得る。例えば、表示パネルを複数備えたり、筐体を適宜複数に分割して蝶番により開閉式とした構成としても、上記した作用効果を奏することができる。

できる。

【0388】

本発明を図46(A)～図46(B)、図47に示す携帯電話に使用することにより、品質のよい表示装置を備えた携帯電話を得ることが可能となる。

【0389】

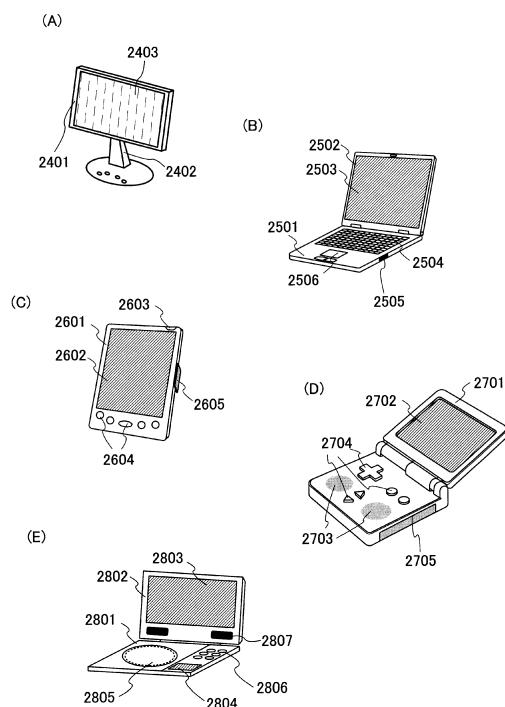

図48(A)は液晶ディスプレイであり、筐体2401、支持台2402、表示部2403などによって構成されている。本発明は表示部2403に適用が可能である。

【0390】

本発明を使用することにより、品質のよい表示装置を備えた液晶ディスプレイを得ることが可能となる。

【0391】

図48(B)はコンピュータであり、本体2501、筐体2502、表示部2503、キーボード2504、外部接続ポート2505、ポインティングマウス2506等を含む。本発明は表示部2503に適用することができる。

【0392】

本発明を使用することにより、品質のよい表示装置を備えたコンピュータを得ることが可能となる。

【0393】

10

20

30

40

50

図48( C )は携帯可能なコンピュータであり、本体2601、表示部2602、スイッチ2603、操作キー2604、赤外線ポート2605等を含む。本発明は表示部2602に適用することができる。

**【0394】**

本発明を使用することにより、品質のよい表示装置を備えたコンピュータを得ることが可能となる。

**【0395】**

図48( D )は携帯型のゲーム機であり、筐体2701、表示部2702、スピーカ部2703、操作キー2704、記録媒体挿入部2705等を含む。本発明は表示部2702に適用することができる。

10

**【0396】**

本発明を使用することにより、品質のよい表示装置を備えたゲーム機を得ることが可能となる。

**【0397】**

図48( E )は記録媒体を備えた携帯型の画像再生装置（具体的にはDVD再生装置）であり、本体2801、筐体2802、表示部A2803、表示部B2804、記録媒体（DVD等）読込部2805、操作キー2806、スピーカ部2807等を含む。表示部A2803は主として画像情報を表示し、表示部B2804は主として文字情報を表示する。本発明は表示部A2803、表示部B2804及び制御用回路部等に適用することができる。なお、記録媒体を備えた画像再生装置には家庭用ゲーム機器なども含まれる。

20

**【0398】**

本発明を使用することにより、品質のよい表示装置を備えた画像再生装置を得ることが可能となる。

**【0399】**

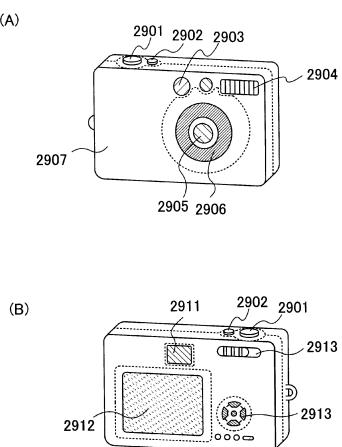

図49( A )及び図49( B )は、本発明の液晶表示装置をカメラ、例えばデジタルカメラに組み込んだ例を示す図である。図49( A )は、デジタルカメラの前面方向から見た斜視図、図49( B )は、後面方向から見た斜視図である。図49( A )において、デジタルカメラには、リリースボタン2901、メインスイッチ2902、ファインダ窓2903、フラッシュ2904、レンズ2905、鏡胴2906、筐体2907が備えられている。

30

**【0400】**

また、図49( B )において、ファインダ接眼窓2911、モニタ2912、操作ボタン2913が備えられている。

**【0401】**

リリースボタン2901は、半分の位置まで押下されると、焦点調整機構および露出調整機構が作動し、最下部まで押下されるとシャッターが開く。

**【0402】**

メインスイッチ2902は、押下又は回転によりデジタルカメラの電源のON/OFFを切り替える。

**【0403】**

ファインダ窓2903は、デジタルカメラの前面のレンズ2905の上部に配置されており、図49( B )に示すファインダ接眼窓2911から撮影する範囲やピントの位置を確認するための装置である。

40

**【0404】**

フラッシュ2904は、デジタルカメラの前面上部に配置され、被写体輝度が低いときに、リリースボタン2901が押下されてシャッターが開くと同時に補助光を照射する。

**【0405】**

レンズ2905は、デジタルカメラの正面に配置されている。レンズは、フォーカシングレンズ、ズームレンズ等により構成され、図示しないシャッター及び絞りと共に撮影光学系を構成する。また、レンズの後方には、CCD(Charge Coupled D

50

e v i c e ) 等の撮像素子が設けられている。

**【 0 4 0 6 】**

鏡胴 2 9 0 6 は、フォーカシングレンズ、ズームレンズ等のピントを合わせるためにレンズの位置を移動するものであり、撮影時には、鏡胴を繰り出すことにより、レンズ 2 9 0 5 を手前に移動させる。また、携帯時は、レンズ 2 9 0 5 を沈銅させてコンパクトにする。なお、本実施例においては、鏡胴を繰り出すことにより被写体をズーム撮影することができる構造としているが、この構造に限定されるものではなく、筐体 2 9 0 7 内での撮影光学系の構成により鏡胴を繰り出さずともズーム撮影が可能なデジタルカメラでもよい。

**【 0 4 0 7 】**

ファインダ接眼窓 2 9 1 1 は、デジタルカメラの後面上部に設けられており、撮影する範囲やピントの位置を確認する際に接眼するために設けられた窓である。

**【 0 4 0 8 】**

操作ボタン 2 9 1 3 は、デジタルカメラの後面に設けられた各種機能ボタンであり、セットアップボタン、メニューボタン、ディスプレイボタン、機能ボタン、選択ボタン等により構成されている。

**【 0 4 0 9 】**

本発明の液晶表示装置は、図 4 9 ( A ) 及び図 4 9 ( B ) に示すカメラのモニタ 2 9 1 2 に組み込むことができる。これにより品質のよい表示装置を備えたデジタルカメラを得ることが可能となる。

**【 0 4 1 0 】**

なお、本実施例に示した例はごく一例であり、これらの用途に限定するものではないことを付記する。

**【 0 4 1 1 】**

また本実施例は、実施の形態及び実施例 1 ~ 実施例 1 0 の構成全てあるいはその一部と自由に組み合せて実施することが可能である。

**【 産業上の利用可能性 】**

**【 0 4 1 2 】**

本発明により、保護膜を開口部になるべく重ならないように形成することで、開口部が増大した表示装置を得ることができる。さらに本発明では、開口部をソース配線に平行に列方向に延在させることにより、保護膜形成のための絶縁膜のエッチングの際に発生する残渣を低減することができ、残渣に由来する画素電極とドレイン電極とのコンタクト不良を低減することができる。

**【 0 4 1 3 】**

また本発明によって、品質のよい表示装置を備えた電子機器を得ることが可能となる。

**【 符号の説明 】**

**【 0 4 1 4 】**

1 0 0 基板

1 0 1 開口部

1 0 2 ゲート電極及びゲート配線

1 0 3 島状半導体膜

1 0 3 a 島状非晶質半導体膜

1 0 3 b 島状不純物半導体膜

1 0 4 ソース電極及びソース配線

1 0 5 ドレイン電極

1 0 6 画素電極

1 0 7 補助容量

1 0 8 ゲート絶縁膜

1 0 9 保護膜

2 0 1 T F T

10

20

30

40

50

|       |                                                       |    |

|-------|-------------------------------------------------------|----|

| 2 0 3 | 島状半導体膜                                                |    |

| 2 0 4 | ソース領域                                                 |    |

| 2 0 5 | ドレイン領域                                                |    |

| 2 0 6 | チャネル形成領域                                              |    |

| 2 0 8 | 配向膜                                                   |    |

| 2 1 1 | 対向基板                                                  |    |

| 2 1 2 | 着色層                                                   |    |

| 2 1 3 | 遮光層(ブラックマトリクス)                                        |    |

| 2 1 4 | オーバーコート層                                              |    |

| 2 1 5 | 対向電極                                                  | 10 |

| 2 1 6 | 配向膜                                                   |    |

| 2 1 8 | 液晶                                                    |    |

| 2 2 1 | シール材                                                  |    |

| 2 2 2 | F P C ( F l e x i b l e P r i n t e d C i r c u i t ) |    |

| 2 3 1 | 画素部                                                   |    |

| 3 0 0 | 基板                                                    |    |

| 3 0 1 | 開口部                                                   |    |

| 3 0 2 | ゲート電極及びゲート配線                                          |    |

| 3 0 3 | 島状半導体膜                                                |    |

| 3 0 4 | ソース電極及びソース配線                                          | 20 |

| 3 0 5 | ドレイン電極                                                |    |

| 3 0 6 | 画素電極                                                  |    |

| 3 0 7 | 補助容量                                                  |    |

| 3 0 8 | ゲート絶縁膜                                                |    |

| 3 0 9 | 保護膜                                                   |    |

| 3 1 4 | ソース領域                                                 |    |

| 3 1 5 | ドレイン領域                                                |    |

| 3 1 7 | レジストマスク                                               |    |

| 3 2 1 | 非晶質半導体膜                                               |    |

| 3 2 2 | 一導電型を付与する不純物を含有する半導体膜                                 | 30 |

| 3 2 3 | 導電膜                                                   |    |

| 3 3 0 | 基板                                                    |    |

| 3 3 1 | 開口部                                                   |    |

| 3 3 2 | ゲート電極及びゲート配線                                          |    |

| 3 3 3 | 島状半導体膜                                                |    |

| 3 3 4 | ソース電極及びソース配線                                          |    |

| 3 3 5 | ドレイン電極                                                |    |

| 3 3 6 | 画素電極                                                  |    |

| 3 3 7 | レジストマスク                                               |    |

| 3 3 8 | ゲート絶縁膜                                                | 40 |

| 3 3 9 | 保護膜                                                   |    |

| 3 4 1 | 非晶質半導体膜                                               |    |

| 3 4 2 | 一導電型を付与する不純物を含有する半導体膜                                 |    |

| 3 4 4 | ソース領域                                                 |    |

| 3 4 5 | ドレイン領域                                                |    |

| 3 4 6 | 導電膜                                                   |    |

| 4 0 1 | 下層ソース電極及びソース配線                                        |    |

| 4 0 2 | 下層ドレイン電極                                              |    |

| 4 0 3 | 上層ソース電極及びソース配線                                        |    |

| 4 0 4 | 電極                                                    | 50 |

|       |                |    |

|-------|----------------|----|

| 4 0 6 | 絶縁膜            |    |

| 4 0 7 | 保護膜            |    |

| 4 0 8 | 上層ドレイン電極       |    |

| 4 0 9 | 電極             |    |

| 4 1 1 | 開口部            |    |

| 4 1 4 | ソース電極及びソース配線   |    |

| 4 1 5 | ドレイン電極         |    |

| 4 1 6 | 画素電極           |    |

| 4 3 1 | 下層ソース電極及びソース配線 |    |

| 4 3 2 | 下層ドレイン電極       | 10 |

| 4 3 3 | 中層ソース電極及びソース配線 |    |

| 4 3 4 | 中層ドレイン電極       |    |

| 4 3 5 | 上層ソース電極及びソース配線 |    |

| 4 3 6 | 上層ドレイン電極       |    |

| 4 3 7 | 保護膜            |    |

| 4 3 9 | 絶縁膜            |    |

| 4 4 1 | 開口部            |    |

| 4 4 6 | 画素電極           |    |

| 4 5 4 | ソース電極及びソース配線   |    |

| 4 5 5 | ドレイン電極         | 20 |

| 5 0 1 | 反射電極           |    |

| 5 0 2 | 反射電極           |    |

| 5 0 3 | 反射電極           |    |

| 5 0 4 | 反射電極           |    |

| 5 1 1 | 基板             |    |

| 5 1 2 | 配線             |    |

| 5 1 3 | ゲート絶縁膜         |    |

| 5 1 4 | 配線             |    |

| 5 1 5 | 保護膜            |    |

| 5 1 6 | レジストマスク        | 30 |

| 5 1 7 | 保護膜            |    |

| 5 1 8 | レジストマスク        |    |

| 5 2 1 | 保護膜            |    |

| 5 2 3 | 導電膜            |    |

| 5 2 5 | コンタクトホール       |    |

| 5 2 6 | 開口部            |    |

| 6 0 0 | 基板             |    |

| 6 0 1 | ゲート配線          |    |

| 6 0 2 | コモン配線          |    |

| 6 0 3 | コンタクトホール       | 40 |

| 6 0 4 | 開口部            |    |

| 6 0 5 | ソース配線          |    |

| 6 0 6 | ドレイン電極         |    |

| 6 0 7 | 島状半導体膜         |    |

| 6 0 8 | ソース電極          |    |

| 6 1 1 | 画素電極           |    |

| 6 1 2 | コモン電極          |    |

| 6 1 4 | ゲート絶縁膜         |    |

| 6 1 5 | 保護膜            |    |

| 6 2 1 | ソース領域          | 50 |

|       |                |    |

|-------|----------------|----|

| 6 2 2 | ドレイン領域         |    |

| 6 3 0 | 基板             |    |

| 6 3 1 | ゲート配線          |    |

| 6 3 2 | ゲート絶縁膜         |    |

| 6 3 3 | 島状半導体膜         |    |

| 6 3 4 | ソース領域          |    |

| 6 3 5 | ドレイン領域         |    |

| 6 3 6 | ドレイン電極         |    |

| 6 3 7 | ソース電極          |    |

| 6 3 8 | ソース配線          | 10 |

| 6 3 9 | 画素電極           |    |

| 6 4 1 | 対向基板           |    |

| 6 4 2 | 着色層            |    |

| 6 4 3 | 遮光層（ブラックマトリクス） |    |

| 6 4 4 | オーバーコート層       |    |

| 6 4 5 | 対向電極           |    |

| 6 4 6 | 配向膜            |    |

| 6 4 8 | 液晶             |    |

| 6 5 1 | 保護膜            |    |

| 6 5 2 | 配向膜            | 20 |

| 6 5 3 | 溝              |    |

| 6 5 5 | 突起             |    |

| 6 5 7 | 開口部            |    |

| 6 6 1 | 液晶分子           |    |

| 6 6 3 | 電界             |    |

| 6 6 5 | 補助容量           |    |

| 7 0 0 | 基板             |    |

| 7 0 1 | ゲート配線          |    |

| 7 0 2 | ゲート絶縁膜         |    |

| 7 0 3 | 島状半導体膜         | 30 |

| 7 0 4 | ソース領域          |    |

| 7 0 5 | ドレイン領域         |    |

| 7 0 7 | ソース電極          |    |

| 7 0 6 | ドレイン電極         |    |

| 7 0 8 | ソース配線          |    |