(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第3915963号

(P3915963)

(45) 発行日 平成19年5月16日(2007.5.16)

(24) 登録日 平成19年2月16日(2007.2.16)

(51) Int.C1.

F 1

A63F 7/02 (2006.01)

A 63 F 7/02 334

A 63 F 7/02 304 Z

A 63 F 7/02 324 C

請求項の数 4 (全 48 頁)

(21) 出願番号 特願2000-241930 (P2000-241930)

(22) 出願日 平成12年8月9日 (2000.8.9)

(65) 公開番号 特開2002-52151 (P2002-52151A)

(43) 公開日 平成14年2月19日 (2002.2.19)

審査請求日 平成16年8月31日 (2004.8.31)

前置審査

(73) 特許権者 000144153

株式会社三共

群馬県桐生市境野町6丁目460番地

(74) 代理人 100103090

弁理士 岩壁 冬樹

(74) 代理人 100124501

弁理士 塩川 誠人

(74) 代理人 100134692

弁理士 川村 武

(74) 代理人 100135161

弁理士 真野 修二

(72) 発明者 鶴川 詔八

群馬県桐生市相生町1丁目164番地の5

最終頁に続く

(54) 【発明の名称】遊技機

## (57) 【特許請求の範囲】

## 【請求項 1】

遊技者が所定の遊技を行うことが可能な遊技機であって、

制御を行う際に発生する変動データを記憶する遊技制御用変動データ記憶手段を有し、

遊技の進行を制御する遊技制御用マイクロコンピュータと、

制御を行う際に発生する変動データを記憶する払出制御用変動データ記憶手段を有し、

遊技媒体の払出の制御を行う払出制御用マイクロコンピュータと、

遊技機への電力供給が停止していても前記遊技制御用変動データ記憶手段および前記払

出制御用変動データ記憶手段の記憶内容を所定期間保持させることができ記憶内容保持

手段と、

遊技機で使用される所定の電源の状態を監視して電源断の発生を検出したときに検出信

号を出力する電源監視手段と、

操作に応じて操作信号を出力する初期化操作手段とを備え、

前記遊技制御用マイクロコンピュータは、前記検出信号の入力に応じて、バックアップ

フラグを前記遊技制御用変動データ記憶手段に設定し、かつ、前記遊技制御用変動データ

記憶手段へのアクセスを禁止する遊技制御用電力供給停止時処理を実行した後に待機状態

に移行し、

前記払出制御用マイクロコンピュータは、前記検出信号の入力に応じて、制御状態を前

記払出制御用変動データ記憶手段に保存させるための処理である払出制御用電力供給停止

時処理を実行した後に待機状態に移行し、

前記遊技制御用マイクロコンピュータが前記遊技制御用電力供給停止時処理を完了した後に、前記遊技制御用マイクロコンピュータを動作停止状態とするための信号を出力するリセット手段と、

前記電源監視手段が前記検出信号を出力した後の所定期間経過後に電力供給が停止していないときに、前記待機状態から復帰させるための復帰信号を出力する復帰信号出力手段とを備え、

前記遊技制御用マイクロコンピュータは、

電力供給が開始されたときまたは前記復帰信号の入力に応じて、前記初期化操作手段からの操作信号が入力されているか否かを確認する遊技制御側操作信号確認処理を行い、該遊技制御側操作信号確認処理によって、前記初期化操作手段からの操作信号が入力されていることが確認されなかったときには、前記遊技制御用変動データ記憶手段に前記バックアップフラグが設定されていることを条件に前記遊技制御用変動データ記憶手段に保存されていた記憶内容にもとづいて制御状態を前記遊技制御用電力供給停止時処理を開始したときの状態に復旧させる状態復旧処理を行い、

前記遊技制御側操作信号確認処理によって、前記初期化操作手段からの前記操作信号が入力されていることを確認したときには、前記遊技制御用変動データ記憶手段に前記バックアップフラグが設定されていても、該遊技制御用変動データ記憶手段の記憶内容を初期化する処理を行い、

前記払出制御用マイクロコンピュータは、

電力供給が開始されたときまたは前記復帰信号の入力に応じて、前記初期化操作手段からの操作信号が入力されているか否かを確認する払出制御側操作信号確認処理を行い、該払出制御側操作信号確認処理によって、前記初期化操作手段からの操作信号が入力されていることが確認されなかったことを条件に、前記払出制御用変動データ記憶手段に保存されていた記憶内容にもとづいて制御状態を復旧させる状態復旧処理を行い、

前記払出制御側操作信号確認処理によって、前記初期化操作手段からの前記操作信号が入力されていることを確認したときには、前記払出制御用変動データ記憶手段に記憶内容が保存されていても、該払出制御用変動データ記憶手段の記憶内容を初期化する処理を行い、

前記遊技制御用マイクロコンピュータおよび前記払出制御用マイクロコンピュータは、前記初期化操作手段からの操作信号が入力されているか否かを、遊技媒体を検出するための遊技媒体検出手段からの検出信号を判定する遊技媒体検出判定期間よりも短い要求検出判定期間で確認し、

前記遊技制御用マイクロコンピュータは、受皿に貯留される遊技媒体が満タンになったことを検出するための満タン検出手段からの検出信号が入力されているか否かを、前記遊技媒体検出手段からの検出信号を判定する遊技媒体検出判定期間よりも長い検出判定期間で確認し、前記検出信号が入力されていると判定したときに、前記払出制御用マイクロコンピュータに払出の停止を示す旨のコマンドを送信する

ことを特徴とする遊技機。

#### 【請求項 2】

初期化操作手段からの操作信号は、遊技制御用マイクロコンピュータおよび払出制御用マイクロコンピュータの入力ポート部に入力される

請求項 1 記載の遊技機。

#### 【請求項 3】

復帰信号出力手段は、払出制御用マイクロコンピュータに復帰信号を出力した後に遊技制御用マイクロコンピュータに復帰信号を出力する

請求項 1 または請求項 2 記載の遊技機。

#### 【請求項 4】

待機状態は無限ループである

請求項 1 から請求項 3 のうちのいずれかに記載の遊技機。

#### 【発明の詳細な説明】

10

20

30

40

50

**【0001】****【発明の属する技术分野】**

本発明は、本発明は、遊技者の操作に応じて遊技が行われるパチンコ遊技機、コイン遊技機、スロット機等の遊技機に關し、特に、遊技盤における遊技領域において遊技者の操作に応じて遊技が行われる遊技機に關する。

**【0002】****【従来の技术】**

遊技機の一例として、遊技球などの遊技媒体を発射装置によって遊技領域に発射し、遊技領域に設けられている入賞口などの入賞領域に遊技媒体が入賞すると、所定個の賞球が遊技者に払い出されるものがある。さらに、表示状態が変化可能な可変表示部が設けられ、可変表示部の表示結果があらかじめ定められた特定の表示態様となつた場合に所定の遊技価値を遊技者に与えるように構成されたものがある。

10

**【0003】**

遊技価値とは、遊技機の遊技領域に設けられた可変入賞球装置の状態が打球が入賞しやすい遊技者にとって有利な状態になることや、遊技者にとって有利な状態となるための権利を発生させたりすることや、景品遊技媒体払出の条件が成立しやすくなる状態になることである。

**【0004】**

特別図柄を表示する可変表示部を備えた第1種パチンコ遊技機では、特別図柄を表示する可変表示部の表示結果があらかじめ定められた特定の表示態様の組合せとなることを、通常、「大当たり」という。大当たりが発生すると、例えば、大入賞口が所定回数開放して打球が入賞しやすい大当たり遊技状態に移行する。そして、各開放期間において、所定個（例えば10個）の大入賞口への入賞があると大入賞口は閉成する。そして、大入賞口の開放回数は、所定回数（例えば16ラウンド）に固定されている。なお、各開放について開放時間（例えば29.5秒）が決められ、入賞数が所定個に達しなくても開放時間が経過すると大入賞口は閉成する。また、大入賞口が閉成した時点で所定の条件（例えば、大入賞口内に設けられているVゾーンへの入賞）が成立していない場合には、大当たり遊技状態は終了する。

20

**【0005】**

また、「大当たり」の組合せ以外の表示態様の組合せのうち、複数の可変表示部の表示結果のうちの一部が未だに導出表示されていない段階において、既に確定的な、または一時的な表示結果が導出表示されている可変表示部の表示態様が特定の表示態様の組合せとなる表示条件を満たしている状態を「リーチ」という。そして、可変表示部に可変表示される識別情報の表示結果が「大当たり」となる条件を満たさない場合には「はずれ」となり、可変表示状態は終了する。遊技者は、大当たりをいかにして発生させるかを楽しみつつ遊技を行う。

30

**【0006】**

そして、遊技球が遊技盤に設けられている入賞口に遊技球が入賞すると、あらかじめ決められている個数の賞球払出が行われる。遊技の進行は主基板に搭載された遊技制御手段によって制御されるので、入賞にもとづく賞球個数は、遊技制御手段によって決定され、払出制御基板に送信される。なお、以下、遊技制御手段およびその他の制御手段は、遊技機に設けられている各種電気部品を制御するので、それらを電気部品制御手段と呼ぶことがある。

40

**【0007】****【発明が解決しようとする課題】**

以上のように、遊技機には、遊技制御手段を始めとする種々の電気部品制御手段が搭載されている。一般に、各電気部品制御手段はマイクロコンピュータを含んだ構成とされる。そのような電気部品制御手段は、一般に、電源電圧が立ち上ると初期化処理を行い初期状態から制御を開始する。すると、停電等の不測の電源断生じ、その後、電源復旧すると初期状態に戻ってしまうので、遊技者が得た遊技価値等が消滅してしまう等の問題が生ず

50

あることがある。そのような問題が生じないようにするには、電源電圧値の低下に伴なって発生される所定の信号に応じて遊技制御を中断し、そのときの制御状態を、遊技機に対する電力供給停止中でも電源バックアップされている記憶手段（バックアップ記憶手段）に保存し、電力供給が完全に停止するのを待つように制御すればよい。そのような遊技機は、記憶手段に遊技状態が保存されている状態で電力供給が再開されたら、保存されている制御状態にもとづいて遊技を再開するので、遊技者に不利益が与えられることが防止される。

#### 【0008】

しかし、電源の瞬断等によって極めて短い期間電源電圧が低下したような場合には、電源電圧は直ちに復旧する。そのような場合、マイクロコンピュータの制御が、電力供給が完全に停止するのを待つ状態から抜けきらないことも考えられる。すなわち、遊技機への電力供給は平常時の状態になっているにもかかわらず、遊技機制御が平常時の状態に戻らないことも考えられる。

#### 【0009】

さらに、バックアップ記憶手段に制御状態が保存されている場合に、その内容をクリアしたいときもあるが、バックアップ記憶手段はコンデンサや電池で電力供給されているので、その内容をクリアするには煩雑な作業が必要とされる。例えば、コンデンサを使用している場合には、何らかの方法でコンデンサに蓄えられている電荷を放電しなければならない。電池を用いている場合には、電池をバックアップ記憶手段から切り離さなければならない。

#### 【0010】

そこで、本発明は、不測の電源断時等にそのときの制御状態を保存するように構成されている遊技機において、ごく短時間で復旧する電源の瞬断等が生じても制御に支障を来すことのないようにすることができるとともに、保存されている制御状態を容易にクリアすることができる遊技機を提供することを目的とする。

#### 【0011】

##### 【課題を解決するための手段】

本発明による遊技機は、遊技者が所定の遊技を行うことが可能な遊技機であって、制御を行う際に発生する変動データを記憶する遊技制御用変動データ記憶手段を有し、遊技の進行を制御する遊技制御用マイクロコンピュータと、制御を行う際に発生する変動データを記憶する払出制御用変動データ記憶手段を有し、遊技媒体の払出の制御を行う払出制御用マイクロコンピュータと、遊技機への電力供給が停止していても遊技制御用変動データ記憶手段および払出制御用変動データ記憶手段の記憶内容を所定期間保持させることができ記憶内容保持手段と、遊技機で使用される所定の電源の状態を監視して電源断の発生を検出したときに検出信号を出力する電源監視手段と、操作に応じて操作信号を出力する初期化操作手段とを備え、遊技制御用マイクロコンピュータは、検出信号の入力に応じて、バックアップフラグを遊技制御用変動データ記憶手段に設定し、かつ、遊技制御用変動データ記憶手段へのアクセスを禁止する遊技制御用電力供給停止時処理を実行した後に待機状態に移行し、払出制御用マイクロコンピュータは、検出信号の入力に応じて、制御状態を払出制御用変動データ記憶手段に保存させるための処理である払出制御用電力供給停止時処理を実行した後に待機状態に移行し、遊技制御用マイクロコンピュータが遊技制御用電力供給停止時処理を完了した後に、遊技制御用マイクロコンピュータを動作停止状態とするための信号を出力するリセット手段と、電源監視手段が検出信号を出力した後の所定期間経過後に電力供給が停止していないときに、待機状態から復帰させるための復帰信号を出力する復帰信号出力手段とを備え、遊技制御用マイクロコンピュータは、電力供給が開始されたときまたは復帰信号の入力に応じて、初期化操作手段からの操作信号が入力されているか否かを確認する遊技制御側操作信号確認処理を行い、該遊技制御側操作信号確認処理によって、初期化操作手段からの操作信号が入力されていることが確認されなかつたときには、遊技制御用変動データ記憶手段にバックアップフラグが設定されていることを条件に遊技制御用変動データ記憶手段に保存されていた記憶内容にもとづいて制御状

10

20

30

40

50

態を遊技制御用電力供給停止時処理を開始したときの状態に復旧させる状態復旧処理を行い、遊技制御側操作信号確認処理によって、初期化操作手段からの操作信号が入力されていることを確認したときには、遊技制御用変動データ記憶手段にバックアップフラグが設定されていても、該遊技制御用変動データ記憶手段の記憶内容を初期化する処理を行い、払出制御用マイクロコンピュータは、電力供給が開始されたときまたは復帰信号の入力に応じて、初期化操作手段からの操作信号が入力されているか否かを確認する払出制御側操作信号確認処理を行い、該払出制御側操作信号確認処理によって、初期化操作手段からの操作信号が入力されていることが確認されなかったことを条件に、払出制御用変動データ記憶手段に保存されていた記憶内容にもとづいて制御状態を復旧させる状態復旧処理を行い、払出制御側操作信号確認処理によって、初期化操作手段からの操作信号が入力されていることを確認したときには、払出制御用変動データ記憶手段に記憶内容が保存されても、該払出制御用変動データ記憶手段の記憶内容を初期化する処理を行い、遊技制御用マイクロコンピュータおよび払出制御用マイクロコンピュータは、初期化操作手段からの操作信号が入力されているか否かを、遊技媒体を検出するための遊技媒体検出手段からの検出信号を判定する遊技媒体検出判定期間よりも短い要求検出判定期間で確認し、遊技制御用マイクロコンピュータは、受皿に貯留される遊技媒体が満タンになったことを検出するための満タン検出手段からの検出信号が入力されているか否かを、遊技媒体検出手段からの検出信号を判定する遊技媒体検出判定期間よりも長い検出判定期間で確認し、検出信号が入力されると判定したときに、払出制御用マイクロコンピュータに払出の停止を示す旨のコマンドを送信することを特徴とする。

10

20

#### 【0012】

初期化操作手段からの操作信号は、遊技制御用マイクロコンピュータおよび払出制御用マイクロコンピュータの入力ポート部に入力される。

#### 【0014】

復帰信号出力手段は、払出制御用マイクロコンピュータに復帰信号を出力した後に遊技制御用マイクロコンピュータに復帰信号を出力するように構成されていてもよい。

#### 【0015】

待機状態は、例えば無限ループである。

#### 【0021】

#### 【発明の実施の形態】

30

以下、本発明の一実施形態を図面を参照して説明する。

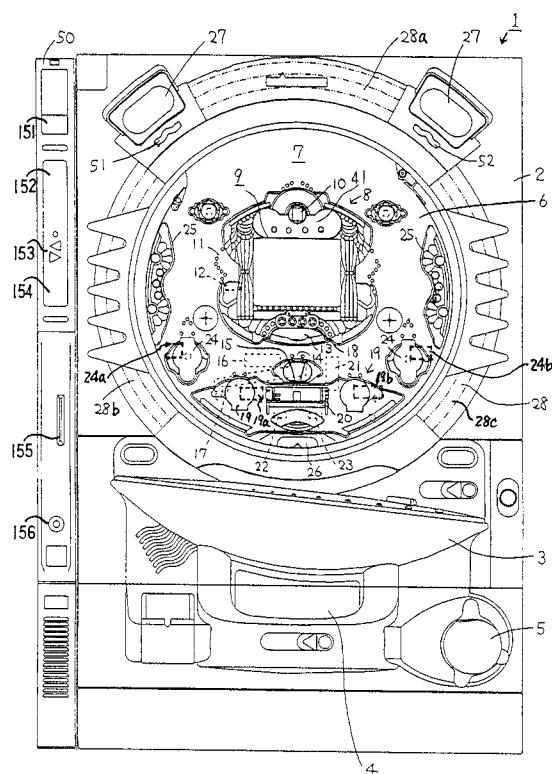

まず、遊技機の一例であるパチンコ遊技機の全体の構成について説明する。図1はパチンコ遊技機1を正面からみた正面図である。なお、ここでは、遊技機の一例としてパチンコ遊技機を示すが、本発明はパチンコ遊技機に限らず、例えばコイン遊技機やスロット機等であってもよい。

#### 【0022】

図1に示すように、パチンコ遊技機1は、額縁状に形成されたガラス扉枠2を有する。ガラス扉枠2の下部表面には打球供給皿3がある。打球供給皿3の下部には、打球供給皿3からあふれた遊技球を貯留する余剰玉受皿4と打球を発射する打球操作ハンドル（操作ノブ）5が設けられている。ガラス扉枠2の後方には、遊技盤6が着脱可能に取り付けられている。また、遊技盤6の前面には遊技領域7が設けられている。

40

#### 【0023】

遊技領域7の中央付近には、複数種類の図柄を可変表示するための可変表示部（特別図柄表示装置）9と7セグメントLEDによる普通図柄表示器（普通図柄表示装置）10とを含む可変表示装置8が設けられている。可変表示部9には、例えば「左」、「中」、「右」の3つの図柄表示エリアがある。可変表示装置8の側部には、打球を導く通過ゲート11が設けられている。通過ゲート11を通過した打球は、玉出口13を経て始動入賞口14の方に導かれる。通過ゲート11と玉出口13との間の通路には、通過ゲート11を通過した打球を検出するゲートスイッチ12がある。また、始動入賞口14に入った入賞球は、遊技盤6の背面に導かれ、始動口スイッチ17によって検出される。また、始動入賞

50

口 14 の下部には開閉動作を行う可変入賞球装置 15 が設けられている。可変入賞球装置 15 は、ソレノイド 16 によって開状態とされる。

【 0 0 2 4 】

可変入賞球装置 15 の下部には、特定遊技状態（大当たり状態）においてソレノイド 21 によって開状態とされる開閉板 20 が設けられている。この実施の形態では、開閉板 20 が大入賞口を開閉する手段となる。開閉板 20 から遊技盤 6 の背面に導かれた入賞球のうち一方（Vゾーン）に入った入賞球はV入賞スイッチ 22 で検出される。また、開閉板 20 からの入賞球はカウントスイッチ 23 で検出される。可変表示装置 8 の下部には、始動入賞口 14 に入った入賞球数を表示する 4 個の表示部を有する始動入賞記憶表示器 18 が設けられている。この例では、4 個を上限として、始動入賞がある毎に、始動入賞記憶表示器 18 は点灯している表示部を 1 つずつ増やす。そして、可変表示部 9 の可変表示が開始される毎に、点灯している表示部を 1 つ減らす。

【 0 0 2 5 】

遊技盤 6 には、複数の入賞口 19, 24 が設けられ、遊技球のそれぞれの入賞口 19, 24 への入賞は、対応して設けられている入賞口スイッチ 19a, 19b, 24a, 24b によって検出される。遊技領域 7 の左右周辺には、遊技中に点滅表示される装飾ランプ 25 が設けられ、下部には、入賞しなかった打球を吸収するアウトロ 26 がある。また、遊技領域 7 の外側の左右上部には、効果音を発する 2 つのスピーカ 27 が設けられている。遊技領域 7 の外周には、遊技効果 LED 28a および遊技効果ランプ 28b, 28c が設けられている。

10

【 0 0 2 6 】

そして、この例では、一方のスピーカ 27 の近傍に、賞球残数があるときに点灯する賞球ランプ 51 が設けられ、他方のスピーカ 27 の近傍に、補給球が切れたときに点灯する球切れランプ 52 が設けられている。さらに、図 1 には、パチンコ遊技機 1 に隣接して設置され、プリペイドカードが挿入されることによって球貸しを可能にするカードユニット 50 も示されている。

20

【 0 0 2 7 】

カードユニット 50 には、使用可能状態であるか否かを示す使用可表示ランプ 151、カード内に記録された残額情報に端数（100円未満の数）が存在する場合にその端数を打球供給皿 3 の近傍に設けられる度数表示 LED に表示させるための端数表示スイッチ 152、カードユニット 50 がいずれの側のパチンコ遊技機 1 に対応しているのかを示す連結台方向表示器 153、カードユニット 50 内にカードが投入されていることを示すカード投入表示ランプ 154、記録媒体としてのカードが挿入されるカード挿入口 155、およびカード挿入口 155 の裏面に設けられているカードリーダライタの機構を点検する場合にカードユニット 50 を解放するためのカードユニット錠 156 が設けられている。

30

【 0 0 2 8 】

打球発射装置から発射された打球は、打球レールを通って遊技領域 7 に入り、その後、遊技領域 7 を下りてくる。打球が通過ゲート 11 を通ってゲートスイッチ 12 で検出されると、普通図柄表示器 10 の表示数字が連続的に変化する状態になる。また、打球が始動入賞口 14 に入り始動口スイッチ 17 で検出されると、図柄の変動を開始できる状態であれば、可変表示部 9 内の図柄が回転を始める。図柄の変動を開始できる状態でなければ、始動入賞記憶を 1 増やす。

40

【 0 0 2 9 】

可変表示部 9 内の画像の回転は、一定時間が経過したときに停止する。停止時の画像の組み合わせが大当たり図柄の組み合わせであると、大当たり遊技状態に移行する。すなわち、開閉板 20 が、一定時間経過するまで、または、所定個数（例えば 10 個）の打球が入賞するまで開放する。そして、開閉板 20 の開放中に打球が特定入賞領域に入賞し V 入賞スイッチ 22 で検出されると、継続権が発生し開閉板 20 の開放が再度行われる。継続権の発生は、所定回数（例えば 15 ラウンド）許容される。

【 0 0 3 0 】

50

停止時の可変表示部 9 内の画像の組み合わせが確率変動を伴う大当たり図柄の組み合わせである場合には、次に大当たりとなる確率が高くなる。すなわち、高確率状態という遊技者にとってさらに有利な状態となる。また、普通図柄表示器 10 における停止図柄が所定の図柄（当たり図柄 = 小当たり図柄）である場合に、可変入賞球装置 15 が所定時間だけ開状態になる。さらに、高確率状態では、普通図柄表示器 10 における停止図柄が当たり図柄になる確率が高められるとともに、可変入賞球装置 15 の開放時間と開放回数が高められる。

#### 【0031】

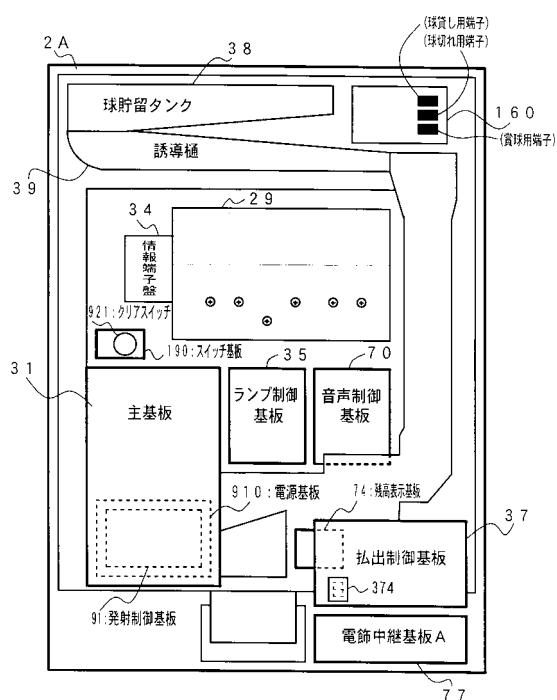

次に、パチンコ遊技機 1 の裏面に配置されている各基板について説明する。

図 2 に示すように、パチンコ遊技機 1 の裏面では、枠体 2 A 内の機構板の上部に玉貯留タンク 38 が設けられ、パチンコ遊技機 1 が遊技機設置島に設置された状態でその上方から遊技球が球貯留タンク 38 に供給される。球貯留タンク 38 内の遊技球は、誘導樋 39 を通って賞球ケース 40 A で覆われる球払出装置に至る。

10

#### 【0032】

遊技機裏面側では、可変表示部 9 を制御する可変表示制御ユニット 29 、遊技制御用マイクロコンピュータ等が搭載された遊技制御基板（主基板） 31 が設置されている。また、球払出制御を行う払出制御用マイクロコンピュータ等が搭載された払出制御基板 37 、およびモータの回転力をを利用して打球を遊技領域 7 に発射する打球発射装置が設置されている。さらに、装飾ランプ 25 、遊技効果 LED 28 a 、遊技効果ランプ 28 b , 28 c 、賞球ランプ 51 および球切れランプ 52 に信号を送るためのランプ制御基板 35 、スピーカ 27 からの音声発生を制御するための音声制御基板 70 および打球発射装置を制御するための発射制御基板 91 も設けられている。

20

#### 【0033】

さらに、DC 30 V 、DC 21 V 、DC 12 V およびDC 5 V を作成する電源回路が搭載された電源基板 910 が設けられ、上方には、各種情報を遊技機外部に出力するための各端子を備えたターミナル基板 160 が設置されている。ターミナル基板 160 には、少なくとも、球切れ検出スイッチの出力を導入して外部出力するための球切れ用端子、賞球個数信号を外部出力するための賞球用端子および球貸し個数信号を外部出力するための球貸し用端子が設けられている。また、中央付近には、主基板 31 からの各種情報を遊技機外部に出力するための各端子を備えた情報端子盤 34 が設置されている。

30

#### 【0034】

さらに、図 2 には、度数表示 LED 等を搭載した残高表示基板 74 が示されている。また、各基板（主基板 31 や払出制御基板 37 等）に含まれる記憶内容保持手段（例えば、電力供給停止時にもその内容を保持可能なバックアップ RAM ）に記憶されたバックアップデータをクリアするための初期化操作手段としてのクリアスイッチ 921 が搭載されたスイッチ基板 190 が設けられている。スイッチ基板 190 には、主基板 31 等の他の基板と接続されるコネクタ（図 2 において図示せず）が設けられている。

#### 【0035】

なお、図 2 には、ランプ制御基板 35 および音声制御基板 70 からの信号を、枠側に設けられている遊技効果 LED 28 a 、遊技効果ランプ 28 b , 28 c 、賞球ランプ 51 および球切れランプ 52 に供給するための電飾中継基板 A77 が示されているが、信号中継の必要に応じて他の中継基板も設けられる。

40

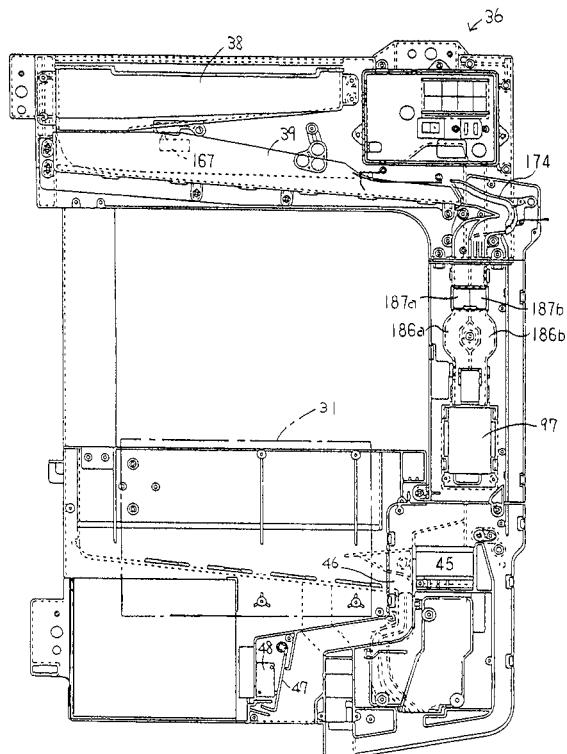

#### 【0036】

図 3 はパチンコ遊技機 1 の機構板を背面からみた背面図である。球貯留タンク 38 に貯留された玉は誘導樋 39 を通り、図 3 に示されるように、球切れ検出器（球切れスイッチ） 187 a , 187 b を通過して球供給樋 186 a , 186 b を経て球払出装置 97 に至る。球切れスイッチ 187 a , 187 b は遊技球通路内の遊技球の有無を検出するスイッチであるが、球タンク 38 内の補給球の不足を検出する球切れ検出スイッチ 167 も設けられている。以下、球切れスイッチ 187 a , 187 b を、球切れスイッチ 187 と表現することがある。

#### 【0037】

50

球払出装置 97 から払い出された遊技球は、連絡口 45 を通ってパチンコ遊技機 1 の前面に設けられている打球供給皿 3 に供給される。連絡口 45 の側方には、パチンコ遊技機 1 の前面に設けられている余剰玉受皿 4 に連通する余剰玉通路 46 が形成されている。

【0038】

入賞にもとづく景品球が多数払い出されて打球供給皿 3 が満杯になり、ついには遊技球が連絡口 45 に到達した後さらに遊技球が払い出されると遊技球は、余剰玉通路 46 を経て余剰玉受皿 4 に導かれる。さらに遊技球が払い出されると、感知レバー 47 が満タンスイッチ 48 を押圧して満タンスイッチ 48 がオンする。その状態では、球払出装置 97 内のステッピングモータの回転が停止して球払出装置 97 の動作が停止するとともに打球発射装置の駆動も停止する。

10

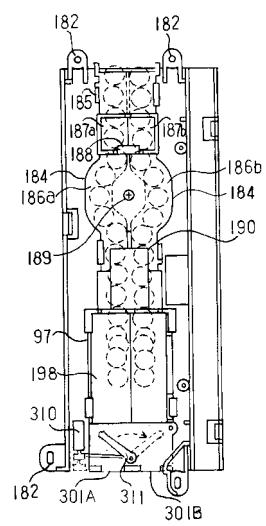

【0039】

次に、機構板 36 に設置されている中間ベースユニットの構成について説明する。中間ベースユニットには、球供給樋 186a, 186b や球払出装置 97 が設置される。図 4 に示すように、中間ベースユニットの上下には連結凹突部 182 が形成されている。連結凹突部 182 は、中間ベースユニットと機構板 36 の上部ベースユニットおよび下部ベースユニットを連結固定するものである。

【0040】

中間ベースユニットの上部には通路体 184 が固定されている。そして、通路体 184 の下部に球払出装置 97 が固定されている。通路体 184 は、カーブ樋 174 (図 3 参照) によって流下方向を左右方向に変換された 2 列の遊技球を流下させる払出球通路 186a, 186b を有する。払出球通路 186a, 186b の上流側には、球切れスイッチ 187a, 187b が設置されている。球切れスイッチ 187a, 187b は、払出球通路 186a, 186b 内の遊技球の有無を検出するものであって、球切れスイッチ 187a, 187b が遊技球を検出しなくなると球払出装置 97 における払出モータ (図 4 において図示せず) の回転を停止して球払出が不動化される。

20

【0041】

なお、球切れスイッチ 187a, 187b は、払出球通路 186a, 186b に 27~28 個程度の遊技球が存在することを検出できるような位置に係止片 188 によって係止されている。すなわち、球切れスイッチ 187a, 187b は、賞球の一単位の最大払出量 (この実施の形態では 15 個) および球貸しの一単位の最大払出量 (この実施の形態では 100 円 : 25 個) 以上が確保されていることが確認できるような位置に設置されている。

30

【0042】

通路体 184 の中央部は、内部を流下する遊技球の球圧を弱めるように、左右に湾曲する形状に形成されている。そして、払出球通路 186a, 186b の間に止め穴 189 が形成されている。止め穴 189 の裏面は中間ベースユニットに設けられている取付ボスがはめ込まれる。その状態で止めねじがねじ止めされて、通路体 184 は中間ベースユニットに固定される。なお、ねじ止めされる前に、中間ベースユニットに設けられている係止突片 185 によって通路体 184 の位置合わせを行えるようになっている。

【0043】

40

通路体 184 の下方には、球払出装置 97 に遊技球を供給するとともに故障時等には球払出装置 97 への遊技球の供給を停止する球止め装置 190 が設けられている。球止め装置 190 の下方に設置される球払出装置 97 は、直方体状のケース 198 の内部に収納されている。ケース 198 の左右 4 箇所には突部が設けられている。各突部が中間ベースユニットに設けられている位置決め突片に係った状態で、中間ベースユニットの下部に設けられている弾性係合片にケース 198 の下端がはめ込まれる。

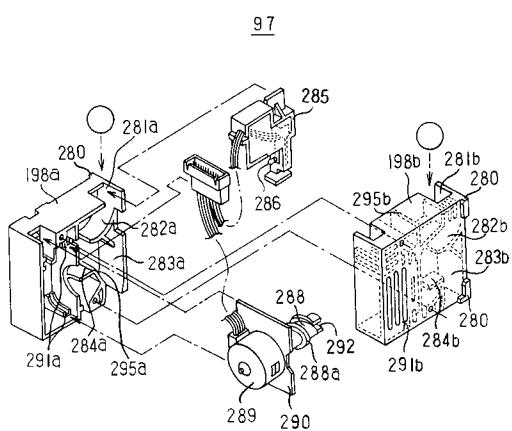

【0044】

図 5 は球払出装置 97 の分解斜視図である。球払出装置 97 の構成および作用について図 5 を参照して説明する。この実施形態における球払出装置 97 は、ステッピングモータ (払出モータ) 289 がスクリュー 288 を回転させることによりパチンコ玉を 1 個ずつ払

50

い出す。なお、球払出装置 97 は、入賞にもとづく景品球だけでなく、貸し出すべき遊技球も払い出す。

【0045】

図5に示すように、球払出装置 97 は、2つのケース 198a, 198b を有する。それぞれのケース 198a, 198b の左右2箇所に、球払出装置 97 の設置位置上部に設けられた位置決め突片に当接される係合突部 280 が設けられている。また、それぞれのケース 198a, 198b には、球供給路 281a, 281b が形成されている。球供給路 281a, 281b は湾曲面 282a, 282b を有し、湾曲面 282a, 282b の終端の下方には、球送り水平路 284a, 284b が形成されている。さらに、球送り水平路 284a, 284b の終端に球排出路 283a, 283b が形成されている。

10

【0046】

球供給路 281a, 281b、球送り水平路 284a, 284b、球排出路 283a, 283b は、ケース 198a, 198b をそれぞれ前後に区画する区画壁 295a, 295b の前方に形成されている。また、区画壁 295a, 295b の前方において、玉圧緩衝部材 285 がケース 198a, 198b 間に挟み込まれる。玉圧緩衝部材 285 は、球払出装置 97 に供給される玉を左右側方に振り分けて球供給路 281a, 281b に誘導する。

【0047】

また、玉圧緩衝部材 285 の下部には、発光素子 (LED) 286 と受光素子 (図示せず) とによる払出モータ位置センサが設けられている。発光素子 286 と受光素子とは、所定の間隔をあけて設けられている。そして、この間隔内に、スクリュー 288 の先端が挿入されるようになっている。なお、玉圧緩衝部材 285 は、ケース 198a, 198b が張り合わされたときに、完全にその内部に収納固定される。

20

【0048】

球送り水平路 284a, 284b には、払出モータ 289 によって回転させられるスクリュー 288 が配置されている。払出モータ 289 はモータ固定板 290 に固定され、モータ固定板 290 は、区画壁 295a, 295b の後方に形成される固定溝 291a, 291b にはめ込まれる。その状態で払出モータ 289 のモータ軸が区画壁 295a, 295b の前方に突出するので、その突出の前方にスクリュー 288 が固定される。スクリュー 288 の外周には、払出モータ 289 の回転によって球送り水平路 284a, 284b に載置された遊技球を前方に移動させるための螺旋突起 288a が設けられている。

30

【0049】

そして、スクリュー 288 の先端には、発光素子 286 を収納するよう凹部が形成され、その凹部の外周には、2つの切欠部 292 が互いに 180 度離れて形成されている。従って、スクリュー 288 が1回転する間に、発光素子 286 からの光は、切欠部 292 を介して受光素子で2回検出される。

【0050】

つまり、発光素子 286 と受光素子とによる払出モータ位置センサは、スクリュー 288 を定位置で停止するためのものであり、かつ、払出動作が行われた旨を検出するものである。なお、発光素子 286、受光素子および払出モータ 289 からの配線は、まとめられてケース 198a, 198b の後部下方に形成された引出穴から外部に引き出されコネクタに結線される。

40

【0051】

遊技球が球送り水平路 284a, 284b に載置された状態において、払出モータ 289 が回転すると、スクリュー 288 の螺旋突起 288a によって、遊技球は、球送り水平路 284a, 284b 上を前方に向かって移動する。そして、遂には、球送り水平路 284a, 284b の終端から球排出路 283a, 283b に落下する。このとき、左右の球送り水平路 284a, 284b からの落下は交互に行われる。すなわち、スクリュー 288 が半回転する毎に一方から1個の遊技球が落下する。従って、1個の遊技球が落下する毎に、発光素子 286 からの光が受光素子によって検出される。

50

## 【0052】

図4に示すように、球払出装置97の下方には、球振分部材311が設けられている。球振分部材311は、振分ソレノイド310によって駆動される。例えば、ソレノイド310のオン時には、球振分部材311は右側に倒れ、オフ時には左側に倒れる。振分ソレノイド310の下方には、近接スイッチによる賞球カウントスイッチ301Aおよび球貸しカウントスイッチ301Bが設けられている。入賞にもとづく賞球時には、球振分部材311は右側に倒れ、球排出路283a, 283bからの玉はともに賞球カウントスイッチ301Aを通過する。また、球貸し時には、球振分部材311は左側に倒れ、球排出路283a, 283bからの玉はともに球貸しカウントスイッチ301Bを通過する。従って、球払出装置97は、賞球時と球貸し時とで払出流下路を切り替えて、所定数の遊技媒体の払出を行うことができる。10

## 【0053】

このように、球振分部材311を設けることによって、2条の玉流路を落下してきた玉は、賞球カウントスイッチ301Aと球貸しカウントスイッチ301Bとのうちのいずれか一方しか通過しない。従って、賞球であるのか球貸しであるのかの判断をすることなく、賞球カウントスイッチ301Aと球貸しカウントスイッチ301Bの検出出力から、直ちに賞球数または球貸し数を把握することができる。

## 【0054】

なお、この実施の形態では、電気的駆動源の駆動によって遊技球を払い出す球払出装置として、ステッピングモータの回転によって遊技球が払い出される球払出装置97を用いることにすると、その他の駆動源によって遊技球を送り出す構造の球払出装置を用いてよいし、電気的駆動源の駆動によってストップバを外し遊技球の自重によって払い出しがなされる構造の球払出装置を用いてよい。また、この実施の形態では、球払出装置97は賞球にもとづく景品球と貸出要求にもとづく貸し球の双方を払い出すが、それについて払出装置が設けられていてよい。20

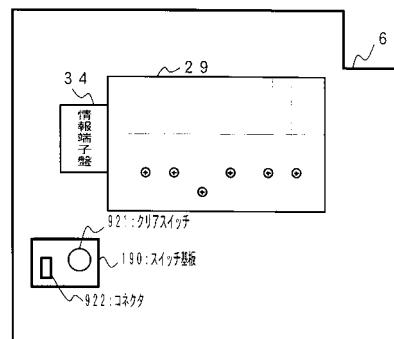

## 【0055】

図6は、遊技盤6におけるスイッチ基板190の部分を示す正面図である。スイッチ基板190は、遊技機1の裏面側の遊技盤6に設置されている。図6に示すように、スイッチ基板190には、主基板31等の他の基板に、ケーブルを介してクリアスイッチ921の出力を接続するためのコネクタ922が搭載されている。30

## 【0056】

図7は、スイッチ基板190に搭載されたクリアスイッチ921の構成の一例を示す構成図である。図7(A)には、押しボタン構造のクリアスイッチ921が示されている。クリアスイッチ921が押下されるとローレベル(オン状態)のクリアスイッチ信号が出力され、コネクタ922を介して主基板31等に送信される。また、クリアスイッチ921が押下されていなければハイレベル(オフ状態)の信号が出力される。

## 【0057】

図7(B)は、クリアスイッチ921の他の構成例を示す構成図である。図7(B)に示すクリアスイッチ921は、「OFF」、「ON」および「クリア」の選択切り換えを行うための切換操作部921aを有する。切換操作部921aによって、「OFF」が選択されているときは何らの信号も発生しない。「ON」が選択されているときはハイレベルの信号を出力する。さらに、クリアスイッチ921は、遊技機1に対する電源供給のオン/オフ切換のためのスイッチも兼ねている。従って、「OFF」が選択されると、遊技機1に対する電源供給が停止された状態(遊技機の電源がオフの状態)になる。「ON」または「クリア」が選択されると、遊技機1に対して電源供給が行われる状態(遊技機の電源がオンの状態)になる。また、「クリア」が選択されているときに、ローレベルのクリアスイッチ信号が出力される。40

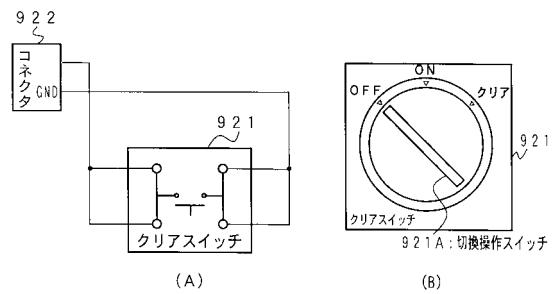

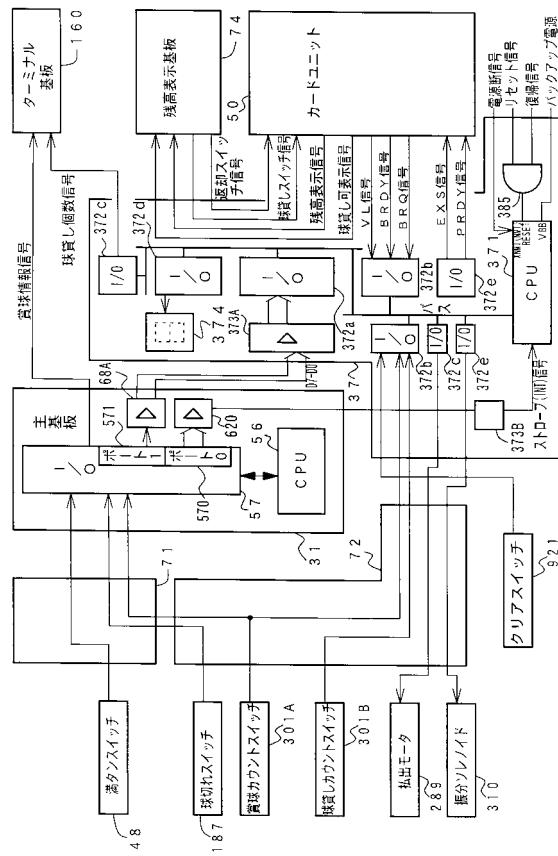

## 【0058】

図8は、主基板31における回路構成の一例を示すブロック図である。なお、図8には、払出制御基板37、ランプ制御基板35、音声制御基板70、発射制御基板91および図50

柄制御基板 8 0 も示されている。主基板 3 1 には、プログラムに従ってパチンコ遊技機 1 を制御する基本回路 5 3 と、ゲートスイッチ 1 2 、始動口スイッチ 1 7 、V 入賞スイッチ 2 2 、カウントスイッチ 2 3 、入賞口スイッチ 1 9 a , 1 9 b , 2 4 a , 2 4 b 、満タンスイッチ 4 8 、球切れスイッチ 1 8 7 および賞球カウントスイッチ 3 0 1 A からの信号を基本回路 5 3 に与えるスイッチ回路 5 8 と、可変入賞球装置 1 5 を開閉するソレノイド 1 6 、開閉板 2 0 を開閉するソレノイド 2 1 および大入賞口内の経路を切り換えるためのソレノイド 2 1 A を基本回路 5 3 からの指令に従って駆動するソレノイド回路 5 9 とが搭載されている。

#### 【 0 0 5 9 】

なお、図 8 には示されていないが、カウントスイッチ短絡信号もスイッチ回路 5 8 を介して基本回路 5 3 に伝達される。また、スイッチ基板 1 9 0 に搭載されたクリアスイッチ 9 2 1 からの信号もスイッチ回路 5 8 を介して基本回路 5 3 に伝達される。 10

#### 【 0 0 6 0 】

また、基本回路 5 3 から与えられるデータに従って、大当たりの発生を示す大当たり情報、可変表示部 9 の画像表示開始に利用された始動入賞球の個数を示す有効始動情報、確率変動が生じたことを示す確変情報等の情報出力信号をホールコンピュータ等の外部機器に対して出力する情報出力回路 6 4 が搭載されている。

#### 【 0 0 6 1 】

基本回路 5 3 は、ゲーム制御用のプログラム等を記憶する ROM 5 4 、ワークメモリとして使用される記憶手段（変動データを記憶する手段）の一例である RAM 5 5 、プログラムに従って制御動作を行う CPU 5 6 および I / O ポート部 5 7 を含む。この実施の形態では、ROM 5 4 , RAM 5 5 は CPU 5 6 に内蔵されている。すなわち、CPU 5 6 は、1 チップマイクロコンピュータである。なお、1 チップマイクロコンピュータは、少なくとも RAM 5 5 が内蔵されればよく、ROM 5 4 および I / O ポート部 5 7 は外付けであっても内蔵されていてもよい。 20

#### 【 0 0 6 2 】

遊技球を打撃して発射する打球発射装置は発射制御基板 9 1 上の回路によって制御される駆動モータ 9 4 で駆動される。そして、駆動モータ 9 4 の駆動力は、操作ノブ 5 の操作量に従って調整される。すなわち、発射制御基板 9 1 上の回路によって、操作ノブ 5 の操作量に応じた速度で打球が発射されるように制御される。 30

#### 【 0 0 6 3 】

この実施の形態では、電源基板 9 1 0 から主基板 3 1 に対して、ローレベルがリセット状態を示すリセット信号、ローアクティブの復帰信号およびローアクティブの電源断信号も入力される。リセット信号と復帰信号とは AND 回路 1 6 1 に入力され、AND 回路 1 6 1 の出力が CPU 5 6 のリセット端子に入力される。また、電源断信号は、CPU 5 6 のマスク不能割込（NMI）端子に入力される。さらに、図 8 には明示されていないが、RAM ( CPU 内蔵 RAM であってもよい。) 5 5 の一部または全部が、電源基板 9 1 0 において作成されるバックアップ電源によってバックアップされているバックアップ RAM である。すなわち、遊技機に対する電力供給が停止しても、所定期間は、RAM 5 5 の一部または全部の内容は保存される。 40

#### 【 0 0 6 4 】

なお、この実施の形態では、ランプ制御基板 3 5 に搭載されているランプ制御手段が、遊技盤に設けられている始動記憶表示器 1 8 、ゲート通過記憶表示器 4 1 および装飾ランプ 2 5 の表示制御を行うとともに、枠側に設けられている遊技効果ランプ・LED 2 8 a , 2 8 b , 2 8 c 、賞球ランプ 5 1 および球切れランプ 5 2 の表示制御を行う。また、特別図柄を可変表示する可変表示部 9 および普通図柄を可変表示する普通図柄表示器 1 0 の表示制御は、図柄制御基板 8 0 に搭載されている表示制御手段によって行われる。

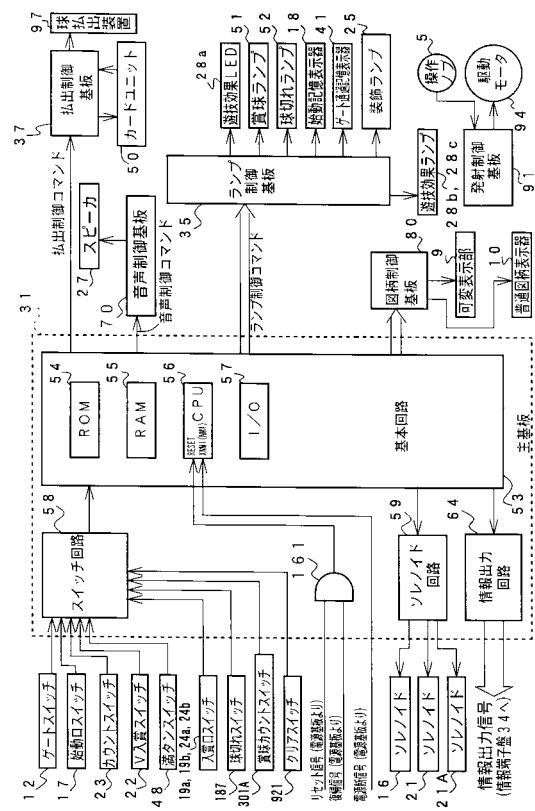

#### 【 0 0 6 5 】

図 9 は、払出手制御基板 3 7 および球払出手装置 9 7 の構成要素などの払出手に関連する構成要素を示すブロック図である。図 9 に示すように、満タンスイッチ 4 8 からの検出信号は、 50

中継基板 7 1 を介して主基板 3 1 の I / O ポート部 5 7 に入力される。満タンスイッチ 4 8 は、余剰球受皿 4 の満タンを検出するスイッチである。また、球切れスイッチ 1 8 7 ( 1 8 7 a , 1 8 7 b ) からの検出信号も、中継基板 7 2 および中継基板 7 1 を介して主基板 3 1 の I / O ポート部 5 7 に入力される。

#### 【 0 0 6 6 】

主基板 3 1 の C P U 5 6 は、球切れスイッチ 1 8 7 からの検出信号が球切れ状態を示しているか、または、満タンスイッチ 4 8 からの検出信号が満タン状態を示していると、払出禁止を指示する払出制御コマンドを送出する。払出禁止を指示する払出制御コマンドを受信すると、払出制御基板 3 7 の払出制御用 C P U 3 7 1 は球払出処理を停止する。

#### 【 0 0 6 7 】

さらに、賞球カウントスイッチ 3 0 1 A からの検出信号は、中継基板 7 2 および中継基板 7 1 を介して主基板 3 1 の I / O ポート部 5 7 に入力されるとともに、中継基板 7 2 を介して払出制御基板 3 7 の入力ポート 3 7 2 b に入力される。賞球カウントスイッチ 3 0 1 A は、球払出装置 9 7 の払出機構部分に設けられ、実際に払い出された賞球払出球を検出する。

#### 【 0 0 6 8 】

入賞があると、払出制御基板 3 7 には、主基板 3 1 の出力ポート ( ポート 0 , 1 ) 5 7 0 , 5 7 1 から賞球個数を示す払出制御コマンドが入力される。出力ポート ( 出力ポート 1 ) 5 7 1 は 8 ビットのデータを出力し、出力ポート 5 7 0 は 1 ビットのストローブ信号 ( I N T 信号 ) を出力する。賞球個数を示す払出制御コマンドは、入力バッファ回路 3 7 3 A を介して I / O ポート 3 7 2 a に入力される。I N T 信号は、入力バッファ回路 3 7 3 B を介して払出制御用 C P U 3 7 1 の割込端子に入力されている。払出制御用 C P U 3 7 1 は、I / O ポート 3 7 2 a を介して払出制御コマンドを入力し、払出制御コマンドに応じて球払出装置 9 7 を駆動して賞球払出を行う。なお、この実施の形態では、払出制御用 C P U 3 7 1 は、1 チップマイクロコンピュータであり、少なくとも R A M が内蔵されている。

#### 【 0 0 6 9 】

また、主基板 3 1 において、出力ポート 5 7 0 , 5 7 1 の外側にバッファ回路 6 2 0 , 6 8 A が設けられている。バッファ回路 6 2 0 , 6 8 A として、例えば、汎用の C M O S - I C である 7 4 H C 2 5 0 , 7 4 H C 1 4 が用いられる。このような構成によれば、外部から主基板 3 1 の内部に入力される信号が阻止されるので、払出制御基板 3 7 から主基板 3 1 に信号が与えられる可能性がある信号ラインをさらに確実になくすことができる。なお、バッファ回路 6 2 0 , 6 8 A の出力側にノイズフィルタを設けてもよい。

#### 【 0 0 7 0 】

払出制御用 C P U 3 7 1 は、出力ポート 3 7 2 c を介して、貸し球数を示す球貸し個数信号をターミナル基板 1 6 0 に出力する。さらに、出力ポート 3 7 2 d を介して、エラー表示用 L E D 3 7 4 にエラー信号を出力する。

#### 【 0 0 7 1 】

さらに、払出制御基板 3 7 の入力ポート 3 7 2 b には、中継基板 7 2 を介して球貸しカウントスイッチ 3 0 1 B からの検出信号が入力される。球貸しカウントスイッチ 3 0 1 B は、球払出装置 9 7 の払出機構部分に設けられ、実際に払い出された貸し球を検出する。払出制御基板 3 7 からの払出モータ 2 8 9 への駆動信号は、出力ポート 3 7 2 c および中継基板 7 2 を介して球払出装置 9 7 の払出機構部分における払出モータ 2 8 9 に伝えられ、振分ソレノイド 3 1 0 への駆動信号は、出力ポート 3 7 2 e および中継基板 7 2 を介して球払出装置 9 7 の払出機構部分における振分ソレノイド 3 1 0 に伝えられる。また、クリアスイッチ 9 2 1 の出力も、入力ポート 3 7 2 b に入力される。

#### 【 0 0 7 2 】

カードユニット 5 0 には、カードユニット制御用マイクロコンピュータが搭載されている。また、カードユニット 5 0 には、端数表示スイッチ 1 5 2 、連結台方向表示器 1 5 3 、カード投入表示ランプ 1 5 4 およびカード挿入口 1 5 5 が設けられている ( 図 1 参照 ) 。

10

20

30

40

50

残高表示基板 74 には、打球供給皿 3 の近傍に設けられている度数表示 LED、球貸しスイッチおよび返却スイッチが接続される。

【0073】

残高表示基板 74 からカードユニット 50 には、遊技者の操作に応じて、球貸しスイッチ信号および返却スイッチ信号が払出制御基板 37 を介して与えられる。また、カードユニット 50 から残高表示基板 74 には、プリペイドカードの残高を示すカード残高表示信号および球貸し可表示信号が払出制御基板 37 を介して与えられる。カードユニット 50 と払出制御基板 37 の間では、接続信号 (VL 信号)、ユニット操作信号 (BRDY 信号)、球貸し要求信号 (BRQ 信号)、球貸し完了信号 (EXS 信号) およびパチンコ機動作信号 (PRDY 信号) が入力ポート 372b および出力ポート 372e を介してやりとりされる。 10

【0074】

パチンコ遊技機 1 の電源が投入されると、払出制御基板 37 の払出制御用 CPU371 は、カードユニット 50 に PRDY 信号を出力する。また、カードユニット制御用マイクロコンピュータは、VL 信号を出力する。払出制御用 CPU371 は、VL 信号の入力状態により接続状態 / 未接続状態を判定する。カードユニット 50 においてカードが受け付けられ、球貸しスイッチが操作され球貸しスイッチ信号が入力されると、カードユニット制御用マイクロコンピュータは、払出制御基板 37 に BRDY 信号を出力する。この時点から所定の遅延時間が経過すると、カードユニット制御用マイクロコンピュータは、払出制御基板 37 に BRQ 信号を出力する。 20

【0075】

そして、払出制御基板 37 の払出制御用 CPU371 は、カードユニット 50 に対する EXS 信号を立ち上げ、カードユニット 50 からの BRQ 信号の立ち下がりを検出すると、払出モータ 289 を駆動し、所定個の貸し球を遊技者に払い出す。このとき、振分ソレノイド 310 は駆動状態とされている。すなわち、球振分部材 311 を球貸し側に向ける。そして、払出が完了したら、払出制御用 CPU371 は、カードユニット 50 に対する EXS 信号を立ち下げる。その後、カードユニット 50 からの BRDY 信号がオン状態でなければ、賞球払出制御を実行する。

【0076】

以上のように、カードユニット 50 からの信号は全て払出制御基板 37 に入力される構成になっている。従って、球貸し制御に関して、カードユニット 50 から主基板 31 に信号が入力されることはなく、主基板 31 の基本回路 53 にカードユニット 50 の側から不正に信号が入力される余地はない。また、カードユニット 50 で用いられる電源電圧 AC 24V は払出制御基板 37 から供給される。 30

【0077】

この実施の形態では、電源基板 910 から払出制御基板 37 に対して、リセット信号、復帰信号および電源断信号も入力される。リセット信号と復帰信号とは AND 回路 385 に入力され、AND 回路 385 の出力が払出制御用 CPU371 のリセット端子に入力される。また、電源断信号は、払出制御用 CPU371 のマスク不能割込 (NMI) 端子に入力される。さらに、払出制御基板 37 に存在する RAM (CPU 内蔵 RAM であってもよい。) の少なくとも一部は、電源基板 910 において作成されるバックアップ電源によって、バックアップされている。すなわち、遊技機に対する電力供給が停止しても、所定期間は、RAM の少なくとも一部の内容は保存される。 40

【0078】

なお、この実施の形態では、カードユニット 50 が遊技機とは別体として遊技機に隣接して設置されている場合を例にするが、カードユニット 50 は遊技機と一体化されていてもよい。また、コイン投入に応じてその金額に応じた遊技球が貸し出されるような場合でも本発明を適用できる。

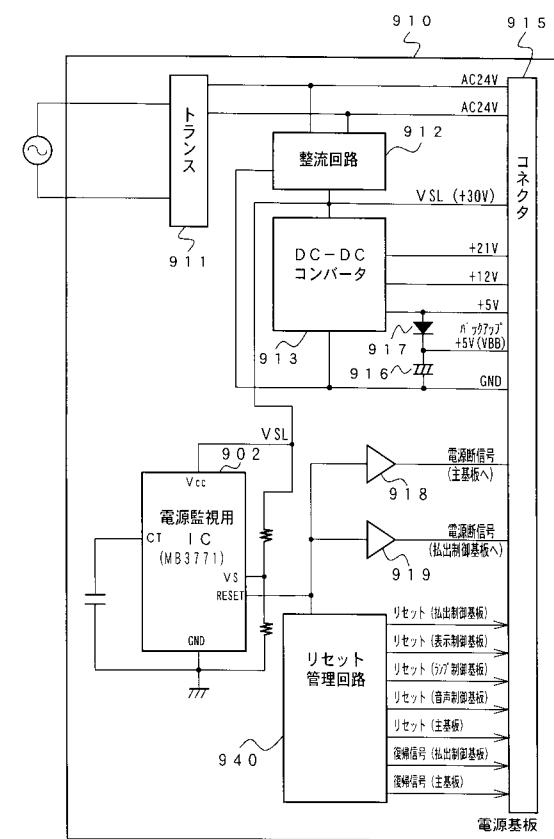

【0079】

図 10 は、遊技機の電源基板 910 の一構成例を示すブロック図である。電源基板 910 50

は、主基板 31、図柄制御基板 80、音声制御基板 70、ランプ制御基板 35 および払出制御基板 37 等の電気部品制御基板と独立して設置され、遊技機内の各電気部品制御基板および機構部品が使用する電圧を生成する。この例では、AC 24V、VSL (DC + 30V)、DC + 21V、DC + 12V および DC + 5V を生成する。また、バックアップ電源となるコンデンサ 916 は、DC + 5V すなわち各基板上の IC 等を駆動する電源のラインから充電される。

#### 【0080】

トランジスタ 911 は、交流電源からの交流電圧を 24V に変換する。AC 24V 電圧は、コネクタ 915 に出力される。また、整流回路 912 は、AC 24V から +30V の直流電圧を生成し、DC - DC コンバータ 913 およびコネクタ 915 に出力する。DC - DC コンバータ 913 は、+21V、+12V および +5V を生成してコネクタ 915 に出力する。コネクタ 915 は例えば中継基板に接続され、中継基板から各電気部品制御基板および機構部品に必要な電圧の電力が供給される。

#### 【0081】

ただし、電源基板 910 に各電気部品制御基板に至る各コネクタを設け、電源基板 910 から、中継基板を介さずにそれぞれの基板に至る各電圧を供給するようにしてもよい。また、図 10 には 1 つのコネクタ 915 が代表して示されているが、コネクタは、各電気部品制御基板対応に設けられている。

#### 【0082】

DC - DC コンバータ 913 からの +5V ラインは分岐してバックアップ +5V ラインを形成する。バックアップ +5V ラインとグラウンドレベルとの間には大容量のコンデンサ 916 が接続されている。コンデンサ 916 は、遊技機に対する電力供給が遮断されたときの電気部品制御基板のバックアップ RAM (電源バックアップされている RAM すなわち記憶内容保持状態となりうる記憶手段) に対して記憶状態を保持できるように電力を供給するバックアップ電源となる。また、+5V ラインとバックアップ +5V ラインとの間に、逆流防止用のダイオード 917 が挿入される。

#### 【0083】

なお、バックアップ電源として、+5V 電源から充電可能な電池を用いてもよい。電池を用いる場合には、+5V 電源から電力供給されない状態が所定時間継続すると容量がなくなるような充電池が用いられる。

#### 【0084】

また、電源基板 910 には、電源監視用 IC 902 が搭載されている。電源監視用 IC 902 は、VSL 電源電圧を導入し、VSL 電源電圧を監視することによって電源断の発生を検出する。具体的には、VSL 電源電圧が所定値 (この例では +22V) 以下になつたら、電源断が生ずるとして電源断信号を出力する。なお、監視対象の電源電圧は、各電気部品制御基板に搭載されている回路素子の電源電圧 (この例では +5V) よりも高い電圧であることが好ましい。この例では、交流から直流に変換された直後の電圧である VSL が用いられている。電源監視用 IC 902 からの電源断信号は、主基板 31 や払出制御基板 37 等に供給される。

#### 【0085】

電源監視用 IC 902 が電源断を検知するための所定値は、通常時の電圧より低いが、各電気部品制御基板上の CPU が暫くの間動作しうる程度の電圧である。また、電源監視用 IC 902 が、CPU 等の回路素子を駆動するための電圧 (この例では +5V) よりも高く、また、交流から直流に変換された直後の電圧を監視するように構成されているので、CPU が必要とする電圧に対して監視範囲を広げることができる。従って、より精密な監視を行うことができる。

#### 【0086】

さらに、監視電圧として VSL (+30V) を用いる場合には、遊技機の各種スイッチに供給される電圧が +12V であることから、電源瞬断時のスイッチオン誤検出の防止も期待できる。すなわち、+30V 電源の電圧を監視すると、+30V 作成の以降に作られる +

10

20

30

40

50

12Vが落ち始める以前の段階でその低下を検出できる。よって、+12V電源の電圧が低下するとスイッチ出力がオン状態を呈するようになるが、+12Vより早く低下する+30V電源電圧を監視して電源断を認識すれば、スイッチ出力がオン状態を呈する前に電源復旧待ちの状態に入り、スイッチ出力を検出しない状態となることができる。

#### 【0087】

また、電源監視用IC902は、電気部品制御基板とは別個の電源基板910に搭載されているので、電源監視回路から複数の電気部品制御基板に電源断信号を供給することができる。電源断信号を必要とする電気部品制御基板が幾つあっても電源監視手段は1つ設ければよいので、各電気部品制御基板における各電気部品制御手段が後述する復帰制御を行っても、遊技機のコストはさほど上昇しない。

10

#### 【0088】

なお、図10に示された構成では、電源監視用IC902の検出出力（電源断信号）は、バッファ回路918、919を介してそれぞれの電気部品制御基板（例えば主基板31と拡出制御基板37）に伝達されるが、例えば、1つの検出出力を中継基板に伝達し、中継基板から各電気部品制御基板に同じ信号を分配する構成でもよい。また、電源断信号を必要とする基板数に応じたバッファ回路を設けてもよい。

#### 【0089】

さらに、電源基板910には、各基板にリセット信号および復帰信号を供給するリセット管理回路940が搭載されている。リセット管理回路940は、起動順序制御手段の一実現例である。

20

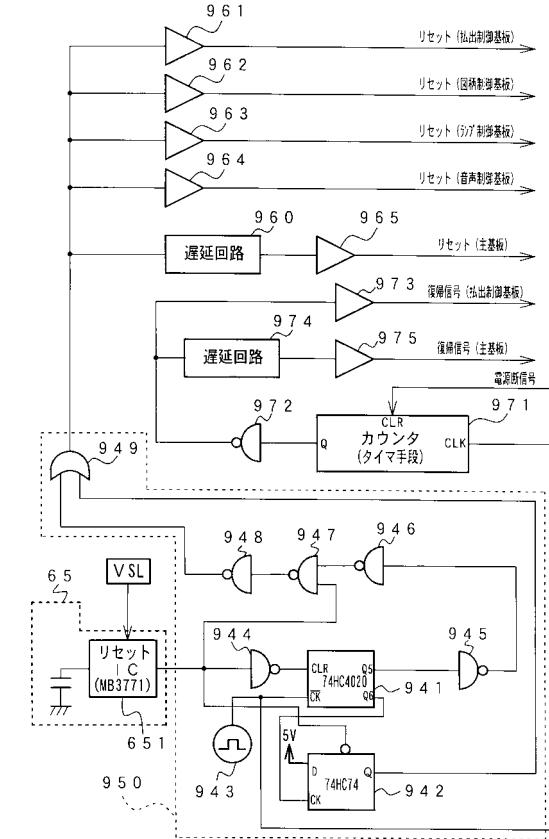

#### 【0090】

図11は、リセット管理回路940の構成例を示すブロック図である。リセット管理回路940において、リセット回路65におけるリセットIC651は、電源投入時に、外付けのコンデンサの容量で決まる所定時間だけ出力をローレベルとし、所定時間が経過すると出力をハイレベルにする。リセットIC651の出力は、各回路941～949を介して、バッファ回路961～964および遅延回路960に供給される。遅延回路960の出力はバッファ回路965に入力する。そして、バッファ回路961～965が各電気部品制御基板にリセット信号として供給される。従って、リセットIC651の出力がハイレベルになると、各電気部品制御基板におけるCPUが動作可能状態になる。

#### 【0091】

また、リセットIC651は、電源監視用IC902が監視する電源電圧と等しい電源電圧であるVSLの電源電圧を監視して電圧値が所定値（電源監視用IC902が電源断信号を出力する電源電圧値よりも低い値）以下になるとローレベルになる。従って、CPU56および拡出制御用CPU371は、電源監視用IC902からの電源断信号に応じて所定の電力供給停止準備処理を行った後、システムリセットされることになる。

30

#### 【0092】

図11に示すように、リセットIC651からのリセット信号は、NAND回路947に入力されるとともに、反転回路（NOT回路）944を介してカウンタIC941のクリア端子に入力される。カウンタIC941は、クリア端子への入力がローレベルになると、発振器943からのクロック信号をカウントする。そして、カウンタIC941のQ5出力がNOT回路945、946を介してNAND回路947に入力される。

40

#### 【0093】

また、カウンタIC941のQ6出力は、フリップフロップ（FF）942のクロック端子に入力される。フリップフロップ942のD入力はハイレベルに固定され、Q出力は論理和回路（OR回路）949に入力される。OR回路949の他方の入力には、NAND回路947の出力がNOT回路948を介して導入される。そして、OR回路949の出力が、バッファ回路961～965を介して各CPUに供給されている。このような構成によれば、電源投入時に、各CPUのリセット端子に2回のリセット信号（ローレベル信号）が与えられるので、各CPUは、確実に動作を開始する。

#### 【0094】

50

そして、例えば、電源監視手段である電源監視用 I C 9 0 2 の検出電圧（電源断信号を出力することになる電圧）を + 2 2 V とし、リセット I C 6 5 1 の検出電圧を + 9 V とする。そのように構成した場合には、電源監視手段とリセット I C 6 5 1 とは、同一の電源 V SL の電圧を監視するので、電源監視手段が電源断信号を出力するタイミングとリセット I C 6 5 1 がリセットレベルであるローレベルを出力するタイミングとの差を所望の所定期間に確実に設定することができる。所望の所定期間とは、電源監視手段からの電源断信号に応じて電力供給停止準備処理（電力供給停止時処理）を開始してから、その処理が確実に完了するまでの期間である。

#### 【 0 0 9 5 】

この例では、電源監視手段が検出信号を出力することになる検出条件は + 3 0 V 電源電圧が + 2 2 V にまで低下したことであり、リセット I C 6 5 1 がリセットレベルであるローレベルを出力することになる条件は + 3 0 V 電源電圧が + 9 V にまで低下したことになる。ただし、ここで用いられている電圧値は一例であって、他の値を用いてもよい。

#### 【 0 0 9 6 】

ただし、監視範囲が狭まるが、電源監視手段およびリセット I C 6 5 1 の監視電圧として + 5 V 電源電圧を用いることも可能である。その場合にも、電源監視回路の検出電圧は、リセット I C 6 5 1 の検出電圧よりも高く設定される。

#### 【 0 0 9 7 】

主基板 3 1 および払出制御基板 3 7 の C P U 5 6 および払出制御用 C P U 3 7 1 の駆動電源である + 5 V 電源から電力が供給されていない間、R A M の少なくとも一部は、電源基板 9 1 0 から供給されるバックアップ電源によってバックアップされ、遊技機に対する電源が断しても内容は保存される。そして、電源が復旧すると、リセット管理回路 9 4 0 からのリセット信号がハイレベルになるので、C P U 5 6 および払出制御用 C P U 3 7 1 は、通常の動作状態に復帰する。そのとき、必要なデータがバックアップ R A M に保存されているので、停電等からの復旧時に停電発生時の遊技状態に復帰することができる。

#### 【 0 0 9 8 】

なお、図 1 1 には、電源投入時に各電気部品制御基板の C P U のリセット端子に 2 回のリセット信号（ローレベル信号）が与えられる構成が示されたが、リセット信号の立ち上がりタイミングが 1 回しかなくても確実にリセット解除される C P U を使用する場合には、符号 9 4 1 ~ 9 4 9 で示された回路素子は不要である。その場合、リセット I C 6 5 1 の出力がそのままバッファ回路 9 6 1 ~ 9 6 4 および遅延回路 9 6 0 に接続される。

#### 【 0 0 9 9 】

また、この実施の形態では、電源基板 9 1 0 から各電気部品制御基板の C P U にリセット信号が供給されるときに、遅延回路 9 6 0 が、主基板 3 1 の C P U 5 6 に対するリセット信号を遅延させる。従って、電源投入時に、主基板 3 1 の C P U 5 6 に対するリセット信号は、他の電気部品制御基板の C P U に対するリセット信号よりも遅く立ち上がる。

#### 【 0 1 0 0 】

例えば、主基板 3 1 の C P U 5 6 が他の電気部品制御基板に対して制御コマンドを出力する際に、他の電気部品制御基板における C P U は既に立ち上がっているので、制御コマンドは確実に受信側の電気部品制御基板の C P U で受信される。

#### 【 0 1 0 1 】

さらに、主基板 9 1 0 には、タイマ手段の一例であるカウンタ 9 7 1 が搭載されている。カウンタ 9 7 1 は、電源断信号がローレベルになってクリアが解けると、発振器 9 4 3 からのクロック信号をカウントする。そして、カウントアップすると、Q 出力として、ハイレベルの 1 パルスを発生する。そのパルス信号は反転回路 9 7 2 で論理反転され、バッファ回路 9 7 3 および遅延回路 9 7 4 に入力する。遅延回路 9 7 4 は、入力信号を所定期間遅延させてバッファ回路 9 7 5 に入力させる。

#### 【 0 1 0 2 】

バッファ回路 9 7 3 の出力は、払出制御基板 3 7 への復帰信号となる。また、バッファ回路 9 7 5 の出力は、主基板 3 1 への復帰信号となる。なお、バッファ回路 9 7 3, 9 7 5

10

20

30

40

50

は、派出制御基板 37、主基板 31 に設けられていてもよい。

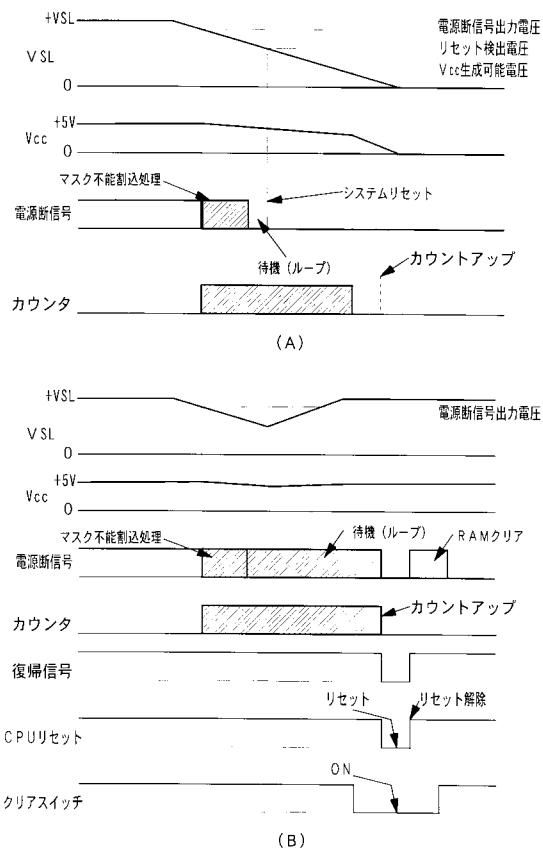

【0103】

図 12 は、カウンタ 971 の作用を説明するためのタイミング図である。(A) に示すように、電源電圧が低下し、VSL の電圧値が電源断信号出力レベル(この例では +22V)まで低下すると電源断信号が発生する。具体的には、電源断信号がローレベルになる。すると、後述するように、主基板 31 の CPU31 および派出制御用 CPU371 は、電力供給停止時処理の実行を開始し、その処理が終了すると、何の制御もしないループ状態(待機状態)に入る。

【0104】

カウンタ 971 は、電源断信号がローレベルになるとカウントを開始するのであるが、カウントアップ値は、電源断信号がローレベルになってから、VSL の電圧値が Vcc 生成可能電圧にまで低下する時間以上に設定される。すなわち、少なくとも、電源電圧が、制御動作が不能になる電圧にまで低下する時間以上に設定される。カウンタ 971 は Vcc を電源として動作するので、カウントアップ値は、カウンタ 971 の動作可能期間に相当する値以上に設定される。従って、一般には、カウンタ 971 がカウントアップして復帰信号が出力される前に、カウンタ 971 およびその他の回路部品は動作しなくなる。

10

【0105】

電源の瞬断等が生ずると、図 12 (B) に示すように、VSL の電圧レベルが短時間低下した後に復旧する。VSL の電圧レベルが電源断信号出力レベル以下になると、電源断信号がローレベルになって、電力供給停止時処理が開始される。そして、CPU56 および派出制御用 CPU371 は電力供給停止時処理終了後にループ状態に入る。何らの制御も行わないと、ループ処理から抜けられないのであるが、この場合には、カウンタ 971 がカウントアップして復帰信号が発生する。

20

【0106】

図 8 および図 9 に示されたように、主基板 31 および派出制御基板 371 において、復帰信号は、AND 回路 161, 385 を介して、CPU56 および派出制御用 CPU371 のリセット端子に入力される。従って、CPU56 および派出制御用 CPU371 にはシステムリセットがかかる。その結果、CPU56 および派出制御用 CPU371 は、待機状態である無限ループの状態から抜け出すことができる。CPU56 は、システムリセットが解除されると、すなわち復帰信号がハイレベルになると、電源投入時の場合と同様に、起動時の先頭番地からプログラムを実行する。

30

【0107】

なお、図 12 (B) には、カウンタ 971 のカウントアップ後に、直ちに復帰信号が出力される場合が示されているが、図 11 に示されたように電源基板 910 には遅延回路 974 があるので、主基板 31 の CPU56 に対する復帰信号の供給タイミングは、派出制御用 CPU371 に対する復帰信号の供給タイミングよりも遅れる。すなわち、通常の電力供給開始時にリセット信号が与えられる場合と同様に、遊技制御手段のリセット解除タイミングは、派出制御手段のリセット解除タイミングに対して遅れる。よって、復帰信号によって制御動作が復旧する場合も、遊技制御手段は、他の電気部品制御手段に対して、遅れて起動されることになる。

40

【0108】

また、図 12 には、CPU56 が復帰信号に応じたシステムリセットによって起動する際に、クリアスイッチ 921 がオンしていたときに RAM クリア処理を行うことも示されている。なお、起動する際にクリアスイッチ 921 がオンしていた場合に RAM クリア処理を行うことは、電源投入による起動の場合でも同様である。

【0109】

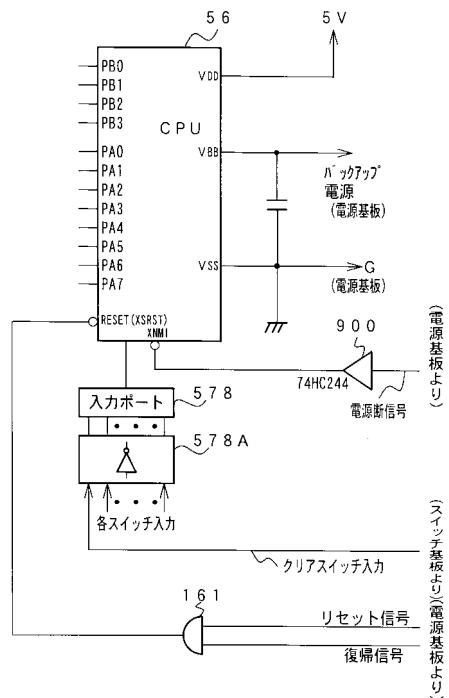

図 13 は、主基板 31 における CPU56 周りの一構成例を示すブロック図である。図 13 に示すように、電源基板 910 の電源監視回路(電源監視手段)からの電源断信号(電圧低下信号)が、CPU56 のマスク不能割込端子(XNMI 端子)に接続されている。電源監視回路は、遊技機が使用する各種直流電源のうちのいずれかの電源の電圧を監視し

50

て電源電圧低下を検出する回路である。この実施の形態では、VSLの電源電圧を監視して電圧値が所定値以下になるとローレベルの電源断信号を発生する。VSLは、遊技機で使用される直流電圧のうちで最大のものであり、この例では+30Vである。従って、CPU56は、割込処理によって電源断の発生を確認することができる。

【0110】

また、スイッチ基板190に搭載されたクリアスイッチ921の出力信号が、バッファ回路(反転回路)578Aおよび入力ポート578を介してCPU56に入力される。なお、入力ポート578には、バッファ回路578Aを介して賞球カウントスイッチ301A等の他の各スイッチの出力信号も入力されている。このような構成によれば、クリアスイッチ921に対する操作に応じてクリアスイッチ921の出力信号がローレベルを示すと、CPU56にクリアスイッチ信号が与えられる。CPU56は、クリアスイッチ信号が与えられると、後述するように、記憶内容保持手段による最終記憶内容を初期データにする処理を行う。この実施の形態では、クリアスイッチ921の出力信号が入力ポート578を介して入力されるので、簡単な構成でクリアスイッチ信号がCPU56に導入される。

10

【0111】

電源基板910からのリセット信号と復帰信号とはAND回路161に入力され、AND回路161の出力がCPU56のリセット端子に入力される。

【0112】

図14および図15は、この実施の形態における遊技制御手段の出力ポートの割り当てを示す説明図である。図14に示すように、出力ポート0は各電気部品制御基板に送出される制御コマンドのストローブ信号(INT信号)の出力ポートである。また、払出制御基板37に送出される払出制御コマンドの8ビットのデータは出力ポート1から出力され、図柄制御基板80に送出される表示制御コマンドの8ビットのデータは出力ポート2から出力され、ランプ制御基板35に送出されるランプ制御コマンドの8ビットのデータは出力ポート3から出力される。そして、図15に示すように、音声制御基板70に送出される音声制御コマンドの8ビットのデータは出力ポート4から出力される。

20

【0113】

また、出力ポート5から、情報出力回路64を介して情報端子板34等に至る各種情報出力用信号すなわち制御に関わる情報の出力データが出力される。そして、出力ポート6から、可変入賞球装置15を開閉するためのソレノイド16、大入賞口の開閉板20を開閉するためのソレノイド21、および大入賞口内の経路を切り換えるためのソレノイド21Aに対する駆動信号が出力される。

30

【0114】

図16は、この実施の形態における入力ポートのピット割り当てを示す説明図である。図16に示すように、入力ポート0のピット0~7には、それぞれ、入賞口スイッチ24a、入賞口スイッチ24b、入賞口スイッチ19a、入賞口スイッチ19b、始動口スイッチ17、カウントスイッチ23、V入賞スイッチ(特定領域スイッチ)22、ゲートスイッチ12の検出信号が入力される。また、入力ポート1のピット0~4には、それぞれ、賞球カウントスイッチ301A、満タンスイッチ48、球切れスイッチ187の検出信号、カウントスイッチ短絡信号、クリアスイッチ921の出力信号が入力される。

40

【0115】

次に遊技機の動作について説明する。

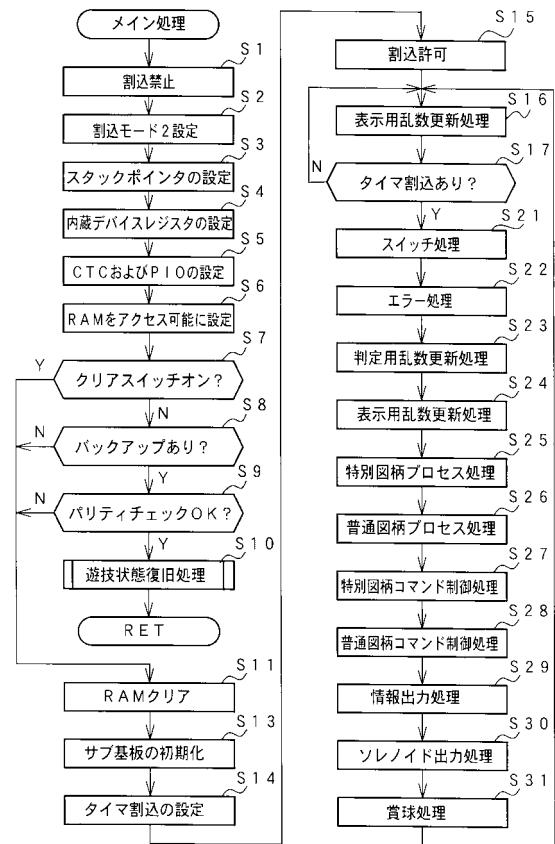

図17は、主基板31におけるCPU56が実行するメイン処理を示すフローチャートである。遊技機に対して電源が投入され、リセット端子の入力レベルがハイレベルになると、CPU56は、ステップS1以降のメイン処理を開始する。メイン処理において、CPU56は、まず、必要な初期設定を行う。なお、リセット端子の入力レベルがハイレベルになる場合として、遊技機に対する電力供給が開始された場合の他に、電源基板910から復帰信号が入力された場合(ローレベルからハイレベルに変化した場合)がある。

【0116】

50

初期設定処理において、C P U 5 6 は、まず、割込禁止に設定する（ステップS 1）。次に、割込モードを割込モード2に設定し（ステップS 2）、スタックポインタにスタックポインタ指定アドレスを設定する（ステップS 3）。そして、内蔵デバイスレジスタの初期化を行う（ステップS 4）。また、内蔵デバイス（内蔵周辺回路）であるC T C（カウンタ／タイマ）およびP I O（パラレル入出力ポート）の初期化（ステップS 5）を行った後、R A Mをアクセス可能状態に設定する（ステップS 6）。

#### 【0117】

この実施の形態で用いられるC P U 5 6 は、I / Oポート（P I O）およびタイマ／カウンタ回路（C T C）も内蔵している。また、C T Cは、2本の外部クロック／タイマトリガ入力C L K / T R G 2, 3と2本のタイマ出力Z C / T O 0, 1を備えている。 10

#### 【0118】

この実施の形態で用いられているC P U 5 6 には、マスク可能な割込（I N T）のモードとして以下の3種類のモードが用意されている。なお、マスク可能な割込が発生すると、C P U 5 6 は、自動的に割込禁止状態に設定するとともに、プログラムカウンタの内容をスタックにセーブする。

#### 【0119】

割込モード0：割込要求を行った内蔵デバイスがR S T命令（1バイト）またはC A L L命令（3バイト）をC P Uの内部データバス上に送出する。よって、C P U 5 6 は、R S T命令に対応したアドレスまたはC A L L命令で指定されるアドレスの命令を実行する。リセット時に、C P U 5 6 は自動的に割込モード0になる。よって、割込モード1または割込モード2に設定したい場合には、初期設定処理において、割込モード1または割込モード2に設定するための処理を行う必要がある。 20

#### 【0120】

割込モード1：割込が受け付けられると、常に0 0 3 8（h）番地に飛びモードである。

#### 【0121】

割込モード2：C P U 5 6 の特定レジスタ（レジスタ）の値（1バイト）と内蔵デバイスが出力する割込ベクタ（1バイト：最下位ビット0）から合成されるアドレスが、割込番地を示すモードである。すなわち、割込番地は、上位アドレスが特定レジスタの値とされ下位アドレスが割込ベクタとされた2バイトで示されるアドレスである。従って、任意の（飛び飛びではあるが）偶数番地に割込処理を設置することができる。各内蔵デバイスは割込要求を行うときに割込ベクタを送出する機能を有している。 30

#### 【0122】

よって、割込モード2に設定されると、各内蔵デバイスからの割込要求を容易に処理することが可能になり、また、プログラムにおける任意の位置に割込処理を設置することが可能になる。さらに、割込モード1とは異なり、割込発生要因毎のそれぞれの割込処理を用意しておくことも容易である。上述したように、この実施の形態では、初期設定処理のステップS 2において、C P U 5 6 は割込モード2に設定される。

#### 【0123】

次いで、C P U 5 6 は、入力ポート5 7 0を介して入力されるクリアスイッチ9 2 1の出力信号の状態を1回だけ確認する（ステップS 7）。その確認においてオンを検出した場合には、C P U 5 6 は、通常の初期化処理を実行する（ステップS 1 1～ステップS 1 5）。クリアスイッチ9 2 1がオンである場合（押下されている場合）には、ローレベルのクリアスイッチ信号が出力されている。なお、入力ポート5 7 8では、クリアスイッチ信号のオン状態はハイレベルである（図16参照）。 40

#### 【0124】

クリアスイッチ9 2 1がオンの状態でない場合には、電源断時にバックアップR A M領域のデータ保護処理（例えばパリティデータの付加等の電力供給停止時処理）が行われたか否か確認する（ステップS 8）。この実施の形態では、不測の電源断が生じた場合には、バックアップR A M領域のデータを保護するための処理が行われている。そのような保護処理が行われていた場合をバックアップありとする。バックアップなしを確認したら、C 50

P U 5 6 は初期化処理を実行する。

【 0 1 2 5 】

この実施の形態では、バックアップ R A M 領域にバックアップデータがあるか否かは、電源断時にバックアップ R A M 領域に設定されるバックアップフラグの状態によって確認される。この例では、図 1 8 に示すように、バックアップフラグ領域に「 5 5 H 」が設定されていればバックアップあり（オン状態）を意味し、「 5 5 H 」以外の値が設定されていればバックアップなし（オフ状態）を意味する。

【 0 1 2 6 】

バックアップありを確認したら、C P U 5 6 は、バックアップ R A M 領域のデータチェック（この例ではパリティチェック）を行う（ステップ S 9）。この実施の形態では、クリアデータ（ 0 0 ）をチェックサムデータエリアにセットし、チェックサム算出開始アドレスをポインタにセットする。また、チェックサムの対象となるデータ数に対応するチェックサム算出回数をセットする。そして、チェックサムデータエリアの内容とポインタが指す R A M 領域の内容との排他的論理和を演算する。演算結果をチェックサムデータエリアにストアするとともに、ポインタの値を 1 増やし、チェックサム算出回数の値を 1 減算する。以上の処理が、チェックサム算出回数の値が 0 になるまで繰り返される。チェックサム算出回数の値が 0 になったら、C P U 5 6 は、チェックサムデータエリアの内容の各ビットの値を反転し、反転後のデータをチェックサムとする。

【 0 1 2 7 】

電源断時に、上記の処理と同様の処理によってチェックサムが算出され、チェックサムはバックアップ R A M 領域に保存されている。ステップ S 9 では、算出したチェックサムと保存されているチェックサムとを比較する。不測の電源断が生じた後に復旧した場合には、バックアップ R A M 領域のデータは保存されているはずであるから、チェック結果（比較結果）は正常（一致）になる。チェック結果が正常でないということは、バックアップ R A M 領域のデータが、電源断時のデータとは異なっていることを意味する。そのような場合には、内部状態を電源断時の状態に戻すことができないので、停電復旧時でない電源投入時に実行される初期化処理を実行する。

【 0 1 2 8 】

チェック結果が正常であれば、C P U 5 6 は、遊技制御手段の内部状態と表示制御手段等の電気部品制御手段の制御状態を電源断時の状態に戻すための遊技状態復旧処理を行う（ステップ S 1 0）。そして、バックアップ R A M 領域に保存されていた P C （プログラムカウンタ）の退避値が P C に設定され、そのアドレスに復帰する。

【 0 1 2 9 】

初期化処理では、C P U 5 6 は、まず、R A M クリア処理を行う（ステップ S 1 1）。また、所定の作業領域（例えば、普通図柄判定用乱数カウンタ、普通図柄判定用バッファ、特別図柄左中右図柄バッファ、払出コマンド格納ポインタなど）に初期値を設定する初期値設定処理も行われる。さらに、サブ基板（ランプ制御基板 3 5 、払出制御基板 3 7 、音声制御基板 7 0 、図柄制御基板 8 0 ）を初期化するための処理を実行する（ステップ S 1 3）。サブ基板を初期化する処理とは、例えば初期設定コマンドを送出する処理である。

【 0 1 3 0 】

そして、2 m s 毎に定期的にタイマ割込がかかるように C P U 5 6 に設けられている C T C のレジスタの設定が行われる（ステップ S 1 4）。すなわち、初期値として 2 m s に相当する値が所定のレジスタ（時間定数レジスタ）に設定される。そして、初期設定処理のステップ S 1 において割込禁止とされているので、初期化処理を終える前に割込が許可される（ステップ S 1 5）。

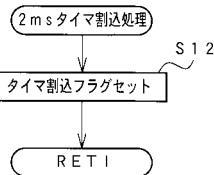

【 0 1 3 1 】

この実施の形態では、C P U 5 6 の内蔵 C T C が繰り返しタイマ割込を発生するように設定される。この実施の形態では、繰り返し周期は 2 m s に設定される。そして、タイマ割込が発生すると、図 1 9 に示すように、C P U 5 6 は、例えばタイマ割込が発生したことを示すタイマ割込フラグをセットする（ステップ S 1 2）。

10

20

30

40

50

## 【0132】

初期化処理の実行(ステップS11～S15)が完了すると、メイン処理で、タイマ割込が発生したか否かの監視(ステップS17)の確認が行われるループ処理に移行する。なお、ループ内では、表示用乱数更新処理(ステップS16)も実行される。

## 【0133】

CPU56は、ステップS17において、タイマ割込が発生したことを認識すると、ステップS21～S31の遊技制御処理を実行する。遊技制御処理において、CPU56は、まず、スイッチ回路58を介して、ゲートセンサ12、始動口センサ17、カウントセンサ23および入賞口スイッチ19a, 19b, 24a, 24b等のスイッチの状態を入力し、それらの状態判定を行う(スイッチ処理:ステップS21)。

10

## 【0134】

次いで、パチンコ遊技機1の内部に備えられている自己診断機能によって種々の異常診断処理が行われ、その結果に応じて必要ならば警報が発せられる(エラー処理:ステップS22)。

## 【0135】

次に、遊技制御に用いられる大当たり判定用の乱数等の各判定用乱数を示す各カウンタを更新する処理を行う(ステップS23)。CPU56は、さらに、停止図柄の種類を決定する乱数等の表示用乱数を更新する処理を行う(ステップS24)。

## 【0136】

さらに、CPU56は、特別図柄プロセス処理を行う(ステップS25)。特別図柄プロセス制御では、遊技状態に応じてパチンコ遊技機1を所定の順序で制御するための特別図柄プロセスフラグに従って該当する処理が選び出されて実行される。そして、特別図柄プロセスフラグの値は、遊技状態に応じて各処理中に更新される。また、普通図柄プロセス処理を行う(ステップS26)。普通図柄プロセス処理では、7セグメントLEDによる可変表示器10を所定の順序で制御するための普通図柄プロセスフラグに従って該当する処理が選び出されて実行される。そして、普通図柄プロセスフラグの値は、遊技状態に応じて各処理中に更新される。

20

## 【0137】

次いで、CPU56は、特別図柄に関する表示制御コマンドをRAM55の所定の領域に設定して表示制御コマンドを送出する処理を行う(特別図柄コマンド制御処理:ステップS27)。また、普通図柄に関する表示制御コマンドをRAM55の所定の領域に設定して表示制御コマンドを送出する処理を行う(普通図柄コマンド制御処理:ステップS28)。

30

## 【0138】

さらに、CPU56は、例えばホール管理用コンピュータに供給される大当たり情報、始動情報、確率変動情報などのデータを出力する情報出力処理を行う(ステップS29)。

## 【0139】

また、CPU56は、所定の条件が成立したときにソレノイド回路59に駆動指令を行う(ステップS30)。ソレノイド回路59は、駆動指令に応じてソレノイド16, 21を駆動し、可変入賞球装置15または開閉板20を開状態または閉状態とする。

40

## 【0140】

そして、CPU56は、各入賞口への入賞を検出するためのスイッチ17, 23, 19a, 19b, 24a, 24bの検出出力にもとづく賞球数の設定などを行う賞球処理を実行する(ステップS31)。具体的には、入賞検出に応じて払出制御基板37に払出制御コマンドを出力する。払出制御基板37に搭載されている払出制御用CPU371は、払出制御コマンドに応じて球払出装置97を駆動する。

## 【0141】

以上の制御によって、この実施の形態では、遊技制御処理は2ms毎に起動されることになる。なお、この実施の形態では、タイマ割込処理では例えば割込が発生したことを示すフラグのセットのみがなされ、遊技制御処理はメイン処理において実行されるが、タイマ

50

割込処理で遊技制御処理を実行してもよい。

【0142】

また、メイン処理には遊技制御処理に移行すべきか否かを判定する処理が含まれ、C P U 56の内部タイマが定期的に発生するタイマ割込にもとづくタイマ割込処理で遊技制御処理に移行すべきか否かを判定するためのフラグがセット等がなされるので、遊技制御処理の全てが確実に実行される。つまり、遊技制御処理の全てが実行されるまでは、次回の遊技制御処理に移行すべきか否かの判定が行われないので、遊技制御処理中の全ての各処理が実行完了することは保証されている。

【0143】

以上に説明したように、この実施の形態では、電力供給開始時、または、復帰信号の入力時にクリアスイッチ921の出力の状態を判定する処理が実行され、クリアスイッチ921がオン状態であることを条件に、遊技状態が保存されていたとしても遊技状態復旧処理は実行されず通常の初期化処理が実行される。よって、遊技店員等は、遊技機の電源供給再開時に、クリアスイッチ921を操作することによって、バックアップデータ記憶領域（記憶内容保持手段）に記憶されているバックアップデータを容易にクリアすることができる。従って、遊技店での遊技機運用上の利便性を向上させることもできる遊技機が提供される。

【0144】

なお、この実施の形態では、ステップS7でクリアスイッチ921のオンが検出されない場合に、バックアップデータの有無が確認されたが、バックアップデータの有無を確認した後にクリアスイッチ921の操作状態を確認するようにしてもよい。さらに、バックアップ領域のチェックを行いバックアップ領域のチェック結果が正常であったことが確認された場合に、クリアスイッチ921の操作状態を確認するようにしてもよい。

【0145】

また、この実施の形態では、ステップS8でバックアップデータの有無が確認された後でステップS9でバックアップ領域のチェックが行われたが、バックアップ領域のチェック結果が正常であったことが確認された後にバックアップデータの有無の確認を行うようにしてもよい。また、バックアップデータの有無の確認とバックアップ領域のチェックとのいずれれか一方の処理を行うことによって、遊技状態復旧処理を実行するか否か判定してもよい。さらに、遊技状態を復旧するか否か判断する際に、保存されていたR A Mデータにおける特別プロセスフラグ等や始動入賞記憶数データによって、遊技機が遊技待機状態（図柄変動中でなく、大当たり遊技中でなく、確変中でなく、また、始動入賞記憶がない状態）であることが確認されたら、遊技状態復旧処理を行わずに初期化処理を実行するようにしてもよい。

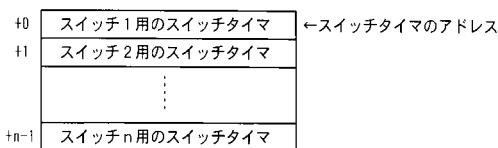

【0146】

この実施の形態では、遊技球を検出するためのスイッチ（各入賞口スイッチ）の検出信号のオン状態が所定時間継続すると、確かにスイッチがオンしたと判定されスイッチオンに対応した処理が開始される。所定時間を計測するために、スイッチタイマが用いられる。スイッチタイマは、バックアップR A M領域に形成された1バイトのカウンタであり、検出信号がオン状態を示している場合に2m s毎に+1される。図20に示すように、スイッチタイマは検出信号の数Nだけ設けられている。この実施の形態ではN=12である。また、R A Mにおいて、各スイッチタイマのアドレスは、入力ポートのビット配列順（図16に示された上から下への順）と同じ順序で並んでいる。

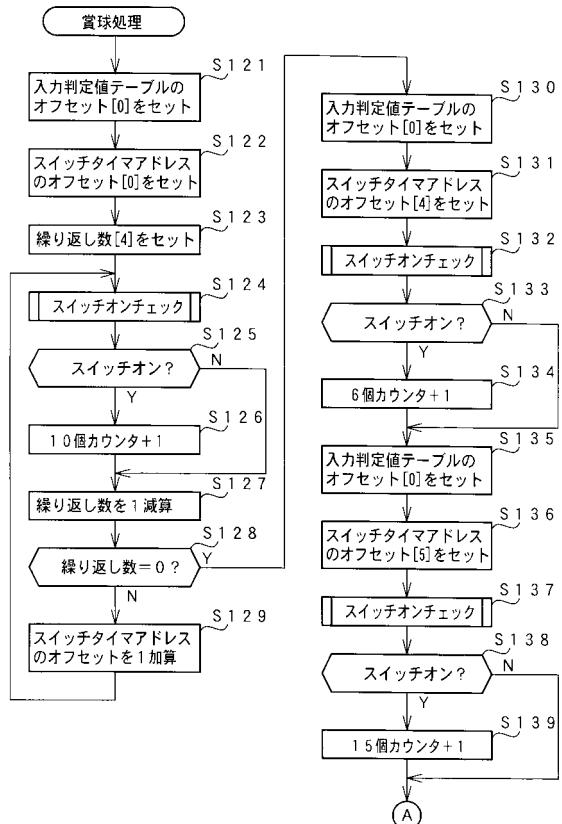

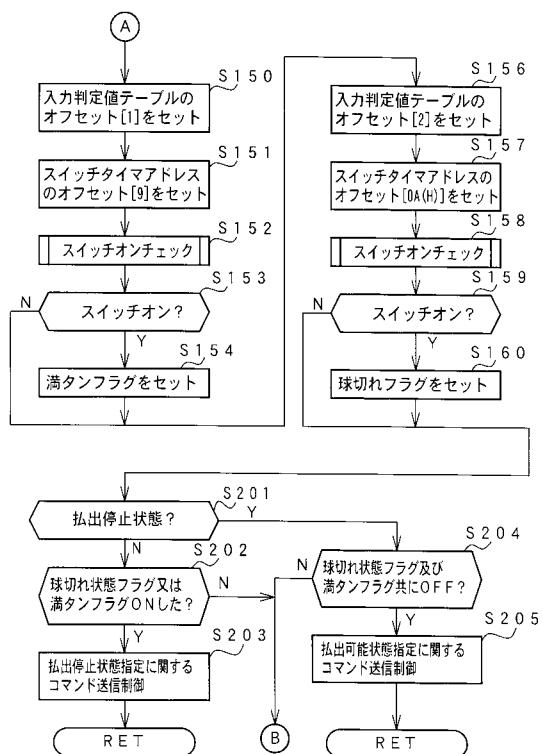

【0147】

図21～図23は、遊技制御処理におけるステップS31の賞球処理の一例を示すフローチャートである。この実施の形態では、賞球処理では、入賞口スイッチ19a, 19b, 24a, 24b、カウントスイッチ23および始動口スイッチ17が確実にオンしたか否か判定されるとともに、オンしたら所定の払出制御コマンドが払出制御基板37に送出されるように制御し、また、満タンスイッチ48および球切れスイッチ187が確実にオンしたか否か判定されるとともに、オンしたら所定の払出制御コマンドが払出制御基板37

10

20

30

40

50

に送出されるように制御する等の処理が行われる。

【0148】

賞球処理において、CPU56は、入力判定値テーブルのオフセットとして「0」を設定し(ステップS121)、スイッチタイマのアドレスのオフセットとして「0」を設定する(ステップS122)。入力判定値テーブルのオフセット「0」は、入力判定値テーブルの最初のデータを使用することを意味する。また、各スイッチタイマは、図16に示された入力ポートのビット順と同順に並んでいるので、スイッチタイマのアドレスのオフセット「0」は入賞口スイッチ24aに対応したスイッチタイマが指定されることを意味する。また、繰り返し数として「4」をセットする(ステップS123)。そして、スイッチオンチェックルーチンがコールされる(ステップS124)。

10

【0149】

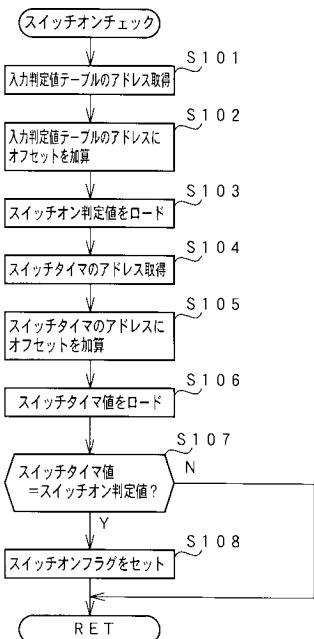

入力判定値テーブルとは、各スイッチについて、連続何回のオンが検出されたら確かにスイッチがオンしたと判定するための判定値が設定されているROM領域である。入力判定値テーブルの構成例は図25に示されている。図25に示すように、入力判定値テーブルには、上から順に、すなわちアドレス値が小さい領域から順に、「2」、「50」、「250」、「30」、「250」、「1」の判定値が設定されている。また、スイッチオンチェックルーチンでは、入力判定値テーブルの先頭アドレスとオフセット値とで決まるアドレスに設定されている判定値と、スイッチタイマの先頭アドレスとオフセット値とで決まるスイッチタイマの値とが比較され、一致した場合には、例えばスイッチオンフラグがセットされる。

20

【0150】

スイッチオンチェックルーチンの一例が図24に示されている。スイッチオンチェックルーチンにおいて、CPU56は、入力判定値テーブル(図24参照)の先頭アドレスを設定する(ステップS101)。そして、そのアドレスにオフセットを加算し(ステップS102)、加算後のアドレスからスイッチオン判定値をロードする(ステップS103)。

【0151】

次いで、CPU56は、スイッチタイマの先頭アドレスを設定し(ステップS104)、そのアドレスにオフセットを加算し(ステップS105)、加算後のアドレスからスイッチタイマの値をロードする(ステップS106)。各スイッチタイマは、図16に示された入力ポートのビット順と同順に並んでいるので、スイッチに対応したスイッチタイマの値がロードされる。

30

【0152】

そして、CPU56は、ロードしたスイッチタイマの値とスイッチオン判定値とを比較する(ステップS107)。それらが一致すれば、スイッチオンフラグをセットする(ステップ108)。

【0153】

この場合には、スイッチオンチェックルーチンにおいて、入賞口スイッチ24aに対応するスイッチタイマの値がスイッチオン判定値「2」に一致していればスイッチオンフラグがセットされる(ステップS125)。スイッチオンフラグがセットされたら、10個カウンタが1加算される(ステップS126)。スイッチチェックオンルーチンは、スイッチタイマのアドレスのオフセットが更新されつつ(ステップS129)、最初に設定された繰り返し数分だけ実行されるので(ステップS127, S128)、結局、入賞口スイッチ19a, 19b, 24a, 24bについて、対応するスイッチタイマの値がスイッチオン判定値「2」と比較されることになる。なお、10個カウンタとは、景品としての10個の遊技球払出の回数を示すカウンタである。

40

【0154】

次に、CPU56は、入力判定値テーブルのオフセットとして「0」を設定し(ステップS130)、スイッチタイマのアドレスのオフセットとして「4」を設定する(ステップS131)。入力判定値テーブルのオフセット「0」は、入力判定値テーブルの最初のデ

50

ータを使用することを意味する。また、各スイッチタイマは、図16に示された入力ポートのビット順と同順に並んでいるので、スイッチタイマのアドレスのオフセット「4」は始動口スイッチ17に対応したスイッチタイマが指定されることを意味する。そして、スイッチオンチェックルーチンがコールされる（ステップS132）。

#### 【0155】

スイッチオンチェックルーチンにおいて、始動口スイッチ17に対応するスイッチタイマの値がスイッチオン判定値「2」に一致していればスイッチオンフラグがセットされるので（ステップS133）、6個カウンタが1加算される（ステップS134）。なお、6個カウンタとは、景品としての6個の遊技球払出の回数を示すカウンタである。

#### 【0156】

次いで、CPU56は、入力判定値テーブルのオフセットとして「0」を設定し（ステップS135）、スイッチタイマのアドレスのオフセットとして「5」を設定する（ステップS136）。入力判定値テーブルのオフセット「0」は、入力判定値テーブルの最初のデータを使用することを意味する。また、各スイッチタイマは、図16に示された入力ポートのビット順と同順に並んでいるので、スイッチタイマのアドレスのオフセット「5」はカウントスイッチ23に対応したスイッチタイマが指定されることを意味する。そして、スイッチオンチェックルーチンがコールされる（ステップS137）。

#### 【0157】

スイッチオンチェックルーチンにおいて、カウントスイッチ23に対応するスイッチタイマの値がスイッチオン判定値「2」に一致していればスイッチオンフラグがセットされるので（ステップS138）、15個カウンタが1加算される（ステップS134）。なお、15個カウンタとは、景品としての15個の遊技球払出の回数を示すカウンタである。

#### 【0158】

さらに、CPU56は、入力判定値テーブルのオフセットとして「1」を設定し（ステップS150）、スイッチタイマのアドレスのオフセットとして「9」を設定する（ステップS151）。入力判定値テーブルのオフセット「1」は、入力判定値テーブルの2番目のデータ「50」を使用することを意味する。また、各スイッチタイマは、図16に示された入力ポートのビット順と同順に並んでいるので、スイッチタイマのアドレスのオフセット「9」は満タンスイッチ48に対応したスイッチタイマが指定されることを意味する。そして、スイッチオンチェックルーチンがコールされる（ステップS152）。

#### 【0159】

スイッチオンチェックルーチンにおいて、満タンスイッチ48に対応するスイッチタイマの値が満タンスイッチオン判定値「50」に一致していればスイッチオンフラグがセットされるので（ステップS153）、満タンフラグがセットされる（ステップS154）。なお、図22には明示されていないが、満タンスイッチ48に対応したスイッチタイマの値が0になると、満タンフラグはリセットされる。

#### 【0160】

また、CPU56は、入力判定値テーブルのオフセットとして「2」を設定し（ステップS156）、スイッチタイマのアドレスのオフセットとして「0A(H)」を設定する（ステップS157）。入力判定値テーブルのオフセット「2」は、入力判定値テーブルの3番目のデータ「250」を使用することを意味する。また、各スイッチタイマは、図16に示された入力ポートのビット順と同順に並んでいるので、スイッチタイマのアドレスのオフセット「0A(H)」は球切れスイッチ187に対応したスイッチタイマが指定されることを意味する。そして、スイッチオンチェックルーチンがコールされる（ステップS158）。

#### 【0161】

スイッチオンチェックルーチンにおいて、球切れスイッチ187に対応するスイッチタイマの値が球切れスイッチオン判定値「250」に一致していればスイッチオンフラグがセットされるので（ステップS159）、球切れフラグがセットされる（ステップS160）。なお、図22には明示されていないが、球切れスイッチ187に対応したスイッチオ

10

20

30

40

50

フタイマが用意され、その値が 50 になると、球切れフラグはリセットされる。

【0162】

そして、CPU56 は、払出停止状態であるか否か確認する（ステップ S201）。払出停止状態は、払出制御基板 37 に対して払出停止状態指定のコマンドを送出した後の状態である。払出停止状態でなければ、上述した球切れ状態フラグまたは満タンフラグがオンになったか否かを確認する（ステップ S202）。

【0163】

いずれかがオン状態に変化したときには、払出停止状態指定に関するコマンド送信制御処理を行う（ステップ S203）。コマンド送信制御処理では、払出制御コマンド用のコマンド送信テーブルに所定のデータが設定された後、払出制御コマンドの送出処理が実行される。なお、ステップ S202において、いずれか一方のフラグが既にオン状態であったときに他方のフラグがオン状態になったときには、コマンド送信制御処理（ステップ S203）は行われない。10

【0164】

また、払出停止状態であれば、球切れ状態フラグおよび満タンフラグがともにオフ状態になったか否かを確認する（ステップ S204）。ともにオフ状態となったときには、払出停止解除指定に関するコマンド送信制御処理を行う（ステップ S205）。

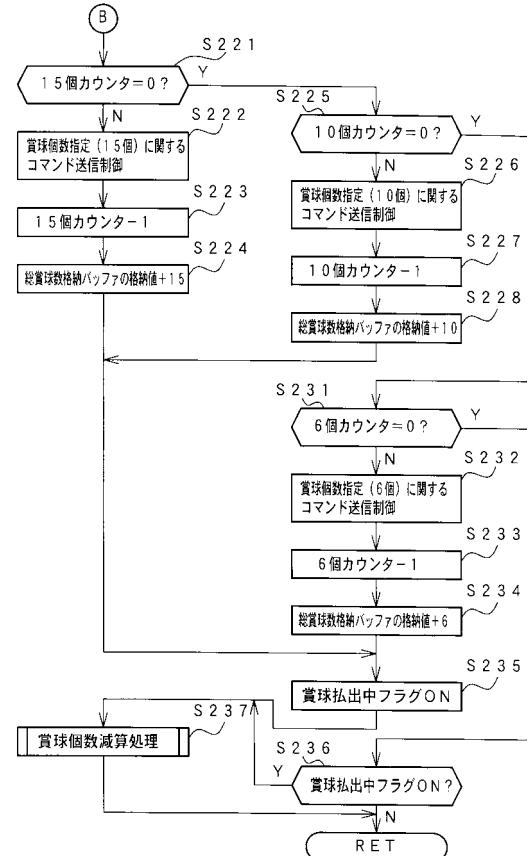

【0165】

次いで、CPU56 は、入賞に応じた賞球個数に関する払出制御コマンドをコマンド送信テーブルに設定し、設定内容に応じた払出制御コマンドを送出する制御を行う。まず、15 個カウンタの値をチェックする（ステップ S221）。上述したように、15 個カウンタは、遊技球が大入賞口に入賞してカウントスイッチ 23 がオンするとカウントアップされる。15 個カウンタの値が 0 でない場合には、15 個の賞球個数指示に関するコマンド送信制御処理を行う（ステップ S222）。コマンド送信制御処理では、払出制御コマンド用のコマンド送信テーブルに所定のデータが設定された後、払出制御コマンドの送出処理が実行される。また、15 個カウンタの値を -1 する（ステップ S223）。さらに、総賞球数格納バッファの格納値に 15 を加算する（ステップ S224）。20

【0166】

総賞球数格納バッファは、払出制御手段に対して指示した賞球個数の累積値（ただし、払い出しがなされると減算される）が格納されるバッファであり、バックアップ RAM に形成されている。30

【0167】

15 個カウンタの値が 0 であれば、10 個カウンタの値をチェックする（ステップ S225）。上述したように、10 個カウンタは、遊技球が入賞口に入賞して入賞口スイッチ 19a, 19b, 24a, 24b がオンするとカウントアップされる。10 個カウンタの値が 0 でない場合には、10 個の賞球個数指示に関するコマンド送信制御処理を行う（ステップ S226）。また、10 個カウンタの値を -1 する（ステップ S227）。さらに、総賞球数格納バッファの格納値に 10 を加算する（ステップ S228）。

【0168】

10 個カウンタの値が 0 であれば、6 個カウンタの値をチェックする（ステップ S231）。上述したように、6 個カウンタは、遊技球が始動入賞口に入賞して始動口スイッチ 17 がオンするとカウントアップされる。6 個カウンタの値が 0 でない場合には、6 個の賞球個数指示に関するコマンド送信制御処理を行う（ステップ S232）。また、6 個カウンタの値を -1 する（ステップ S233）。さらに、総賞球数格納バッファの格納値に 6 を加算する（ステップ S234）。40

【0169】

以上のようにして、遊技制御手段から払出制御基板 37 に賞球個数を指示する払出制御コマンドを出力しようとすると、コマンド送信テーブルの設定が行われた後、コマンド送信テーブルに設定された払出制御コマンドが払出制御基板 37 に送出される。そして、賞球個数を指示する払出制御コマンドの送出が行われたときには、賞球払出中フラグをオ50

ンする（ステップS235）。また、賞球払出中フラグをオンしているときには（ステップS236）、球払出装置97から実際に払い出された賞球数を監視して総賞球数格納バッファの格納値を減算する賞球個数減算処理が行われる（ステップS237）。

#### 【0170】

賞球処理は、2ms毎に起動されるので、スイッチオン判定値として「2」が用いられる場合には、賞球処理が少なくとも2回起動されないと、スイッチオンとは見なされない。つまり、オン状態が少なくとも2ms（1回目の検出直前に検出信号がオンした場合）継続しないとスイッチオンとは見なされない。これに対して、この実施の形態では、クリアスイッチ921のオン検出の場合には、1回のオン判定でオン／オフが判定される。すなわち、初期化操作手段としてのクリアスイッチ921が所定の操作状態であるか否かをCPU56が判定するための初期化要求検出判定期間は、遊技媒体検出手段としての各入賞口スイッチが遊技媒体を検出したことを判定するための遊技媒体検出判定期間とは異なる期間とされている。

#### 【0171】

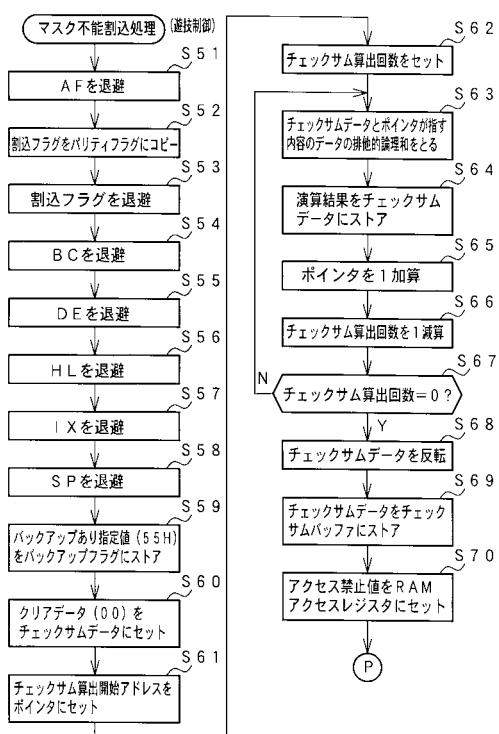

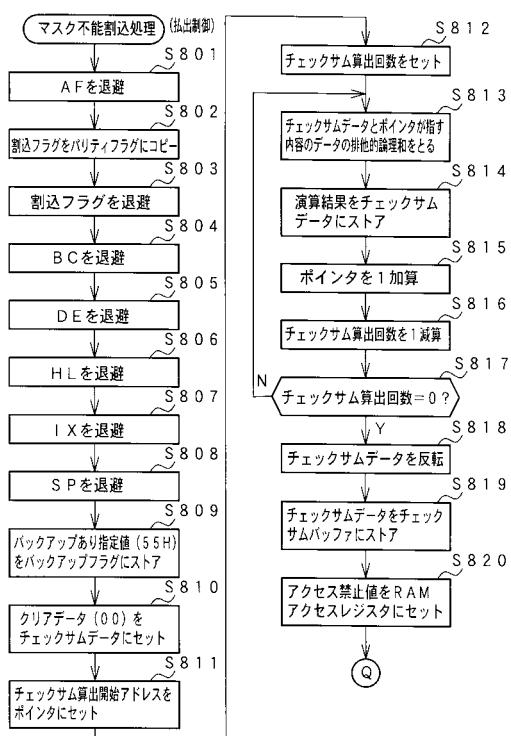

図26、図27は、電源基板910からの電源断信号に応じて実行されるマスク不能割込処理（電力供給停止時処理）の処理例を示すフローチャートである。

#### 【0172】

電力供給停止時処理において、CPU56は、AFレジスタ（アキュミュレータとフラグのレジスタ）を所定のバックアップRAM領域に退避する（ステップS51）。また、割込フラグをパリティフラグにコピーする（ステップS52）。パリティフラグはバックアップRAM領域に形成されている。また、BCレジスタ、DEレジスタ、HLレジスタ、IXレジスタおよびスタックポインタをバックアップRAM領域に退避する（ステップS54～S58）。

#### 【0173】

次に、バックアップあり指定値（この例では「55H」）をバックアップフラグにストアする。バックアップフラグはバックアップRAM領域に形成されている。次いで、パリティデータを作成する（ステップS60～S67）。すなわち、まず、クリアデータ（00）をチェックサムデータエリアにセットし（ステップS60）、チェックサム算出開始アドレスをポインタにセットする（ステップS61）。また、チェックサム算出回数をセットする（ステップS62）。

#### 【0174】

そして、チェックサムデータエリアの内容とポインタが指すRAM領域の内容との排他的論理和を演算する（ステップS63）。演算結果をチェックサムデータエリアにストアするとともに（ステップS64）、ポインタの値を1増やし（ステップS65）、チェックサム算出回数の値を1減算する（ステップS66）。ステップS63～S66の処理が、チェックサム算出回数の値が0になるまで繰り返される（ステップS67）。

#### 【0175】

チェックサム算出回数の値が0になったら、CPU56は、チェックサムデータエリアの内容の各ビットの値を反転する（ステップS68）。そして、反転後のデータをチェックサムデータエリアにストアする（ステップS69）。このデータが、電源投入時にチェックされるパリティデータとなる。次いで、RAMアクセスレジスタにアクセス禁止値を設定する（ステップS70）。以後、内蔵RAM55のアクセスができなくなる。従って、電圧低下に伴ってプログラムの暴走が生じても、RAMの記憶内容が破壊されるようなことはない。

#### 【0176】

さらに、CPU56は、クリアデータ（00）を適当なレジスタにセットし（ステップS71）、処理数（この例では「7」）を別のレジスタにセットする（ステップS72）。また、出力ポート0のアドレスをI/Oポインタに設定する（ステップS73）。I/Oポインタとして、さらに別のレジスタが用いられる。

#### 【0177】

10

20

30

40

50

そして、I/Oポインタが指すアドレスにクリアデータをセットするとともに（ステップS74）、I/Oポインタの値を1増やし（ステップS75）、処理数の値を1減算する（ステップS77）。ステップS74～S76の処理が、処理数の値が0になるまで繰り返される。その結果、全ての出力ポート0～6（図14および図15参照）にクリアデータが設定される。図14および図15に示すように、この例では、「1」がオン状態であり、クリアデータである「00」が各出力ポートにセットされるので、全ての出力ポートがオフ状態になる。

#### 【0178】

従って、遊技状態を保存するための処理（この例では、チェックサムの生成およびRAMアクセス防止）が実行された後、各出力ポートは直ちにオフ状態になる。なお、この実施の形態では、遊技制御処理において用いられるデータが格納されるRAM領域は全て電源バックアップされている。従って、その内容が正しく保存されているか否かを示すチェックサムの生成処理、およびその内容を書き換えないようにするためのRAMアクセス防止処理が、遊技状態を保存するための処理に相当する。

10

#### 【0179】

遊技状態を保存するための処理が実行された後、直ちに各出力ポートがオフ状態になるので、保存される遊技状態と整合しない状況が発生することは確実に防止される。図26に示す処理が実行されるときには、遊技機に対する電源供給が停止するので、電気部品に印加される電圧が低下していく。そして、印加電圧が駆動可能電圧を下回った時点で電気部品の駆動は停止する。従って、遊技機に対する電力供給停止時には、短時間の遅れはあるものの電気部品の駆動は停止する。

20

#### 【0180】

出力ポートに対するクリア処理が完了すると、CPU56は、待機状態（ループ状態）に入る。従って、システムリセットされるまで、何もしない状態になる。

#### 【0181】

上述したように、電源の瞬断等に起因して電源断信号が発生した場合には、電源電圧は平常時の値に復旧し遊技機は制御可能な状態に戻る。そのような状況が発生したときには、電源基板910から復帰信号が主基板31に供給される。主基板31において、復帰信号が入力されると、CPU56にリセットがかかる。従って、CPU56は、図17に示されたメイン処理の実行を開始することができる。その際、電源断信号が出力されたときに遊技状態が保存されているので、ステップS9の処理で遊技状態復旧処理が実行され、遊技制御は、電源断信号発生時の状態に戻り、その状態から遊技制御が続行される。

30

#### 【0182】

なお、この実施の形態では、NMIに応じて電力供給停止時処理が実行されたが、電源断信号をCPU56のマスク可能端子に接続し、マスク可能割込処理によって電力供給停止時処理を実行してもよい。また、電源断信号を入力ポートに入力し、入力ポートのチェック結果に応じて電力供給停止時処理を実行してもよい。

#### 【0183】

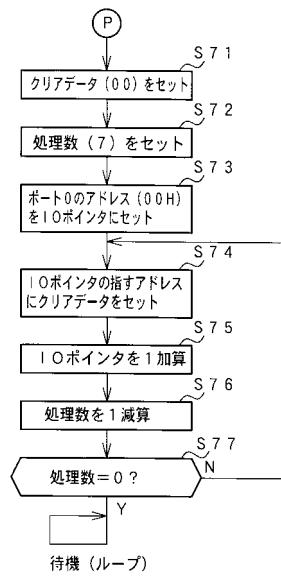

以下、遊技状態復旧処理について説明する。

図28は、図17のステップS10に示された遊技状態復旧処理の一例を示すフローチャートである。この例では、CPU56は、バックアップRAMに保存されていた値を各レジスタに復元する（ステップS91）。そして、バックアップRAMに保存されていたデータにもとづいて停電時の遊技状態を確認して復帰させる。すなわち、バックアップRAMに保存されていたデータにもとづいて、ソレノイド回路59を介してソレノイド16やソレノイド21を駆動し、始動入賞口14や開閉板20の開閉状態の復旧を行う（ステップS92, S93）。また、電源断中でも保存されていた特別図柄プロセスフラグおよび普通図柄プロセスフラグの値に応じて、電源断時の特別図柄プロセス処理の進行状況および普通図柄プロセス処理の進行状況に対応した制御コマンドを、図柄制御基板80、ランプ制御基板35および音声制御基板70に送出する（ステップS94）。

40

#### 【0184】

50

以上のように、遊技状態復旧処理では、復元された内部状態に応じて、各種電気部品の状態復元が行われるとともに、図柄制御基板80、ランプ制御基板35および音声制御基板70に対して、制御状態を電源断時の状態に戻すための制御コマンド（電源断時の制御状態を生じさせるための制御コマンド）が送出される。そのような制御コマンドは、一般に、電源断前に最後に送出された1つまたは複数の制御コマンドである。

#### 【0185】

遊技状態を電源断時の状態に復帰させると、この実施の形態では、CPU56は、前回の電源断時の割込許可／禁止状態を復帰させるため、バックアップRAMに保存されていたパリティフラグの値を確認する（ステップS95）。パリティフラグがオフ状態であれば、割込許可設定を行う（ステップS96）。しかし、パリティフラグがオン状態であれば、そのまま（ステップS1で設定された割込禁止状態のまま）遊技状態復旧処理を終了する。パリティフラグがオン状態であるということは、図26におけるステップS52に示されたように、前回の電源断時に割込禁止状態であったことを意味する。従って、パリティフラグがオン状態である場合には、割込許可はなされない。

10

#### 【0186】

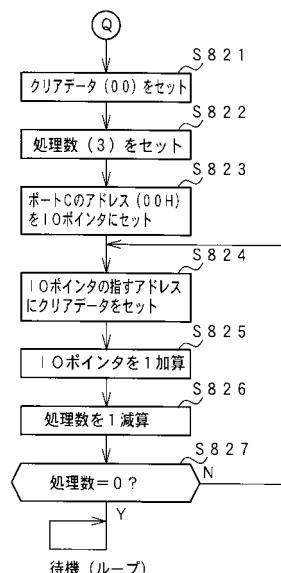

図29は、遊技制御手段のマスク不能割込処理（電力供給停止時処理）の他の例の一部を示すフローチャートである。図29に示すフローチャートは、図26に示されたステップS51～S70の処理に続いて実行される。すなわち、この実施の形態では、RAMアクセス禁止状態に設定された後（ステップS70）、クリアデータテーブルの先頭アドレスがポインタにセットされ（ステップS78）、次いで、データクリア処理が実行された後に（ステップS79）、システムリセットを待つ待機状態に入る。なお、ポインタとして所定のレジスタが用いられる。

20

#### 【0187】

図30は、クリアデータテーブルの一構成例を示す説明図である。図30に示す例では、クリアデータテーブルには、順に、処理数データ（この例では「7」）、出力ポート0のアドレス、出力ポート0に設定されるべきクリアデータ、・・・、出力ポート6のアドレス、出力ポート6に設定されるべきクリアデータが設定されている。出力ポートのアドレスとクリアデータとは、出力ポートのアドレスが小さいものから順に設定されている。

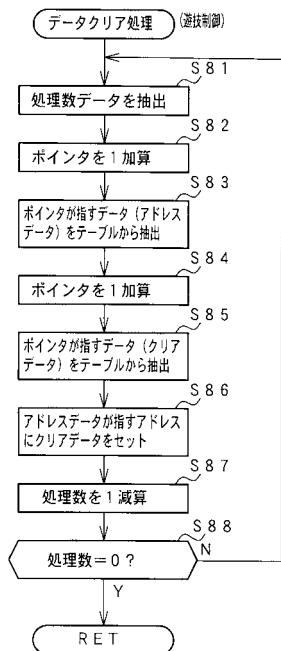

#### 【0188】

図31は、ステップS79のデータクリア処理を示すフローチャートである。データクリア処理において、CPU56は、ポインタの指すアドレスから処理数データを抽出する（ステップS81）。そして、ポインタの値を1増やす（ステップS82）。次いで、ポインタの指すアドレスからアドレスデータ（出力ポートのアドレス）を抽出する（ステップS83）。さらに、ポインタの値を1増やす（ステップS84）。

30

#### 【0189】

そして、ポインタの指すアドレスからクリアデータを抽出し（ステップS85）、そのデータを、ステップS83で抽出したアドレスに設定する（ステップS86）。次に、処理数の値を1減算し（ステップS87）、処理数が0になったらデータクリア処理を終了する（ステップS88）。処理数が0でない場合には、ステップS81に戻る。

#### 【0190】

40

なお、出力ポートのアドレス割り当ては、規則的に並んだアドレスであれば、1つ飛び等でもよく、そのような場合でも、ポートアドレスを求める演算処理（ステップS82）において、加算値を変えることによって次アドレスを容易に求めることができる。また、演算は加算に限らず、アドレスの割り当て方等に応じて減算や積算等であってもよい。

#### 【0191】

クリアデータテーブルを用いるようにしても、クリア信号出力処理を迅速に行なうことができ、遊技機への電力供給停止時に保存した制御状態と実際の制御状態との間の矛盾発生をより効果的に防止できる。そして、クリアデータテーブルを用いる場合には、テーブルにおいて、アドレスデータとクリアデータとをアドレス順に並べなくともよく、テーブル構成の自由度が増す。例えば、試験信号などを用いる遊技機において試験信号をクリアしな

50

いようにしたい場合に、試験信号に関する出力ポートに関するデータをテーブルから除外することによって、容易に試験信号のクリア処理を除外することができる。また、出力ポートの増減や変更があったような場合に、テーブルの内容を変更するだけでよく、プログラム変更の必要はない。

#### 【0192】

マスク不能割込処理が図31に示すように構成されている場合でも、電源基板910から復帰信号が主基板31に供給されると、CPU56にリセットがかかるので、CPU56は、図17に示されたメイン処理の実行を開始することができる。その際、電源断信号が10出力されたときに遊技状態が保存されているので、ステップS9の処理で遊技状態復旧処理が実行され、遊技制御は、電源断信号発生時の状態に戻り、その状態から遊技制御が続行される。

#### 【0193】

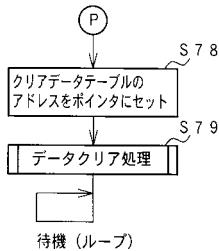

次に、遊技制御手段以外の電気部品制御手段においてデータ保存処理および復旧処理が行われる場合の例として、払出制御手段においてデータ保存や復旧が行われる場合について説明する。

#### 【0194】

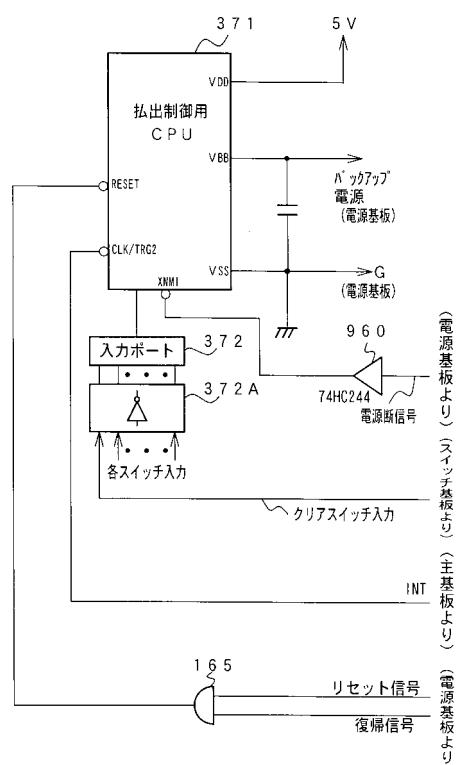

図32は、払出制御用CPU371周りの一構成例を示すブロック図である。図32に示すように、電源基板910の電源監視回路（電源監視手段）からの電源断信号が、バッファ回路960を介して払出制御用CPU371のマスク不能割込端子（XNM1端子）に接続されている。従って、払出制御用CPU371は、マスク不能割込処理によって電源断の発生を確認することができる。また、電源基板910からのリセット信号と復帰信号とはAND回路165に入力され、AND回路161の出力がCPU56のリセット端子に入力される。

#### 【0195】

払出制御用CPU371のCLK/TRG2端子には、主基板31からのINT信号が接続されている。CLK/TRG2端子にクロック信号が入力されると、払出制御用CPU371に内蔵されているタイマカウンタレジスタCLK/TRG2の値がダウンカウントされる。そして、レジスタ値が0になると割込が発生する。従って、タイマカウンタレジスタCLK/TRG2の初期値を「1」に設定しておけば、INT信号の入力に応じて割込が発生することになる。なお、INT信号とは、遊技制御手段から払出制御手段に対する払出制御コマンドが送出されたことを意味する信号である。払出制御用CPU371は、INT信号の入力に応じて発生する割込によって、払出制御コマンド受信処理を開始する。

#### 【0196】

また、スイッチ基板190に搭載されたクリアスイッチ921の出力信号が、バッファ回路（反転回路）372Aおよび入力ポート372を介して払出制御用CPU371に入力される。なお、入力ポート372には、バッファ回路372Aを介して賞球カウントスイッチ301Aおよび球貸しカウントスイッチ301Bの各スイッチの出力信号も入力されている。このような構成によれば、クリアスイッチ921に対する操作に応じてクリアスイッチ921の出力信号がローレベルを示すと、払出制御用CPU371にクリアスイッチ信号が与えられる。CPU56は、クリアスイッチ信号が与えられると、後述するように、バックアップRAMの記憶内容を初期データにする処理を行う。

#### 【0197】

図33は、この実施の形態における出力ポートの割り当てを示す説明図である。図33に示すように、出力ポートC（アドレス00H）は、払出モータ289に出力される駆動信号の出力ポートである。また、出力ポートD（アドレス01H）は、7セグメントLEDであるエラー表示LED374に出力される表示制御信号の出力ポートである。そして、出力ポートE（アドレス02H）は、振分ソレノイド310に出力される駆動信号、およびカードユニット50に対するEXS信号とPRDY信号とを出力するための出力ポートである。

## 【0198】

図34は、この実施の形態における入力ポートのピット割り当てを示す説明図である。図34に示すように、入力ポートA（アドレス06H）は、主基板31から送出された払出制御コマンドの8ビットの払出制御信号を取り込むための入力ポートである。また、入力ポートB（アドレス07H）のピット0～2には、それぞれ、賞球カウントスイッチ301A、球貸しカウントスイッチ301B、モータ位置センサの検出信号入力される。ピット3～6には、カードユニット50からのBRDY信号、BRQ信号、VL信号、クリアスイッチ921の出力信号が入力される。

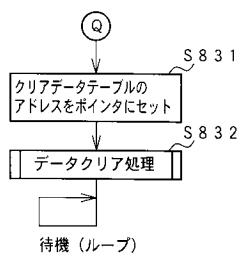

## 【0199】

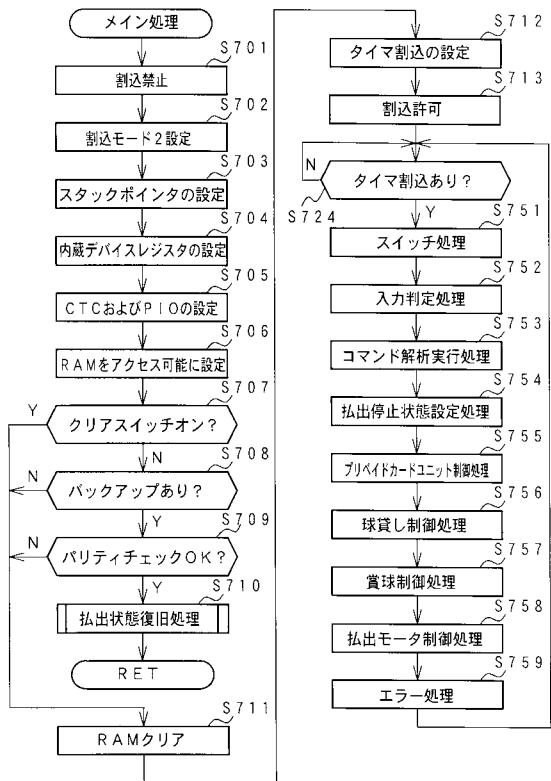

図35は、払出制御用CPU371が実行するメイン処理を示すフローチャートである。遊技機に対して電源が投入され、リセット端子の入力レベルがハイレベルになると、払出制御用CPU371は、ステップS701以降のメイン処理を開始する。なお、リセット端子の入力レベルがハイレベルになる場合として、遊技機に対する電力供給が開始された場合の他に、電源基板910から復帰信号が入力された場合（ローレベルからハイレベルに変化した場合）がある。

## 【0200】

初期設定処理において、払出制御用CPU371は、割込禁止に設定する（ステップS701）。次に、割込モードを割込モード2に設定し（ステップS702）、スタックポインタにスタックポインタ指定アドレスを設定する（ステップS703）。また、払出制御用CPU371は、内蔵デバイスレジスタの初期化を行い（ステップS704）、CTCおよびPIOの初期化（ステップS705）を行った後に、RAMをアクセス可能状態に設定する（ステップS706）。

## 【0201】

この実施の形態では、内蔵CTCのうちの一つのチャネルがタイマモードで使用される。従って、ステップS704の内蔵デバイスレジスタの設定処理およびステップS705の処理において、使用するチャネルをタイマモードに設定するためのレジスタ設定、割込発生を許可するためのレジスタ設定および割込ベクタを設定するためのレジスタ設定が行われる。そして、そのチャネルによる割込がタイマ割込として用いられる。タイマ割込を例えば2ms毎に発生させたい場合は、初期値として2msに相当する値が所定のレジスタ（時間定数レジスタ）に設定される。

## 【0202】

なお、タイマモードに設定されたチャネル（この実施の形態ではチャネル3）に設定される割込ベクタは、タイマ割込処理の先頭番地に相当するものである。具体的には、Iレジスタに設定された値と割込ベクタとでタイマ割込処理の先頭番地が特定される。タイマ割込処理ではタイマ割込フラグがセットされ、メイン処理でタイマ割込フラグがセットされていることが検知されると、払出制御処理が実行される。すなわち、タイマ割込処理では、電気部品制御処理の一例である払出制御処理を実行するための設定がなされる。

## 【0203】

また、内蔵CTCのうちの他の一つのチャネル（この実施の形態ではチャネル2）が、遊技制御手段からの払出制御コマンド受信のための割込発生用のチャネルとして用いられ、そのチャネルがカウンタモードで使用される。従って、ステップS704の内蔵デバイスレジスタの設定処理およびステップS705の処理において、使用するチャネルをカウンタモードに設定するためのレジスタ設定、割込発生を許可するためのレジスタ設定および割込ベクタを設定するためのレジスタ設定が行われる。

## 【0204】

カウンタモードに設定されたチャネル（チャネル2）に設定される割込ベクタは、後述するコマンド受信割込処理の先頭番地に相当するものである。具体的には、Iレジスタに設定された値と割込ベクタとでコマンド受信割込処理の先頭番地が特定される。

## 【0205】

この実施の形態では、払出制御用CPU371でも割込モード2が設定される。従って、

10

20

30

40

50

内蔵 C T C のカウントアップにもとづく割込処理を使用することができる。また、 C T C が送出した割込ベクタに応じた割込処理開始番地を設定することができる。

#### 【 0 2 0 6 】

C T C のチャネル 2 ( C H 2 ) のカウントアップにもとづく割込は、上述したタイマカウンタレジスタ C L K / T R G 2 の値が「 0 」になったときに発生する割込である。従って、例えばステップ S 7 0 5 において、特定レジスタとしてのタイマカウンタレジスタ C L K / T R G 2 に初期値「 1 」が設定される。また、 C T C のチャネル 3 ( C H 3 ) のカウントアップにもとづく割込は、 C P U の内部クロック ( システムクロック ) をカウントダウンしてレジスタ値が「 0 」になったら発生する割込であり、後述する 2 m s タイマ割込として用いられる。具体的には、 C H 3 のレジスタ値はシステムクロックの 1 / 2 5 6 周期で減算される。ステップ S 7 0 5 において、 C H 3 のレジスタには、初期値として 2 m s に相当する値が設定される。10

#### 【 0 2 0 7 】

C T C の C H 2 のカウントアップにもとづく割込は、 C H 3 のカウントアップにもとづく割込よりも優先順位が高い。従って、同時にカウントアップが生じた場合に、 C H 2 のカウントアップにもとづく割込、すなわち、コマンド受信割込処理の実行契機となる割込の方が優先される。

#### 【 0 2 0 8 】

次いで、払出制御用 C P U 3 7 1 は、入力ポート 3 7 2 を介して入力されるクリアスイッチ 9 2 1 の出力信号の状態を 1 回だけ確認する ( ステップ S 7 0 7 ) 。その確認においてオンを検出した場合には、払出制御用 C P U 3 7 1 は、通常の初期化処理を実行する ( ステップ S 7 1 1 ~ ステップ S 7 1 5 ) 。クリアスイッチ 9 2 1 がオンである場合 ( 押下されている場合 ) には、ローレベルのクリアスイッチ信号が出力されている。なお、入力ポート 3 7 2 では、クリアスイッチ信号のオン状態はハイレベルである。20

#### 【 0 2 0 9 】

なお、払出制御用 C P U 3 7 1 も、主基板 3 1 の C P U 5 6 と同様に、遊技球検出出力のオン判定を行う場合には、例えば、オン状態が少なくとも 2 m s ( 2 m s 毎に起動される処理の 1 回目の処理における検出直前に検出信号がオンした場合 ) 繼続しないとスイッチオンとは見なさないが、クリアスイッチ 9 2 1 のオン検出の場合には、1 回のオン判定でオン / オフが判定される。すなわち、初期化操作手段としてのクリアスイッチ 9 2 1 が所定の操作状態であるか否かを払出制御用 C P U 3 7 1 が判定するための初期化要求検出判定期間は、遊技媒体検出手段としての賞球カウントスイッチ等が遊技媒体を検出したことを判定するための遊技媒体検出判定期間とは異なる期間とされている。30

#### 【 0 2 1 0 】

クリアスイッチ 9 2 1 がオンの状態でない場合には、払出制御用 C P U 3 7 1 は、払出制御用のバックアップ RAM 領域にバックアップデータが存在しているか否かの確認を行う ( ステップ S 7 0 8 ) 。例えば、主基板 3 1 の C P U 5 6 の処理と同様に、電源断時にセットされるバックアップフラグがセット状態になっているか否かによって、バックアップデータが存在しているか否か確認する。バックアップフラグがセット状態になっている場合には、バックアップデータありと判断する。40

#### 【 0 2 1 1 】

バックアップありを確認したら、払出制御用 C P U 3 7 1 は、バックアップ RAM 領域のデータチェック ( この例ではパリティチェック ) を行う。不測の電源断が生じた後に復旧した場合には、バックアップ RAM 領域のデータは保存されていたはずであるから、チェック結果は正常になる。チェック結果が正常でない場合には、内部状態を電源断時の状態に戻すことができないので、停電復旧時でない電源投入時に実行される初期化処理を実行する。

#### 【 0 2 1 2 】

チェック結果が正常であれば ( ステップ S 7 0 9 ) 、払出制御用 C P U 3 7 1 は、内部状態を電源断時の状態に戻すための払出状態復旧処理を行う ( ステップ S 7 1 0 ) 。そして50

、バックアップRAM領域に保存されていたPC（プログラムカウンタ）の指すアドレスに復帰する。

【0213】

初期化処理では、払出制御用CPU371は、まず、RAMクリア処理を行う（ステップS711）。そして、2ms毎に定期的にタイマ割込がかかるように払出制御用CPU371に設けられているRTCのレジスタの設定が行われる（ステップS712）。すなわち、初期値として2msに相当する値が所定のレジスタ（時間定数レジスタ）に設定される。そして、初期設定処理のステップS701において割込禁止とされているので、初期化処理を終える前に割込が許可される（ステップS713）。

【0214】

この実施の形態では、払出制御用CPU371の内蔵RTCが繰り返しタイマ割込を発生するように設定される。この実施の形態では、繰り返し周期は2msに設定される。そして、タイマ割込が発生すると、図36に示すように、払出制御用CPU371は、例えばタイマ割込が発生したこと음을示すタイマ割込フラグをセットする（ステップS721）。なお、図36には割込を許可することも明示されているが（ステップS720）、2msタイマ割込処理では、最初に割込許可状態に設定される。すなわち、2msタイマ割込処理中には割込許可状態になってので、INT信号の入力にもとづく払出制御コマンド受信処理を優先して実行することができる。

【0215】

払出制御用CPU371は、ステップS724において、タイマ割込フラグがセットされたことを検出するとステップS751以降の払出制御処理を実行する。以上の制御によって、この実施の形態では、払出制御処理は2ms毎に起動されることになる。なお、この実施の形態では、タイマ割込処理ではフラグセットのみがなされ、払出制御処理はメイン処理において実行されるが、タイマ割込処理で払出制御処理を実行してもよい。

【0216】

払出制御処理において、払出制御用CPU371は、まず、中継基板72を介して入力ポート372bに入力される賞球カウントスイッチ301A、球貸しカウントスイッチ301Bがオンしたか否かを判定する（スイッチ処理：ステップS751）。

【0217】

次に、払出制御用CPU371は、センサ（例えば、払出モータ289の回転数を検出するモータ位置センサ）からの信号入力状態を確認してセンサの状態を判定する等の処理を行う（入力判定処理：ステップS752）。払出制御用CPU371は、さらに、受信した払出制御コマンドを解析し、解析結果に応じた処理を実行する（コマンド解析実行処理：ステップS753）。

【0218】

次いで、払出制御用CPU371は、主基板31から払出停止指示コマンドを受信してから払出停止状態に設定し、払出開始指示コマンドを受信してから払出停止状態の解除を行う（ステップS754）。また、プリペイドカードユニット制御処理を行う（ステップS755）。

【0219】

次いで、払出制御用CPU371は、球貸し要求に応じて貸し球を払い出す制御を行う（ステップS756）。このとき、払出制御用CPU371は、振分ソレノイド310によって球振分部材311を球貸し側に設定する。

【0220】

さらに、払出制御用CPU371は、総合個数記憶に格納された個数の賞球を払い出す賞球制御処理を行う（ステップS757）。このとき、払出制御用CPU371は、振分ソレノイド310によって球振分部材311を賞球側に設定する。そして、出力ポート372cおよび中継基板72を介して球払出装置97の払出機構部分における払出モータ289に対して駆動信号を出力し、所定の回転数分払出モータ289を回転させる払出モータ制御処理を行う（ステップS758）。

10

20

30

40

50

## 【0221】

なお、この実施の形態では、払出モータ289としてステッピングモータが用いられ、それらを制御するために1-2相励磁方式が用いられる。従って、具体的には、払出モータ制御処理において、8種類の励磁パターンデータが繰り返し払出モータ289に出力される。また、この実施の形態では、各励磁パターンデータが4msずつ出力される。

## 【0222】

次いで、エラー検出処理が行われ、その結果に応じてエラー表示LED374に所定の表示を行う（エラー処理：ステップS759）。

## 【0223】

なお、出力ポートCは、払出制御処理における払出モータ制御処理（ステップS758）10でアクセスされる。また、出力ポートDは、払出制御処理におけるエラー処理（ステップS759）でアクセスされる。そして、出力ポートEは、払出制御処理における球貸し制御処理（ステップS756）および賞球制御処理（ステップS757）でアクセスされる。

## 【0224】

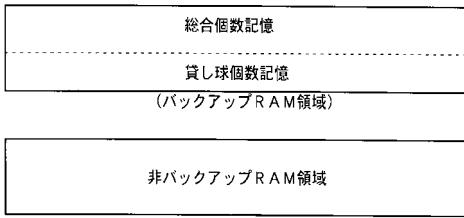

図37は、払出制御用CPU371が内蔵するRAMの使用例を示す説明図である。この例では、バックアップRAM領域に、総合個数記憶（例えば2バイト）と貸し球個数記憶とがそれぞれ形成されている。総合個数記憶は、主基板31の側から指示された賞球払出個数の総数を記憶するものである。貸し球個数記憶は、未払出の球貸し個数を記憶するものである。

20

## 【0225】

このように、未払出の賞球個数と貸し球個数とが、所定期間はその内容を保持可能なバックアップRAM領域に記憶されるので、停電等の不測の電源断が生じても、所定期間内に電源復旧すれば、バックアップRAM領域に記憶される賞球処理および球貸し処理を続行できる。従って、遊技者に与えられる不利益を低減することができる。

## 【0226】

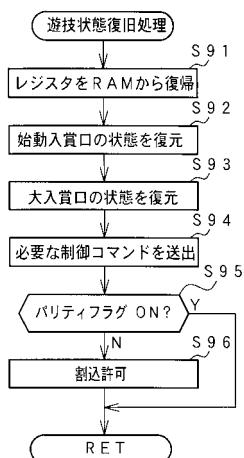

図38、図39は、電源基板910からの電源断信号に応じて実行されるマスク不能割込処理（電力供給停止時処理）の処理例を示すフローチャートである。

## 【0227】

電力供給停止時処理において、払出制御用CPU371は、AFレジスタを所定のバックアップRAM領域に退避する（ステップS801）。また、割込フラグをパリティフラグにコピーする（ステップS802）。パリティフラグはバックアップRAM領域に形成されている。また、BCレジスタ、DEレジスタ、HLレジスタ、IXレジスタおよびスタックポインタをバックアップRAM領域に退避する（ステップS804～808）。

30

## 【0228】

次に、バックアップあり指定値（この例では「55H」）をバックアップフラグにストアする。バックアップフラグはバックアップRAM領域に形成されている。次いで、主基板31のCPU56の処理と同様の処理を行ってパリティデータを作成しバックアップRAM領域に保存する（ステップS810～S819）。そして、RAMアクセスレジスタにアクセス禁止値を設定する（ステップS820）。以後、内蔵RAMのアクセスができないくなる。

40

## 【0229】

さらに、払出制御用CPU371は、クリアデータ（00）を適当なレジスタにセットし（ステップS821）、処理数（この例では「3」）を別のレジスタにセットする（ステップS822）。また、出力ポートCのアドレス（この例では「00H」）をI/Oポインタに設定する（ステップS823）。I/Oポインタとして、さらに別のレジスタが用いられる。

## 【0230】

そして、I/Oポインタが指すアドレスにクリアデータをセットするとともに（ステップS824）、I/Oポインタの値を1増やし（ステップS825）、処理数の値を1減算する

50

(ステップS827)。ステップS824～S826の処理が、処理数の値が0になるまで繰り返される。その結果、全ての出力ポートC～E(図33参照)にクリアデータが設定される。図33に示すように、この例では、「1」がオン状態であり、クリアデータである「00」が各出力ポートにセットされるので、全ての出力ポートがオフ状態になる。

#### 【0231】

従って、遊技状態を保存するための処理(この例では、チェックサムの生成およびRAMアクセス防止)が実行された後、各出力ポートは直ちにオフ状態になる。なお、この実施の形態では、払出制御処理において用いられるデータが格納されるRAM領域は全て電源バックアップされている。従って、その内容が正しく保存されているか否かを示すチェックサムの生成処理、およびその内容を書き換えないようにするためのRAMアクセス防止処理が、払出制御状態を保存するための処理に相当する。

10

#### 【0232】

制御状態を保存するための処理が実行された後、直ちに各出力ポートがオフ状態になるので、保存される遊技状態と整合しない状況が発生することは確実に防止される。一般に遊技機に対する電源供給が停止するときには、短時間の遅れはあるものの、各電気部品に対する電力供給も停止して動作が停止する。

#### 【0233】

出力ポートに対するクリア処理が完了すると、払出制御用CPU371は、待機状態(ループ状態)に入る。従って、システムリセットされるまで、何もしない状態になる。

#### 【0234】

上述したように、電源の瞬断等に起因して電源断信号が発生した場合には、電源電圧は平常時の値に復旧し遊技機は制御可能な状態に戻る。そのような状況が発生したときには、電源基板910から復帰信号が払出基板37に供給される。復帰信号が入力されると、払出制御用CPU371にリセットがかかる。従って、払出制御用CPU371は、図35に示されたメイン処理の実行を開始することができる。その際、電源断信号が出力されたときに制御状態が保存されているので、ステップS709の処理で払出状態復旧処理が実行され、払出制御は、電源断信号発生時の状態に戻り、その状態から払出制御が続行される。

20

#### 【0235】

図40は、本発明の他の実施の形態における払出制御手段のクリアデータテーブルを用いたマスク不能割込処理(電力供給停止時処理)の一部を示すフローチャートである。図40に示すフローチャートは、図38に示されたステップS801～S820の処理に続いて実行される。すなわち、この実施の形態では、RAMアクセス禁止状態に設定された後(ステップS820)、クリアデータテーブルの先頭アドレスがポインタにセットされ(ステップS831)、次いで、データクリア処理が実行された後に(ステップS832)、システムリセットを待つ待機状態に入る。なお、ポインタとして所定のレジスタが用いられる。

30

#### 【0236】

図41は、クリアデータテーブルの一構成例を示す説明図である。図41に示す例では、クリアデータテーブルには、順に、処理数データ(この例では「3」)、出力ポートCのアドレス(アドレス00H)、出力ポートCに設定されるべきクリアデータ、・・・、出力ポートEのアドレス(アドレス02H)、出力ポートEに設定されるべきクリアデータが設定されている。出力ポートのアドレスとクリアデータとは、出力ポートのアドレスが小さいものから順に設定されている。なお、出力ポートのアドレス割り当ては、規則的に並んだアドレスであれば、1つ飛び等でもよく、そのような場合でも、加算値を変えることによって次アドレスを容易に求めることができる。また、演算は加算に限らず、アドレスの割り当て方等に応じて減算や積算等であってもよい。

40

#### 【0237】

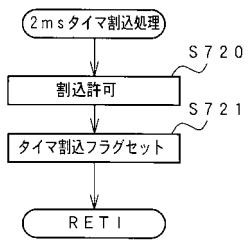

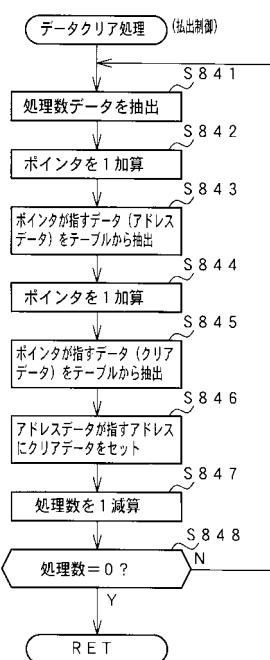

図42は、ステップS832のデータクリア処理を示すフローチャートである。データクリア処理において、払出制御用CPU371は、ポインタの指すアドレスから処理数データ

50

タを抽出する（ステップS841）。そして、ポインタの値を1増やす（ステップS842）。次いで、ポインタの指すアドレスからアドレスデータ（出力ポートのアドレス）を抽出する（ステップS843）。さらに、ポインタの値を1増やす（ステップS844）。

【0238】

そして、ポインタの指すアドレスからクリアデータを抽出し（ステップS845）、そのデータを、ステップS843で抽出したアドレスに設定する（ステップS846）。次に、処理数の値を1減算し（ステップS847）、処理数が0にならデータクリア処理を終了する（ステップS848）。処理数が0でない場合には、ステップS841に戻る。

10

【0239】

マスク不能割込処理が図40に示すように構成されている場合でも、電源基板910から復帰信号が払出制御基板37に供給されると、払出制御用CPU371にリセットがかかるので、払出制御用CPU371は、図35に示されたメイン処理の実行を開始することができる。その際、電源断信号が出力されたときに制御状態が保存されているので、ステップS709の処理で払出状態復旧処理が実行され、払出制御は、電源断信号発生時の状態に戻り、その状態から払出制御が続行される。

【0240】

以上のように、上記の各実施の形態では、記憶内容保持手段（例えばバックアップRAM）を有する遊技制御手段および払出制御手段が電源断信号に応じて電力供給停止時処理を行った後にシステムリセットを待つ待機状態にあるときに、電源復旧に応じて復帰信号が出力されると、遊技制御手段および払出制御手段は、プログラムの最初部分から動作を再開する。または、ソフトウェアによるタイマ処理でタイムアウトが生ずると、遊技制御手段および払出制御手段は、プログラムの最初部分から動作を再開する。その際、電力供給停止時処理において保存された制御状態が復旧されるので、遊技者から見ると、何事もなかったかのように遊技が続行される。

20

【0241】

また、電源基板に設けられている起動順序制御手段が、記憶内容保持手段を有していない電気部品制御手段と記憶内容保持手段を有している電気部品制御手段とを含む全ての電気部品制御手段を対象に、リセット信号の供給順序を制御することによって起動順序を制御するので、全ての電気部品制御手段の起動順序制御を、簡単な構成で実現できる。なお、上記の各実施の形態では、記憶内容保持手段を有していない電気部品制御手段は、表示制御手段、ランプ制御手段および音声制御手段であり、記憶内容保持手段を有している電気部品制御手段遊技制御手段および払出制御手段である。

30

【0242】

さらに、起動順序制御手段は、遊技制御手段を最後に起動するので、各電気部品制御手段が、遊技制御手段からの制御コマンドを取りこぼしてしまうという不都合は生じない。

【0243】

また、上記の各実施の形態では、電源基板910にクリアスイッチ921が設置され、バックアップ記憶手段を有する電気部品制御手段が起動する際に、クリアスイッチ921の出力信号がオン状態であれば、バックアップ記憶手段を初期化する。そして、電気部品制御手段の起動の契機は、電力供給開始に伴うリセット信号の立ち上がり、または、復帰信号の入力（ローレベルからハイレベルへの変化）である。従って、遊技機の電源投入時にクリアスイッチ921をオン状態にするだけで、バックアップ記憶手段に保存されていた制御状態をクリアすることができる。

40

【0244】

クリアスイッチ921のオン判定は、遊技機の制御処理の起動に先立ってバックアップ復帰（バックアップ記憶内容にもとづく復帰）の意思を確認するために、上記の各実施の形態のように、初期設定処理前に行われることが好ましい。その場合、初期設定処理前にタイマ処理や複数回のスイッチ入力判定を実行するとバックアップ記憶内容を破壊する可能

50

性が生じてくるので、クリアスイッチ 921 のオン判定処理では 1 回の判定でオン / オフの結果を判断することが好ましい。遊技機裏面等では遊技球が流動するのでノイズが生じやすいが、初期設定処理前に判定すれば、遊技球の検出を行うためのスイッチ入力判定処理の場合とは異なり、遊技開始前に判定が行われるので遊技球の流動は生じていない。従って、スイッチ入力判定処理の場合に複数回の検出を行うのに対して、クリアスイッチ 921 のオン判定の場合に 1 回の判定でオン / オフの結果を判断しても、ノイズの影響で誤判断がなされてしまう可能性は低い。また、1 回だけ判定するように構成すれば、プログラム構成が簡略化され開発効率が向上する。

#### 【 0 2 4 5 】

なお、上記の各実施の形態のパチンコ遊技機 1 は、始動入賞にもとづいて可変表示部 9 に可変表示される特別図柄の停止図柄が所定の図柄の組み合わせになると所定の遊技価値が遊技者に付与可能になる第 1 種パチンコ遊技機であったが、始動入賞にもとづいて開放する電動役物の所定領域への入賞があると所定の遊技価値が遊技者に付与可能になる第 2 種パチンコ遊技機や、始動入賞にもとづいて可変表示される図柄の停止図柄が所定の図柄の組み合わせになると開放する所定の電動役物への入賞があると所定の権利が発生または継続する第 3 種パチンコ遊技機であっても、本発明を適用できる。

#### 【 0 2 4 6 】

また、パチンコ遊技機に限らず、スロット機等においても、何らかの動作をする電気部品が備えられている場合などには本発明を適用することができる。

#### 【 0 2 4 7 】

##### 【発明の効果】

以上のように、本発明によれば、遊技機を、遊技制御用マイクロコンピュータおよび払出制御用マイクロコンピュータが、初期化操作手段が所定の操作状態である場合に記憶内容保持手段によって所定期間保持される記憶内容を初期化することが可能であるとともに、所定の電源の状態があらかじめ定められた所定の状態になったことが検出された場合に電力供給停止時処理を行った後に待機状態に移行し、電源監視手段によって所定の状態になったことが検出された後の所定期間経過後に電力供給が停止していない場合に待機状態から復帰させるための復帰信号を遊技制御用マイクロコンピュータおよび払出制御用マイクロコンピュータに向けて出力可能な復帰信号出力手段を備えた構成としたので、復帰信号によって遊技制御用マイクロコンピュータおよび払出制御用マイクロコンピュータを制御実行状態に復帰させることができ、その結果、ごく短時間で復旧する電源の瞬断等が生じても制御に支障を来すことがないという効果を得ることができ、さらに、記憶内容保持手段によって所定期間保存されている制御状態を容易にクリアすることができる。また、遊技制御用マイクロコンピュータおよび払出制御用マイクロコンピュータが、初期化操作手段からの操作信号が入力されているか否かを、遊技媒体を検出するための遊技媒体検出手段からの検出信号を判定する遊技媒体検出判定期間よりも短い要求検出判定期間で確認する場合には、初期化操作手段の操作状態を判定する処理と遊技媒体検出を行う処理とを異ならせることができるので、各々のオン判定期間を適切な期間に設定することができる。

#### 【 0 2 4 9 】

初期化操作手段からの操作信号が、遊技制御用マイクロコンピュータおよび払出制御用マイクロコンピュータの入力ポート部に入力されるように構成されている場合には、記憶内容保持手段によって所定期間保存されている制御状態をクリアするための構成を簡略化することができる。

#### 【 0 2 5 3 】

復帰信号出力手段が払出制御用マイクロコンピュータに復帰信号を出力した後に遊技制御用マイクロコンピュータに復帰信号を出力するように構成されている場合には、復帰信号による各マイクロコンピュータの復帰順序を適切に設定することができ、例えば、復帰直後にマイクロコンピュータから他のマイクロコンピュータに指令信号を送信するような場合に、容易に、受信側のマイクロコンピュータが指令信号を取りこぼさないように構成

10

20

30

40

50

することができる。

【0254】

待機状態が無限ループで構成されている場合には、待機状態を容易に形成することができる。すなわち、マイクロコンピュータにおけるプログラム構成が簡略化される。

【図面の簡単な説明】

- 【図1】 パチンコ遊技機を正面からみた正面図である。

- 【図2】 パチンコ遊技機の裏面に設けられている各基板を示す説明図である。

- 【図3】 パチンコ遊技機の機構盤を背面からみた背面図である。

- 【図4】 機構板に設置されている中間ベースユニット周りの構成を示す正面図である。

- 【図5】 球払装置を示す分解斜視図である。 10

- 【図6】 遊技盤におけるスイッチ基板の部分を示す正面図である。

- 【図7】 スイッチ基板に搭載されたクリアスイッチの構成の一例を示す構成図である。

- 【図8】 遊技制御基板（主基板）の回路構成を示すブロック図である。

- 【図9】 払出制御基板および球払装置の構成要素などの賞球に関連する構成要素を示すブロック図である。

- 【図10】 電源基板の一構成例を示すブロック図である。

- 【図11】 リセット管理回路の構成例を示すブロック図である。

- 【図12】 タイマ手段の一例であるカウンタの作用を説明するためのタイミング図である。

- 【図13】 主基板におけるCPU周りの一構成例を示すブロック図である。 20

- 【図14】 出力ポートのビット割り当ての一例を示す説明図である。

- 【図15】 出力ポートのビット割り当ての一例を示す説明図である。

- 【図16】 入力ポートのビット割り当ての一例を示す説明図である。

- 【図17】 主基板におけるCPUが実行するメイン処理を示すフローチャートである。

- 【図18】 バックアップフラグと遊技状態復旧処理を実行するか否かとの関係の一例を示す説明図である。

- 【図19】 2ms タイマ割込処理を示すフローチャートである。

- 【図20】 RAMにおけるスイッチタイマの形成例を示す説明図である。

- 【図21】 賞球処理の一例を示すフローチャートである。

- 【図22】 賞球処理の一例を示すフローチャートである。 30

- 【図23】 賞球処理の一例を示すフローチャートである。

- 【図24】 スイッチオンチェック処理を示すフローチャートである。

- 【図25】 入力判定値テーブルの構成例を示す説明図である。

- 【図26】 遊技制御手段における電力供給停止時処理を示すフローチャートである。

- 【図27】 遊技制御手段における電力供給停止時処理を示すフローチャートである。

- 【図28】 遊技状態復旧処理の一例を示すフローチャートである。

- 【図29】 遊技制御手段における電力供給停止時処理の他の例を示すフローチャートである。

- 【図30】 クリアデーターテーブルの一構成例を示す説明図である。

- 【図31】 データクリア処理を示すフローチャートである。 40

- 【図32】 払出制御基板におけるCPU周りの一構成例を示すブロック図である。

- 【図33】 払出制御基板における出力ポートのビット割り当ての一例を示す説明図である。

- 【図34】 払出制御基板における入力ポートのビット割り当ての一例を示す説明図である。

- 【図35】 払出制御基板におけるCPUが実行するメイン処理を示すフローチャートである。

- 【図36】 2ms タイマ割込処理を示すフローチャートである。

- 【図37】 払出制御手段におけるRAMの一構成例を示す説明図である。

- 【図38】 払出制御手段における電力供給停止時処理を示すフローチャートである。 50

【図39】 払出制御手段における電力供給停止時処理を示すフローチャートである。

【図40】 払出制御手段における電力供給停止時処理の他の例を示すフローチャートである。

【図41】 クリアデータテーブルの一構成例を示す説明図である。

【図42】 データクリア処理を示すフローチャートである。

【符号の説明】

3 1 遊戯制御基板（主基板）

3 7 払出制御基板

5 4 R O M

5 5 R A M

5 6 C P U

5 7 I / O ポート

1 9 0 スイッチ基板

3 7 1 払出制御用 C P U

9 1 0 電源基板

9 2 1 クリアスイッチ

9 4 0 リセット管理回路

9 7 1 カウンタ（タイマ手段）

10

【図1】

【図2】

【 図 3 】

【 図 4 】

【図5】

【図6】

【 図 7 】

【図8】

【 四 9 】

【 図 1 0 】

【 図 1 1 】

【図12】

【図13】

【図14】

| アドレス              | ビット | データ内容        | 論理 | 状態 |

|-------------------|-----|--------------|----|----|

| 出力ポート0<br>(0 0 H) | 0   | 払出制御信号 INT   | 1  | オン |

|                   | 1   | 表示制御信号 INT   | 1  | オン |

|                   | 2   | ランプ制御信号 INT  | 1  | オン |

|                   | 3   | 音声制御信号 INT   | 1  | オン |

|                   | 4   | 未使用          | —  | —  |

|                   | 5   | 未使用          | —  | —  |

|                   | 6   | 未使用          | —  | —  |

|                   | 7   | 未使用          | —  | —  |

| 出力ポート1<br>(0 1 H) | 0   | 払出制御信号 CD 0  | 1  | オン |

|                   | 1   | 払出制御信号 CD 1  | 1  | オン |

|                   | 2   | 払出制御信号 CD 2  | 1  | オン |

|                   | 3   | 払出制御信号 CD 3  | 1  | オン |

|                   | 4   | 払出制御信号 CD 4  | 1  | オン |

|                   | 5   | 払出制御信号 CD 5  | 1  | オン |

|                   | 6   | 払出制御信号 CD 6  | 1  | オン |

|                   | 7   | 払出制御信号 CD 7  | 1  | オン |

| 出力ポート2<br>(0 2 H) | 0   | 表示制御信号 CD 0  | 1  | オン |

|                   | 1   | 表示制御信号 CD 1  | 1  | オン |

|                   | 2   | 表示制御信号 CD 2  | 1  | オン |

|                   | 3   | 表示制御信号 CD 3  | 1  | オン |

|                   | 4   | 表示制御信号 CD 4  | 1  | オン |

|                   | 5   | 表示制御信号 CD 5  | 1  | オン |

|                   | 6   | 表示制御信号 CD 6  | 1  | オン |

|                   | 7   | 表示制御信号 CD 7  | 1  | オン |

| 出力ポート3<br>(0 3 H) | 0   | ランプ制御信号 CD 0 | 1  | オン |

|                   | 1   | ランプ制御信号 CD 1 | 1  | オン |

|                   | 2   | ランプ制御信号 CD 2 | 1  | オン |

|                   | 3   | ランプ制御信号 CD 3 | 1  | オン |

|                   | 4   | ランプ制御信号 CD 4 | 1  | オン |

|                   | 5   | ランプ制御信号 CD 5 | 1  | オン |

|                   | 6   | ランプ制御信号 CD 6 | 1  | オン |

|                   | 7   | ランプ制御信号 CD 7 | 1  | オン |

【図15】

| アドレス              | ビット | データ内容            | 論理 | 状態 |

|-------------------|-----|------------------|----|----|

| 出力ポート4<br>(0 4 H) | 0   | 音声制御信号 CD 0      | 1  | オン |

|                   | 1   | 音声制御信号 CD 1      | 1  | オン |

|                   | 2   | 音声制御信号 CD 2      | 1  | オン |

|                   | 3   | 音声制御信号 CD 3      | 1  | オン |

|                   | 4   | 音声制御信号 CD 4      | 1  | オン |

|                   | 5   | 音声制御信号 CD 5      | 1  | オン |

|                   | 6   | 音声制御信号 CD 6      | 1  | オン |

|                   | 7   | 音声制御信号 CD 7      | 1  | オン |

| 出力ポート5<br>(0 5 H) | 0   | 始動口              | 1  | オン |

|                   | 1   | 図柄確定回数 1         | 1  | オン |

|                   | 2   | 大当たり 1           | 1  | オン |

|                   | 3   | 大当たり 2           | 1  | オン |

|                   | 4   | 確率変動             | 1  | オン |

|                   | 5   | 図柄確定回数 2         | 1  | オン |

|                   | 6   | 役物回数             | 1  | オン |

|                   | 7   | 賞球               | 1  | オン |

| 出力ポート6<br>(0 6 H) | 0   | ソレノイド (大入賞口扉)    | 1  | オン |

|                   | 1   | ソレノイド (大入賞口内誘導板) | 1  | オン |

|                   | 2   | ソレノイド (普通電動役物)   | 1  | オン |

|                   | 3   | 未使用              | —  | —  |

|                   | 4   | 未使用              | —  | —  |

|                   | 5   | 未使用              | —  | —  |

|                   | 6   | 未使用              | —  | —  |

|                   | 7   | 未使用              | —  | —  |

【図16】

| アドレス            | ビット | データ内容                | 論理 | 状態  |

|-----------------|-----|----------------------|----|-----|

| 入力ポート0<br>(0EH) | 0   | 左袖入賞口スイッチ (24a)      | 1  | オン  |

|                 | 1   | 右袖入賞口スイッチ (24b)      | 1  | オン  |

|                 | 2   | 左落とし入賞口スイッチ (19a)    | 1  | オン  |

|                 | 3   | 右落とし入賞口スイッチ (19b)    | 1  | オン  |

|                 | 4   | 始動口スイッチ              | 1  | オン  |

|                 | 5   | カウントスイッチ             | 1  | オン  |

|                 | 6   | 特定領域スイッチ (Vカウントスイッチ) | 1  | オン  |

|                 | 7   | ゲートスイッチ              | 1  | オン  |

| 入力ポート1<br>(0FH) | 0   | 賞球カウントスイッチ           | 1  | オン  |

|                 | 1   | 満タンスイッチ              | 1  | オン  |

|                 | 2   | 球切れスイッチ              | 1  | オン  |

|                 | 3   | カウントスイッチ短絡           | 1  | オン  |

|                 | 4   | クリアスイッチ              | 1  | オン  |

|                 | 5   | 未使用                  | -  | 0固定 |

|                 | 6   | 未使用                  | -  | 0固定 |

|                 | 7   | 未使用                  | -  | 0固定 |

【図17】

【図18】

| バックアップフラグの値 | 55H | 55H以外 |

|-------------|-----|-------|

| 正常          | 復旧  | 初期化   |

| 異常          | 初期化 | 初期化   |

【図19】

【図20】

【図21】

【図22】

【図23】

【図24】

【図25】

| 種類               | 判定値 |

|------------------|-----|

| スイッチオン判定値        | 2   |

| 満タンスイッチオン判定値     | 50  |

| 球切れスイッチオン判定値     | 250 |

| 球切れスイッチオフ判定値     | 30  |

| カウントスイッチ断線エラー判定値 | 250 |

| カウントスイッチ短絡エラー判定値 | 1   |

【図26】

【図27】

【図28】

【図30】

| (遮技制御手段のクリアデーターブル) |  |

|--------------------|--|

| 処理数データ(7)          |  |

| アドレス(00H)          |  |

| クリアデータ(00H)        |  |

| アドレス(01H)          |  |

| クリアデータ(00H)        |  |

| アドレス(02H)          |  |

| クリアデータ(00H)        |  |

| アドレス(03H)          |  |

| クリアデータ(00H)        |  |

| アドレス(04H)          |  |

| クリアデータ(00H)        |  |

| アドレス(05H)          |  |

| クリアデータ(00H)        |  |

| アドレス(06H)          |  |

| クリアデータ(00H)        |  |

【図29】

【図31】

【図32】

【図33】

| アドレス            | ビット | データ内容     | 論理 | 状態 |

|-----------------|-----|-----------|----|----|

| 出力ポートC<br>(00H) | 0   | 払出モータφ4   | 1  | オン |

|                 | 1   | 払出モータφ3   | 1  | オン |

|                 | 2   | 払出モータφ2   | 1  | オン |

|                 | 3   | 払出モータφ1   | 1  | オン |

|                 | 4   | 発射制御信号    | 1  | オン |

|                 | 5   | 球貸し       | 1  | オン |

|                 | 6   | 未使用       | —  | —  |

|                 | 7   | 未使用       | —  | —  |

| 出力ポートD<br>(01H) | 0   | エラー表示LEDa | 1  | オン |

|                 | 1   | エラー表示LEDb | 1  | オン |

|                 | 2   | エラー表示LEDc | 1  | オン |

|                 | 3   | エラー表示LEDd | 1  | オン |

|                 | 4   | エラー表示LEDe | 1  | オン |

|                 | 5   | エラー表示LEDf | 1  | オン |

|                 | 6   | エラー表示LEDg | 1  | オン |

|                 | 7   | 未使用       | —  | —  |

| 出力ポートE<br>(02H) | 0   | 振分ソレノイド   | 1  | オン |

|                 | 1   | EXS       | 1  | オン |

|                 | 2   | PRDY      | 1  | オン |

|                 | 3   | 未使用       | —  | —  |

|                 | 4   | 未使用       | —  | —  |

|                 | 5   | 未使用       | —  | —  |

|                 | 6   | 未使用       | —  | —  |

|                 | 7   | 未使用       | —  | —  |

【図34】

| アドレス            | ビット | データ内容       | 論理 | 状態  |

|-----------------|-----|-------------|----|-----|

| 入力ポートA<br>(06H) | 0   | 払出制御信号CD0   | 1  | オン  |

|                 | 1   | 払出制御信号CD1   | 1  | オン  |

|                 | 2   | 払出制御信号CD2   | 1  | オン  |

|                 | 3   | 払出制御信号CD3   | 1  | オン  |

|                 | 4   | 払出制御信号CD4   | 1  | オン  |

|                 | 5   | 払出制御信号CD5   | 1  | オン  |

|                 | 6   | 払出制御信号CD6   | 1  | オン  |

|                 | 7   | 払出制御信号CD7   | 1  | オン  |

| 入力ポートB<br>(07H) | 0   | 賞球カウントスイッチ  | 1  | オン  |

|                 | 1   | 球貸しカウントスイッチ | 1  | オン  |

|                 | 2   | モータ位置センサ    | 0  | オン  |

|                 | 3   | BRDY        | 0  | オン  |

|                 | 4   | BRQ         | 0  | オン  |

|                 | 5   | VL          | 0  | オン  |

|                 | 6   | クリアスイッチ     | 1  | オン  |

|                 | 7   | 未使用         | —  | 0固定 |

【図35】

【図36】

【図37】

【図38】

【図39】

【図40】

【図41】

(抽出制御手段のクリアデータテーブル)

|              |

|--------------|

| 処理数データ (3)   |

| アドレス (00H)   |

| クリアデータ (00H) |

| アドレス (01H)   |

| クリアデータ (00H) |

| アドレス (02H)   |

| クリアデータ (00H) |

【図42】

---

フロントページの続き

(72)発明者 近藤 武宏

群馬県桐生市境野町6丁目460番地 株式会社三共内

(72)発明者 石川 貴之

群馬県桐生市境野町6丁目460番地 株式会社三共内

審査官 澤田 真治

(56)参考文献 特開平10-003331 (JP, A)

特開平08-229208 (JP, A)

特開平06-233867 (JP, A)

特開昭60-058186 (JP, A)

特開昭62-143153 (JP, A)

特開2000-140336 (JP, A)

実開平04-067733 (JP, U)

特許第2582489 (JP, B2)

(58)調査した分野(Int.Cl., DB名)

A63F 7/02