(19)日本国特許庁(JP)

**(12)特許公報(B2)**

(11)特許番号

**特許第7325314号**

**(P7325314)**

(45)発行日 令和5年8月14日(2023.8.14)

(24)登録日 令和5年8月3日(2023.8.3)

(51)国際特許分類

H 03 K 17/08 (2006.01)

H 02 M 1/00 (2007.01)

F I

H 03 K 17/08

H 02 M 1/00

C

E

請求項の数 7 (全15頁)

(21)出願番号 特願2019-224421(P2019-224421)

(22)出願日 令和1年12月12日(2019.12.12)

(65)公開番号 特開2021-93676(P2021-93676A)

(43)公開日 令和3年6月17日(2021.6.17)

審査請求日 令和4年3月16日(2022.3.16)

(73)特許権者 000006013

三菱電機株式会社

東京都千代田区丸の内二丁目7番3号

(74)代理人 110001195

弁理士法人深見特許事務所

羽生 洋

東京都千代田区丸の内二丁目7番3号

三菱電機株式会社内

(72)発明者 山本 晃央

東京都千代田区丸の内二丁目7番3号

三菱電機株式会社内

審査官 及川 尚人

最終頁に続く

(54)【発明の名称】 半導体装置

**(57)【特許請求の範囲】****【請求項1】**

半導体装置であって、

半導体スイッチング素子の正電極及び負電極の間に接続された検出回路を備え、

前記検出回路は、

前記正電極及び前記負電極の間に第1のノードを介して直列接続された、電流源、及び、第1の電気抵抗値を有する第1の抵抗素子を含み、

前記電流源は、前記負電極に対する前記正電極が高くなるに従って、飽和した一定値に向けて出力電流が増加する様に動作し、

前記半導体装置は、

第2のノードに入力された直流電圧と、前記第1のノードの電圧との比較結果を出力する電圧比較器を更に備え、

前記直流電圧及び前記第1の電気抵抗値は、前記正電極及び前記負電極の間の電極間電圧が予め定められた判定電圧よりも高いときに、前記第1のノードの電圧が前記直流電圧よりも高くなるように定められ、

前記検出回路及び前記電圧比較器は、同じ集積回路上に搭載される、半導体装置。

**【請求項2】**

前記検出回路は、

前記正電極及び前記第1のノードの間に前記電流源と直列に接続された第2の抵抗素子を更に含み、

10

20

前記第2の抵抗素子は、第2の電気抵抗値を有し、

前記第1及び第2の電気抵抗値並びに前記直流電圧は、前記電極間電圧が前記判定電圧よりも高いときに、前記第1のノードの電圧が前記直流電圧よりも高くなるように定められる、請求項1記載の半導体装置。

**【請求項3】**

前記電流源は、ダイオード接続された電界効果トランジスタを有する、請求項1又は2に記載の半導体装置。

**【請求項4】**

前記電流源は、カレントミラー回路を構成する複数の電界効果トランジスタを有する、

請求項1又は2に記載の半導体装置。

10

**【請求項5】**

前記半導体スイッチング素子の制御電極を駆動する駆動回路を更に備え、

前記駆動回路は、前記検出回路及び前記電圧比較器と同一の前記集積回路上に搭載される、

請求項1～4のいずれか1項に記載の半導体装置。

**【請求項6】**

前記半導体スイッチング素子のオンオフを制御するための第1の制御信号と、前記電圧比較器の出力信号とを受けて、前記駆動回路に対して第2の制御信号を出力する保護回路を更に備え、

前記第2の制御信号は、前記第1の制御信号が前記半導体スイッチング素子のオフを指示する第1のレベルからオンを指示する第2のレベルに変化しても、前記電極間電圧が前記判定電圧よりも低下しないときには、前記半導体スイッチング素子のオフを前記駆動回路に指示するように生成される、請求項5記載の半導体装置。

20

**【請求項7】**

前記保護回路は、前記駆動回路と同一の前記集積回路上に搭載される、請求項6記載の半導体装置。

**【発明の詳細な説明】**

**【技術分野】**

**【0001】**

本発明は半導体装置に関する。

**【背景技術】**

30

**【0002】**

インバータ等において、2個の半導体スイッチング素子（以下、単に「スイッチング素子」と称する）が、高電位ノード及び低電位ノードの間に中間電位ノードを介して接続される、所謂、アーム構成が用いられる。以下では、アーム構成において、高電位側に接続されたスイッチング素子をハイサイドのスイッチング素子とも称するとともに、低電位側に接続されたスイッチング素子をローサイドのスイッチング素子とも称する。

**【0003】**

特開2019-4535号公報（以下、特許文献1）には、上記アーム構成において、ハイサイドのスイッチング素子の状態情報の検出回路を有する半導体装置が記載されている。特許文献1では、IGBT（Insulated Gate Bipolar Transistor）で構成されたハイサイド及びローサイドのスイッチング素子の駆動回路が搭載された半導体チップ（IC：Integrated Circuit）の外部に設けられた回路素子を含む、検出回路及び信号伝達回路によって、ハイサイドのスイッチング素子の状態情報をモニタする構成が示される。

40

**【0004】**

特許文献1では、検出回路は、ハイサイドのスイッチング素子の状態情報に応じた電圧を出力する。更に、信号伝達回路は、検出回路の出力に応じてオンオフする半導体チップ上に搭載された信号スイッチング素子と、半導体チップの外部で当該信号スイッチング素子に対して直列に接続されるダイオードとを含む。これにより、ローサイド及びハイサイドの間で求められる絶縁をダイオードによって確保した上で、検出回路の出力をモニタすることが可能となる。

50

【先行技術文献】

【特許文献】

【0005】

【文献】特開2019-4535号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、特許文献1の構成では、ICの外部に接続されたダイオードによって、ハイサイド及びローサイドの間に求められる絶縁が確保されるため、ICの搭載素子と、IC外の素子とによって、スイッチング素子の状態情報がモニタされる。この結果、部品点数の増加、及び、回路規模の増大が懸念される。

10

【0007】

一方で、スイッチング素子では、過電流が生じると不飽和状態が発生して、オン状態であるのに、正電極及び負電極間の電圧が上昇する電圧異常が発生することが知られている。このため、スイッチング素子の継続的な過電流状態を回避するために、上記電圧異常の検出が有効であるが、この際には、特許文献1の様な回路構成の複雑化を避けて、簡易な回路構成による異常検出機能の実現が望まれる。

【0008】

本発明はこのような問題点を解決するためになされたものであって、本発明の目的は、絶縁を確保した上で、スイッチング素子のオン時における正電極及び負電極間の電圧異常検出が可能な半導体装置の簡易な構成を提供することである。

20

【課題を解決するための手段】

【0009】

本発明のある局面では、半導体装置であって、半導体スイッチング素子の正電極及び負電極の間に接続された検出回路と、電圧比較器とを備える。前記検出回路は、電流源、及び、第1の電気抵抗値を有する第1の抵抗素子を含む。電流源及び第1の抵抗素子は、正電極及び前記負電極の間に、第1のノードを介して直列接続される。電圧比較器は、第2のノードに入力された直流電圧と、第1のノードの電圧との比較結果を出力する。直流電圧及び前記第1の電気抵抗値は、前記正電極及び前記負電極の間の電極間電圧が予め定められた判定電圧よりも高いときに、前記第1のノードの電圧が前記直流電圧よりも高くなるように定められる。検出回路及び前記電圧比較器は、同じ集積回路上に搭載される。

30

【発明の効果】

【0010】

本発明によれば、電流源及び第1の抵抗素子によって検出回路を構成することにより、検出回路及び電圧比較器を同じ集積回路上に搭載できるので、検出回路内の電流源によって絶縁を確保した上で、半導体スイッチング素子のオン時における正電極及び負電極間の電圧異常を簡易な回路構成で検出可能な半導体装置を提供することができる。

【図面の簡単な説明】

【0011】

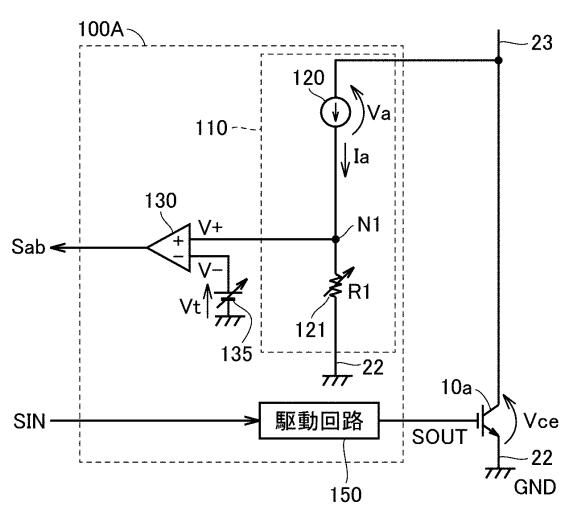

【図1】実施の形態1に係る半導体装置の構成を説明する第1の回路図である。

40

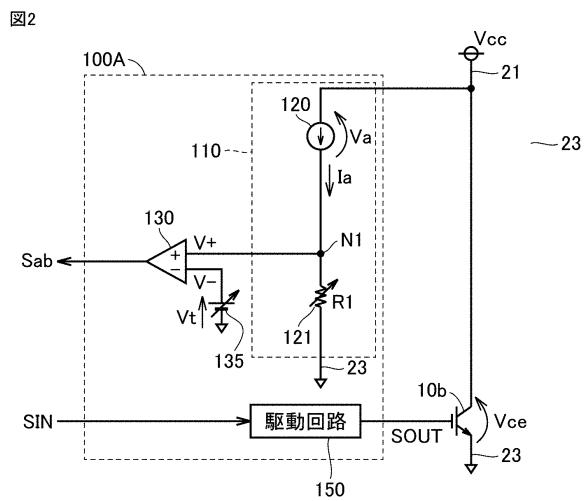

【図2】実施の形態1に係る半導体装置の構成を説明する第2の回路図である。

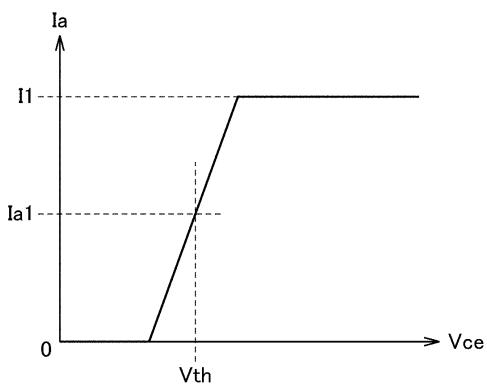

【図3】図1に示された検出回路の電圧電流特性を示す概念図である。

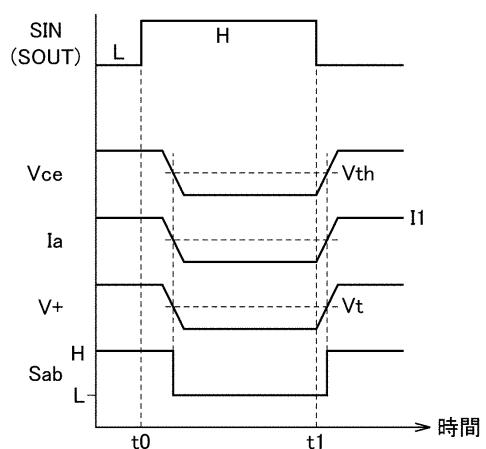

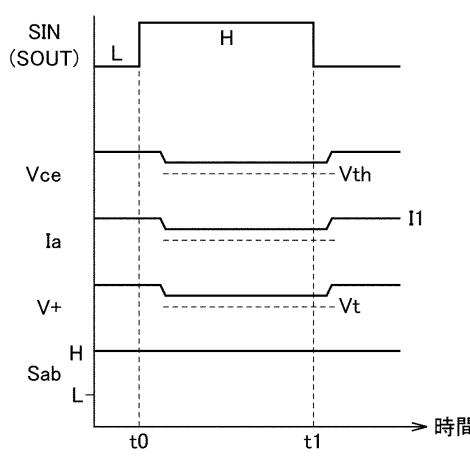

【図4】実施の形態1に係る半導体装置の動作例を説明する第1の波形図である。

【図5】実施の形態1に係る半導体装置の動作例を説明する第2の波形図である。

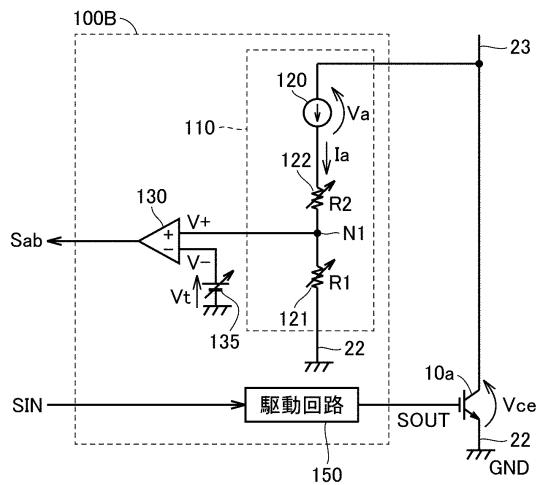

【図6】実施の形態2に係る半導体装置の構成を説明する第1の回路図である。

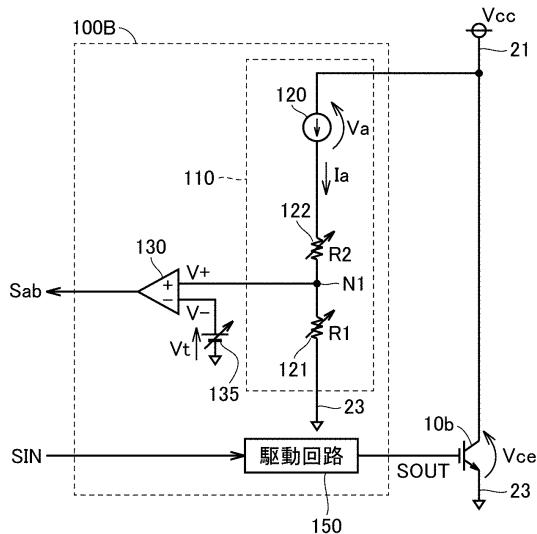

【図7】実施の形態2に係る半導体装置の構成を説明する第2の回路図である。

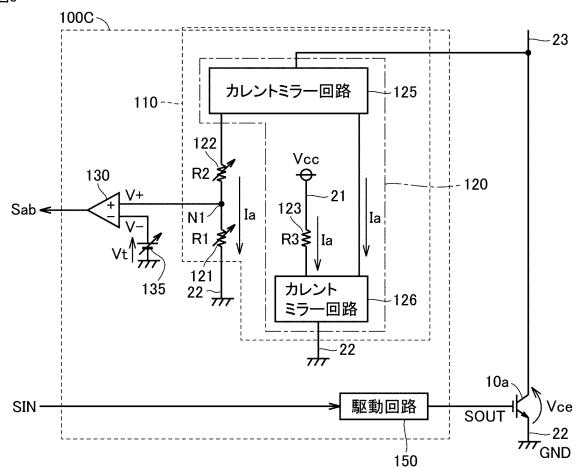

【図8】実施の形態3に係る半導体装置の構成を説明する回路図である。

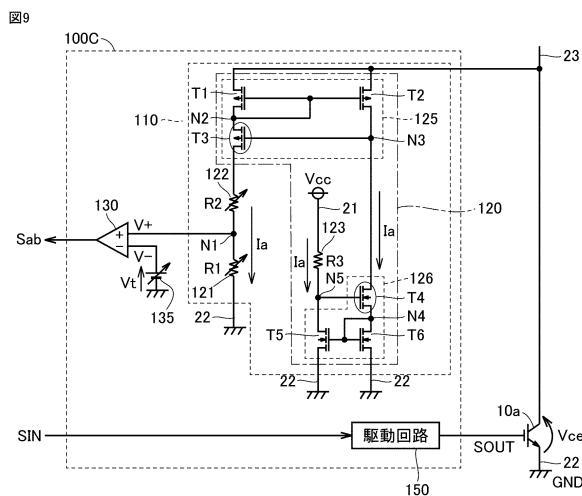

【図9】図8に示されたカレントミラー回路の構成例を説明する回路図である。

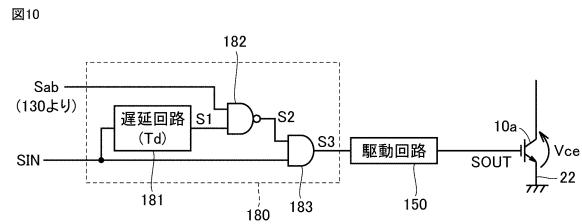

【図10】実施の形態4に係る半導体装置が備える保護回路の構成例を説明する回路図である。

50

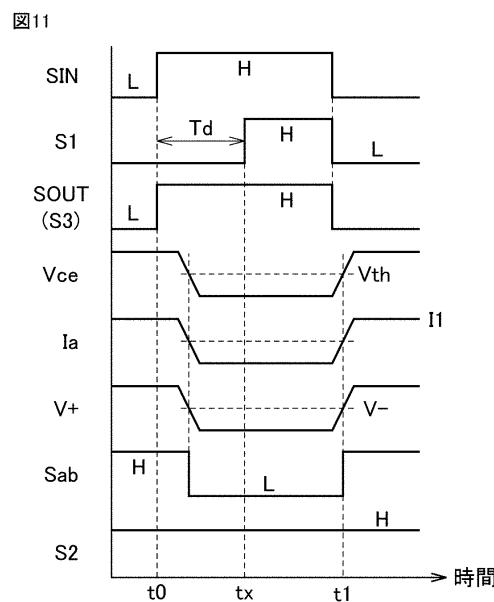

【図11】実施の形態4に係る半導体装置の動作例を説明する第1の波形図である。

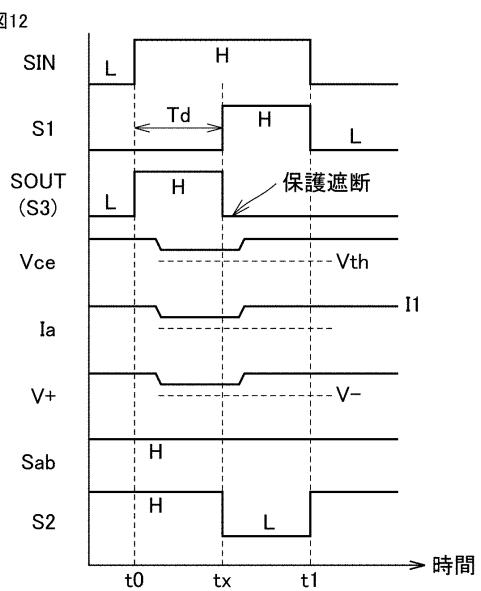

【図12】実施の形態4に係る半導体装置の動作例を説明する第2の波形図である。

【発明を実施するための形態】

【0012】

以下に、本発明の実施の形態について、図面を参照して詳細に説明する。なお、以下では、図中の同一又は相当部分には同一符号を付して、その説明は原則的に繰返さないものとする。

【0013】

実施の形態1.

図1及び図2は、実施の形態1に係る半導体装置の構成を説明する回路図である。

10

【0014】

図1を参照して、半導体装置100Aは、スイッチング素子10aの駆動ICの機能を有する。半導体装置100Aによってオンオフされるスイッチング素子10aは、代表的にはIGBTで構成されて、中間電位ノード23と、低電位GNDが供給される低電位ノード22との間に接続される。即ち、スイッチング素子10aは、ローサイドのスイッチング素子に相当する。

【0015】

図2を参照して、半導体装置100Aは、スイッチング素子10bの駆動ICの機能を有する。半導体装置100Aによってオンオフされるスイッチング素子10bは、代表的にはIGBTで構成されて、高電位Vccが供給される高電位ノード21と、図1と共にの中間電位ノード23との間に接続される。即ち、スイッチング素子10bは、ハイサイドのスイッチング素子に相当する。

20

【0016】

図1及び図2から理解されるように、ローサイドのスイッチング素子10aに対応して設けられる半導体装置100A(図1)と、ハイサイドのスイッチング素子10bに対応して設けられる半導体装置100A(図2)との構成は同様であるので、まず、ローサイドの半導体装置100Aの構成について詳細に説明する。

【0017】

再び図1を参照して、半導体装置100Aは、スイッチング素子10aの駆動回路150と、スイッチング素子10aのコレクタ-エミッタ間電圧(Vce)の検出回路110と、電圧比較器130とを備える。Vceは、スイッチング素子の正電極及び負電極間の電圧に対応する。

30

【0018】

駆動回路150は、スイッチング素子10aの制御信号SINを受けて、ゲート信号SOUTをスイッチング素子10aのゲート(制御電極)に出力する。例えば、2値信号である制御信号SINのハイレベル(以下、「Hレベル」と表記する)期間には、ゲート信号SOUTをHレベルに設定することにより、スイッチング素子10aがオンされる。ゲート信号SOUTのHレベル電圧は、スイッチング素子10aの負電極(エミッタ)に対して、スイッチング素子10aを構成するIGBTの閾値電圧よりも高くなるように設定される。

40

【0019】

一方で、制御信号SINのローレベル(以下、「Lレベル」と表記する)期間には、ゲート信号SOUTをLレベルに設定することにより、スイッチング素子10aがオフされる。例えば、ゲート信号SOUTのLレベル電圧は、スイッチング素子10aに負電極(エミッタ)、即ち、低電位GNDと同等に設定される。

【0020】

検出回路110は、直列接続された、電流源120及び抵抗素子121を有する。抵抗素子121は、可変抵抗素子で構成することが好ましい。例えば、デジタルトリミングによって電気抵抗値R1が調整できるように、抵抗素子121を構成することができる。

【0021】

50

電流源 120 及び抵抗素子 121 は、中間電位ノード 23 及び低電位ノード 22 の間、即ち、スイッチング素子 10a の正電極（コレクタ）及び負電極（エミッタ）の間に、ノード N1 を介して直列接続される。

#### 【0022】

電圧比較器 130 は、+ 側の入力端子の電圧  $V_+$  と、- 側の入力端子の電圧  $V_-$  との比較結果に応じて、検出信号  $S_{ab}$  を出力する。検出信号  $S_{ab}$  は、 $V_+ > V_-$  のとき H レベルに設定される一方で、 $V_+ < V_-$  のとき L レベルに設定される。

#### 【0023】

電圧比較器 130 の + 側の入力端子は、検出回路 110 のノード N1 と接続される。即ち、電圧  $V_+$  は、ノード N1 の電圧に相当する。一方で、電圧比較器 130 の - 側の入力端子と、低電位ノード 22（スイッチング素子 10a のエミッタ）との間には、直流電圧  $V_t$  を出力する電圧源 135 が電気的に接続される。電圧源 135 は、直流電圧  $V_t$  を可変に調整できるように構成されることが好ましい。ノード N1 は「第 1 のノード」の一実施例に対応し、電圧比較器 130 の - 側の出力端子は「第 2 のノード」の一実施例に対応する。又、スイッチング素子の  $V_{ce}$  は「電極間電圧」に対応し、検出回路 110 の抵抗素子 121 は「第 1 の抵抗素子」に対応する。

10

#### 【0024】

電流源 120 は、例えば、半導体装置 100A を構成する IC 上に形成された高耐圧を有するトランジスタをダイオード接続することによって構成することができる。図 1 の構成例では、電流源 120 は、中間電位ノード 23（スイッチング素子 10a のコレクタ）とノード N1 との間に接続される。抵抗素子 121 は、ノード N1 及び低電位ノード（スイッチング素子 10a のエミッタ）との間に接続される。抵抗素子 121 についても、半導体装置 100A を構成する IC 上に形成される。

20

#### 【0025】

電圧比較器 130 は、任意の回路構成を適用することが可能である。例えば、半導体装置 100A を構成する IC 上に形成された、トランジスタ及び抵抗素子等を用いて、電圧比較器 130 を構成することにより、電圧比較器 130 は、検出回路 110 と同様に、半導体装置 100A を構成する IC 上に搭載される。

#### 【0026】

一方で、電圧源 135 は半導体装置 100A (IC) の外部に配置されてもよい。この場合には、電圧比較器 130 の - 側の入力端子と電気的に接続された端子（図示せず）に対して、半導体装置 100A の外部から直流電圧  $V_t$  が供給される。或いは、電圧源 135 として、半導体装置 100A 上のトランジスタ等を用いて、高電位  $V_{cc}$  を降圧した一定電圧を生成する回路を構成することも可能である。

30

#### 【0027】

上述の様に、オン状態のスイッチング素子 (IGBT) が過電流状態に陥ると、オン状態であるにも関わらず  $V_{ce}$  が十分に下がりきらない不飽和状態となることが知られている。本実施の形態に係る半導体装置では、検出回路 110 及び電圧比較器 130 は、スイッチング素子 10a (IGBT) の不飽和状態を検出するように構成される。具体的には、制御信号 SIN の H レベル期間において、 $V_{ce}$  が判定電圧  $V_{th}$  よりも高いときに、電圧比較器 130 が検出信号  $S_{ab}$  を H レベルに設定すると、不飽和状態を検出することができる。判定電圧  $V_{th}$  は、スイッチング素子 10a の特性に照らして、不飽和状態の発生時における  $V_{ce}$  に対して、マージン分だけ低い電圧に設定される。一般的には、判定電圧  $V_{th}$  は、10 (V) 未満のレベルである。

40

#### 【0028】

図 3 には、検出回路 110 の電圧電流特性が示される。

#### 【0029】

図 3 を参照して、電流源 120 の出力電流  $I_a$  について、スイッチング素子 10a の  $V_{ce}$  が低い領域では、 $I_a = 0$  である一方で、 $V_{ce}$  が高い領域では、飽和した一定値 ( $I_a = I_1$ ) を示す。上述した判定電圧  $V_{th}$  を含む  $V_{ce}$  領域では、出力電流  $I_a$  は、

50

電気抵抗値  $R_1$  (抵抗素子 121) の逆数に従った傾きに従い、 $V_{ce}$  に比例して変化する。

#### 【0030】

ここで、 $V_{ce} = V_{th}$  であるときの電流源 120 の電圧及び電流を  $V_{a1}$  及び  $I_{a1}$  とすると、判定電圧  $V_{th}$  と、電圧  $V_{a1}$  及び電流  $I_{a1}$ との間には、下記の式(1)に示す関係が成立する。

#### 【0031】

$$V_{th} = V_{a1} + R_1 \times I_{a1} \quad \dots (1)$$

更に、直流電圧  $V_t$  について、式(1)での電流  $I_{a1}$  を用いて、下記の式(2)となるように調整すると、 $V_{ce} > V_{th}$  のときに、電圧比較器 130 の出力(検出信号  $S_{ab}$ )を H レベルとすることができます。

10

#### 【0032】

$$V_t = R_1 \times I_{a1} \quad \dots (2)$$

式(1), (2)より、判定電圧  $V_{th}$  について、下記の式(3)が成立する。

#### 【0033】

$$V_{th} = V_{a1} + V_t \quad \dots (3)$$

式(3)から、判定電圧  $V_{th}$  は、抵抗素子 121 の電気抵抗値  $R_1$ 、及び、電圧源 135 からの直流電圧  $V_t$  によって調整することができる。即ち、電圧異常の監視対象となるスイッチング素子 10a の特性に合わせて、判定電圧  $V_{th}$  を調整することが可能である。

20

#### 【0034】

図 4 及び図 5 には、実施の形態 1 に係る半導体装置の動作例が示される。図 4 には、スイッチング素子 10a の正常動作時の波形例が示される。

#### 【0035】

図 4 を参照して、時刻  $t_0$  以前では、制御信号  $S_{IN}$  が L レベルに設定されているため、ローサイドのスイッチング素子 10a はオフ状態である。このとき、通常はハイサイドのスイッチング素子 10b がオンしているので、 $V_{ce} = V_{cc}$  であるため、 $V_{ce} > V_{th}$  である。検出回路 110 では、図 3 で説明した様に、 $I_a = I_1$  である。又、電圧比較器 130 では、 $V_{ce} > V_{th}$  に対応して、 $V_+ > V_-$  となるので、スイッチング素子 10a のオフ時には、検出信号  $S_{ab}$  は H レベルである。

30

#### 【0036】

時刻  $t_0$ において、制御信号  $S_{IN}$  が L レベルから H レベルに変化すると、スイッチング素子 10a がターンオンする。具体的には、駆動回路 150 が出力するゲート信号  $S_{OUT}$  が H レベルに変化するのに応じて、スイッチング素子 10a のゲート電圧が上昇する。これにより、スイッチング素子 10a では、 $V_{ce}$  が低下するとともにコレクタ - エミッタ間電流が流れ始める。

30

#### 【0037】

スイッチング素子 10a の正常なオン状態では、不飽和状態が発生することなく、 $V_{ce}$  はゼロ近傍の電圧まで低下して、正常なコレクタ - エミッタ間電流が発生する。即ち、 $V_{ce}$  は判定電圧  $V_{th}$  よりも低下する。

40

#### 【0038】

このような  $V_{ce}$  の低下に応じて、検出回路 110 では、電流源 120 の出力電流  $I_a = 0$  となり、電圧比較器 130 では、 $V_+ < V_-$  となる。この結果、検出信号  $S_{ab}$  は L レベルに変化する。

#### 【0039】

時刻  $t_1$ において、制御信号  $S_{IN}$  が H レベルから L レベルに変化すると、スイッチング素子 10a はターンオフする。これにより、 $V_{ce}$ 、 $I_a$ 、 $V_+$ 、及び、検出信号  $S_{ab}$  は、時刻  $t_0$  以前の状態に戻る。このように、スイッチング素子 10a の正常なオン状態では、制御信号  $S_{IN}$  が H レベルに変化すると、検出信号  $S_{ab}$  が L レベルとなる。

#### 【0040】

50

一方で、図 5 には、スイッチング素子 10 a に不飽和状態が発生したときの動作例が示される。図 5 を参照して、図 4 と同様に、時刻  $t_0$  において、制御信号 S I N が L レベルから H レベルに変化することにより、スイッチング素子 10 a がターンオンする。

#### 【0041】

しかしながら、図 5 では、スイッチング素子 10 a において、コレクタ - エミッタ電流が過大（過電流状態）であることによる不飽和状態が発生するため、 $V_{c e}$  が図 4 のように低下しない異常が生じる。このような電圧異常により、 $V_{c e} > V_{t h}$  であるため、図 3 の特性に従った出力電流  $I_a$  に応じて、 $V_+ > V_-$  が維持される。この結果、図 4 とは異なり、制御信号 S I N が H レベルに変化しても、検出信号 S a b が H レベルに維持される。

10

#### 【0042】

従って、実施の形態 1 に係る半導体装置 100 A では、検出回路 110 及び電圧比較器 130 により発生される検出信号 S a b に基づき、スイッチング素子 10 a のオン期間における不飽和状態の発生を検出することが可能である。

#### 【0043】

又、検出回路 110 は、スイッチング素子 10 a のオフ時において、高電位  $V_{c c}$  が伝達された状態の中間電位ノード 23 と、低電位ノード 22 との間の絶縁を、電流源 120（例えば、ダイオード接続された高耐圧の電界効果トランジスタ）によって確保することができる。即ち、駆動回路 150 を含む半導体装置 100 A を構成する I C 上に形成された素子（例えば、上記の高耐圧の電界効果トランジスタ）を用いて、特許文献 1 の様な I C の外付け素子を用いることなく、検出回路 110 の絶縁を確保することが可能となる。

20

#### 【0044】

再び図 2 を参照して、半導体装置 100 A は、図 1 と同様の回路構成により、ハイサイドのスイッチング素子 10 b に適用することが可能である。図 2 の回路構成は、図 1 での中間電位ノード 23 を高電位ノード 21 とし、低電位ノード 22 を中間電位ノード 23 としたものに相当する。

#### 【0045】

図 2 において、検出回路 110 は、高電位ノード 21 及び中間電位ノード 23 の間、即ち、スイッチング素子 10 b のコレクタ及びエミッタ間に接続されることで、ハイサイドのスイッチング素子 10 b の  $V_{c e}$  を検出することができる。即ち、電流源 120 の出力電流  $I_a$  は、スイッチング素子 10 b の  $V_{c e}$  に対して、図 3 と同様の特性を有する。

30

#### 【0046】

電圧比較器 130 において、+ 側の入力端子は、図 1 と同様に検出回路 110 のノード N1 と接続される。一方で、電圧源 135 は、中間電位ノード 23 と、電圧比較器 130 の - 側の入力端子との間に電気的に接続される。上述の様に、電圧源 135 は、半導体装置 100 A の外部から直流電圧  $V_t$  を入力することも可能である。

#### 【0047】

図 2 に示された半導体装置 100 A についても、スイッチング素子 10 b のオンオフ制御のための制御信号 S I N の変化に対して、図 4 及び図 5 で説明したように動作する。即ち、半導体装置 100 A は、ローサイドのスイッチング素子 10 a 及びハイサイドのスイッチング素子 10 b の両方に対して、同じ回路構成で適用することが可能である。

40

#### 【0048】

実施の形態 2 。

実施の形態 2 では不飽和状態を検出するための判定電圧を容易に調整するための回路構成を説明する。

#### 【0049】

図 6 は、実施の形態 2 に係る半導体装置の構成を説明する第 1 の回路図である。

#### 【0050】

図 6 を参照して、実施の形態 2 に係る半導体装置 100 B は、実施の形態 1 に係る半導体装置 100 A と比較して、検出回路 110 の構成が異なる。具体的には、実施の形態 2

50

では、検出回路 110 は、図 1 の構成と比較して、中間電位ノード 23 及びノード N1 の間に、電流源 120 と直列接続される抵抗素子 122 を更に有する。抵抗素子 122 についても、トリミング等によって電気抵抗値 R2 を可変調整できることが好ましい。半導体装置 100B のその他の部分の構成は、半導体装置 100A と同様である。抵抗素子 122 は「第 2 の抵抗素子」に対応する。

#### 【0051】

実施の形態 2 の検出回路 110 では、抵抗素子 122（電気抵抗値 R2）の追加により、上述の式（1）は、下記の式（4）に変形される。

#### 【0052】

$$V_{th} = V_{a1} + (R_1 + R_2) \times I_{a1} \quad \dots (4)$$

又、実施の形態 2 においても、 $V_{ce} = V_{th}$  であるときの電流源 120 の電流  $I_{a1}$  を用いて、式（2）に示した様に、 $V_{th} = R_1 \times I_{a1}$  とすると、判定電圧  $V_{th}$  について、下記の式（5）が成立する。

#### 【0053】

$$V_{th} = V_{a1} + V_t \cdot (R_1 + R_2) / R_1 \quad \dots (5)$$

実施の形態 2 では、式（5）で示された判定電圧  $V_{th}$  に対して、 $V_{ce} > V_{th}$  のときには  $Sab = H$  レベルとなる一方で、 $V_{ce} < V_{th}$  のときには、 $Sab = L$  レベルとなる。式（5）から理解されるように、実施の形態 2 では、電圧源 135 の直流電圧  $V_t$ 、並びに、抵抗素子 121 及び 122 の電気抵抗値  $R_1$  及び  $R_2$  によって、判定電圧  $V_{th}$  を調整することが可能である。

#### 【0054】

実施の形態 2 に係る半導体装置 100B の動作は、判定電圧  $V_{th}$  の設定以外は、半導体装置 100A と同様である。このため、実施の形態 2 に係る半導体装置 100B では、実施の形態 1 に係る半導体装置 100A の効果に加えて、判定電圧  $V_{th}$  の調整が容易となる。

#### 【0055】

図 7 には、実施の形態 2 に係る半導体装置 100B をハイサイドのスイッチング素子 10b に適用したときの回路構成が示される。

#### 【0056】

図 7 を参照して、実施の形態 2 に係る半導体装置 100B についても、図 6 と同様の回路構成により、ハイサイドのスイッチング素子 10b に適用することが可能である。図 7 の回路構成は、図 6 での中間電位ノード 23 を高電位ノード 21 とし、低電位ノード 22 を中間電位ノード 23 としたものに相当する。

#### 【0057】

図 7においては、ハイサイドのスイッチング素子 10b の  $V_{ce}$  と、判定電圧  $V_{th}$ との比較によって、スイッチング素子 10b の不飽和状態を検出することが可能である。判定電圧  $V_{th}$  は、図 6 と同様に、電圧源 135 の直流電圧  $V_t$ 、並びに、抵抗素子 121 及び 122 の電気抵抗値  $R_1$  及び  $R_2$  によって調整することができる。

#### 【0058】

即ち、半導体装置 100B についても、ローサイドのスイッチング素子 10a 及びハイサイドのスイッチング素子 10b の両方に対して、同じ回路構成で適用することが可能である。尚、実施の形態 2 では、図 6 及び図 7 において、直列接続された電流源 120 及び抵抗素子 122 の接続順を入れ替えることも可能である。

#### 【0059】

実施の形態 3。

実施の形態 3 では、検出回路 110 の電流源 120 の好ましい構成例を説明する。

#### 【0060】

図 8 は、実施の形態 3 に係る半導体装置の構成を説明する回路図である。

#### 【0061】

図 8 を参照して、実施の形態 3 に係る半導体装置 100C は、実施の形態 2 に係る半導

10

20

30

40

50

体装置 100B の検出回路 110 に含まれる電流源 120 の構成例を示すものである。

#### 【0062】

具体的には、実施の形態 3 では、検出回路 110 の電流源 120 は、カレントミラー回路 125 及び 126 を含む。図 8 のその他の構成は、実施の形態 2 ( 図 6 ) と同様であるので、詳細な説明は繰り返さない。即ち、半導体装置 100C における検出信号 S<sub>a b</sub> は、実施の形態 2 に係る半導体装置 100B と同様に生成されるので、V<sub>c e</sub> > V<sub>t h</sub> の発生、即ち、スイッチング素子 10a の不飽和状態の発生を、実施の形態 2 と同様に検出することができる。

#### 【0063】

更に、実施の形態 3 によれば、カレントミラー回路を用いて電流源 120 を構成することによって出力電流 I<sub>a</sub> が安定化するので、V<sub>c e</sub> > V<sub>t h</sub> の検出精度を高めることが可能となる。又、以下で説明する、カレントミラー回路 125, 126 の構成素子 ( パンジスタ及び抵抗素子 ) についても、電圧比較器 130 及び駆動回路 150 と同様に、半導体装置 100C を構成する IC 上に形成される。

10

#### 【0064】

図 9 には、図 8 に示されたカレントミラー回路 125, 126 の好ましい構成例が示される。

#### 【0065】

図 9 を参照して、電流源 120 は、カレントミラー回路 125 を構成するトランジスタ T<sub>1</sub> ~ T<sub>3</sub> と、カレントミラー回路 126 を構成するトランジスタ T<sub>4</sub> ~ T<sub>6</sub> と、抵抗素子 123 とを有する。

20

#### 【0066】

カレントミラー回路 125 において、トランジスタ T<sub>1</sub> は、中間電位ノード 23 ( スイッチング素子 10a のコレクタ ) 及びノード N<sub>2</sub> の間に接続され、トランジスタ T<sub>2</sub> は、中間電位ノード 23 及びノード N<sub>3</sub> の間に接続される。トランジスタ T<sub>3</sub> は、ノード N<sub>2</sub> 及び抵抗素子 121 の間に接続される。トランジスタ T<sub>1</sub> 及び T<sub>2</sub> のゲートは、ノード N<sub>2</sub> と接続され、トランジスタ T<sub>3</sub> のゲートは、ノード N<sub>3</sub> と接続される。

#### 【0067】

カレントミラー回路 126 において、トランジスタ T<sub>4</sub> は、ノード N<sub>3</sub> 及びノード N<sub>4</sub> の間に接続され、トランジスタ T<sub>5</sub> は、ノード N<sub>4</sub> 及び低電位ノード 22 の間に接続される。トランジスタ T<sub>5</sub> は、ノード N<sub>5</sub> 及び低電位ノード 22 ( スイッチング素子 10a のエミッタ ) の間に接続される。トランジスタ T<sub>5</sub> 及び T<sub>6</sub> のゲートは、ノード N<sub>4</sub> と接続される。トランジスタ T<sub>4</sub> のゲートは、抵抗素子 123 ( 電気抵抗値 R<sub>3</sub> ) を介して高電位ノード 21 と接続されたノード N<sub>5</sub> と接続される。

30

#### 【0068】

図 9 の構成例では、カレントミラー回路 125 及び 126 が カレン上ミラー回路 によって構成されることで、電流源 120 の出力電流 I<sub>a</sub> の精度を向上することができる。この結果、判定電圧 V<sub>t h</sub> の設定精度が向上することで、V<sub>c e</sub> > V<sub>t h</sub> 、即ち、スイッチング素子の不飽和状態の検出精度を向上することができる。

#### 【0069】

図 9 の構成例では、トランジスタ T<sub>3</sub> 及び T<sub>4</sub> を高耐圧トランジスタで構成することにより、検出回路 110 の絶縁を確保することが可能である。

40

#### 【0070】

尚、図 7 に示された半導体装置 100B において、電流源 120 を図 8 及び図 9 で説明したように構成することも可能である。即ち、実施の形態 3 に係る半導体装置 100C についても、ローサイドのスイッチング素子 10a 及びハイサイドのスイッチング素子 10b の両方に対して、同じ回路構成で適用することが可能である。

#### 【0071】

又、実施の形態 3 に係る半導体装置は、又、実施の形態 1 ( 図 1 及び図 2 ) の半導体装置 100A において、電流源 120 を図 8 及び図 9 で説明したカレントミラー回路で構成

50

とすることによって実現することも可能である。

#### 【0072】

実施の形態4.

実施の形態4では、実施の形態1～3で説明した、スイッチング素子の不飽和状態の検出に応じた保護回路の適用について説明する。

#### 【0073】

図10は、実施の形態4に係る半導体装置が備える保護回路180の構成例を説明する回路図である。実施の形態4に係る半導体装置は、実施の形態1～3に係る半導体装置100A～100Cにおいて、制御信号SINが保護回路180を経由して、駆動回路150へ入力される構成を有する。

10

#### 【0074】

図10を参照して、保護回路180は、遅延回路181と、NANDゲート182と、ANDゲート183とを有する。

#### 【0075】

遅延回路181は、制御信号SINに遅延時間Tdを付与した遅延信号S1を出力する。NANDゲート182は、電圧比較器130が出力する検出信号Sabと、遅延信号S1とのNAND演算結果に従う、信号S2を出力する。遅延回路181は、例えば、直列接続された複数個（偶数個）のインバータ（NOTゲート）によって構成することができる。

20

#### 【0076】

ANDゲート183は、遅延回路181を通過していない制御信号SINと、信号S2とのAND演算結果に従い、駆動回路150へ入力される制御信号S3を生成する。駆動回路150は、制御信号S3に従って、ゲート信号SOUTを生成する。

#### 【0077】

次に、図11及び図12を用いて、実施の形態4に係る半導体装置の動作例を説明する。図11には、図4と同様に、正常動作時の波形例が示される。

#### 【0078】

図11を参照して、図4と同様に時刻t0において、制御信号SINがLレベルからHレベルに変化すると、図4と同様に、Vce, Ia, V+、及び、検出信号Sabが変化する。上述のように、正常動作時には、Vceの低下に応じて、検出信号Sabは、HレベルからLレベルへ変化する。

30

#### 【0079】

遅延信号S1は、時刻t0から遅延回路181によって付与された遅延時間Tdが経過した時刻txにおいて、LレベルからHレベルに変化する。遅延時間Tdは、正常動作時において、ターンオンの開始（時刻t0）から検出信号SabがLレベルに変化するまでに要する回路動作時間よりも長くなるように予め定められる。

#### 【0080】

NANDゲート182が出力する信号S2は、時刻t0～txの間、遅延信号S1がLレベルに止まることにより、Hレベルに維持される。更に、時刻tx～t1では、検出信号SabがLレベルに設定されることにより、信号S2はHレベルに維持される。

40

#### 【0081】

従って、正常動作時には、ANDゲート183に入力される信号S2は、常にHレベルに維持される。従って、駆動回路150へ入力される制御信号S3は、制御信号SINと同様の波形を有することになる。この結果、スイッチング素子10a, 10bは、実施の形態4に係る半導体装置の駆動回路150からのゲート信号SOUTによって、制御信号SINに応じてオン及びオフされる。

#### 【0082】

一方で、図12には、図5と同様に、スイッチング素子10aに不飽和状態が発生したときの動作例が示される。

#### 【0083】

50

図12を参照して、図5及び図11と同様に、時刻 $t_0$ において、制御信号SINがLレベルからHレベルに変化する。又、遅延信号S1の波形は、図11(正常動作時)と同様である。このため、信号S2は、遅延信号S1がHレベルに変化する時刻 $t_x$ までの間、Lレベルに維持される。

#### 【0084】

従って、少なくとも時刻 $t_x$ までの間、駆動回路150に入力される制御信号S3は、制御信号SINと同様であるので、図11と同様にスイッチング素子10a, 10bがターンオンする。

#### 【0085】

スイッチング素子10a, 10bでの不飽和状態の発生時ににおける、Vce、Ia, V+、及び、検出信号Sabの挙動は、図5と同様である。即ち、検出信号Sabは、制御信号SINのHレベル期間を通じて、Hレベルに維持される。

#### 【0086】

この結果、時刻 $t_x$ 以降では、NANDゲート182から出力される信号S2がLレベルに変化する。これに応じて、ANDゲート183から出力される制御信号S3がLレベルに設定されるのに応じて、スイッチング素子10a, 10bは、不飽和状態の検出に応じて、強制遮断(オフ)される。これにより、スイッチング素子10a, 10bを過電流から保護することができる。

#### 【0087】

このように、実施の形態4に係る半導体装置によれば、実施の形態1~3の半導体装置の効果に加えて、不飽和状態の検出に応じてスイッチング素子を自動的に遮断する保護機能を実現することができる。

#### 【0088】

尚、保護回路180は、半導体装置100A~100Cを構成するIC上に形成されたトランジスタを用いた論理回路、例えば、CMOS(Complementary Metal Oxide Semiconductor)論理回路によって構成することが可能である。これにより、検出回路110、電圧比較器130、及び、駆動回路150と同一の集積回路上に、保護回路180を搭載することができる。或いは、保護回路180に相当する機能を半導体装置(IC)の外部に設けて、制御信号S3に相当する信号を、半導体装置の外部から駆動回路150へ入力することも可能である。

#### 【0089】

本実施の形態では、スイッチング素子10a, 10bとしてIGBTを例示したが、アーム構成のハイサイド及びローサイドに用いられた、IGBT以外のスイッチング素子に対しても実施の形態1~4に係る半導体装置を適用することにより、絶縁を確保した上で、オン時に正電極及び負電極の間に電圧が発生する異常を検知することが可能である。

#### 【0090】

今回開示された実施の形態はすべての点で例示であって制限的なものではないと考えられるべきである。本発明の範囲は上記した説明ではなくて特許請求の範囲によって示され、特許請求の範囲と均等の意味及び範囲内でのすべての変更が含まれることが意図される。

#### 【符号の説明】

#### 【0091】

10a, 10b スイッチング素子、21 高電位ノード、22 低電位ノード、23 中間電位ノード、100A~100C 半導体装置、110 検出回路、120 電流源、121~123 抵抗素子、125, 126 カレントミラー回路、130 電圧比較器、135 電圧源、150 駆動回路、180 保護回路、181 遅延回路、GND 低電位、IC 駆動、Ia 出力電流(電流源)、Ia1 電流、SIN 制御信号、SOUT ゲート信号、Sab 検出信号、Td 遅延時間、Vcc 高電位、Vt 直流電圧、Vth 判定電圧。

10

20

30

40

50

## 【図面】

## 【図 1】

図1

## 【図 2】

10

20

## 【図 3】

図3

## 【図 4】

図4

30

40

50

【図 5】

図5

【図 6】

図6

【図 7】

図7

【図 8】

図8

10

20

30

40

50

【図 9】

【図 10】

10

【図 11】

【図 12】

20

30

40

50

---

フロントページの続き

- (56)参考文献

- 特開平03-105262 (JP, A)

特開平05-146049 (JP, A)

特開2007-019728 (JP, A)

特開2002-185294 (JP, A)

特開2016-163051 (JP, A)

特許第3242672 (JP, B2)

- (58)調査した分野 (Int.Cl., DB名)

- H03K 17/00 - 17/70

H02M 1/00