(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第6030248号

(P6030248)

(45) 発行日 平成28年11月24日(2016.11.24)

(24) 登録日 平成28年10月28日(2016.10.28)

(51) Int.Cl.

F 1

H03F 3/191 (2006.01)

H03F 3/24 (2006.01)H03F 3/191

H03F 3/24

請求項の数 20 (全 15 頁)

(21) 出願番号 特願2015-548059 (P2015-548059)

(86) (22) 出願日 平成25年12月17日 (2013.12.17)

(65) 公表番号 特表2016-500499 (P2016-500499A)

(43) 公表日 平成28年1月12日 (2016.1.12)

(86) 國際出願番号 PCT/US2013/075880

(87) 國際公開番号 WO2014/100046

(87) 國際公開日 平成26年6月26日 (2014.6.26)

審査請求日 平成28年1月14日 (2016.1.14)

(31) 優先権主張番号 61/738,251

(32) 優先日 平成24年12月17日 (2012.12.17)

(33) 優先権主張国 米国(US)

(31) 優先権主張番号 13/775,026

(32) 優先日 平成25年2月22日 (2013.2.22)

(33) 優先権主張国 米国(US)

早期審査対象出願

(73) 特許権者 595020643

クアアルコム・インコーポレイテッド

QUALCOMM INCORPORATED

アメリカ合衆国、カリフォルニア州 92

121-1714、サン・ディエゴ、モア

ハウス・ドライブ 5775

(74) 代理人 100108855

弁理士 蔵田 昌俊

(74) 代理人 100109830

弁理士 福原 淑弘

(74) 代理人 100158805

弁理士 井関 守三

(74) 代理人 100194814

弁理士 奥村 元宏

最終頁に続く

(54) 【発明の名称】同調広帯域ドライバ増幅器

## (57) 【特許請求の範囲】

## 【請求項 1】

増幅器の出力端子と回路接地との間に選択的に接続され、且つ、第1の帯域選択回路に供給される2つのイネーブル信号に基づいて、増幅帯域を第1の周波数帯域から第2の周波数帯域に調節するように構成された第1の帯域選択回路と、

前記増幅帯域を前記第1の周波数帯域に設定するように構成された第2の帯域選択回路と、前記第2の帯域選択回路は、前記出力端子と前記回路接地との間に接続された選択されたキャパシタを備え、

前記第1の帯域選択回路と前記回路接地との間に選択的に接続され、且つ、前記増幅帯域が前記第1の周波数帯域に設定されたときに、前記第1の周波数帯域に関連付けられた第二高調波周波数を低減させるように構成された第1の高調波低減回路と

を備える装置。

## 【請求項 2】

前記第2の帯域選択回路は、

前記出力端子と電源電圧との間に接続された第1のインダクタを備える、請求項1に記載の装置。

## 【請求項 3】

前記第1の帯域選択回路は、

前記出力端子に接続された第1のインダクタと、

前記第1のインダクタに接続された第1のキャパシタと、

10

20

前記增幅帯域を前記第2の周波数帯域に設定するために前記第1のキャパシタを前記回路接地に選択的に接続するように構成されたスイッチと

を備える、請求項1に記載の装置。

**【請求項4】**

前記第1の高調波低減回路は、

前記第1のインダクタに接続された第2のキャパシタと、

前記增幅帯域が前記第1の周波数帯域に設定されたときには、前記第1の周波数帯域における前記第二高調波周波数の低減をイネーブルにし、前記增幅帯域が前記第2の周波数帯域に設定されたときには、前記第2の周波数帯域の中央周波数を同調するために、前記第2のキャパシタを前記回路接地に選択的に接続するように構成されたスイッチと

を備える、請求項3に記載の装置。 10

**【請求項5】**

前記增幅器は、第1のトランジスタ及び第2のトランジスタを備え、前記出力端子は、前記第1のトランジスタのドレイン端子に接続される、請求項1に記載の装置。

**【請求項6】**

前記第2のトランジスタのソース端子に結合され、前記增幅帯域が前記第2の周波数帯域に設定されたときに第二高調波周波数を低減させるように構成された第2の高調波低減回路を更に備える、請求項5に記載の装置。

**【請求項7】**

前記第2の高調波低減回路は、

前記第2のトランジスタの前記ソース端子と、前記回路接地との間に接続されたインダクタと、

前記第2のトランジスタの前記ソース端子と前記回路接地との間に接続されたキャパシタと

を備える、請求項6に記載の装置。 20

**【請求項8】**

前記第1の周波数帯域は、前記第2の周波数帯域の第2の中央周波数よりも周波数が低い第1の中央周波数を有する、請求項1に記載の装置。

**【請求項9】**

增幅器の出力端子と回路接地との間に選択的に接続され、第1の帯域選択回路に供給される2つのイネーブル信号に基づいて、前記增幅器の増幅帯域を第1の周波数帯域から第2の周波数帯域に調節するための手段と、 30

前記出力端子と前記回路接地との間に選択されたキャパシタを提供するための手段を含み、前記增幅器の前記増幅帯域を前記第1の周波数帯域に設定するための手段と、

調節するための前記手段と前記回路接地との間に接続され、前記增幅帯域が前記第1の周波数帯域に設定されたときに、前記第1の周波数帯域における第二高調波周波数を低減させるための手段と、

を備える装置。

**【請求項10】**

前記增幅器の前記増幅帯域を前記第1の周波数帯域に設定するための前記手段は、

前記出力端子と電源電圧との間に接続された第1のインダクタ

を備える、請求項9に記載の装置。 40

**【請求項11】**

調節するための前記手段は、

前記出力端子に接続された第1のインダクタと、

前記第1のインダクタに接続された第1のキャパシタと、

前記增幅帯域を前記第2の周波数帯域に設定するために、前記第1のキャパシタを前記回路接地に選択的に接続するように構成されたスイッチと

を備える、請求項9に記載の装置。

**【請求項12】**

低減させるための前記手段は、

前記第1のインダクタに接続された第2のキャパシタと、

前記増幅帯域が前記第1の周波数帯域に設定されたときには、前記第1の周波数帯域における前記第二高調波周波数の低減をイネーブルにし、前記増幅帯域が前記第2の周波数帯域に設定されたときには、前記第2の周波数帯域の中央周波数を同調するために、前記第2のキャパシタを前記回路接地に選択的に接続するように構成されたスイッチと

を備える、請求項1-1に記載の装置。

**【請求項1-3】**

前記増幅器は、第1のトランジスタ及び第2のトランジスタを備え、前記出力端子は、前記第1のトランジスタのドレイン端子に接続される、請求項9に記載の装置。 10

**【請求項1-4】**

前記第2のトランジスタのソース端子に接続され、且つ、前記増幅帯域が前記第2の周波数帯域に設定されたときに第二高調波周波数を低減させるように構成されたトラップするための手段を更に備える、請求項1-3に記載の装置。

**【請求項1-5】**

トラップするための前記手段は、

前記第2のトランジスタの前記ソース端子と、前記回路接地との間に接続されたインダクタと、

前記第2のトランジスタの前記ソース端子と前記回路接地との間に接続されたキャパシタと 20

を備える、請求項1-4に記載の装置。

**【請求項1-6】**

前記第1の周波数帯域は、前記第2の周波数帯域の第2の中央周波数よりも周波数が低い第1の中央周波数を有する、請求項9に記載の装置。

**【請求項1-7】**

増幅器の増幅帯域が低周波数帯域に設定されることとなるか高周波数帯域に設定されこととなるかを決定することと、

前記増幅帯域が前記低周波数帯域に設定されることとなる場合には、前記増幅器の出力端子と回路接地との間に接続された選択されたキャパシタを有する第1の帯域選択回路をイネーブルにし、増幅器の前記出力端子と前記回路接地との間に接続された第2の帯域選択回路をディセーブルにすることと、 30

前記増幅帯域が前記高周波数帯域に設定されることとなる場合には、前記第1の帯域選択回路をディセーブルにし、前記第2の帯域選択回路をイネーブルにすることと、

を備える方法。

**【請求項1-8】**

前記増幅帯域が前記低周波数帯域に設定されることとなる場合に、低帯域トラップ回路がイネーブルにされることとなるかどうかを決定することと、

前記低帯域トラップ回路がイネーブルにされることとなる場合に、前記低周波数帯域に関連付けられた第二高調波周波数を低減させるために前記低帯域トラップ回路をイネーブルにすることと 40

を更に備える、請求項1-7に記載の方法。

**【請求項1-9】**

前記増幅帯域が前記高周波数帯域に設定されることとなる場合に、前記高周波数帯域に関連付けられた第二高調波周波数を低減させるために高帯域トラップ回路をイネーブルにすることを更に備える、請求項1-7に記載の方法。

**【請求項2-0】**

前記低周波数帯域は、前記高周波数帯域の第2の中央周波数よりも周波数が低い第1の中央周波数を有する、請求項1-7に記載の方法。

**【発明の詳細な説明】**

**【米国特許法第119条に基づく優先権の主張】**

**【0001】**

[0001] 本願は、本讓受人に譲渡され、参照により本明細書に明確に組み込まれる、2012年12月17日に出願された、「TUNABLE WIDEBAND DRIVER AMPLIFIER」と題する米国仮特許出願第61/738251号からの優先権の利益を主張する。

**【技術分野】****【0002】**

[0002] 本願は一般にアナログフロントエンドの動作及び設計に関し、より詳細には、アナログフロントエンドで使用するためのドライバ増幅器の動作及び設計に関する。

**【背景技術】****【0003】**

[0003] ワイヤレスデバイスは、益々複雑になってきており、それは、より小さいチップ及び回路基板上により多くの回路が組み込まれることに帰着する。例えば、ワイヤレスデバイスにおいて使用される従来の送信機は、それぞれ低周波数帯域と高周波数帯域の両方で信号を増幅するために多数のドライバ増幅器（DA）を含みうる。特定の周波数帯域に対して専用のDAを有することで、所望の増幅目標が達成されうるが、そのような実現はいくつかの不利益も有しうる。例えば、多数のDAを利用することは、ダイエリア要件の観点からコストの増加に帰着しうる。更に、アップコンバータのような、送信機内の他の回路は、多数のDA構成をサポートするように変形される必要があり、その結果、この送信機の複雑性を増加させうる。

**【0004】**

[0004] したがって、必要なものは、ワイヤレスデバイスにおけるダイエリア及び送信機設計複雑性を減らすように構成された高効率の広帯域ドライバ増幅器である。

**【0005】**

[0005] 本明細書で説明される先の態様は、添付の図面と併せて考慮されるとき、以下の説明を参考することによって、より容易に明らかになるであろう。

**【図面の簡単な説明】****【0006】**

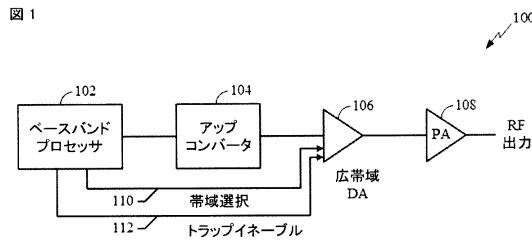

**【図1】**図1は、同調広帯域ドライバ増幅器の例示的な実施形態を含むデバイスで使用するための送信機を示す。

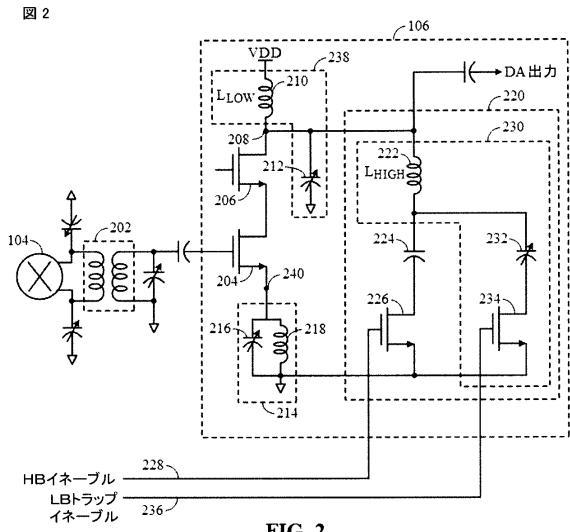

**【図2】**図2は、図1に例示された同調広帯域ドライバ増幅器の詳細な例示的な実施形態を示す。

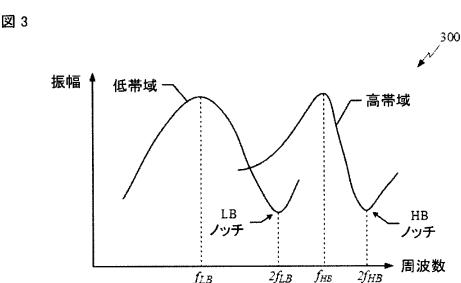

**【図3】**図3は、図2に示されるドライバ増幅器の出力の広帯域周波数範囲を例示する周波数プロットを示す。

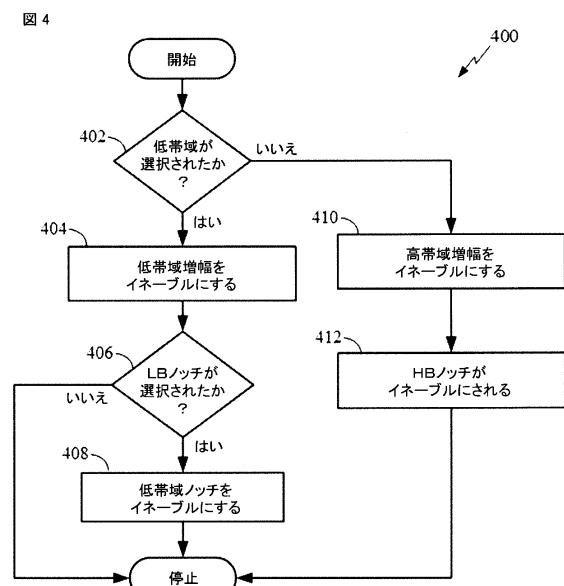

**【図4】**図4は、ワイヤレスデバイスにおける広帯域増幅のための方法の例示的な実施形態を示す。

**【図5】**図5は、同調広帯域ドライバ増幅器装置の例示的な実施形態を示す。

**【発明を実施するための形態】****【0007】**

[0011] 添付の図面に関連して以下に記載される詳細な説明は、本発明の例示的な実施形態の説明として意図されており、本発明が実施されることのできる唯一の実施形態を表すことは意図されない。この説明全体にわたって使用される「例示的な」という用語は、「例、実例、又は例示としての役割を果たす」を意味し、必ずしも、他の例示的な実施形態よりも好ましい又は有利であると解釈されるべきではない。詳細な説明は、本発明の例示的な実施形態の完全な理解を与えることを目的とした特定の詳細を含む。本発明の例示的な実施形態がこれらの特定の詳細なしに実施されうることは当業者に明らかになるであろう。いくつかの事例では、周知の構造及びデバイスが、本明細書に提示される例示的な実施形態の新規性を曖昧にしないために、ロック図の形式で示される。

**【0008】**

[0012] 図1は、新しい同調広帯域DAの例示的な実施形態を含むデバイスで使用するための送信機100を示す。送信機100は、アップコンバータ104に送るべきベース

10

20

30

40

50

バンドデータを出力するベースバンドプロセッサ 102 を備える。アップコンバータ 104 は、ベースバンドデータを無線周波数 (RF) 信号へとアップコンバートし、この RF 信号を同調広帯域 DA 106 に入力する。同調 DA 106 は、2 つの選択可能な周波数帯域へと分割される広い周波数範囲（即ち、800 MHz から 2.4 GHz）にわたり増幅を提供するように構成される。同調 DA 106 は、ベースバンドプロセッサ 102 から帯域選択信号 110 を受け取る。帯域選択信号 110 は、増幅が提供されるであろう 2 つの選択可能な帯域のうちの 1 つを選択する。同調 DA 106 は、また、ベースバンドプロセッサ 102 からトラップイネーブル信号 112 を受け取る。トラップイネーブル信号 112 は、第二高調波 (2<sup>nd</sup> harmonic) 及びより高い周波数の減衰を、増幅出力に提供するトラップ回路をイネーブル又はディセーブルにする。次に、同調 DA 106 の増幅出力は、送信のために RA 信号が更に増幅される電力増幅器 (PA) 108 に入力される。様々な例示的な実施形態では、同調 DA 106 は、広い周波数範囲にわたり増幅を提供し、多数の増幅器を利用する従来の複数の DA 構成と比べてダイエリアを半分に減らすように構成される。

10

#### 【0009】

[0013] 図 2 は、図 1 に例示される同調広帯域ドライバ増幅器 106 の詳細な例示的な実施形態を示す。アップコンバータ 104 は、差動信号をシングルエンド信号に変換する平衡不平衡変成器（パラン (balun)）202 に差動信号を出力する。シングルエンド信号は、DA 106 のトランジスタ 204 に入力される。トランジスタ 204 は、トランジスタ 206 とともに動作して、シングルエンド信号を増幅させ、トランジスタ 206 のドレイン端子 208 において増幅出力信号 (DA 出力) を発生させる。トランジスタ 204、206 はカスコードペアとして構成されているが、増幅器 106 が任意の適切なトランジスタ構成を利用しうることに留意されたい。

20

#### 【0010】

[0014] 例示的な実施形態では、第 1 の帯域選択回路 238 は、増幅器の増幅帯域を第 1 の周波数帯域に設定するように動作する。第 1 の周波数帯域（本明細書では、低周波数帯域とも呼ばれる）は、(f<sub>LB</sub>) と指定された中央周波数を有する。第 1 の帯域選択回路 238 は、インダクタ L<sub>LOW</sub> 210 及び可変キャパシタ 212 を備える。インダクタ L<sub>LOW</sub> 210 は、ドレイン端子 208 と電源電圧 (VDD) との間に接続される。可変キャパシタ 212 は、ドレイン端子 208 と回路接地との間に接続される。例示的な実施形態では、インダクタ L<sub>LOW</sub> 210 は、大きなインダクタンス値（即ち、4 nH）を有し、可変キャパシタ 212 は、同調キャパシタンス範囲（即ち、1 - 10 pF）を有する。インダクタ L<sub>LOW</sub> 210 及び可変キャパシタ 212 は組み合わさって、DA 106 について動作の第 1 の周波数帯域を設定する。例示的な実施形態では、インダクタ L<sub>LOW</sub> 210 及び可変キャパシタ 212 は、第 1 の周波数帯域の中央周波数 (f<sub>LB</sub>) を 800 MHz から 1.4 GHz へと同調するように構成される。

30

#### 【0011】

[0015] 低帯域トラップ回路 230 は、動作の第 1 の周波数帯域で動作するときに、増幅 DA 出力信号に第二高調波周波数低減を提供するように動作する。低帯域トラップ回路 230 は、インダクタ L<sub>HIGH</sub> 222 とトランジスタ 234 のドレイン端子との間に接続された可変キャパシタ 232 を備える。インダクタ L<sub>HIGH</sub> 222 は、ドレイン端子 208 にも接続される。例示的な実施形態では、キャパシタ 232 は、1 ~ 6 pF の範囲の同調キャパシタンス値を有し、インダクタ L<sub>HIGH</sub> 222 は、2 nH のインダクタンス値を有する。トランジスタ 234 は、回路接地に接続されたソース端子と、低帯域 (LB) トラップイネーブル信号 236 によって制御されるゲート端子とを有する。例えば、LB トラップイネーブル信号 236 が「高電圧」又は「イネーブル」状態であるとき、キャパシタ 232 が回路接地に結合されるように、トランジスタ 234 がオンにされる。LB トラップイネーブル信号 236 が「低電圧」又は「ディセーブル」状態であるとき、キャパシタ 232 が回路接地から結合解除されるようにトランジスタ 234 がオフにされる。例示的な実施形態では、図 1 に例示されたトラップイネーブル信号 112 は、L

40

B ト ラッ プ イ ネーブル 信 号 2 3 6 を 備え、ベース バンド プロセッサ 1 0 2 又は デバイス の 何 等か の 其 他 の エンティティ に よって 発生させられる。

#### 【 0 0 1 2 】

[0016] キャパシタ 2 3 2 が 回路 接地 に 結合される ように、L B ト ラッ プ イ ネーブル 信 号 2 3 6 が トランジスタ 2 3 4 を イ ネーブル に する（又は、オン に する）とき、インダクタ  $L_{HIGH}$  2 2 2 及び キャパシタ 2 3 2 の 組み 合わせ は、動作 の 低周波数 帯域 に あるとき、増幅 D A 出力 信 号 に 対する 第二 高調波 周波数 低減 を 提供する ため に 低帯域 ト ラップ 回路 を 形成する ように 動作する。例えば、低帯域 ト ラップ 回路 2 3 0 が イ ネーブル に されるとき、低帯域 中央 周波数（ $f_{LB}$ ）の 第二 高調波 周波数（ $2f_{LB}$ ）以上 の D A 出力 周波数 が 低減 又は 減衰される。

10

#### 【 0 0 1 3 】

[0017] 例示的 な 実施形態 で は、第 2 の 帯域選択回路 2 2 0 は、D A 1 0 6 の 増幅 帯域 を 第 2 の 周波数 帯域 に 設定する ように 動作する。第 2 の 周波数 帯域（本明細書 で は、高周波数 帯域 とも 呼ばれる）は、（ $f_{HB}$ ）と 指定された 中央 周波数 を 有する。第 2 の 帯域選択回路 2 2 0 は、低帯域 ト ラップ 回路 2 3 0 を 含む。例示的 な 実施形態 で は、第 2 の 帯域選択回路 2 2 0 は また、キャパシタ 2 2 4 と 直列 に 接続された インダクタ  $L_{HIGH}$  2 2 2 を 備える。例えば、例示的 な 実施形態 で は、キャパシタ 2 2 4 は、10 pF と いう 固定 キャパシタンス 値 を 有する。キャパシタ 2 2 4 は、同様に 回路 接地 に 接続された ソース 端子 を 有する トランジスタ 2 2 6 の ドレイン 端子 に 更に 接続される。トランジスタ 2 2 6 は、高帯域（HB）の イ ネーブル 信 号 2 2 8 に 接続され、それ に よって 制御される ゲート 端子 を 有する。例えば、HB イ ネーブル 信 号 2 2 8 が「高電圧」又は「イ ネーブル」状態 であるとき、キャパシタ 2 2 4 が 回路 接地 に 結合される ように トランジスタ 2 2 6 が オン に される。HB イ ネーブル 信 号 2 2 8 が「低電圧」又は「ディセーブル」状態 であるとき、キャパシタ 2 2 4 が 回路 接地 から 結合解除される ように、トランジスタ 2 2 6 が オフ に される。例示的 な 実施形態 で は、図 1 に 例示された 帯域選択 信 号 1 1 0 は、HB イ ネーブル 信 号 2 2 8 を 備え、ベース バンド プロセッサ 1 0 2 又は デバイス の 何 等か の 其 他 の エンティティ に よって 発生させられる。

20

#### 【 0 0 1 4 】

[0018] 例示的 な 実施形態 で は、HB イ ネーブル 信 号 2 2 8 及び L B ト ラッ プ イ ネーブル 信 号 2 3 6 の 両方 が イ ネーブル 状態 に 設定されるとき、キャパシタ 2 2 4 及び 2 3 2 が 回路 接地 に 結合される ように、トランジスタ 2 2 6 及び 2 3 4 が イ ネーブル に される（即ち、オン に される）。この構成 は、キャパシタ 2 2 4 及び 2 3 2 の キャパシタンス 値 を 組み 合せて、キャパシタ 2 3 2 の 同調 に 依存して、10 ~ 16 pF の 総合 キャパシタンス 値 を 作り出す。この 総合 キャパシタンス は、インダクタ  $L_{HIGH}$  2 2 2、インダクタ  $L_{LOW}$  2 1 0、キャパシタ 2 1 2 と 組み 合わせ て、D A 1 0 6 の 増幅 帯域 を 第 2 の（又は、高い）周波数 帯域 に 調節する ように 動作する。例示的 な 実施形態 で は、第 2 の 帯域選択回路 2 2 0 は、第 2 の 周波数 帯域 の 中央 周波数（ $f_{HB}$ ）を 1.4 GHz から 2.4 GHz に 同調する ように 構成される。

30

#### 【 0 0 1 5 】

[0019] 同調 キャパシタ 2 1 6 及び インダクタ 2 1 8 を 備える タンク 回路 2 1 4 は、トランジスタ 2 0 4 の ソース 端子 2 4 0 と、回路 接地 との 間 に 接続される。タンク 回路 2 1 4 は、D A 1 0 6 の 増幅 帯域 が 第 2 の（又は、高い）周波数 帯域 に 設定されるとき、第二 高調波 低減 を 提供する ように 動作する。例示的 な 実施形態 で は、インダクタ 2 1 8 は、0.25 nH の インダクタンス 値 を 有し、同調 キャパシタ 2 1 6 は、0.5 ~ 4 pF の 範囲 の キャパシタンス 値 を 有する。例えば、タンク 回路 2 1 4 は、高帯域 中央 周波数（ $f_{HB}$ ）の 二 次 高調波（ $2f_{HB}$ ）以上 の D A 出力 周波数 が 低減 又は 減衰される ように 動作する。例えば、タンク 回路 2 1 4 は、高帯域 の 高次 高調波 周波数（即ち、第二 高調波（ $2f_{HB}$ ）及び より 高い 周波数）で 高インピーダンス を 示す ように 動作する。基本 周波数（ $f_{HB}$ ）において、タンク 2 1 4 は、著しく 低い インピーダンス を 示す、共通 ソース 段 の 利得 に 対して 小さな インパクト しか 与えない で ある。更に、低周

40

50

波数帯域において、インダクタ 218 が及ぼす影響はほぼなくなり、同調キャパシタ 216 は、ディセーブルにされるか又はオフにされることができる。

#### 【0016】

[0020] 様々な例示的な実施形態では、インダクタ  $L_{LOW}$  210、 $L_{HIGH}$  222、及び可変キャパシタ 212、216、232 の値は、製造中に、インストール中に、又は動作中に設定されうる。例示的な実施形態では、インダクタ  $L_{LOW}$  210 及び  $L_{HIGH}$  222 の値は、製造時に決定され、可変キャパシタ 212、216、及び 232 の値は、ベースバンドプロセッサ 102 によって動作中に決定される。例えば、例示的な実施形態では、ベースバンドプロセッサ 102 から出力される帯域選択信号 110 は、可変キャパシタ 212、216、及び 232 をイネーブルにする、ディセーブルにする、及び、その容量値を選択する制御信号（図 2 には示されない）を備える。10

#### 【0017】

[0021] 広帯域 DA 106 の動作中、DA 106 の増幅帯域を、第 1 の（低い）周波数帯域又は第 2 の（高い）周波数帯域のいずれかに設定するために、イネーブル信号 228 及び 236 が使用される。各周波数帯域について、選択された帯域の中央周波数の第二高調波周波数以上の出力周波数を低減又は減衰させるために、第二高調波低減は、自動的にイネーブルにされるか又は選択的にイネーブルにできる。広帯域ドライバ增幅器 106 の動作についてのより詳細な説明が以下に提供される。

#### 【0018】

[0022] 図 3 は、ドライバ增幅器 106 の DA 出力の広い周波数範囲（即ち、800 MHz ~ 2.4 GHz）にわたって増幅を例示する周波数プロット 300 を示す。プロット 300 は、同調基本周波数 ( $f_{LB}$ ) を有する低周波数帯域にわたった増幅を示す。低周波数帯域における動作は、第 1 の（又は、より低い）帯域選択回路 238 の動作から決定される。プロット 300 はまた、LB トランプ回路 230 によって提供される低帯域周波数の第二高調波 ( $2f_{LB}$ ) における第二高調波減衰 (LB ノッチ) を示す。20

#### 【0019】

[0023] プロット 300 はまた、同調基本周波数 ( $f_{HB}$ ) を有する高周波数帯域にわたった増幅を示す。高周波数帯域における動作は、第 2 の（又は、より高い）帯域選択回路 220 の動作から決定される。プロット 330 はまた、高帯域第二高調波トランプ回路 214 によって提供される高帯域周波数の第二高調波 ( $2f_{HB}$ ) における第二高調波減衰 (HB ノッチ) を示す。30

#### 【0020】

[0024] 図 4 は、ワイヤレスデバイスにおける広帯域増幅のための方法 400 の例示的な実施形態を示す。例えば、方法 400 は、図 2 に示されたドライバ增幅器 106 との使用に適している。

#### 【0021】

[0025] ブロック 402において、低周波数帯域での増幅が選択されるかどうかを決定するために決定が行われる。例えば、ベースバンドプロセッサ 102 は、増幅帯域を設定するために、HB イネーブル信号 228 を出力する。HB イネーブル信号 228 がディセーブルされる場合、低周波数帯域での増幅が選択される。HB イネーブル信号 228 がイネーブルされる場合、高周波数帯域での増幅が選択される。低周波数帯域での増幅が選択された場合、方法はブロック 404 に進む。高周波数帯域での増幅が選択された場合、方法はブロック 410 に進む。40

#### 【0022】

[0026] ブロック 404において、低帯域での増幅がイネーブルにされる。例示的な実施形態では、トランジスタ 226 がディセーブルにされ、それによって、キャパシタ 224 を回路接地から結合解除するように、HB イネーブル信号 228 がディセーブル状態に設定される。結果として、インダクタ  $L_{LOW}$  210 及びキャパシタ 212 を備える低帯域選択回路 238 は、低帯域での増幅ために同調中央周波数 ( $f_{LB}$ ) を設定する。例示的な実施形態では、インダクタ  $L_{LOW}$  210 及び可変キャパシタ 212 は、第 1 の50

(低い)周波数帯域の中央周波数( $f_{L_B}$ )を800MHzから1.4GHzへとチューニングするように構成される。

#### 【0023】

[0027] ブロック406において、低帯域ノッチフィルタがイネーブルにされるべきかどうかについての決定が行われる。例えば、ベースバンドプロセッサ102は、低帯域ノッチフィルタがイネーブルにされるべきかを決定するために使用されるLBトラップイネーブル信号236を出力する。LBトラップイネーブル信号236がディセーブルにされた場合、低帯域ノッチフィルタはディセーブルにされ、方法は終了する。LBトラップイネーブル信号236がイネーブルにされた場合、低帯域ノッチフィルタはイネーブルにされることとなり、方法はブロック408に進む。

10

#### 【0024】

[0028] ブロック408において、低帯域ノッチがイネーブルにされる。例示的な実施形態では、LBトラップイネーブル信号236は、トランジスタ234がキャパシタ232を回路接地に結合させるように、低帯域トラップ回路230をイネーブルにするよう動作する。インダクタ $L_{HIGH}$ 222及びキャパシタ232の組み合わせは、低帯域第二高調波周波数( $2f_{L_B}$ )以上の周波数を低減又は減衰させるために、低帯域トラップを提供するように動作する。

#### 【0025】

[0029] ブロック410において、高帯域増幅がイネーブルにされる。例示的な実施形態では、トランジスタ226がイネーブルにされ、それによって、キャパシタ224を回路接地に結合するように、HBイネーブル信号228がイネーブル状態に設定される。結果として、第2の帯域選択回路220がイネーブルにされる。追加的に、LBトラップ回路230は、LBトラップイネーブル信号236によってイネーブルにされる。インダクタ $L_{HIGH}$ 222、キャパシタ224、及びキャパシタ232の組み合わせは、増幅器106の増幅帯域を高帯域に押し上げる又は調節するように動作する。例えば、高帯域での増幅を提供するために、中央周波数は( $f_{H_B}$ )に同調される。

20

#### 【0026】

[0030] ブロック412において、高帯域ノッチフィルタがイネーブルにされる。例示的な実施形態では、インダクタ218及びキャパシタ216の組み合わせを備えるタンク回路214は、高帯域第二高調波周波数( $2f_{H_B}$ )以上の周波数を低減又は減衰させるために、高帯域トラップを提供するように動作する。

30

#### 【0027】

[0031] したがって、方法400は、従来の増幅器よりも、必要とされるダイエリアを減らす、ワイヤレスデバイスにおける広帯域増幅を提供する。方法400の動作が、他の等価的な方法が可能となるように当業者によって再配列されうること、修正されうること、又は変えられうることに留意されたい。

#### 【0028】

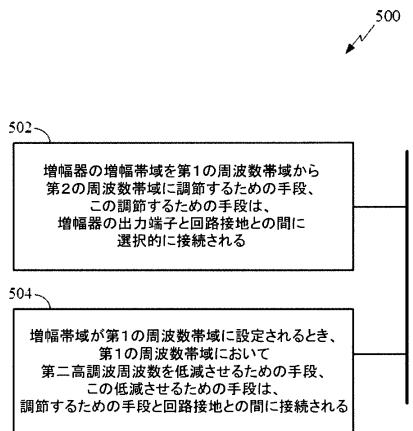

[0032] 図5は、広帯域ドライバ増幅器装置500の例示的な実施形態を示す。例えば、方法500は、図2に示されたドライバ増幅器106との使用に適している。一様様では、装置500は、本明細書で説明されるような機能を提供するように構成された1つ又は複数のモジュールによって実現される。例えば、ある様様では、各モジュールは、ハードウェア及び/又はハードウェア実行ソフトウェアを備える。

40

#### 【0029】

[0033] 装置500は、増幅器の増幅帯域を第1の周波数帯域から第2の周波数帯域に調節するための手段(502)を備える第1のモジュールを備える。この調節するための手段は、増幅器の出力端子と回路接地との間で選択的に接続される。これは、ある様様では、第2の帯域選択回路220を備える。

#### 【0030】

[0034] 装置500は、増幅帯域が第1の周波数帯域に設定されるとき、第1の周波数帯域において第二高調波周波数を低減させるための手段(504)を備える第2のモジュ

50

ールを備え、この低減させるための手段は、調節するための手段と回路接地との間に接続される。これは、ある態様では、第1の高調波低減回路230を備える。

### 【0031】

[0035] 当業者であれば、情報及び信号が、多種多様な技術及び技法のうちの任意のものを使用して処理又は表されうることを理解するであろう。例えば、上記説明の全体にわたって参照されうるデータ、命令、コマンド、情報、信号、ビット、シンボル、及びチップは、電圧、電流、電磁波、磁場又は磁性粒子、光場又は光粒子、或いはこれらの任意の組み合わせによって表されうる。トランジスタのタイプ及び技術が、同じ結果を達成するために、代用、再配列、又は他の方法で修正されうることに更に留意されたい。例えば、P M O Sトランジスタを利用して示される回路は、N M O Sトランジスタを使用するように修正されることができ、逆もまた同様である。このように、本明細書で開示された増幅器は、様々なトランジスタタイプ及び技術を使用して実現されることができ、図面に例示されているこれらトランジスタタイプ及び技術に限定されない。例えば、B J T、G a A s、M O S F E Tのようなトランジスタタイプ又はその他のトランジスタ技術が使用される。

10

### 【0032】

[0036] 当業者であれば、本明細書で開示された実施形態に関連して説明された実例となる様々な論理ブロック、モジュール、回路、及びアルゴリズムステップが、電子ハードウェア、コンピュータソフトウェア、又は両方の組み合わせとして実現されうることを更に認識するであろう。このハードウェアとソフトウェアとの互換性を明確に例示するために、実例となる様々な構成要素、ブロック、モジュール、回路、及びステップが、概してそれらの機能の観点から上に説明されている。このような機能がハードウェアとして実現されるかソフトウェアとして実現されるかは、特定の用途及びシステム全体に課せられている設計制約に依存する。当業者は、特定の用途ごとに、説明された機能を様々な方法で実現することができるが、このような実現の判定（decision）は本発明の例示的な実施形態の適用範囲（scope）からの逸脱の原因になるとして解釈されるべきではない。

20

### 【0033】

[0037] 本明細書で開示された実施形態に関連して説明された実例となる様々な論理ブロック、モジュール、及び回路は、汎用プロセッサ、デジタルシグナルプロセッサ（D S P）、特定用途向け集積回路（A S I C）、フィールドプログラマブルゲートアレイ（F P G A）又は他のプログラマブル論理デバイス、ディスクリートゲート又はトランジスタ論理回路、ディスクリートハードウェア構成要素、或いは本明細書で説明された機能を行うように設計されたこれらの任意の組み合わせで実現されるか又は行われうる。汎用プロセッサはマイクロプロセッサでありうるが、代替として、このプロセッサは、任意の従来のプロセッサ、コントローラ、マイクロコントローラ、又はステートマシンでありうる。プロセッサはまた、コンピュータデバイスの組み合わせとして、例えば、D S Pと、1つのマイクロプロセッサ、複数のマイクロプロセッサ、D S Pコアと連携した1つ又は複数のマイクロプロセッサ、又はその他のこのような構成との組み合わせとして実現されうる。

30

### 【0034】

[0038] 本明細書で開示された実施形態に関連して説明された方法又はアルゴリズムのステップは、直接ハードウェアで、プロセッサによって実行されるソフトウェアモジュールで、又は両者の組み合わせで具現化されうる。ソフトウェアモジュールは、ランダムアクセスメモリ（R A M）、フラッシュメモリ、読み専用メモリ（R O M）、電気的プログラマブルR O M（E P R O M）、電気的消去可能プログラマブルR O M（E E P R O M（登録商標））、レジスタ、ハードディスク、リムーバルディスク、C D - R O M、又は当技術分野において知られている他の形状の記憶媒体に存在しうる。例示的な記憶媒体は、プロセッサがこの記憶媒体から情報を読み取り、この記憶媒体に情報を書き込むことができるように、プロセッサに結合される。代替として、記憶媒体はプロセッサと一体化されうる。プロセッサ及び記憶媒体はA S I Cに存在しうる。A S I Cはユーザ端末内に

40

50

存在しうる。代替として、プロセッサ及び記憶媒体は、ディスクリート構成要素として、ユーザ端末に存在しうる。

### 【0035】

[0039] 1つ又は複数の例示的な実施形態では、説明された機能は、ハードウェアで、ソフトウェアで、ファームウェアで、又はこれらの任意の組み合わせで実現されうる。ソフトウェアで実現される場合、これら機能は、コンピュータ可読媒体上で、1つ又は複数の命令又はコードとして送信又は記憶されうる。コンピュータ可読媒体は、ある場所から別の場所へのコンピュータプログラムの転送を容易にする任意の媒体を含む通信媒体及び非一時的なコンピュータ記憶媒体の両方を含む。非一時的な記憶媒体は、コンピュータによってアクセスされることができる任意の利用可能な媒体でありうる。限定ではなく例として、このようなコンピュータ可読媒体は、RAM、ROM、EEPROM、CD-ROM又は他の光ディスク記憶装置、磁気ディスク記憶装置又は他の磁気記憶デバイス、或いは、データ構造又は命令の形式で所望のプログラムコードを記憶又は伝送するために使用可能であり、且つコンピュータによってアクセスされうるその他の媒体を備えうる。更に、任意の接続は、厳密にはコンピュータ読み取可能な媒体と呼ばれる。例えば、ソフトウェアが、同軸ケーブル、光ファイバーケーブル、ツイストペア、デジタル加入者回線(DSL)、又は赤外線、電波、及びマイクロ波のような無線技術を使用して、ウェブサイト、サーバ、又は他の遠隔ソースから送信される場合には、この同軸ケーブル、光ファイバーケーブル、ツイストペア、DSL、又は赤外線、電波、及びマイクロ波のような無線技術は、媒体の定義に含まれる。本明細書で使用される場合、ディスク(disk)及びディスク(disc)は、コンパクトディスク(CD)、レーザーディスク(登録商標)、光ディスク、デジタル多用途ディスク(DVD)、フロッピー(登録商標)ディスク、及びブルーレイ(登録商標)ディスクを含み、ここで、ディスク(disk)は、通常磁気的にデータを再生し、ディスク(disc)は、レーザーを用いて光学的にデータを再生する。上記の組み合わせもまた、コンピュータ可読媒体の適用範囲内に含まれるべきである。

。

### 【0036】

[0040] 開示された例示的な実施形態の説明は、当業者であれば本発明の製造又は使用を可能にするために提供される。これら例示的な実施形態への様々な修正は、当業者には容易に明らかであり、本明細書で定義された包括的な原理は、本発明の精神又は適用範囲から逸脱することなく他の実施形態にも適用されうる。このように、本発明は、本明細書に示された例示的な実施形態に限定されるものであることを意図せず、本明細書で開示された原理及び新規な特徴と一致する最も広い範囲を与えるべきである。

以下に本願発明の当初の特許請求の範囲に記載された発明を付記する。

#### [C1]

増幅器の出力端子と回路接地との間に選択的に接続され、且つ、増幅帯域を第1の周波数帯域から第2の周波数帯域に調節するように構成された第1の帯域選択回路と、前記第1の帯域選択回路と前記回路接地との間に選択的に接続され、且つ、前記増幅帯域が前記第1の周波数帯域に設定されたときに、前記第1の周波数帯域に関連付けられた第二高調波周波数を低減させるように構成された第1の高調波低減回路とを備える装置。

#### [C2]

前記増幅帯域を前記第1の周波数帯域に設定するように構成された第2の帯域選択回路を更に備え、前記第2の帯域選択回路は、前記出力端子と電源電圧との間に接続された第1のインダクタと、前記出力端子と前記回路接地との間に接続された第1のキャパシタとを備える、C1に記載の装置。

#### [C3]

前記第1の帯域選択回路は、前記出力端子に接続された第1のインダクタと、

10

20

30

40

50

前記第1のインダクタに接続された第1のキャパシタと、

前記増幅帯域を前記第2の周波数帯域に設定するために前記第1のキャパシタを前記

回路接地に選択的に接続するように構成されたスイッチと

を備える、C1に記載の装置。

## [ C 4 ]

前記第1の高調波低減回路は、

前記第1のインダクタに接続された第2のキャパシタと、

前記増幅帯域が前記第1の周波数帯域に設定されたときには、前記第1の周波数帯域

における前記第二高調波周波数の低減をイネーブルにし、前記増幅帯域が前記第2の周波

数帯域に設定されたときには、前記第2の周波数帯域の前記中央周波数を同調するために

、前記第2のキャパシタを前記回路接地に選択的に接続するように構成されたスイッチと

を備える、C3に記載の装置。

## [ C 5 ]

前記増幅器は、第1のトランジスタ及び第2のトランジスタを備え、前記出力端子は、

前記第1のトランジスタのドレイン端子に接続される、C1に記載の装置。

## [ C 6 ]

前記第2のトランジスタのソース端子に結合され、前記増幅帯域が前記第2の周波数帯

域に設定されたときに第二高調波周波数を低減させるように構成された第2の高調波低減

回路を更に備える、C5に記載の装置。

## [ C 7 ]

前記第2の高調波低減回路は、

前記第2のトランジスタの前記ソース端子と、前記回路接地との間に接続されたイン

ダクタと、

前記第2のトランジスタの前記ソース端子と前記回路接地との間に接続されたキャパ

シタと

を備える、C6に記載の装置。

## [ C 8 ]

前記第1の周波数帯域は、前記第2の周波数帯域の第2の中央周波数よりも周波数が低

い第1の中央周波数を有する、C1に記載の装置。

## [ C 9 ]

増幅器の増幅帯域を第1の周波数帯域から第2の周波数帯域に調節するための手段と、

調節するための前記手段は、前記増幅器の出力端子と回路接地との間に選択的に接続され

る、

前記増幅帯域が前記第1の周波数帯域に設定されたときに、前記第1の周波数帯域にお

ける第二高調波周波数を低減させるための手段と、低減させるための前記手段は、調節す

るための前記手段と前記回路接地との間に接続される、

を備える装置。

## [ C 10 ]

前記増幅器の前記増幅帯域を前記第1の周波数帯域に設定するための手段を更に備え、

設定するための前記手段は、

前記出力端子と電源電圧との間に接続された第1のインダクタと、

前記出力端子と前記回路接地との間に接続された第1のキャパシタと

を備える、C9に記載の装置。

## [ C 11 ]

調節するための前記手段は、

前記出力端子に接続された第1のインダクタと、

前記第1のインダクタに接続された第1のキャパシタと、

前記増幅帯域を前記第2の周波数帯域に設定するために、前記第1のキャパシタを前

記回路接地に選択的に接続するように構成されたスイッチと

を備える、C9に記載の装置。

10

20

30

40

50

## [ C 1 2 ]

低減させるための前記手段は、

前記第1のインダクタに接続された第2のキャパシタと、

前記増幅帯域が前記第1の周波数帯域に設定されたときには、前記第1の周波数帯域における前記第二高調波周波数の低減をイネーブルにし、前記増幅帯域が前記第2の周波数帯域に設定されたときには、前記第2の周波数帯域の前記中央周波数を同調するために、前記第2のキャパシタを前記回路接地に選択的に接続するように構成されたスイッチとを備える、C 1 1に記載の装置。

## [ C 1 3 ]

前記増幅器は、第1のトランジスタ及び第2のトランジスタを備え、前記出力端子は、前記第1のトランジスタのドレイン端子に接続される、C 9に記載の装置。

10

## [ C 1 4 ]

前記第2のトランジスタのソース端子に接続され、且つ、前記増幅帯域が前記第2の周波数帯域に設定されたときに第二高調波周波数を低減させるように構成されたトラップするための手段を更に備える、C 1 3に記載の装置。

## [ C 1 5 ]

トラップするための前記手段は、

前記第2のトランジスタの前記ソース端子と、前記回路接地との間に接続されたインダクタと、

前記第2のトランジスタの前記ソース端子と前記回路接地との間に接続されたキャパシタと

20

を備える、C 1 4に記載の装置。

## [ C 1 6 ]

前記第1の周波数帯域は、前記第2の周波数帯域の第2の中央周波数よりも周波数が低い第1の中央周波数を有する、C 9に記載の装置。

## [ C 1 7 ]

方法であって、

増幅器の増幅帯域が低周波数帯域に設定されることとなるか高周波数帯域に設定されこととなるかを決定することと、

前記増幅帯域が前記低周波数帯域に設定されることとなる場合には、第1の帯域選択回路をイネーブルにし、第2の帯域選択回路をディセーブルにすることと、

30

前記増幅帯域が前記高周波数帯域に設定されることとなる場合には、前記第1の帯域選択回路をイネーブルにし、前記第2の帯域選択回路をイネーブルにすることと、

を備える方法。

## [ C 1 8 ]

前記増幅帯域が前記低周波数帯域に設定されることとなる場合に、低帯域トラップ回路がイネーブルにされることとなるかどうかを決定することと、

前記低帯域トラップ回路がイネーブルにされることとなる場合に、前記低周波数帯域に関連付けられた第二高調波周波数を低減させるために前記低帯域トラップ回路をイネーブルにすることと

40

を更に備える、C 1 7に記載の方法。

## [ C 1 9 ]

前記増幅帯域が前記高周波数帯域に設定されることとなる場合に、前記高周波数帯域に関連付けられた第二高調波周波数を低減させるために高帯域トラップ回路をイネーブルにすることを更に備える、C 1 7に記載の方法。

## [ C 2 0 ]

前記低周波数帯域は、前記高周波数帯域の第2の中央周波数よりも周波数が低い第1の中央周波数を有する、C 1 7に記載の方法。

【図1】

FIG. 1

【図2】

FIG. 2

【図3】

FIG. 3

【図4】

FIG. 4

【図5】

図5

FIG. 5

---

フロントページの続き

(72)発明者 フェン、ハイガン

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72)発明者 パニッカス、ビノド・ブイ・

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72)発明者 サンカラナラヤナン、ジャナキラム・ジー・

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

(72)発明者 アスリ、ブーシャン・シャンティ

アメリカ合衆国、カリフォルニア州 92121、サン・ディエゴ、モアハウス・ドライブ 57

75

審査官 緒方 寿彦

(56)参考文献 特開平07-263980(JP, A)

米国特許第07764125(US, B1)

特開平09-260963(JP, A)

特開2007-110685(JP, A)

国際公開第2008/136080(WO, A1)

国際公開第2007/099622(WO, A1)

米国特許第07202734(US, B1)

米国特許出願公開第2008/0020947(US, A1)

(58)調査した分野(Int.Cl., DB名)

H03F 1/00 - 3/45, 3/50 - 3/52,

3/62 - 3/64, 3/68 - 3/72