(19) 대한민국특허청(KR)

(12) 등록특허공보(B1)

(51) Int. Cl.

H01L 21/30 (2006.01)

(45) 공고일자

2007년03월09일

(11) 등록번호

10-0691706

(24) 등록일자

2007년02월28일

(21) 출원번호 10-2005-0033431

(22) 출원일자 2005년04월22일

심사청구일자 2005년04월22일

(65) 공개번호 10-2006-0047389

(43) 공개일자 2006년05월18일

(30) 우선권주장 04 102 36.4 2004년05월07일 영국(GB)

(73) 특허권자 세이코 앱슨 가부시키가이샤

일본 도쿄도 신주쿠구 니시신주쿠 2초메 4-1

(72) 발명자 리, 슐푸

영국 캠브리지 씨비4 0에프이 밀턴 로드 캠브리지 싸이언스 파크 9에이

캠브리지 리씨치 래버리토리 오브 앱슨 내

뉴섬, 크리스토퍼

영국 캠브리지 씨비4 0에프이 밀턴 로드 캠브리지 싸이언스 파크 9에이

캠브리지 리씨치 래버리토리 오브 앱슨 내

쿠글러, 토마스

영국 캠브리지 씨비4 0에프이 밀턴 로드 캠브리지 싸이언스 파크 9에이

캠브리지 리씨치 래버리토리 오브 앱슨 내

러셀, 테이비드

영국 캠브리지 씨비4 0에프이 밀턴 로드 캠브리지 싸이언스 파크 9에이

캠브리지 리씨치 래버리토리 오브 앱슨 내

(74) 대리인 문두현

문기상

(56) 선행기술조사문헌

KR 10-270497B1 \*

\* 심사관에 의하여 인용된 문헌

심사관 : 송현정

전체 청구항 수 : 총 30 항

(54) 전자 기능 재료를 원하는 패턴으로 제조하는 방법

(57) 요약

본 발명은 기판(1)상에 전자 기능 재료(3)를 원하는 패턴으로 형성하는 방법을 제공한다. 본 발명의 방법은 기판 상에, 원하는 패턴이 형성되도록 기판의 일부분이 노출되게 남겨두고 패터닝 재료(2)의 제1층을 형성하는 공정; 상기 패터닝 재료에 스며들지 않고 액체 분산제(liquid dispersant) 중에 전자 기능 재료(3)의 입자를 포함하는 혼탁액을, 상기 패터닝 재료 및 노출된 기판상에 프린팅하는 공정; 상기 입자들이 압밀(consolidate)되도록 상기 액체 분산제의 적어도 일부를 상기 혼탁액으로부터 제거하는 공정; 및 상기 압밀 입자에, 상기 패터닝 재료를 용해할 수 있고 상기 압밀 입자를 투과하여 상기 패터닝 재료와 그 위에 덮힌 전자 기능 재료를 함께 기판으로부터 제거하는 제1 용제를 도포하는 공정을 포함한다.

## 대표도

도 6

## 특허청구의 범위

### 청구항 1.

기판 상에 패터닝 재료의 제1층을 제조하는 공정;

상기 패터닝 재료에 스며들지 않고 액체 분산제 중에 전자 기능 재료의 입자를 포함하는 혼탁액을, 상기 패터닝 재료 및 상기 제1층이 형성되지 않은 기판의 노출된 영역상에 프린팅하는 공정;

상기 입자들이 압밀(consolidate)되도록 상기 분산제의 적어도 일부를 상기 혼탁액으로부터 제거하는 공정; 및

상기 압밀 입자에, 상기 패터닝 재료를 용해할 수 있고 상기 압밀 입자를 투과하는 제1 용제를 도포하여, 상기 패터닝 재료를 제거하는 공정;을 포함하는, 기판 상에 전자 기능 재료를 원하는 패턴으로 형성하는 방법.

### 청구항 2.

제1항에 있어서,

상기 패터닝 재료를 제거하는 공정 동안, 상기 패터닝 재료를 덮고 있는 전자 기능 재료가 상기 기판으로부터 제거되는, 기판 상에 전자 기능 재료를 원하는 패턴으로 형성하는 방법.

### 청구항 3.

제2항에 있어서,

상기 패터닝 재료가 포토레지스트이고, 상기 원하는 패턴이 상기 포토레지스트층을 퇴적한 다음 포토리소그래피에 의해 포토레지스트의 선택된 부분을 제거함으로써 형성되어 제1층을 제조하는, 기판 상에 전자 기능 재료를 원하는 패턴으로 형성하는 방법.

### 청구항 4.

제2항에 있어서,

상기 패터닝 재료가 열가소성 중합체이고, 상기 원하는 패턴이 열가소성 중합체층을 퇴적한 다음 그 층을 마이크로엠보싱 함으로써 형성되어 제1층을 제조하는, 기판 상에 전자 기능 재료를 원하는 패턴으로 형성하는 방법.

### 청구항 5.

제4항에 있어서,

상기 열가소성 중합체가 폴리메틸메타크릴레이트인, 기판 상에 전자 기능 재료를 원하는 패턴으로 형성하는 방법.

### 청구항 6.

제2항 내지 제5항 중 어느 한 항에 있어서,

상기 전자 기능 재료의 혼탁액이 콜로이드상인, 기판 상에 전자 기능 재료를 원하는 패턴으로 형성하는 방법.

### 청구항 7.

제2항에 있어서,

상기 혼탁액이 액적 형태로 토출되어 프린팅되는, 기판 상에 전자 기능 재료를 원하는 패턴으로 형성하는 방법.

### 청구항 8.

제2항에 있어서,

상기 혼탁액으로부터 상기 액체 분산제의 적어도 일부의 제거는 실온에서 건조시키거나, 열 접촉에 의해 가열, 마이크로파 방사, 입사 적외선 방사 또는 프린팅된 혼탁액을 대기압보다 저압에 둠에 의해 가속건조시킴으로써 행하는, 기판 상에 전자 기능 재료를 원하는 패턴으로 형성하는 방법.

### 청구항 9.

제2항에 있어서,

상기 액체 분산제가 물인, 기판 상에 전자 기능 재료를 원하는 패턴으로 형성하는 방법.

### 청구항 10.

제2항에 있어서,

상기 제1 용제가 아세톤인, 기판 상에 전자 기능 재료를 원하는 패턴으로 형성하는 방법.

### 청구항 11.

제2항에 있어서,

상기 전자 기능 재료가 젤연체인, 기판 상에 전자 기능 재료를 원하는 패턴으로 형성하는 방법.

### 청구항 12.

제11항에 있어서,

상기 절연체가 이산화규소, 마이카, 라텍스 또는 유전성 중합체인, 기판 상에 전자 기능 재료를 원하는 패턴으로 형성하는 방법.

### 청구항 13.

제2항에 있어서,

상기 전자 기능 재료가 반도체인, 기판 상에 전자 기능 재료를 원하는 패턴으로 형성하는 방법.

### 청구항 14.

제13항에 있어서,

상기 반도체가 카본 나노튜브류, 층상 전이 금속 디칼코게나이드의 플레이크류, 웬타센 입자류 또는 유기 반도체 중합체인, 기판 상에 전자 기능 재료를 원하는 패턴으로 형성하는 방법.

### 청구항 15.

제14항에 있어서,

상기 유기 반도체 중합체가 폴리-3-헥실티오펜인, 기판 상에 전자 기능 재료를 원하는 패턴으로 형성하는 방법.

### 청구항 16.

제2항에 있어서,

상기 전자 기능 재료가 도체인, 기판 상에 전자 기능 재료를 원하는 패턴으로 형성하는 방법.

### 청구항 17.

제16항에 있어서,

상기 도체가 금속, 인듐 주석 산화물, 주석 산화물, 폴리티오펜, 폴리아닐린 또는 폴리피롤인, 기판 상에 전자 기능 재료를 원하는 패턴으로 형성하는 방법.

### 청구항 18.

제17항에 있어서,

상기 폴리티오펜이 폴리(3,4-에틸렌디옥시티오펜)-폴리스티렌설폰산인, 기판 상에 전자 기능 재료를 원하는 패턴으로 형성하는 방법.

### 청구항 19.

제18항에 있어서,

상기 압밀입자를, 제1 용제를 도포한 후 N-메틸피롤리돈 및 이소프로판올에 용해된 D-솔비톨로 처리하는 공정을 더 포함하는, 기판 상에 전자 기능 재료를 원하는 패턴으로 형성하는 방법.

### 청구항 20.

제18항에 있어서,

상기 압밀 입자를, 제1 용제로 처리한 후 가교제를 함유하는 제2 용제로 처리하는 공정을 더 포함하는, 기판 상에 전자 기능 재료를 원하는 패턴으로 형성하는 방법.

### 청구항 21.

제19항 또는 제20항에 있어서,

상기 압밀 입자를, 처리 후 그 표면을 매끄럽게 하기 위해서 어닐링하는, 기판 상에 전자 기능 재료를 원하는 패턴으로 형성하는 방법.

### 청구항 22.

제16항에 기재된 방법에 의해 기판 상에 도체를 원하는 패턴으로 형성하는 공정을 포함하는 전계 효과 트랜지스터의 제조 방법으로서, 상기 패턴은 소스 및 드레인 전극을 형성하고, 소스 및 드레인 전극과 전기적 접촉하는 반도체층을 퇴적하고, 그 반도체층상에 절연체층을 퇴적하고, 그 절연체층상에 게이트 전극을 마련하는, 전계 효과 트랜지스터의 제조 방법.

### 청구항 23.

제22항에 있어서,

상기 절연체층이 제11항 또는 제12항 기재의 방법에 의해 퇴적되고, 및/또는 상기 반도체층은 제13항 내지 제15항 중 어느 한 항 기재의 방법에 의해 퇴적되는, 전계 효과 트랜지스터의 제조 방법.

### 청구항 24.

제22항에 있어서,

상기 반도체층은 액적 형태로 토출 또는 패드 프린팅(pad-printing)에 의해 퇴적되는, 전계 효과 트랜지스터의 제조 방법.

### 청구항 25.

제22항 또는 제24항에 있어서,

상기 절연체층이 액적 형태로 토출 또는 패드 프린팅에 의해 퇴적되는, 전계 효과 트랜지스터의 제조 방법.

### 청구항 26.

각 전계 효과 트랜지스터가 제22항 기재의 방법에 의해 제조되는, 통상의 기판상에 제조된 전계 효과 트랜지스터의 어레이.

### 청구항 27.

제22항에 있어서,

상기 게이트 전극이 액적 형태로 토출 또는 패드 프린팅에 의해 퇴적되는 전계 효과 트랜지스터의 제조 방법.

### 청구항 28.

제22항에 있어서,

상기 반도체층이 유기 반도체 중합체로 형성되는 전계 효과 트랜지스터의 제조 방법.

### 청구항 29.

제22항에 있어서,

상기 절연체층이 폴리메틸메타크릴레이트로 형성되는 전계 효과 트랜지스터의 제조 방법.

### 청구항 30.

제22항에 있어서,

상기 게이트 전극이 폴리(3,4-에틸렌디옥시티오펜)-폴리스티렌설폰산으로 형성되는 전계 효과 트랜지스터의 제조 방법.

## 명세서

### 발명의 상세한 설명

#### 발명의 목적

#### 발명이 속하는 기술 및 그 분야의 종래기술

본 발명은 기판상에 전자 기능 재료(electronically functional material)를 원하는 패턴으로 제조하는 방법에 관한 것으로서, 전자 기능 재료를 상기 패턴으로 삽입한(incorporating) 박막 트랜지스터의 제조에 적용할 수 있다.

통상, 전자 기능 재료는 주로 포토리소그래피를 이용하여 패터닝된다. 이 기술에 의하면 기판상에 매우 고해상도의 부품(high-resolution component)들이 형성된다. 포토리소그래피는 설비 비용이 높고, 다수의 프로세싱 단계를 필요로 하고, 다량의 원료를 필요로 하는 주요 단점이 있으므로, 바람직하지 못한 기술이다.

종래, 프린팅에 의한 재료의 퇴적(deposition)에 의해 기판상에 전자 장치를 제조하는 방법이 공지되어 있다. 현재 이 방법들은 프로세싱 비용을 줄이기 위해서, 더 발전되고 있으며, 그 중의 하나가 앱슨의 마이크로리퀴드 기술(micro-liquid technology)이다. 프린팅에 의한 퇴적은 사실상 부가적(additive)이기 때문에, 포토리소그래피법보다 전자 기능 재료와

프로세싱 단계를 더 적게 필요로 한다. 그러나, 마이크로리퀴드 기술은 현시점까지 포토리소그래피에 비해 2개의 주요한 단점을 가지고 있다. 첫째, 프리-포맷 마이크로리퀴드 기술에서 성취할 수 있는 해상도가 포토리소그래피에 의해 성취할 수 있는 해상도보다 뒤떨어진다. 둘째, 프린팅 헤드로부터 그들의 정확한 토출이 만족스럽게 달성되는 잉크 제제(ink formulation)을 제공하기 어렵다. 하지만 잉크의 퇴적 및 건조 후, 얻어진 재료의 전자 성능은 박막 트랜지스터 등의 전자 부품의 제조용으로 적당히 높다.

### 발명이 이루고자 하는 기술적 과제

본 발명의 목적은 포토리소그래피 기술의 상기 요구는 감소시키지만, 그 고해상도 성능은 유지하는 패터닝 방법을 제공하는 것이다.

본 발명의 또다른 목적은 정확한 퇴적을 위해 잉크 제제를 최적화시킬 필요가 없는 프린팅법을 채용하는 패터닝 방법을 제공하는 것이며, 그로 인해 잉크 제제가 그 얻어진 재료의 전자 성능에 대해 최적화되게 된다.

### 발명의 구성

넓은 관점에서, 본 발명은 기판 상에, 원하는 패턴이 형성되도록 기판의 일부분이 노출되게 남겨두고 패터닝 재료의 제1층을 형성하는 공정; 상기 패터닝 재료에 스며들지 않고 액체 분산체 중에 전자 기능 재료의 입자를 포함하는 혼탁액을, 상기 패터닝 재료 및 노출된 기판상에 프린팅하는 공정; 상기 입자들이 압밀(consolidate)되도록 상기 액체 분산체의 적어도 일부를 상기 혼탁액으로부터 제거하는 공정; 및 상기 압밀 입자에, 상기 패터닝 재료를 용해할 수 있고 상기 압밀 입자를 투과하여 상기 패터닝 재료와 그위에 덮힌 전자 기능 재료를 함께 기판으로부터 제거하는 제1 용제를 도포하는 공정을 포함하는, 기판 상에 전자 기능 재료를 원하는 패턴으로 형성하는 방법을 제공한다.

상기 패터닝 재료와 그위에 덮힌 전자 기능 재료를 용해하여 제거하는 제1 용제를 사용함으로써, 남아있는 전자 기능 재료의 패턴이 포토리소그래피 등의 고해상도 방법에 의해 퇴적되거나, 또는 형성되는 것 만큼 정확하게 형성되게 된다.

또한, 프린팅법은 종래의 포토리소그래피에 사용되는 스펀 코팅이나 딥 코팅 등의 방법에 비해서 전자 기능 재료를 더 정확하게 퇴적할 수 있기 때문에, 상기 제거 공정 동안 전자 기능 재료가 덜 소모된다. 이러한 이점은, 프린팅법 자체는 원래 전자 기능 재료를 충분히 고해상도로 원하는 패턴에 따라 똑바로 퇴적할 만큼 충분히 정확하지 않음에도 불구하고, 여전히 명백하다.

본 명세서 중에서 "프린팅"은 "잉크젯 프린팅(ink-jet printing)" 또는 "패드 프린팅(pad-printing)" 또는 기판의 소정의 선택 영역상에 원하는 패턴을 제조하기 위해 재료층을 제어된 방식으로 퇴적할 수 있는 어떠한 다른 방법을 의미한다. "잉크젯 인쇄"은 혼탁액을 포함한, 유액을 미세 액적의 형태로 프린팅 헤드로부터 기판 상에 퇴적하는 것을 의미한다.

상기 패터닝 재료는 포토레지스트일 수 있으며, 원하는 패턴은 포토레지스트층을 퇴적하고 이어서 포토리소그래피에 의해 상기 포토레지스트의 선택된 부분을 제거하여 제1층을 생성함에 의해 형성할 수 있다. 포토리소그래피는 얻어진 전자 기능 재료의 패턴이 상기 포토레지스트를 용해하여 제거한 후에 정확하게 형성되는 고해상도 방법이다.

상기 패터닝 재료는 열 전사 프린팅(thermal transfer printing)과 유사한 방법으로 레이저 전사 기술(laser transfer technology)에 의해 선택적으로 퇴적할 수 있다.

상기 패터닝 재료는 열가소성 중합체일 수도 있으며, 그 원하는 패턴은 열가소성 중합체층을 퇴적한 다음 이것을 마이크로 엠보싱(micro-embossing)하여 제1층을 생성함에 의해 형성할 수 있다. 상기 열가소성 중합체는 증가된 온도, 즉, 액체 상태에서 마이크로 엠보싱할 수 있다. 마이크로 엠보싱도 고해상도 방법이다.

상기 열가소성 중합체는 마이크로 엠보싱에 의한 패터닝에 특히 적합한 폴리메틸메타크릴레이트일 수 있다.

전자 기능 재료의 혼탁액은 콜로이드상일 수 있다. 콜로이드는 전자 기능 재료의 패턴을 제조하는데 특히 적합하다. 상기 혼탁액 중의 전자 기능 재료의 평균 입자 크기는  $0.01\sim1\mu\text{m}$ 가 바람직하다.

상기 혼탁액은 액적 형태로 토출하여 프린팅할 수 있다(잉크젯 프린팅). 이 프린팅법은 종래의 잉크젯 프린팅법에 의해 빠르게 수행할 수 있다.

상기 프린팅된 혼탁액은 건조 공정에서 건조하여 상기 액체 분산체의 적어도 일부를 제거할 수 있다. 건조는 실온에서 행할 수 있고, 또는 가속화된 건조는 열 접촉에 의한 가열, 마이크로파 조사, 입사 적외선 방사 또는 상기 프린팅된 혼탁액을 대기압보다 낮은 압력에 둠에 의해 행할 수 있다. 이 방법들 중 어느 하나를 상기 액체 분산액의 적어도 일부를 제거하기 위해 사용할 수 있으며, 상기 가속화된 건조 방법 중의 하나를 사용하여 입자를 효과적으로 압밀하는데 걸리는 시간을 줄일 수 있다.

상기 액체 분산액은 각종 전자 기능 재료 입자에 대해 자유롭게 이용할 수 있는 효과적인 액체 분산액인 물일 수 있다.

상기 제1 용제는 에테르 또는 케톤 등의 유기 용제일 수도 있다. 다양한 종류의 패터닝 재료를 용해하는데 효과적이고 값싼 용제인 아세톤이 특히 바람직하다.

상기 전자 기능 재료는, 예를 들면, 이산화 규소, 마이카, 라텍스 또는 유전 중합체(dielectric polymer) 입자 등의 전기 절연체일 수 있다. 이 재료들 중의 어느 하나는, 예를 들면 박막 트랜지스터의 절연 부품을 형성하는데 적합하다.

상기 전자 기능 재료는 반도체, 예를 들면, 카본 나노튜브류, 카드뮴 셀레나이드 등의 화합물 반도체류, 층상 전이 금속 디칼코게나이드류(dichalcogenides), 펜타센 입자류 또는 유기 반도체성 중합체 입자일 수 있다. 상기 유기 반도체성 중합체 입자는 폴리-3-헥실티오펜일 수 있다. 이 재료들은 모두, 예를 들면 박막 트랜지스터의 반도체 부품을 형성하는데 적합하다.

상기 전자 기능 재료는 전기 전도체, 예를 들면, 금속, 인듐 주석 산화물, 산화 주석, 폴리티오펜, 폴리아닐린 또는 폴리피롤일 수 있다. 폴리티오펜은 폴리(3,4-에틸렌디옥시티오펜)-폴리스티렌설폰산일 수 있다. 이 재료들 중의 어느 하나는, 예를 들면 박막 트랜지스터의 부품을 형성하는데 적합하다.

상기 전자 기능 재료가 폴리(3,4-에틸렌디옥시티오펜)-폴리스티렌설폰산인 경우, 상기 압밀 입자는 제1 용제를 도포한 후에 N-메틸페롤리돈과 이소프로판올에 용해된 D-솔비톨로 처리할 수 있다. 이러한 처리는 폴리(3,4-에틸렌디옥시티오펜)-폴리스티렌설폰산의 얻어진 패턴의 전기 컨덕턴스를 증강시킨다.

상기 전자 기능 재료가 폴리(3,4-에틸렌디옥시티오펜)-폴리스티렌설폰산인 경우, 상기 압밀 입자는, 상기 제1 용제를 도포한 후에, 실퀘스트(Silquest(상표명)) 등의 가교제를 함유하는 제2 용제로 처리할 수 있다. 이러한 처리 방법은 상기 폴리(3,4-에틸렌디옥시티오펜)-폴리스티렌설폰산의 기계적 특성을 향상시킨다.

상기 압밀 입자를, 폴리(3,4-에틸렌디옥시티오펜)-폴리스티렌설폰산으로 형성했을 때에는, 압밀 입자가 처리된 후에 상기 전자 기능 재료의 패턴의 표면을 매끄럽게 하기 위해 어닐링할 수 있다. 어닐링은 상기 압밀 입자로부터 잔류하는 용제를 제거하며, 그 결과 더 컴팩트한 몰풀로지와 증가된 전기 전도성을 갖게 된다.

상기 전자 기능 재료가 도체인 경우, 상기 원하는 패턴은 전계 효과 트랜지스터(field effect transistor)의 제조 시에 소스 및 드레인 전극 형태를 취하며, 그 제조 프로세스는 소스 전극 및 드레인 전극과 전기적으로 접촉하는 반도체층을 퇴적하는 공정, 반도체층 위에 절연체층을 퇴적하는 공정 및 절연체층 위에 게이트 전극을 마련하는 공정을 포함한다. 이러한 전계 효과 트랜지스터는 빠르고 정확하게 제조할 수 있다.

상기 전계 효과 트랜지스터는 상기한 방식으로 원하는 패턴의 절연체를 퇴적 및/또는 상기한 방식으로 원하는 패턴의 반도체를 퇴적함으로써 제조할 수 있다. 이렇게, 상기 반도체 및/또는 절연체는 소스 및 드레인 전극 만큼 정확하게 퇴적될 수 있다.

상기 반도체층은 액적 형태의 토출(잉크젯 프린팅)이나 패드 프린팅에 의해 퇴적할 수 있는 폴리-3-헥실티오펜 등의 유기 반도체성 중합체로 형성할 수 있고; 상기 절연체층은 액적 형태로 토출하거나 패드 프린팅에 의해 퇴적할 수 있는 폴리메틸메타크릴레이트로 형성할 수 있고; 또한 상기 게이트 전극은 액적 형태로 토출하거나 패드 프린팅에 의해 퇴적할 수 있는 폴리(3,4-에틸렌디옥시티오펜)-폴리스티렌설폰산으로 형성할 수 있다. 이들 재료 각각 및 그 퇴적 방법은 전계 효과 트랜지스터를 정확하게 제조하고자 하는 그들의 목적을 잘 만족시킨다. 하지만, 각 재료에 대해서 어떠한 퇴적 방법이라도 사용할 수 있다.

전계 효과 트랜지스터의 어레이에는 반도체층들이 액적 형태의 토출이나 패드 프린팅에 의해 각각 퇴적되는 통상의 기판 상에 제조될 수 있다. 액적 형태의 토출, 패드 프린팅 또는 본 발명에 의해 제공되는 패턴 형성 방법 등의 정확한 프린팅법을 사용함으로써, 반도체 패턴이 인접한 전계 효과 트랜지스터를 덮고 있는 반도체층과의 전기적 접촉없이, 하나의 전계 효과 트랜지스터의 소스 및 드레인 전극을 덮을 수 있도록 퇴적된다.

전계 효과 트랜지스터의 어레이에는 절연체층들이 액적 형태의 토출이나 패드 프린팅에 의해 각각 퇴적되는 통상의 기판 상에 제조할 수 있다. 액적 형태의 토출, 패드 프린팅 또는 본 발명에 의해 제공되는 패턴 형성 방법 등의 정확한 프린팅 방법을 사용함으로써, 절연체층이 인접한 전계 효과 트랜지스터를 덮고 있는 반도체층과의 전기적 접촉없이, 단지 하나의 전계 효과 트랜지스터의 소스 및 드레인 전극 및 반도체층을 덮을 수 있도록 퇴적된다. 이때, 상기 소스 및 드레인 전극 각각의 일부는 노출되어 남겨지고, 하나의 전계 효과 트랜지스터의 드레인 전극과 인접한 전계 효과 트랜지스터의 게이트 전극 사이의 전기적 커넥션은 홀을 거쳐 제조하거나 다른 파괴 프로세스(destructive process)를 사용할 필요없이 퇴적될 수 있다.

이렇게 잘 형성된 전자 기능 재료의 패턴은 기타 전자, 자기 및 광학 회로류, 바이오칩류 및 초소형 전자 기계 시스템류 (microelectronic mechanical systems)에도 적합하다.

본 명세서에서, "PEDOT:PSS"는 폴리(3,4-에틸렌디옥시티오펜)-폴리스티렌설폰산을 의미하고; "PMMA"는 폴리메틸메타크릴레이트를 의미하고; "P3HT"는 폴리-3-헥실티오펜을 의미한다.

본 발명을 더 잘 이해하고 더 효과적으로 실행할 수 있는 방법을 나타내기 위해, 단지 실시예에 의해 첨부한 도면을 참조하여 설명한다.

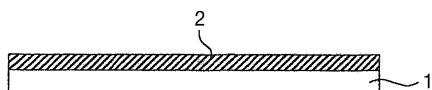

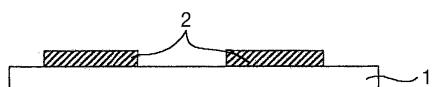

우선 도 1을 참고하면, 유리로 형성된 기판(1)이 S1818 포토레지스트층(2)(Shipley UK제)으로 덮여있다. 포토리소그래피법에 의해 상기 포토레지스트 재료(2)의 일부를 제거함으로써 원하는 패턴을 형성하여, 도 2에 나타낸 패턴을 얻는다.

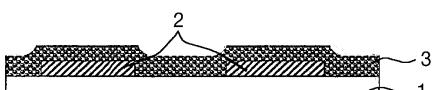

평균 직경이 약 100nm이고 물을 분산제로 하는 PEDOT:PSS 콜로이드상 입자층(3)을 평균 입경이 30μm인 액적 형태로, 기판(1)과 포토레지스트 재료(2) 상에, 잉크젯 프린팅이라 불리는 프로세스에 의해 토출한 다음, 건조 공정을 거쳐 상기 입자를 압밀한다. 그 결과 얻어진 층의 두께는 약 300nm 이다.

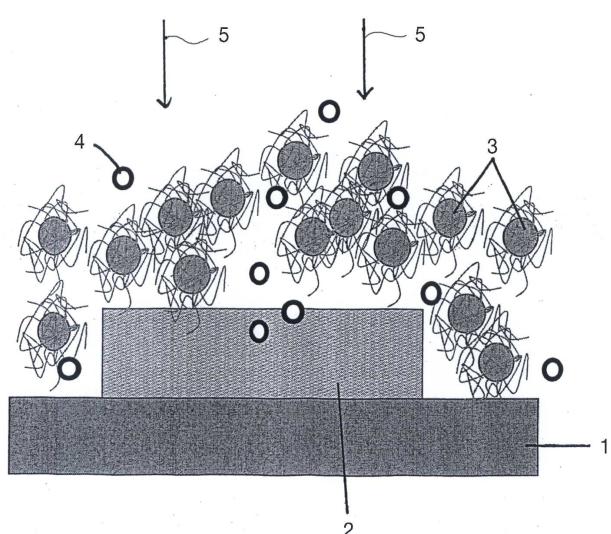

상기 PEDOT:PSS의 압밀 입자층(3)은 소량의 물을 함유한다. 도 4는 물 분자(4)에 산재해 있는 PEDOT:PSS 입자(3)를 나타낸다. 그 다음 PEDOT:PSS 층(3)을 아세톤(5)으로 적신다. PEDOT:PSS 층(3) 중의 물 분자(4)의 존재에 의해 느슨하게 패킹된 저밀도 물풀로지가 확보된다. 상기 물풀로지는 아세톤 분자(도시하지 않음)의 포토레지스트(2)로의 통과를 용이하게 한다. 아세톤(5)은 포토레지스트(2)를 용해하여 제거하며, 그 결과 포토레지스트(2)를 직접 덮고 있는 PEDOT:PSS(3) 부분도 제거된다.

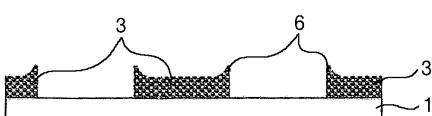

도 5는 기판(1)상의 얻어진 PEDOT:PSS 패턴을 나타낸다. 포토레지스트층(2)의 제거에 의해 PEDOT:PSS(3)의 첨단에 거칠고 날카로운 에지(edge)(6)가 남는다. 그 다음 PEDOT:PSS(3)를 메틸피롤리돈 및 이소프로판올에 용해된 D-솔비톨로 처리한 후, 불활성 용제 중의 실퀘스트(상표명)로 처리한다. 그 다음, 상기 에지(6)를 100~200°C의 어닐링 공정에서 매끄럽게 한다. 도 6은 매끄럽게 한 후 얻어진 PEDOT:PSS(3)의 패턴을 나타낸다.

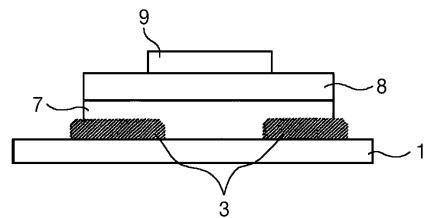

얻어진 PEDOT:PSS(3)의 패턴은 전계 효과 트랜지스터 제조용 소스 및 드레인 전극을 구성한다. 전계 효과 트랜지스터는 도 7에 나타내며, 두께 40nm의 P3HT층(7)은 PEDOT:PSS 소스 및 드레인 전극(3) 위에 그들간에 전기적으로 접촉하도록 프린팅에 의해 퇴적된다. 두께 600nm의 PMMA층(8)은 P3HT층(7) 위에 프린팅에 의해 퇴적되고, 최종적으로 두께 300nm의 또다른 PEDOT:PSS 층(9)이 프린팅에 의해 퇴적된다. P3HT층(7)은 반도체층을 구성하고, PMMA층(8)은 절연체층을 구성하고, PEDOT:PSS층(9)은 게이트 전극을 구성한다.

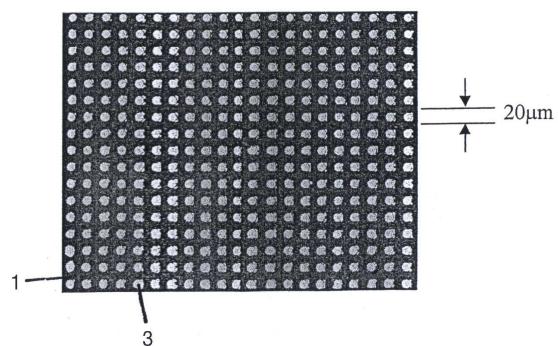

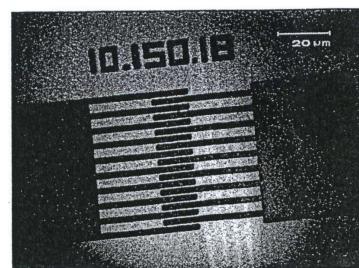

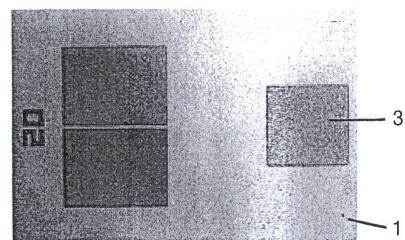

도 8은 패터닝 재료가 포토레지스트인 본 발명의 실시 형태에 의해 제조된 PEDOT:PSS 패턴을 나타낸다.

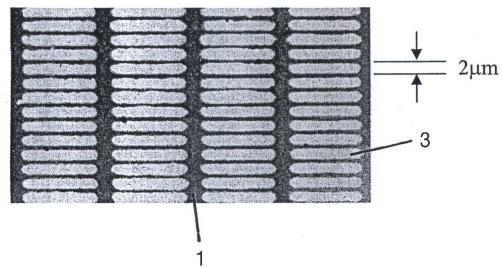

도 9 및 10은 본 발명의 실시 형태에 의해 제조된 대표적인 소스-드레인 전극 구조를 나타낸다.

본 발명의 또다른 실시 형태에서, 패터닝 재료는 PMMA 등의 열가소성 중합체일 수 있으며, 이들은 마이크로엠보싱에 의해 패터닝되며 두께가 300nm이다. 포토레지스트층(2)이 열가소성 중합체로 대체된 것을 제외하고는 도 2에 나타낸 것과 유사한 구조가 이 실시 형태에서 얻어진다.

도 11 및 12는 본 발명의 또다른 실시 형태에 의한 방법을 사용하여 제조된 PEDOT:PSS(3) 패턴을 나타내며, 그 패터닝 재료는 PMMA이고, 마이크로엠보싱에 의해 패터닝된다.

액체 분산제 중의 전자 기능 재료의 콜로이드는 금속, 인듐 주석 산화물, 주석 산화물, 폴리아닐린, 폴리피롤; 실리콘, 게르마늄, 셀레늄, 카본 나노튜브,  $C_{60}$  등의 원소 반도체류; 층상 전이금속 디칼코게나이드, 갈륨 비소(GaAs), 인듐 인(InP)의 플레이크류 등의 화합물 반도체류; 웨타센 입자류 등의 소분자 유기 반도체류; 유기 반도체 중합체 입자류; 또는 이산화규소, 마이카, 라텍스 또는 유전 중합체 입자 등의 절연체류의 콜로이드일 수 있다.

상기 전자 기능 재료가 금속 콜로이드일 때, 적합한 포스트 패터닝 처리는 씨멀 어닐링이며, 그 결과 도전성이 크게 증가한다. 전자 기능 재료가 폴리아닐린일 때, 적합한 포스트 패터닝 처리는 m-크레졸로 처리함에 의한 "2차 도핑"이며 그 결과 도전성이 크게 증가한다.

표준 포토리소그래피법에서 중합체를 제거하기 위해 과거에 사용해 온 몇몇 에칭액은 그 위를 덮고 있는 포토레지스트층을 부풀리거나, 심지어 제거하는 경향이 있으며, 그로 인해 하부 중합체의 패턴에 원하지 않는 데미지를 준다. 이러한 문제는 산소 플라즈마 에칭을 이용하여 극복할 수 있지만, 이 방법은 고가의 장비를 필요로 한다. 절연체류, 반도체류 또는 도체류 등 중합체류의 패터닝을 위해 본 발명에 의해 제공된 패터닝 방법을 사용함으로써, 상기한 에칭액을 사용할 필요가 없어진다. 아세톤 등의, 포토레지스트층을 용해하기 위해 사용할 수 있는 에칭액 종류들은 패터닝 중합체로서의 용도에 적합한 중합체 종류들에 영향을 미칠 정도로 공격적이지는 않다. 또한 산소 플라즈마법을 사용할 필요도 없어진다.

여기에 기재하는 방법들은 전자 부품을 제조하는 공지의 접근법의 이점을 나타낸다. 고성능으로 제제화된 입자계 "잉크", 프리폼 전자 기능 재료들은 미리 패터닝된 구조상에 어떠한 프린팅법에 의해 퇴적될 수 있다. 잉크젯 프린팅의 경우, 혼탁액의 매우 정확한 퇴적이 요구되지 않기 때문에, 전자 기능 재료 입자를 포함하는 혼탁액의 토출 특성이 공지의 마이크로리퀴드 기술보다 훨씬 덜 중요하다. 또한, 잉크젯 프린팅보다 패드 프린팅이 더 나을 경우에는 패드 프린팅에 의해 적합한 잉크를 프린팅할 수 있다. 여기서 기재하는 방법들은 배치식 또는 연속식 웹 프로세스(batch or continuous web process) 둘다에서, 넓은 영역의, 대량 생산에 대한 고해상 능력과 잠재성을 갖는다.

본 발명의 방법들을 그들의 실시 형태를 참조하여 설명하였으나, 당업자는 첨부한 청구항에 규정된 바와 같은 본 발명으로부터 벗어나지 않는 범위에서 그 형태와 상세한 내용에서의 다양한 변화를 줄 수 있다는 것을 알 수 있다.

### 발명의 효과

본 발명에 의하면, 기판상에 전자 기능 재료(electronically functional material)를 원하는 패턴으로 제조하는 방법을 제공할 수 있다. 본 발명은 포토리소그래피 기술의 상기 요구는 감소시키지만, 그 고해상도 성능은 유지하는 패터닝 방법을 제공할 수 있으며, 또한, 정확한 퇴적을 위해 잉크 제제를 최적화시킬 필요가 없는 프린팅법을 채용하는 패터닝 방법을 제공할 수 있다.

### 도면의 간단한 설명

도 1은 본 발명의 실시 형태에 의한 제1 제조 단계에서의 기판의 측면도.

도 2는 제2 제조 단계에서의 도 1의 기판을 나타내는 도면.

도 3은 제3 제조 단계에서의 도 1의 기판을 나타내는 도면.

도 4는 도 3에 나타낸 제3 제조 단계의 기판을 아세톤에 침지한 측면도.

도 5는 제4 제조 단계에서의 도 1의 기판의 측면도.

도 6는 제5 제조 단계에서의 도 1의 기판의 측면도.

도 7은 제5 제조 단계에서의 도 1의 기판으로부터 제조된 전계 효과 트랜지스터의 개략도.

도 8은 포토리소그래피에 의해 제거되는 포토레지스트를 사용하여 제조된 PEDOT:PSS 패턴을 가진 기판의 평면도.

도 9 및 10은 본 발명에 의해 제조된 대표적인 소스-드레인 전극 구조의 평면도.

도 11은 본 발명의 또다른 실시 형태에 의해 PMMA 및 마이크로엠보싱을 사용하여 제조된 PEDOT:PSS 패턴을 가진 기판의 평면도.

도 12는 본 발명의 또다른 실시 형태에 의해 PMMA 및 마이크로엠보싱을 사용하여 제조된 PEDOT:PSS의 또다른 패턴을 가진 기판의 평면도.

도면

도면1

도면2

도면3

도면4

도면5

도면6

도면7

도면8

도면9

도면10

도면11

도면12