(19) 日本国特許庁(JP)

## (12) 公開特許公報(A)

(11) 特許出願公開番号

特開2005-293751

(P2005-293751A)

(43) 公開日 平成17年10月20日(2005.10.20)

(51) Int.Cl.<sup>7</sup>

G 11 C 11/413

F 1

G 11 C 11/34 335 Z

テーマコード(参考)

5 B 0 1 5

審査請求 未請求 請求項の数 7 O L (全 15 頁)

(21) 出願番号

特願2004-109059 (P2004-109059)

(22) 出願日

平成16年4月1日 (2004.4.1)

(71) 出願人 000004226

日本電信電話株式会社

東京都千代田区大手町二丁目3番1号

(74) 代理人 100083194

弁理士 長尾 常明

(72) 発明者 柴田 信太郎

東京都千代田区大手町二丁目3番1号 日本電信電話株式会社内

F ターム(参考) 5B015 HH01 HH03 HH04 JJ02 KA06

KB25 KB64 KB72

(54) 【発明の名称】半導体メモリ

## (57) 【要約】

【課題】 半導体メモリの高速化と低消費電力化を図る。

【解決手段】 メモリセル10と、擬似電源線VPと、一対の擬似GND線VG, /VGと、一対のビット線BL, /BLに接続された一対の書き込みバッファ2と、電流センス回路5とを有する半導体メモリにおいて、VDDとVLL(VDD > VLL)の電源をもち、書き込みバッファ2のHigh出力レベルを読み出し時はVDDに、書き込み時はVLLに切り替え、擬似電源線VPのレベルを読み出し時はVDDに、書き込み時はVLLに切り替える。

【選択図】 図1

**【特許請求の範囲】****【請求項 1】**

一对の負荷用MOSFETおよび一对の駆動用MOSFETからなるフリップフロップ回路並びに該フリップフロップ回路の一方と他方の入出力側にそれぞれ接続した一对のセル選択用MOSFETからなるメモリセルと、前記一对のセル選択用MOSFETの前記フリップフロップ回路に接続される側と反対のドレイン又はソースにそれぞれ接続した一对のビット線と、前記一对の負荷用MOSFETのソースに共通接続した擬似電源線と、前記一对の駆動用MOSFETのソースにそれぞれ接続した一对の擬似GND線と、前記一对のビット線にそれぞれ接続した一对の書き込みバッファと、前記一对の擬似GND線に共通接続した電流センス回路とを有する半導体メモリにおいて、

出力電圧が異なる第1および第2の電源と、前記各書き込みバッファのHigh出力レベルを前記第1又は第2の電源の電圧に対応する電圧に個々に切り替える手段と、前記擬似電源線のレベルを前記第1又は第2電源の電圧に対応する電圧に切り替える手段を設けたことを特徴とする半導体メモリ。

**【請求項 2】**

請求項1に記載の半導体メモリにおいて、

前記擬似電源線を開放状態にする手段を設けたことを特徴とする半導体メモリ。

**【請求項 3】**

請求項1又は2に記載の半導体メモリにおいて、

スタンバイ状態時に、前記擬似電源線と前記一对のビット線を、前記第1および第2の電源のうちの低い電圧の電源に対応する第1のHighレベルに制御する手段を設けたことを特徴とする半導体メモリ。

**【請求項 4】**

請求項1又は2に記載の半導体メモリにおいて、

メモリセルからのデータの読み出しの際に、当該メモリセルの擬似電源線と一对のビット線を、前記第1および第2の電源のうちの高い電圧の電源に対応する第2のHighレベルに制御し、非選択状態のメモリセルの擬似電源線と一对のビット線を、前記第1および第2の電源のうちの低い電圧の電源に対応する第1のHighレベルに制御する手段を設けたことを特徴とする半導体メモリ。

**【請求項 5】**

請求項1に記載の半導体メモリにおいて、

メモリセルへのデータの書き込みの際に、当該メモリセルの擬似電源線と一对のビット線のうちのHigh側ビット線を、前記第1および第2の電源のうちの低い電圧の電源に対応する第1のHighレベルに制御する手段を設けたことを特徴とする半導体メモリ。

**【請求項 6】**

請求項1に記載の半導体メモリにおいて、

前記擬似電源線を開放状態にする手段を設け、

メモリセルへのデータの書き込みの際に、当該メモリセルの擬似電源線を開放状態に制御し、かつ当該メモリセルの一对のビット線のうちのHigh側ビット線を、前記第1および第2の電源のうちの低い電圧の電源に対応する第1のHighレベルに制御する手段を設けたことを特徴とする半導体メモリ。

**【請求項 7】**

請求項3乃至6のいずれか1つに記載の半導体メモリにおいて、

前記第1のHighレベルに制御する手段に前記第1の電源を使用し、前記第2のHighレベルに制御する手段に前記第2の電源を使用することを特徴とする半導体メモリ。

**【発明の詳細な説明】****【技術分野】****【0001】**

本発明は、極微細LSI製造プロセスを用いた半導体メモリに関するものであり、特に高速なスタティック形ランダムアクセスメモリ(Static Random Access Memory;SRAM)に

適用して有効な低消費電力化技術に関する。

**【背景技術】**

**【0002】**

上記の技術分野に属する従来の半導体メモリとして、例えば、特許文献1に記載のものがある。図10はその特許文献1に記載された半導体メモリの回路図である。以下の説明において、特に断らない限り、High状態とはVDDもしくはVDD近傍の高レベルのことであり、Low状態とはGNDもしくはGND近傍の低レベルのことを示す。

**【0003】**

メモリセル10は、フリップフロップ回路を構成する一対の負荷用pMOSFET Q1, Q2と一対の駆動用nMOSFET Q3, Q4に、セル選択用のnMOSトランジスタゲートQ5, Q6を組み合わせて構成される。フリップフロップ回路の一対の回路節点N1, N2は何れか一方がHighレベル状態、他方がLowレベル状態となり、その状態の違いによってメモリセル10は1ビットのデータを記憶する。WLはワード線、BL, /BLは対となるビット線、VG, /VGは対となる擬似GND線である。

**【0004】**

ワード線WLはメモリセル10の選択信号を伝送する線路であり、非選択状態でGNDレベル、選択状態でVDDレベルに制御される。一対のビット線BL, /BLは、書き込み時に入力データに対応した電圧信号を差動信号の形態で当該メモリセル10まで伝送する線路である。このビット線BL, /BLは、非書き込み期間中は共にVDDもしくはVDD近傍の高レベルに制御されており、メモリセル10にデータを書き込む時のみ、入力データに応じて何れか一方のビット線だけがGNDもしくはGND近傍の低レベルに制御される。一対の擬似GND線VG, /VGは、読み出し時にメモリセル10の記憶内容に応じた電流信号を差動信号の形態で電流センス回路5まで伝送する線路である。擬似GND線VG, /VGのレベルは、GNDもしくはGND近傍の低レベルである。

**【0005】**

なお、通常は複数のワード線と複数のビット線ペア（および擬似GND線ペア）を用意し、それらの交点にメモリセル10を配置してメモリセルアレイが構成される。図10では説明図の煩雑さを避ける意味で、着目しているワード線、ビット線ペア、擬似GND線ペア、そしてメモリセルだけを図示し、他のワード線、ビット線ペア、擬似GND線ペア、メモリセルについては省略している。

**【0006】**

図10において、DI、Y、WE、SAEは入力端子、DOは出力端子である。入力端子DIには入力データDI、入力端子Yには当該ビット線ペアに対応したコラム選択信号Y、入力端子WEには書き要求信号WE、入力端子SAEには当該擬似GND線ペアに対応した電流センス回路活性化信号SAEを入力する。出力端子DOからは読み出しだデータDOが出力される。これらの入力信号又は出力信号は、何れも2値の電圧信号（VDD又はGNDレベル）である。その他、図10では省略しているが、半導体メモリの入力信号のひとつにチップ選択信号CSがある。チップ選択信号CSは半導体メモリをスタンバイ状態もしくは動作状態に切り替える特別な制御信号である。データの読み出し又は書き込みを行う際は、当該半導体メモリを事前に動作状態に制御する必要があるが、以下で述べる読み出し動作もしくは書き込み動作に直接関与しないので、記述を省略する。

**【0007】**

図10の構成要素の内、1'は入力データDIの書き込み動作を制御する書き込み制御回路、2'はビット線BL, /BLをドライブする反転形の一対の書き込みバッファであり、これらで書き込み回路を構成している。データの非書き込み時は、書き込みバッファ2'はビット線BL, /BLをVDDもしくはVDD近傍のHighレベルにプルアップする。3'は固定電源であり、メモリセル10に電圧VDDを供給する。4は擬似的に定電流源として機能する高抵抗、5は電流センス回路であり、これらで読み出し回路を構成している。電流センス回路5は、入力端子から流出する電流（IS1, IS2）の大小比較を行い、その結果を2値の電圧信号（VDD又はGNDレベル）の形態で出力端子DOに出力する。

10

20

30

40

50

## 【0008】

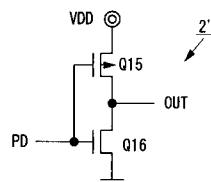

図11は図10における反転型の書き込みバッファ2'の回路図である。この書き込みバッファ2'はpMOSFET Q15とnMOSFET Q16より構成されるインバータからなり、入力端子PDがHigh状態(VDDレベル)のとき出力端子OUTはGNDレベルである。逆に、入力端子PDがLow状態(GNDレベル)のとき出力端子OUTはVDDレベルである。

## 【0009】

半導体メモリに対して、データを書き込む又は読み出す操作を以下に概説する。図10のメモリセル10にはデータ“1”が記憶されており、回路節点N1はHighレベル状態、N2はLowレベル状態にあるとする。

10

## 【0010】

## &lt;読み出し動作&gt;

図10の従来例において、メモリセル10に記憶されたデータ“1”を出力端子DOに読み出す動作は以下の通りである。読み出し動作を通じて、書込要求信号WEは非書き込み状態(GNDレベル)である。

## 【0011】

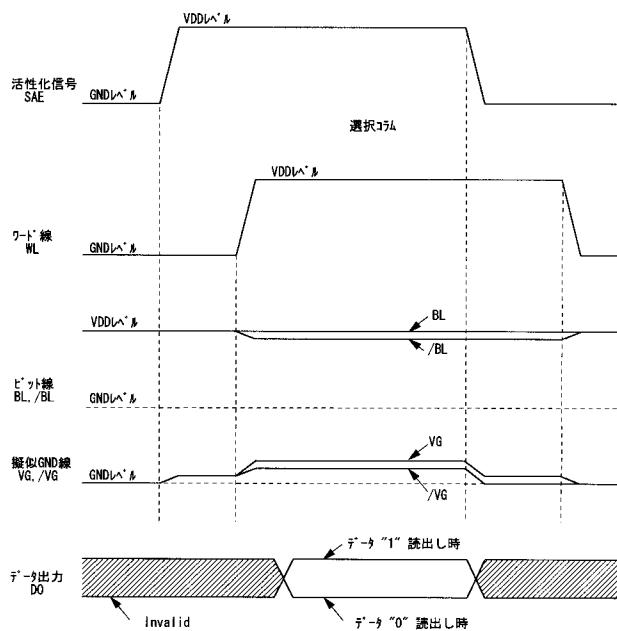

図12は図10の半導体メモリの主要な回路節点の動作波形である。一連の読み出し動作の初期状態として、活性化信号SAEは非活性状態(GNDレベル)とする。ワード線WLは非選択状態(GNDレベル)、ビット線BL, /BLはVDDレベル、擬似GND線VG, /VGはGNDレベルである。メモリセル10内のMOSFETに関しては、Q1, Q4は導通状態、Q2, Q3, Q5, Q6は非導通状態である。

20

## 【0012】

読み出し動作は、当該コラムの活性化信号SAEをVDDレベルに制御して、電流センス回路5を活性状態にすることから始まる。その際、電流センス回路5から擬似GND線VG, /VGに定常的に流出する電流によって高抵抗4の両端に逆起電力が発生し、擬似GND線VG, /VGのレベルがGNDからGND近傍の低レベルまで上昇する。しかる後、ワード線WLを選択状態(VDDレベル)に制御する。このとき、記憶内容を反映してMOSFET Q6が導通し、ビット線/BLから擬似GND線VGへの電流経路が形成される。MOSFET Q5については非導通状態を維持するので、対となるビット線BLから擬似GND線/VGへの電流経路は形成されない。メモリセル10から擬似GND線へ流出した読み出し電流は、定電流源として機能する高抵抗4で折り返されて、電流センス回路5に入力される。議論を簡単にする為に、高抵抗4を理想定電流源と見なすと、メモリセル10から擬似GND線/VG, VGへ流出する読み出し電流IR1, IR2と電流センス回路5から流出する電流IS1, IS2には、以下の関係がある。

30

$$IR_1 + IS_1 = IR_2 + IS_2$$

上述の例では、「 $IR_2 > 0$ かつ $IR_1 = 0$ 」であるので、電流センス回路5の入力信号には「 $IS_1 > IS_2 > 0$ 」の関係がある。これを電流センス回路5は検出して、データ“1”に相当するVDDレベルの信号を出力端子DOから出力する。

## 【0013】

一方、メモリセル10にデータ“0”が記憶されている場合は、回路節点N1がLow状態、N2がHigh状態になるので、電流センス回路5はデータ“0”に相当するGNDレベルの信号を出力端子DOから出力する。

40

## 【0014】

図10では省略されているが、ビット線ペアが複数ある場合は、出力端子DOからの読み出しデータDOを多重化して外部へ出力する為のマルチプレクサが電流センス回路5の後段に設けられる。その際、非選択コラムについては、電流センス回路5が活性化されないので、ワード線WLが選択されてもデータは読み出されない。

## 【0015】

## &lt;書き込み動作&gt;

データ“1”が記憶された図10のメモリセル10に、入力端子DIから入力された逆

50

データ“0”を書き込む動作について以下に述べる。書き込み動作を通じて、活性化信号S A Eは非活性状態(GNDレベル)である。

#### 【0016】

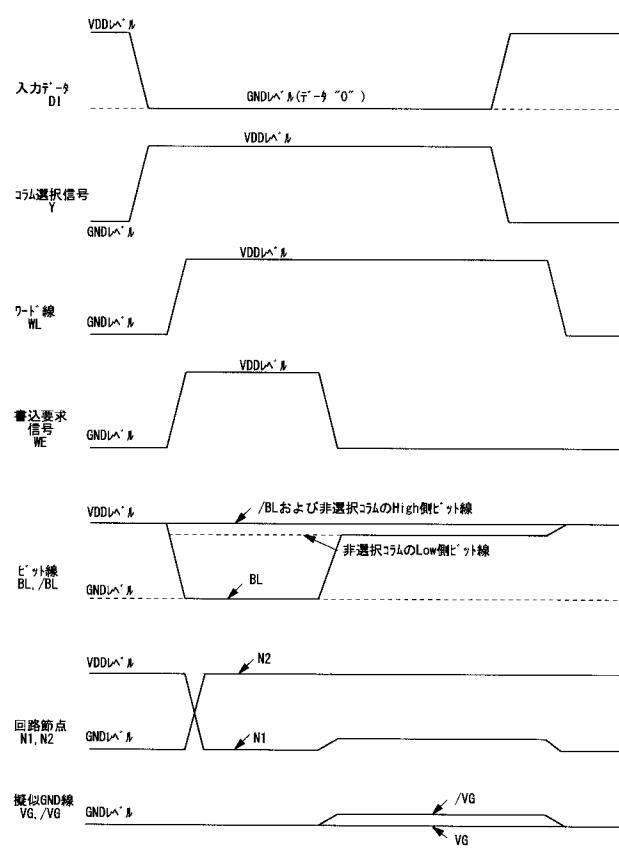

図13は図10の半導体メモリの主要な回路節点の動作波形である。一連の書き込み動作の初期状態として、コラム選択信号Yは非選択状態(Lowレベル)、ワード線WLは非選択状態(GNDレベル)、書き要求信号WEは非書き込み状態(GNDレベル)とする。ビット線BL側の書き込みバッファ2'の入力とビット線/BL側の書き込みバッファ2'の入力は共にLowレベルであり、ビット線BL, /BLは共にVDDレベルに設定されている。擬似GND線VG, /VGはGNDレベルである。メモリセル10内のMOSFETに関しては、Q1, Q4は導通状態、Q2, Q3, Q5, Q6は非導通状態である。

10

#### 【0017】

入力端子DIに入力されたデータ“0”的書き込み動作は、入力端子Yの当該コラム選択信号Yを選択状態(VDDレベル)にして、ビット線ペアを特定することから始まる。しかる後、ワード線WLを選択状態(VDDレベル)、書き要求信号WEを書き込み状態(VDDレベル)に制御する。その際、書き制御回路1'の動作により、ビット線BL側の書き込みバッファ2'の入力がHighレベル状態に制御されるので、ビット線BLはGNDレベルにドライブされる。ビット線/BL側の書き込みバッファ2'については、その入力はLowレベル状態から変化しないので、ビット線/BLはVDDレベルを維持する。ビット線BLの電位の低下と共に、MOSFET Q5のゲート・ソース(ビット線BL側のMOSFET節点)間にはMOSFETの閾値電圧を超える十分大きな電圧が印加されることになり、MOSFET Q5は導通状態になる。その結果、回路節点N1の電位は低下し、MOSFET Q2, Q4で構成されるインバータの論理閾値を下回ると、フリップフロップ回路の状態は反転し、回路節点N1がLowレベル状態、回路節点N2がHighレベル状態に変化して、メモリセル10は更新データを保持可能になる。しかる後、書き要求信号WEを非書き込み状態(GNDレベル)に制御し、それに続いてワード線WLを非選択状態(GNDレベル)に復帰させる。書き要求信号WEを非書き込み状態に制御することにより、書き制御回路1'はビット線BL側および/BL側の書き込みバッファ2'の入力を共にLowレベルに制御するので、書き込みバッファ2'の動作により、ビット線BLは初期のVDDレベルまで回復する。書き要求信号WEを非書き込み状態(Lowレベル)に制御するタイミングは、メモリセル10内のフリップフロップ回路の状態が反転した後であれば、特に制約はない。入力データDI、コラム選択信号Y、ワード線WLに関しては、ビット線BLが初期のレベルに回復した後であれば、状態を変化させるタイミング特に制約はない。

20

#### 【0018】

なお、非選択コラムのビット線については、書き込み動作を通じて、ビット線BL側も/BL側も書き込みバッファ2'によってVDD又はその近傍の高レベルにプルアップされている。

30

#### 【0019】

【特許文献1】特開2000-057778号公報

40

#### 【発明の開示】

#### 【発明が解決しようとする課題】

#### 【0020】

ところで、半導体メモリの動作速度と消費電力、そして使用するMOSFETのゲート長には密接な関係がある。ゲート長の短いMOSFETを利用可能な極微細LSI製造プロセスを適用することは、半導体メモリの動作速度を改善する有効な手段ではあるが、同時にMOSFETのサブスレッショルドリーク電流の増大を招く。サブスレッショルドリーク電流とは、オフ状態のMOSFETに流れるゲート・ソース間のリーク電流のことであり、スタンバイ状態/動作状態の別なく、半導体メモリの消費電力増の原因になる。その為、大規模な半導体メモリでは、高速化手段としての極微細LSIプロセスの適用が制限されてしまうという問題があった。

50

## 【0021】

また、サブスレッショルドリーク電流にはゲート長の他に、ソース・ドレイン間に印加される電圧にも依存する性質があるので、電源電圧を下げる事である程度低減可能である。しかし、電源電圧を下げる事で、オン状態のMOSFETのゲート・ソース間に印加される電圧が低下する為に、MOSFETのオン電流（ドレイン電流）が減少し、デジタル回路、アナログ回路を問わず遅延時間は増大する。これは、半導体メモリの動作速度の低下に繋がるので、動作電圧の低電圧化だけでは解決できないという問題があった。

## 【0022】

本発明の目的は、上述の問題点を解決するべく、極微細LSI製造プロセスを適用して有効な、動作速度の低下のない、低消費電力な半導体メモリを提供することにある。

10

## 【課題を解決するための手段】

## 【0023】

請求項1にかかる発明は、一対の負荷用MOSFETおよび一対の駆動用MOSFETからなるフリップフロップ回路並びに該フリップフロップ回路の一方と他方の入出力側にそれぞれ接続した一対のセル選択用MOSFETからなるメモリセルと、前記一対のセル選択用MOSFETの前記フリップフロップ回路に接続される側と反対のドレイン又はソースにそれぞれ接続した一対のビット線と、前記一対の負荷用MOSFETのソースに共通接続した擬似電源線と、前記一対の駆動用MOSFETのソースにそれぞれ接続した一対の擬似GND線と、前記一対のビット線にそれぞれ接続した一対の書き込みバッファと、前記一対の擬似GND線に共通接続した電流センス回路とを有する半導体メモリにおいて、出力電圧が異なる第1および第2の電源と、前記各書き込みバッファのHigh出力レベルを前記第1又は第2の電源の電圧に対応する電圧に個々に切り替える手段と、前記擬似電源線のレベルを前記第1又は第2電源の電圧に対応する電圧に切り替える手段を設けたことを特徴とする。

20

## 【0024】

請求項2にかかる発明は、請求項1に記載の半導体メモリにおいて、前記擬似電源線を開放状態にする手段を設けたことを特徴とする。

## 【0025】

請求項3にかかる発明は、請求項1又は2に記載の半導体メモリにおいて、スタンバイ状態時に、前記擬似電源線と前記一対のビット線を、前記第1および第2の電源のうちの低い電圧の電源に対応する第1のHighレベルに制御する手段を設けたことを特徴とする。

30

## 【0026】

請求項4にかかる発明は、請求項1又は2に記載の半導体メモリにおいて、メモリセルからのデータの読み出しの際に、当該メモリセルの擬似電源線と一対のビット線を、前記第1および第2の電源のうちの高い電圧の電源に対応する第2のHighレベルに制御し、非選択状態のメモリセルの擬似電源線と一対のビット線を、前記第1および第2の電源のうちの低い電圧の電源に対応する第1のHighレベルに制御する手段を設けたことを特徴とする。

40

## 【0027】

請求項5にかかる発明は、請求項1に記載の半導体メモリにおいて、メモリセルへのデータの書き込みの際に、当該メモリセルの擬似電源線と一対のビット線のうちのHigh側ビット線を、前記第1および第2の電源のうちの低い電圧の電源に対応する第1のHighレベルに制御する手段を設けたことを特徴とする。

## 【0028】

請求項6にかかる発明は、請求項1に記載の半導体メモリにおいて、前記擬似電源線を開放状態にする手段を設け、メモリセルへのデータの書き込みの際に、当該メモリセルの擬似電源線を開放状態に制御し、かつ当該メモリセルの一対のビット線のうちのHigh側ビット線を、前記第1および第2の電源のうちの低い電圧の電源に対応する第1のHighレベルに制御する手段を設けたことを特徴とする。

50

## 【0029】

請求項 7 にかかる発明は、請求項 3 乃至 6 のいずれか 1 つに記載の半導体メモリにおいて、前記第 1 の H i g h レベルに制御する手段に前記第 1 の電源を使用し、前記第 2 の H i g h レベルに制御する手段に前記第 2 の電源を使用することを特徴とする。

## 【発明の効果】

## 【0030】

本発明によれば、出力電圧の異なる第 1 および第 2 の電源を使用するので、動作速度を低下させることなく、サブスレッショルドリーク電流によるメモリセルアレイの消費電力と、書き込み時のビット線の充放電による消費電力を下げることができる利点がある。その為、大規模で高速なメモリを必用とする際に本発明の半導体メモリを適用すれば、ゲート長の短い M O S F E T を利用可能な極微細 L S I 製造プロセスを適用しても消費電力の増大を極力抑えることができ効果大である。10

## 【発明を実施するための最良の形態】

## 【0031】

本発明では、出力電圧が異なる第 1 および第 2 の電源を使用することにより、非選択状態のメモリセルに印加される電圧を下げられるので、サブスレッショルドリーク電流による無駄な消費電力を低減できること、また書き込み時のビット線の振幅を下げられるので、ビット線の寄生容量の充放電による消費電力を低減できることができ、従来技術と異なる。

## 【実施例 1】

## 【0032】

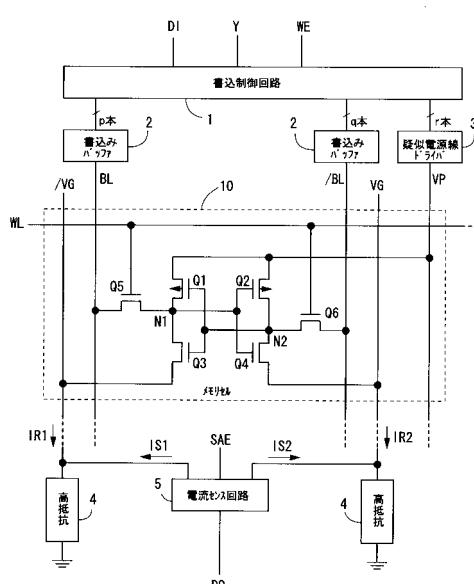

図 1 は、出力電圧が異なる第 1 および第 2 の高電位電源 V D D , V L L ( V D D > V L L ) を使用した本発明の実施例 1 の半導体メモリの構成を示す図である。以下の説明において、特に断らない限り、H i g h 状態とは V D D もしくは V D D 近傍の高レベルのことであり、L o w 状態とは G N D もしくは G N D 近傍の低レベルのことを示す。20

## 【0033】

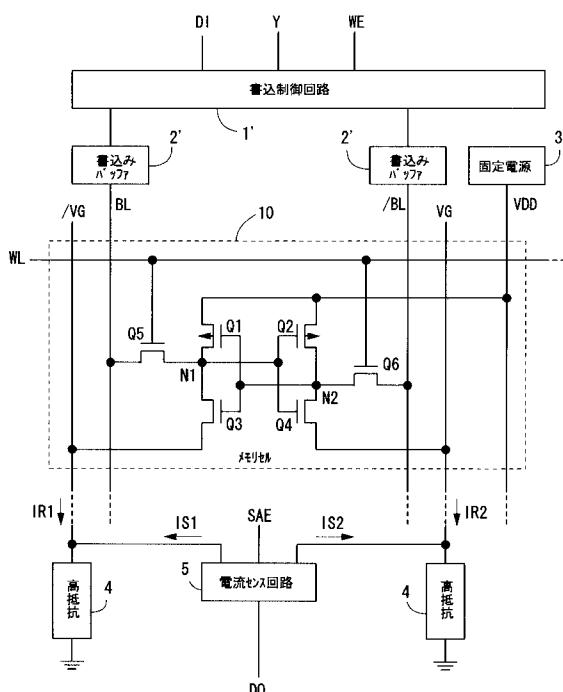

図 1 において、6 トランジスタ構成 ( Q 1 ~ Q 6 ) のメモリセル 1 0 を使用すること、入力データ D I の書き込みを制御する書き制御回路 1 と一対のビット線 B L , / B L をドライブする一対の書き込みバッファ 2 で書き込み回路を構成すること、擬似的な定電流源として機能する高抵抗 4 と電流センス回路 5 で読み出し回路を構成することは、基本的に図 1 0 の従来例と同じである。但し、書き制御回路 1 と書き込みバッファ 2 の機能は従来例よりも拡張されており、書き制御回路 1 の制御によって、書き込みバッファ 2 の出力は V D D と G N D レベルの他に、第 3 の状態として V L L レベル ( V D D と G N D の中間レベル ) をとれることが異なる。さらに、メモリセル 1 0 の高電位側電源端子を擬似電源線 V P に接続すること、擬似電源線 V P に接続された擬似電源線ドライバ 3 の出力電圧 ( V D D もしくは V L L ) を書き制御回路 1 によって制御できることことが異なる。30

## 【0034】

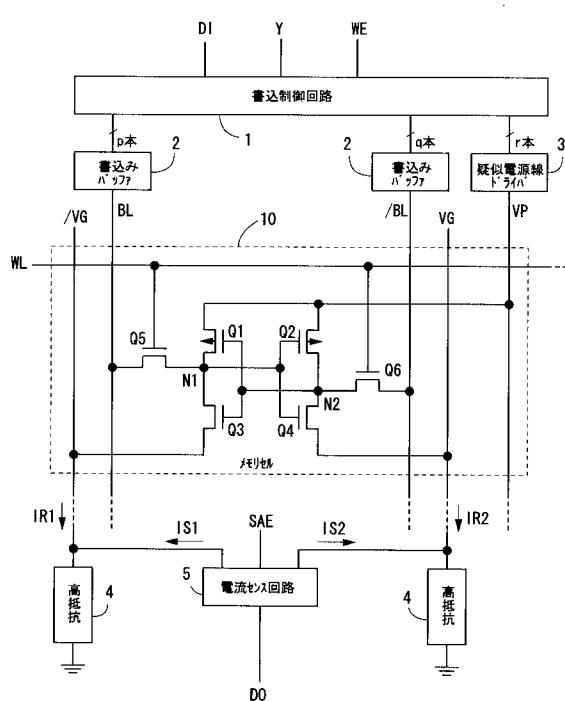

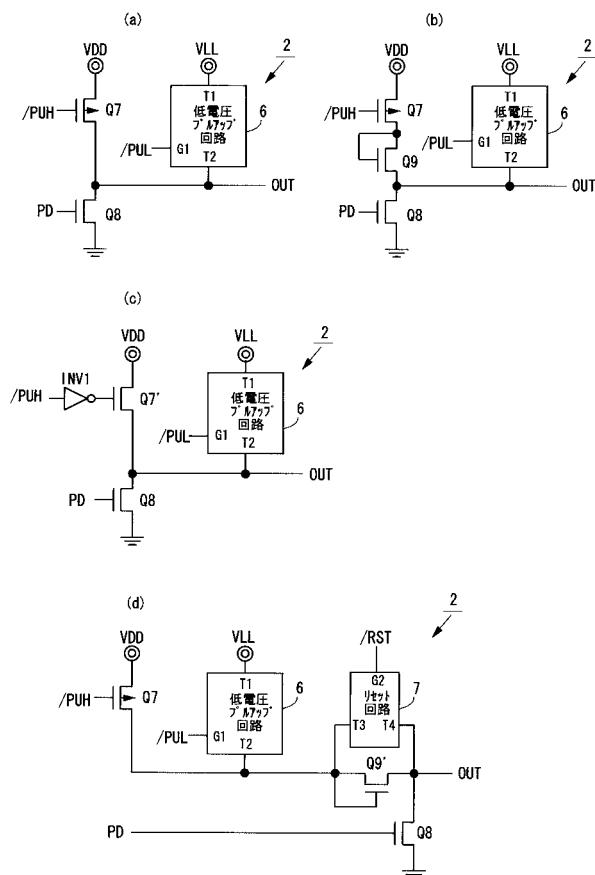

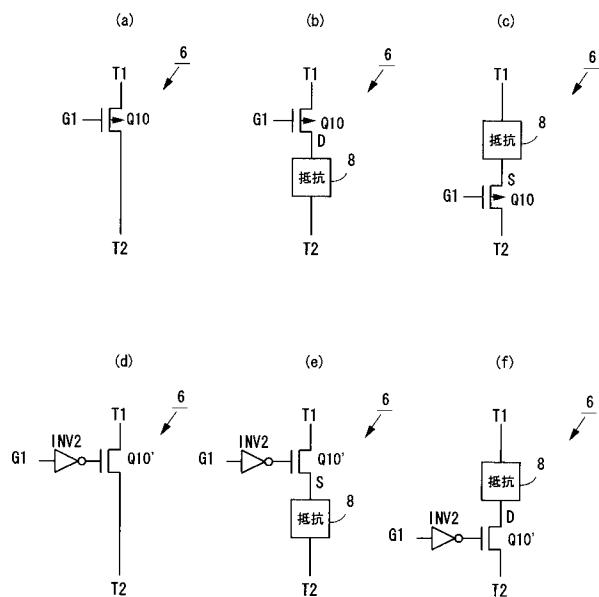

図 2 ( a ) は書き込みバッファ 2 の回路図、図 3 ( a ) ~ ( f ) は図 2 ( a ) 中の低電圧プルアップ回路 6 の構成例である。図 3 ( a ) の p M O S F E T Q 1 0 を使う構成、図 3 ( d ) の n M O S F E T Q 1 0 ' を使う構成の何れも適用可能である。また、図 3 ( b ) , ( c ) , ( e ) , ( f ) のように、M O S F E T Q 1 0 又は Q 1 0 ' のオン電流を制限する手段として、M O S F E T のソース又はドレインに直列に抵抗 8 を設けた構成も適用可能である。抵抗 8 は、抵抗素子の他、M O S F E T のチャネル抵抗でも代用できる。図 2 ( a ) に示す書き込みバッファ 2 の 3 個の制御入力 ( P D , / P U H , / P U L ) は、H i g h 状態で V D D レベル、L o w 状態で G N D レベルをとる。これらの入力信号 P D , / P U H , / P U L と出力信号 O U T の関係は、図 1 4 に示す通りである。40

## 【0035】

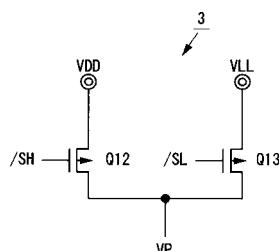

図 5 は擬似電源線ドライバ 3 の構成例である。2 個の制御入力 ( / S H , / S L ) は、H i g h 状態で V D D レベル、L o w 状態で G N D レベルをとる。これらの入力信号 / S H , / S L と出力電圧 V P の関係は、図 1 5 に示す通りである。

## 【0036】

10

20

30

40

50

上記の半導体メモリに対して、データを書き込む又は読み出す動作を以下に概説する。図1のメモリセル10にはデータ“1”が記憶されており、回路節点N1はHighレベル状態、回路節点N2はLowレベル状態にあるとする。

#### 【0037】

##### <スタンバイ状態>

図1の実施例1において、スタンバイ状態すなわちメモリセルアレイに対してデータの読み出しも書き込みも行わない状態における各部の電位関係について、以下に説明する。書き込み要求信号WEは非書き込み状態(GNDレベル)、活性化信号SAEは非活性状態(GNDレベル)、疑似電源線VPはVLLレベルである。ワード線WLは非選択状態(GNDレベル)、ピット線BL, /BLはVLLレベル、疑似GND線VG, /VGはGNDレベルである。メモリセル10内のMOSFETに関しては、Q1, Q4は導通状態、Q2, Q3, Q5, Q6は非導通状態である。10

#### 【0038】

スタンバイ状態では、ピット線ペアBL, /BLと疑似電源線VPが共にVLLレベルに制御される。それ故、VDDが印加される従来例に比べると、MOSFETのサブスレッショルドリーク電流による無駄な消費電力は減少する。

#### 【0039】

##### <読み出し動作>

図1の実施例1において、メモリセル10に記憶されたデータ“1”を出力端子DOに読み出す動作は以下の通りである。読み出し動作を通じて、書き込み要求信号WEは非書き込み状態(GNDレベル)である。20

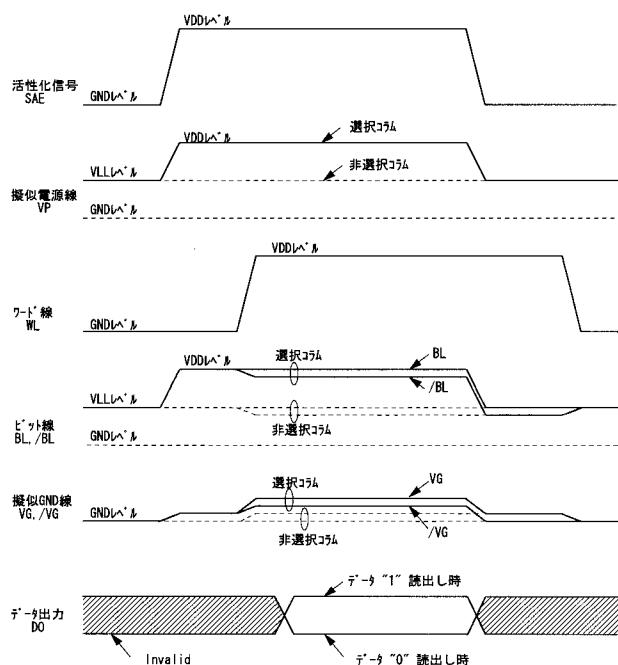

#### 【0040】

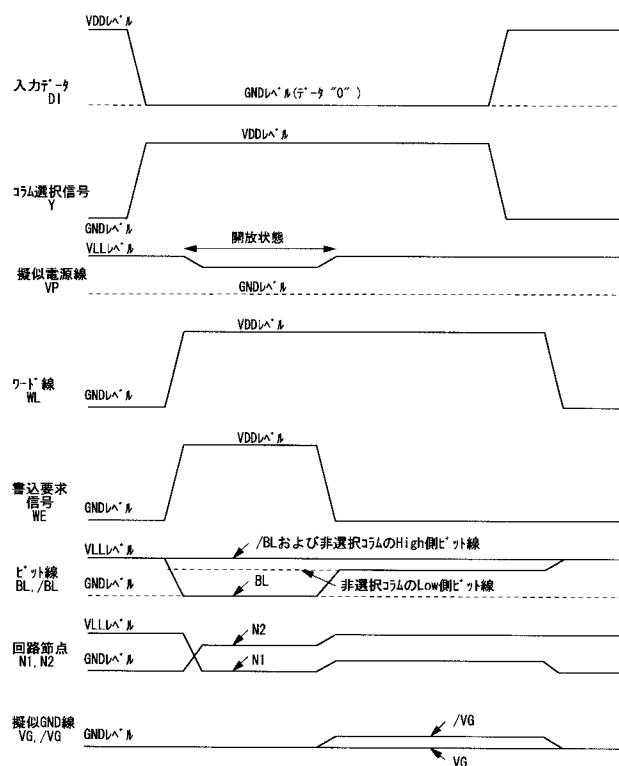

図6は図1の半導体メモリの主要な回路節点の動作波形である。一連の読み出し動作の初期状態として、活性化信号SAEは非活性状態(GNDレベル)、疑似電源線VPはVLLレベルとする。ワード線WLは非選択状態(GNDレベル)、ピット線BL, /BLは共にVLLレベル、疑似GND線VG, /VGはGNDレベルである。メモリセル10内のMOSFETに関しては、Q1, Q4は導通状態、Q2, Q3, Q5, Q6は非導通状態である。

#### 【0041】

読み出し動作は、当該コラムの活性化信号SAEをVDDレベルに制御して、電流センス回路5を活性状態にすると共に、疑似電源線ドライバ3を用いて当該コラムの疑似電源線VPの電位をVLLからVDDに昇圧することから始まる。その際、電流センス回路5から疑似GND線に定常的に流出する電流によって高抵抗4の両端に逆起電力が発生し、疑似GND線のレベルがGNDからGND近傍の低レベルまで上昇する。しかる後、ワード線WLを選択状態(VDDレベル)に制御する。以降の動作は、図12の従来例の説明と同じであり、重複を避ける為に説明を省略する。読み出し対象のメモリセル10の疑似電源線VPには、従来例と同じくVDDなる電圧が印加されるので、本実施例によって動作速度は低下しない。30

#### 【0042】

図1の半導体メモリでは省略されているが、ピット線ペアが複数ある場合は、出力端子DOの読み出しデータDOを多重化して外部へ出力する為のマルチプレクサが電流センス回路5の後段に設けられる。その際、非選択コラムについては、電流センス回路が活性化されないので、ワード線が選択されてもデータは読み出されない。また、非選択コラムの疑似電源線VPは、VDDに昇圧されることなく、VLLレベルを維持する。40

#### 【0043】

##### <書き込み動作>

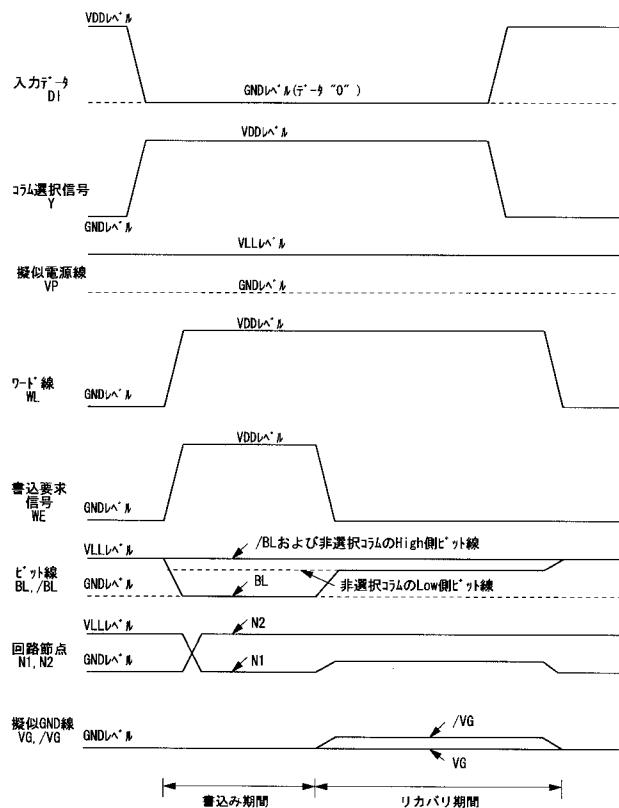

データ“1”が記憶された図1のメモリセル10に、入力端子DIから入力された逆データ“0”を書き込む動作について以下に述べる。書き込み動作を通じて、活性化信号SAEは非活性状態(GNDレベル)、疑似電源線VPはVLLレベルである。

#### 【0044】

10

20

30

40

50

図7は図1の半導体メモリの主要な回路節点の動作波形である。一連の書き込み動作の初期状態として、コラム選択信号Yは非選択状態(Lowレベル)、ワード線WLは非選択状態(GNDレベル)、書き要求信号WEは非書き込み状態(GNDレベル)とする。ビット線BL側の書き込みバッファ2の入力とビット線/BL側の書き込みバッファ2の入力は共にLowレベルであり、ビット線BL, /BLは共にVLLレベルに設定されている。擬似GND線VG, /VGはGNDレベルである。メモリセル10内のMOSFETに関しては、Q1, Q4は導通状態、Q2, Q3, Q5, Q6は非導通状態である。

#### 【0045】

10

入力端子DIに入力されたデータ“0”的書き込み動作は、コラム選択信号Yを選択状態(VDDレベル)にして、ビット線ペアを特定することから始まる。しかる後、ワード線WLを選択状態(VDDレベル)、書き要求信号WEを書き込み状態(VDDレベル)に制御する。その際、書き制御回路1の動作により、ビット線BL側の書き込みバッファ2の入力がHighレベル状態に制御されるので、ビット線BLはGNDレベルにドライブされる。ビット線/BL側の書き込みバッファ2については、その入力はLowレベル状態から変化しないので、ビット線/BLはVLLレベルを維持する。ビット線BLの電位の低下と共に、MOSFET Q5のゲート・ソース(ビット線BL側のMOSFET節点)間にMOSFETの閾値電圧を超える十分大きな電圧が印加されることになり、MOSFET Q5は導通状態になる。その結果、回路節点N1の電位は低下し、Q2, Q4で構成されるインバータの論理閾値を下回ると、フリップフロップ回路の状態は反転し、回路節点N1がLowレベル状態、回路節点N2がHighレベル状態に変化して、メモリセル10は更新データを保持可能になる。上記の動作は、電源電圧が異なるだけで、書き込み動作そのものは図13の従来例と同じである。重複を避ける為に、以降の動作説明を省略する。

#### 【0046】

書込み期間に繰り返しリカバリ期間(図7参照)において、擬似電源線VPとビット線(BL, /BL)をVLLもしくはVLL近傍のレベルに制御できるのは、例えばOE信号とWE信号間で論理をとることで、リカバリ動作と読み出し動作を区別できることによる。ここで、OE信号とは、入出力ピンを共通化したデータI/Oバッファに関して、データ入力モードとデータ出力モードを切り替える信号である。書き込み期間とリカバリ期間は共にデータ入力モード、読み出し期間はデータ出力モードに制御する。

#### 【0047】

30

ビット線BL, /BLには大きな寄生容量があり、その充放電電流が書き込み時の消費電力の大半を占める。従って、実施例1のように、書き込み時のビット線BL, /BLの振幅をVDD(従来例)からVLLに低減することで、書き込み時の消費電力を(VLL/VDD)<sup>2</sup>に低減できる。

#### 【0048】

なお、非選択コラムのビット線については、書き込み動作を通じて、BL側も/BL側も書き込みバッファ2によってVLL又はその近傍の中間レベルにプルアップされている。

#### 【0049】

本発明の実施例1の変形例として、書き込みバッファ2の別構成を図2(b)~(d)に示す。これらの変形例は、選択状態のワード線WLの電位がVDDの場合、ビット線BL, /BLのレベルを「VDD - Vthn」以上に昇圧してもデータ読み出し時の動作速度の改善に寄与しないという理論限界に着目して低電力化を図ったものである。書き込みバッファ2の出力のHighレベルをVDDから「VDD - Vthn」に低減することで、データ読み出し時のビット線の充放電による消費電力を

$$(VDD - Vthn) / VDD$$

に低減できる。ここで、VthnはnMOSFETの閾値電圧である。

#### 【0050】

書き込みバッファ2の出力のHighレベルを「VDD - Vthn」に抑える手段として、図2(b)はダイオード接続されたnMOSFET Q9をMOSFET Q7に直列に接続している。また、図2(c)は、MOSFET Q7をpMOSからnMOSFET Q7

10

20

30

30

40

50

’に置き換えている。構成は異なるが、図2(b)と(c)は同等の効果がある。さらに、図2(d)は、図2(b)のMOSFETQ9の挿入位置を変えた変形例であり、MOSFETQ7だけではなく低電圧プルアップ回路6に対しても直列になる位置にMOSFETQ9’を配置していることに特徴がある。データ読み出し時に出力OUTのHighレベルを‘VDD-Vthn’に抑えることは、図2(b)又は(c)の構成と同じである。差異はデータ書き込み時の出力OUTのHighレベルにあり、図2(b)および(c)の構成がVLLであるのに対して、図2(d)の構成は‘VLL-Vthn’となる。その結果、書き込み時の消費電力を、図2(b)又は(c)の構成に比べて

$$(VLL - Vthn) / VLL$$

に低減できる。

10

#### 【0051】

また、図2(d)の第2の特徴として、ダイオード接続されたMOSFETQ9’の両端に、書き制御回路1からのリセット信号/RSTで制御されるリセット回路7を具備することが挙げられる。VDD近傍に昇圧された擬似電源線VPのレベルをVLLもしくはVLL近傍に復帰させる際に、リセット信号/RSTをGNDレベルに制御してMOSFETQ9’のソースとドレインを短絡させる。

#### 【0052】

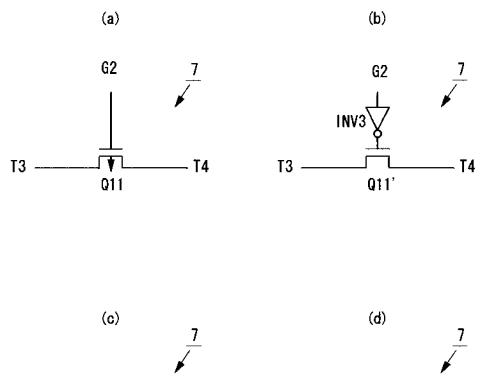

図4(a)と(b)はリセット回路7の具体例であり、pMOSFETQ11、nMOSFETQ11’の何れも適用可能である。その他、図4(c)、(d)のようにダイオード接続されたnMOSFETQ11”又はpMOSFETQ11’”も利用可能である。復帰される電圧は、ダイオード接続されたnMOS用いる場合は‘VLL+Vthn’、ダイオード接続されたpMOSを用いる場合は‘VLL+|Vthp|’になる。ここで、VthpはpMOSFETの閾値電圧(負値)である。

20

#### 【実施例2】

#### 【0053】

本発明の実施例2として、特に低消費電力化を追求する場合の構成について以下に述べる。サブスレッショルドリーク電流によるメモリセルアレイの消費電力を低減するには、VLLの値をできる限り低く設定することが有効である。VLLの理論上の下限は、

$$VLL > \max(Vthn, |Vthp|)$$

で与えられる。このような低動作電圧条件では、書き込みバッファ2の駆動力が低下する為に、ビット線BL、/BLをLowレベルに制御してもメモリセル10内のフリップフロップ回路を反転できないという現象が発生する。実施例2は、上記の問題に対処するものである。

30

#### 【0054】

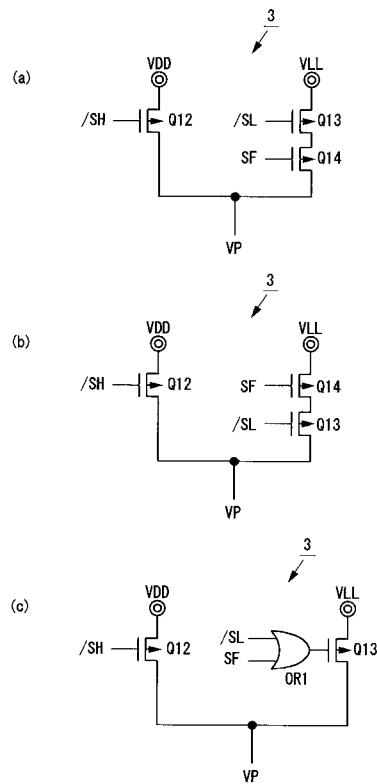

半導体メモリの構成は、図1に示す実施例1と同じである。実施例1とは、書き制御回路1および擬似電源線ドライバ3の機能が拡張されていることが異なり、データ書き込み時の擬似電源線VPを開放状態(フローティング状態)に制御可能である。図8(a)～(c)は、機能拡張された擬似電源線ドライバ3の回路図である。図8(a)はMOSFETQ13のドレイン側、図8(b)はMOSFETQ13のソース側にpMOSFETQ14を附加している。当該コラムの読み出し時を除いて、/SH節点はVDDレベルに制御されているので、データを書き込む際は、SF入力をVDDレベルに制御することで出力VPをハイインピーダンス状態に設定できる。その結果、擬似電源線VPは開放状態になる。図8(c)は、論理ゲートOR1を使用した別構成であり、機能上は図8(a)又は(b)と同じである。

40

#### 【0055】

図9は、機能拡張された擬似電源線ドライバ3を使用した際の半導体メモリの書き込み動作波形である。データ書き込み期間中、擬似電源線VPを開放状態に制御して電源からの電荷の供給を遮断することで、メモリセル10内のフリップフロップ回路の回路節点N1の電位をGNDレベルまで低下させられる。図7に示した実施例1の書き込み動作波形との違いは、擬似電源線VPとメモリセル10内の回路節点N2の波形である。擬似電源線VP

50

が開放状態の期間は、メモリセル10内のフリップフロップ回路のH i g h側節点の電位は( V L L - V t h )であり、擬似電源線V Pの開放状態が解除された時点で、V L Lまで上昇する。このように機能拡張された擬似電源線ドライバ3を用いることで、書き込みバッファ2の駆動力が低下する低電圧動作条件においても、データの確実な書き込みを保証できる。

【図面の簡単な説明】

【0056】

【図1】本発明の実施例1の半導体メモリの回路図である。

【図2】(a)～(d)は実施例1における書き込みバッファの構成例を示す回路図である。

10

【図3】(a)～(f)は図2の書き込みバッファ内の低電圧プルアップ回路6の構成例を示す回路図である。

【図4】(a)～(d)は図2(d)の書き込みバッファ内のリセット回路7の構成例を示す回路図である。

【図5】実施例1における擬似電源線ドライバの構成例を示す回路図である。

【図6】実施例1における読み出し動作波形図である。

【図7】実施例1における書き込み動作波形図である。

【図8】(a)～(c)は実施例2における擬似電源線ドライバの構成例を示す回路図である。

20

【図9】実施例2における書き込み動作波形図である。

【図10】従来の半導体メモリの回路図である。

【図11】従来の半導体メモリで使用されている書き込みバッファの回路図である。

【図12】従来の半導体メモリの読み出し動作波形図である。

【図13】従来の半導体メモリの書き込み動作波形である。

【図14】実施例1における書き込みバッファの入出力関係の説明図である。

【図15】実施例1における擬似電源線ドライバの入出力関係の説明図である。

【符号の説明】

【0057】

1, 1' : 書込み制御回路

2, 2' : 書込みバッファ

30

3 : 擬似電源線ドライバ

3' : 固定電源

4 : 高抵抗

5 : 電流センス回路

6 : 低電圧プルアップ回路

7 : リセット回路

8 : 電流制限抵抗

10 : メモリセル

W L : ワード線

B L, / B L : ビット線ペア

V G, / V G : 擬似GND線ペア

40

V P : 擬似電源線

Q 1, Q 2, Q 7, Q 10, Q 11, Q 12, Q 13, Q 14, Q 15 : pMOSFE

T

Q 3, Q 4, Q 5, Q 6, Q 7', Q 8, Q 9, Q 9', Q 10', Q 11', Q 11

", Q 11", Q 16 : nMOSFET

I N V 1, I N V 2, I N V 3 : インバータ

O R 1 : オアゲート

Y : コラム選択信号、入力端子、

S A E : 活性化信号、入力端子

50

WE : 書込要求信号、入力端子

DI : データの入力端子

DO : 出力データ、出力端子

/PUH : ビット線の High レベルプルアップ信号

/PUL : ビット線の Low レベルプルアップ信号

PD : ビット線のプルダウン信号

/RST : リセット信号

/SH : 擬似電源線の High レベル制御信号

/SL : 擬似電源線の Low レベル制御信号

SF : 擬似電源線の開放(フローティング)制御信号

N1, N2, G1, G2, T1, T2, T3, T4 : 回路節点

10

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図 8】

【図 9】

【図 10】

【図 11】

【図12】

【図13】

【図14】

書き込みパッカ2の入出力関係

| 入力信号 |      |      | 出力信号   |

|------|------|------|--------|

| PD   | /PUH | /PUL | OUT    |

| High | High | High | GNDレベル |

| Low  | Low  | High | VDDレベル |

| Low  | High | Low  | VLLレベル |

【図15】

擬似電源線ドライバ3の入出力関係

| 入力信号 |      | 出力電圧 |

|------|------|------|

| /SH  | /SL  | VP   |

| Low  | High | VDD  |

| High | Low  | VLL  |