(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5271426号

(P5271426)

(45) 発行日 平成25年8月21日(2013.8.21)

(24) 登録日 平成25年5月17日(2013.5.17)

|                |           |               |       |

|----------------|-----------|---------------|-------|

| (51) Int.Cl.   | F 1       |               |       |

| HO 1 L 21/314  | (2006.01) | HO 1 L 21/314 | A     |

| HO 1 L 21/3205 | (2006.01) | HO 1 L 21/88  | M     |

| HO 1 L 21/768  | (2006.01) | HO 1 L 21/90  | J     |

| HO 1 L 23/532  | (2006.01) | HO 1 L 21/285 | S     |

| HO 1 L 23/522  | (2006.01) | HO 1 L 21/28  | 301 R |

請求項の数 24 (全 33 頁) 最終頁に続く

|               |                               |           |                                             |

|---------------|-------------------------------|-----------|---------------------------------------------|

| (21) 出願番号     | 特願2011-554343 (P2011-554343)  | (73) 特許権者 | 000219967<br>東京エレクトロン株式会社<br>東京都港区赤坂五丁目3番1号 |

| (86) (22) 出願日 | 平成22年1月22日(2010.1.22)         | (74) 代理人  | 100088155<br>弁理士 長谷川 芳樹                     |

| (65) 公表番号     | 特表2012-516065 (P2012-516065A) | (74) 代理人  | 100113435<br>弁理士 黒木 義樹                      |

| (43) 公表日      | 平成24年7月12日(2012.7.12)         | (74) 代理人  | 100122507<br>弁理士 柏岡 潤二                      |

| (86) 國際出願番号   | PCT/JP2010/000347             | (72) 発明者  | 堀込 正弘<br>山梨県韮崎市穂坂町三ツ沢650 東京エレクトロン技術研究所株式会社内 |

| (87) 國際公開番号   | W02010/084759                 | (72) 発明者  | 黒鳥 託也<br>山梨県韮崎市穂坂町三ツ沢650 東京エレクトロン技術研究所株式会社内 |

| (87) 國際公開日    | 平成22年7月29日(2010.7.29)         |           |                                             |

| 審査請求日         | 平成24年10月12日(2012.10.12)       |           |                                             |

| (31) 優先権主張番号  | 61/205,752                    |           |                                             |

| (32) 優先日      | 平成21年1月22日(2009.1.22)         |           |                                             |

| (33) 優先権主張国   | 米国(US)                        |           |                                             |

| (31) 優先権主張番号  | 61/207,971                    |           |                                             |

| (32) 優先日      | 平成21年2月17日(2009.2.17)         |           |                                             |

| (33) 優先権主張国   | 米国(US)                        |           |                                             |

早期審査対象出願

最終頁に続く

(54) 【発明の名称】フッ化炭素膜の表面処理

## (57) 【特許請求の範囲】

## 【請求項 1】

絶縁性層をアニーリングする工程であって、前記絶縁性層はフッ化炭素(CFx)膜を含んでいる、該工程と、

金属元素を含んだ障壁層を前記絶縁性層上に形成する工程であって、前記障壁層は、前記アニーリングする工程の後に高温スパッタリングプロセスによって形成される、該工程と、

を含み、

前記アニーリングする工程は、前記絶縁性層の表面を不活性ガスに露出させながら所定の条件下において行われ、

10

前記高温スパッタリングプロセスの間、基板温度が70 ~ 200 に保持され、

前記高温スパッタリングプロセスは、前記絶縁性層の表面上にカーボンリッチな表面を形成しつつ、前記絶縁性層の表面上からフッ素を除去する効果を有している、半導体デバイスの製造方法。

## 【請求項 2】

前記アニーリングする工程は、結合の弱いフッ素濃度を削減するために前記絶縁性層の前記表面から水分を除去する工程を更に含んでいる請求項1に記載の方法。

## 【請求項 3】

前記所定の条件は、3 ~ 5分間の期間に亘って180 ~ 220 の温度を付加することを含んでいる請求項1に記載の方法。

20

**【請求項 4】**

前記不活性ガスはアルゴン( A r )ガスを含んでいる請求項 1 に記載の方法。

**【請求項 5】**

前記高温スパッタリングプロセスは、

金属フッ化物溶液を形成する工程と、

前記絶縁性層の前記表面から前記金属フッ化物溶液を蒸発させる工程と、

を更に含んでいる請求項 1 に記載の方法。

**【請求項 6】**

絶縁性層をアニーリングする工程であって、前記絶縁性層はフッ化炭素( C F x )膜を

含んでいる、該工程と、

10

金属元素を含んだ障壁層を前記絶縁性層上に形成する工程であって、前記障壁層は、前記アニーリングする工程の後に高温スパッタリングプロセスによって形成される、該工程

と、

を含み、

前記アニーリングする工程は、前記絶縁性層の表面を不活性ガスに露出させながら所定

の条件下において行われ、

前記金属元素は、チタン( T i )、タンタル( T a )、ルテニウム( R u )、マンガン

( M n )又はコバルト( C o )を含んでおり、

前記障壁層は、流量 7 0 s c c m のアルゴン( A r )雰囲気内において、基板温度が 2

0 0 、出力レベルが 3 0 0 W 、及び処理時間が 5 0 秒間の条件下において形成される、

半導体デバイスの製造方法。

20

**【請求項 7】**

前記障壁層は多層構造を有している請求項 1 又は 6 に記載の方法。

**【請求項 8】**

前記形成する工程の後にポストアニーリング処理を行う工程を更に含み、前記ポストアニーリング処理は、 5 0 ~ 2 0 0 の温度において 1 8 0 秒を超えない期間に亘って行

われる請求項 1 又は 6 に記載の方法。

**【請求項 9】**

前記絶縁性層は、ラジアルラインスロットアンテナ( R L S A )マイクロ波プラズマ処

理デバイスを用いて、所定の設定条件下において形成される請求項 1 又は 6 に記載の方法

。

30

**【請求項 10】**

前記所定の設定条件は、 2 5 m T o r r ~ 3 0 m T o r r の圧力と、 1 5 0 0 W ~ 2 0

0 0 W のマイクロ波出力とを含んでいる請求項 9 に記載の方法。

**【請求項 11】**

炭素対フッ素の組成比( C / F )が 1 を超えるカーボンリッチな表面を形成するよう

に、絶縁性層上に前処理プロセスを行う工程を含み、前記絶縁性層は、前記前処理プロセス

が行われる前に任意の炭素対フッ素( C F x )組成比を有したフッ化炭素を含んでおり、

前記前処理プロセスを行う工程は、前記絶縁性層の表面をプラズマに露出させることに

より、前記絶縁性層にプラズマ処理を行う工程を含み、前記プラズマは、水素原子又は炭

素原子を含んだガスを所定の条件下において励起することによって生成される、

半導体デバイスの製造方法。

40

**【請求項 12】**

前記プラズマ処理を行う工程は、前記絶縁性層の前記表面上の炭素濃度を増加させつつ

、前記絶縁性層の前記表面上のフッ素濃度を低減させる効果を有している請求項 11 に記

載の方法。

**【請求項 13】**

前記水素原子を含んだガスは、水素ガス( H 2 )、メタンガス( C H 4 )又はシランガ

ス( S i H 4 )を含み、前記フッ素濃度は、前記絶縁性層の前記表面から脱着されたフッ

化水素( H F )を形成することにより低減される請求項 12 に記載の方法。

50

## 【請求項 14】

前記炭素原子を含んだガスは、一酸化炭素ガス ( C O ) 又はメタンガス ( C H 4 ) を含み、前記フッ素濃度は、前記絶縁性層の前記表面からフッ素 ( F ) を脱着させる C F 結合を形成することにより低減される請求項 1\_2 に記載の方法。

## 【請求項 15】

前記プラズマは、ラジアルラインスロットアンテナ ( R L S A ) マイクロ波プラズマ処理デバイスを用いて生成される請求項 1\_1 に記載の方法。

## 【請求項 16】

絶縁性層の表面を不活性ガス雰囲気に露出しつつ、所定の条件下において前記絶縁性層をアニーリングする工程と、

前記アニーリングする工程の後に高温スパッタリングプロセスを行う工程であって、前記絶縁性層と障壁層との界面に金属 - C 結合を形成するために金属元素を含む該障壁層を形成し、基板温度は、前記高温スパッタリングプロセスの間、70 ~ 200 の温度で保持される、該工程と、

を含み、

前記アニーリングする工程は、前記絶縁性層の前記表面から水分を除去する工程を更に含み、

前記絶縁性層は、フッ化炭素 ( C F x ) 膜を含んでおり、

前記障壁層は、流量 70 sccm のアルゴン ( A r ) 雰囲気内において、前記基板温度が 200 、出力レベルが 300 W 、及び処理時間が 50 秒間の条件下において形成される、

半導体デバイスの製造方法。

## 【請求項 17】

前記所定の条件は、3 ~ 5 分間の期間に亘って 180 ~ 220 の温度を付加することを含んでいる請求項 1\_6 に記載の方法。

## 【請求項 18】

前記不活性ガス雰囲気はアルゴン ( A r ) ガスを含んでいる請求項 1\_6 に記載の方法。

## 【請求項 19】

前記金属元素は、チタン ( T i ) 、タンタル ( T a ) 、ルテニウム ( R u ) 、マンガン ( M n ) 又はコバルト ( C o ) を含んでいる請求項 1\_6 に記載の方法。

## 【請求項 20】

絶縁性層の表面を不活性ガス雰囲気に露出しつつ、所定の条件下において前記絶縁性層をアニーリングする工程と、

前記アニーリングする工程の後に高温スパッタリングプロセスを行う工程であって、前記絶縁性層と障壁層との界面に金属 - C 結合を形成するために金属元素を含む該障壁層を形成し、基板温度は、前記高温スパッタリングプロセスの間、70 ~ 200 の温度で保持される、該工程と、

を含み、

前記アニーリングする工程は、前記絶縁性層の前記表面から水分を除去する工程を更に含み、

前記絶縁性層は、フッ化炭素 ( C F x ) 膜を含んでおり、

前記高温スパッタリングプロセスは、前記絶縁性層の表面上にカーボンリッチな表面を形成しつつ、前記絶縁性層の表面からフッ素を除去する効果を有している、

半導体デバイスの製造方法。

## 【請求項 21】

前記高温スパッタリングプロセスは、

前記高温スパッタリングプロセスの初期段階において、金属フッ化物溶液を形成する工程と、

前記初期段階後、前記絶縁性層の前記表面から前記金属フッ化物溶液を蒸発させる工程と、

10

20

30

40

50

を更に含んでいる請求項2\_0に記載の方法。

【請求項22】

前記障壁層を形成した後にポストアニーリング処理を行う工程を更に含み、前記ポストアニーリング処理は、50～200の温度において180秒を超えない期間に亘って行われる請求項1\_6又は2\_0に記載の方法。

【請求項23】

絶縁性層の表面を不活性ガス雰囲気に露出しつつ、所定の条件下において前記絶縁性層をアニーリングする工程と、

前記アニーリングする工程の後に高温スパッタリングプロセスを行う工程であって、前記絶縁性層と障壁層との界面に金属-C結合を形成するために金属元素を含む該障壁層を形成し、基板温度は、前記高温スパッタリングプロセスの間、70～200の温度で保持される、該工程と、

を含み、

前記アニーリングする工程は、前記絶縁性層の前記表面から水分を除去する工程を更に含み、

前記絶縁性層は、フッ化炭素(CFx)膜を含んでおり、

前記絶縁性層は、ラジアルライൻスロットアンテナ(RLSA)マイクロ波プラズマ処理デバイスを用いて、所定の設定条件下において形成される、

半導体デバイスの製造方法。

【請求項24】

前記所定の設定条件は、25mTorr～30mTorrの圧力と、1500W～2000Wのマイクロ波出力とを含んでいる請求項2\_3に記載の方法。

【発明の詳細な説明】

【技術分野】

【0001】

本出願は、米国仮出願シリアル番号第61/205,752号(出願日:2009年1月22日、名称:「Surface Treatment for a Fluorocarbon Film」)及び米国仮出願シリアル番号第61/207,971号(出願日:2009年2月17日、名称:「Metal Formation of CFx Film」)からの優先権を主張し、両出願の内容は全て、援用により本明細書中に組み込まれる。

【0002】

本発明は、半導体デバイス及びその製造方法に関する。より詳細には、本発明は、フッ化炭素(CFx)によって構成された層間絶縁性層と金属で構成された障壁層との間の接着性を向上させる表面処理方法及び障壁層形成方法に関する。

【背景技術】

【0003】

近年、半導体デバイスの高速稼動及び小型化を達成するために、多層配線構造が用いられている。しかしながら、これらの構造には、前記配線層の全配線抵抗及び寄生容量の増加に起因した配線遅延という問題がある。

【0004】

銅(Cu)などの低抵抗配線材料を相互接続体として用いた場合、配線抵抗が低下する。一方、低誘電率又は低k材料を用いれば、寄生容量を低下させることができる。特に、フッ素が付加された炭素(フッ化炭素:CFx)を絶縁性層として用いた場合、寄生容量の低下及び半導体デバイスの動作速度向上を達成することができる。

【0005】

絶縁性層内への銅(Cu)の拡散を回避するために、相互接続体と絶縁性層との間に障壁層が設けられる。半導体デバイスの障壁層は、チタン(Ti)、タンタル(Ta)、タンゲステン(W)、ルテニウム(Ru)又はリン(P)から構成される。

【0006】

10

20

30

40

50

絶縁性層の材料としてフッ化炭素 (C F x) を用いた場合、C F x 層に含まれているフッ素が、C F x 層と障壁層との界面におけるフッ素化反応の原因となる。その結果、C F x 層と障壁層との間の接着性が低下し、結果として、絶縁性層と相互接続体との間の接着性が低下する。

#### 【0007】

一方、フッ化炭素 (C F x) 材料は、主に金属元素で構成される障壁層との十分な接着性を有する必要がある。半導体デバイス製造においては、後続プロセス、例えば、化学的及び機械的研磨 (C M P) プロセス、例セッサワイヤ接合プロセスが用いられるため、さらなる応力が基板に附加される。そのため、障壁層と C F x 絶縁性層との間の接着が弱いと、障壁層が絶縁性層から剥離する場合がある。

10

#### 【0008】

本発明は、上述した問題に鑑みて提案される。本発明により、絶縁性層と障壁層との界面におけるフッ素化反応を抑制するための表面処理方法が提供される。更に、本発明により、絶縁 (insulating) 層と障壁層との間のフッ素化反応を抑制しつつ、絶縁 (insulating) 層と障壁層との間の接着性を増加させるための障壁層形成方法が提供される。

#### 【発明の概要】

#### 【0009】

本発明の一側面によると、半導体デバイスを製造する方法が提供される。前記方法は、フッ化炭素 (C F x) 膜を含んだ絶縁性層をアニーリングする工程と、金属元素を含んだ障壁層を前記絶縁性層上に形成する工程とを含んでいる。前記障壁層は、前記アニーリング工程の後、高温スパッタリングプロセスによって形成される。

20

#### 【0010】

本発明の第 2 の側面によると、半導体デバイスを製造する方法が提供される。前記方法は、炭素対フッ素の組成比 (C / F) が 1 を超えるカーボンリッチな表面を形成するよう、絶縁性層上に前処理プロセスを行う工程を含んでいる。前記絶縁性層は、前記前処理プロセスを実施する前には、任意の炭素対フッ素組成比を有したフッ化炭素 (C F x) を含んでいる。

#### 【0011】

本発明の第 3 の側面によると、半導体デバイスを製造する方法が提供される。前記方法は、絶縁性層の表面を不活性ガス雰囲気に露出しつつ、所定の条件下において前記絶縁性層をアニーリングする工程と、前記アニーリング工程後に高温スパッタリングプロセスを行う工程であって、前記絶縁性層と前記障壁層との界面において金属 - C 結合が形成されるよう、金属元素を含んだ障壁層を形成する工程とを含み、前記高温スパッタリングプロセスの間、基板温度は約 70 ~ 200 において維持される。前記アニーリング工程は、前記絶縁性層の前記表面から水分を除去する工程を更に含んでいる。

30

#### 【図面の簡単な説明】

#### 【0012】

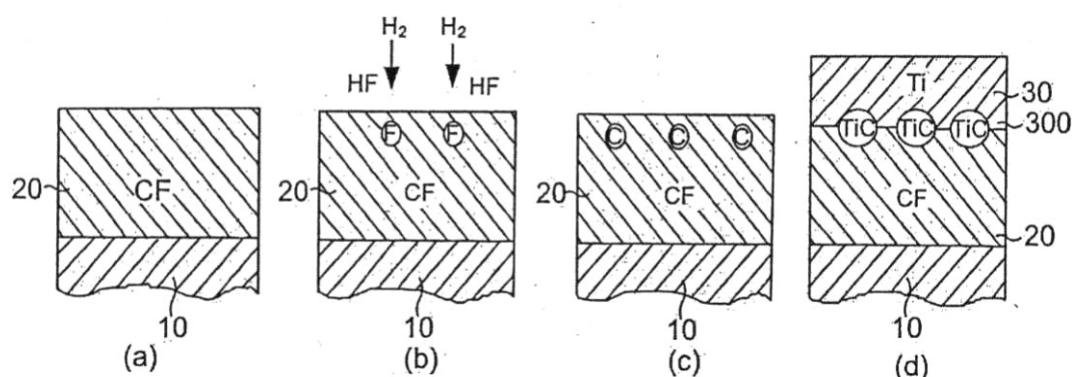

【図 1】図 1 は、水素プラズマを用いた C F x 前処理プロセスの一実施形態の模式図である。

40

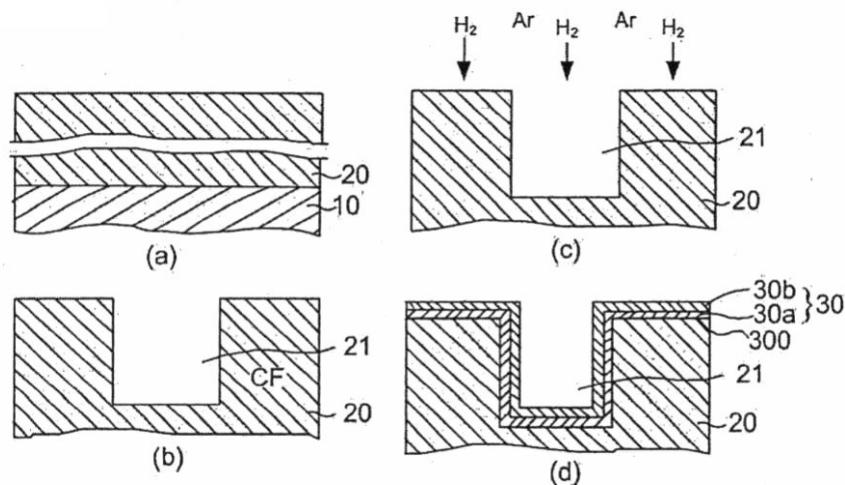

【図 2】図 2 は、水素プラズマを用いた C F x 前処理プロセスの別の実施形態の模式図である。

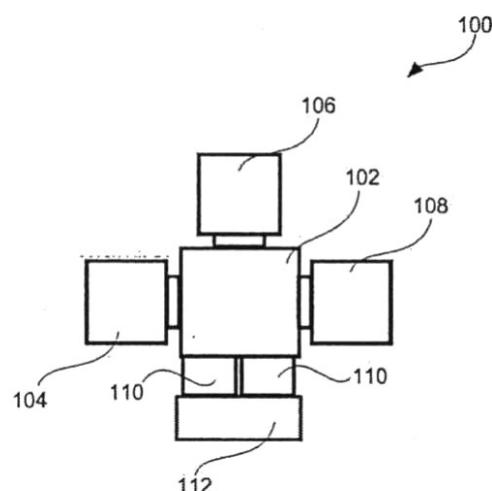

#### 【図 3】図 3 は、スパッタリングデバイスの一実施形態の模式図である。

【図 4】図 4 は実験サンプルの平面図であり、接着剤をその表面に塗布した後の様子と、そのブリスター及びテープ試験結果を示している。

#### 【図 5】図 5 は、図 4 に示す実験サンプルの前半部分の断面図及び表面図である。

#### 【図 6】図 6 は、図 4 に示す実験サンプルの後半部分の断面図及び表面図である。

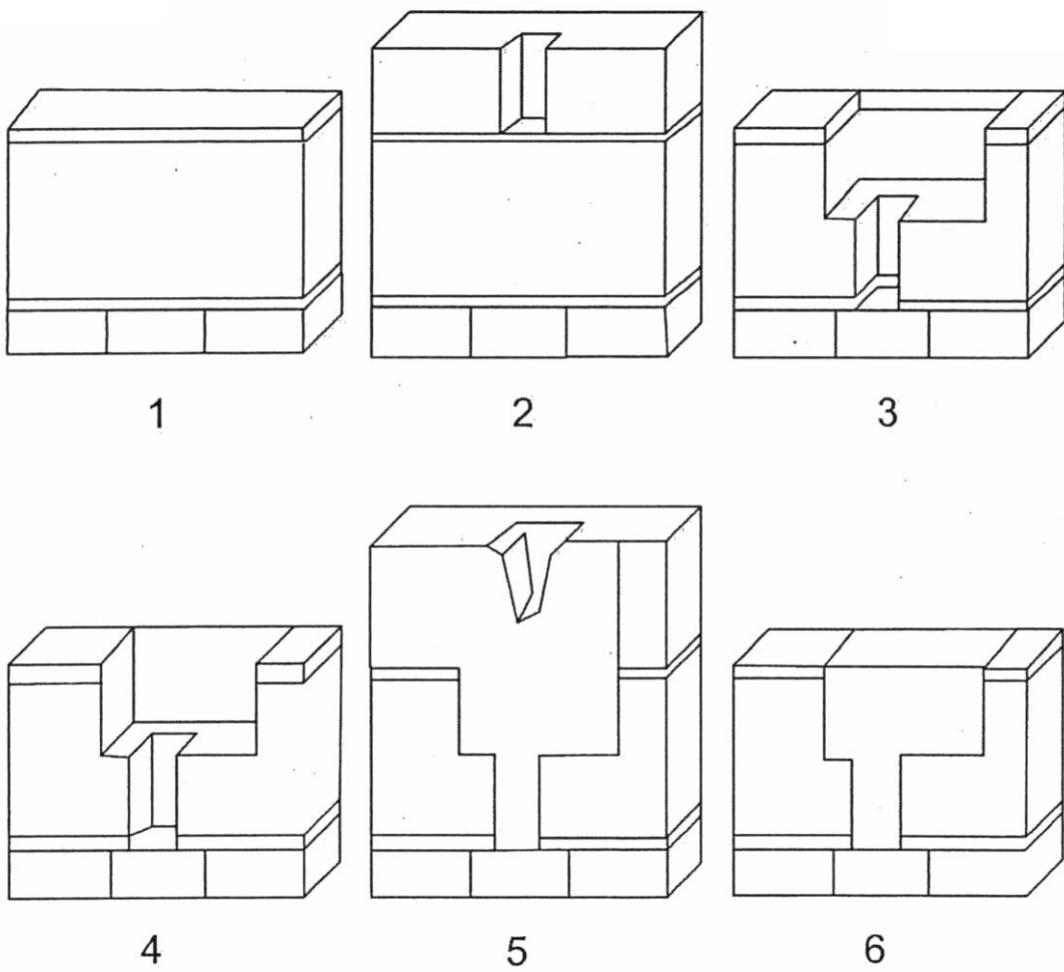

【図 7】図 7 は、デュアルダマシン型銅相互接続構造の実施形態の製造プロセスの模式図である。

#### 【図 8】図 8 は、多層構造の C F x 絶縁性層の断面図である。

50

【図9】図9は、フッ化物の蒸気圧曲線を温度の関数として示している。

【図10】図10は、多様な実験サンプルのターゲット構造と、障壁層の厚さの測定の際に用いられる前記サンプルのXRF強度とを示している。

【図11】図11は、実験サンプルのスパッタリング時間の関数としてのXRF強度を示している。

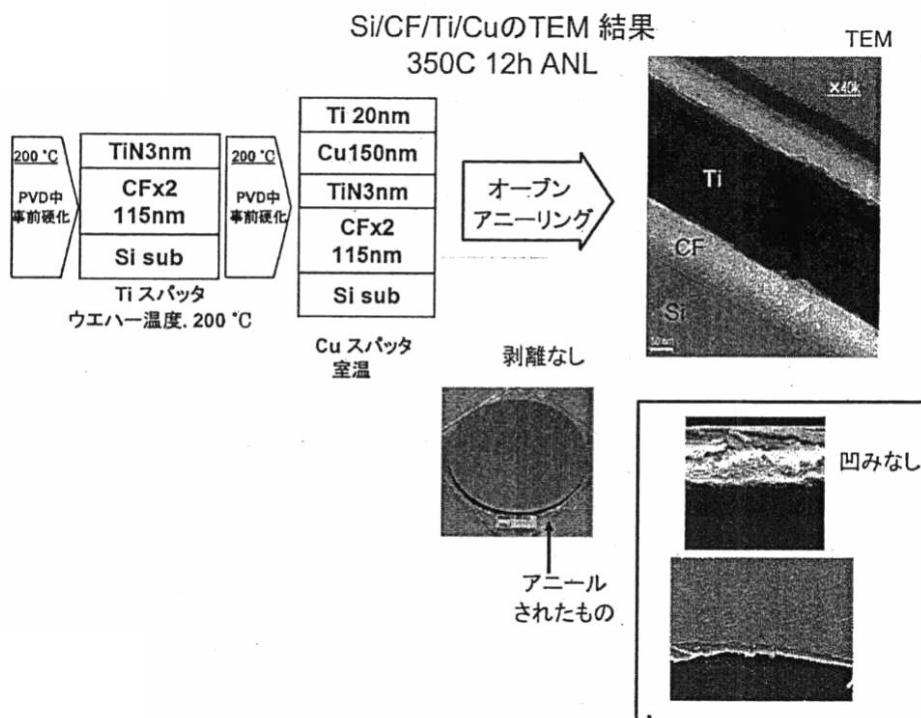

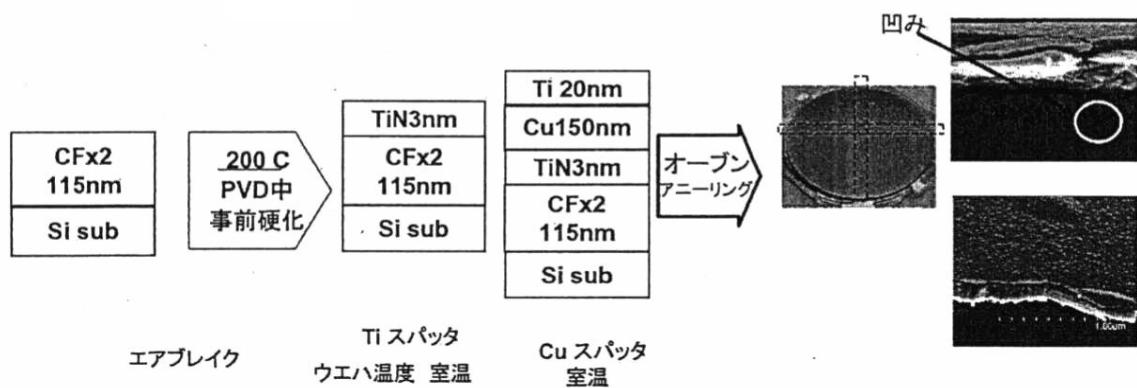

【図12】図12は、実験サンプル及びそのプロセスフローの一例の断面図及び表面図を示している。

【図13】図13は、別の実験サンプルの一例の断面図及び表面図であり、そのプロセスフロー、プリスター試験結果、及びテープ試験結果を示している。

【図14】図14は、別の実験サンプルの一例の断面図及び表面図であり、そのプロセスフロー、プリスター試験結果、及びテープ試験結果を示している。 10

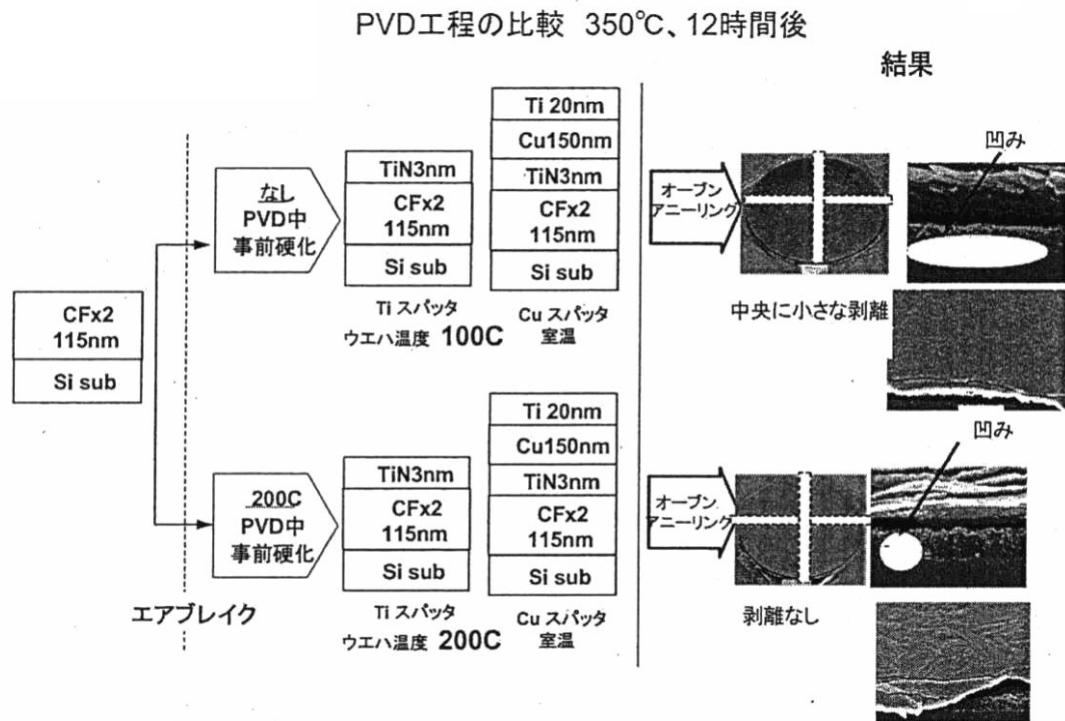

【図15】図15は、実験サンプルの別の実施形態の一例のターゲット構造及びプロセスフローであり、そのプリスター結果及びテープ試験結果を示している。

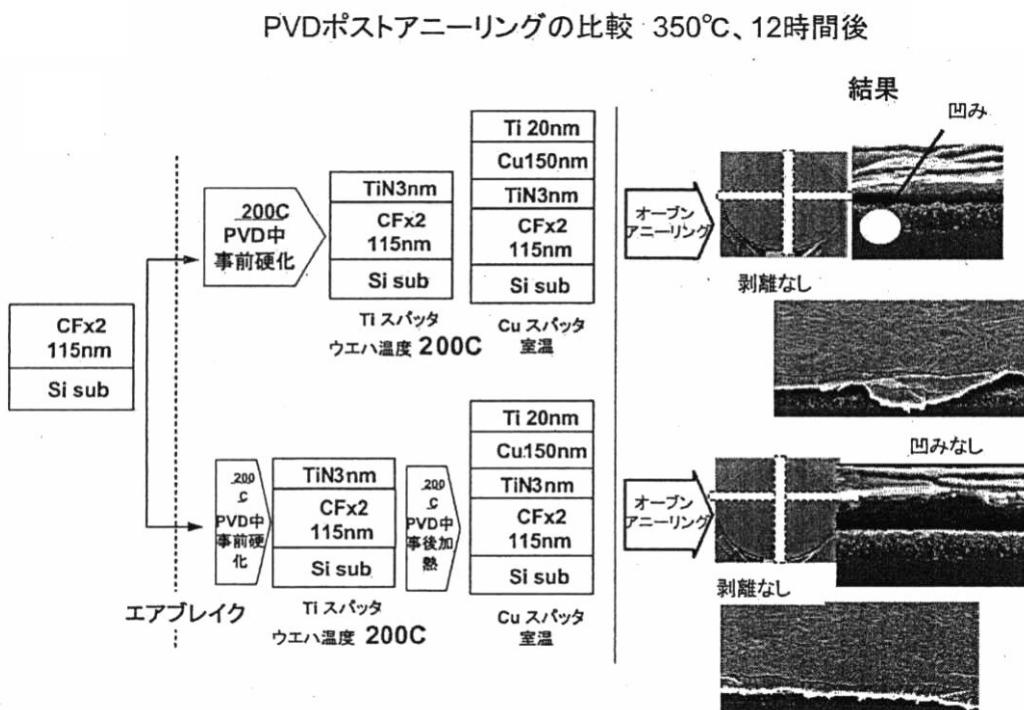

【図16】図16は、図15中に示す実験サンプルの断面図及び表面図を示している。

【図17】図17は、実験サンプルの別の実施形態のターゲット構造及びプロセスフローであり、接着剤テープ適用後の平面図と、プリスター試験結果と、テープ試験結果とを示している。

【図18】図18は、図17に示す実験サンプルの断面図及び表面図を示している。

【図19】図19は、実験サンプルの実施形態及びそのプロセスフローの断面図及び表面図を示している。 20

【図20】図20は、実験サンプルの別の実施形態及びそのプロセスフローの断面図及び表面図を示している。

【図21】図21は、実験サンプルの更に別の実施形態及びそのプロセスフローの断面図及び表面図を示している。

#### 【発明を実施するための形態】

##### 【0013】

以下、本発明の実施形態について、添付図面を参照しながら説明する。図面中、本発明の好ましい代表的な実施形態が図示される。以下の説明は、本開示の範囲、適用性又は構成を限定することを意図しておらず、好ましい代表的な実施形態についての以下の記載により、本開示の好ましい代表的な実施形態の実施を可能にする記載が当業者に提供される。 30 本発明は、添付の特許請求の範囲に記載のような本発明の意図及び範囲から逸脱することなく、異なる形式においても実現可能である点に留意されたい。

##### 【0014】

本開示は、主に、半導体デバイス及びその製造プロセスに関する。より詳細には、本開示は、絶縁性層と障壁金属層との間の接着性を向上させる、新規な表面処理プロセス及び障壁金属層形成プロセスに関する。

##### 【0015】

本発明の実施形態は、絶縁性層からの障壁層の剥離を回避し、且つ、相互接続体からの銅(Cu)が絶縁性層内に浸透するのを回避するプロセスに関する。これは、以下の2つの別個の方法を通じて、達成される。すなわち、1)前記絶縁性層の表面上に前処理プロセスを適用した後、前記障壁層を形成する方法、及び、2)高温スパッタリングプロセスを用いて前記障壁層を形成する方法の2つである。 40

##### 【0016】

前記前処理プロセスをフッ化炭素(CFx)絶縁性層の表面上に適用することにより、前記絶縁性層の表面上のフッ素濃度が低下する。その結果、カーボンリッチな表面(carbon-rich surface)が前記CFx絶縁性層の表面上に形成され、これにより、前記絶縁性層の表面上に前記障壁層が形成される際の金属-C結合生成が支援される。

##### 【0017】

主に金属元素によって構成されている前記障壁層の形成において用いられる高温は、前記 50

$\text{C F}_x$  層と前記障壁層との界面におけるフッ素化反応をもたらす。これにより、高い蒸気圧を有するフッ化物が、前記  $\text{C F}_x$  絶縁性層の表面から蒸発し、炭素 (C) 濃度が上昇する。その結果、前記絶縁性層のカーボンリッチな表面が形成され、これにより、前記障壁層と前記絶縁性層との界面における金属 - C 結合形成が支援される。

【0018】

本発明に係る半導体デバイスの製造プロセスは、以下の工程を含んでいる：(1)  $\text{C F}_x$  絶縁性層を形成する工程、(2) 前処理プロセスを行って、前記  $\text{C F}_x$  層の表面上のフッ素濃度を低下させる工程、(3) 基板をプレアニーリングする工程、(4) 金属元素を含んだ前記障壁層を高温スパッタリング法を用いて形成する工程、(5) 前記基板をポストアニーリングする工程、(6) 銅 (Cu) シード層を形成する工程、及び(7) 電解めっき法を用いて銅 (Cu) 相互接続を形成する工程。

10

【0019】

本発明の一実施形態によると、前記  $\text{C F}_x$  層の表面上のフッ素濃度を低下させる工程は、前記絶縁性層の表面をアルゴン (Ar) などの不活性ガス雰囲気に曝しながら、所定の条件下において前記絶縁性層をアニーリングすることによって実行される。

【0020】

別の実施形態によれば、前記  $\text{C F}_x$  層の表面上のフッ素濃度を低下させる工程は、前記絶縁性層の表面を、水素 ( $\text{H}_2$ ) などの反応性ガス雰囲気に曝しながら、所定の条件下において前記絶縁性層をアニーリングすることによって行われる。

20

【0021】

更に別の実施形態によれば、前記  $\text{C F}_x$  層の表面上のフッ素濃度を低下させる工程は、前記絶縁性層にプラズマ処理を適用することによって行われる。この実施形態において、前記絶縁性層は前記プラズマに曝され、前記プラズマは、所定の条件下において水素 ( $\text{H}_2$ ) 原子又は炭素 (C) 原子を含んだガスを励起することによって生成される。

【0022】

更に別の実施形態によれば、前記  $\text{C F}_x$  層の表面上のフッ素濃度を低下させる工程は、金属元素の水酸化物を含んだ溶液中に前記絶縁性層を浸漬させた後、前記絶縁性層を純水で洗浄し、最後に前記絶縁性層を乾燥することによって行われる。

【0023】

更に別の実施形態によれば、前記絶縁性層を乾燥させる工程は、従来のドライヤを用いて行われるか、又は、前記絶縁性層を室温において空気乾燥することにより行われる。

30

【0024】

更に別の実施形態によれば、金属元素を含んだ前記障壁層を高温スパッタリング法を用いて形成する工程は、スパッタリングプロセス全体にわたって、前記基板温度を約 70 ~ 約 200 の温度で維持することによって行われる。

【0025】

本発明による半導体デバイスの製造に用いられるプロセスについて、下記の独立した各セクションにおいて詳述する：前記フッ化炭素絶縁性層の形成、前記  $\text{C F}_x$  層の表面上のフッ素濃度を低下させるための前記絶縁性層の表面処理、前記基板のプレアニーリング、前記障壁層の形成、前記基板のポストアニーリング、前記銅 (Cu) シード層の形成、及び前記銅 (Cu) 相互接続層の形成。最初に、フッ化炭素 ( $\text{C F}_x$ ) 絶縁性層を形成するプロセスについて説明する。

40

【0026】

(フッ化炭素 ( $\text{C F}_x$ ) 絶縁性層を形成するプロセス)

本発明に関連する絶縁性層は、炭素とフッ素との比が任意であるフッ化炭素 ( $\text{C F}_x$  :  $k \sim 2.2$ ) を用いて形成される。フッ化炭素 ( $\text{C F}_x$ ) 絶縁性層が、基板表面上に設けられる。この基板表面上には、トランジスタなどの何らかの微細構造が形成されている。前記フッ化炭素 ( $\text{C F}_x$ ) 絶縁性層は、多孔質材料などの他の低  $k$  材料絶縁性層と比較して、より高密度である。そのため、前記フッ化炭素 ( $\text{C F}_x$ ) 層は、より高い機械的強度を有している。十分な相互接続を得るための前記絶縁性層の所望の厚さは、例えば、約 10

50

0 ~ 1 2 0 nm である。この実施形態において、約 1 1 5 nm の厚みを、前記フッ化炭素 (CF<sub>x</sub>) 絶縁性層の形成の際の目標とする。前記 CF<sub>x</sub> 絶縁性層の形成は、ラジアルラインスロットアンテナ (RLSA) マイクロ波プラズマ処理デバイスを用いて、所定の設定条件で行われる。例えば、厚さ約 1 1 5 nm のフッ化炭素絶縁性 (CF<sub>x</sub>) 層を形成する際には、流量約 1 0 0 sccm のアルゴン (Ar) ガスをプラズマ励起ガスとして用いる。前記形成ガスとしては、流量約 2 0 0 sccm の C<sub>5</sub>F<sub>8</sub> ガスを用いる。前記 RLSA マイクロ波プラズマ処理デバイスの内部を調節し、圧力約 2 5 mTorr において維持し、入力電力を約 1 5 0 0 W とする。前記 CF<sub>x</sub> 層は比較的低温において形成され、損傷を受けやすいため、前記ウエハ温度は、好ましくは 3 0 0 ~ 4 0 0 の温度に維持される。この実施形態においては、ウエハ状態温度は約 3 5 0 に設定される。更に、処理時間を 1 5 0 秒に設定し、RLSA マイクロ波プラズマ処理デバイスには、バイアスを付加しない。

10

#### 【0027】

(前記 CF<sub>x</sub> 層のフッ素濃度を低下させるための前処理プロセス)

半導体デバイス製造において用いられる従来のプロセスにおいて、障壁層を CF<sub>x</sub> 絶縁性層上に形成する際、前処理プロセスは何も用いられない。そのため、CF<sub>x</sub> 絶縁性層中に含まれるフッ素が障壁層内に拡散し、その結果、障壁層と絶縁性層との界面におけるフッ素化反応に起因して、障壁層が腐食する。そのため、相互接続体からの銅 (Cu) が絶縁性層内に拡散し、その結果、障壁層が絶縁性層 (CF<sub>x</sub>) から剥離する。CF<sub>x</sub> 絶縁性層表面上のフッ素濃度を低下させることにより、絶縁性層からのフッ素と障壁層からの金属元素との間の反応であるフッ素化反応を抑制することができる。このような低下に起因して、前記 CF<sub>x</sub> 絶縁性層表面上の炭素 (C) 濃度が上昇し、その結果、障壁層と絶縁性層との界面において、金属元素と炭素原子との間の結合 (金属元素の炭化物) の比が上昇する。そのため、腐食に起因する障壁層の剥離を回避しつつ、CF<sub>x</sub> 層と障壁層との接着性が向上する。更に、前記金属元素の炭化物を障壁層と絶縁性層との界面に形成することにより、CF<sub>x</sub> 絶縁性層中への銅 (Cu) の拡散を回避することができる。

20

#### 【0028】

本発明によると、上記した機構を用いてフッ化炭素 (CF<sub>x</sub>) 絶縁性層の表面上のフッ素濃度を低下させる方法がいくつか存在する。これらの方法は、以下のようなものである：1) 水素 (H<sub>2</sub>) アニーリング、2) 水素 (H<sub>2</sub>) プラズマ処理、3) 金属元素の水酸化物中への浸漬後の水洗浄、及び 4) 一酸化炭素 (CO) プラズマ処理。以下、上述したプロセスの各々について説明する。

30

#### 【0029】

##### 1) 水素 (H<sub>2</sub>) によるアニーリング：

この実施形態において、CF<sub>x</sub> 層の表面上のフッ素濃度を低下させる工程は、絶縁性層表面を水素 (H<sub>2</sub>) などの反応性ガス雰囲気に露出させつつ、所定の条件下において絶縁性層をアニーリングすることにより行われる。この実施形態において、前記絶縁性層をアニーリングする工程は、約 1 0 0 以上の温度において、前記水素 (H<sub>2</sub>) ガスを前記処理デバイス内に導入することにより行われる。水素 (H<sub>2</sub>) は、前記 CF<sub>x</sub> 層の表面上のフッ素 (F) と反応し、フッ化水素 (HF) となる。その後、フッ化水素 (HF) は前記 CF<sub>x</sub> 層の表面から脱着し、その結果、カーボンリッチな表面が生成される。

40

#### 【0030】

##### 2) 水素 (H<sub>2</sub>) によるプラズマ処理：

水素 (H<sub>2</sub>) プラズマ処理プロセスは、CF<sub>x</sub> 絶縁性層表面上のフッ素濃度を低下させるための別の方法である。図 1 に、水素プラズマを用いた CF<sub>x</sub> 前処理プロセスの実施形態が示されている。このプロセスでは、先ず初めに、CF<sub>x</sub> 絶縁性層 20 を基板 10 上に形成する。CF<sub>x</sub> 層 20 は、段落 [0026] において説明したプロセスと同じプロセスにより、RLSA マイクロ波プラズマ処理デバイスを用いて形成することができる。次の工程において、水素 (H<sub>2</sub>) ガスを処理デバイス内に導入し、従来の方法及びデバイスを用いて水素 (H<sub>2</sub>) 原子を励起することにより、水素プラズマを発生させる。このようにし

50

て、基板 10 上に形成されたフッ化炭素 (C F x) 絶縁性層 20 を水素プラズマに露出させることにより、C F x 前処理プロセスが行われる。図 1 (b) に示すように、C F x 表面層内に含まれるフッ素 (F) が、水素プラズマと反応することにより、前記表面から隔離される。いくつかの実施形態において、水素 (H<sub>2</sub>) ガスに加えて、水素原子を含んだ他のガスを用いてもよい。水素原子を含んだ他のガスの例としては、シランガス (SiH<sub>4</sub>) 又はメタンガス (CH<sub>4</sub>) が挙げられる。その後、前記 C F x 層の表面上に炭素が豊富な表面が形成される (図 1 (c))。

#### 【0031】

図 1 (d) は、水素プラズマを用いて C F x 前処理プロセスを行った後の、前記半導体デバイスの製造プロセスの最終工程を示す。最終工程において、絶縁性層 20 のカーボンリッチな表面上に障壁層 30 を形成する。この障壁層 30 は、実質的に、チタン (Ti) などの金属元素からなる。このカーボンリッチな表面により、金属元素 300 の炭化物が生成し、障壁層 30 と絶縁性層 20 との間の接合の強化が支援される。この実施形態において、金属元素 300 の炭化物は、チタン炭化物 (TiC) によって構成される。加えて、障壁層 30 は、スパッタリング法又は化学的蒸気 (CVD) 方法などの従来の方法を用いて形成される。いくつかの実施形態において、他の金属元素を用いて障壁層 30 を形成してもよい。他の金属元素の例としては、タンタル (Ta)、ルテニウム (Ru)、又はタンゲステン (W) が挙げられる。

#### 【0032】

図 2 には、水素プラズマを用いた C F x 前処理プロセスの別の実施形態が示されている。この実施形態においては、単一のダマシン型相互接続構造が用いられる。C F x 絶縁性層 20 を基板 10 上に形成した後、エッチングプロセスにより開口部 21 を C F x 絶縁性層 30 内に形成する。次の工程において、水素 (H<sub>2</sub>) ガスを処理デバイス内に導入し、励起水素プラズマを用いて C F x 前処理プロセスを行うことにより、絶縁性層 20 を水素プラズマの露出させる。この実施形態において、前記水素ガスと共に、アルゴンガス (Ar) などの不活性ガスを前記処理デバイス内に付加する。最終工程において、障壁層 30 は、開口部 21 の内側と、C F x 層の表面 20 上とに形成される。障壁層 30 は多層構造であり、第 1 の層 30a が C F x 層上に形成され、第 2 の層 30b が第 1 の層上に形成される。多層構造 30 の形成に用いられる金属元素の例としては、チタン / チタン窒化物 (Ti / TiN)、チタン / タンタル - 窒化物 (Ti / TaN)、及びタンタル / タンタル - 窒化物 (Ta / TaN) が挙げられる。水素プラズマ処理を用いた第 1 の実施形態と同様に、金属元素 300 の炭化物は、水素プラズマを用いた C F x 前処理プロセス実行後に得られるカーボンリッチな表面の存在に起因して、C F x 絶縁性層 20 と障壁層 30 との界面に形成される。

#### 【0033】

##### 3) 金属元素の水酸化物中への浸漬後における水を用いた洗浄 :

この実施形態において、C F x 絶縁性層は、単純に、金属元素の水酸化物を含んだ溶液中に浸漬される。金属元素の例としては、カルシウム (Ca)、ストロンチウム (Sr)、バリウム (Ba)、ナトリウム (Na)、カリウム (K)、又はマグネシウム (Mg) が挙げられる。金属元素の水酸化物、例えばカルシウムの水酸化物 (Ca(OH)<sub>2</sub>) 中に前記絶縁性層を浸漬させた後、C F x 絶縁性層を純水によって洗浄し、従来の方法によって乾燥させる。一実施形態において、前記乾燥工程は、従来の乾燥器を用いて行われ得る。別の実施形態において、前記乾燥工程は、前記絶縁性層を室温において空気乾燥することによって行われ得る。

#### 【0034】

##### 4) 一酸化炭素 (CO) によるプラズマ処理

この方法において、前記 C F x 前処理プロセスは、一酸化炭素 (CO) プラズマを用いて行われる。一酸化炭素 (CO) プラズマ中に含まれる炭素 (C) により、C F x 表面層内に含まれるフッ素 (F) との C F 結合が形成される。このような C F 結合の形成に起因して、フッ素 (F) が前記 C F x 表面層から脱着する。そのため、このプラズマ処理におい

10

20

30

40

50

て、一酸化炭素 (CO) ガスに加えて、メタンガス (CH<sub>4</sub>) などの他の炭素原子含有ガスを用いてよい。

【0035】

プラズマ処理 (#2 及び #4) に基づいた方法によれば、ガス含有水素 (H<sub>2</sub>) 原子又は炭素 (C) 原子の励起によって得られたプラズマに前記CF<sub>x</sub>表面層を露出させることにより、CF<sub>x</sub>表面層内に含まれるフッ素 (F) を前記表面から隔離させることができる。そのため、水素 (H<sub>2</sub>) ガス又は一酸化炭素 (CO) ガスの他にも、任意のガス含有水素原子又は炭素原子をプラズマ処理デバイスに付加することができる。これらのガスの例としては、シリコンガス (SiH<sub>4</sub>)、メタンガス (CH<sub>4</sub>) などが挙げられる。

【0036】

RLSAマイクロ波プラズマ処理デバイスは、所定の条件下において水素 (H<sub>2</sub>) プラズマ又は一酸化炭素 (CO) プラズマを生成する際に用いられる。例えば、RLSAマイクロ波プラズマ処理デバイス内の圧力は、100 ~ 2000 mTorr に調節することができる。この実施形態において、以下の条件は、水素 (H<sub>2</sub>) プラズマ及び一酸化炭素 (CO) プラズマ双方を生成するための所定の条件として用いられる。第1に、RLSAマイクロ波プラズマ処理デバイス内部の圧力を約1200 mTorr に設定し、第2に、少なくとも約500Wのマイクロ波出力をRLSAマイクロ波プラズマ処理デバイスに付加し、第3に、処理時間を約5秒に設定する。

【0037】

上述したように、上記した方法すべてにおいて用いられる機構は、フッ素濃度を低下させることにより、CF<sub>x</sub>絶縁性層からのフッ素 (F) と障壁層からの金属元素との間のフッ素化反応を抑制するためのものである。フッ素化反応を抑制することにより、前記CF<sub>x</sub>層の表面上のフッ素濃度を低下させ、これにより、前記CF<sub>x</sub>層の表面上にカーボンリッチな表面を得る。その結果、カーボンリッチな表面上に障壁層が形成される際、障壁層と絶縁性層との界面において、金属元素と炭素原子との結合 (金属元素の炭化物) の割合が増加する。

【0038】

5) アルゴン (Ar) アニーリング処理 :

別の実施形態において、CF<sub>x</sub>絶縁性層表面上のフッ素濃度を低下させるために、異なる機構が用いられる。この別の実施形態においては、アルゴン (Ar) アニーリング処理を用いて、フッ化炭素 (CF<sub>x</sub>) 絶縁性層の表面上の水分を除去する。CF<sub>x</sub>層の表面上に水分が有ると、フッ素との結合が弱くなる。フッ素原子との結合が弱い場合、例えば、四フッ化チタン (TiF<sub>4</sub>) などの四フッ化金属元素が、障壁層とCF<sub>x</sub>絶縁性層との界面に発生する。四フッ化チタン (TiF<sub>4</sub>) は蒸気圧が高いため、CF<sub>x</sub>絶縁性層と金属元素との接着性が低下する。そのため、アルゴン (Ar) アニーリング処理により水分を除去することで、結合の弱いフッ素をフッ化炭素 (CF<sub>x</sub>) 絶縁性層表面から低減し易くし、これにより、この上にカーボンリッチな表面を形成する。この別の実施形態においては、前記アニーリング工程を不活性ガス雰囲気中において所定の条件下において行うことが好ましい。不活性ガス雰囲気の例としては、ヘリウム (He)、ネオン (Ne)、アルゴン (Ar)、クリプトン (Kr)、キセノン (Xe) などが挙げられる。この実施形態においては、CF<sub>x</sub>絶縁性層のアニーリングにおける経済効率の観点から、アルゴン (Ar) ガスをアニーリングガスとして用いる。

【0039】

本発明のアルゴン (Ar) アニーリング処理を行う際には、スパッタリングデバイスが用いられる。しかしながら、スパッタリングデバイスとは別個のアニーリングデバイスを用いてもよい。上述したように、アルゴン (Ar) アニーリング処理を行う際には、所定の条件が用いられる。例えば、スパッタリングデバイス内部の圧力を100 mTorr ~ 1 Torr に調節することが好ましい。この実施形態においては、スパッタリングデバイス内部の圧力を約10 mTorr に設定し、状態温度を約200 °C に設定する。また、処理時間を約5分 (300秒) に設定する。

10

20

30

40

50

## 【0040】

図3には、スパッタリングデバイス100の実施形態の模式図が示されている。この図に示すように、スパッタリングデバイスの中央上に、真空移送チャンバ102が設けられている。その周囲の領域において、アニーリングチャンバ104、障壁層スパッタリングチャンバ106及び銅スパッタリングチャンバ108が、真空移送チャンバ102を包囲している。スパッタリングデバイス100の下側には、少なくとも1つのロードロックチャンバ110が真空移送チャンバ102に接続され、移送チャンバ112がロードロックチャンバ110に接続され、これにより、ウエハがカセット(図示せず)からロードロックチャンバ110へと移送される。

## 【0041】

10

## 実験サンプル

障壁特性と、事前処理されたフッ化炭素(CFx)絶縁性層上の障壁層の接着とを評価するため、いくつかの実験サンプルを製造した。その後、これらの実験サンプルそれぞれに対し、ブリスター試験及びテープ試験を行った。図4は、前記実験サンプルそれぞれにおけるCFx絶縁性層の表面処理において用いられる構造及びプロセスを示す。加えて、この図中に、セロハンテープをサンプル表面上に接着した後の実験サンプルの平面図と、ブリスター試験及びテープ試験の結果とを示す。この評価において用いられる構造は、バルケイ素(Si)基板上に形成されたフッ化炭素(CFx)絶縁性層を含んでいる。フッ化炭素(CFx)絶縁性層は、厚さ約115nmであり、段落[0026]において説明したプロセスを用いて、RLSAプラズマ処理デバイス内に形成される。前記実験サンプルそれぞれにおけるCFx絶縁性層の表面上にCFx前処理プロセスを行った後、主にチタン(Ti)によって構成され且つ厚さ約3nmである障壁層を、スパッタリングデバイス100を用いてCFx絶縁性層上に形成する。スパッタリングデバイス100中においては、チタン(Ti)をスパッタリング標的として用いる。最終工程において、スパッタリングデバイス100を用いて、厚さ約150nmの銅(Cu)相互接続層を障壁層上に形成する。前記実験サンプルの障壁層は、従来のスパッタリング法又は化学的蒸気(CVD)方法又は電解めっき法を用いて形成され得る。前記障壁層の形成前に、必要ならばアニーリング工程を行って水分又は有機物質を除去してもよい。このアニーリングは、スパッタリング又はCVDデバイスのチャンバを形成する障壁層において、約100～約200の温度で行われる。

20

## 【0042】

30

この評価のために、9個の異なる実験サンプルを製造した。各実験サンプルに対して、表面のフッ素濃度を低下させつつ前記表面上の相対的炭素濃度を増加させるために、CFx絶縁性層表面に別個のCFx前処理プロセスが実行される。図4に示すように、処理の行において、各実験サンプル中のCFx絶縁性層表面に対して行われた表面処理プロセスが要約されている。

## 【0043】

40

(実験サンプル1)：CFx絶縁性層表面上への前処理プロセスは行っていない。図4に示すように、「wo」の記号によって示されるこのサンプルは、ブリスター試験及びテープ試験双方において合格したことが分かった。この実施形態において、炭素/フッ素/酸素の比は、C:F:O = 47:53:0である。

## 【0044】

(実験サンプル2)：この実験サンプルのフッ化炭素(CFx)絶縁性層を、一酸化炭素(CO)アニーリングプロセスによって処理した。この実施形態において、一酸化炭素(CO)ガスを処理デバイス内に導入し、約200の温度で約60秒間に亘って、アニーリングを行った。上記の場合と同様に、このサンプル(#2)は、ブリスター試験及びテープ試験に合格した。

## 【0045】

(実験サンプル3)：フッ化炭素(CFx)絶縁性層表面上に、一酸化炭素(CO)プラズマ処理を行った。RLSAマイクロ波プラズマ処理デバイスを用いて、一酸化炭素(CO)

50

O ) プラズマ処理を行った。この実施形態において、約 3 kW のマイクロ波出力が R L S A マイクロ波プラズマ処理デバイスに適用され、処理時間は、約 10 秒に設定された。段落

【 0046 】

において説明したように、 R L S A マイクロ波プラズマ処理デバイス内部の圧力は、約 1200 mTorr に設定した。上記の場合と同様に、実験サンプル #3 は、ブリスター試験及びテープ試験双方に合格した。この実施形態において、炭素 / フッ素 / 酸素の比は、 C : F : O = 48 : 46 : 6 である。

【 0047 】

( 実験サンプル 4 ) : この実験サンプルにおいては、絶縁性層表面をジシラン ( Si<sub>2</sub>H<sub>6</sub> ) ガスに露出させつつ、絶縁性層をアニーリングすることにより、 C F x 層の表面上のフッ素濃度を低下させる工程を行った。この実施形態において、ジシラン ( Si<sub>2</sub>H<sub>6</sub> ) ガスを処理デバイス内に導入し、アニーリング工程を約 200 の温度において約 60 秒に亘って行った。この実験サンプルは、ブリスター試験及びテープ試験双方に合格した。

【 0048 】

( 実験サンプル 5 ) : C F x 絶縁性層表面に対し、アルゴン ( Ar ) アニーリング処理を用いた事前処理を行った。上述したように、アルゴン ( Ar ) アニーリング処理は、スパッタリングデバイス 100 内において行われる。ここで、アニーリング工程及びスパッタリング工程は、同一処理デバイス内において行ってもよい。また、この実施形態において、スパッタリングデバイスとは別のアニーリングデバイスを用いることもできる。スパッタリングデバイス内部の圧力は約 10 mTorr に設定され、基板温度は約 200 の温度に維持される。この実験サンプルの処理時間は、約 60 秒とした。上記の場合と同様に、実験サンプル #5 は、ブリスター試験及びテープ試験双方に合格した。

【 0049 】

( 実験サンプル 6 ) : C F x 絶縁性層表面に対し、水素 ( H<sub>2</sub> ) アニーリングプロセスによる事前処理を行った。この実験サンプルのアニーリング工程は、約 300 の温度において約 900 秒間に亘って行われる。実験サンプル #6 は、ブリスター試験及びテープ試験双方に合格した。この実施形態において、炭素 / フッ素 / 酸素の比は、 C : F : O = 50 : 50 : 0 である。

【 0050 】

( 実験サンプル 7 ) : フッ化炭素 ( C F x ) 絶縁性層表面上に、水素 ( H<sub>2</sub> ) プラズマ処理を行った。実験サンプル #3 の場合と同様に、 R L S A マイクロ波プラズマ処理デバイスを用いて、水素 ( H<sub>2</sub> ) プラズマ処理を行った。この実施形態において、少なくとも約 500 W のマイクロ波出力が用いられ、処理時間は約 5 秒に設定される。上述したように、 R L S A マイクロ波プラズマ処理デバイス内部の圧力を約 1200 mTorr に設定した。図 4 に示すように、この実験サンプル ( #7 ) の場合、若干の剥離が認められた。この場合、さらなる調査を行ったところ、この剥離の原因は何らかの環境条件であり、そのため、このサンプルは、上記の場合と同様に、ブリスター試験及びテープ試験に合格したことが分かった。この実施形態において、炭素 / フッ素 / 酸素の比は、 C : F : O = 55 : 45 : 0 である。

【 0051 】

( 実験サンプル 8 ) : 先ず、 C F x 絶縁性層が、カルシウム水酸化物 ( Ca(OH)<sub>2</sub> ) 溶液中に浸される。前記浸漬工程後、 C F x 絶縁性層を純水によって洗浄し、室温において空気乾燥させる。実験サンプル #8 は、ブリスター試験及びテープ試験双方に合格した。金属元素の水酸化物を用いた洗浄処理では、炭素 / フッ素 / 酸素間の比についてのデータは得られなかった。

【 0052 】

( 実験サンプル 9 ) : C F x 絶縁性層を、フロロボンダー処理により事前処理した。図 4 に示すように、この実験サンプルの場合、ブリスター試験は合格したが、テープ試験においては不合格となり、障壁層と C F x 絶縁性層との間の接着接合は低かった。

10

20

30

40

50

## 【0053】

図4に示す上記実験結果によれば、フロロボンダー処理を行ったものを除く全ての実験サンプルにおいて、障壁層とCF<sub>x</sub>絶縁性層との間の高接着接合が観察された。しかし、フッ化炭素処理を行った実験サンプル#9においては、低接着接合に起因する障壁層の剥離の可能性がある。

## 【0054】

図5～図6に、走査型電子顕微鏡(SEM)画像を用いた実験サンプル#1～#9それぞれの断面図及び上面図が示されている。SEM画像は、全実験サンプルを約360℃の温度で約1時間に亘ってアニーリングした後に得た。図5及び図6に示すように、実験サンプル#1は、CF<sub>x</sub>絶縁性層上に前処理プロセスが適用されていない状態では、CF<sub>x</sub>層からの障壁層の剥離は示さない。しかし、このサンプルは、障壁特性についていくつかの問題を示した。すなわち、断面図に示すように、CF<sub>x</sub>絶縁性層とケイ素(Si)基板との界面に存在する高輝度粒子に起因して、銅相互接続体からの銅(Cu)が障壁層及びCF<sub>x</sub>絶縁性層をそれぞれ通過することが分かる。そのため、ケイ素(Si)基板と銅(Cu)が結合し、SiCuが発生する。実験サンプル#1の上面図については、凹凸部分がより多数見られたことから、構造の下層中へと銅(Cu)が浸透していることが分かる。

10

## 【0055】

高輝度粒子は、実験サンプル#6の場合を除いて、ほとんど全ての実験サンプル中に見られた。実験サンプル#6の場合、CF<sub>x</sub>絶縁性層表面上に水素(H<sub>2</sub>)アニーリング処理が適用されている。更に、銅(Cu)表面上の凹みも見られなかった。更に、フロロボンダー処理が施された実験サンプル#9の断面図及び表面図から、ケイ素(Si)基板とCF<sub>x</sub>絶縁性層との界面における高輝度粒子の存在と、銅(Cu)表面上の凹みの存在についても、好適と思われる結果が得られた。しかし、実験サンプル#9の場合、プリスター試験及びテープ試験において、CF<sub>x</sub>/金属界面の接着性が悪かった。

20

## 【0056】

フッ素低減処理が施された全ての実験サンプルについて、ケイ素(Si)基板層内への銅(Cu)の拡散について、十分な障壁特性が見られた点に留意されたい。この結果は、Si/CF<sub>x</sub>界面における高輝度粒子の存在及び銅(Cu)表面上の凹みの存在があるのにも拘らず得られている。

30

## 【0057】

## (基板のプレアニーリング)

以下、本発明による半導体デバイス製造プロセスにおいて用いられる第3の工程について説明する。フッ化炭素(CFx)絶縁性層に対して前処理プロセスを行った後、スパッタリングデバイス100を用いて、基板上に事前加熱工程を行う。この熱処理は、障壁層蒸着チャンバー106内において、約50℃～約200℃の基板温度範囲において行われ得る。処理時間は、180秒以下に設定され得る。

## 【0058】

## (主に金属元素によって構成される障壁層を形成するプロセス)

従来の障壁層形成プロセスにおいては、CF<sub>x</sub>絶縁性層と、主にチタン(Ti)などの金属元素で構成された障壁層との間の接着性が悪いという問題があった。このような接着性を改善するために、2重の(又は複数の)障壁層構造が提案されている。この構造では、チタン窒化物(TiN)によって構成された第1の層が絶縁性層上に形成され、チタン(Ti)によって形成された第2の層が、銅相互接続に対向する第1の層上に形成される。しかし、障壁層中にチタン窒化物(TiN)を用いた場合、電気抵抗が高くなるため、信号遅延が増加する。

40

## 【0059】

本発明による主に金属元素によって構成される障壁層は、高温スパッタリング法を用いて形成される。このプロセスにおいて、スパッタリングプロセス全体において、基板温度を比較的高温に保持する。好適な実施形態において基板温度を約70℃～約200℃の温度において加熱及び保持する。基板を上記した温度範囲まで加熱し、スパッタリングプロセ

50

ス全体において基板温度を同一レベルに保持することにより、例えばフッ化炭素（C F x）絶縁性層表面からの高い蒸気圧に基づいて、フッ素原子を Ti F 4 として除去する。

#### 【 0 0 6 0 】

好適な温度範囲の下限を 70 にしている理由としては、フッ化炭素（C F x）絶縁性層の表面上の水分がこの温度において真空中で蒸発し始めるからである。一方、温度範囲の上限を 200 としている理由としては、基板温度が 200 を超えると、下側の導電層の銅（C u）が凝集し始めるからである。その主因としては、銅（C u）がビアホールの底部に露出されると、基板温度による影響を直接受ける点がある。そのため、基板温度がこの上限範囲を超えると、導電層からの銅（C u）が凝集し始める。凝集した銅は、性質が不均一であるため、半導体デバイスにおける使用は困難となる。

10

#### 【 0 0 6 1 】

図 7 に、デュアルダマシン型銅相互接続構造の実施形態の製造プロセスの模式図が示されている。このデュアルダマシン技術は、以下の工程を含んでいる：

- 1 ) 絶縁性層を形成する工程

- 2 ) ビア / 相互接続パターンを形成する工程

- 3 ) ビア / 相互接続溝のエッチング工程

- 4 ) 障壁金属 / シード銅層を形成する工程

- 5 ) 電解めっき法によって銅（C u）を埋設する工程

- 6 ) C u / 障壁金属層の化学機械研磨（C M P）を行う工程

なお、説明を簡潔にするために、前処理プロセス並びにプレアニーリング工程及びポストアニーリング工程は省略している。

20

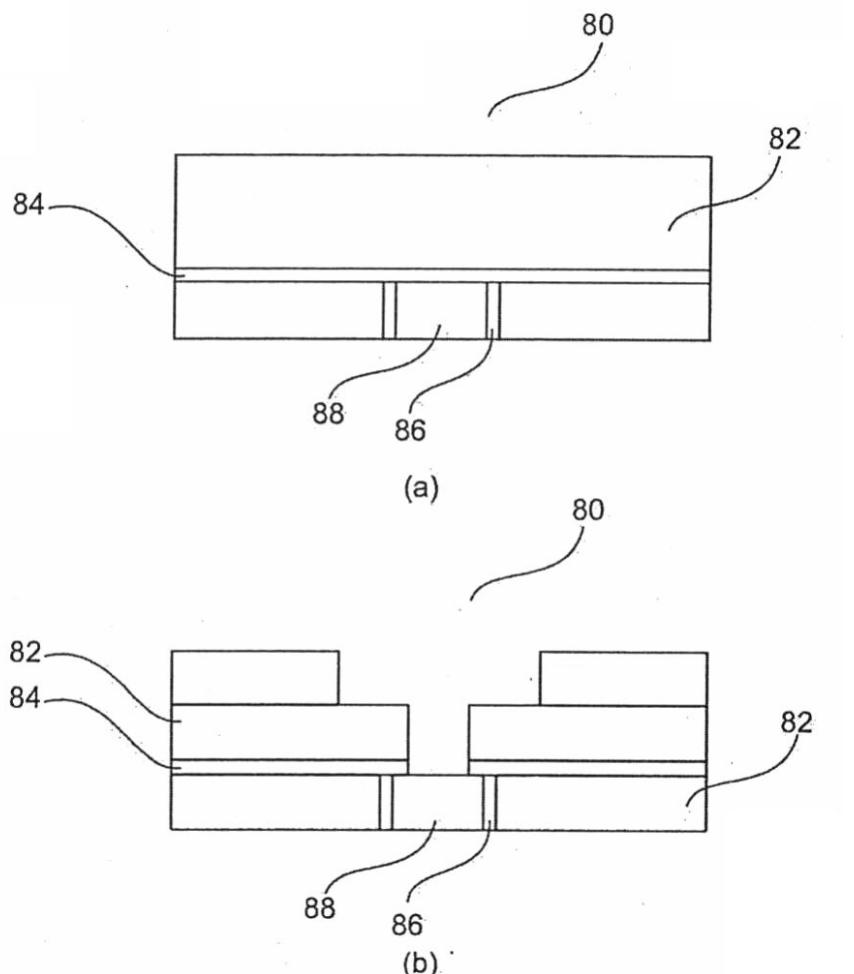

#### 【 0 0 6 2 】

デュアルダマシン技術を用いた製造プロセスの前半部分を図 8 に示す。多層構造 8 0 を備えた C F x 絶縁性層の断面図を図 8 ( a ) 中に示す。図 8 ( a ) 中に示すように、この多層構造は、フッ化炭素絶縁性層 8 2 と、キャップ層 8 4 ( ハードマスク層又はエッチング停止層とも呼ばれる ) と、障壁層 8 6 と、銅（C u）配線層 8 8 とを含んでいる。この実施形態において、キャップ層 8 4 は、アモルファス炭素又は炭化ケイ素窒化物（S i C N）を含み得る。また、障壁層 8 6 は、チタン（Ti）から形成される。なお、下側の多層構造からの銅（C u）配線層 8 6 は、C F x 絶縁性層 8 2 形成時において露出しない。しかししながら、障壁金属 / シード銅層を形成する際、ビア / 相互接続溝のエッチング後、銅（C u）配線層 8 6 が雰囲気に露出され、基板温度による影響を直接受ける（図 8 ( b ) を参照されたい）。

30

#### 【 0 0 6 3 】

高温スパッタリングプロセス中のフッ素濃度を低下させるための機構は、以下のようなものである。スパッタリングプロセスの初期段階において、四フッ化チタン（Ti F 4）などの金属フッ化物の溶液が、C F x 絶縁性層表面上に形成される。基板温度を同一の所望のレベルにおいて保持することにより、四フッ化チタン（Ti F 4）の高レベルの蒸気圧に起因して蒸発する。その結果、C F x 絶縁性層表面上のフッ素濃度が低下する一方、炭素濃度は増加し、これにより、カーボンリッチな表面がC F x 層表面上に形成される。

40

#### 【 0 0 6 4 】

カーボンリッチな表面は、フッ化炭素（C F x）絶縁性層とチタン（Ti）障壁層との界面において、複数の金属炭素結合、例えば Ti - C 結合を効果的に生成する。チタン（Ti）障壁層は Ti - C 結合の形成後に形成されるため、障壁層が安定化し、これにより、C F x 層と障壁層との間の接着性が確保される。そのため、電気抵抗が高いチタン窒化物（Ti N）層をチタン（Ti）障壁層と C F x 絶縁性層との間に挿入する必要が無くなり、これにより、その接着性が確保される。そのため、本発明の高温スパッタリングプロセスにより、従来の障壁層形成プロセスと比較して電気抵抗が低くかつ損失の少ない障壁層が得られる。

#### 【 0 0 6 5 】

C F x 絶縁性層表面上に残留フッ素（F）がまだ残っている場合、金属炭素結合が形成さ

50

れる可能性は低くなる。その理由としては、金属フッ素結合は、金属炭素結合と比較して共有結合エネルギー結合が低い点が挙げられる。そのため、フッ化炭素 (C F x) 絶縁性層と障壁金属層との界面に金属フッ素結合が形成される。

#### 【 0 0 6 6 】

主に金属元素によって形成される障壁層は、スパッタリングデバイス 100 を所定の設定条件で用いることにより形成される。障壁層は、障壁層スパッタリングチャンバー 106 内で、約 200 °C の基板温度において形成され得る。厚さ 18 nm のチタン (Ti) 障壁層を形成するには、処理時間を 50 秒に設定すればよい。その際、障壁層スパッタリングチャンバー 106 内で、約 300 W の入力電力において、流量約 70 sccm のアルゴン (Ar) ガスも用いられる。

10

#### 【 0 0 6 7 】

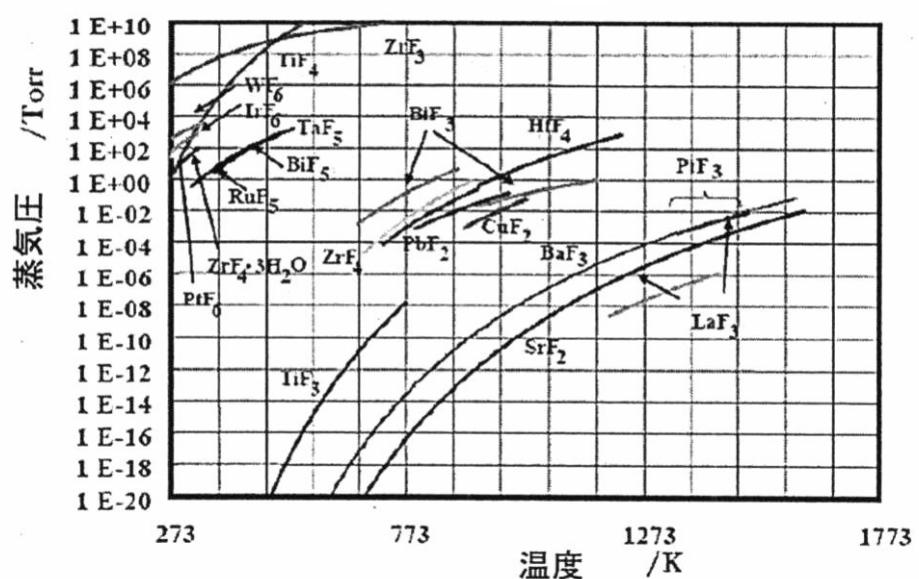

この実施形態において、主に金属元素によって構成される障壁層は、チタン (Ti) から形成される。その主因を挙げると、第 1 に、チタン (Ti) は、四フッ化チタン溶液を形成するためのフッ素原子と組み合わされた場合、高い蒸気圧を生じる材料であり、第 2 に、チタン (Ti) は、銅 (Cu) に対して障壁性能を有する点がある。他の実施形態において、高温スパッタリングプロセスを用いて障壁層を形成する際、他の金属元素を用いてもよい。上記した性質を有する他の金属元素としては、タンタル (Ta)、ルテニウム (Ru)、マンガン (Mn) 又はコバルト (Co) が挙げられる。図 9 は、フッ化物 (F) の蒸気圧曲線を温度の関数として示す。この図に示すように、タンタル (Ta) 及びルテニウム (Ru) はどちらとも、高い蒸気圧を有する。図 9 中のタンタルフッ化物 (TaF<sub>5</sub>) の曲線及びルテニウムフッ化物 (RuF<sub>5</sub>) の曲線を参照されたい。一方、タングステン (W) は高蒸気圧の材料であり、図 9 中の WF<sub>6</sub> 曲線を有する、しかしながら、タングステン (W) は、銅 (Cu) に対する障壁性能が良くないため、本発明の金属障壁層の候補としては選択されない。

20

#### 【 0 0 6 8 】

この実施形態において、主に金属元素によって構成される障壁層は、単一の層構造を有する。そのため、銅 (Cu) 相互接続体を、チタン (Ti) などの障壁層上に直接配置することが可能になる。他の実施形態において、多層構造の障壁層を形成してもよい。多層構造の障壁層は、主に第 1 の金属元素 (例えばチタン (Ti)) によって構成された第 1 の層と、前記第 1 の金属元素以外の金属元素によって主に形成された第 2 の層とを含み得る。チタン (Ti) 以外の金属元素の例としては、タンタル (Ta)、ルテニウム (Ru)、コバルト (Co)、ニッケル (Ni) 及びマンガン (Mn) が挙げられる。別の実施形態において、前記多層構造の第 2 の層が、前記第 1 の金属元素の窒化物 (例えば、チタン窒化物 (TiN)) 又は前記第 1 の金属元素以外の金属元素の窒化物 (例えば、タンタル窒化物 (TaN)) などから形成され得る。

30

#### 【 0 0 6 9 】

以下において更に説明するように、本発明により、銅相互接続体の直接下側に配置された第 1 の層 (例えば、チタン (Ti) 層) 上に第 2 の層である多層構造を形成する機会が得られる。このようにして、障壁層を多層構造と共に形成することにより、プロセス選択における自由度が増加する。これが可能となるのは、従来のプロセスにおける制約に縛られること無く、チタン (Ti) 障壁層上に任意の層を形成できるためである。

40

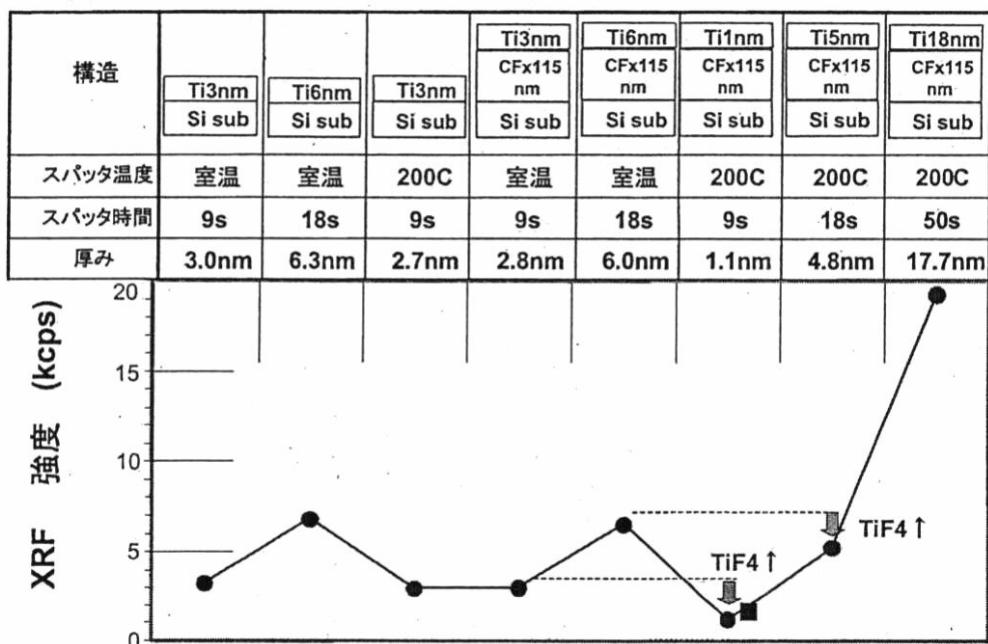

#### 【 0 0 7 0 】

図 10 に、多様なスパッタリング温度及びスパッタリング時間における、チタン (Ti) 障壁層の厚さの測定において用いられる実験サンプルのターゲット構造を示す。蛍光 X 線 (XRF) 分析を用いて、主にチタン (Ti) によって構成される障壁層の厚さを測定する。各実験サンプルの障壁層の厚さを示す XRF 強度曲線も図 10 中に示す。図 10 中に示すように、同一スパッタリング温度において形成された同一構造を有する実験サンプルの場合、スパッタリング期間が長くなるほど、チタン (Ti) 障壁層の厚さが増加する。しかし、同一スパッタリング期間内において多様なスパッタリング温度において形成された同一構造の実験サンプルの場合、ターゲット構造に応じて 2 つの異なる傾向が観察され

50

た。チタン (Ti) 障壁層をケイ素 (Si) 基板上に直接形成した場合、障壁層の厚さは、スパッタリング温度の関数として変化しない。XRF分析の結果、実験サンプル#1及び#3について、ほとんど同じ厚さの値 (3 nm及び2.7 nm) が見られた (XRF厚さの行中の表中の第1の列及び第3の列を参照されたい)。

【0071】

チタン (Ti) 障壁層をフッ化炭素 (CFx) 障壁層上に形成した場合、障壁層の厚さは、スパッタリング温度の関数として変化しない。例えば、実験サンプル#4及び#6のXRF厚さは、それぞれ、2.8 nm及び1.1 nmである。厚さ値の差が1.7 nmとなっているが、これは、四フッ化チタン (TiF4) 溶液がまず形成された後、高温スパッタリングプロセス時において四フッ化チタン (TiF4) 溶液が蒸発したことに起因している可能性があることが分かった。この実施形態においては、スパッタリング時間を9秒に設定した。実験サンプル#5及び#7のXRF厚さは、それぞれ、6.0 nm及び4.8 nmと測定された。この場合も同様に、厚さ値の差が1.2 nmあるが、これは、四フッ化チタン (TiF4) 溶液の蒸着に起因し得る。この実施形態において、スパッタリング時間は18秒に設定した。実験サンプル#8のXRF厚さを約17.7 nmにおいて測定した。この実施形態において、スパッタリング温度を200とし、スパッタリング時間を50秒とした。なお、全測定におけるXRF分析は、基板を約350の温度において12時間にわたってアニーリングした後に行った。

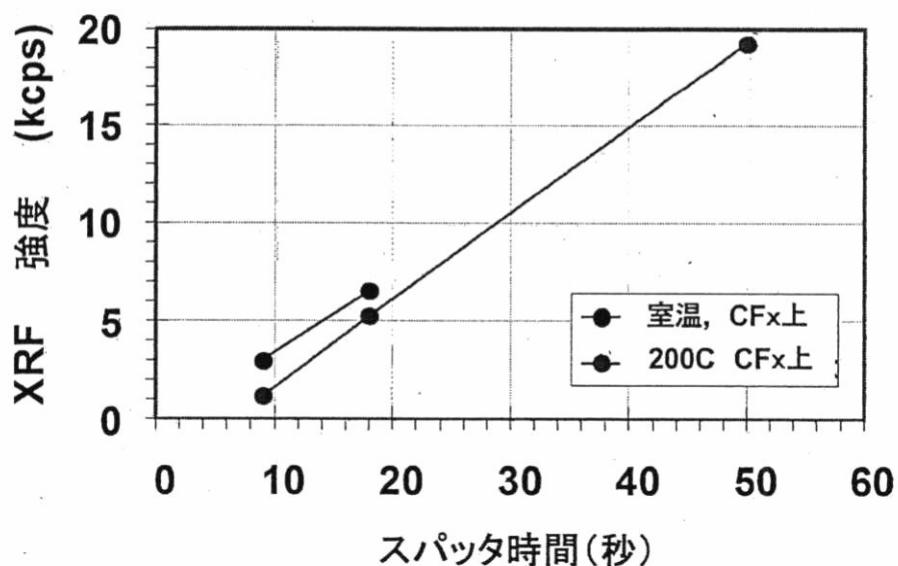

【0072】

これらの結果によれば、より高いスパッタリング温度 (例えば200)において形成されたチタン (Ti) 障壁層の厚さは、室温において形成されたチタン (Ti) 障壁層の厚さよりも約1.2~1.7 nmだけ薄かった。図11は、実験サンプル#4~#8のXRF強度を、両方のスパッタリング温度 (200及び室温 (R.T.)) におけるスパッタリング時間の関数として示している。

【0073】

四フッ化チタン (TiF4) 溶液を形成した後、前記四フッ化チタン (TiF4) 溶液を蒸発させることにより、早期段階においてフッ化炭素 (CFx) 絶縁性層の表面からフッ素 (F) を除去するために、チタン (Ti) が消費される。そのため、障壁層の厚さの値を従来のプロセスによって得られる障壁層の厚さ値と比較して約1.2~1.7 nmだけ高い値に設定することにより、障壁層の厚さの目標値を得ることができる。

【0074】

(基板のポストアニーリング)

高温スパッタリングプロセスを用いて前記障壁層を形成した後、同一のスパッタリングデバイス100を用いて、基板に対してポストアニーリング工程を行う。この熱処理は、約50~約200の基板温度において、障壁層蒸着チャンバ106内において行うことができる。処理時間は、180秒以下に設定することができる。

【0075】

(銅 (Cu) シード層の形成プロセス)

以下、本発明による半導体デバイスの製造において用いられるプロセスの第5の工程について説明する。主に金属元素によって構成される障壁層を形成した後、同一のスパッタリングデバイス100を用いて、前記障壁層上に銅 (Cu) シード層を形成する。前記銅 (Cu) シード層は、障壁層蒸着チャンバ106とは別のスパッタリングチャンバ108内において、室温において形成され得る。この実施形態において、前記銅 (Cu) シード層は、物理的気相成長法 (PVD) プロセスにより形成される。銅相互接続部をピアホール又は相互接続溝内に埋設するための十分な空間があれば、任意の厚さのシード層を用いることができる。銅 (Cu) シード層の所望の厚さは、約5 nmである。

【0076】

(銅相互接続部を形成するプロセス)

製造プロセスの最終工程において、厚さ約4~5 nmの銅 (Cu) シード層を形成した後、従来の電解めっきプロセスを用いて、厚さ約120~130 nmの銅相互接続を形成す

10

20

30

40

50

る。

【0077】

実験サンプル

事前処理されたフッ化炭素 (C F x) 絶縁性層上に高温スパッタリングプロセスによって形成された障壁層の障壁性能及び接着性を評価するために、上記した製造プロセスを用いて、いくつかの実験サンプルを製造した。実験サンプルの評価目的のために、厚さ約 150 nm の銅層を、銅スパッタリングチャンバ 108 内において、障壁層上に以下の条件に基づいて形成した。すなわち、アルゴン (Ar) ガスの流量を 100 sccm とし、入力電力を 500 W とし、処理時間を 100 秒とした。以下において、これらの評価結果について詳述する。

10

【0078】

(実験サンプル 10) : この実験サンプルを本発明のプロセスに基づいて製造し、障壁特性と、C F x 絶縁性層に対する障壁層の接着性とを評価した。この実験サンプルにおいて、C F x 絶縁性層表面に対し、アルゴンアニーリング処理を行った。本発明のプロセスによる半導体製造プロセスにおける工程 (2) の前処理プロセスとして、このアルゴン (Ar) アニーリング処理を用いた。

【0079】

図 12 には、アルゴンアニーリング処理後の、実験サンプルの製造プロセスの模式図が示されている。図 12 には、透過電子顕微鏡法 (TEM) 画像を用いた実験サンプルの断面図及び平面図も図示されている。この図中に示すように、約 200 の温度におけるプレアニーリング処理が、C F x 絶縁性層表面上に適用されている。その後、厚さ約 3 nm のチタン (Ti) 障壁層を高温スパッタリングプロセスを用いて形成した。このチタン (Ti) 障壁層は、スパッタリングデバイス 100 から、障壁層スパッタリングチャンバ 106 内において基板温度約 200 において形成した。その後、ポストアニーリング工程を、チタン (Ti) 障壁層を含む基板上に 200 において実行した。また、プレアニーリング工程及びポストアニーリング工程も、障壁層蒸着チャンバ 106 内において行った。最終工程において、銅スパッタリングチャンバ 108 において、厚さ 150 nm の銅 (Cu) 層を従来のスパッタリングプロセスを用いて室温において形成した。銅の酸化を回避するために、厚さ 20 nm のさらなるチタン (Ti) 層を銅層上に形成した。その後、温度約 350 において 12 時間にわたって評価前アニーリングを行った後、実験サンプルを評価した。この評価前アニーリングは、スパッタリングデバイスのアニーリングチャンバ 104 内において行った。

20

【0080】

図 12 中に示すように、チタン障壁層の C F x 絶縁性層に対する接着性を評価するために、テープ試験を行った。その結果、このサンプル中の前記障壁層の層間剥離又は剥離は見られなかった。更に、この実験サンプルの断面図及び平面図は、チタン (Ti) 層の障壁性能について、極めて好ましかった。前記断面図の拡大部分中に示すように、C F x 層とケイ素 (Si) 基板との界面において、高輝度粒子は見られなかった。すなわち、相互接続体からの銅は、フッ化炭素 (C F x) 絶縁性層内に浸透していなかった。これは、実験サンプルの平面図中、実験サンプル表面上の凹凸が観察されないことからも確認できる。この実験サンプルは、優れた障壁性能と、チタン (Ti) 障壁層及び C F x 絶縁性層間の強力な接着結合とを示した。これは、前記フッ化炭素 (C F x) 絶縁性層表面に前処理プロセスのみを行い、障壁層を従来のスパッタリングプロセスから室温で形成した実験サンプルから得られた従来の結果と対照的である。図 5 ~ 図 6 (特に、実験サンプル #5) を参照されたい。

30

【0081】

(実験サンプル 11 ~ 12) : 以下において、厚さ値がおよそ 18 nm という高い値であるチタン (Ti) 障壁層を形成した場合の、実験サンプルの障壁性能が評価される。図 13 は、ターゲット構造と、実験サンプル 11 の製造に用いられるプロセスフローとを示している。この図に示すように、C F x 絶縁性層表面上のフッ素濃度を低下させるために、

40

50

CF<sub>x</sub>絶縁性層表面上に水素(H<sub>2</sub>)アニーリング処理を行う。その後、水素(H<sub>2</sub>)雰囲気下におけるプレアニーリング処理を180秒間行う。前記プレアニーリング工程後、チタン(Ti)障壁層を、基板温度約200において高温スパッタリングプロセスを用いて形成する。前記高温スパッタリングプロセスのスパッタリング時間を50秒に設定したところ、厚さ18nmのチタン障壁層が形成された。ポストアニーリング処理において、水素(H<sub>2</sub>)を200において180秒間前記基板に付加した後、銅(Cu)層形成工程において、厚さ150nmの銅(Cu)層を室温において形成した。その後、この実験サンプル(#11)に対して、ブリスター試験及びテープ試験を行った。セロハンテープを表面に貼付した後の構造の平面図も図13中に示す。ウエハ全体を評価した後、貼付されたテープ上に変色は認められなかった。また、この実験サンプルは、ブリスター試験及びテープ試験双方に合格した。更に、図13は、実験サンプル11の断面図及び上面図を示す。図示のように、チタン(Ti)障壁層の厚さ値が高いことに起因する銅(Cu)拡散は認められなかった。

#### 【0082】

実験サンプル12の製造に用いられるターゲット構造及びプロセスフローを図14中に示す。図14中に示すプロセスフローを用いて、2つの実験サンプルを形成した。すなわち、第1のサンプルにおいては、フッ素濃度低減のために、CF<sub>x</sub>絶縁性層表面上に(H<sub>2</sub>)アニーリング処理を行ったが、第2のサンプルにおいては、CF<sub>x</sub>絶縁性層上に水素(H<sub>2</sub>)アニーリングは行わなかった。加えて、これらの実験サンプル双方に対して、プレアニーリング工程は行わなかった。厚さ18nmのチタン(Ti)障壁層を基板温度約200において形成した後、ソフトエッチング処理及びアルゴン冷却処理を基板上にそれぞれ行った。ソフトエッチング処理とは、400kHzのRFを基板に付加してアルゴン(Ar)イオンを引き寄せるにより、チタン(Ti)障壁層表面上の酸化物膜を除去するプロセスである。このようなソフトエッチングプロセスを、アルゴン雰囲気内において温度200で360秒間行った。このプロセスは、温度200度において行われるため、ポストアニーリング及び酸化物膜除去処理として構成され得る。更に、アルゴン(Ar)冷却処理とは、20~30の温度において保持された冷却プレート上に基板を60秒間配置することにより、基板を冷却するプロセスである。このようなアルゴン(Ar)冷却処理を、銅(Cu)層を室温において蒸着させるために行った。特に明記されていない実験例においては、このプロセスは行っていない点に留意されたい。最終工程において、厚さ150nmの銅(Cu)層を室温においてチタン(Ti)障壁層上に形成した。これらの実験サンプル双方に対して、ブリスター試験及びテープ試験を行った。セロハンテープを表面に貼付した後の両者の構造の平面図も図14中に示す。水素(H<sub>2</sub>)アニーリング処理を施した第1の実験サンプルについては、前記貼付されたテープ周囲において、銅(Cu)表面の若干の変色が認められた。図14に示すように、実験サンプル#11の場合と同様に、実験サンプル12双方は、ブリスター試験及びテープ試験に合格した。図14はまた、双方の実験サンプルの断面図及び上面図を示す。上記の場合(サンプル#11)と同様に、チタン(Ti)障壁層の厚さに起因する銅(Cu)拡散は認められなかった。基板を350において12時間アニーリングした後、ブリスター試験、テープ試験及びSEM画像取得を行った。チタン障壁層の厚さ値が高い(例えば18nm)場合のチタン障壁層の障壁性能を確認するために、実験サンプル11~12を製造した。しかし、相互接続幅の短縮を回避するために、金属障壁層の厚さは薄くせざるをえなかった。例えば、幅20nmのビアホールを通じて所望の銅相互接続体を形成するには、障壁層を厚さ約3nmに形成する必要がある。このようにして、14nm幅の所望の銅(Cu)相互接続体が設けられる。

#### 【0083】

(実験サンプル13~15):図15は、実験サンプル13~15の製造において用いられるターゲット構造及びプロセスフローを示す。この図に示すように、3つの実験サンプル全てにおけるCF<sub>x</sub>絶縁性層表面上のフッ素濃度を低減するために、水素(H<sub>2</sub>)アニーリング処理をCF<sub>x</sub>絶縁性層表面上に行った。この水素(H<sub>2</sub>)アニーリング処理は、

10

20

30

40

50

温度約300において900秒間行った。その後、水素( $H_2$ )雰囲気下においてプレアニーリング処理を温度約200において180秒間行った。前記プレアニーリング工程後、高温スパッタリングプロセスを用いて、チタン( $Ti$ )障壁層を基板温度約200において行った。実験サンプル13~15のスパッタリング時間は、それぞれ9秒間、17秒間及び25秒間とした。上記したスパッタリング時間により、厚さ1nm、4nm及び7nmのチタン障壁層がそれぞれ形成された。200において180秒間行われる水素( $H_2$ )アニーリングであるポストアニーリング処理を基板に行った後、銅( $Cu$ )層形成工程において、厚さ150nmの銅( $Cu$ )層を室温において形成した。

#### 【0084】

基板を温度約350において12時間アニーリングした後、実験サンプル13~15に10対してプリスター試験及びテープ試験を行った。3つの構造上にセロハンテープを貼付した後の構造平面図も図15中に示す。この図に示すように、厚さ7nmのチタン( $Ti$ )障壁層を備えた実験サンプル#15のみが、プリスター試験及びテープ試験に合格した。その他2つのサンプルについては、厚さ4nmのチタン( $Ti$ )障壁層を備えた実験サンプル#14がプリスター試験のみに合格し、厚さ1nmのチタン( $Ti$ )障壁層を備えた実験サンプル#13がテープ試験のみに合格した。

#### 【0085】

図16には、実験サンプル13~15の断面図及び上面図がSEM画像で示されている。基板を温度約350において12時間に亘ってアニーリングした後、SEM画像を取得した。この図中に示すように、3つのサンプル(#13~#15)全てにおいて、CFx絶縁性層とケイ素( $Si$ )基板との界面上に高輝度粒子が見られた。しかしながら、より肉厚の障壁層を備えた実験サンプルにおいては、銅( $Cu$ )の浸透がより少量であることが認められた。また、障壁層厚さがより肉厚である(7nm)実験サンプル#15の場合においては、銅表面上の凹みもより少量であることが認められた。

#### 【0086】

以下において、障壁性能及び障壁層への接着について、フッ化炭素( $CF_x$ )絶縁性層の性質を調査した。この目的のため、一連の3つの実験サンプルを製造した。各組において、異なるフッ化炭素( $CF_x$ 及び $CF_x2$ )の絶縁性層を有する2つの実験サンプルを形成した。 $CF_x$ 絶縁性層及び $CF_x2$ 絶縁性層をRLSAデバイスを用いて2つの異なる設定条件下において形成した。表I中に、 $CF_x$ 層及び $CF_x2$ 層についての設定条件の概要を示す。

#### 【表1】

表I:  $CF_x$ 及び $CF_x2$ 絶縁層の形成に用いられる設定条件

|                  | $CF_x$ | $CF_x2$ |

|------------------|--------|---------|

| マイクロ波出力(W)       | 3000   | 1500    |

| 圧力(mTorr)        | 56     | 28      |

| $CF_x$ 流量(sccm)  | 2.50   | 1.30    |

| アルゴン(Ar)流量(sccm) | 200    | 120     |

#### 【0087】

$CF_x2$ 層はフッ化炭素( $CF$ )絶縁性層であり、 $CF_x$ 層の場合よりも脱ガス量を低くした条件下において形成した。表I中に示すように、 $CF_x2$ 層の形成に用いられた設定条件(例えば、マイクロ波出力、圧力、及びガス流量)は、従来の $CF_x$ 層形成において用いられた量の約半分である。しかし、 $CF_x2$ 層を形成するための処理時間は、 $CF_x$ 層の場合よりも約3倍長い(40秒~120秒)。 $CF_x$ 層の場合と同様に、 $CF_x2$ 絶縁性層の形成時のウエハ状態温度を約350とした。そのため、この長期間において、脱フッ素処理について同じ作用が達成され得る。現在の $CF_x$ 層が形成される方向は、 $CF_x2$ 形成において用いられた方向の近隣である。

#### 【0088】

図17には、各一連の実験サンプルの製造において用いられるターゲット構造及びフロープロセスが示されている。水素( $H_2$ )アニーリング処理、プレアニーリング処理及びボ

10

20

30

40

50

ストアニーリング処理を各一連の実験サンプルにおいて用いた。フッ素濃度低減のための水素アニーリングを、温度200において900秒間行った。チタン(Ti)障壁層の形成を、高温スパッタリングプロセスを用いて基板温度200において行った。第1の一連の実験サンプルにおいては、ポストアニーリング処理の処理時間を360秒間とし、第2の一連の実験サンプル及び第3の一連の実験サンプルにおいては、この処理時間を180秒間とした。第1の一連の実験サンプルの場合においては、その他の事後処理は基板に対して行わなかった。しかし、第2の実験サンプル及び第3の実験サンプルの基板については、酸素(O<sub>2</sub>)アニーリングを300秒間及びアルゴン(Ar)アニーリングを600秒間それぞれ行った。

## 【0089】

10

基板を温度約350において12時間アニーリングした後、各組中の実験サンプルに対して、プリスター試験及びテープ試験を行った。各組の実験サンプル表面上にセロハンテープを貼付した後の平面図も図17中に示す。CF×2絶縁性層を備えたサンプルは全て、プリスター試験及びテープ試験に合格した。このことから、CF×2絶縁性層をCF×絶縁性層と比較すると、CF×2絶縁性層は障壁層剥離に対してより高い抵抗を有していることが分かる。

## 【0090】

図18には、各組の実験サンプルの断面図及び上面図がSEM画像として示されている。基板を温度約350において12時間アニーリングした後、SEM画像を取得した。この図に示すように、CF×2絶縁性層とケイ素(Si)基板との界面においては、CF×絶縁性層とケイ素(Si)基板との界面に比べて、より少量の高輝度粒子が認められた。更に、CF×2絶縁性層を備えた実験サンプルの場合、銅(Cu)表面上の凹みもより少量であった。

20

## 【0091】

以下、各製造工程(例えば、プレアニーリング工程、ポストアニーリング工程、障壁層形成工程)の効果を、障壁性能と障壁層及びCF×絶縁性層間の接着性とに対する温度の関数として示す点について、詳細に説明する。この目的のため、異なる基板温度及びプロセス工程において形成されたチタン窒化物(TiN)障壁層を備えた多様な実験サンプルを評価した。

## 【0092】

30

図19は、実験サンプル製造において用いられるターゲット構造及びプロセスフローを示している。実験サンプル製造において用いられるプロセスを以下に示す：1) CF×2絶縁性層をケイ素(Si)基板上に形成する。2) 温度約200においてプレアニーリング処理を行う。3) 従来のスパッタリング法を用いて、室温においてチタン窒化物(TiN)層を形成する。4) 従来のスパッタリング法を用いて、室温で銅(Cu)層を形成する。5) 銅(Cu)酸化を回避するためのチタンキャップ層を形成する。チタン窒化物(TiN)障壁層は、チタン(Ti)障壁層と比較して窒素(N)原子の存在に起因して比較的少量のチタンを含んでいたため、障壁特性が低かった点に留意されたい。以下において更に説明するように、チタン窒化物(TiN)層などの障壁層を形成した後にポストアニーリング工程を付加することで、CF×絶縁性層上(CF×絶縁性層表面近隣を含む)のフッ素(F)濃度のさらなる低減が支援され、その結果、チタン窒化物(TiN)層の障壁特性が向上する。

40

## 【0093】

評価前アニーリングを、温度約350において12時間に亘って行った後、実験サンプルに対してテープ試験及びSEM分析を行った。また、接着剤セロハンテープの貼付後の実験サンプルの平面図と、実験サンプル上の断面図及び上面図とを図19中に示す。これらの結果によれば、このサンプル中、障壁層の剥離は認められなかった。しかし、CF×2絶縁性層とケイ素(Si)基板との界面において、銅(Cu)の浸透は認められなかつた。障壁層が剥離しなかつたことが、この実験サンプルにおいて銅(Cu)浸透が多く生じたことと直接関連していると考えられる。

50

## 【0094】

次の工程において、別個の製造プロセスによって2つの実験サンプルを形成した。第1の実験サンプルの製造において用いられるプロセスを以下に示す：1) CF<sub>x</sub>2絶縁性層をケイ素(Si)基板上に形成する。2) 高温スパッタリングプロセスを用いて、基板温度約100 においてチタン窒化物(TiN)層を形成する。3) 従来のスパッタリング法を用いて、室温で銅(Cu)層を形成する。4) チタンキャップ層を形成する。

## 【0095】

第2の実験サンプルの製造において用いられるプロセスを以下に示す：1) CF<sub>x</sub>2絶縁性層をケイ素(Si)基板上に形成する。2) 2) 温度約200 においてプレアニーリング処理を行う。3) 高温スパッタリングプロセスを用いて、基板温度約200 でチタン窒化物(TiN)層を形成する。4) 従来のスパッタリング法を用いて、室温で銅(Cu)層を形成する。5) 銅(Cu)酸化を回避するために、チタンキャップ層を形成する。このプロセスが第1の実験サンプルのプロセスと異なる点は、プレアニーリング工程を行った後、障壁層を形成し、より高い温度(200)において障壁層を形成したことである。上記実験サンプル双方において、チタン窒化物(TiN)障壁層形成後、ポストアニーリング処理は行わなかった。

## 【0096】

双方の実験サンプルを製造する際に用いられたターゲット構造及びプロセスを図20中に示す。評価前アニーリングを温度約350 において12時間行った。その後、双方の実験サンプルに対して、テープ試験及びSEM分析を行った。また、接着剤セロハンテープ貼付後の実験サンプルの平面図と、双方の実験サンプルの断面図及び上面図とを図20中に示す。障壁層を100 において形成した第1の実験サンプルの場合、障壁層剥離及び銅の浸透の双方が認められたことが分かった。障壁層形成温度がより高い(200)第2の実験サンプルの場合、剥離は認められなかった。しかし、CF<sub>x</sub>2絶縁性層とケイ素(Si)基板との界面において、少量の銅(Cu)の浸透が認められた。

## 【0097】

図21には、別の実験サンプルを製造する際に用いられたターゲット構造及びプロセスフローが示されている。この実験サンプルの製造において用いられるプロセスを以下に示す：1) CF<sub>x</sub>2絶縁性層をケイ素(Si)基板上に形成する。2) プレアニーリング処理を温度約200 において行う。3) 高温スパッタリングプロセスを用いて、基板温度約200 でチタン窒化物(TiN)層を形成する。4) ポストアニーリング処理を温度約200 で行う。5) 従来のスパッタリング法を用いて、室温で銅(Cu)層を形成する。6) 銅(Cu)酸化を回避するために、チタンキャップ層を形成する。記載を簡潔にするため、段落

## 【0098】

において説明したような第2の実験サンプルの製造において用いられるターゲット構造及びプロセスをこの図中にも示す。このプロセスが第2の実験サンプルのプロセスと異なる点は、高温スパッタリングプロセスによって障壁層を形成した後、ポストアニーリング工程を行ったことである。

## 【0099】

上記の場合と同様に、評価前アニーリングを、温度約350 において12時間行った。その後、実験サンプルに対して、テープ試験及びSEM分析を行った。接着剤セロハンテープ貼付後の実験サンプルの平面図と、実験サンプルの断面図及び上面図とを図21中にも示す。記載を簡潔にするため、第2の実験サンプルからの結果もこの図中に示す。この図に示すように、さらなるポストアニーリング工程を施した実験サンプルの場合、CF<sub>x</sub>2絶縁性層とケイ素(Si)基板との界面において、銅(Cu)の浸透は認められなかった。これは、ポストアニーリング工程によってCF<sub>x</sub>絶縁性層内のフッ素(F)濃度が更に低減したことに主に起因する。このようにして、チタン窒化物(TiN)層の障壁特性が向上し、これにより、ケイ素(Si)基板とCF<sub>x</sub>2絶縁性層との間の銅の浸透は認められなかった。また、このサンプル中、障壁層の剥離も認められなかった。

10

20

30

40

50

## 【0100】

結論として、製造プロセス全体において（すなわち、CF×形成プロセス、前処理表面プロセス、プレアニーリングプロセス、障壁層形成プロセス、及びポストアニーリングプロセス）において、本発明に係る基板温度は、約200℃の温度に調整及び維持される。換言すれば、製造プロセス全体において、CF×絶縁性層のフッ素低減を行う。

## 【0101】

本開示の原理について、特定の装置及び方法と関連して説明してきたが、本記載はひとえに例示目的のためのものであり、本発明の範囲を限定するものではないことが明確に理解されるべきである。

【図1】

【図2】

【図3】

【図4】

## ブリスター、テープ試験、360C、1時間後

| 構造               |          |                  |                      |                     |                  |                   |                  |             |                    |

|------------------|----------|------------------|----------------------|---------------------|------------------|-------------------|------------------|-------------|--------------------|

|                  | Cu150nm  |                  |                      |                     |                  |                   |                  |             |                    |

|                  | Ti3nm    |                  |                      |                     |                  |                   |                  |             |                    |

|                  | CFx115nm |                  |                      |                     |                  |                   |                  |             |                    |

|                  | Si sub   |                  |                      |                     |                  |                   |                  |             |                    |

| 処理               | wo       | CO<br>ANL<br>60s | CO<br>プラズマ<br>3kW10s | Si2H6<br>ANL<br>60s | Ar<br>ANL<br>60s | H2<br>ANL<br>900s | H2<br>プラズマ<br>5s | Ca<br>(OH)2 | フルオロ<br>ポンダー<br>処理 |

| 写真<br>テープ<br>試験後 |          |                  |                      |                     |                  |                   |                  |             |                    |

| ブリスター            | OK       | OK               | OK                   | OK                  | OK               | OK                | OK               | OK          | OK                 |

| テープ試験            | OK       | OK               | OK                   | OK                  | OK               | OK                | OK               | OK          | NG                 |

【図5】

## SEM 360C、1時間後(1)

| 構造         |          |                |                     |                  |                |

|------------|----------|----------------|---------------------|------------------|----------------|

|            | Cu150nm  |                |                     |                  |                |

|            | Ti3nm    |                |                     |                  |                |

|            | CFx115nm |                |                     |                  |                |

|            | Si sub   |                |                     |                  |                |

| 処理         | wo       | CO<br>ANL60sec | CO プラズマ<br>3kW10sec | Si2H6 ANL<br>60s | H2 ANL<br>900s |

| 断面<br>×150 |          |                |                     |                  |                |

| 表面<br>×50K |          |                |                     |                  |                |

【図6】

## SEM 360C、1時間後(2)

|          |               |                                                                                                                                   |                 |  |  |         |       |          |        |

|----------|---------------|-----------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|---------|-------|----------|--------|

| 構造       |               | <table border="1"> <tr><td>Cu150nm</td></tr> <tr><td>Ti3nm</td></tr> <tr><td>CFx115nm</td></tr> <tr><td>Si sub</td></tr> </table> |                 |  |  | Cu150nm | Ti3nm | CFx115nm | Si sub |

| Cu150nm  |               |                                                                                                                                   |                 |  |  |         |       |          |        |

| Ti3nm    |               |                                                                                                                                   |                 |  |  |         |       |          |        |

| CFx115nm |               |                                                                                                                                   |                 |  |  |         |       |          |        |

| Si sub   |               |                                                                                                                                   |                 |  |  |         |       |          |        |

| wo       | Ar ANL<br>60s | H2<br>プラズマ5s                                                                                                                      | Ca<br>(OH)2 10s |  |  |         |       |          |        |

|          |               |                                                                                                                                   |                 |  |  |         |       |          |        |

|          |               |                                                                                                                                   |                 |  |  |         |       |          |        |

|          |               |                                                                                                                                   |                 |  |  |         |       |          |        |

【図7】

【図8】

【図9】

### フッ化物の蒸気圧曲線

【図10】

## スパッタに対するXRF強度

【図11】

## スパッタに対するXRF強度

スパッタ温度依存性

【図12】

【図13】

プリスター、テープ試験及びSEM 350°C、12時間後

| 構造及び<br>プロセスフロー                      | H2 ANL<br>300C,900s | 事前加熱<br>180s | Ti 200C,50s<br>Ti18nm<br>CF2<br>Si sub | 事後加熱<br>180s | Cu 室温<br>Ti18nm<br>CF2<br>Si sub |

|--------------------------------------|---------------------|--------------|----------------------------------------|--------------|----------------------------------|

| H2 ANL                               |                     |              |                                        | 有            |                                  |

| 事後加熱                                 |                     |              |                                        | 180s         |                                  |

| Ar 冷却                                |                     |              |                                        | wo           |                                  |

| 写真                                   |                     |              |                                        |              |                                  |

| プリスター                                |                     |              |                                        | OK           |                                  |

| テープ試験                                |                     |              |                                        | OK           |                                  |

| SEM<br>(断面<br>×150k<br>/ 表面<br>×50k) |                     |              |                                        |              |                                  |

【図14】

## ブリスター、テープ試験及びSEM 350°C、12時間後

| 構造及び<br>プロセスフロー                     | H2 ANL<br>300C,900s | Ti 室温,50s ソフトエッチング; Ar<br>Ti18nm<br>200°C<br>600s<br>ANL 360 s | Cu150nm<br>Ti18nm<br>CF2<br>Si sub | Cu 室温         |

|-------------------------------------|---------------------|----------------------------------------------------------------|------------------------------------|---------------|

|                                     | CF2<br>Si sub       | CF2<br>Si sub                                                  | CF2<br>Si sub                      | CF2<br>Si sub |

| H2 ANL                              | WO                  |                                                                | 有                                  |               |

| 写真                                  |                     |                                                                |                                    |               |

| ブリスター                               | OK                  |                                                                | OK                                 |               |

| テープ試験                               | OK                  |                                                                | OK                                 |               |

| SEM<br>(断面<br>×150k<br>/表面<br>×50k) |                     |                                                                |                                    |               |

【図15】

## ブリスター、テープ試験、350°C、12時間後

| 層           | CFx           |                             | Ti              |                        |                  | Cu                                |

|-------------|---------------|-----------------------------|-----------------|------------------------|------------------|-----------------------------------|

| プロセス        | CFx           | H2 アニーリング                   | 事前加熱            | Ti200C,Xs              | 事後加熱             | Cu 室温,94s                         |

| プロセス<br>フロー | CFx<br>Si sub | STG.温度.<br>300C,900s<br>sec | 200C,180<br>sec | TiXnm<br>CFx<br>Si sub | 200C,180s<br>sec | Cu150nm<br>TiXnm<br>CFx<br>Si sub |

| TI 時間       | 9 sec(1nm)    |                             | 17sec(4nm)      |                        | 25sec(7nm)       |                                   |

| アニーリング後の写真  |               |                             |                 |                        |                  |                                   |

| ブリスター       | 少量            |                             | OK              |                        | OK               |                                   |

| テープ試験       | OK            |                             | NG              |                        | OK               |                                   |

【図16】

## SEM 350°C、12時間後

| 層             | CFx           |                             | Ti              |                        |                  | Cu                                |

|---------------|---------------|-----------------------------|-----------------|------------------------|------------------|-----------------------------------|

| プロセス          | CFx           | H2アニーリング                    | 事前加熱            | Ti200C,Xs              | 事後加熱             | Cu 室温,94s                         |

| プロセスフロー       | CFx<br>Si sub | STG.温度、<br>300C,900s<br>sec | 200C,180<br>sec | TiXnm<br>CFx<br>Si sub | 200C,180s<br>sec | Cu150nm<br>TiXnm<br>CFx<br>Si sub |

| Ti 時間         | 9 sec(1nm)    |                             | 17sec(4nm)      |                        | 25sec(7nm)       |                                   |

| 断面<br>(×150k) |               |                             |                 |                        |                  |                                   |

| 表面<br>(×50k)  |               |                             |                 |                        |                  |                                   |

【図17】

## ブリスター、テープ試験、350°C、12時間後

|           |                 |                              |                          |                  |                          |                     |

|-----------|-----------------|------------------------------|--------------------------|------------------|--------------------------|---------------------|

| 構造        | CF115<br>Si sub | H2 ANL 事前加熱<br>900sec 180sec | Ti3nm<br>CF115<br>Si sub | 事後加熱<br>XX sec   | Cu150nm                  | Ti PVD<br>温度: 200°C |

|           |                 |                              |                          |                  | Ti3nm<br>CF115<br>Si sub |                     |

| CFx 膜     | CFx             | CFx2                         | CFx                      | CFx2             | CFx                      | CFx2                |

| Ti 事後加熱時間 | 360sec          |                              |                          | 180sec           |                          |                     |

| TI 事後処理   |                 | TEM                          | MEP2 O2 ANL300sec        | MEP2Ar ANL600sec |                          |                     |

| 写真        |                 |                              |                          |                  |                          |                     |

| ブリスター     | OK              | OK                           | OK                       | OK               | OK                       | OK                  |

| テープ試験     | NG              | OK                           | NG                       | OK               | NG                       | OK                  |

【図18】

## SEM 350°C、12時間後

| 構造            | H2 ANL 事前加熱<br>900sec 180sec |        |                              | 事後加熱<br>XX sec  | Ti PVD<br>温度: 200°C |       |

|---------------|------------------------------|--------|------------------------------|-----------------|---------------------|-------|

|               | CF115                        | Si sub | CF115                        |                 | Cu150nm             | Ti3nm |

| CFx 膜         | CFx                          | CFx2   | CFx                          | CFx2            | CFx                 | CFx2  |

| Ti 事後加熱時間     | 360sec                       |        |                              | 180sec          |                     |       |

| Ti 事後処理       | TEM                          |        | MEP O <sub>2</sub> ANL300sec | MEPAr ANL600sec |                     |       |

| 断面<br>(×150k) |                              |        |                              |                 |                     |       |

| 表面<br>(×50k)  |                              |        |                              |                 |                     |       |

【図19】

## アニーリング工程の比較 350°C、12時間後

【図20】

【図21】

---

フロントページの続き

(51)Int.Cl. F I

|         |             |           |         |             |       |

|---------|-------------|-----------|---------|-------------|-------|

| H 0 1 L | 2 1 / 2 8 5 | (2006.01) | H 0 1 L | 2 1 / 2 8 5 | 3 0 1 |

| H 0 1 L | 2 1 / 2 8   | (2006.01) | H 0 1 L | 2 1 / 2 8   | A     |

(72)発明者 小林 保男

山梨県韮崎市穂坂町三ツ沢 6 5 0 東京エレクトロン技術研究所株式会社内

(72)発明者 松岡 孝明

東京都港区赤坂五丁目 3 番 1 号 赤坂 B i z タワー 東京エレクトロン技術研究所株式会社内

(72)発明者 野沢 俊久

兵庫県尼崎市扶桑町 1 - 8 東京エレクトロン技術研究所株式会社内

審査官 今井 淳一

(56)参考文献 特開平 1 1 - 2 9 7 6 8 6 ( J P , A )

特開 2 0 0 1 - 2 8 4 3 5 8 ( J P , A )

(58)調査した分野(Int.Cl., DB名)

|         |               |

|---------|---------------|

| H 0 1 L | 2 1 / 3 1 4   |

| H 0 1 L | 2 1 / 2 8     |

| H 0 1 L | 2 1 / 2 8 5   |

| H 0 1 L | 2 1 / 3 2 0 5 |

| H 0 1 L | 2 1 / 7 6 8   |

| H 0 1 L | 2 3 / 5 2 2   |

| H 0 1 L | 2 3 / 5 3 2   |