(12)发明专利

(10)授权公告号 CN 106233451 B

(45)授权公告日 2020.06.30

(21)申请号 201580006538.6

专利权人 安堤格里斯公司

(22)申请日 2015.01.30

(72)发明人 岱尔·K·史东 理查尔·库肯

(65)同一申请的已公布的文献号

林奕宽 朱利安·G·布雷克

留德米拉·史东

申请公布号 CN 106233451 A

(43)申请公布日 2016.12.14

(74)专利代理机构 北京同立钧成知识产权代理

有限公司 11205

(30)优先权数据

代理人 杨文娟 臧建明

61/933,659 2014.01.30 US

14/280,245 2014.05.16 US

(85)PCT国际申请进入国家阶段日

(51)Int.Cl.

2016.07.29

H01L 21/687(2006.01)

H01L 21/205(2006.01)

(86)PCT国际申请的申请数据

(56)对比文件

PCT/US2015/013772 2015.01.30

US 2010/0103584 A1, 2010.04.29,

(87)PCT国际申请的公布数据

US 2010/0103584 A1, 2010.04.29,

W02015/116930 EN 2015.08.06

US 2009/0161285 A1, 2009.06.25,

(73)专利权人 瓦里安半导体设备公司

JP 特开平8-288376 A, 1996.11.01,

地址 美国麻萨诸塞州格洛斯特郡都利路35

号

CN 102047386 A, 2011.05.04,

审查员 毕长栋

权利要求书1页 说明书8页 附图7页

(54)发明名称

制造静电夹的方法、静电夹及静电夹系统

(57)摘要

本发明提供一种制造静电夹的方法、一种静电夹及一种静电夹系统。在一个实施例中，一种制造静电夹的方法包含：形成绝缘体主体；在所述绝缘体主体上形成电极；以及在所述电极上沉积层堆叠，所述层堆叠包括使用原子层沉积(ALD)而沉积的氧化铝层。抗扩散层堆叠设置在静电夹的电极与将由静电夹固持的衬底之间。可在操作期间抑制金属从静电夹滤出，避免污染衬底。

1.一种制造静电夹的方法,包括:

形成绝缘体主体;

在所述绝缘体主体上形成电极;以及

在所述电极上沉积层堆叠,所述层堆叠包括使用原子层沉积而沉积的氧化铝层,

其中所述电极为通过原子层沉积而形成的铂电极,所述氧化铝层的厚度介于500纳米与10微米之间,

其中沉积所述层堆叠包括:

在所述电极上沉积所述氧化铝层;以及

在所述氧化铝层上沉积多个绝缘体层,多个所述绝缘体层包括氮化硅层及氮氧化铝层。

2.根据权利要求1所述的制造静电夹的方法,其中多个所述绝缘体层的厚度介于40微米与200微米之间。

3.根据权利要求1所述的制造静电夹的方法,包括以75微米或小于75微米的厚度沉积所述层堆叠。

4.根据权利要求1所述的制造静电夹的方法,包括将所述氧化铝层沉积为非晶层。

5.一种静电夹,包括:

绝缘体主体;

电极,设置在所述绝缘体主体上;以及

层堆叠,包括厚度为10微米或小于10微米的非晶氧化铝层和所述非晶氧化铝层上的多个绝缘体层,多个所述绝缘体层包括氮化硅层及氮氧化铝层,其中所述非晶氧化铝层的厚度介于500纳米与10微米之间。

6.根据权利要求5所述的静电夹,其中所述层堆叠的厚度介于40微米与200微米之间。

7.根据权利要求6所述的静电夹,其中所述层堆叠包括:

至少一个额外绝缘体层,邻近于所述电极而设置;以及

氧化铝层,设置在所述至少一个额外绝缘体层上。

8.一种静电夹系统,包括:

绝缘体主体;

电极,包括设置在所述绝缘体主体上的金属材料;

层堆叠,包括具有小于100微米的总厚度的绝缘材料,且包含厚度为10微米或小于10微米的非晶氧化铝层和所述非晶氧化铝层上的多个绝缘体层,多个所述绝缘体层包括氮化硅层及氮氧化铝层;以及

加热器,经配置以对所述绝缘体主体进行加热,其中静电夹经配置以在500℃或高于500℃的温度下操作,而所述金属材料未穿过所述层堆叠而扩散。

9.根据权利要求8所述的静电夹系统,其中所述层堆叠包括:

氧化铝层,邻近于所述电极而设置,厚度小于5微米;以及

至少一个额外绝缘体层,设置在所述氧化铝层上,其中所述层堆叠的总厚度大于40微米。

## 制造静电夹的方法、静电夹及静电夹系统

### 技术领域

[0001] 本发明的实施例涉及衬底处理,且更明确地说,涉及用于固持衬底的静电夹、制造静电夹的方法及静电夹系统。

### 背景技术

[0002] 衬底固持器例如静电夹广泛用于许多制造工艺,包含半导体制造、太阳电池制造和其它组件的处理。许多衬底固持器实现衬底加热和衬底冷却以便在所要温度下处理衬底。静电夹在高温(例如,400°C或高于400°C)下操作时展现多个不同故障机制。作为其中一个,当静电夹的介质部分中所存在的金属元素从介质部分滤出且进入邻近衬底(例如,半导体芯片)时,可出现不良金属污染。

[0003] 另一故障机制涉及静电夹的夹持电极内的金属材料变得可移动之时的电迁移。这可导致箝位电流的增大,且最终导致施加到衬底的夹持力减小。

[0004] 相对于这些和其它考虑因素来说,需要本发明的改进。

### 发明内容

[0005] 提供此发明内容以按简化形式介绍概念的选择,下文在具体实施方式中进一步描述所述概念。此发明内容不希望确定所主张标的物的关键特征或基本特征,也不希望辅助确定所主张标的物的范围。

[0006] 在一个实施例中,一种制造静电夹的方法包含:形成绝缘体主体;在所述绝缘体主体上形成电极;以及在所述电极上沉积层堆叠,所述层堆叠包括使用原子层沉积(ALD)而沉积的氧化铝层。

[0007] 在另一实施例中,一种静电夹可包含:绝缘体主体;电极,设置在所述绝缘体主体上;以及层堆叠,包括厚度为10微米或小于10微米的非晶氧化铝层和至少一个额外绝缘体层。

[0008] 在又一实施例中,一种静电夹系统可包含:绝缘体主体;电极,包括设置在所述绝缘体主体上的金属材料;层堆叠,包括总厚度小于100微米的绝缘材料,且包含厚度为10微米或小于10微米的非晶氧化铝层;以及加热器,经配置以对所述绝缘体主体进行加热,其中所述静电夹经配置以在500°C或高于500°C的温度下操作,而所述金属材料未穿过所述层堆叠而扩散。

### 附图说明

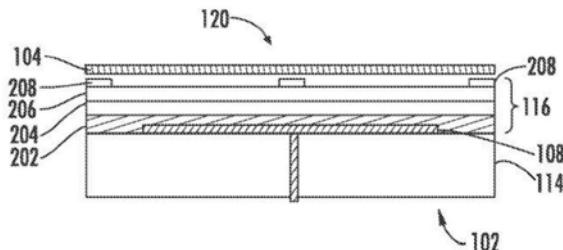

[0009] 图1示出根据本发明的实施例的静电夹系统。

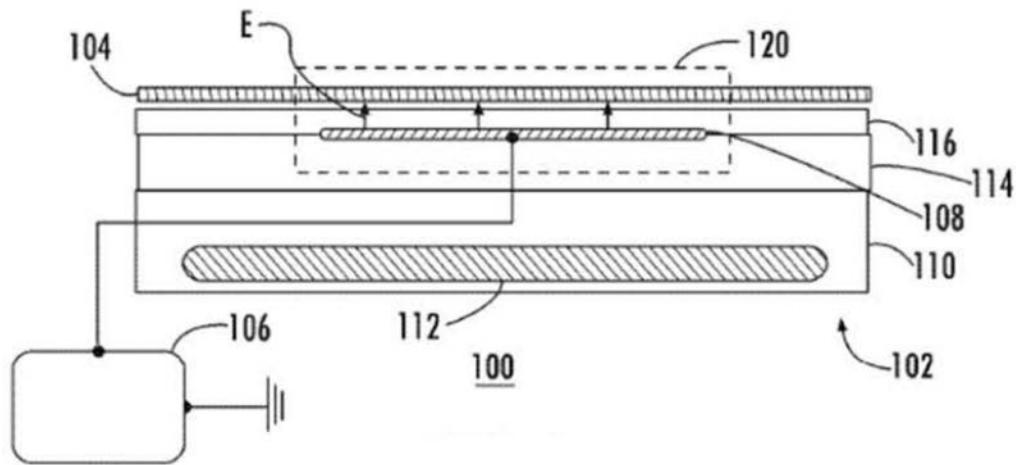

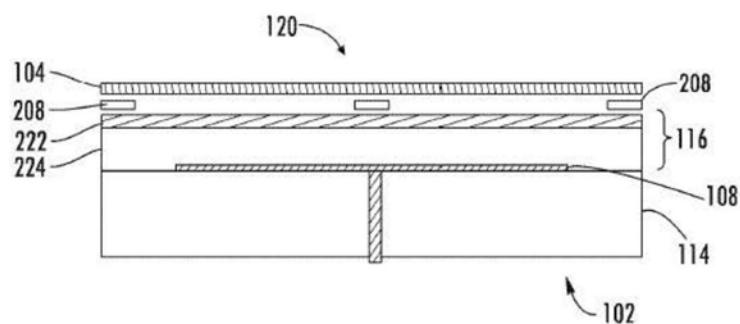

[0010] 图2A示出根据本发明的各种实施例的所组装的静电夹的一部分的侧视横截面图。

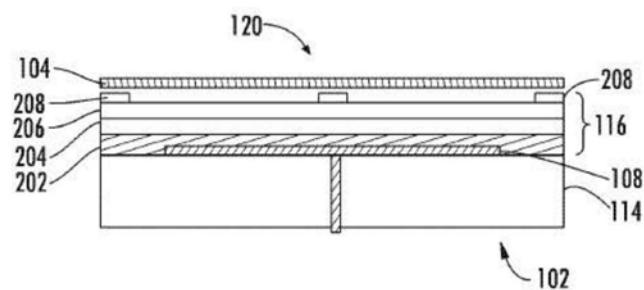

[0011] 图2B示出根据本发明的各种额外实施例的所组装的静电夹的一部分的侧视横截面图。

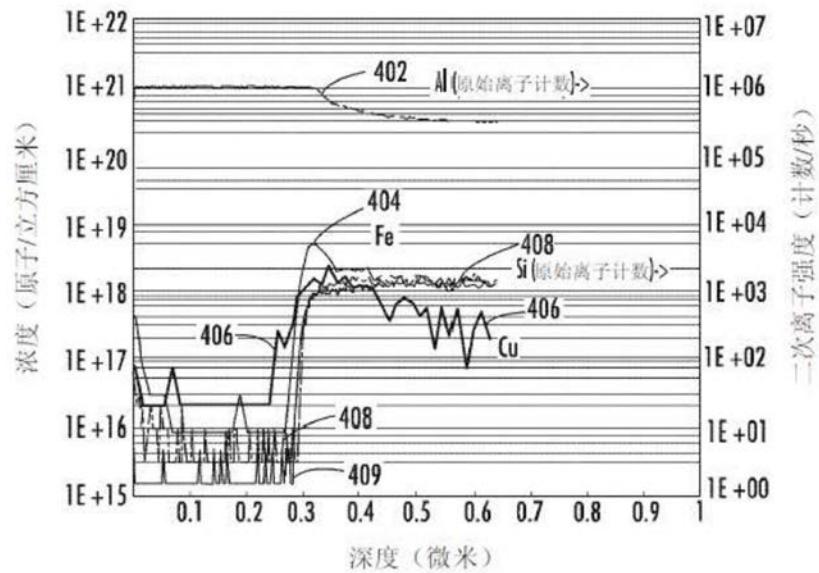

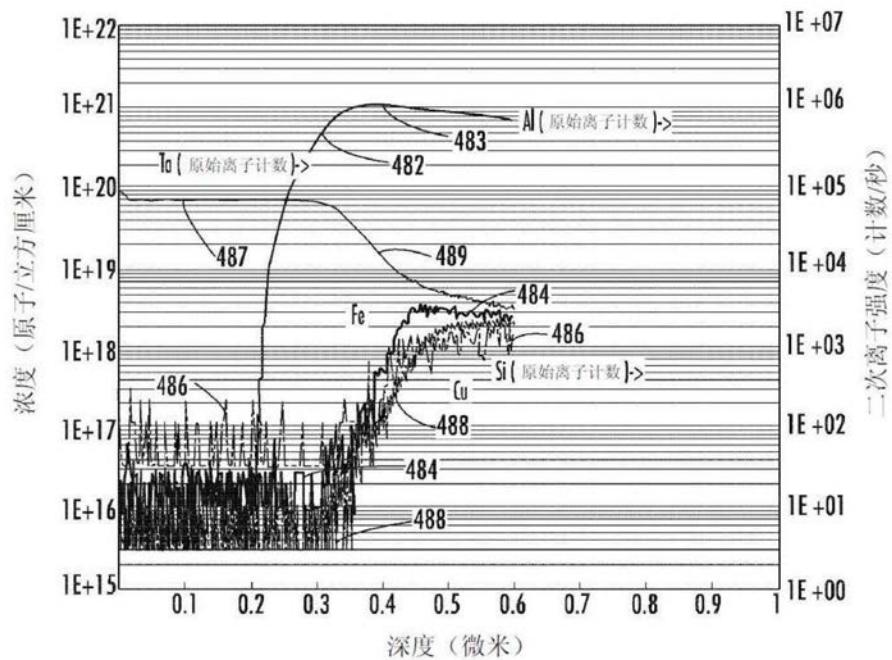

[0012] 图3A示出层堆叠的二次离子质谱分析的结果。

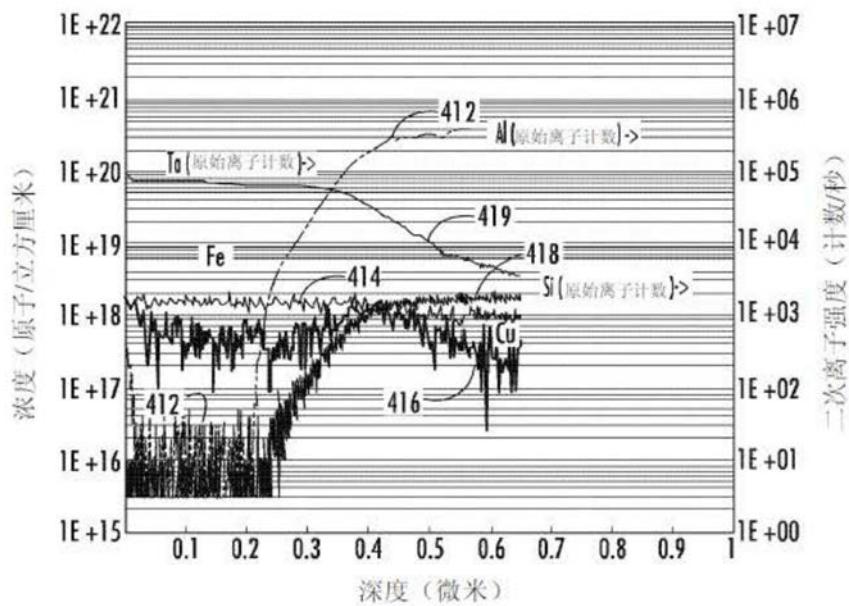

- [0013] 图3B示出另一层堆叠的二次离子质谱分析的结果。

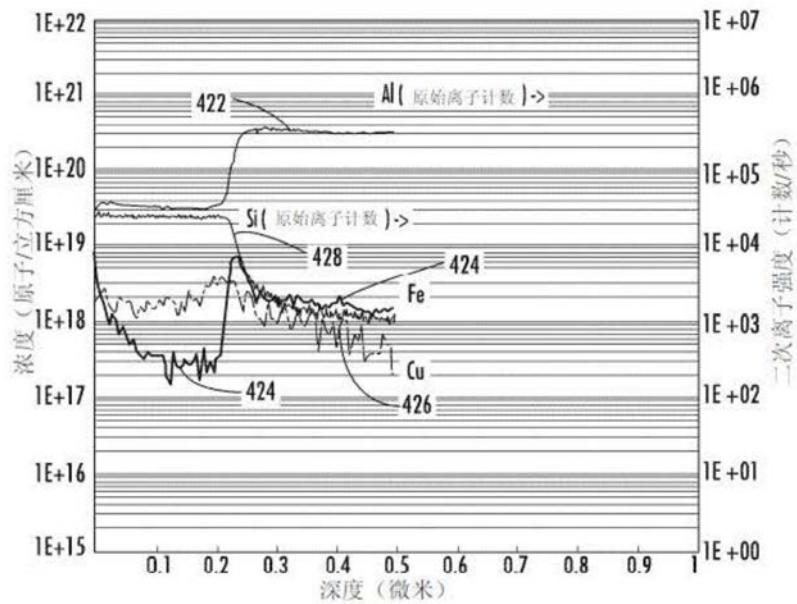

- [0014] 图3C示出再一层堆叠的二次离子质谱分析的结果。

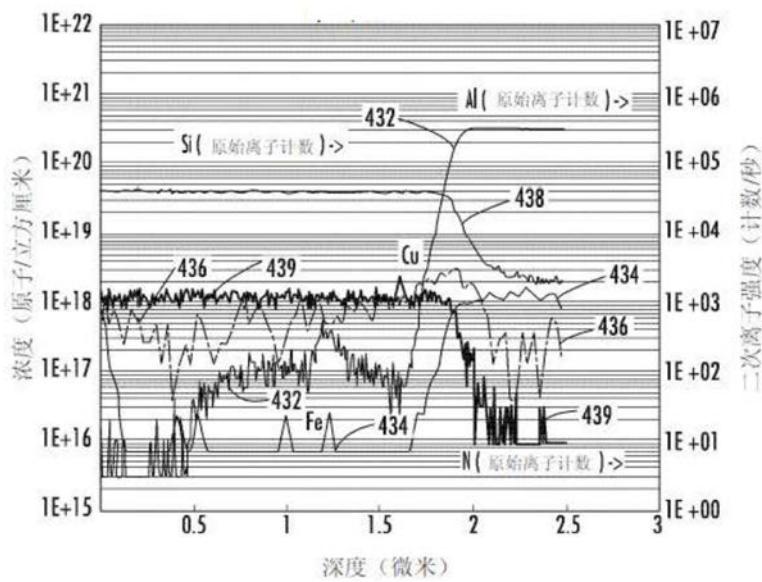

- [0015] 图3D示出再一层堆叠的二次离子质谱分析的结果。

- [0016] 图3E示出又一层堆叠的二次离子质谱分析的结果。

- [0017] 图3F示出又一层堆叠的二次离子质谱分析的结果。

- [0018] 图3G示出额外层堆叠的二次离子质谱分析的结果。

- [0019] 图3H示出对比样本的二次离子质谱分析的结果。

- [0020] 图3I示出另一层堆叠的二次离子质谱分析的结果。

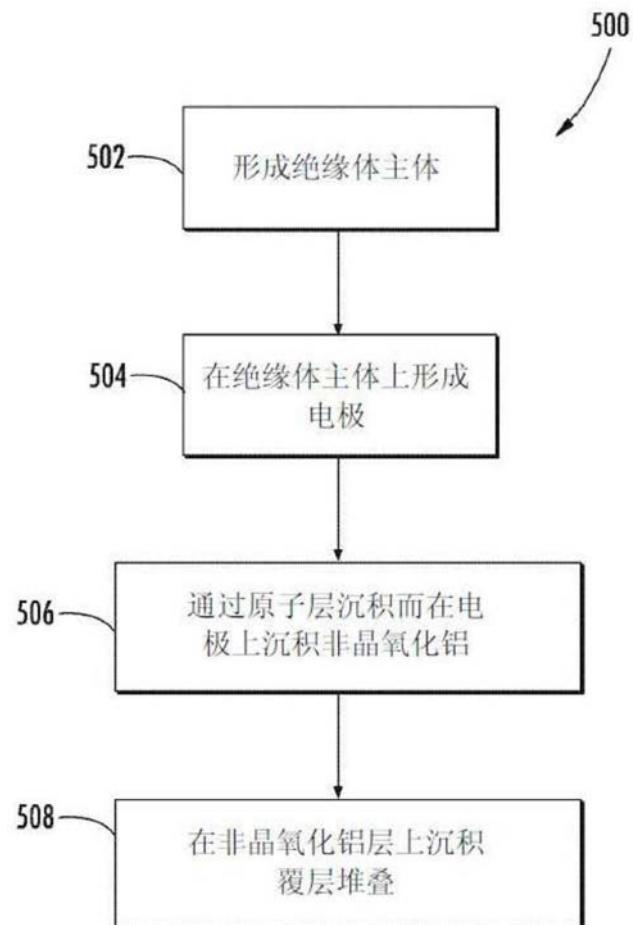

- [0021] 图4为示范性工艺流程。

## 具体实施方式

[0022] 本发明的实施例提供一种抗扩散静电夹，其解决当今静电夹中所发现的多个问题。在本发明的实施例中，抗扩散层堆叠设置在静电夹的电极与将由静电夹固持的衬底之间。抗扩散层堆叠可在操作期间抑制金属从静电夹滤出，而这种滤出原本会污染衬底。抗扩散层堆叠还可防止静电夹的夹持力的减小，而这可由于操作期间夹持金属电极中所诱发的电迁移而发生。

[0023] 在各种实施例中，抗扩散的层堆叠可为至少一层，且在特定实施例中，层堆叠由多层制成。层堆叠可电绝缘以便支持在静电夹与衬底之间产生电场。在一些实施例中，层堆叠的每一层是电绝缘的。在一些实施例中，层堆叠的至少一层可通过原子层沉积(ALD)而形成。通过原子层沉积而形成的至少一层(“ALD层”)可对可存在于静电夹中的金属提供增强的抗扩散性。适用于根据本发明的实施例的抗扩散ALD层的材料包含氧化铝( $\text{Al}_2\text{O}_3$ )。

[0024] 原子层沉积(ALD)为与化学气相沉积(CVD)相关的沉积方法。在ALD中，依序进行使用独立前驱物的多个独立反应(例如，在两个独立反应的状况下，为半循环)以完成沉积固定量的材料的单一完整沉积循环。在例如氧化铝的二元化合物的沉积期间，通过重复两个不同半循环来沉积将形成的层。在每一半循环之后，由第一前驱物供应的固定量的反应性物质保留在衬底表面上。理想地(但未必)，可在第一半循环之后产生第一物质的单一单层。第一物质的单层的每一物质可与下一半循环中所供应的第二前驱物的物质反应。在每一半循环中，在供应反应性物质之后，可执行净化以移除沉积材料的任何未反应的物质。因此，在一循环中反应的材料的总量可均等于每一反应物的单层。以这种方式，每一循环可产生与任何其它循环相同的量的材料。因此，在宽工艺窗口内，层的总厚度仅取决于所执行的循环的数量。此外，这种层的微结构的特征可在于组份材料的交替单层(例如，层A、层B、层A、层B等)。

[0025] 现参看附图，在图1中，展示了根据本发明的实施例而布置的静电夹系统100。静电夹系统100包含用于支撑并固持衬底104以进行处理的静电夹102。静电夹系统100包含电压供应器106，其经配置以将电压施加到电极108。因此，产生了可夹持衬底104的电场E。虽然将静电夹102说明为具有单一电极，但在一些实施例中，静电夹102可包含多个电极，且在不同实施例中，可如同在常规静电夹中一样以DC电压或AC电压来操作。

[0026] 静电夹102包含基底110，在一些实施例中，基底110可为金属材料。在各种实施例中，基底110可包含加热器112。加热器112经设计以在处理期间对静电夹102进行加热，且因

此对衬底104进行加热。在一些实施例中，加热器可经设计以产生400°C或高于400°C、500°C或高于500°C(例如,600°C或800°C)的衬底温度。在其它实施例中，静电夹102可由处于静电夹外部或附着到静电夹的加热器加热。

[0027] 虽然图1中未示出,但如同在常规静电夹中一样,静电夹系统100可包含气体源,其将气体递送到静电夹102内的气体分配系统(未示出),以在衬底104与静电夹之间提供热传导。

[0028] 静电夹102还包含邻近于基底的绝缘体主体114。在一些实施例中,绝缘体主体由氧化铝制成。绝缘体主体114的至少一部分上所设置的是层堆叠116,其可包含至少一个绝缘体层。层堆叠还可覆盖电极108,以使得电极108如图所示设置在绝缘体主体114与层堆叠116之间。在静电夹系统100的操作期间,电极108所产生的电场E与加热器112所产生的高温的组合可施加力,而所述力迫使金属物质从电极108扩散。为了防止或减少金属物质的这种迁移,层堆叠116包含提供增强的抗扩散性的至少一层。在如下文所论述的特定实施例中,所述至少一层是通过原子层沉积而形成。

[0029] 图2A示出根据一个实施例的静电夹102的部分120的特写视图。在这个实施例中,层堆叠116包含多个层。如图2A所说明,层202设置在电极108和绝缘体主体114的一部分上。额外层(即,层204)设置在层202上,而另一层(即,层206)设置在层204上,且邻近于衬底104。表面特征208可形成在层206上,其中,表面特征208可用于支撑衬底104且还可界定背侧气体可设置在衬底104与静电夹102之间的区域。

[0030] 在各种实施例中,层202、层204和层206为绝缘体。在一些实施例中,层202是通过ALD而形成,且与常规静电夹相比,对材料从电极108的扩散提供增强的抗性。在特定实施例中,层202是通过ALD而形成,而层204和层206是通过其它工艺(例如,物理气相沉积(PVD)、化学气相沉积(CVD)或等离子体增强化学气相沉积(PECVD))而形成。然而,所述实施例在此上下文中不受限制。在一些实施例中,层堆叠116的总厚度可为40微米到200微米。

[0031] 在一些实施例中,层202为通过ALD而形成的Al<sub>2</sub>O<sub>3</sub>层。明确地说,层202可为厚度处于0.5微米(500纳米)到10微米范围中的Al<sub>2</sub>O<sub>3</sub>层(本文中亦称为“氧化铝”)。在各种实施例中,通过ALD而形成的氧化铝层可为所沉积的非晶层。如所注明,通过ALD而形成的非晶氧化铝层的特性可包含无针孔的微结构,其对物质穿过层而扩散有抗性。此外,氧化铝层可在通常用于静电夹的使用温度(例如,800°C或低于800°C)下保持为非晶的。所述实施例在此上下文中不受限制。在一些实施例中,通过ALD而形成的Al<sub>2</sub>O<sub>3</sub>层的另一特征为在Al<sub>2</sub>O<sub>3</sub>层内不存在除铝和氧以外的额外元素,其中额外元素可被发现于通过其它技术(例如,常规化学气相沉积或物理气相沉积)而生长的Al<sub>2</sub>O<sub>3</sub>层中。

[0032] 在静电夹102中,由通过ALD而形成的Al<sub>2</sub>O<sub>3</sub>材料构成的层202的实施例可用于多个用途。在第一实例中,层202可用作防止底层金属从电极108扩散出的扩散阻障。第二,层202可用作高介电强度涂层,其提供介质在静电夹应用中适当地发挥作用所需的电压隔绝的实质部分。在一些实施方案中,例如电压供应器106等电压供应器可在电极108(以及未示出的其它电极)上产生200伏到1000伏的电压。如图2A所说明,(介质)层堆叠116介入在电极108(其可处于1000伏的电位下)与衬底104之间。根据报告,经ALD沉积的Al<sub>2</sub>O<sub>3</sub>的介电强度为每微米1000伏。因此,在经ALD沉积的Al<sub>2</sub>O<sub>3</sub>层(即,层202)的厚度为1微米或大于1微米的实施例中,即使在不考虑层204和层206(其总厚度可高达150微米到200微米)的介电强度的情况下,

下,层202也可提供对高达1000伏的电压的介电击穿的足够抗性。

[0033] 在额外实施例中,层202为通过ALD而形成的Al<sub>2</sub>O<sub>3</sub>层,而层204为通过PVD而形成的氮氧化铝(ALON)层,且层206为通过PECVD而形成的氮化硅层。在其它实施例中,可重复地沉积可分别为通过PVD而形成的ALON层和通过PECVD而形成的氮化硅层的层204和层206以形成一系列层,即,层204、层206、层204、层206等。换句话说,可为氮氧化铝层的层204和可为氮化硅层的层206可被视为形成在层202上的覆层堆叠。这种覆层堆叠可接着沉积至少两次以使层堆叠的总厚度累积达所要量。这可用于使层堆叠116的总厚度累积到100微米到200微米,其中,每一个别层的厚度小得多,例如,为约1微米或10微米。所述实施例在此上下文中不受限制。PVD ALON的使用可添加介质厚度,以在维持高介电常数(例如,大于值9)的同时提高层堆叠116的总介电强度。此外,PVD ALON的使用可维持高纯度(>99.95%)。氮化硅层的使用可提供可通过干式蚀刻处理来图案化的接触表面,因此促进产生如表面特征208和其它特征(未示出)所说明的压纹(embossment),所述其它特征可在衬底104被吸引到静电夹102时用作气体密封件。此外,例如PECVD氮化硅等氮化硅层的使用提供面向衬底104的超高纯度表面(>99.995%)。

[0034] 在额外实施例中,单一绝缘体层可布置在层202的顶部上以代替多个层。举例来说,在一个实施例中,具有小于100微米的厚度的单一绝缘体层可设置在层202上,而层202由通过ALD而形成的氧化铝构成且具有1微米的厚度。在其它实施例中,层202可由通过ALD而形成的氧化铝构成,具有1微米的厚度,且可作为邻近于衬底104的最外层而布置,而至少一个绝缘体层设置在层202与电极108之间。举例来说,至少一个绝缘体层可具有50微米到200微米的厚度,且可由用于静电夹中的任何常规绝缘体材料构成。这种配置的优点在于层202可不仅能有效地防止不想要的物质从电极108扩散,而且能有效地防止从用于在电极上形成静电夹的绝缘体层的大部分厚度的常规绝缘体材料扩散。

[0035] 在一些实施例中,层堆叠116可促进静电夹102在相比使用单块介质材料的常规静电夹较低的电压条件和较低的介电强度条件下操作。举例来说,在静电夹102的特定实施例中,层堆叠116可具有75微米或小于75微米的厚度,例如,介于40微米与75微米之间的厚度,且静电夹102可在从电压供应器106施加的小于500伏AC的电压下操作。图2B展示静电夹102的一个变化,其中层堆叠116由被展示为层222的非晶氧化铝层构成。层222设置在覆层堆叠224的顶部上,而覆层堆叠224直接形成在电极108上。层222可通过(例如)ALD而形成,且在一些情形下,可具有0.5微米到5微米的厚度。所述实施例在此上下文中不受限制。覆层堆叠224为可由除氧化铝之外的绝缘体材料(例如,氮化硅或氮氧化铝)的多于一个层构成的绝缘体。覆层堆叠224可通过化学气相沉积、物理气相沉积、等离子体增强物理气相沉积或其它技术而沉积。在一个特定实例中,层222的厚度可为1微米到2微米。给定这个厚度范围且给定层222可由通过ALD而沉积的氧化铝形成,层222可抗击穿,直到跨越层222施加至少1000伏为止。在这个实例中,覆层堆叠224的存在可赋予对击穿的进一步抗性,以使得直到跨越层堆叠116施加大于1000伏,层堆叠116才击穿。使用ALD来提供1微米厚的氧化铝层的优点在于,静电夹102可在高达1000伏或高于1000伏的电压下操作,而不需要形成过厚的层堆叠。举例来说,如果覆层堆叠224由氮氧化铝或氮化硅或两者的组合构成,那么层堆叠116可形成为具有小于100微米(例如,40微米到75微米)的总厚度。这种总厚度可足以产生衬底的适当夹持所需的电容,而同时提供对高达1000伏或高于1000伏的电压的介电击穿的抗

性。同时,可实现这些静电夹性质而不需要使用ALD来沉积过厚的层,而原本沉积过厚的层的工艺相比常规物理气相沉积或化学气相沉积工艺可能需要相对较多时间和成本来沉积给定层厚度。

[0036] 在其它实施例中,电极108可通过ALD而形成,且在特定实施例中,可为铂电极(Pt)。这种电极可提供与高温下的静电夹102的操作兼容的电极层,且将通孔传导提供到绝缘体主体114(在一些实施例中,其可为氧化铝)的背侧。

[0037] 由图2A和图2B示范的实施例不同于常规静电夹,其中常规静电夹通常通过将固态绝缘体接合到电极或在电极上沉积等离子体喷涂层而在电极上形成绝缘层来制造。然而,这些制造绝缘层的方法可导致一种静电夹结构,其尤其在静电夹在高温下(例如,在400°C或高于400°C的温度下)操作时提供对电极金属材料的扩散的不充分的抗性。这可为这些材料中的缺陷或其它非理想特征的结果,如此可导致穿过如常规静电夹中所形成的这种绝缘层的扩散。

[0038] 相比之下,本发明者已发现与照惯例沉积的层相比,将经ALD沉积的Al<sub>2</sub>O<sub>3</sub>层用作静电夹中的电极的覆盖层大幅改进扩散阻障性质。在不同实施例中,经ALD沉积的Al<sub>2</sub>O<sub>3</sub>层可直接沉积在夹电极上(如此,可抑制物质从电极扩散出)或可沉积在自身直接形成在夹电极上的绝缘体层的顶部上。在后者的状况下,经ALD沉积的Al<sub>2</sub>O<sub>3</sub>可抑制存在于绝缘体层中的金属或其它污染物扩散出,且抑制从电极物质扩散出。

[0039] 明确地说,已观察到这些经ALD沉积的Al<sub>2</sub>O<sub>3</sub>层无缺陷和变薄的区域,从而导致比照惯例沉积的层好数个量级的扩散阻障性质。举例来说,本发明者已发现,在电极被使用ALD而制造的Al<sub>2</sub>O<sub>3</sub>层覆盖的静电夹中,与未制造有扩散阻障的静电夹相比,包含Zn、Cu和Pb的金属污染已减少约三个量级。此外,与电极被例如Si<sub>3</sub>N<sub>4</sub>、SiO<sub>2</sub>等其它所沉积的扩散阻障层覆盖的静电夹相比,金属污染减少两个量级,其中这些层是通过如上文所论述的常规薄膜沉积技术而沉积。

[0040] 因此,各种实施例可使用通过ALD而沉积的非晶氧化铝层以促进静电夹的高温操作。明确地说,非晶氧化铝层可设置在静电夹的电极与夹持表面之间的层堆叠中,以使得静电夹可在500°C或高于500°C的温度下操作,而电极的金属材料未穿过层堆叠而扩散。如上文所注明,这种扩散可导致由静电夹固持的衬底的污染,且可另外导致夹持性质(例如,可由静电夹施加的夹持力)和层堆叠的介电强度的降低。

[0041] 为了研究使用ALD而制造的Al<sub>2</sub>O<sub>3</sub>层对防止金属污染物的扩散的效益,在玻璃绝缘体衬底上沉积一系列不同候选扩散阻障层堆叠。玻璃绝缘体衬底由常规静电夹中可见的已知绝缘体材料制成。发现玻璃绝缘体衬底具有浓度在1×10<sup>17</sup>/立方厘米到1×10<sup>18</sup>/立方厘米的范围中的低含量的铜和铁杂质。玻璃绝缘体衬底上所沉积的扩散阻障层堆叠含有包含以下各者的不同组合的至少一层:使用ALD而制造的200纳米到300纳米厚的Al<sub>2</sub>O<sub>3</sub>层、使用ALD而制造的200纳米厚的Ta<sub>2</sub>O<sub>5</sub>层以及使用PECVD而制造的200纳米或2微米厚的氮化硅层。在具有Al<sub>2</sub>O<sub>3</sub>层的所有层堆叠中,Al<sub>2</sub>O<sub>3</sub>层邻近于衬底而形成,而在具有氮化硅层的所有层堆叠中,氮化硅层为形成与空气的界面的最外层。

[0042] 表1呈现以这种方式形成的扩散阻障层堆叠的矩阵的概述。在玻璃衬底上制造层堆叠且通过加热在550°C下处理层堆叠持续24小时后,执行成分分析。通过二次离子质谱法(SIMS)来执行成分分析,其中二次离子质谱法(SIMS)为根据相对于物体的表面的深度而执

行物体内的不同元素的成分剖析的技术,其中物体可为衬底、层或层群组。

[0043] 表1

| 扩散阻障测试矩阵        |                                                 |                                                 |                        |                      |

|-----------------|-------------------------------------------------|-------------------------------------------------|------------------------|----------------------|

| 玻璃介质衬底的约 1×1 样本 |                                                 |                                                 |                        |                      |

|                 | ALD<br>Al <sub>2</sub> O <sub>3</sub><br>200 纳米 | ALD<br>Ta <sub>2</sub> O <sub>5</sub><br>200 纳米 | PECVD<br>SiN<br>200 纳米 | PECVD<br>SiN<br>2 微米 |

| 图 3A            | X                                               |                                                 |                        |                      |

| 图 3B            |                                                 | X                                               |                        |                      |

| 图 3C            |                                                 |                                                 | X                      |                      |

| 图 3D            |                                                 |                                                 |                        | X                    |

| 图 3E            | X                                               |                                                 |                        | X                    |

| 图 3F            |                                                 | X                                               |                        | X                    |

| 图 3G            | X                                               | X                                               |                        | X                    |

| 图 3H            | 无涂层—参考样本                                        |                                                 |                        |                      |

| 图 3I            | X                                               | X                                               |                        |                      |

[0045] SIMS分析的结果展示在图3A到图3I中,且可如下概述。值得注意的是,虽然氧化钽和氧化铝层的标称厚度为200纳米,但SIMS分析的结果暗示这些层中的每一者具有较接近于300纳米的厚度。然而,这些层可仍如同在表1中一样被称为“200纳米厚”或在下文的论述中被称为“标称200纳米厚”。当制造包含通过ALD而形成的Al<sub>2</sub>O<sub>3</sub>层的层堆叠(具有或不具有额外层)时,铜和铁扩散受到抑制。换句话说,与底层衬底中的铜或铁信号量相比,层堆叠中的铜或铁信号量大幅减少。当ALD Al<sub>2</sub>O<sub>3</sub>层不存在于层堆叠中时,2微米厚的氮化硅层能有效地抑制铁扩散而不能有效地抑制铜扩散,以致于氮化硅层中的铜浓度与衬底中的铜浓度相当。使用ALD而制造的单一标称200纳米厚的Ta<sub>2</sub>O<sub>5</sub>层的使用不能有效地抑制铜或铁扩散。2微米厚的氮化硅层和200纳米厚的Ta<sub>2</sub>O<sub>5</sub>层的双层也不能有效地抑制铜扩散。

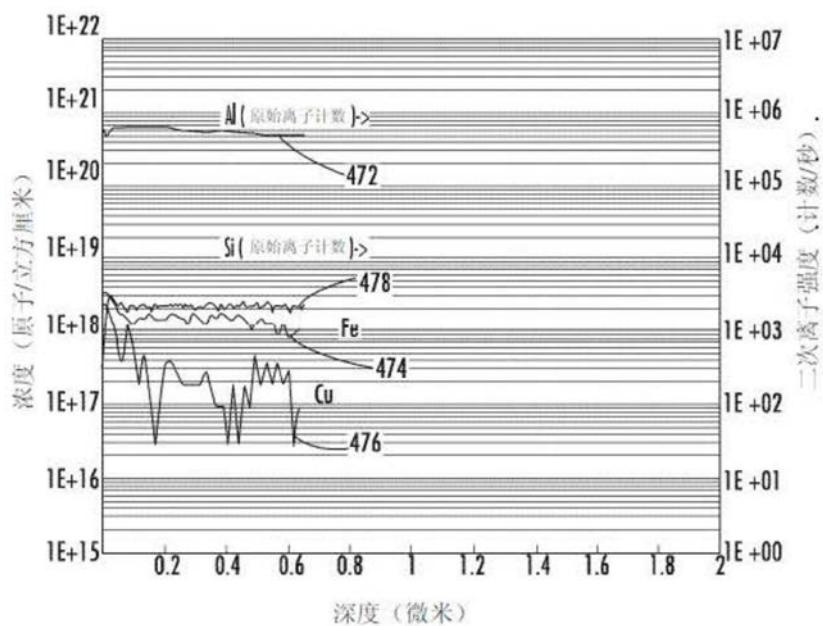

[0046] 图3H示出对比(衬底)样本的二次离子质谱分析的结果,其指示衬底中所存在的铜和铁的含量。该图指示在不具有任何扩散阻障层的情况下衬底中的硅(曲线478)、铝(曲线472)、铁(曲线474)和铜(曲线476)的信号水平。

[0047] 参看图3A,展示由使用ALD而制造的单一200纳米到300纳米厚的Al<sub>2</sub>O<sub>3</sub>层构成的层堆叠的二次离子质谱分析的结果,其中大于300纳米的深度处所存在的铝和硅信号表示衬底。如图3A所说明,防止铜与铁两者从玻璃绝缘体衬底扩散。对于不同元素来说,数据绘制为给定元素的原始信号计数或浓度。明确地说,曲线402表示铝,其信号水平在约0.3微米的深度(其指示使用ALD而制造的Al<sub>2</sub>O<sub>3</sub>层与底层玻璃衬底之间的界面)处降低。底层玻璃衬底中的铝信号可指示处理之前的玻璃衬底中的铝的浓度。如图还展示,玻璃衬底包含硅(曲线408)、铜(曲线406)、铁(曲线404)和钽(曲线409)。衬底中的铜和铁浓度在衬底中处于1×

$10^{18}$ 的范围内,这指示一浓度,该浓度指示衬底中的这些金属元素的百万分之十的范围中的相对原子浓度。在小于0.3微米的深度处的区域中测量的铜和铁浓度表示其在使用ALD而制造的Al<sub>2</sub>O<sub>3</sub>层内的相应浓度。如图3A所说明,铜与铁两者的浓度处于 $1 \times 10^{16}$ 的范围内,这可对应于这些元素的近似检测极限,从而指示铜或铁极少扩散或不扩散到使用ALD而制造的Al<sub>2</sub>O<sub>3</sub>层中。

[0048] 图3B示出由使用ALD而制造的标称200纳米厚的Ta<sub>2</sub>O<sub>5</sub>层构成的另一层堆叠的二次离子质谱分析的结果。在这种状况下,铜和铁穿过标称200纳米厚的Ta<sub>2</sub>O<sub>5</sub>层而扩散。曲线419表示钽,其信号水平在约0.3微米的深度(其指示使用ALD而制造的Ta<sub>2</sub>O<sub>5</sub>层与包含硅(曲线418)、铜(曲线416)、铁(曲线414)和铝(曲线412)的底层玻璃衬底之间的界面)处降低。如图3B所说明,如深度小于0.3微米时的信号所指示的氧化钽层内的铜和铁的浓度与衬底中的铜和铁的相应浓度(如大于0.3微米的深度的信号所指示)大致上相同。这说明在550°C下处理持续24小时后,氧化钽层不抑制铜和铁从衬底扩散。

[0049] 图3C示出由通过PECVD而制造的单一200纳米厚的氮化硅层构成的再一层堆叠的二次离子质谱分析的结果。在这个实例中,氮化硅层中所存在的硅由曲线428指示,其中曲线428在0.2微米的深度(其对应于氮化硅层与衬底之间的界面)处降低。铜(曲线426)和铁(曲线424)在较小程度上穿过硅层而扩散。铝(曲线422)也看似扩散到氮化硅层中。

[0050] 图3D示出由通过PECVD而制造的单一2微米厚的氮化硅层构成的再一层堆叠的二次离子质谱分析的结果,且由曲线438指示硅,由曲线439指示氮。在这个实例中,铜穿过阻障层而扩散,且铁扩散受到抑制。铜(曲线436)贯穿硅层而扩散以使得铜浓度的水平在氮化硅层中与衬底中大致上相同。在小于2微米的深度处的氮化硅膜中的铁信号(曲线434)的低水平展示铁扩散受到抑制。少量的铝(曲线432)还看似至少扩散到较接近衬底的氮化硅层的下方区域中。氮(曲线439)为氮化硅层的一部分。

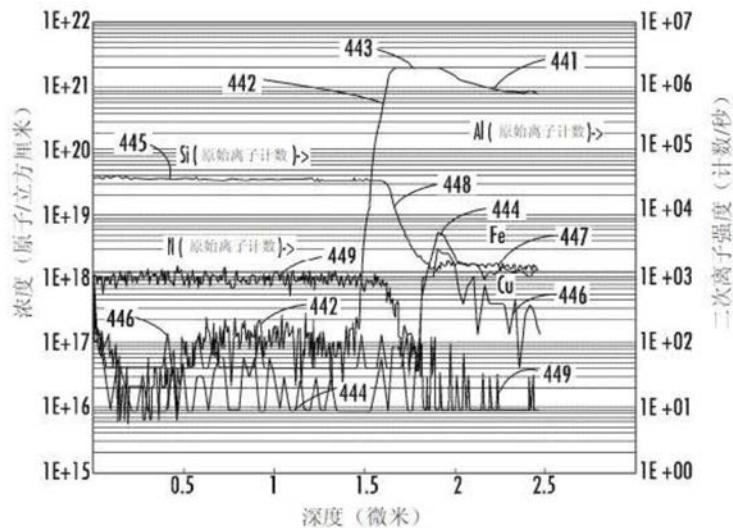

[0051] 图3E示出由使用ALD而制造的标称200纳米厚的Al<sub>2</sub>O<sub>3</sub>层构成的又一层堆叠的二次离子质谱分析的结果,所述Al<sub>2</sub>O<sub>3</sub>层由铝曲线442的平稳部分443指示。这层邻近于衬底,其位置由铝曲线442的部分441和硅曲线448的部分447指示。通过PECVD而制造的2微米厚的氮化硅层设置在标称200纳米厚的Al<sub>2</sub>O<sub>3</sub>层的顶部上,如氮曲线449和硅曲线448的平稳部分445所指示。在这种状况下,铜(曲线446)和铁(曲线444)扩散有效地受到抑制。

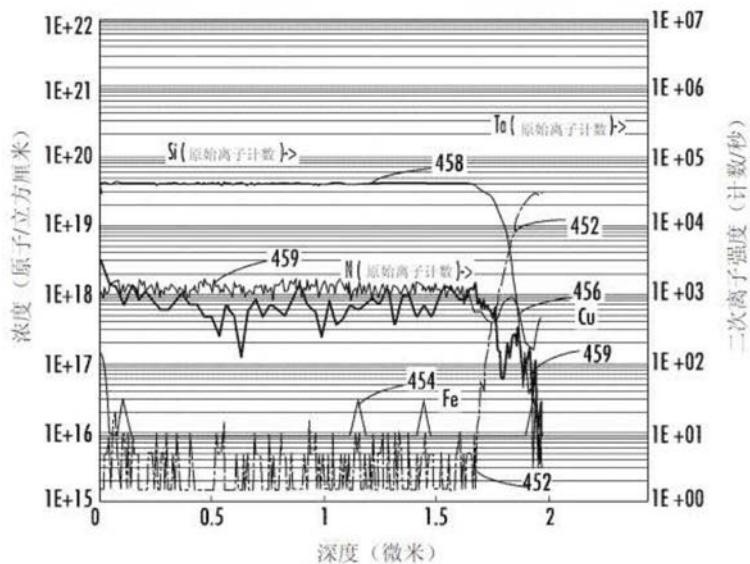

[0052] 图3F示出由使用ALD而制造的200纳米厚的Ta<sub>2</sub>O<sub>5</sub>层构成的又一层堆叠的二次离子质谱分析的结果,所述Ta<sub>2</sub>O<sub>5</sub>层由曲线452指示。通过PECVD而制造的2微米厚的氮化硅层设置在标称200纳米厚的Ta<sub>2</sub>O<sub>5</sub>层的顶部上,如氮曲线459和硅曲线458所指示。未展示底层衬底。在这种状况下,铁扩散(曲线454)受到抑制,且铜(曲线456)贯穿层堆叠而扩散。

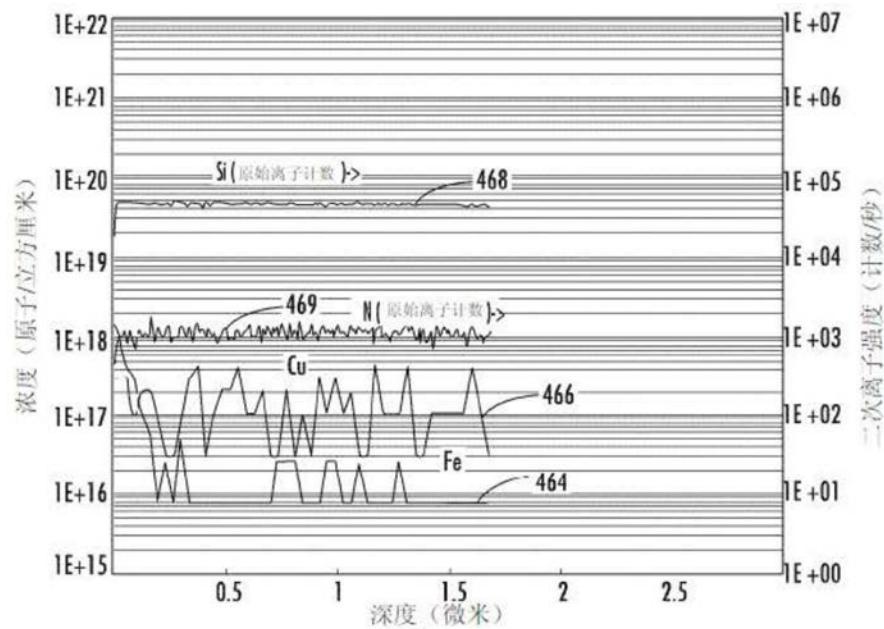

[0053] 图3G示出由使用ALD而制造的标称200纳米厚的Al<sub>2</sub>O<sub>3</sub>层、使用ALD而制造的200纳米厚的Ta<sub>2</sub>O<sub>5</sub>层和通过PECVD而制造的2微米厚的氮化硅层(如硅曲线468和氮曲线469所指示)构成的额外层堆叠的二次离子质谱分析的结果。收集SIMS数据直到刚好1.7微米的深度,因此不反映较接近于衬底的氧化铝或氧化钽层。然而,可见,铜(曲线466)和铁(曲线464)扩散受到抑制,如氮化硅层中的低计数水平所证实。

[0054] 图3I示出由使用ALD而制造的标称200纳米厚的Al<sub>2</sub>O<sub>3</sub>层(由铝曲线482的平稳部分483指示)和使用ALD而制造的标称200纳米厚的Ta<sub>2</sub>O<sub>5</sub>层(由钽曲线489的平稳部分487指示)构成的另一层堆叠的二次离子质谱分析的结果。这些层设置在由硅曲线488指示的衬底上。

再一次,铜(曲线486)和铁(曲线484)扩散受到抑制,以使得铜和铁不扩散到层堆叠中。

[0055] 图4示出根据本发明的实施例的用于制造静电夹的过程500中所涉及的示范性操作。在框502中,形成静电夹的绝缘体主体。绝缘体主体可形成在基底(例如,金属块)上。基底可包含加热器或可耦接到用于对静电夹进行加热的加热器。在一些状况下,绝缘体主体可由陶瓷(例如,氧化铝)构成。在框504中,在绝缘体主体上形成电极。在一些实例中,电极可由金属材料(例如,钨、钼或铂)构成。所述实施例在此上下文中不受限制。在一些变化中,电极可为布置在绝缘体主体上的多个电极。在框506中,通过原子层沉积而在电极上沉积非晶氧化铝层。在一些实施例中,氧化铝层可具有500纳米到10微米的厚度。氧化铝层可按照包封电极和未被电极覆盖的绝缘体主体的暴露部分的保形方式沉积。

[0056] 在框508中,在非晶氧化铝层上沉积覆层堆叠。覆层堆叠可包含单一绝缘体层,例如,氮化硅或氮氧化铝。覆层堆叠可包含相继沉积的多个绝缘体层,其中每一绝缘体层与先前沉积的绝缘体层不同。在一些实例中,覆层堆叠可具有介于40微米与200微米之间的总厚度。覆层堆叠可通过仅一个沉积工艺(例如,化学气相沉积)来制备,或可使用多个不同沉积工艺来制备。举例来说,形成覆层堆叠的一部分的氮氧化铝层可通过物理气相沉积工艺来沉积,而形成覆层堆叠的另一部分的氮化硅层是通过等离子体增强化学气相沉积来沉积。

[0057] 在过程500的一个变化中,可在框506之前执行框508,以使得覆层堆叠直接沉积在电极的顶部上,且氧化铝层沉积在覆层堆叠的顶部上。

[0058] 虽然可部署前述实施例以用于高温(例如,100°C到700°C的温度)下的静电夹的操作,但预期本发明的实施例还可在未加热的静电夹的操作期间抑制不想要的物质扩散。

[0059] 总的来说,本发明的实施例提供改进的静电夹,其包含使用ALD而制造的Al<sub>2</sub>O<sub>3</sub>层,其中所述Al<sub>2</sub>O<sub>3</sub>层设置在夹电极与将夹持的衬底之间。在各种实施例中,使用ALD而制造的Al<sub>2</sub>O<sub>3</sub>层可形成电绝缘材料的层堆叠的一部分,所述层堆叠具有50微米到200微米的总厚度。在各种实施例中,使用ALD而制造的Al<sub>2</sub>O<sub>3</sub>层可邻近于夹电极而设置;可设置在另一绝缘体材料的顶部上,因此形成最外层;或可设置在绝缘体层的堆叠内,以使得绝缘体层设置在使用ALD而制造的Al<sub>2</sub>O<sub>3</sub>与夹电极之间,且另一绝缘体层设置在使用ALD而制造的Al<sub>2</sub>O<sub>3</sub>与将夹持的衬底之间。除了提供扩散阻障以防止不想要的物质从夹电极、绝缘体层或其它静电夹组件扩散外,使用ALD而制造的Al<sub>2</sub>O<sub>3</sub>还可促进实现绝缘体层的目标击穿强度,以使得在静电夹的操作期间将电压施加到电极时,绝缘体堆叠不击穿。

[0060] 本发明在范围上不受本文所描述的具体实施例限制。实际上,除本文所描述的实施例之外,根据上述描述和随附附图,本发明的其它各种实施例和修改对于所属领域的技术人员来说将为明显的。因此,希望这些其它实施例和修改落入本发明的范围内。此外,尽管本文中已在特定实施方案的上下文中在特定环境中针对特定目的描述了本发明,但所属领域的技术人员应认识到,其用处不限于此且本发明可有益地在任何数量的环境中针对任何数量的目的而实施。因此,本文阐述的权利要求书应鉴于如本文中描述的本发明的全宽度和精神来解释。

图1

图2A

图2B

图3A

图3B

图3C

图3D

图3E

图3F

图3G

图3H

图3I

图4