(19) RÉPUBLIQUE FRANÇAISE

INSTITUT NATIONAL

DE LA PROPRIÉTÉ INDUSTRIELLE

COURBEVOIE

(11) **Nº de publication :**

(à n'utiliser que pour les

commandes de reproduction)

(21) **Nº d'enregistrement national :**

**14 59130**

(51) Int Cl<sup>8</sup> : **H 01 L 21/04** (2017.01)

**3 026 557**

(12)

## BREVET D'INVENTION

**B1**

(54) **PROCEDE DE DOPAGE D'UN SEMI-CONDUCTEUR A BASE DE GAN.**

(22) **Date de dépôt :** 26.09.14.

(30) **Priorité :**

(43) **Date de mise à la disposition du public

de la demande :** 01.04.16 Bulletin 16/13.

(45) **Date de la mise à disposition du public du

brevet d'invention :** 16.03.18 Bulletin 18/11.

(56) **Liste des documents cités dans le rapport de

recherche :**

*Se reporter à la fin du présent fascicule*

(60) **Références à d'autres documents nationaux

apparentés :**

**Demande(s) d'extension :**

(71) **Demandeur(s) :** COMMISSARIAT A L'ENERGIE

ATOMIQUE ET AUX ENERGIES ALTERNATIVES —

FR.

(72) **Inventeur(s) :** AGRAFFEIL CLAIRE.

(73) **Titulaire(s) :** COMMISSARIAT A L'ENERGIE

ATOMIQUE ET AUX ENERGIES ALTERNATIVES.

(74) **Mandataire(s) :** CABINET HECKE Société anonyme.

## Procédé de dopage d'un semi-conducteur à base de GaN

### 5 Domaine technique de l'invention

L'invention est relative à un procédé d'implantation ionique et d'activation d'impuretés dopantes dans un semi-conducteur à base de GaN.

10

### État de la technique

L'implantation ionique est couramment utilisée pour doper des semi-conducteurs. Pour fabriquer des jonctions p-n, on utilise généralement des masques afin de sélectionner les zones du semi-conducteur qui doivent être implantées et les zones à protéger. On réalise ensuite l'étape d'implantation, en utilisant des ions généralement produits à partir d'une source gazeuse ou solide (source utilisée pour le Mg par exemple), qui impactent le semi-conducteur après avoir été accélérés à une énergie comprise par exemple 15 entre 10 et 500 keV.

20

La nature des ions implantés est choisie en fonction du type de dopage que l'on souhaite obtenir. Les ions  $Mg^+$  sont par exemple utilisés pour réaliser un dopage p (excès de trous) dans des semi-conducteurs à base de GaN, 25 tandis que les ions  $Si^+$  sont souvent employés pour réaliser un dopage n (excès d'électrons) du même type de semi-conducteur. Le semi-conducteur subit ensuite un traitement thermique afin d'activer plus ou moins efficacement les impuretés dopantes.

Le document « Implanted *p-n* junctions in GaN » (X.A. Cao et al., Solid-state Electronics, 43 (1999) 1235-1238) décrit une méthode d'implantation d'ions Si<sup>+</sup> dans un semi-conducteur de type GaN dopé par des ions Mg<sup>+</sup>, afin d'obtenir un semi-conducteur dopé n<sup>+</sup>/p. Ici les ions Si<sup>+</sup> sont implantés dans des zones sélectionnées au moyen d'un masque déposé sur le semi-conducteur. Le masque est enlevé après implantation, puis une couche d'AIN est déposée par pulvérisation cathodique sur le semi-conducteur afin de protéger ce dernier lors du traitement thermique d'activation des dopants.

10 Le document « Experimental and numerical investigation of the electrical characteristics of vertical n-p junction diodes created by Si implantation into p-GaN » (A. Baharin, Institute of Electrical and Electronics Engineers, 978-1-4244-2717-8/08, (2008)) décrit une méthode de fabrication de jonctions p-n verticales à partir de semi-conducteurs de type GaN dopés p/p<sup>+</sup> au moyen 15 d'ions Mg<sup>+</sup>. Ici, des ions Si<sup>+</sup> sont implantés au moyen de faisceaux d'ions de différentes énergies, pour maîtriser la profondeur d'implantation dans le semi-conducteur.

20 **Objet de l'invention**

Un objet de l'invention est de prévoir une alternative aux procédés de l'art antérieur afin de doper un semi-conducteur, notamment dans le but de fabriquer des jonctions p-n.

25 On tend à résoudre ce problème au moyen d'un procédé qui comporte les étapes suivantes :

- prévoir un substrat comprenant une couche en matériau semi-conducteur à base de GaN recouvert par un masque à base de silicium,

30

- planter des impuretés dans le masque de manière à transférer des impuretés dopantes de type Si par diffusion depuis le masque vers la couche en matériau semi-conducteur à base de GaN,

- réaliser un traitement thermique configuré pour activer les impuretés dopantes.

5

Selon un aspect de l'invention, le masque peut couvrir partiellement le substrat de manière à définir une zone recouverte par le masque et une zone découverte, l'implantation étant réalisée avec des ions  $Mg^+$  pour doper la zone découverte du substrat.

10

Le procédé peut également comprendre une étape de dépôt d'une couche de protection réalisée avant l'étape de traitement thermique. Le matériau de la couche de protection peut être choisi parmi l'oxyde de silicium, ou le nitre de silicium du type  $Si_xN_y$ , le silicium amorphe, et les composés du type  $HfSi_xO_y$ , et préférentiellement parmi l'oxyde d'aluminium et le nitre d'aluminium.

15

Le dépôt de la couche de protection est réalisé avant l'étape de traitement thermique, et peut par exemple être effectué après l'étape d'implantation des impuretés dopantes et des impuretés dopantes supplémentaires, directement sur le masque, ou après retrait de ce dernier. De manière alternative, il est envisageable de déposer la couche de protection avant l'implantation des impuretés dopantes dans le cas où la couche de protection n'est pas à base de silicium. Après le traitement thermique, la couche de protection peut avantageusement être retirée.

20

De manière préférée, l'étape d'implantation peut être réalisée à une température comprise entre 15 et 700°C, de préférence entre 450 et 600°C.

25

30

Par ailleurs, l'étape de traitement thermique peut avantageusement comprendre une combinaison d'au moins deux recuits de durées et de températures différentes. Au moins l'un des recuits peut en outre être réalisé à une température supérieure à 1000°C.

5

En ce qui concerne le masque, celui-ci peut avantageusement avoir une épaisseur comprise entre 2 et 400 nm. L'épaisseur de la couche en matériau semi-conducteur peut quant à elle être comprise entre 5 nm et 10  $\mu$ m, préférentiellement entre 500nm et 10 $\mu$ m, idéalement égale à 1 $\mu$ m.

10

### **Description sommaire des dessins**

15

D'autres avantages et caractéristiques ressortiront plus clairement de la description qui va suivre de modes particuliers de réalisation de l'invention donnés à titre d'exemples non limitatifs et représentés aux dessins annexés, dans lesquels les figures 1 à 10 illustrent de façon schématique un mode de mise en œuvre du procédé de dopage d'un semi-conducteur à base de GaN.

20

### **Description détaillée**

25

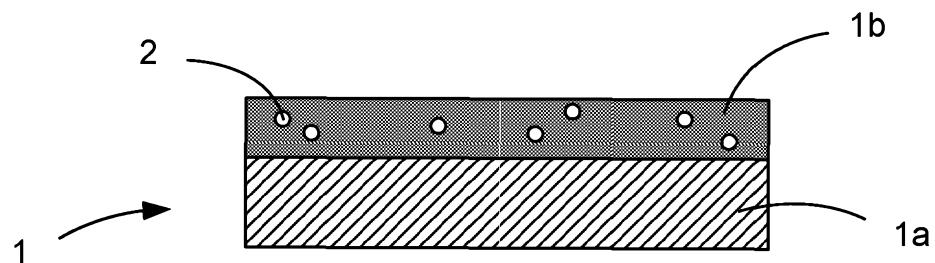

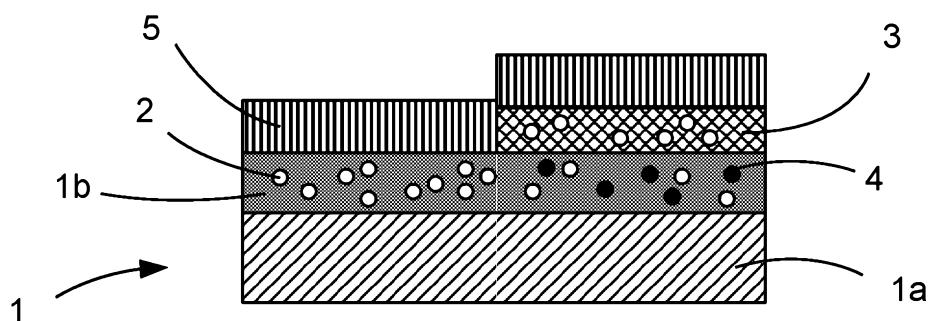

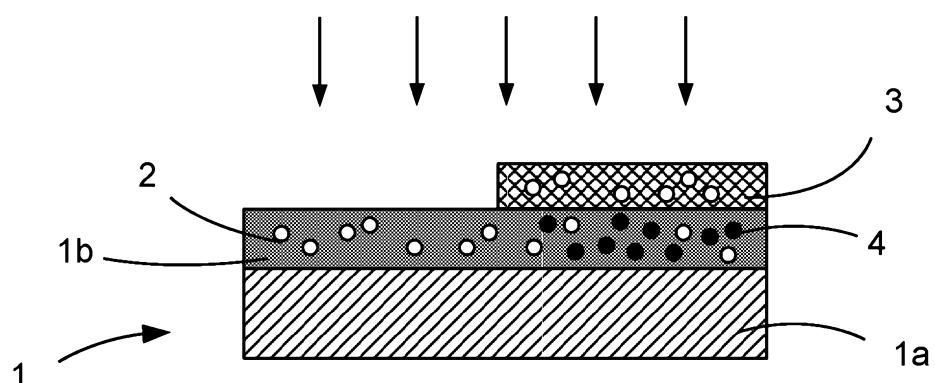

Selon un premier mode de mise en œuvre du procédé de dopage représenté sur les figures 1 à 10, il faut tout d'abord prévoir un substrat 1 tel que celui représenté à la figure 1. Celui-ci comporte un support 1a par exemple en silicium ou en saphire,  $Al_2O_3$ , SiC, et une couche en matériau semi-conducteur 1b à base de GaN. En alternative, le substrat 1 peut être en GaN massif.

30

Lorsque le substrat 1 est un bloc de GaN massif, il est possible de recouvrir la face arrière de couches de protection avantageusement identiques à celles déposées sur le substrat 1 en face avant, et qui vont être décrites ci-après. La face avant du substrat 1 est définie ici comme la face impactée par le faisceau d'impuretés dopantes, et la face arrière comme la face opposée à la face avant.

La réalisation du substrat 1 comprend avantageusement une première étape de nettoyage du support 1a, comme par exemple un nettoyage de type RCA si le support 1a est en silicium. La couche en matériau semi-conducteur 1b est ensuite fabriquée par croissance épitaxiale directement sur le support 1a. Le choix du matériau du support 1a est choisi avantageusement pour avoir des paramètres de maille similaires à ceux de la couche en matériau semi-conducteur 1b afin que cette dernière croisse de manière cohérente.

Pour améliorer la qualité de la couche en matériau semi-conducteur 1b, une couche intermédiaire à base d'AlGaN d'au moins 1  $\mu\text{m}$  d'épaisseur peut éventuellement être déposée sur le support 1a avant la croissance épitaxiale de la couche 1b (mode de réalisation non représenté). Par exemple, pour un support 1a en saphhire, la couche en matériau semi-conducteur 1b à base de GaN peut être directement déposée sur le support 1a si celui-ci est réalisé en saphhire. En revanche, s'il est réalisé en silicium, il est judicieux de déposer une couche tampon à base d'AlGaN.

Lorsque la réalisation de la couche en matériau semi-conducteur 1b est terminée, celle-ci peut avantageusement avoir une épaisseur comprise entre 100 nm et 10  $\mu\text{m}$ , préférentiellement entre 5nm et 10 $\mu\text{m}$ , idéalement égale à 1 $\mu\text{m}$ .

5 Selon un mode de réalisation avantageux, le matériau semi-conducteur 1b à base de GaN n'est pas dopé initialement ou n'est pas intentionnellement dopé initialement. Cela permet de réaliser simultanément un dopage p et n lors de l'étape d'implantation ionique, comme on le verra plus loin et de former une couche 1b apte des former des circuits complémentaires avec des dispositifs utilisant un excès d'électrons et des dispositifs utilisant un excès de trous.

10 De manière alternative, il est possible d'utiliser une couche en matériau semi-conducteur 1b dopée p. Dans ce mode de mise en œuvre, les impuretés dopantes 2 peuvent par exemple être des ions Mg+, introduits directement lors de la croissance épitaxiale (cf. figure 1).

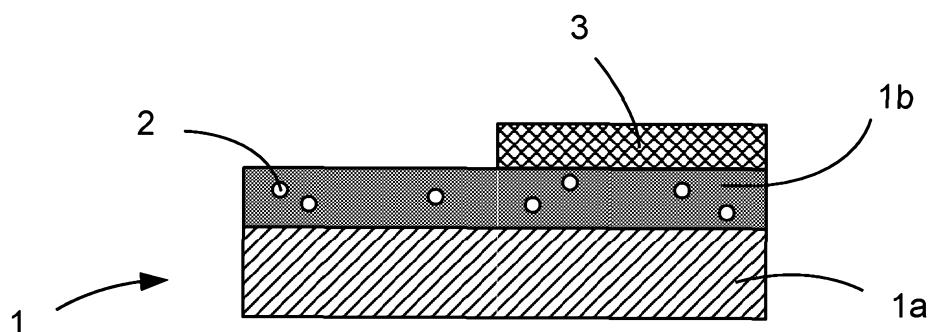

15 Dans la deuxième étape du mode de mise en œuvre, on réalise un masque 3 configuré pour recouvrir en totalité ou en partie la surface de la couche en matériau semi-conducteur 1b. Cette étape du procédé est représentée à la figure 2. Comme illustré, le masque 3 peut couvrir partiellement le substrat 1 de façon à définir une zone recouverte et une zone découverte. Ce masque 3 peut par exemple être réalisé par photolithographie ou lithographie 20 électronique. Son épaisseur est avantageusement comprise entre 2 et 400 nm.

25 Le matériau du masque 3 est à base de silicium préférentiellement, d'oxyde de silicium et/ou de nitrure de silicium, de silicium amorphe, ou de HfSiO<sub>2</sub>. Il comporte donc des atomes de Si capables de diffuser dans le substrat 1 lorsqu'on leur apporte l'énergie nécessaire. Cette propriété permet d'implanter des atomes de Si dans le matériau semi-conducteur 1b et donc de réaliser un dopage local n.

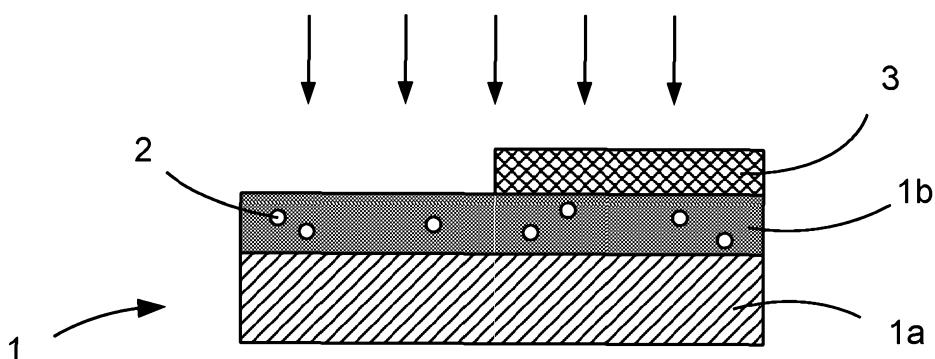

Dans une troisième étape du mode de mise en œuvre, on réalise une implantation de dopants 2 appliquée sur le masque 3 et sur la zone découverte du substrat 1 (cf. figure 3). Les dopants 2 peuvent être de type p, par exemple des d'ions  $Mg^+$ , de type n comme par exemple des ions  $Si^+$ , ou des dopants non électriquement actifs tels que des ions  $N^+$ .

5 De manière classique, les conditions d'implantation sont imposées d'une part par les performances techniques des équipements d'implantation, et d'autre part par la concentration et la localisation des impuretés dopantes 2 que l'on souhaite planter dans la couche en matériau semi-conducteur 1b.

10 Par exemple, pour un faisceau d'ions  $Mg^+$  ayant une fluence de  $2.10^{15}$  atomes/cm<sup>2</sup> et une énergie de 200keV, les impuretés dopantes 2 peuvent être implantées dans une couche de GaN jusqu'à une profondeur de l'ordre de 400 nm avec un pic de concentration estimé à 160-180 nm. Cette profondeur est également appelée profondeur d'implantation moyenne ou  $R_p$ .

15 L'énergie d'implantation des dopants 2 peut être choisie pour que, dans les zones recouvertes par le masque 3, la profondeur d'implantation moyenne  $R_p$  soit située : (i) dans le masque 3 à proximité de l'interface avec la couche en matériau semi-conducteur 1b, ou (ii) dans la couche en matériau semi-conducteur 1b à proximité de l'interface avec le masque 3, ou (iii) en profondeur dans la couche en matériau semi-conducteur 1b.

20 25 Quelle que soit l'énergie d'implantation choisie, celle-ci est suffisante pour que les dopants 2 implantés apportent l'énergie nécessaire aux atomes de Si présents dans le masque 3 pour diffuser dans la couche en matériau semi-conducteur 1b.

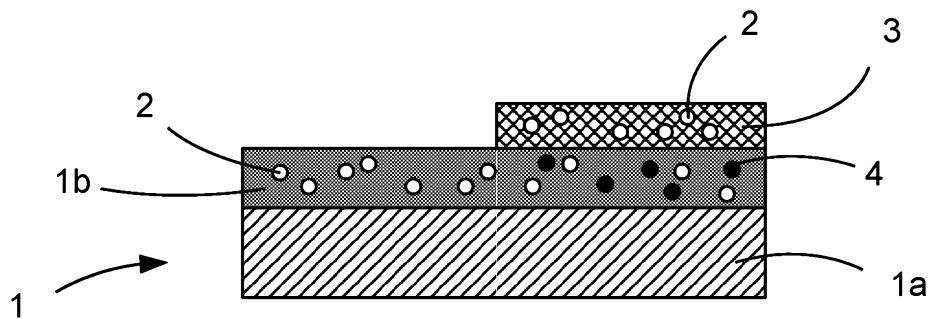

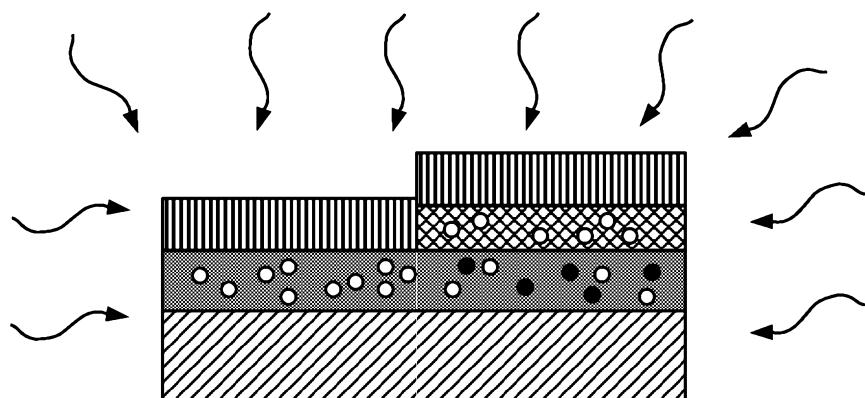

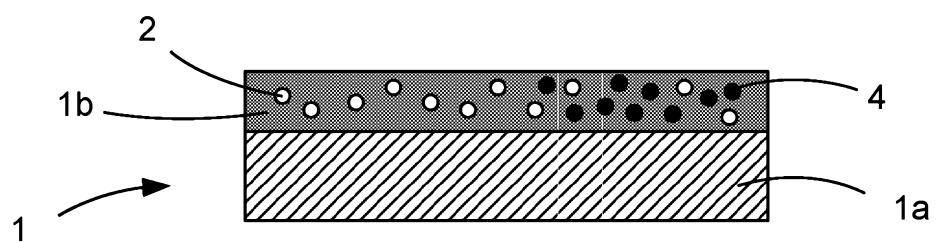

Lorsque les dopants 2 sont de type p, les zones qui ne sont pas recouvertes par le masque 3 sont directement dopées p, tandis que les dans les zones recouvertes du masque, les dopants de type p apportent l'énergie nécessaire aux atomes de Si pour diffuser. A l'issue de l'implantation ionique, la couche en matériau semi-conducteur 1b comprend des zones découvertes dotées d'impuretés dopantes 2 de type p, et des zones recouvertes dotées à la fois d'impuretés dopantes 2 de type p et d'impuretés dopantes supplémentaires 4 de type n, le dopage résiduel dans cette zone étant au final un dopage de type n (cf. figure 4).

10

Dans le cas de dopants 2 de type p, il peut être avantageux de choisir l'énergie d'implantation de sorte que la profondeur d'implantation moyenne soit située à l'interface entre le masque 3 et la couche en matériau semi-conducteur 1b, ou alors à proximité de cette interface, soit dans le masque 3, 15 soit dans la couche en matériau semi-conducteur 1b. Après implantation, les impuretés dopantes 2 de type p et les impuretés dopantes supplémentaires 4 de type n sont alors situées dans la zone dite active du semi-conducteur 1b, c'est-à-dire la profondeur utilisée par exemple pour réaliser des jonctions ou des transistors. La zone active du semi-conducteur 1b s'étend par exemple 20 jusqu'à 100 ou 300 nm de profondeur.

Effectuer une implantation de Si à travers le masque 3 présente l'intérêt de moins dégrader la surface de la couche en matériau semi-conducteur 1b en comparaison avec une implantation conventionnelle de Si.

25

Lorsque le maximum d'implantation est situé dans le masque 3 ou à l'interface entre le masque 3 et la couche semi-conductrice 1b, l'énergie apportée par les dopants 2 est suffisante pour permettre l'incorporation des atomes de Si du masque 3 jusqu'à la zone active du matériau semi-conducteur 1b. Lorsque le maximum d'implantation est situé en profondeur 30

dans la couche semi-conductrice 1b, l'énergie apportée par les dopants de type n permettent aux atomes de Si de diffuser dans la couche 1b dans une zone plus profonde.

- 5        Réaliser une implantation de dopants non électriquement actifs peut être utile pour fabriquer une couche en matériau semi-conducteur 1b qui soit dopée n dans les zones du semi-conducteur 1b recouvertes par le masque 3, et non dopée ailleurs. Comme pour les implantations de type n ou de type p, l'énergie d'implantation est choisie de sorte à permettre la diffusion d'atomes

10      de Si plus ou moins en profondeur dans la matrice semi-conductrice 1b. L'utilisation des dopants non électriquement actifs peut donner lieu à la réparation de lacunes qui sont soit créées par la diffusion des atomes de Si, soit déjà présentes dans la couche en matériau semi-conducteur 1b.

- 15      Selon un aspect de l'invention, il peut être avantageux de contrôler la température à laquelle l'implantation ionique est réalisée. De manière préférée, cette dernière peut être exécutée à une température comprise dans une plage allant de 15°C à 700°C, avantageusement entre 200°C et 600°C, et de manière préférée entre 450°C et 600°C. Pour cela, on peut avantageusement utiliser un système permettant de chauffer la face arrière

20      du support 1a, par exemple de type module à effet Peltier.

25      Le fait de réaliser un chauffage du substrat lors de l'étape d'implantation ionique permet à la fois une meilleure diffusion des dopants dans la couche en matériau semi-conducteur 1b, et une meilleure diffusion des atomes de Si depuis le masque 3 vers la couche en matériau semi-conducteur 1b.

30      Selon un mode de mise en œuvre particulier du procédé (non représenté), le masque 3 peut être retiré après l'étape d'implantation ionique, avant de réaliser un traitement thermique du substrat 1. Le retrait peut par exemple

être réalisé par gravure humide au moyen d'acide fluorhydrique (HF) si le masque est en  $\text{SiO}_2$  ou d'acide phosphorique ( $\text{H}_3\text{PO}_4$ ) si le masque est en  $\text{SiN}_x$  ou AlN.

5 Avantageusement, pour activer les impuretés dopantes 2 et les impuretés dopantes supplémentaires 4, le substrat 1 peut être recuit à une température élevée, par exemple supérieure à 1000°C. Or, au-delà d'une température de l'ordre de 850°C, la couche en matériau semi-conducteur 1b à base de GaN est fortement dégradée et une partie de l'azote s'évapore.

10

Il est donc avantageux de réaliser une étape de dépôt d'une couche de protection 5 après l'étape d'implantation des impuretés dopantes 2 et des impuretés dopantes supplémentaires 4, et avant de réaliser le traitement thermique. La couche de protection 5 a pour rôle de limiter fortement la dégradation de la surface de la couche semi-conductrice 1b. Cette étape du 15 procédé est représentée à la figure 5.

Le matériau de la couche de protection 5 peut être choisi parmi l'oxyde d'aluminium, le nitre d'aluminium, le nitre de silicium du type  $\text{Si}_x\text{N}_y$  ou 20 l'oxyde de silicium, ou les composés du type  $\text{HfSi}_x\text{O}_y$ . De préférence, le matériau de la couche de protection 5 en nitre d'aluminium.

Le dépôt peut par exemple être un dépôt chimique en phase vapeur aux organométalliques (« Metalorganic Chemical Vapor Deposition » ou 25 « MOCVD » en anglais) réalisé dans un équipement identique à celui ayant servi pour la croissance épitaxiale de la couche en matériau semi-conducteur 1b. Le dépôt peut également être réalisé par un dépôt chimique en phase vapeur à basse pression (« Low Pressure Chemical Vapor Deposition » ou « LPCVD » en anglais).

30

Déposer une couche de protection 5 en nitrate d'aluminium AlN peut être judicieux car les paramètres de maille de ce matériau sont très proches de ceux du matériau semi-conducteur à base de nitrate de gallium, ce qui permet d'augmenter l'adhérence de la couche de protection 5 sur le substrat

5 1. Il est également possible de remplacer l'AlN par de l'AlGaN, ou par un empilement de couches d'AlN et d'AlGaN. Dans ce cas, la couche d'AlGaN peut comporter jusqu'à 50% de Ga, avantageusement jusqu'à 20% de Ga, et préférentiellement moins de 5% de Ga.

10 Selon un mode de mise en œuvre préféré, la couche de protection 5 peut avoir une épaisseur comprise entre 1 et 200 nm, et plus précisément entre 1 et 100 nm. Cette épaisseur est suffisante pour créer une barrière efficace afin empêcher l'évaporation des molécules d'azote de la couche en matériau semi-conducteur 1b lors du traitement thermique.

15 15 L'étape de traitement thermique illustrée schématiquement à la figure 6 peut comprendre des recuits rapides (« Rapid Thermal Annealing » ou « RTA ») et (« Rapid Thermal Processing » ou « RTP ») en anglais) pour que le taux d'activation des impuretés dopantes 2 et des impuretés dopantes supplémentaires 4 soit élevé sans que la surface de la couche semi-conductrice 1b soit endommagée.

20 25 Des recuits standards (« Furnace Annealing ») en anglais peuvent également être réalisés pour permettre une diffusion efficace des impuretés dopantes 2 et des impuretés dopantes supplémentaires 4 dans la couche semi-conductrice 1b en position substitutionnelle.

30 Lors de l'étape de traitement thermique, il est donc possible de réaliser un recuit standard, un recuit rapide, ou toute combinaison de recuits rapides et standards selon le résultat que l'on souhaite obtenir. Au moins l'un des

recuits peut avantageusement être réalisé à une température supérieure à 1000°C pour obtenir un taux d'activation élevé des impuretés dopantes 2 et des impuretés dopantes supplémentaires 4.

5 A titre illustratif, un recuit standard à une température comprise entre 850 et 1250°C peut être réalisé pendant une durée allant de quelques minutes à quelques heures. Un recuit rapide peut également être effectué dans une gamme de température allant de 850 à 1250°C, voire même allant jusqu'à 1600°C si le support 1a est en saphire. Dans ce cas, la durée du recuit rapide est comprise entre quelques secondes et quelques minutes.

10 Avantageusement, le ou les recuits peuvent être réalisés sous une atmosphère contrôlée contenant un gaz choisi avantageusement parmi N<sub>2</sub>, Ar, He, NF<sub>3</sub>, O<sub>2</sub>, ou un mélange de N<sub>2</sub> / O<sub>2</sub>, N<sub>2</sub> / H<sub>2</sub>, Ar / H<sub>2</sub>.

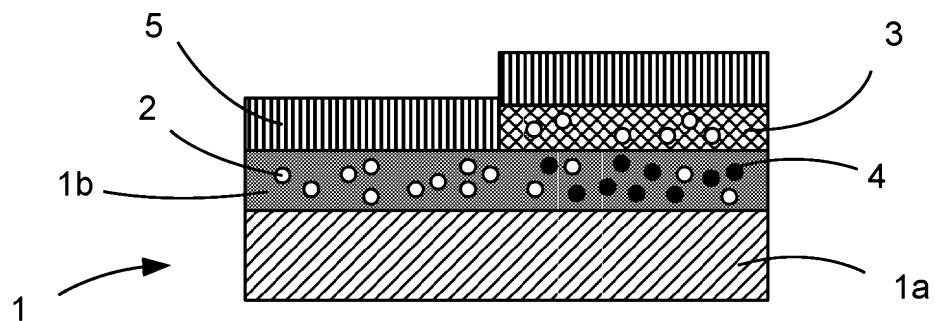

15 Les inventeurs ont observé que le traitement thermique permet d'augmenter la diffusion des dopants de type Si en direction de la couche en matériau semi-conducteur 1b. Par exemple, pour un recuit effectué à 1100°C, la concentration en impuretés dopantes 4 de type n est d'autant plus élevée que la durée du traitement thermique est longue.

20 Par ailleurs, le traitement thermique permet d'activer les impuretés dopantes 2 et les impuretés dopantes supplémentaires 4. Sachant que le rayon atomique des atomes de silicium est de 1.17 Å, que celui des atomes de gallium est de 1.26 Å, et que celui des atomes de magnésium est de 1.36 Å,

25 il est avancé que les atomes de silicium se placent plus facilement en position substitutionnelle dans la couche en matériau semi-conducteur 1b que les atomes de magnésium. Par conséquent, le taux d'activation des impuretés de type Si est plus élevé que le taux d'activation des impuretés de type Mg dans la zone recouverte par le masque 3 (cf. figure 7).

Les inventeurs ont observé que le taux d'activation des dopants de type n (impuretés de type Si) peut atteindre 100%, tandis que le taux d'activation des dopants de type p (impuretés de type Mg) est compris entre 5 à 60%.

5 Suite au traitement thermique, le masque 3 et la couche de protection 5 peuvent être retirés (cf. figures 8 et 9). On peut par exemple réaliser une gravure humide à l'aide d'acide phosphorique pour la couche de protection si cette dernière est en AlN ou SiN<sub>x</sub>, et à l'aide d'acide fluorhydrique pour enlever le masque 3 s'il est en SiO<sub>x</sub> ou SiN<sub>x</sub>. De manière alternative, la

10 couche de protection 5 peut être retirée par planarisation mécano-chimique (« Chemical-Mechanical Planarization » ou « CMP » en anglais), ou toute autre technique de gravure adaptée.

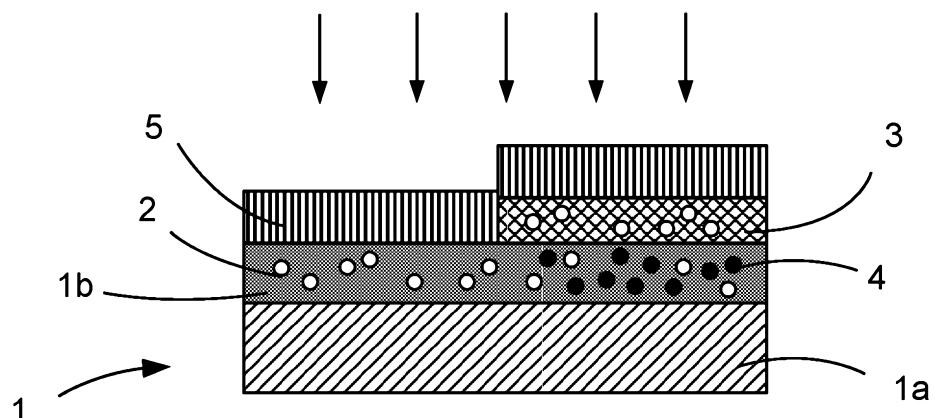

15 La mise en œuvre du procédé permet donc de réaliser un substrat 1 comportant une couche semi-conductrice 1b dopée p dans certaines zones et dopée n dans d'autres zones (cf. figure 10). Ce procédé peut donc être utilisé dans la fabrication de dispositifs nécessitant des jonctions p-n, telles que les diodes Schottchy, dans les transistors à effet de champ (« Metal semi-conductor Field Transistor » ou « MESFET » en anglais), ou les

20 transistors à haute mobilité électronique (« High Electron Mobility Transistor » ou « HEMT » en anglais).

25 Selon un mode de mise en œuvre alternatif non représenté, il est envisageable de retirer le masque 3 avant de déposer la couche de protection 5, avant de réaliser l'étape de traitement thermique. Toutefois cela limite la concentration en dopants de type n dans la couche en matériau semi-conducteur 1b, puisqu'une quantité importante d'ions Si<sup>+</sup> diffusent au cours du traitement thermique.

Selon un troisième mode de mise en œuvre du procédé, il peut être envisagé de déposer tout d'abord une couche de protection 5 ne recouvrant que certaines zones du substrat 1. On peut ensuite déposer le masque 3 sur d'autres zones du substrat recouvrant ou non la couche de protection 5. Les épaisseurs de la couche de protection 5 et du masque 3 sont judicieusement choisies de sorte à correctement protéger le substrat 1. Ainsi, lorsque l'étape d'implantation est réalisée, on assiste à :

- une implantation d'impuretés dopantes 2 dans les zones découvertes du substrat 1,

- une implantation d'impuretés dopantes 2 et d'impuretés dopantes supplémentaires 4 dans les zones du substrat 1 uniquement recouvertes par le masque 3,

- aucune implantation dans les zones du substrat 1 recouvertes par la couche de protection 5.

Ce mode de mise en œuvre du procédé permet avantageusement de réaliser des jonctions p-i-n de manière simple et efficace.

Enfin, dans un quatrième mode de mise en œuvre, il est possible de réaliser l'étape de traitement thermique sans avoir déposé de couche de protection 5 au préalable. Cela est envisageable si le traitement thermique est réalisé au moyen de recuits standards réalisés à des températures inférieures à 1000°C, c'est-à-dire des températures où la dégradation du substrat 1 est faible. Si le traitement thermique est réalisé au moyen de recuits rapides, il est possible de monter à une température de l'ordre de 1100°C pendant quelques secondes.

## Revendications

1. Procédé de dopage d'un semi-conducteur à base de GaN pour fabriquer une jonction p-n, comportant les étapes suivantes :

- 5        • prévoir un substrat (1) comprenant une couche en matériau semi-conducteur (1b) à base de GaN recouvert par un masque (3) à base de silicium,

- 10      • implanter des impuretés dopantes (2) dans le masque (3) de manière à transférer des impuretés dopantes supplémentaires (4) de type Si par diffusion depuis le masque (3) vers la couche en matériau semi-conducteur (1b) pour former une zone de type n adjacente à une zone de type p,

- 15      • réaliser un traitement thermique configuré pour activer les impuretés dopantes (2) et les impuretés dopantes supplémentaires (4).

15

2. Procédé de dopage d'un semi-conducteur selon la revendication 1, dans lequel le masque (3) couvre partiellement le substrat (1) de manière à définir une zone recouverte par le masque (3) et une zone découverte.

20      3. Procédé de dopage d'un semi-conducteur selon l'une quelconque des revendications 1 ou 2, dans lequel les impuretés dopantes (2) sont de type p.

25      4. Procédé de dopage d'un semi-conducteur selon l'une quelconque des revendications 1 à 3, dans lequel la profondeur d'implantation moyenne en impuretés dopantes (2) est disposée à une distance au moins égale à 300 nm de l'interface de sorte à incorporer des impuretés dopantes supplémentaires (4) dans la couche en matériau semi-conducteur (1b).

5. Procédé de dopage d'un semi-conducteur selon l'une quelconque des revendications 1 à 4, comprenant une étape de dépôt d'une couche de protection (5) réalisée avant l'étape de traitement thermique.

- 5 6. Procédé de dopage d'un semi-conducteur selon la revendication 5, dans lequel l'étape de dépôt de la couche de protection (5) est réalisée avant l'étape d'implantation des impuretés dopantes (2).

- 10 7. Procédé de dopage d'un semi-conducteur selon la revendication 6, dans lequel le dépôt de la couche de protection (5) est réalisé après l'étape d'implantation des impuretés dopantes (2) et des impuretés dopantes supplémentaires (4).

- 15 8. Procédé de dopage d'un semi-conducteur selon l'une quelconque des revendications 5 à 7, dans lequel le matériau de la couche de protection (5) est choisi parmi l'oxyde d'aluminium, le nitre d'aluminium, l'oxyde de silicium, ou le nitre de silicium du type  $\text{Si}_x\text{N}_y$ , le silicium amorphe et les composés du type  $\text{HfSi}_x\text{O}_y$ .

- 20 9. Procédé de dopage d'un semi-conducteur selon l'une quelconque des revendications 5 à 8, comportant une étape de retrait de la couche de protection (5) par gravure après le traitement thermique.

- 25 10. Procédé de dopage d'un semi-conducteur selon l'une quelconque des revendications 1 à 9, dans lequel l'étape d'implantation est réalisée à une température comprise entre 15 et 700°C, de préférence entre 450 et 600°C.

11. Procédé de dopage d'un semi-conducteur selon l'une quelconque des revendications 1 à 10, dans lequel l'étape de traitement thermique est une

combinaison d'au moins deux recuits de durées et de températures différentes.

12. Procédé de dopage d'un semi-conducteur selon la revendication 11, dans lequel au moins l'un des recuits est réalisé à une température supérieure à 1000°C.

5 13. Procédé de dopage d'un semi-conducteur selon l'une quelconque des revendications 1 à 12, dans lequel l'épaisseur du masque (3) est comprise 10 entre 2 et 400 nm.

14. Procédé de dopage d'un semi-conducteur selon l'une quelconque des revendications 1 à 13, dans lequel l'épaisseur de la couche en matériau semi-conducteur (1b) est comprise entre 5 nm et 10  $\mu$ m, préférentiellement 15 entre 500nm et 10 $\mu$ m, idéalement égale à 1 $\mu$ m.

1/4

Fig. 1

Fig. 2

Fig. 3

2/4

Fig. 4

Fig. 5

Fig. 6

3/4

Fig. 7

Fig. 8

Fig. 9

4/4

Fig. 10

# RAPPORT DE RECHERCHE

articles L.612-14, L.612-17 et R.612-53 à 69 du code de la propriété intellectuelle

## OBJET DU RAPPORT DE RECHERCHE

L'I.N.P.I. annexe à chaque brevet un "RAPPORT DE RECHERCHE" citant les éléments de l'état de la technique qui peuvent être pris en considération pour apprécier la brevetabilité de l'invention, au sens des articles L. 611-11 (nouveauté) et L. 611-14 (activité inventive) du code de la propriété intellectuelle. Ce rapport porte sur les revendications du brevet qui définissent l'objet de l'invention et délimitent l'étendue de la protection.

Après délivrance, l'I.N.P.I. peut, à la requête de toute personne intéressée, formuler un "AVIS DOCUMENTAIRE" sur la base des documents cités dans ce rapport de recherche et de tout autre document que le requérant souhaite voir prendre en considération.

## CONDITIONS D'ÉTABLISSEMENT DU PRÉSENT RAPPORT DE RECHERCHE

- Le demandeur a présenté des observations en réponse au rapport de recherche préliminaire.

- Le demandeur a maintenu les revendications.

- Le demandeur a modifié les revendications.

- Le demandeur a modifié la description pour en éliminer les éléments qui n'étaient plus en concordance avec les nouvelles revendications.

- Les tiers ont présenté des observations après publication du rapport de recherche préliminaire.

- Un rapport de recherche préliminaire complémentaire a été établi.

## DOCUMENTS CITÉS DANS LE PRÉSENT RAPPORT DE RECHERCHE

La répartition des documents entre les rubriques 1, 2 et 3 tient compte, le cas échéant, des revendications déposées en dernier lieu et/ou des observations présentées.

- Les documents énumérés à la rubrique 1 ci-après sont susceptibles d'être pris en considération pour apprécier la brevetabilité de l'invention.

- Les documents énumérés à la rubrique 2 ci-après illustrent l'arrière-plan technologique général.

- Les documents énumérés à la rubrique 3 ci-après ont été cités en cours de procédure, mais leur pertinence dépend de la validité des priorités revendiquées.

- Aucun document n'a été cité en cours de procédure.

**1. ELEMENTS DE L'ETAT DE LA TECHNIQUE SUSCEPTIBLES D'ETRE PRIS EN

CONSIDERATION POUR APPRECIER LA BREVETABILITE DE L'INVENTION**

KAZUKI NOMOTO ET AL: "Remarkable Reduction of On-Resistance by Ion Implantation in GaN/AlGaN/GaN HEMTs With Low Gate Leakage Current", IEEE ELECTRON DEVICE LETTERS, IEEE SERVICE CENTER, NEW YORK, NY, US, vol. 28, no. 11, 1 novembre 2007 (2007-11-01), pages 939-941, XP011196029, ISSN: 0741-3106, DOI: 10.1109/LED.2007.906930

"THREE-DIMENSIONAL SEMICONDUCTOR DEVICE STRUCTURES USING CHANNELLED ION IMPLANTATION AND ANNEALING TECHNIQUES", IBM TECHNICAL DISCLOSURE BULLETIN, INTERNATIONAL BUSINESS MACHINES CORP. (THORNEWOOD), US, vol. 32, no. 4A, 1 septembre 1989 (1989-09-01), page 358/359, XP000039924, ISSN: 0018-8689

"Thermal annealing characteristics of Si and Mg-implanted GaN thin films", APPLIED PHYSICS LETTERS, AMERICAN INSTITUTE OF PHYSICS, US, vol. 68, no. 19, 6 mai 1996 (1996-05-06), pages 2702-2704, XP012015207, ISSN: 0003-6951, DOI: 10.1063/1.116314

WHELAN S ET AL: "The dependence of the radiation damage formation on the substrate implant temperature in GaN during Mg ion implantation", JOURNAL OF APPLIED PHYSICS, AMERICAN INSTITUTE OF PHYSICS, US, vol. 98, no. 1, 6 juillet 2005 (2005-07-06), pages 13515-013515, XP012077687, ISSN: 0021-8979, DOI: 10.1063/1.1940142

**2. ELEMENTS DE L'ETAT DE LA TECHNIQUE ILLUSTRANT L'ARRIERE-PLAN

TECHNOLOGIQUE GENERAL**

"FORMING OF LOW RESISTANCE OHMIC CONTACTS TO III-V SEMICONDUCTORS", IBM TECHNICAL DISCLOSURE BULLETIN, INTERNATIONAL BUSINESS MACHINES CORP. (THORNEWOOD), US, vol. 32, no. 7, 1 décembre 1989 (1989-12-01), page 141/142, XP000078044, ISSN: 0018-8689

"BARRIER HEIGHT ENHANCEMENT BY RECOIL IMPLANTATION", RESEARCH DISCLOSURE, MASON PUBLICATIONS, HAMPSHIRE, GB, no. 292, 1 août 1988 (1988-08-01), page 932, XP000104853, ISSN: 0374-4353

**3. ELEMENTS DE L'ETAT DE LA TECHNIQUE DONT LA PERTINENCE DEPEND

DE LA VALIDITE DES PRIORITES**

NEANT