【公報種別】特許法第17条の2の規定による補正の掲載

【部門区分】第7部門第3区分

【発行日】平成30年10月4日(2018.10.4)

【公開番号】特開2017-76865(P2017-76865A)

【公開日】平成29年4月20日(2017.4.20)

【年通号数】公開・登録公報2017-016

【出願番号】特願2015-202913(P2015-202913)

【国際特許分類】

H 04 N 5/378 (2011.01)

H 04 N 5/374 (2011.01)

H 01 L 27/146 (2006.01)

【F I】

H 04 N 5/335 7 8 0

H 04 N 5/335 7 4 0

H 01 L 27/14 A

【手続補正書】

【提出日】平成30年8月23日(2018.8.23)

【手続補正1】

【補正対象書類名】明細書

【補正対象項目名】0011

【補正方法】変更

【補正の内容】

【0011】

(列回路の構成)

次に、列回路20の構成について説明する。本実施形態において列回路20は画素部の垂直出力線ごとに設けられる。個々の列回路20は、ランプ発生器30および計測カウンタ40とともに、画素信号をA/D変換する回路を形成する。

【手続補正2】

【補正対象書類名】明細書

【補正対象項目名】0039

【補正方法】変更

【補正の内容】

【0039】

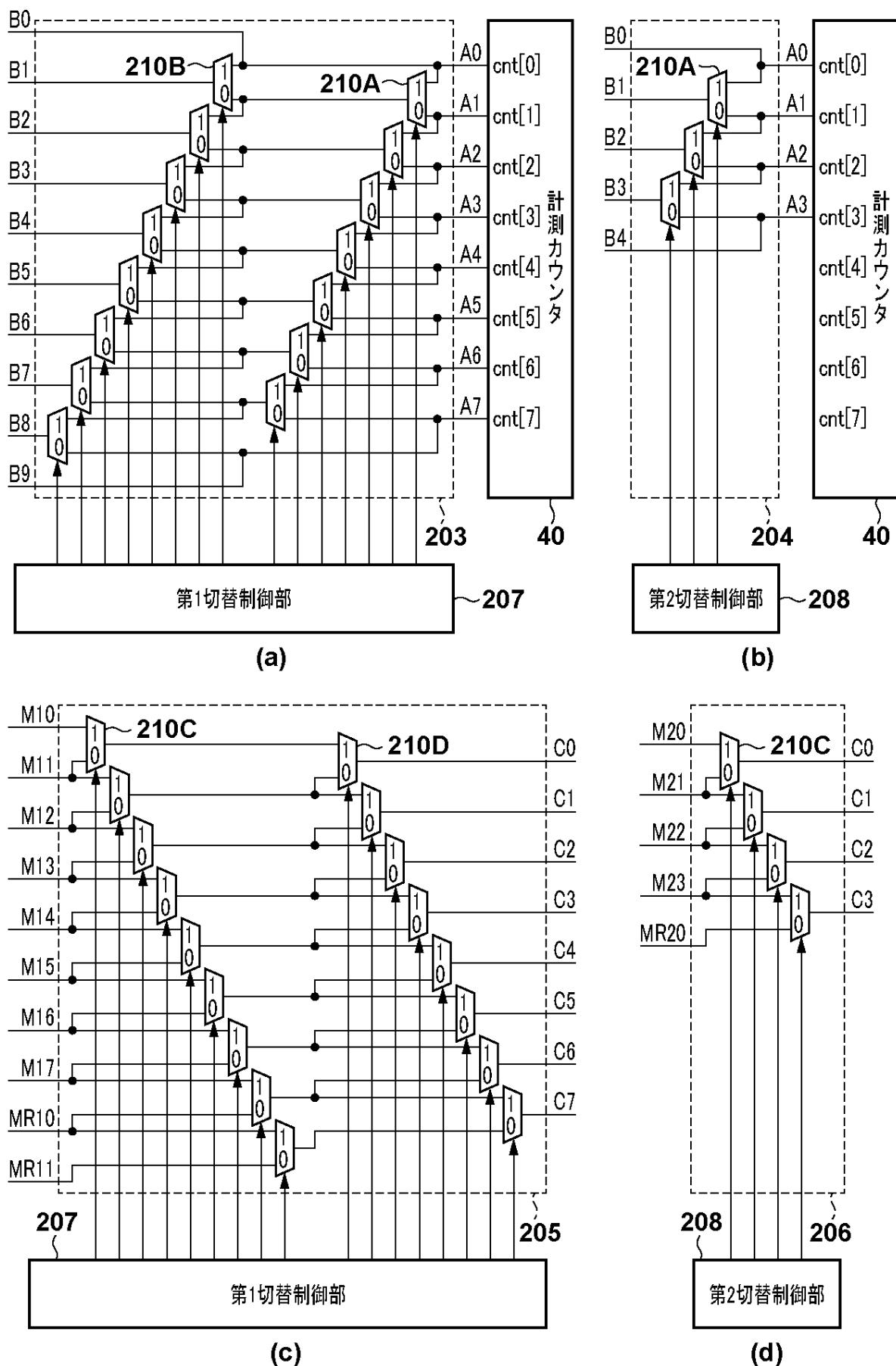

図4(b)は、第2ビット切替部204の回路構成を示す。各セレクタ210Aには第2切替制御部208から制御信号が入力され、計測カウンタ40が出力するOビット(ここではO=4)の信号A0~A3を、Pビット(ここではP=5)の出力B0~B4のうち、Oビット分に割り当てる。

【手続補正3】

【補正対象書類名】明細書

【補正対象項目名】0055

【補正方法】変更

【補正の内容】

【0055】

(変形例)

次に、図6を参照して、本実施形態の変形例について説明する。本変形例は、第1~第4ビット切替部203~206を列回路20ごとに設けずに、複数の列回路20aで共有する点が異なる。第1~第4ビット切替部205~208を共有することで、列回路20aの実装面積もしくは回路集積度を低減することができ、コストダウン、撮像素子の小型

化、もしくは故障発生の抑制を実現することができる。

【手続補正4】

【補正対象書類名】明細書

【補正対象項目名】0063

【補正方法】変更

【補正の内容】

【0063】

本実施形態では、第1実施形態の構成より、比較器200の数が増え、メモリ選択制御部50が不要になる点を除き、第1実施形態と同様の効果が得られる。

【手続補正5】

【補正対象書類名】明細書

【補正対象項目名】0066

【補正方法】変更

【補正の内容】

【0066】

画素101dは、第1のフォトダイオードPD1、第2のフォトダイオードPD2を備え、第1および第2のフォトダイオードPD1、PD2はオンチップマイクロレンズMLを共有している。また、第1および第2のフォトダイオードPD1、PD2の光電変換領域の大きさは、図3(a)のフォトダイオードPDの光電変換領域の大きさの半分であるとする。第1のフォトダイオードPD1と第2のフォトダイオードPD2とは、射出瞳における異なる領域(部分瞳)からの光が入射し、画素101dは瞳分割機能を有する。したがって、焦点検出領域内の画素における、第1のフォトダイオードPD1の出力から得られるA像信号と、第2のフォトダイオードPD2の出力から得られるB像信号とを用いて、位相差検出方式の焦点検出が可能である。

【手続補正6】

【補正対象書類名】図面

【補正対象項目名】図4

【補正方法】変更

【補正の内容】

【図4】