(19) 日本国特許庁(JP)

## (12) 特許公報(B2)

(11) 特許番号

特許第5588949号

(P5588949)

(45) 発行日 平成26年9月10日(2014.9.10)

(24) 登録日 平成26年8月1日(2014.8.1)

(51) Int.Cl.

F 1

|             |              |                  |

|-------------|--------------|------------------|

| <b>A61B</b> | <b>1/04</b>  | <b>(2006.01)</b> |

| <b>G02B</b> | <b>23/24</b> | <b>(2006.01)</b> |

| <b>H04N</b> | <b>7/18</b>  | <b>(2006.01)</b> |

|        |       |         |

|--------|-------|---------|

| A 61 B | 1/04  | 3 6 2 J |

| A 61 B | 1/04  | 3 7 O   |

| G 02 B | 23/24 | B       |

| H 04 N | 7/18  | M       |

請求項の数 15 (全 26 頁)

(21) 出願番号

特願2011-218563 (P2011-218563)

(22) 出願日

平成23年9月30日(2011.9.30)

(65) 公開番号

特開2013-78378 (P2013-78378A)

(43) 公開日

平成25年5月2日(2013.5.2)

審査請求日

平成25年1月25日(2013.1.25)

(73) 特許権者 306037311

富士フィルム株式会社

東京都港区西麻布2丁目26番30号

(74) 代理人 100083116

弁理士 松浦 憲三

(72) 発明者 小谷 学

神奈川県足柄上郡開成町宮台798番地

富士フィルム株式会社内

審査官 原 俊文

最終頁に続く

(54) 【発明の名称】 内視鏡システム及び内視鏡の外部制御装置

## (57) 【特許請求の範囲】

## 【請求項 1】

内視鏡の挿入部先端に搭載された固体撮像素子を有する撮像装置と、

内視鏡に対する外部装置として前記撮像装置に信号線により接続され、前記撮像装置を制御する外部制御装置と、

前記撮像装置において前記固体撮像素子により撮像信号として順次出力された画素データを1画素ごとに順次符号化して1ワードごとのワードデータに順次変換する符号化手段と、

前記撮像装置において前記符号化手段によりワードデータに順次変換された撮像信号をパラレル信号からシリアル信号へと変換して前記信号線を通じて前記外部制御装置へと送信する撮像信号送信手段と、

前記撮像装置において前記外部制御装置に送信する撮像信号にワード同期のためのワード同期データを所定間隔で挿入する同期データ挿入手段と、

前記外部制御装置において前記撮像信号送信手段により送信された撮像信号を受信し、該撮像信号として順次受信したワードデータを1ワードごとにシリアル信号からパラレル信号へと順次変換する撮像信号受信手段と、

前記外部制御装置において前記撮像信号受信手段によりパラレル信号に順次変換されたワードデータを1ワードごとに順次復号化して前記符号化手段による符号化を行う前の1画素ごとの画素データに順次変換する復号化手段と、

前記外部制御装置において前記撮像信号受信手段により受信した撮像信号から前記ワード同期データを所定間隔で挿入する同期データ挿入手段と、

10

20

ド同期データを検出し、該検出したワード同期データに基づいて前記撮像信号受信手段によるパラレル信号への変換又は前記復号化手段による画素データへの変換において1ワードごとのワードデータとして区切るタイミングを調整してワード同期させる同期処理手段と、

前記復号化手段により順次変換された画素データを記憶する記憶手段と、

前記復号化手段において復号化の失敗を示す復号エラーの発生を検出する復号エラー検出手段と、

前記復号エラー検出手段により復号エラーの発生が検出された場合に、該復号エラーの発生が生じたときの画素をエラー画素として該エラー画素の画素データが記憶されるべき前記記憶手段のメモリ領域に、該エラー画素に対して周辺部となる1又は複数の画素の画素データに基づいて生成した補間データを記憶させて前記エラー画素の画素データを補間する補間手段と、

を備えた内視鏡システム。

#### 【請求項2】

前記記憶手段は、伝送単位であるフレーム単位で前記復号化手段により順次変換されて出力される複数画素分の画素データを1フレーム分記憶する1又は複数のバッファメモリにより構成されるものとする請求項1に記載の内視鏡システム。

#### 【請求項3】

前記補間手段は、前記エラー画素に対して周辺部となる1又は複数の画素の画素データであって前記補間データを生成する画素データとして、前記エラー画素に対して同一画像上の所定距離範囲以内に位置する画素の画素データと、前記エラー画素が得られた時間に對して所定時間範囲以内の時間に得られた画像上の前記エラー画素と同一位置の画素の画素データのうちのいずれか1つ又は複数の画素データを使用するものとする請求項1又は2に記載の内視鏡システム。

#### 【請求項4】

前記エラー画素が得られた時間に對して所定時間範囲以内の時間に得られた画像上の前記エラー画素と同一位置の画素の画素データは、該エラー画素に対して1画面分前又は1画面分後における同一位置の画素の正常な画素データからなる請求項3に記載の内視鏡システム。

#### 【請求項5】

前記符号化手段は、8ビットの画素データを8B10B方式により符号化して10ビットを1ワードとするワードデータに変換する8B10Bエンコーダであり、

前記復号化手段は、前記符号化手段により符号化されたワードデータを8B10B方式により1ワードごとに復号化して前記8B10Bエンコーダにより符号化される前の8ビットの画素データに変換する8B10Bデコーダであるものとする請求項1～4のうちのいずれか1項に記載の内視鏡システム。

#### 【請求項6】

前記復号エラー検出手段は、前記復号エラーとして、テーブルエラー及びディスパリティーエラーの発生を検出するものとする請求項5に記載の内視鏡システム。

#### 【請求項7】

前記撮像信号受信手段は、前記撮像信号送信手段により撮像信号として送信されたシリアル信号からクロック信号を抽出すると共に、該クロック信号により撮像信号をリタイミングするクロックデータリカバリ回路を含むものとする請求項1～6のうちのいずれか1項に記載の内視鏡システム。

#### 【請求項8】

前記撮像装置の固体撮像素子は、CMOS型の固体撮像素子であるものとする請求項1～7のうちのいずれか1項に記載の内視鏡システム。

#### 【請求項9】

内視鏡の撮像装置を制御すると共に該撮像装置からシリアル信号として伝送される撮像信号を受信する外部制御装置であって、前記撮像信号として前記撮像装置から順次出力さ

10

20

30

40

50

れた画素データを1画素ごとに順次符号化した1ワードごとのワードデータで、かつ、ワード同期のためのワード同期データが所定間隔で挿入されたワードデータを順次受信する内視鏡の外部制御装置であって、

前記撮像装置により送信された撮像信号を受信し、該撮像信号として順次受信したワードデータを1ワードごとにシリアル信号からパラレル信号へと順次変換する撮像信号受信手段と、

前記撮像信号受信手段によりパラレル信号に順次変換されたワードデータを1ワードごとに順次復号化して前記符号化を行う前の1画素ごとの画素データに順次変換する復号化手段と、

前記撮像装置より受信した撮像信号から前記ワード同期データを検出し、該検出したワード同期データに基づいて前記撮像信号受信手段によるパラレル信号への変換又は前記復号化手段による画素データへの変換において1ワードごとのワードデータとして区切るタイミングを調整してワード同期させる同期処理手段と、 10

前記復号化手段により順次変換された画素データを記憶する記憶手段と、

前記復号化手段において復号化の失敗を示す復号エラーの発生を検出する復号エラー検出手段と、

前記復号エラー検出手段により復号エラーの発生が検出された場合に、該復号エラーの発生が生じたときの画素をエラー画素として該エラー画素の画素データが記憶されるべき前記記憶手段のメモリ領域に、該エラー画素に対して周辺部となる1又は複数の画素の画素データに基づいて生成した補間データを記憶させて、前記エラー画素の画素データを補間する補間手段と、

を備えた内視鏡の外部制御装置。

#### 【請求項10】

前記記憶手段は、伝送単位であるフレーム単位で前記復号化手段により順次変換されて出力される複数画素分の画素データを1フレーム分記憶する1又は複数のバッファメモリにより構成されるものとする請求項9に記載の内視鏡の外部制御装置。

#### 【請求項11】

前記補間手段は、前記エラー画素に対して周辺部となる1又は複数の画素の画素データであって前記補間データを生成する画素データとして、前記エラー画素に対して同一画像上の所定距離範囲以内に位置する画素の画素データと、前記エラー画素が得られた時間に30対して所定時間範囲以内の時間に得られた画像上の前記エラー画素と同一位置の画素の画素データのうちのいずれか1つ又は複数の画素データを使用するものとする請求項9又は10に記載の内視鏡の外部制御装置。

#### 【請求項12】

前記エラー画素が得られた時間に対して所定時間範囲以内の時間に得られた画像上の前記エラー画素と同一位置の画素の画素データは、該エラー画素に対して1画面分前又は1画面分後における同一位置の画素の正常な画素データからなる請求項11に記載の内視鏡の外部制御装置。

#### 【請求項13】

前記撮像装置から撮像信号として伝送されるワードデータは、8ビットの画素データを8B10B方式により符号化した10ビットを1ワードとするワードデータであり、

前記復号化手段は、前記符号化されたワードデータを8B10B方式により1ワードごとに復号化して符号化される前の8ビットの画素データに変換する8B10Bデコーダであるものとする請求項9～12のうちのいずれか1項に記載の内視鏡の外部制御装置。

#### 【請求項14】

前記復号エラー検出手段は、前記復号エラーとして、テーブルエラー及びディスパリティーエラーの発生を検出するものとする請求項13に記載の内視鏡の外部制御装置。

#### 【請求項15】

前記撮像信号受信手段は、前記撮像装置より撮像信号として送信されたシリアル信号からクロック信号を抽出すると共に、該クロック信号により撮像信号をリタイミングするク 50

ロックデータリカバリ回路を含むものとする請求項 9 ~ 14 のうちのいずれか 1 項に記載の内視鏡の外部制御装置。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は内視鏡システム及び内視鏡の外部制御装置に係り、特に内視鏡の挿入部先端に搭載された固体撮像素子からの撮像信号をプロセッサ装置にシリアル伝送する内視鏡システム及び内視鏡の外部制御装置に関する。

【背景技術】

【0002】

内視鏡システムは、一般に体腔内に挿入される挿入部と操作者が把持して各種操作を行う手元操作部とを有する内視鏡と、内視鏡から延設されたユニバーサルケーブルを介して接続されるプロセッサ装置（外部制御装置）とを備えて構成されている。内視鏡の挿入部の先端には撮像装置が搭載されており、その撮像装置により撮像された観察像が撮像信号として内視鏡の挿入部、手元操作部、及びユニバーサルケーブルの内部を挿通する信号線を通じてプロセッサ装置に伝送され、プロセッサ装置において各種画像処理が施されてモニタにその観察像が表示されるようになっている。

【0003】

特許文献 1、2 では、内視鏡の撮像装置からプロセッサ装置へと撮像信号を伝送する方法としてシリアル伝送を用いることが提案されている。これによれば、撮像信号をアナログ信号で伝送する場合と比較して、ノイズの影響を受け難くして伝送特性の向上を図ることができ、また、撮像信号をパラレル信号で伝送する場合と比較して、信号線の本数の削減（即ち、内視鏡の挿入部の細径化）や伝送速度の高速化（即ち、撮影画像の高画質化）を図ることができる。

【0004】

また、特許文献 2 において、上記のような内視鏡システムでは、内視鏡の撮像装置からプロセッサ装置までの撮像信号の伝送距離が長くなるため、高速シリアル伝送技術の適用により撮像信号と共に撮像信号に同期したクロック信号も固体撮像素子からプロセッサ装置に伝送するものとすると、撮像信号とクロック信号の各々の信号線に付随する寄生容量や配線抵抗の差によりタイミングスキーが生じて撮像信号の伝送が不安定化し、その結果、プロセッサ装置においてデータの誤検出が生じて画質の劣化が生じるという不具合が提示されている。そして、特許文献 2 では、撮像装置において撮像信号を 8 B 10 B エンコーダで符号化したシリアル信号に変換し、Low 又は High 状態の期間が 3 クロック以下となるようにしてクロック信号を撮像信号に埋め込み、プロセッサ装置においてクロックデータリカバリ回路（CDR 回路）により撮像信号からクロック信号を抽出することで、タイミングスキーの問題を解消して撮像信号のシリアル伝送の高速化かつ安定化を図ることが提案されている。

【先行技術文献】

【特許文献】

【0005】

【特許文献 1】特開 2002 - 065601 号公報

【特許文献 2】特開 2009 - 201540 号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

ところで、内視鏡の鉗子チャンネルに高周波処置具を挿通して使用する場合や、アルゴン・プラズマ・コアギュレーション（APC）として知られるように鉗子チャンネルを挿通させた処置具からアルゴンガスを患部に吹き付けながら高周波を加える場合に、強いノイズが発生する。そのため、撮像信号の伝送中にビット挿入やビット欠落のようなデータの破損が発生し、撮像信号を受信したプロセッサ装置において撮像信号により得られる画

10

20

30

40

50

像（映像）に乱れが生じ、モニタにその画像を表示した際の視認性が悪くなるという問題がある。

#### 【0007】

本発明は、このような事情に鑑みてなされたもので、内視鏡の撮像装置から外部制御装置（プロセッサ装置）に撮像信号をシリアル伝送する内視鏡システムにおいて、撮像信号の伝送中にノイズ等によりデータ破損が生じた場合であっても画像の乱れを軽減することができる内視鏡システム及び内視鏡の外部制御装置を提供することを目的とする。

#### 【課題を解決するための手段】

#### 【0008】

前記目的を達成するために、本発明の内視鏡システムは、内視鏡の挿入部先端に搭載された固体撮像素子を有する撮像装置と、内視鏡に対する外部装置として前記撮像装置に信号線により接続され、前記撮像装置を制御する外部制御装置と、前記撮像装置において前記固体撮像素子により撮像信号として順次出力された画素データを1画素ごとに順次符号化して1ワードごとのワードデータに順次変換する符号化手段と、前記撮像装置において前記符号化手段によりワードデータに順次変換された撮像信号をパラレル信号からシリアル信号へと変換して前記信号線を通じて前記外部制御装置へと送信する撮像信号送信手段と、前記撮像装置において前記外部制御装置に送信する撮像信号にワード同期のためのワード同期データを所定間隔で挿入する同期データ挿入手段と、前記外部制御装置において前記撮像信号送信手段により送信された撮像信号を受信し、該撮像信号として順次受信したワードデータを1ワードごとにシリアル信号からパラレル信号へと順次変換する撮像信号受信手段と、前記外部制御装置において前記撮像信号受信手段によりパラレル信号に順次変換されたワードデータを1ワードごとに順次復号化して前記符号化手段による符号化を行う前の1画素ごとの画素データに順次変換する復号化手段と、前記外部制御装置において前記撮像信号受信手段により受信した撮像信号から前記ワード同期データを検出し、該検出したワード同期データに基づいて前記撮像信号受信手段によるパラレル信号への変換又は前記復号化手段による画素データへの変換において1ワードごとのワードデータとして区切るタイミングを調整してワード同期させる同期処理手段と、前記復号化手段により順次変換された画素データを記憶する記憶手段と、前記復号化手段において復号化の失敗を示す復号エラーの発生を検出する復号エラー検出手段と、前記復号エラー検出手段により復号エラーの発生が検出された場合に、該復号エラーの発生が生じたときの画素をエラー画素として該エラー画素の画素データが記憶されるべき前記記憶手段のメモリ領域に、該エラー画素に対して周辺部となる1又は複数の画素の画素データに基づいて生成した補間データを記憶させて前記エラー画素の画素データを補間する補間手段と、を備えている。

#### 【0009】

本発明によれば、撮像装置から外部制御装置への撮像信号のシリアル伝送中にノイズ等によってデータ破損（ビット挿入やビット欠落）が生じた場合に、外部制御装置における復号化手段での復号エラーの発生によって正常な画素データが得られないことになるが、その復号エラーが発生したときの画素データが周辺部の画素の画素データ（破損していない画素データ）により補間される。したがって、撮像信号の伝送中にデータ破損が生じた場合であっても撮像信号により得られる画像（映像）の乱れが軽減される。

#### 【0010】

本発明では、前記記憶手段は、伝送単位であるフレーム単位で前記復号化手段により順次変換されて出力される複数画素分の画素データを1フレーム分記憶する1又は複数のバッファメモリにより構成されるものとすることができる。

#### 【0011】

本発明では、前記補間手段は、前記エラー画素に対して周辺部となる1又は複数の画素の画素データであって前記補間データを生成する画素データとして、前記エラー画素に対して同一画像上の所定距離範囲以内に位置する画素の画素データと、前記エラー画素が得られた時間に対して所定時間範囲以内の時間に得られた画像上の前記エラー画素と同一位

10

20

30

40

50

置の画素の画素データのうちのいずれか1つ又は複数の画素データを使用するものとすることができる。

本発明では、前記エラー画素が得られた時間に対して所定時間範囲以内の時間に得られた画像上の前記エラー画素と同一位置の画素の画素データは、該エラー画素に対して1画面分前又は1画面分後における同一位置の画素の正常な画素データからなるものとすることができる。

#### 【0012】

本発明では、前記符号化手段は、8ビットの画素データを8B10B方式により符号化して10ビットを1ワードとするワードデータに変換する8B10Bエンコーダであり、前記復号化手段は、前記符号化手段により符号化されたワードデータを8B10B方式により1ワードごとに復号化して前記8B10Bエンコーダにより符号化される前の8ビットの画素データに変換する8B10Bデコーダであるものとすることができます。10

#### 【0013】

本発明では、前記撮像信号受信手段は、前記撮像信号送信手段により撮像信号として送信されたシリアル信号からクロック信号を抽出すると共に、該クロック信号により撮像信号をリタイミングするクロックデータリカバリ回路を含むものとすることができます。

本発明では、前記復号エラー検出手段は、前記復号エラーとして、テーブルエラー及びディスパリティーエラーの発生を検出するものとすることができます。

#### 【0015】

本発明では、前記撮像装置の固体撮像素子は、CMOS型との固体撮像素子であるものとすることができます。20

#### 【0016】

また、本発明に係る内視鏡の外部制御装置は、内視鏡の撮像装置を制御すると共に該撮像装置からシリアル信号として伝送される撮像信号を受信する外部制御装置であって、前記撮像信号として前記撮像装置から順次出力された画素データを1画素ごとに順次符号化した1ワードごとのワードデータで、かつ、ワード同期のためのワード同期データが所定間隔で挿入されたワードデータを順次受信する内視鏡の外部制御装置であって、前記撮像装置により送信された撮像信号を受信し、該撮像信号として順次受信したワードデータを1ワードごとにシリアル信号からパラレル信号へと順次変換する撮像信号受信手段と、前記撮像信号受信手段によりパラレル信号に順次変換されたワードデータを1ワードごとに順次復号化して前記符号化を行う前の1画素ごとの画素データに順次変換する復号化手段と、前記撮像装置より受信した撮像信号から前記ワード同期データを検出し、該検出したワード同期データに基づいて前記撮像信号受信手段によるパラレル信号への変換又は前記復号化手段による画素データへの変換において1ワードごとのワードデータとして区切るタイミングを調整してワード同期させる同期処理手段と、前記復号化手段により順次変換された画素データを記憶する記憶手段と、前記復号化手段において復号化の失敗を示す復号エラーの発生を検出する復号エラー検出手段と、前記復号エラー検出手段により復号エラーの発生が検出された場合に、該復号エラーの発生が生じたときの画素をエラー画素として該エラー画素の画素データが記憶されるべき前記記憶手段のメモリ領域に、該エラー画素に対して周辺部となる1又は複数の画素の画素データに基づいて生成した補間データを記憶させて、前記エラー画素の画素データを補間する補間手段と、を備えている。30

#### 【0017】

本発明によれば、撮像装置から外部制御装置への撮像信号のシリアル伝送中にノイズ等によってデータ破損（ビット挿入やビット欠落）が生じた場合に、外部制御装置における復号化手段での復号エラーの発生によって正常な画素データが得られないことになるが、その復号エラーが発生したときの画素データが周辺部の画素の画素データ（破損していない画素データ）により補間される。したがって、撮像信号の伝送中にデータ破損が生じた場合であっても撮像信号により得られる画像（映像）の乱れが軽減される。

#### 【0018】

本発明では、前記記憶手段は、伝送単位であるフレーム単位で前記復号化手段により順

50

次変換されて出力される複数画素分の画素データを1フレーム分記憶する1又は複数のバッファメモリにより構成されるものとすることができます。

#### 【0019】

本発明では、前記補間手段は、前記エラー画素に対して周辺部となる1又は複数の画素の画素データであって前記補間データを生成する画素データとして、前記エラー画素に対して同一画像上の所定距離範囲以内に位置する画素の画素データと、前記エラー画素が得られた時間に対して所定時間範囲以内の時間に得られた画像上の前記エラー画素と同一位置の画素の画素データのうちのいずれか1つ又は複数の画素データを使用するものとすることができる。

本発明では、前記エラー画素が得られた時間に対して所定時間範囲以内の時間に得られた画像上の前記エラー画素と同一位置の画素の画素データは、該エラー画素に対して1画面分前又は1画面分後における同一位置の画素の正常な画素データからなるものとすることができる。

#### 【0020】

本発明では、前記撮像装置から撮像信号として伝送されるワードデータは、8ビットの画素データを8B10B方式により符号化した10ビットを1ワードとするワードデータであり、前記復号化手段は、前記符号化されたワードデータを8B10B方式により1ワードごとに復号化して符号化される前の8ビットの画素データに変換する8B10Bデコーダであるものとすることができる。

#### 【0021】

本発明では、前記復号エラー検出手段は、前記復号エラーとして、テーブルエラー及びディスパリティーエラーの発生を検出するものとすることができる。

#### 【0022】

本発明では、前記撮像信号受信手段は、前記撮像装置より撮像信号として送信されたシリアル信号からクロック信号を抽出すると共に、該クロック信号により撮像信号をリタイミングするクロックデータリカバリ回路を含むものとすることができる。

#### 【発明の効果】

#### 【0024】

本発明の内視鏡システムによれば、内視鏡の撮像装置から外部制御装置（プロセッサ装置）に撮像信号をシリアル伝送する内視鏡システムにおいて、撮像信号の伝送中にノイズ等によりデータ破損が生じた場合であっても画像の乱れを軽減することができる。

#### 【図面の簡単な説明】

#### 【0025】

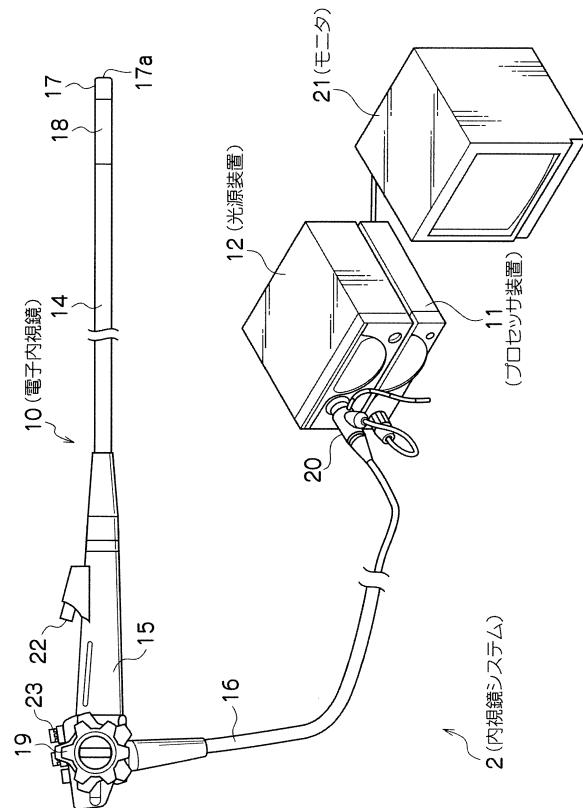

【図1】内視鏡システムの概略構成を示す全体図

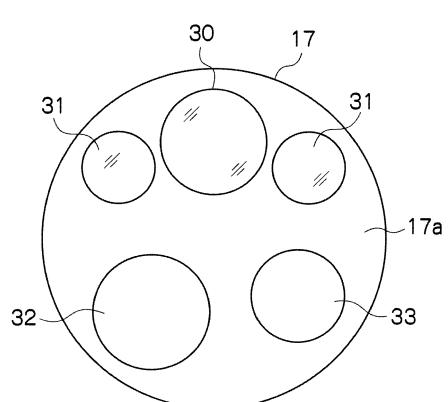

【図2】電子内視鏡の先端部の前面を示す図

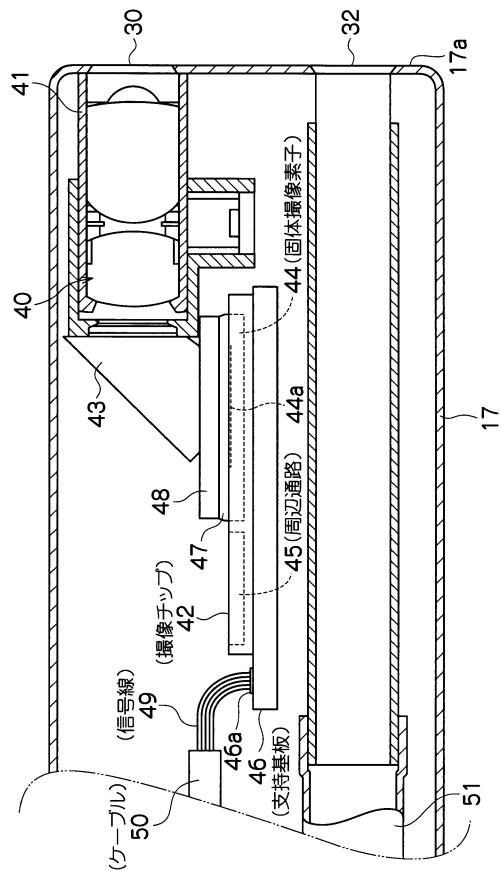

【図3】電子内視鏡の先端部の構成を示す拡大部分断面図

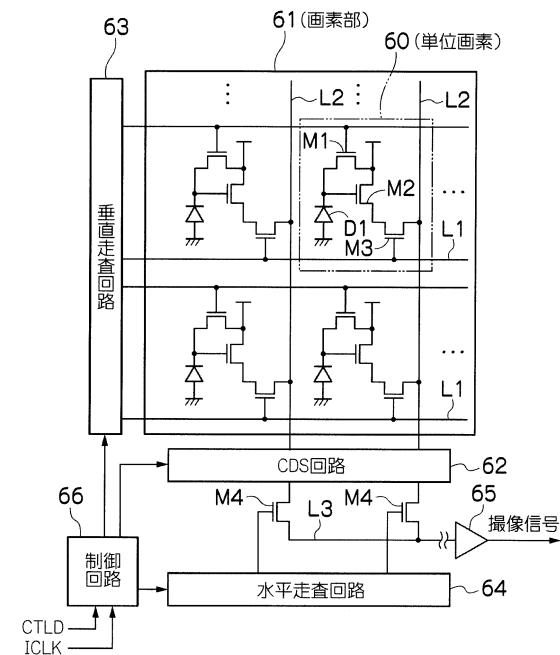

【図4】固体撮像素子の構成を示す回路図

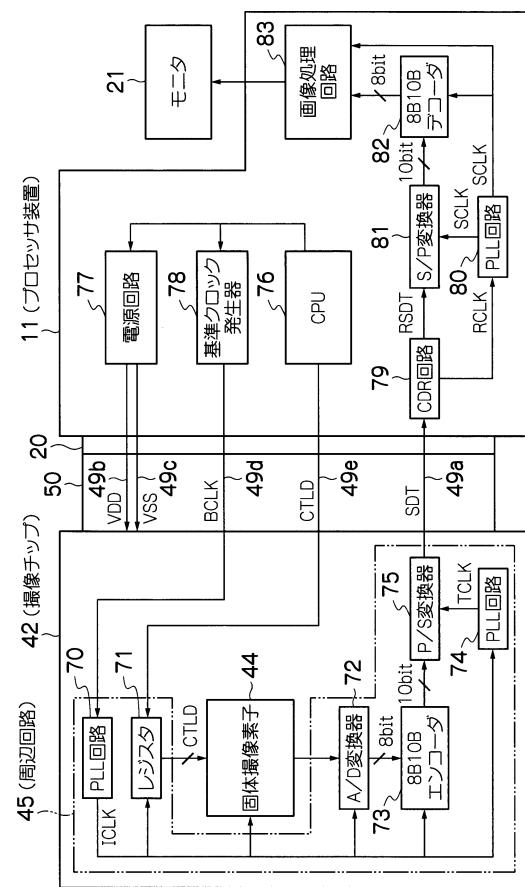

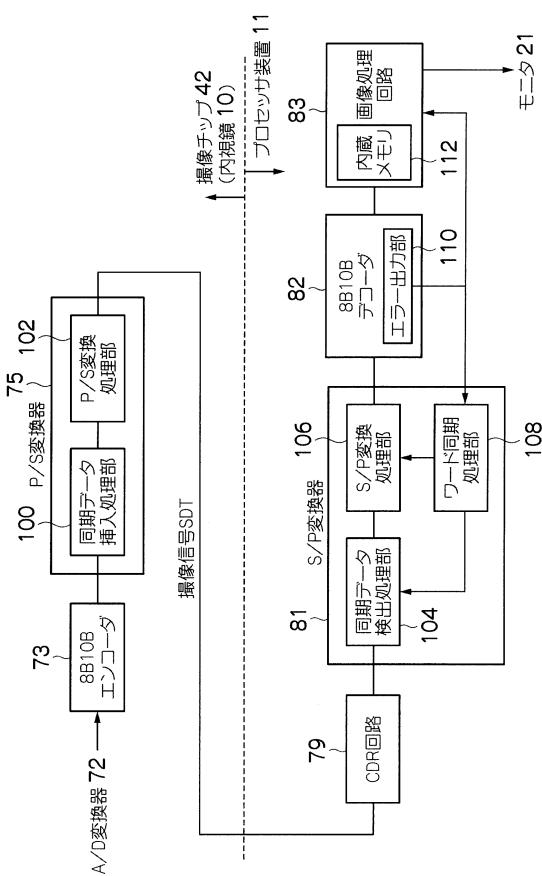

【図5】撮像チップ及びプロセッサ装置の構成を示すブロック図

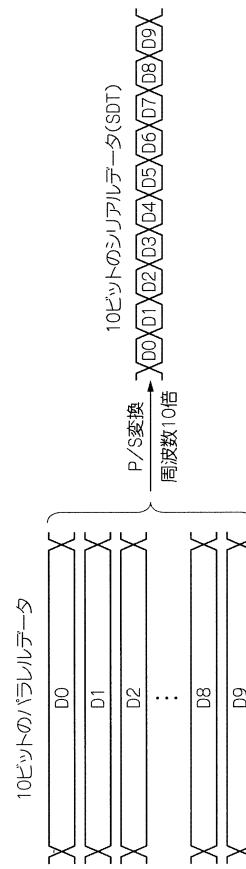

【図6】画素データのパラレル／シリアル変換を説明する説明図

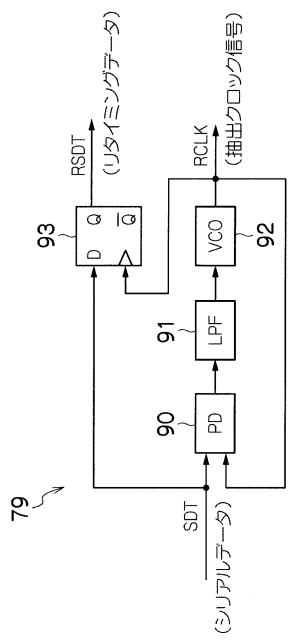

【図7】CDR回路の構成を示すブロック図

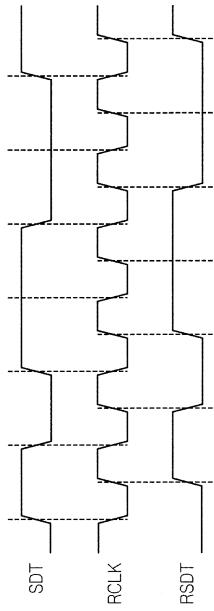

【図8】CDR回路の動作を説明するタイミングチャート

【図9】撮像チップからプロセッサ装置へのデータ伝送に関する伝送系回路の構成を抽出して示したブロック図

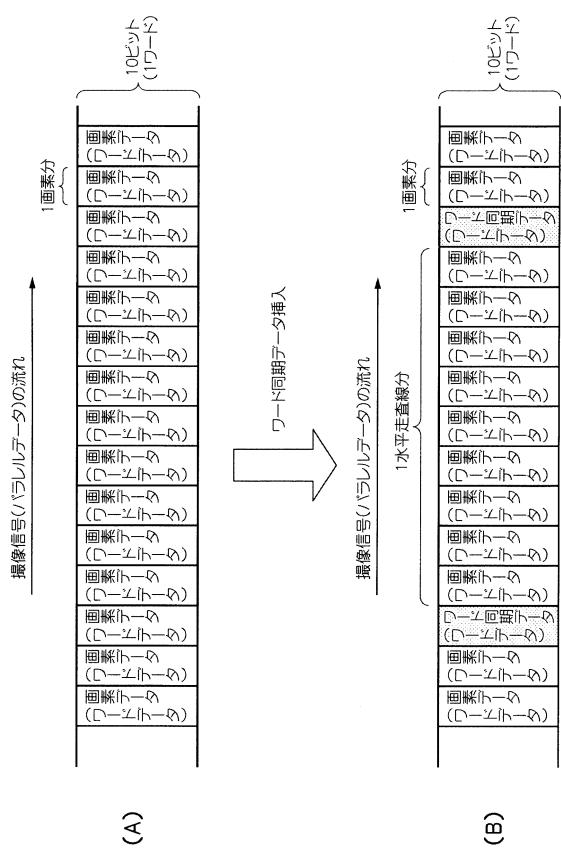

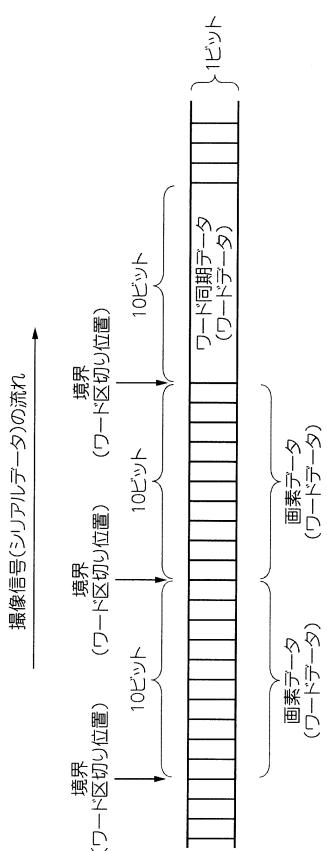

【図10】P/S変換器における同期データ挿入処理部100によるワード同期データの挿入の説明に使用したデータ構成図

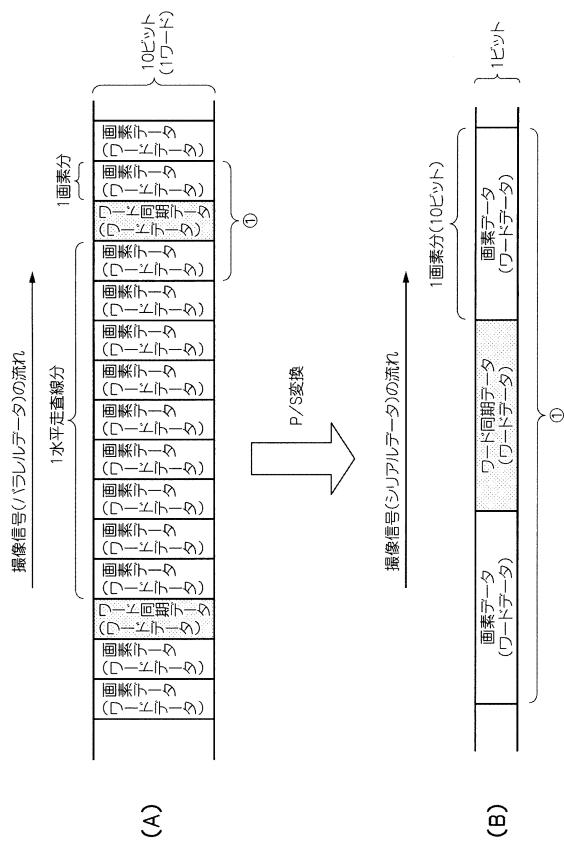

【図11】P/S変換器におけるP/S変換処理部によるP/S変換の説明に使用したデータ構成図

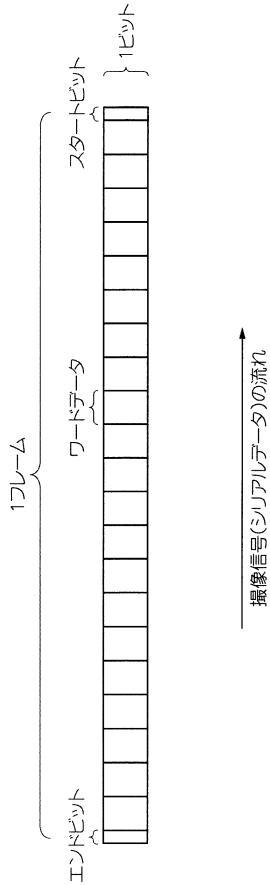

【図12】撮像チップからプロセッサ装置へと伝送される撮像信号のデータ構成図

【図13】S/P変換器に入力される撮像信号のデータ構成図

【図14】S/P変換器におけるワード同期処理部がワード同期データに基づいてワード

10

20

30

40

50

同期処理を実行する際の判断処理の処理手順を示したフローチャート

【図15】S/P変換器におけるワード同期処理部が復号エラーに基づいてワード同期処理を実行する際の処理手順を示したフローチャート

【図16】画像処理回路における補間処理の説明に使用した説明図

【発明を実施するための形態】

【0026】

以下、添付図面に従って本発明の好ましい実施の形態について詳説する。

【0027】

図1に示す内視鏡システム2は、電子内視鏡10、プロセッサ装置11、光源装置12などから構成されている。

10

【0028】

電子内視鏡10は、体腔内に挿入される可撓性の挿入部14と、挿入部14の基端部分に連設された操作部15と、プロセッサ装置11及び光源装置12に接続されるユニバーサルコード16とを備えている。

20

【0029】

挿入部14の先端には、体腔内撮影用の撮像チップ(撮像装置)42(図3参照)などが内蔵された先端部17が連設されている。先端部17の後方には、複数の湾曲駒を連結した湾曲部18が設けられている。湾曲部18は、操作部15に設けられたアングルノブ19が操作されて、挿入部14内に挿設されたワイヤが押し引きされることにより、上下左右方向に湾曲動作する。これにより、先端部17が体腔内の所望の方向に向けられる。

20

【0030】

ユニバーサルコード16の基端は、コネクタ20に連結されている。コネクタ20は、複合タイプのものであり、コネクタ20にはプロセッサ装置11が接続される他、光源装置12が接続される。

【0031】

プロセッサ装置11は、ユニバーサルコード16内に挿通されたケーブル50(図3参照)を介して電子内視鏡10に給電を行い、撮像チップ42の駆動を制御するとともに、撮像チップ42からケーブル50を介して伝送された撮像信号を受信し、受信した撮像信号に各種信号処理を施して画像データに変換する。プロセッサ装置11で変換された画像データは、プロセッサ装置11にケーブル接続されたモニタ21に内視鏡画像として表示される。また、プロセッサ装置11は、コネクタ20を介して光源装置12と電気的に接続され、内視鏡システム2の動作を統括的に制御する。

30

【0032】

図2において、先端部17の前面17aには、観察窓30、照明窓31、鉗子出口32、及び送気・送水用ノズル33が設けられている。観察窓30は、先端部17の片側中央に配置されている。照明窓31は、観察窓30に関して対称な位置に2個配され、体腔内の被観察部位に光源装置12からの照明光を照射する。鉗子出口32は、挿入部14内に配設された鉗子チャンネル51(図3参照)に接続され、操作部15に設けられた鉗子口22(図1参照)に連通している。鉗子口22には、注射針や高周波メスなどが先端に配された各種処置具が挿通され、各種処置具の先端が鉗子出口32から露呈される。送気・送水用ノズル33は、操作部15に設けられた送気・送水ボタン23(図1参照)の操作に応じて、光源装置12に内蔵された送気・送水装置から供給される洗浄水や空気を、観察窓30や体腔内に向けて噴射する。

40

【0033】

図3において、観察窓30の奥には、体腔内の被観察部位の像光を取り込むための対物光学系40を保持する鏡筒41が配設されている。鏡筒41は、挿入部14の中心軸に対物光学系40の光軸が平行となるように取り付けられている。鏡筒41の後端には、対物光学系40を経由した被観察部位の像光を、略直角に曲げて撮像チップ42に向けて導光するプリズム43が接続されている。

【0034】

50

撮像チップ42は、CMOS型の固体撮像素子44と、固体撮像素子44の駆動及び信号の入出力を行う周辺回路45とが一体形成されたモノリシック半導体（いわゆるCMOSセンサチップ）であり、支持基板46上に実装されている。固体撮像素子44の撮像面44aは、プリズム43の出射面と対向するように配置されている。撮像面44a上には、矩形枠状のスペーサ47を介して矩形板状のカバーガラス48が取り付けられている。撮像チップ42、スペーサ47、及びカバーガラス48は、接着剤を介して組み付けられている。これにより、塵埃などの侵入から撮像面44aが保護されている。

#### 【0035】

挿入部14の後端に向けて延設された支持基板46の後端部には、複数の入出力端子46aが支持基板46の幅方向に並べて設けられている。入出力端子46aには、ユニバーサルコード16を介してプロセッサ装置11との各種信号の送り取りを媒介するための信号線49（図5の信号線49a～49e）が接合されており、入出力端子46aは、支持基板46に形成された配線やボンディングパッド等（図示せず）を介して撮像チップ42内の周辺回路45と電気的に接続されている。信号線49は、可撓性の管状のケーブル50内にまとめて挿通されている。ケーブル50は、挿入部14、操作部15、及びユニバーサルコード16の各内部を挿通し、コネクタ20に接続されている。

10

#### 【0036】

また、図示は省略したが、照明窓31の奥には、照明部が設けられている。照明部には、光源装置12からの照明光を導くライトガイドの出射端が配されている。ライトガイドは、ケーブル50と同様に、挿入部14、操作部15、及びユニバーサルコード16の各内部を挿通し、コネクタ20に入射端が接続されている。

20

#### 【0037】

図4において、固体撮像素子44は、単位画素60がマトリクス状に配置された画素部61と、画素部61からの出力信号（画素データ）の処理（ノイズ抑制処理）を行なう相関二重サンプリング（CDS）回路62と、画素部61の垂直方向の走査を制御するとともに画素部61のリセット動作を制御する垂直走査回路63と、水平方向の走査を制御する水平走査回路64と、画素データの出力を行う出力回路65と、各回路62～64に制御信号を与え、垂直・水平走査及びサンプリングのためのタイミング等を制御する制御回路66とから構成されている。

30

#### 【0038】

単位画素60は、1個のフォトダイオードD1、リセット用トランジスタM1、ドライブ用（增幅用）トランジスタM2、及び画素選択用トランジスタM3とからなる。各単位画素60は、垂直走査線（行選択線）L1及び水平走査線（列信号線）L2に接続されており、垂直走査回路63と水平走査回路64によって順次に走査される。

#### 【0039】

制御回路66は、画素部61の行及び列を走査するために垂直走査回路63及び水平走査回路64に入力する制御信号、フォトダイオードD1に蓄積された信号電荷をリセットするために垂直走査回路63に入力する制御信号、及び画素部61とCDS回路62との接続を制御するためにCDS回路62に入力する制御信号をそれぞれ生成する。

#### 【0040】

40

CDS回路62は、列信号線L2ごとに区分して設けられており、垂直走査回路63によって選択された行選択線L1に接続された各単位画素60の画素データを、水平走査回路64が outputする水平走査信号に従って順次に出力する。水平走査回路64は、CDS回路62と、出力回路65に接続された出力バスラインL3との間に設けられた列選択用トランジスタM4のオン／オフを水平走査信号により制御する。出力回路65は、CDS回路62から出力バスラインL3に順次に転送される画素データを增幅して出力する。以下では、出力回路65から出力される一連の画素データをまとめて撮像信号と称する。

#### 【0041】

なお、図示は省略するが、固体撮像素子44は、複数の色セグメントからなるカラーフィルタ（例えば、ベイヤー配列の原色カラーフィルタ）を備えた単板カラー撮像方式の固

50

体撮像素子である。

**【0042】**

図5において、撮像チップ42内の周辺回路45は、内部クロック信号を生成するPLL(Phase-Locked Loop)回路70と、固体撮像素子44に制御データを設定するレジスタ71と、固体撮像素子44から出力された撮像信号をデジタル化するアナログ/デジタル(A/D)変換器72と、デジタル化された撮像信号に対して8B10B方式のエンコードを行う8B10Bエンコーダ73と、内部クロック信号の周波数を遙倍し、シリアル伝送用のクロック信号を生成するPLL回路74と、エンコードされた撮像信号をシリアル信号に変換して出力するパラレル/シリアル(P/S)変換器75とから構成されている。10

**【0043】**

PLL回路70は、位相比較器、ループフィルタ、電圧制御発信器、及び分周器を備える位相同期回路であり、プロセッサ装置11から入力される安定した基準クロック信号BCLKと同期し、かつ基準クロック信号BCLKの周波数と所定の比例関係にある周波数(遙倍された周波数)を持つ内部クロック信号ICLKを生成する。この内部クロック信号ICLKは、周辺回路45内の各部、及び固体撮像素子44の制御回路66(図4参照)に供給される。

**【0044】**

レジスタ71は、プロセッサ装置11から入力される、固体撮像素子44を駆動するための制御データCTLを保持し、固体撮像素子44の制御回路66(図4参照)に入力する。レジスタ71は、シリアル/パラレル変換を行うシフトレジスタであり、シリアル信号形式で入力される制御データCTLを、パラレル信号に変換して制御回路66に入力する。この制御データCTLとしては、画素の走査方式(全画素走査/インターレース走査)、走査する画素領域(走査開始・終了する単位画素60の位置)、シャッタ速度(露光時間)などが入力される。制御回路66は、制御データCTL及び内部クロック信号ICLKに基づいて、固体撮像素子44内の上記各回路62~64を制御する。20

**【0045】**

A/D変換器72は、固体撮像素子44から出力される撮像信号について、アナログ信号である各画素データを量子化して8ビット(256階調)のデジタル信号に変換し、変換した8ビットのデジタル信号を、8本の配線を用いて、8B10Bエンコーダ73にパラレルに入力する。30

**【0046】**

8B10Bエンコーダ73は、A/D変換器72から入力された8ビットの画素データに対し、冗長な2ビットのデータを付加して10ビットの画素データに変換(符号化)する8B10B方式のエンコーダであり、8ビットから10ビットへの変換は、規格で定められた変換表を用いて行う。このとき、10ビットのデータ量を1ワードとして8ビットの画素データごとに変換される10ビットのデータをワードデータというものとする。この変換は、後述するシリアル伝送の際に同じ信号レベル("0"または"1")が所定期間以上連続しないようにするためのものであり、例えば、元の8ビットの画素データが"0000000"のときは"1001110100"の10ビットデータ(1ワードのワードデータ)への変換を行い、元の8ビットの画素データが"00001111"のときは"0101110100"のワードデータへの変換を行う。40

**【0047】**

PLL回路74は、前述のPLL回路70と同様な構成であり、内部クロック信号ICLKの周波数を例えば10倍に遙倍したシリアル伝送用クロック信号TCLKを生成し、P/S変換器75に供給する。

**【0048】**

P/S変換器75は、PLL回路74が生成したシリアル伝送用クロック信号TCLKに応じて、図6に示すように、8B10Bエンコーダ73から順次入力される画素データ(ワードデータ)をパラレル信号(パラレルデータ)からシリアル信号(シリアルデータ)50

)に変換する。このとき、PLL回路74の作用により、変換後のシリアルデータの周波数は、変換前のパラレルデータの周波数の10倍となる。P/S変換器75により生成されたシリアルデータは、撮像信号SDTとしてケーブル50内の信号線49aを介してプロセッサ装置11に伝送される。

#### 【0049】

プロセッサ装置11は、図5に示すように装置全体の制御を行う主制御回路(CPU)76と、電源電圧VDD及び接地電圧VSSを生成する電源回路77と、基準クロック信号BCLKを生成する基準クロック発生器78と、撮像チップ42から撮像信号SDTを受信し、撮像信号SDTからクロック信号及びデータ信号を再生するクロックデータリカバリ(Clock & Data Recovery: CDR)回路79と、CDR回路79により生成されたクロック信号の周波数を遅倍し、撮像チップ42内の内部クロック信号ICKと同一の周波数を有する信号処理用のクロック信号を生成するPLL回路80と、CDR回路79により生成されたデータ信号(ワードデータ)をシリアルデータからパラレルデータへと変換するシリアル/パラレル(S/P)変換器81と、S/P変換器81からのワードデータに対して8B10B方式のデコード(復号化)を行いエンコードされる前の8ビットの画素データからなる撮像信号を生成する8B10Bデコーダ82と、デコードされた撮像信号に対して画像処理を施し、モニタ21に表示するための画像データを生成する画像処理回路83とから構成されている。10

#### 【0050】

電源回路77は、電源電圧VDD及び接地電圧VSSを、プロセッサ装置11内の各部に供給するとともに、信号線49b, 49cを介して撮像チップ42内の各部に供給する。基準クロック発生器78は、周波数が安定した基準クロック信号BCLKを生成し、信号線49dを介して、撮像チップ42内のPLL回路70に入力する。20

#### 【0051】

CPU76は、プロセッサ装置11内の各部を制御するとともに、前述の制御データCTLを生成し、信号線49eを介して、撮像チップ42内のレジスタ71に入力する。

#### 【0052】

CDR回路79は、撮像チップ42からシリアル伝送される撮像信号SDTの位相を検出して、この撮像信号SDTの周波数に同期した抽出クロック信号RCLKを発生し、この抽出クロック信号RCLKにより撮像信号SDTをサンプリングすることで、撮像信号SDTを抽出クロック信号RCLKによりリタイミングしたデータ(リタイミングデータ:撮像信号RSDT)を生成する。30

#### 【0053】

具体的には、CDR回路79は、図7に示すように、位相比較器(PD)90と、ループフィルタ(LPF)91と、電圧制御発信器(VCO)92と、D型フリップフロップ93とから構成されている。PD90には、撮像信号SDTと、VCO92により発生される抽出クロック信号RCLKとが入力され、PD90の出力は、LPF91を介してVCO92に入力される。D型フリップフロップ93は、データ入力端子Dに撮像信号SDTが入力され、クロック入力端子に抽出クロック信号RCLKが入力される。

#### 【0054】

PD90は、撮像信号SDTと抽出クロック信号RCLKとの各立ち上がりエッジを比較することで位相差を検出し、その検出信号を、LPF91を介してVCO92に入力する。VCO92は、入力された検出信号に応じて抽出クロック信号RCLKの周波数を変更する。その結果、VCO92からは、図8に示すように、撮像信号SDTの周波数に同期した抽出クロック信号RCLKが出力される。40

#### 【0055】

D型フリップフロップ93は、撮像信号SDTを、抽出クロック信号RCLKの立ち上がりエッジでサンプリングしてデータ保持を行うものであり、抽出クロック信号RCLKに位相同期したリタイミングデータとして撮像信号RSDTを再生し、データ出力端子Qから出力する。CDR回路79により生成された抽出クロック信号RCLKは、PLL回50

路 8 0 に入力され、再生された撮像信号 R S D T は、S / P 変換器 8 1 に入力される。

【 0 0 5 6 】

図 5 に戻り、P L L 回路 8 0 は、前述の P L L 回路 7 0 と同様な構成であり、抽出クロック信号 R C L K の周波数を 1 / 10 倍に遅倍し、内部クロック信号 I C L K と同一の周波数を有する信号処理用のクロック信号 S C L K を生成し、S / P 変換器 8 1、8 B 1 0 B デコーダ 8 2、及び画像処理回路 8 3 に供給する。

【 0 0 5 7 】

S / P 変換器 8 1 は、P L L 回路 8 0 が生成したクロック信号 S C L K に応じて、C D R 回路 7 9 から入力される撮像信号 R S D T に対し、図 6 に示したパラレル / シリアル変換の逆変換に相当するシリアル / パラレル変換を行い、順次入力されるワードデータをシリアルデータからパラレルデータへと変換する。S / P 変換器 8 1 によりワードデータごとにシリアルデータからパラレルデータに変換された撮像信号 R S D T は、8 B 1 0 B デコーダ 8 2 に入力される。

【 0 0 5 8 】

8 B 1 0 B デコーダ 8 2 は、8 B 1 0 B 方式の規格で定められた変換表を用い、前述の 8 B 1 0 B エンコーダ 7 3 とは逆の変換（復号化）を行い、順次入力される撮像信号 R S D T を 10 ビットのパラレルデータ（ワードデータ）から元の 8 ビットのパラレルデータ（画素データ）へと復元する。これにより、8 B 1 0 B エンコーダ 7 3 による符号化を行う前の画素データが得られる。そして、8 B 1 0 B デコーダ 8 2 により復元された画素データからなる撮像信号は、画像処理回路 8 3 に入力される。

【 0 0 5 9 】

画像処理回路 8 3 は、クロック信号 S C L K に基づいて、撮像信号に含まれる各画素データを検出し、内蔵メモリ 1 1 2 へ記録を行うとともに、ホワイトバランス調整、ゲイン補正、色補間、輪郭強調、ガンマ補正、カラーマトリックス演算等の画像処理を行い画像データを生成する。また、画像処理回路 8 3 は、画像データをモニタ 2 1 に表示するための信号形式に変換し、モニタ 2 1 に画像表示を行う。

【 0 0 6 0 】

上記のように構成された内視鏡システム 2 で体腔内を観察する際には、電子内視鏡 1 0 、プロセッサ装置 1 1 、光源装置 1 2 、及びモニタ 2 1 の電源をオンにして、電子内視鏡 1 0 の挿入部 1 4 を体腔内に挿入し、光源装置 1 2 からの照明光で体腔内を照明しながら、固体撮像素子 4 4 により撮像される体腔内の画像をモニタ 2 1 で観察する。

【 0 0 6 1 】

固体撮像素子 4 4 により生成された撮像信号は、A / D 変換器 7 2 により 8 ビットのパラレルデータに変換され、8 B 1 0 B エンコーダ 7 3 で 10 ビットのパラレルデータに符号化される。この 10 ビットのパラレルデータからなる撮像信号は、P / S 変換器 7 5 によりシリアルデータに変換された後、信号線 4 9 a を介してプロセッサ装置 1 1 に伝送される。

【 0 0 6 2 】

プロセッサ装置 1 1 は、シリアル伝送された撮像信号を C D R 回路 7 9 で受け、C D R 回路 7 9 により、クロック信号（抽出クロック信号 R C L K ）と、このクロック信号に位相同期したデータ信号（リタイミングデータ R S D T ）とを生成する。C D R 回路 7 9 によりリタイミングデータとして生成された撮像信号 R S D T は、抽出クロック信号 R C L K に基づき、S / P 変換器 8 1 及び 8 B 1 0 B デコーダ 8 2 により変換が行われ、元の 8 ビットのパラレルデータに復元される。この 8 ビットのパラレルデータからなる撮像信号は、画像処理回路 8 3 により画像データに変換され、モニタ 2 1 に画像表示が行われる。

【 0 0 6 3 】

次に上記の内視鏡システム 2 において撮像チップ 4 からプロセッサ装置 1 1 への撮像信号の伝送に関して説明する。

【 0 0 6 4 】

図 9 は、撮像チップ 4 2 からプロセッサ装置 1 1 に画素データを伝送する図 5 に示した

10

20

30

40

50

8 B 1 0 B エンコーダ 7 3 以降の撮像信号の伝送系回路を抽出して示した構成図である。

【 0 0 6 5 】

上述のように撮像チップ 4 2 では、A / D 変換器 7 2 から 8 B 1 0 B エンコーダ 7 3 に撮像信号として順次入力される 8 ビットのパラレルデータである画素データが、8 B 1 0 B エンコーダ 7 3 により 10 ビットのパラレルデータ（10 ビットを 1 ワードとするワードデータ）に変換された後、P / S 変換器 7 5 に入力される。P / S 変換器 7 5 に順次入力される画素データは、P / S 変換器 7 5 によりパラレルデータからシリアルデータへと変換されて撮像信号 S D T としてプロセッサ装置 1 1 へと送信される。

【 0 0 6 6 】

このような撮像チップ 4 2 における撮像信号 S D T の送信に際して、撮像信号 S D T には、所定間隔（所定時間間隔又は所定ビット数間隔）でワード同期のためのワード同期データが挿入されるようになっている。

10

【 0 0 6 7 】

ワード同期データは、撮像チップ 4 2 から送信される撮像信号 S D T としてシリアルデータを受信したプロセッサ装置 1 1 において、シリアルデータを 1 ワードずつのワードデータに区切るタイミングが画素データごとに区切るタイミングとして適切な状態であること、即ち、本実施の形態においては、撮像チップ 4 2 の 8 B 1 0 B エンコーダ 7 3 から順次出力されたワードデータと、シリアルデータ（撮像信号 S D T ）を受信したプロセッサ装置 1 1 においてそのシリアルデータから順次取得されるワードデータとが一致（ワード同期）していることを確認し、また、ワード同期していない場合にはワード同期を復旧させるために使用されるデータである。

20

【 0 0 6 8 】

このワード同期データとして 8 B 1 0 B エンコーダ 7 3 の出力データとしては存在しないビットパターンのワードデータが用いられる。例えば、カンマデータ（コンマデータ）と称される“0 1 0 1 1 1 1 0 0”がワード同期データとして用いられる。なお、ワード同期データは他のビットパターンであってもよい。

【 0 0 6 9 】

撮像信号 S D T へのワード同期データの挿入は、例えば、撮像チップ 4 2 の P / S 変換器 7 5 において行われる。図 9 に示すように P / S 変換器 7 5 は、同期データ挿入処理部 1 0 0 と P / S 変換処理部 1 0 2 を備えている。

30

【 0 0 7 0 】

同期データ挿入処理部 1 0 0 は、図 1 0 ( A ) に示すように 8 B 1 0 B エンコーダ 7 3 から撮像信号として順次入力される 10 ビット（1 ワード）のワードデータ（画素データ）を後段の P / S 変換処理部 1 0 2 に通過させると共に、所定のタイミングで 1 ワード分のワード同期データを画素データを示すワードデータの間に挿入し、P / S 変換処理部 1 0 2 に出力する。なお、図 5 に示した固体撮像素子 4 4 から A / D 変換器 7 2 を介して 8 B 1 0 B エンコーダ 7 3 に入力される撮像信号が各画素の画素データ以外のデータを含む場合でもそのデータには言及せず以下においては画素データのみが撮像信号として入力されるものとして説明する。

【 0 0 7 1 】

40

ワード同期データを挿入するタイミングとしては、固体撮像素子 4 4 での画素データの読み出しがインターレース方式やプログレッシブ方式で知られる走査方式とする場合に、例えば、図 1 0 ( B ) のように 1 本の水平走査線分の画素データ（ワードデータ）が同期データ挿入処理部 1 0 0 を通過するごとに（即ち、1 水平走査期間ごとに）、1 つのワード同期データを挿入する。この場合に、同期データ挿入処理部 1 0 0 は、通過させるワードデータのワード数をカウントし、1 水平走査線分のワード数（画素数）のワードデータが通過するごとにワード同期データを挿入するようにしてもよいし、固体撮像素子 4 4 の制御回路 6 6 から現在の画素データの読み出し位置の情報を取得して、その情報に基づいてワード同期データを挿入するようにしてもよい。また、ワード同期データを挿入する位置として、各水平走査線の開始画素のワードデータの前、又は、各水平走査線の終了画素

50

のワードデータの後、即ち、通過させるワードデータの水平走査線（水平走査線の番号）が切り替わる位置（水平帰線期間に相当する位置）のように特定画素のワードデータに隣接する位置にワード同期データを挿入することも可能である。

#### 【0072】

なお、ワード同期データを挿入するタイミングは、必ずしも上記のように1水平走査線ごとである必要はない。

#### 【0073】

P/S変換処理部102は、上記のようにワード同期データが挿入されて同期データ挿入処理部100から撮像信号として順次出力されるワードデータを図6に示したようにパラレルデータからシリアルデータへと変換する。これによって、画素データを示すワードデータに対して所定間隔でワード同期データが挿入されたワードデータが図11(A)のようなパラレルデータから図11(B)のようなシリアルデータに変換され、そのワード同期データが挿入されたシリアルデータが、撮像信号SDTとして撮像チップ42からプロセッサ装置11に送信される。10

#### 【0074】

なお、P/S変換器75は、図12のように所定ビット数のデータを最小の伝送単位（フレームという）として、撮像信号SDTをフレーム単位で送信しており、各フレームごとにフレームの開始を示すスタートビット（例えば“0”）とフレームの終了を示すエンドビット（例えば“1”）を附加している。また、1フレームのデータ量は固体撮像素子44において例えば1画面分（画素データの読み出し方式がインターレース方式の場合には1フィールド分、プログレッシブ方式の場合には1フレーム分）の画素データ（ワード同期データ等を含む）を伝送する際のデータ量としても良いし、1水平走査線分の画素データを伝送する際のデータ量としても良く、任意のデータ量とすることができる。20

#### 【0075】

また、ワード同期データの挿入は、P/S変換器75ではなく、8B10Bエンコーダ73で行うようにすることも可能であるし、8B10Bエンコーダ73やP/S変換器75とは別の処理部で行うことも可能である。

#### 【0076】

一方、上述のようにプロセッサ装置11では、撮像チップ42から伝送された撮像信号SDTが、CDR回路79によりリタイミングされた後、S/P変換器81により10ビットのパラレルデータ（ワードデータ）に変換されて、8B10Bデコーダ82に入力される。8B10Bデコーダ82に順次入力されるワードデータは、S/P変換器81により元の8ビットの画素データに復号された後、画像処理回路83に入力される。30

#### 【0077】

まず、このようなプロセッサ装置11における撮像信号SDTの受信に際してのワード同期データに基づくワード同期処理について説明する。プロセッサ装置11では、ワード同期データに基づいて、ワード同期していることを確認するワード同期の確認と、ワード同期していない場合にはワード同期を復旧させるワード同期の復旧の処理が行われる。

#### 【0078】

ワード同期は、撮像信号SDTとして撮像チップ42から送信されるシリアルデータを受信したプロセッサ装置11において、シリアルデータを1ワードずつのワードデータに区切るタイミングを、画素データごとに区切るタイミングとして適切な状態にすること、即ち、本実施の形態では、撮像チップ42の8B10Bエンコーダ73から順次出力されたワードデータと、プロセッサ装置11の8B10Bデコーダ82に順次入力されるワードデータとを一致させることを意味する。撮像チップ42からプロセッサ装置11への撮像信号SDTの伝送がデータ破損（ビット挿入やビット欠落等）なく正常に行われている場合には、S/P変換器81が撮像信号としてフレーム単位で伝送されるシリアルデータのスタートビットを検出し、それに続くビットデータ列を1ワード（10ビット）ごとにパラレルデータに変換することでワード同期した状態となっている。40

#### 【0079】

一方、撮像信号の伝送中、特に撮像チップ42からプロセッサ装置11への撮像信号S-DTの伝送中にノイズ等の影響によりビット挿入やビット欠落等のデータ破損が発生することがあり、ワード同期のタイミングにずれが生じ、ワード同期していない状態となる場合がある。その場合には、ワード同期の確認によりワード同期していない状態であることが検出され、ワード同期の復旧によりワード同期している状態に復旧するようになっている。

#### 【0080】

ワード同期データに基づくワード同期の確認と復旧に関する処理は、例えば、プロセッサ装置11のS/P変換器81において行われる。図9に示すようにS/P変換器81は、同期データ検出処理部104、S/P変換処理部106、ワード同期処理部108とを備えている。10

#### 【0081】

同期データ検出処理部104は、CDR回路79から撮像信号（リタイミングされた撮像信号RS-DT）として順次入力されるシリアルデータのうちからワード同期データを示すビットパターンを検出すると共に、それによってワード同期データを検出した場合にはワード同期データを検出したことを示す検出信号をワード同期処理部108に与える。また、ワード同期データ以外のワードデータを後段のS/P変換処理部106に通過させ、ワード同期データを撮像信号から取り除く。なお、ワード同期データを撮像信号から取り除く処理は、後段の8B10Bデコーダ82や画像処理回路83において行うようにしてもよい。20

#### 【0082】

S/P変換処理部106は、同期データ検出処理部104を通過したワードデータを1ワード（10ビット）ずつに区切ってシリアルデータから10ビットのパラレルデータへと変換する。

#### 【0083】

ワード同期処理部108は、CDR回路79からS/P変換器81に撮像信号として入力される図13のようなシリアルデータに対して、同期データ検出処理部104からワード同期データを検出したことを示す検出信号が与えられると、S/P変換処理部106に対して、そのワード同期データに続くビットデータ列を10ビットずつに区切るタイミングで10ビットのビットデータ列としてパラレル伝送する10ビットのパラレルデータに変換させる。30

#### 【0084】

即ち、S/P変換処理部106が、ワード同期データに続くビットデータ列を10ビットずつに区切るタイミングで（ワード同期データに続くビットデータ列を10ビットずつに区切る位置をワードデータの境界（ワード区切り位置）として）10ビットのビットデータ列を10ビットのパラレルデータに変換することによってワード同期している状態となるが、ワード同期処理部108は、ワード同期データの検出（同期データ検出処理部104からの検出信号）に基づいて、そのようにワード同期している状態となるようにS/P変換処理部106がシリアルデータ（ビットデータ列）をパラレルデータに変換するS/P変換のタイミングを調整する。40

#### 【0085】

ワード同期処理部108に同期データ検出処理部104からの検出信号が与えられた際にワード同期している状態が確保されている場合には、S/P変換処理部106のS/P変換のタイミングの調整を行っても状態は何も変化せず、実質的にワード同期していることの確認のみが行われたことになる。

#### 【0086】

これに対して、ワード同期処理部108に同期データ検出処理部104からの検出信号が与えられた際にワード同期していない状態となっていた場合には、上記のようにワード同期処理部108がワード同期データの検出に基づいてS/P変換処理部106のS/P変換のタイミングを調整することでワード同期の復旧が行われたことになる。50

**【0087】**

このようにワード同期処理部108によるワード同期の確認及び復旧の処理（ワード同期処理）により、S/P変換処理部106によりパラレルデータに変換された撮像信号は、図10（A）に示したワード同期データ挿入前の撮像信号と一致したワードデータ（画素データ）により構成されたものとなる。即ち、S/P変換器81によりシリアルデータからパラレルデータへと変換されて後段の8B10Bデコーダ82に入力されるワードデータが8B10Bエンコーダ73により符号化された後のワードデータに一致するようワード同期（アライメント）がなされる。また、撮像信号の伝送中において、ノイズ等の影響でデータ破損が生じてワード同期にずれが生じてしまった場合でもワード同期データに基づくワード同期処理部108でのワード同期処理によりワード同期が適正な状態に復旧するようになっている。10

**【0088】**

ここで、撮像信号の伝送中等にデータ破損が生じた場合に、ワード同期データ以外のデータがワード同期データのビットパターンと一致する可能性がある。このとき、同期データ検出処理部104では、そのワード同期データ以外のデータをワード同期データと誤検出することになり、誤検出されたワード同期データに基づいてワード同期処理部108が上記のワード同期処理を実施してしまうとワード同期していない状態になるという不具合が生じる。

**【0089】**

そこで、そのような不具合を防止するため、所定回数（2回以上の回数であって例えば3回）のワード同期データの検出に基づいて上記のワード同期処理（ワード同期の確認と復旧の処理）を実行すると好適である。即ち、ワード同期データを適切な間隔（P/S変換器75においてワード同期データが挿入される予め決められた時間間隔又はビット数間隔）となるタイミング、即ち、P/S変換器75により挿入されたワード同期データが検出されるべきタイミングで複数回検出した場合に、それらのワード同期データを適正なワード同期データと判断し、上記のワード同期処理（ワード同期の確認と復旧の処理）を実行すると好適である。20

**【0090】**

具体的な態様として、所定回数（2回以上の回数であって例えば3回）のワード同期データが連続して適切な間隔で検出された場合に、それらのワード同期データを適正なワード同期データと判断し、上記のワード同期処理（ワード同期の確認と復旧の処理）を実行するようとする。30

**【0091】**

即ち、同期データ検出処理部104からワード同期処理部108にワード同期データが検出されたことを示す検出信号が、所定回数連続して適切な間隔で与えられた場合に、ワード同期処理部108がそれらを適正なワード同期データの検出と判断する。そして、適正なワード同期データの検出と判断した場合に、それらのうちの最後に検出された最新のワード同期データの検出信号に基づいてワード同期処理を実行する。

**【0092】**

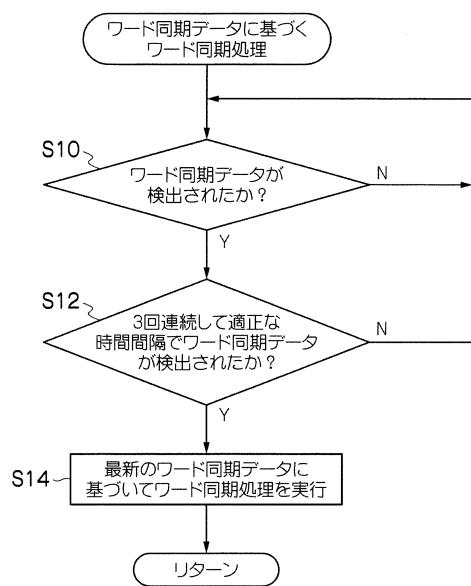

図14は、ワード同期処理部108においてワード同期データに基づくワード同期処理を実行する際の判断処理の処理手順を示したフローチャートである。40

**【0093】**

ステップS10では、ワード同期データが検出されたか否かを判定する。即ち、S/P変換器81に撮像信号として入力されたシリアルデータにおいてワード同期データと一致するビットパターンが検出され、同期データ検出処理部104から検出信号が与えられたか否かを判定する。このステップS10の判定処理においてNOと判定している間は、ステップS10の処理を繰り返す。一方、YESと判定した場合にはステップS12に移行する。

**【0094】**

ステップS12では、3回連続して適切な時間間隔でワード同期データが検出されたか50

否かを判定する。即ち、P/S変換器75においてワード同期データが挿入される時間間隔 $T_i$ （適正なワード同期データが検出される時間間隔）が予め決められており、ステップS12においてワード同期データを検出した時刻 $T_0$ に対して時間間隔 $T_I$ の1回分を過去に遡る時刻 $T_0 - T_i$ と、2回分を過去に遡る時刻 $T_0 - 2 \times T_i$ においてワード同期データを検出したか否かを判定する。このステップS12の判定処理においてNOと判定した場合には、ステップS10の処理に戻り、YESと判定した場合にはステップS14に移行する。なお、本処理において、ワード同期データが連続する回数を3回としたが、3回でなくても2回以上の回数であれば良い。また、適切な時間間隔ではなく、適切なビット数間隔（適正なワード同期データが検出されるビット数間隔、即ち、2つの適正なワード同期データの間に送られるワードデータのビット数）で所定回数連続してワード同期データを検出したか否かを判定してもよい。10

#### 【0095】

ステップS14では、ステップS10において検出した最新のワード同期データに基づいてワード同期処理を実行する。即ち、最新のワード同期データに続くビットデータ列を10ビットずつに区切るタイミングでS/P変換処理部106にS/P変換を実行させる。この処理が終了すると本フローチャートの処理を終了する。なお、本フローチャートの処理は繰り返し実行される。

#### 【0096】

これによれば、ワード同期データ以外のデータをワード同期データと誤検出した場合であってもその検出はワード同期処理の実行に対しては無効となるため、不適切なワード同期処理が実施されないようになる。20

#### 【0097】

また、他の具体的な態様として、上記のように所定回数の適正なワード同期データを連続して検出した場合でなくとも、所定時間の期間内において適切な間隔で検出されるべき複数のワード同期データのうちのいずれか複数のワード同期データを検出した場合にそれらのワード同期データを適正なワード同期データと判断し、ワード同期処理を実行するようにもよい。即ち、同期データ検出処理部104からワード同期処理部108にワード同期データが検出されたことを示す検出信号が、所定時間の期間内に適切な間隔のタイミングに合致して所定回数以上与えられた場合に、ワード同期処理部108がそれらを適正なワード同期データの検出と判断する。そして、適正なワード同期データの検出と判断した場合に、それらのうちの最後に検出されたワード同期データの検出信号に基づいてワード同期処理を実行すればよい。30

#### 【0098】

なお、上記のようなワード同期データの検出やワード同期データに基づくワード同期の確認、復旧の処理はS/P変換器81において行うのではなく、8B10Bデコーダ82で行うようにすることも可能であるし、S/P変換器81や8B10Bデコーダ82以外の処理部で行うようにすることも可能である。即ち、上記実施の形態では、S/P変換器81のS/P変換処理部106に入力される前（S/P変換の前）のシリアルデータからワード同期データを検出し、検出したワード同期データに基づいてS/P変換のタイミングを調整することによってシリアルデータを10ビットずつのワードデータに区切るタイミングを調整してワード同期の復旧を行うようにしている。一方、ワード同期データの検出は、8B10Bデコーダ82に入力する前のパラレルデータから検出することも可能であり、また、ワード同期データに基づくワード同期の確認や復旧に関しても8B10Bデコーダ82による復号化を行う前のパラレルデータを複数ワード分蓄積して、シリアルデータをワードデータとして区切るタイミングを調整したパラレルデータを作り直して8B10Bデコーダ82による復号化を行うことで実施することができる。40

#### 【0099】

次に、プロセッサ装置11における撮像信号S/D/Tの受信に際しての復号エラーに基づくワード同期処理について説明する。プロセッサ装置11では、8B10Bデコーダ82における復号エラーに基づいてワード同期処理（ワード同期を復旧させる処理）が行われ50

るようになっている。

#### 【0100】

復元エラーとしては、例えば、8B10Bデコーダ82に入力したワードデータが破損しているために変換表に存在しないデータとなっている場合（テーブルエラー）や、ランニングディスパリティが適正でない場合（ディスパリティエラー）がある。

#### 【0101】

このような復号エラーに基づくワード同期の復旧に関する処理は、例えば、S/P変換器81と8B10Bデコーダ82と間で行われる。

#### 【0102】

8B10Bデコーダ82は、図9のように、復元エラーが発生した場合にエラー信号を出力するエラー出力部110を備えている。8B10Bデコーダ82において、S/P変換器81から入力される撮像信号を10ビットのパラレルデータ（ワードデータ）から元の8ビットのパラレルデータ（画素データ）へと復号する際に復号エラーが生じた場合には、エラー出力部110がその復号エラーが発生したことを検出してエラー信号を出力する。そのエラー信号は、上記のS/P変換器81のワード同期処理部108に入力される。

10

#### 【0103】

ワード同期処理部108は、エラー出力部110からのエラー信号が入力されると、S/P変換処理部106におけるS/P変換のタイミングを1ビット分シフトさせる。即ち、S/P変換処理部106がシリアルデータ（ビットデータ列）をパラレルデータに変換するタイミングを1ビットデータ分シフトさせて（遅らせるか、又は、早くする）、シリアルデータとして入力されるビットデータ列をワードデータに区切る位置（図13に示すワード区切り位置）を1ビット分ずらす。そして、この処理をエラー出力部110からのエラー信号が入力されなくなるまで繰り替えし実行し、エラー信号が入力されなくなった場合に上記処理を停止する。

20

#### 【0104】

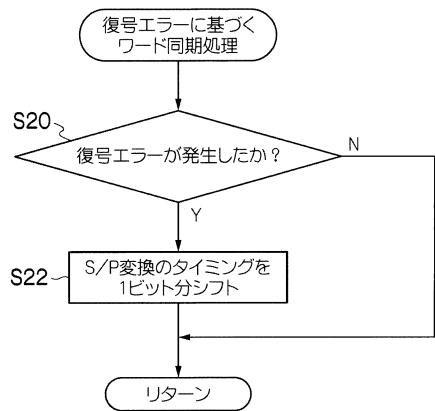

図15は、ワード同期処理部108において8B10Bデコーダ82の復号エラーに基づくワード同期処理を実行する際の処理手順を示したフローチャートである。

#### 【0105】

ステップS20では、8B10Bデコーダ82において復号エラーが発生したか否かを判定する。即ち、8B10Bデコーダ82において復号エラーが発生して8B10Bデコーダ82のエラー出力部からエラー信号が与えられたか否かを判定する。このステップS20の判定処理においてNOと判定した場合には、このフローチャートの処理を終了する。一方、YESと判定した場合にはステップS22に移行する。なお、このフローチャートの処理は繰り返し実行されるためステップS20の判定処理が繰り返し実行される。

30

#### 【0106】

ステップS22では、S/P変換器81のS/P変換処理部106におけるS/P変換のタイミングを1ビット分シフトさせる。即ち、S/P変換処理部106がシリアルデータ（ビットデータ列）をパラレルデータに変換するタイミングを1ビットデータ分だけ、現在のタイミングよりも遅いタイミング又は早いタイミングのいずれかにシフトさせる。この処理が終了すると本フローチャートの処理を終了する。

40

#### 【0107】

以上のフローチャートの処理によれば、復号エラーが発生した場合に復号エラーが発生しなくなるまでステップS22の処理が繰り返されて、S/P変換のタイミングが1ビットデータ分ずつシフトする。復号エラーが発生しなくなった状態ではワード同期している状態と考えられるため、ワード同期にそれが生じた場合に上記フローチャートの処理によりワード同期の復旧が行われることになる。

#### 【0108】

これにより、撮像信号の伝送中にノイズ等の影響でデータ破損等が生じてワード同期にそれが生じてしまった場合でも復号エラーに基づくワード同期処理部108での上記のワ

50

ード同期処理によりワード同期が適正な状態に復旧するようになっている。また、ワード同期データに基づくワード同期処理によるワード同期の復旧よりも短時間で復旧することが可能となり、早急に復旧することができる。

#### 【0109】

なお、上記のような復号エラーに基づくワード同期の復旧の処理はS/P変換器81において行うのではなく、8B10Bデコーダ82で行うようにすることも可能であるし、S/P変換器81や8B10Bデコーダ82以外の処理部で行うようにすることも可能である。即ち、上記実施の形態では、S/P変換器81のS/P変換処理部106におけるS/P変換のタイミングを変更（1ビットずつシフト）することによってシリアルデータを10ビットずつのワードデータに区切るタイミングを変更してワード同期の復旧を行うようにしている。一方、8B10Bデコーダ82による復号化を行う前のパラレルデータを複数ワード分蓄積して、シリアルデータをワードデータとして区切るタイミングを変更（1ビットずつシフト）したパラレルデータを作り直して8B10Bデコーダ82による復号化を行うことによっても上記実施の形態と同様に復号エラーに基づくワード同期の復旧を行うことができる。10

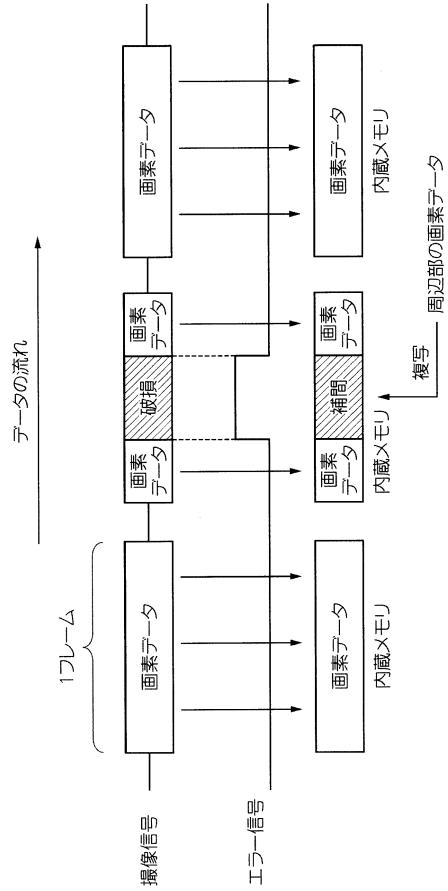

#### 【0110】

次に、プロセッサ装置11における撮像信号SDTの受信に際しての画像データの補間処理について説明する。プロセッサ装置11では、8B10Bデコーダ82において復号エラーが発生した場合に、そのときの画素データを周辺部の画素の画素データに基づいて生成された画素データ（補間データ）で補間する補間処理が行われるようになっている。20

#### 【0111】

補間処理は、例えば、8B10Bデコーダ82と画像処理回路83との間で行われる。

#### 【0112】

画像処理回路83は、図9に示すように内蔵メモリ（バッファメモリ）112を備えており、その内蔵メモリ112には、8B10Bデコーダ82から撮像信号として画像処理回路83に入力される所定データ量（例えば所定数の画面分の画素データのデータ量）の画素データが蓄積されると共に、内蔵メモリ112のメモリ容量分の画素データが蓄積されると新しく入力された画素データが最も古い画素データに置き換えられて記憶がされるようになっている。

#### 【0113】

また、画像処理回路83に対しても、上記の8B10Bデコーダ82のエラー出力部110からのエラー信号が与えられるようになっており、画像処理回路83では、図16に示すように、8B10Bデコーダ82から撮像信号として順次フレーム単位で入力される画素データを内蔵メモリ112に記憶する。そして、エラー出力部110からエラー信号が与えられた場合には、そのときに8B10Bデコーダ82から出力された画素（エラー画素）の画素データを内蔵メモリ112に記憶させず、そのエラー画素の画素データが記憶されるべき内蔵メモリ112のメモリ領域に、エラー画素の周辺部の画素の画素データから生成された補間データを記憶させて、エラー画素の画素データを補間データで補間するようしている。30

#### 【0114】

エラー画素に対して周辺部となる画素の画素データとして、エラー画素に対して空間的に近傍となる画素の画素データの他に、時間的に近傍となる画素の画素データも含まれており、エラー画素に対して空間的に近傍となる画素の画素データとしては、エラー画素に対して同一画像上の所定距離範囲以内の画素の画素データが該当する。このうち、補間データの生成に使用する画素データとしては、例えば、エラー画素に対して上下方向又は左右方向の所定距離範囲以内の画素の画素データに限定してもよいし、エラー画素に対して隣接する画素の画素データに限定してもよい。40

#### 【0115】

エラー画素に対して時間的に近傍となる画素としては、エラー画素が得られた時間に対して所定時間範囲以内の時間に得られた画像上のエラー画素と同一位置の画素データ

10

20

30

40

50

タが該当する。このうち、補間データの生成に使用する画素データとしては、例えば、1画面分前又は1画面分後に得られた画像上の画素データに限定してもよい。

#### 【0116】

一方、エラー画素の画素データを補間する補間データは、上記のようにエラー画素に対して周辺部となる画素のうちの複数の画素の画素データに基づいて所定の演算処理により生成したものであってもよいし、エラー画素に対して周辺部となる画素のうちのいずれか1つの画素の画素データをそのまま使用したものであってもよい。

#### 【0117】

前者の場合に、例えば、エラー画素に対して周辺部となる画素のうち、補間データの生成に使用する複数の画素が予め決められており、それらの画素の画素データの平均値を求めて、その平均値を補間データとする様態が考えられる。このとき、補間データの生成に使用する画素の画素データを正常な画素データ（エラー画素以外の画素データ）のみに限定してもよい。なお、複数の画素データに基づいて補間データを生成するための演算処理は平均を求める処理に限らず、他の処理によって補間データを生成してもよい。

10

#### 【0118】

後者の場合には、例えば、エラー画素に対して周辺部となる画素のうち、補間データの生成に使用する1つの画素を予め決められており、その画素の画素データを補間データとする様態が考えられる。また、この場合には、補間データとする画素データを正常な画素データであることが望ましいため、例えば、エラー画素に対して周辺部となる画素のうち、補間データの生成に使用する画素として複数の画素を優先順位を付けて決めており、それらの画素のうち、正常な画素データが得られた画素の中から優先順位が最も高い画素の画素データを選出して、その画素データを補間データとすると好適である。

20

#### 【0119】

画像処理回路83は、8B10Bデコーダ82のエラー出力部110からのエラー信号が与えられた場合には、このようにして生成した補間データをエラー画素の画素データの代わりに内蔵メモリ112に記憶させ、内蔵メモリ112に記憶させた複数の画素データからなる画像データに所要の画像処理を施してその画像をモニタ21に表示させるようしている。したがって、撮像信号の伝送中にノイズ等の影響でデータ破損が生じた場合であっても、モニタ21に表示される画像の乱れを最小限に抑えることができる。

30

#### 【0120】

なお、画像処理回路83の内蔵メモリ112を使用して補間処理を行う場合に限らず、8B10Bデコーダ82と画像処理回路83との間に設けたバッファメモリにおいて補間処理を行うことも可能であり、例えば、撮像信号の伝送単位である1フレーム分の画素データを記憶するバッファメモリを1又は複数設けるようにしてもよい。この場合に、8B10Bデコーダ82から出力された画素データをフレーム単位でバッファメモリに一時的に記憶せしようにし、全てのバッファメモリに画素データが蓄積されると、最も古いフレームの画素データをバッファメモリから画像処理回路83に出力させると共に、そのバッファメモリに8B10Bデコーダ82からの新たなフレームの画素データを記憶せしようにする。複数のバッファメモリを備える場合には、8B10Bデコーダ82から順次出力された画素データをフレーム単位で複数のバッファメモリに巡回的に記憶せしようにする。この場合において、バッファメモリの数は、エラー画素の補間データを記憶せしるメモリ領域がバッファメモリに存在している状態において、そのエラー画素に対して補間データの生成に使用する画素の画素データをバッファメモリに記憶せしることができる容量分を満たす数であればよい。また、この場合にバッファメモリから補間データの生成に使用する画素データを読み出して補間データを生成する処理を、画像処理回路83で行ってもよいし、他の処理部、又は専用に設けた処理部で行うようにしてもよい。

40

#### 【0121】

以上、上記実施の形態では、固体撮像素子44をCMOS型の固体撮像素子としているが、本発明はこれに限定されず、固体撮像素子44をCCD型の固体撮像素子としても良い。

50

## 【0122】

また、上記実施形態では、A / D 変換器 72 により生成された 8 ビットの画素データを 8 B 1 0 B エンコーダ 73 により 10 ビットの画素データに変換するとしているが、本発明はこれに限定されず、変換前後のビット数は適宜変更しても良い。

## 【符号の説明】

## 【0123】

2 ... 内視鏡システム、10 ... 電子内視鏡、11 ... プロセッサ装置、12 ... 光源装置、14 ... 挿入部、15 ... 操作部、16 ... ユニバーサルコード、42 ... 撮像チップ（撮像装置）、44 ... 固体撮像素子、72 ... A / D 変換器、73 ... 8 B 1 0 B エンコーダ、75 ... P / S 変換器、76 ... C P U、79 ... C D R 回路、81 ... S / P 変換器、82 ... 8 B 1 0 B デコーダ、100 ... 同期データ挿入処理部、102 ... P / S 変換処理部、104 ... 同期データ検出処理部、106 ... S / P 変換処理部、108 ... ワード同期処理部、110 ... 8 B 1 0 B デコーダ、112 ... 内蔵メモリ

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図 1 1】

【図 1 2】

【図 1 3】

【図 1 4】

【図15】

【図16】

---

フロントページの続き

(56)参考文献 特開2009-201540(JP,A)

特開2008-148835(JP,A)

特開2004-229006(JP,A)

特開2006-250824(JP,A)

国際公開第2008/059588(WO,A1)

特開2008-080007(JP,A)

特開2006-051336(JP,A)

(58)調査した分野(Int.Cl., DB名)

|         |           |

|---------|-----------|

| A 6 1 B | 1 / 0 4   |

| G 0 2 B | 2 3 / 2 4 |

| H 0 4 N | 7 / 1 8   |