### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特**期2010-9687** (P2010-9687A)

(43) 公開日 平成22年1月14日(2010.1.14)

(51) Int.Cl.

$\mathbf{F} \mathbf{I}$

テーマコード (参考)

G 1 1 C 11/22 (2006.01)

G11C 11/22 501H G11C 11/22 501F

審査請求 未請求 請求項の数 5 OL (全 19 頁)

(21) 出願番号 (22) 出願日 特願2008-168781 (P2008-168781) 平成20年6月27日 (2008.6.27) (71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74)代理人 100075812

弁理士 吉武 賢次

(74)代理人 100082991

弁理士 佐藤 泰和

(74)代理人 100096921

弁理士 吉元 弘

(74)代理人 100103263

弁理士 川崎 康

(74)代理人 100118843

弁理士 赤岡 明

最終頁に続く

## (54) 【発明の名称】半導体記憶装置

#### (57)【要約】

【課題】ビット線容量の変動を抑制し、データを正確に 読み出すことができる半導体記憶装置を提供する。

【解決手段】半導体記憶装置は、強誘電体キャパシタと セルトランジスタとから成る複数のユニットセルを直列 に接続して構成されたセルブロックと、選択トランジス タを介してセルブロックの一端に接続されたビット線 、複数のダミートランジスタを直列に接続した複数のダミートランジスタを直列に接続した複数の ミーストリングの一端を共通に接続して構成されたダミーブロックと、ダミーブロックとビット線との間に接続されたダミーブロック選択トランジスタと、ビット線に 接続されたセンスアンプと、ワード線に接続されたダミード線ドライバと、ダミーワード線に接続されたケミーワード線ドライバとを備え、データ読出し動作において、 ダミーワード線ドライバは、読出し対象のユニットセル とビット線との間に介在するセルトランジスタの個数に 応じた個数のダミートランジスタをビット線に対して導 通状態にする。

【選択図】図2

#### 【特許請求の範囲】

### 【請求項1】

第1の電極と該第2の電極との間に設けられた強誘電体膜を含む複数の強誘電体キャパシタと、複数の前記強誘電体キャパシタのそれぞれに対応して設けられた複数のセルトランジスタとを含み、各前記強誘電体キャパシタおよび各前記セルトランジスタを並列に接続することによってユニットセルを成し、複数の該ユニットセルを直列に接続して構成されたセルブロックと、

前記複数のセルトランジスタのゲートに接続された複数のワード線と、

前記セルブロックの一端に接続された選択トランジスタと、

前記選択トランジスタを介して前記セルブロックの一端に接続されたビット線と、

前記セルブロックの他端に接続されたプレート線と、

複数のダミートランジスタを直列に接続することによってダミーストリングを成し、複数の該ダミーストリングの一端を共通に接続して構成されたダミーブロックと、

前記複数のダミートランジスタのゲートに接続された複数のダミーワード線と、

前記ダミーブロックと前記ビット線との間に接続されたダミーブロック選択トランジスタと、

前記ビット線に接続されたセンスアンプと、

前記ワード線に接続されたワード線ドライバと、

前記ダミーワード線に接続されたダミーワード線ドライバとを備え、

データ読出し動作において、前記ダミーワード線ドライバは、読出し対象の前記ユニットセルと前記ビット線との間に介在する前記セルトランジスタの個数に応じた個数の前記ダミートランジスタを前記ビット線に対して導通状態にすることを特徴とする半導体記憶装置。

#### 【請求項2】

データ読出し動作において、読出し対象の前記ユニットセルおよび前記ビット線の間に介在する前記セルトランジスタの容量と前記ビット線に対して導通状態となる前記ダミートランジスタの容量との和が一定値近傍で維持されるように、前記ダミーワード線ドライバは、前記ビット線に対して導通状態となる前記ダミートランジスタの個数を制御することを特徴とする請求項1に記載の半導体記憶装置。

## 【請求項3】

前記ダミートランジスタのサイズ(ゲート幅/ゲート長)は、前記セルトランジスタのサイズ(ゲート幅/ゲート長)とほぼ等しく、

データ読出し動作において、読出し対象の前記ユニットセルおよび前記ビット線の間に介在する前記セルトランジスタの個数と前記ビット線に対して導通状態となる前記ダミートランジスタの個数との和が一定値近傍に維持されるように、前記ダミーワード線ドライバは、前記ビット線に対して導通状態となる前記ダミートランジスタの個数を制御することを特徴とする請求項1または請求項2に記載の半導体記憶装置。

#### 【請求項4】

同一の前記ダミーブロック内にある複数の前記ダミーストリングは、前記複数のダミー ワード線を共有しており、

前記ダミーワード線ドライバが前記ダミーワード線のいずれかを選択することによって、該ダミーブロック内の複数のダミートランジスタが駆動されることを特徴とする請求項 1から請求項3のいずれかに記載の半導体記憶装置

## 【請求項5】

第1の電極と該第2の電極との間に設けられた強誘電体膜を含む複数の強誘電体キャパシタと、複数の前記強誘電体キャパシタのそれぞれに対応して設けられた複数のセルトランジスタとを含み、各前記強誘電体キャパシタおよび各前記セルトランジスタを並列に接続することによってユニットセルを成し、複数の該ユニットセルを直列に接続して構成されたセルブロックと、

前記複数のセルトランジスタのゲートに接続された複数のワード線と、

10

20

30

前記セルブロックの一端に接続された選択トランジスタと、

前記選択トランジスタを介して前記セルブロックの一端に接続されたビット線と、

前記セルブロックの他端に接続されたプレート線と、

複数のダミートランジスタを直列に接続することによってストリングを成し、複数の該 ダミーストリングで構成されたダミーブロックと、

前記複数のダミートランジスタのゲートに接続された複数のダミーワード線と、

前記ビット線に接続されたセンスアンプと、

前記ワード線に接続されたワード線ドライバと、

前記ダミーワード線に接続されたダミーワード線ドライバとを備え、

情報データおよびリファレンスデータをそれぞれ伝達する2本の前記ビット線の対が前記センスアンプに接続されており、

前記センスアンプは、前記リファレンスデータに基づいて前記情報データの論理値を検出し、

前記ダミーブロックは、前記2本のビット線対の間に接続され、

データ読出し動作において、前記ダミーワード線ドライバは、読出し対象の前記ユニットセルと前記ビット線との間に介在する前記セルトランジスタの個数に応じた個数の前記ダミートランジスタを前記ビット線に対して導通状態にすることを特徴とする半導体記憶装置。

【発明の詳細な説明】

## 【技術分野】

[0001]

本発明は、半導体記憶装置に係わり、例えば、強誘電体キャパシタの極性によって論理データを記憶する強誘電体メモリに関する。

#### 【背景技術】

[0002]

セルトランジスタ(T)のソースドレイン間にキャパシタ(C)の両端をそれぞれ接続し、これをユニットセルとし、このユニットセルを複数直列に接続した「TC並列ユニット直列接続型強誘電体メモリ」(Memory which consists of series connected memory cells each having a transistor having a source terminal and a drain terminal and a ferroelectric capacitor inbetween said two terminals, hereafter named "Series connected TC unit type ferroelectric RAM")が開発されている(非特許文献 1 参照)

[0003]

TC並列ユニット直列接続型強誘電体メモリ(以下、単に、強誘電体メモリともいう)において、センスアンプは、直列に接続された複数のユニットセルからなるセルブロックのうち或るユニットセルからデータを読み出す。このとき、読出し対象のユニットセルとビット線との間には、非選択ユニットセルが介在する場合がある。介在する非選択ユニットセルの個数は、読出し対象のユニットセルの位置によって異なる。データ読出し時に非選択ユニットの容量がビット線容量に付加するため、読出し対象のユニットセルの位置によって、ビット線容量が変動する。

[0004]

読出し対象のユニットセルの位置に応じてビット線容量が変動すると、データ読出し時における動作点が読出し対象のユニットセルの位置に応じて異なる。これは、センスマージンを低下させる原因となる。

【非特許文献 1】D.Takashima et al., "High-density chain Ferroelectric random memory (CFeRAM)" in proc.VLSI Symp. June 1997,pp.83-84

## 【発明の開示】

【発明が解決しようとする課題】

## [0005]

読出し対象のユニットセルの位置に応じたビット線容量の変動を抑制し、データを正確

20

10

30

に読み出すことができる半導体記憶装置を提供する。

【課題を解決するための手段】

#### [00006]

データ読出し動作において、前記ダミーワード線ドライバは、読出し対象の前記ユニットセルと前記ビット線との間に介在する前記セルトランジスタの個数に応じた個数の前記ダミートランジスタを前記ビット線に対して導通状態にすることを特徴とする。

#### [0007]

本発明に係る実施形態に従った半導体記憶装置は、第1の電極と該第2の電極との間に設けられた強誘電体膜を含む複数の強誘電体キャパシタと、複数の前記強誘電体キ電体やヤパシタとを含み、各前記強誘電体キャパシタおよび各前記セルトランジスタを並列に接続することによってユニットセルを直列に接続して構成されたセルブロックの一端に接近と、複数のがコニットセルを直列に接続して構成されたセルブロックの一端に接接に選択トランジスタと、前記セルブロックの一端にに接続されたピット線と、前記セルブロックの他端に接続されたプレート線と、前記セルブロックの他端に接続されたピット線と、前記セルブロックのがランジスタを直列に接続することによってストリングを成し、複数のダミーストリンで構成されたダミーブロックと、前記複数のダミートランジスタのゲートに接続されたセンスアンプと、前記ワード線に接続されたワード線ドライバと、前記ダミーワード線に接続されたダミーワード線ドライバとを備え、

情報データおよびリファレンスデータをそれぞれ伝達する2本の前記ビット線の対が前記センスアンプに接続されており、前記センスアンプは、前記リファレンスデータに基づいて前記情報データの論理値を検出し、前記ダミーブロックは、前記2本のビット線対の間に接続され、データ読出し動作において、前記ダミーワード線ドライバは、読出し対象の前記ユニットセルと前記ビット線との間に介在する前記セルトランジスタの個数に応じた個数の前記ダミートランジスタを前記ビット線に対して導通状態にすることを特徴とする。

#### 【発明の効果】

## [0008]

本発明による半導体記憶装置は、読出し対象のユニットセルの位置に応じたビット線容量の変動を抑制し、データを正確に読み出すことができる。

【発明を実施するための最良の形態】

#### [0009]

以下、図面を参照して本発明に係る実施形態を説明する。本実施形態は、本発明を限定するものではない。

## [0010]

10

20

30

(第1の実施形態)

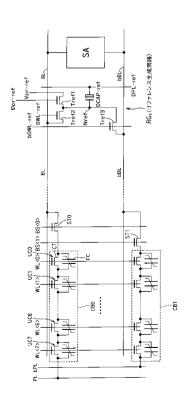

図1は、本発明に係る実施形態に従った強誘電体メモリの一例を示す構成図である。本実施形態による強誘電体メモリは、ロウ方向へ延伸する複数のワード線WLと、ロウ方向に対して直交するカラム方向へ延伸する複数のビット線BL、bBLと、ロウ方向へ延伸する複数のプレート線PL、bPLとを備える。尚、図1では、プレート線PL、bPLは、ワード線WLと区別するために破線で示されている。ビット線BLおよびbBLは対を成しており、互いに相補のデータを伝達する。プレート線PLおよびbPLもまた対を成しており、互いに相補の信号を伝達する。

[0011]

複数のユニットセルから成るセルブロック C B が 4 × 4 のマトリクス状に配置されている。セルブロック C B は、ビット線 B L とプレート線 P L との間、あるいは、ビット線 b B L とプレート線 b P L との間に接続されている。

[ 0 0 1 2 ]

ワード線駆動回路WLDがワード線WLに接続されている。ワード線駆動回路WLDは、ロウデコーダRDから受け取ったアドレスに従って、一部の(単数または複数の)ワード線WLを選択し、選択されたワード線WLに電圧を印加する。センスアンプS/Aがにット線BLおよびbBLに接続されている。センスアンプS/Aは、データ読出し時に、一部の(単数または複数の)ビット線BL、bBLに伝播するユニットセルからのデータを検出する。また、センスアンプS/Aは、データ書込み時に、一部の(単数または複数の)ビット線BL、bBLを選択し、選択されたビット線BL、bBLに電圧を印加する。これによって、センスまとができる。このように、ワード線WLとビット線BLとに電圧を印加することができる。このように、ワード線WLとビット線BLとに電圧を印加することができる。プレート線駆動回路PLDは、データの読出したのでで、プレート線PL、bPLに電圧を印加するように構成されている。

図1は、4×4のマトリクス状に配置されたセルブロックCBを示している。しかし、セルブロックの個数はこれに限定されない。これに伴い、ワード線WL、ビット線BL、bBLおよびプレート線PL、bPLの各本数も限定しない。

[0014]

[0013]

本実施形態による強誘電体メモリは、ビット線対BLとbBLとの間に接続されたダミーブロックDBと、ロウ方向に延伸する複数のダミーワード線DWLと、ダミーブロックデコーダDBDと、ダミーワード線DWLを駆動するダミーワード線ドライバDWLDと、をさらに備えている。ダミーワード線ドライバDWLDは、ダミーブロックデコーダDBDから受け取ったアドレスに従って、一部の(単数または複数の)ダミーワード線DWLを選択し、選択されたダミーワード線DWLに電圧を印加する。ダミーブロックDBは、読出し時において、読出し対象のユニットセルの位置に応じたビット線容量の変動を抑制するために設けられている。

[0015]

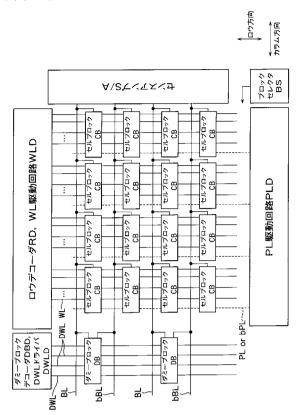

図 2 は、本実施形態によるセルブロック C B およびリファレンス生成回路 R G を示す回路図である。尚、図 1 においては、リファレンス生成回路 R G は、省略されている。

[0016]

セルブロック C B O 、 C B 1 は、第 1 の電極と該第 2 の電極との間に設けられた強誘電体膜を含む複数の強誘電体キャパシタ F C と、複数の強誘電体キャパシタ C F のそれぞれに対応して設けられた複数のセルトランジスタ C T とを含む。各々の強誘電体キャパシタ F C および対応する各々のセルトランジスタ C T は互いに並列に接続されており、それぞれユニットセル U C O ~ U C 7 を構成している。さらに、複数のユニットセル U C O ~ U C 7 を直列に接続することによってセルブロック C B O 、 C B 1 が構成されている。本実施形態では、各セルブロック C B O 、 C B 1 は、8個のユニットセル U C O ~ U C 7 を直列に接続することによって構成されている。しかし、セルブロックは、9個以上、あるい

10

20

30

40

20

30

40

50

は、7個以下のユニットセルで構成されていてもよい。図1に示す他のセルブロックCBの内部構成は、セルブロックCBOおよびCB1の内部構成と同様である。ユニットセルUCO~UC7は、それぞれバイナリデータあるいはマルチビットデータを強誘電体キャパシタに記憶するメモリセルである。

[0017]

セルブロックCB0の一端は、選択トランジスタST0を介してビット線BLに接続されている。セルブロックCB0の他端は、プレート線PLに接続されている。セルブロックCB1の一端は、選択トランジスタST1を介してビット線bBLに接続されている。セルブロックCB1の他端は、プレート線bPLに接続されている。

[0018]

ユニットセルUC0~UC7の各セルトランジスタのゲートは、それぞれワード線WL<0>~WL<7>に接続されている。選択トランジスタST0およびST1のゲートは、それぞれビット選択信号BS0およびBS1によって制御されている。セルブロック選択信号BS0およびBS1は、図1に示すブロックセレクタ回路BSCによって生成される。

[0019]

リファレンス生成回路RGは、リファレンスデータを生成するために設けられている。 リファレンス生成回路RGは、リファレンスデータが生成されるリファレンスノードNrefと、リファレンスノードNrefを昇圧するリファレンスキャパシタDCAP-refと、リファレンスノードNrefをプリチャージするプリチャージ電圧Vpr-refと、プリチャージ電圧Vpr-refとリファレンスノードNrefとの間に接続されたトランジスタTref2と、ビット線BLとリファレンスノードNrefとの間に接続されたトランジスタTref3とを備えている。

[0020]

リファレンスキャパシタDCAP-refの一端は、リファレンスノードNrefに接続され、その他端はリファレンスプレート線DPL-refに接続されている。

[0021]

トランジスタTref1は、信号Dpr-refによって制御され、読出し動作前にリファレンスノードNrefをプリチャージ電圧Vpr-refに充電するためにオン状態(導通状態)となっている。読出し動作中において、トランジスタTref1は、オフ状態(非導通状態)となる。

[0022]

トランジスタTref2は、信号DWL-refによって制御され、読出し動作においてビット線BLにリファレンスデータを転送する場合にオン状態となる。このとき、セルブロックCB1からビット線bBLに情報データが伝達される。トランジスタTref3は、信号bDWL-refによって制御され、読出し動作においてビット線bBLにリファレンスデータを転送する場合にオン状態となる。このとき、セルブロックCB0からビット線bBLに情報データが伝達される。即ち、センスアンプS/Aがビット線bBLに伝達される際には、リファレンスノードNrefがビット線BLに伝達される情報データを検出する際には、リファレンスノードNrefがビット線BLに伝達される情報データを検出する際には、リファレンスノードNrefがビット線bBLに接続され、リファレンスデータはビット線bBLに転送される。

[0023]

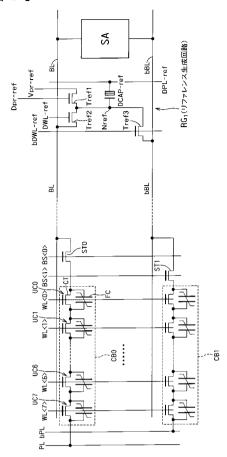

図 3 は、本実施形態によるダミーブロック D B およびダミーブロック選択トランジスタ S T d b 0 、 S T d b 1 を示す回路図である。尚、図 1 においては、ダミーブロック選択トランジスタ S T d b 0 、 S T d b 1 は省略されている。

[0024]

ダミーブロック D B は、複数のダミートランジスタ D T 0 0 、 D T 1 0 、 D T 2 0 、 D T 3 0 を直列に接続することによって構成されたダミーストリング D S 0 と、複数のダミ

20

30

40

50

(7)

ートランジスタDT01、DT11、DT21、DT31を直列に接続することによって構成されたダミーストリングDS0とを備えている。これらのダミーストリングDS0およびDS1の一端は、共通にノードNdbに接続されている。ダミーストリングDS0およびDS1の他端は、フローティング状態となっている。

[0025]

ダミートランジスタDT00、DT10、DT20、DT30のゲートは、それぞれダミーワード線 D W L < 0 > ~ D W L < 3 > に接続されている。ダミートランジスタDT01、DT11、DT21、DT31のゲートも、それぞれダミーワード線 D W L < 0 > ~ D W L < 3 > に接続されている。即ち、ダミーストリングDS0およびDS1に含まれるダミートランジスタDTi0およびDTi1の各ゲートは、共通にダミーワード線 D W L < i > に接続されている。ここで、iは、0、1、2、3のいずれかである。

[0026]

ダミートランジスタDT00~DT31の各サイズ(ゲート幅/ゲート長)は、それぞれセルトランジスタCTのサイズ(ゲート幅/ゲート長)とほぼ等しいことが好ましい。これにより、ダミートランジスタDT00~DT31のソースおよびドレインの寄生容量が、それぞれセルトランジスタCTのソースおよびドレインの寄生容量と等しくなる。ソースおよびドレインの寄生容量を等しくする理由は後述する。

[0027]

ダミーブロックDBの一端(ノードNdb)は、ダミーブロック選択トランジスタSTdb0を介してビット線BLに接続されており、ダミーブロック選択トランジスタSTdb1を介してビット線bBLに接続されている。ダミーブロック選択トランジスタSTdb0は、ノードNdbとビット線BLとの間に接続され、ダミーブロック選択トランジスタSTdの制御を受けてノードNdbをビット線BLに接続する。ダミーブロック選択トランジスタSTdb1は、ノードNdbとビット線bBLとの間に接続され、信号DBSの反転信号であるダミーブロック選択信号bDBSの制御を受けてノードNdbをビット線bBLに接続する。ダミーブロック選択信号DBSおよびbDBSは、ビット選択信号BS0およびBS1と同様に、図1に示すブロックセレクタ回路BSCによって生成される。例えば、ブロックセレクタ回路BSCは、ビット選択信号BS0を活性化した場合、ダミーブロック選択信号DBSを活性化する。

[0028]

ここで、活性化とは素子または回路をオンまたは駆動させることを意味し、不活性とは素子または回路をオフまたは停止させることを意味する。従って、HIGH(高電位レベル)の信号が活性化信号である場合もあり、LOW(低電位レベル)の信号が活性化信号である場合もあることに注意されたい。例えば、NMOSトランジスタは、ゲートをHIGHにすることによって活性化する。一方、PMOSトランジスタは、ゲートをLOWにすることによって活性化する。

[0029]

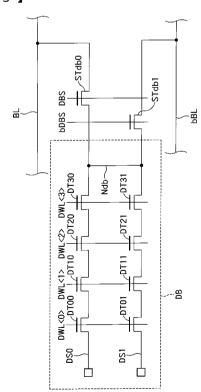

図4は、ダミーブロックデコーダDBDおよびダミーワード線ドライバDWLD(以下、単にダミーワード線ドライバDWLDという)の内部構成を示す回路図である。ダミーワード線ドライバDWLDは、ワード線WL<0>~WL<7>の駆動信号の論理値に基づいてダミーワード線DWL<0>~DWL<3>の駆動信号を生成するロジック回路である。尚、TC並列ユニット直列接続型強誘電体メモリでは、メモリセルMCを選択する際に、選択ワード線の電位のみが論理ロウに設定され、他の非選択ワード線の電位は論理ハイに設定される。

[0030]

NORゲートG0は、ワード線WL<0>およびWL<1>の駆動信号の反転信号を入力し、これらの反転信号をNOR演算する。NORゲートG0は、その結果をダミーワード線DWL<0>の駆動信号として出力する。NORゲートG1は、ワード線WL<2>およびWL<3>の駆動信号の反転信号を入力し、これらの反転信号をNOR演算する。

NORゲートG1は、その結果をダミーワード線 D W L < 1 > の駆動信号として出力する。NORゲートG2は、ワード線W L < 4 > およびW L < 5 > の駆動信号の反転信号を入力し、これらの反転信号をNOR演算する。NORゲートG2は、その結果をダミーワード線 D W L < 2 > の駆動信号として出力する。NORゲートG3は、ワード線W L < 6 > およびW L < 7 > の駆動信号の反転信号を入力し、これらの反転信号をNOR演算する。NORゲートG3は、その結果をダミーワード線 D W L < 3 > の駆動信号として出力する

## [0031]

これにより、論理ロウへ不活性化された選択ワード線WL<j>(j=0~7のいずれか)に対応するダミーワード線DWL<m>(m=0~3のいずれか)が論理ロウに不活性化される。このとき、他のダミーワード線DWL<n>(n=0~3、n m)は、論理ハイのままである。

[0032]

図5は、第1の実施形態による強誘電体メモリのデータ読出し動作の一例を示すタイミング図である。尚、ここでは、センスアンプS/Aは、ビット線BLを介してセルブロックCB0からの情報データを検出する動作を説明する。この場合、ビット線bBLにリファレンスデータが伝達される。センスアンプS/Aがビット線bBLを介して情報データを検出する動作は、以下の具体例から容易に推測可能であるので、その説明を省略する。

[0033]

読出し動作前の初期状態(~t1)では、全ワード線WL<0>~WL<7>が活性状態(ハイレベル)となっており、セルトランジスタCT0~CT7がオンしている。全ダミーワード線DWL<0>~DWL<3>が活性状態(ハイレベル)となっており、ダミートランジスタDT00~DT31がオンしている。ビット選択信号BS0、BS1、ダミービット選択信号DBS0、CBS1は、全て不活性状態(ロウレベル)である。よって、セルブロックCB0、CB1およびダミーブロックDBは、ビット線BL、bBLから切断されている。

[0034]

プレート線 P L 、 b P L は、所定の電位 V P L L に設定されている。これにより、セルブロック C B 0 、 C B 1 は、電位 V P L L にプリチャージされている。所定の電位 V P L L は V S S または V P L に等しい場合がある。この場合であっても、本実施形態の効果は失われない。

[0035]

信号DWL-refおよびbDWL-refは、不活性状態である。よって、リファレンス生成回路RGもビット線BL、bBLから切断されている。図5に示されていないが、信号Dpr-refは、活性状態(ハイレベル)であり、ノードNrefは、電位Vpr-refにプリチャージされている。

[0036]

プリチャージ状態において、ビット線BL、bBLは、センスアンプS/Aによってロウレベル電位VSSにプリチャージされている。また、ユニットセルUC0~UC7はそれぞれセルトランジスタCTの寄生容量にプレート電圧VPLLによるプリチャージ電荷を蓄積している。セルトランジスタCTのプリチャージ電荷もビット線の容量の変化に影響を与える。

[0037]

[0038]

10

20

30

40

20

30

40

50

これと同時に、図1に示すダミーワード線ドライバDWLDがダミーワード線DWL<m>(m=0~3のいずれか)を選択し、この選択されたダミーワード線DWL<m>を不活性状態にする。選択ダミーワード線DWL<m>は、選択ワード線WL<j>に基づいて選択される。その他のダミーワード線DWL<n>(n=0~3、n m)は、活性状態を維持する。これにより、選択ダミーワード線DWL<m>に接続されたダミートランジスタDTm0、DTm1はオン状態のままである。

## [0039]

t2において、ビット選択信号BSOが活性化され、ビット選択信号BSOは不活性状態のままである。これにより、セルブロックCBOが選択トランジスタSTを介してビット線BLに接続される。セルブロックCBOは、ビット線bBLから分離された状態を維持する。

[0040]

これと同時に、信号 b D W L - r e f が活性化される。これにより、図 2 に示すトランジスタT r e f 3 がオンし、リファレンスノードN r e f がトランジスタT r e f 3 を介してビット線 b B L に接続される。信号 D W L - r e f は不活性状態のままであるので、ビット線 B L は、リファレンスノードN r e f から分離されている。

[0041]

さらにこの時、信号DBSが活性化される。これにより、図3に示すダミーブロック選択トランジスタSTdb0がオンし、ダミーブロックDBがダミーブロック選択トランジスタSTdb0を介してビット線BLに接続される。信号bDBSは不活性状態であるので、ダミーブロックDBは、ビット線bBLには接続されない。

[0042]

t2の直後のt3において、プレート線PLがVAAに活性化される。これにより、セルブロックCBO内のユニットセルUCjに含まれる強誘電体キャパシタFCの極性状態(データ"0"またはデータ"1")に基づいてビット線BLの電位が変化する。これと同時に、図2に示す信号DPL-refを立ち上げる。信号DPL-refの信号線とノードNrefとは、リファレンスキャパシタDCAP-refによって容量カップリングされているので、信号DPL-refの電位を立ち上げることによって、ノードNrefの電位が昇圧される。ノードNrefにおいて昇圧された電位がリファレンスデータとしてビット線bBLに伝達される。

[0043]

センスアンプS/Aは、図5に示すように、ビット線bBLに伝達されるリファレンスデータVrefとビット線BLに伝達される情報データV1またはV0との電位差を検出し、増幅する。

[0044]

ダミーブロックDBの役割をより詳細に説明する。例えば、通常、ユニットセルUCOの情報データを読み出す場合(j=0)、ユニットセルUCOをビット線BLとのの間に介証。即ち、ユニットセルUCOをビット線BLとのの間である。ユニットセルUCOをでするセルトランジスタの個数は、ゼロのである。ユニットセルUCOをでするセルトランジスタの個数は、ロークをでである。同様にして、ユニットセルUCOの情報データを読み出す場合(j=2)、ユニットセルUC対の情報データを読み出す場合である。ローットセルUC対の情報データを読み出す場合である。ローットセルUC対の情報データを読み出す場合である。位にはである。である。である。である。である。では、1つのセルトランジスタのソースおよびドレインの寄生容

20

30

40

50

。これは、読出し対象となるユニットセルの位置によって、ビット線容量が変動すること を意味する。

## [0045]

#### [0046]

例えば、ユニットセルUC2またはUC3の情報データを伝達する場合(j=2or3)、ダミーワード線ドライバDWLDは、ダミーワード線DWL<1>を不活性状態に維持し、ダミーワード線DWL<1>を不活性状態にする。これにより、DT20~DT31の計4個のダミートランジスタが情報データを伝達するビット線BLに接続される。つまり、ユニットセルUC2の情報データを読み出す場合(j=2)、ビット線に接続されるセルトランジスタの個数が2であり、ビット線に接続されるセルトランジスタの個数が3であり、ビット線に接続されるセルトランジスタの総容量は6×Ctである。ユニットセルUC3の情報データを読み出す場合(j=3)、ビット線に接続されるセルトランジスタの個数が3であり、ビット線に接続されるダミートランジスタの個数が4である。よって、ビット線容量に付加されるセルトランジスタおよびダミートランジスタの総容量は7×Ctである。

## [0047]

例えば、ユニットセルUC4またはUC5の情報データを伝達する場合(j=4or5)、ダミーワード線ドライバDWLDは、ダミーワード線DWL<2>を不活性状態のまま維持し、ダミーワード線DWL<2>を不活性状態にする。これにより、DT30およびDT31の計2個のダミートランジスタが情報データを伝達するビット線BLに接続される。つまり、本実施形態では、ユニットセルUC4の情報データを読み出す場合(j=4)、ビット線に接続されるセルトランジスタの個数が2である。よって、ビット線容量に付加されるセルトランジスタおよびダミートランジスタの総容量は6×Ctである。ユニットセルUC5の情報データを読み出す場合(j=5)、ビット線に接続されるダミートランジスタの個数が5であり、ビット線に接続されるダミートランジスタの個数が5であり、ビット線に接続されるダミートランジスタの総容量は7×Ctである。

#### [0048]

例えば、ユニットセルUC6またはUC7の情報データを伝達する場合(j = 6 o r 7)、ダミーワード線ドライバDWLDは、ダミーワード線DWL<0>~DWL<2>を活性状態のまま維持し、ダミーワード線DWL<3>を不活性状態にする。これにより、ダミートランジスタは情報データを伝達するビット線BLに接続されない。つまり、本実施形態では、ユニットセルUC6の情報データを読み出す場合(j = 6)、ビット線に接

続されるセルトランジスタの個数が6であり、ビット線に接続されるダミートランジスタの個数が0である。よって、ビット線容量に付加されるセルトランジスタおよびダミートランジスタの総容量は6×Ctである。ユニットセルUC7の情報データを読み出す場合(j=7)、ビット線に接続されるセルトランジスタの個数が7であり、ビット線に接続されるダミートランジスタの個数が0である。よって、ビット線容量に付加されるセルトランジスタおよびダミートランジスタの総容量は7×Ctである。

[0049]

このように、本実施形態では、情報データを伝達するビット線BLに付加されるトランジスタ容量は、6×Ctまたは7×Ctのいずれかであり、ほぼ一定値に近い状態に維持することができる。即ち、本実施形態では、読出し対象のユニットセルUCjとビット線BLとの間に介在するセルトランジスタの容量と、ビット線BLに対して導通状態となるダミートランジスタの容量との和が一定値の近傍に維持されるように、ダミーワード線ドライバDWLDは、ビット線BLに接続されるダミートランジスタの個数を制御する。

[0050]

本実施形態では、ダミートランジスタDT00~DT31のそれぞれのサイズがセルトランジスタCTのサイズとほぼ等しい。従って、ダミーワード線ドライバDWLDは、読出し対象のユニットセルUCjとビット線BLとの間に介在するセルトランジスタCTの個数とビット線BLに対して導通状態となるダミートランジスタの個数との和が一定値近傍に維持されるように、ビット線BLに接続されるダミートランジスタの個数を制御すればよい。

[0051]

このように制御することによって、ビット線BLの容量が、読出し対象のユニットセルUCjの位置に関わらず、一定値の近傍に維持され得る。その結果、一定の論理値を伝達するビット線BLのばらつきが小さくなり、センスアンプS/Aが情報データを誤検出することが抑制されるので、データを正確に検出することができる。

[0052]

図3に示すように、ダミーブロックDBは、並列に接続された複数のダミーストリングDS0、DS1を有し、ダミーストリングDS0、DS1は、ダミーワード線DWL<0>~DWL<3>を共有している。よって、ダミーワード線ドライバDWLDがダミーワード線DWL<0>~DWL<3>のいずれかを選択することによって複数のダミートランジスタが駆動される。例えば、ダミーワード線DWL<0>が選択された場合、ダミートランジスタDT00およびDT01が駆動される。ダミーワード線DWL<m>(m=0~3)が選択された場合、ダミートランジスタDTm0およびDTm1が駆動される。ダミーワード線DWL<m>の選択によって複数のダミートランジスタが駆動されるので、ダミートランジスタのプロセスばらつきが緩和される。

[0053]

例えば、もし、1つのダミーブロックDBにおいて全ダミートランジスタが直列に接続されていた場合、1本のダミーワード線の選択によって単一のダミートランジスタが駆動される。この場合、ダミートランジスタの寄生容量がプロセスばらつきによってセルトランジスタの寄生容量から大きくずれていると、読出し時におけるビット線容量を補正することができない。よって、ビット線に伝達される情報データの電圧がばらついてしまい、センスアンプS/Aがデータを誤検出する虞がある。

[0054]

これに対し、本実施形態のようにダミーワード線DWL<m>の選択によって複数のダミートランジスタが駆動される場合、その一方のダミートランジスタの特性(サイズ、電流駆動能力等)がばらついても、他方のダミートランジスタの特性がばらついていなければ、読出し時におけるビット線容量のばらつきが緩和される。よって、ビット線に伝達される情報データの電圧が安定し、センスアンプS/Aがデータを誤検出する危険性が少なくなる。

[0055]

10

20

30

40

20

30

40

50

[0056]

さらに、ダミーストリング D S を 2 つに分割して並列に接続することによって、ダミーブロック D B を小さくすることができる。

[0057]

本実施形態におけるダミーブロックDBに含まれるダミーストリングの本数は2本である。しかし、ダミーブロックDBに含まれるダミーストリングの本数上であるよい。この場合、読出し時にビット線BLに接続されるダミートランジスタDTの個数は、0,3,6の3段階のいずれかとしてよい。例えば、読出し対象のユニットセルがスを見して2~ロの11がれるがミートランジスタDTの個数は6とする。読出し対象のユニットセルがUC2~ロTの個数は3個にビットは別日に接続されるダミートランジスタDTの個数は0個とする。この場合、ビットは別日に接続されるダミートランジスタDTの個数は0個とする。この場合、ビット線別に付加されるセルトランジスタDTの個数は0個とする。この場合、ビット線別である。このようにダミーブロックDBを駆動すれば、情報データを伝達するビット線別のことができる。が比較的安定する。また、この場合、ダミーワード線トライバDWLDの回路規模を小さくすることができる。

[0058]

代替的に、ダミーブロックDBに含まれるダミーストリングの本数を増大させた場合に、各ダミートランジスタのサイズ(ゲート幅/ゲート長)を小さくしてもよい。例えば、ダミーブロックDBに含まれるダミーストリングの本数が4本である場合に、各ダミートランジスタのゲート幅をセルトランジスタCTのゲート幅の1/2とする。これにより、並列に接続された4本のダミーストリングDSを含むダミーブロックDBは、実質的に図3に示すダミーブロックDBと同じ機能を有する。この場合、さらに、1本のダミーワード線DWLに接続されたダミートランジスタDTが4個であるので、プロセスばらつきが生じたとしても、ビット線容量をより安定に維持することができる。

[0059]

(第1の実施形態の変形例)

本実施形態は、情報データを伝達するビット線BLの容量を補正する。しかし、リファレンスデータを伝達するビット線bBLの容量を補正してもよい。この場合、図3に示す信号bDBSを活性化することによって、ダミーブロックDBをビット線bBLに接続する。ダミー部DBにおいて活性化されるダミートランジスタDTの個数は、読出し対象のユニットセルUCiとビット線BLとの間に介在するセルトランジスタCTの個数に一致させる、あるいは、接近させる。例えば、読出し対象のユニットセルがUCOである場合、ダミーワード線DWL<0>~DWL<3>は不活性状態を維持する。このとき、ビット線BLに付加されるセルトランジスタCTの個数はゼロであり、ビット線bBLに付加

20

30

40

50

されるダミートランジスタDTの個数もゼロである。読出し対象のユニットセルがUC1またはUC2である場合、ダミーワード線DWL<0>のみが活性化される。この、ビット線BLに付加されるセルトランジスタDTの個数は2個である。読出し対象のユニットをルがUC3またはUC4である場合、ダミーワード線DWL<0>およびDWL<1>が活性化される。このとき、ビット線BLに付加されるセルトランジスタDTの個数は3個である。でのとき、ビット線BLに付加されるゼルトランジスタDTの個数は3個である。読出し対象のユニットセルがUC5またはJC6である場BLに付加されるダミーワーれるダミーの切数は3個である。読出し対象のユニットセルがJC5である場BLに付加されるダミーワード線DWL<0>~DWL<2>が活性化される。このとでット線BLに付加るダミーリーがリンジスタDTの個数は5個である。読出し対象のユニットを関BLに付加されるゼットランジスタDTの個数は8個であり、ビットに対して7またはとでット線BLに付加されるセルトランジスタDTの個数は8個であり、ビット線トBLに付加されるダミートランジスタDTの個数は8個である。尚、ダミーワード線トランジスタDTの個数は8個である。一切、ビット線トロのロジック構成は、上記動作を実現するように適宜変更すればよい。

[0060]

このように、ダミー部DBにおいて活性化されるダミートランジスタDTの個数は、読出し対象のユニットセルUCiとビット線BLとの間に介在するセルトランジスタCTの個数に一致し、あるいは、これに近い。これにより、情報データを伝達するビット線BLの容量とがほぼ一致、あるいは、接近する。つまり、読出し対象のユニットセルの位置に関わらず、ビット線容量がほぼ一定に維持され得る。従って、本実施形態は、データ読出し時における動作点が安定するので、センスアンプS/Aによる情報データの誤検出を抑制することができる。

[0061]

(第2の実施形態)

図6は、第2の実施形態によるダミーブロックDBを示す回路図である。第2の実施形態の他の構成は、第1の実施形態と同様でよい。第2の実施形態によるダミーブロックDBは、第1の実施形態のそれと同様に、ダミートランジスタDT00、DT20、DT30からなるダミーストリングDS0と、ダミートランジスタDT01、DT11、DT21、DT21、DT31からなるダミーストリングDS1とを含む。

[0062]

第2の実施形態によるダミーブロックDBは、ビット線BLとbBLとの間に接続されている。より詳細には、ダミーブロックDBの一端のノードNdb0はビット線BLに接続され、他端のノードNdb1はビット線bBLに接続されている。第2の実施形態によるダミーブロックDBの構成は、第1の実施形態によるダミーブロックDBの構成と同様でよい。ダミーワード線DWL<0>~DWL<3>とダミートランジスタDT00~DT31との接続関係も、第1の実施形態のそれと同様でよい。

[0063]

第2の実施形態では、ダミーブロック選択トランジスタが設けられていない。このため、ダミーブロックDBをビット線BLに接続する場合(ビット線BLが情報データを伝達する場合)には、ダミーワード線DWL<0>を不活性化し、ダミーブロックDBをビット線bBLから分離する。

[0064]

図7は、第2の実施形態に従ったダミーワード線ドライバDWLDの内部構成を示す回路図である。信号SBLは、ビット線選択信号である。ビット線BLが選択されビット線bBLが非選択である場合、信号SBLは論理ロウであり、ビット線bBLが選択されビット線BLが非選択である場合、信号SBLは論理ハイであるとする。図7に示す回路構成により、ダミーワード線ドライバDWLDは、次のように動作する。

[0065]

選択ワード線がBLである場合、非選択ビット線bBL側にあるダミーワード線DWL

20

30

40

50

< 0 > は、常時、不活性状態である。選択ワード線が b B L である場合、非選択ビット線 B L 側にあるダミーワード線 D W L < 3 > が、常時、不活性状態である。

#### [0066]

[選択ワード線がBLである場合(DWL0=LOW)]

ワード線WL < 0 > またはWL < 1 > が選択的に論理口ウにされた場合、ダミーワード線ドライバDWL Dは、ダミーワード線DWL < 1 > ~ DWL < 3 > を総て活性状態にする。これにより、 6 個のダミートランジスタDT 1 0 ~ DT 3 1 がビット線 BLに接続される。

### [0067]

ワード線WL < 2 > またはWL < 3 > が選択的に論理口ウにされた場合、ダミーワード線ドライバDWLDは、ダミーワード線DWL < 1を不活性状態にし、ダミーワード線DWL < 2 > およびDWL < 3 > を活性状態にする。これにより、 4 個のダミートランジスタDT 2 0 ~ DT 3 1 がビット線BLに接続される。

#### [0068]

ワード線WL < 4 > またはWL < 5 > が選択的に論理口ウにされた場合、ダミーワード線ドライバDWL Dは、ダミーワード線DWL < 2 > を不活性状態にし、ダミーワード線DWL < 1 > およびDWL < 3 > を活性状態にする。これにより、2個のダミートランジスタDT30およびDT31がビット線BLに接続される。

#### [0069]

ワード線WL < 6 > またはWL < 7 > が選択的に論理口ウにされた場合、ダミーワード線ドライバDWLDは、ダミーワード線DWL < 3 > を不活性状態にし、ダミーワード線DWL < 1 およびDWL < 2 > を活性状態にする。これにより、ダミートランジスタDT10 ~ DT31はいずれもビット線BLに接続されない。

#### [0070]

[選択ワード線が b B L である場合(DWL3 = L O W)]

ワード線WL < 0 > またはWL < 1 > が選択的に論理口ウにされた場合、ダミーワード線ドライバDWLDは、ダミーワード線DWL < 0 > ~ DWL < 2 > を総て活性状態にする。これにより、6個のダミートランジスタDT 00~DT 2 1 がビット線BLに接続される。

## [0071]

ワード線WL < 2 > またはWL < 3 > が選択的に論理口ウにされた場合、ダミーワード線ドライバDWLDは、ダミーワード線DWL2を不活性状態にし、ダミーワード線DWL0およびDWL1を活性状態にする。これにより、4個のダミートランジスタDT00~DT11がビット線BLに接続される。

### [0072]

ワード線WL < 4 > またはWL < 5 > が選択的に論理口ウにされた場合、ダミーワード線ドライバDWLDは、ダミーワード線DWL < 1 > を不活性状態にし、ダミーワード線DWL < 0 > およびDWL < 2 > を活性状態にする。これにより、2個のダミートランジスタDT 0 0 ~ DT 0 1 がビット線BLに接続される。

#### [0073]

ワード線WL < 6 > またはWL < 7 > が選択的に論理口ウにされた場合、ダミーワード線ドライバDWLDは、ダミーワード線DWL < 0 > を不活性状態にし、ダミーワード線DWL < 1 およびDWL < 2 > を活性状態にする。これにより、ダミートランジスタDT10 ~ DT31がいずれもビット線BLに接続されない。

#### [0074]

このような構成により、ダミーワード線ドライバDWLDは、読出し対象のユニットセルUCと選択ビット線BLとの間に介在するセルトランジスタの個数に応じた個数のダミートランジスタDTをビット線BLに対して導通状態にすることができる。

### [0075]

図5を再度参照して、第2の実施形態による強誘電体メモリのより詳細な読出し動作を

20

30

40

50

説明する。尚、ここでは、センスアンプS/Aは、ビット線BLを介してセルブロックCB0からの情報データを検出する動作を説明する。この場合、ビット線bBLにリファレンスデータが伝達される。センスアンプS/Aがビット線bBLを介して情報データを検出する動作は、以下の具体例から容易に推測可能であるので、その説明を省略する。

[0076]

第2の実施形態におけるプリチャージ状態は、第1の実施形態におけるプリチャージ状態と同様である。

[0077]

t 1 において、ダミーワード線ドライバDWLDがダミーワード線DWL<0>を不活性化する。これにより、ダミートランジスタDT00、01がオフになり、ダミーブロックDBがビット線bBLから切断される。ビット線BLから情報データを読み出す動作期間では、ダミーワード線DWL<0>は不活性状態を維持する。

[0078]

これと同時に、読出し対象のユニットセルUC j とビット線BLとの間に介在する前記セルトランジスタの容量とビット線BLに対して導通状態となるダミートランジスタDTの容量との和が一定値近傍で維持されるように、ダミーワード線ドライバDWLDは、ビット線BLに対して導通状態となるダミートランジスタの個数を制御する。

[0079]

例えば、ユニットセルUCOまたはUC1が読出し対象のユニットセルである場合、ダミーワード線ドライバDWLDは、ダミーワード線DWL<1>~ DWL<3>を活性化する。これにより、ビット線BLに付加されるダミートランジスタDTの容量は6×Ctとなる。このとき、ビット線容量に付加されるセルトランジスタおよびダミートランジスタの総容量は、6×Ctまたは7×Ctとなる。

[0080]

ユニットセル U C 2 または U C 3 が読出し対象のユニットセルである場合、ダミーワード線ドライバ D W L D は、ダミーワード線 D W L < 1 > を不活性状態のままとし、ダミーワード線 D W L < 2 > および D W L < 3 > を活性状態にする。これにより、ビット線 B L に付加されるダミートランジスタ D T の容量は 4 × C t となる。このとき、ビット線容量に付加されるセルトランジスタおよびダミートランジスタの総容量は、 6 × C t または 7 × C t となる。

[0081]

ユニットセル U C 4 または U C 5 が読出し対象のユニットセルである場合、ダミーワード線ドライバ D W L D は、ダミーワード線 D W L < 2 > を不活性状態とし、ダミーワード線 D W L D W L < 1 > および < 3 > を活性状態にする。これにより、ビット線 B L に付加されるダミートランジスタ D T の容量は 2 × C t となる。このとき、ビット線容量に付加されるセルトランジスタおよびダミートランジスタの総容量は、 6 × C t または 7 × C t となる。

[0082]

ユニットセル U C 6 または U C 7 が読出し対象のユニットセルである場合、ダミーワード線ドライバ D W L D は、全ダミーワード線 D W L < 3 > を不活性状態とし、ダミーワード線 D W L < 1 > および < 2 > を活性状態にする。にする。これにより、ビット線 B L に付加されるダミートランジスタ D T の容量は 0 となる。このとき、ビット線容量に付加されるセルトランジスタおよびダミートランジスタの総容量は、 6 × C t または 7 × C t となる。

[0083]

このように、読出し対象のユニットセルUCjとビット線BLとの間に介在するセルトランジスタCTの個数とビット線BLに対して導通状態となるダミートランジスタDTの個数との和が6または7に維持される。これにより、読出し時におけるビット線BLの容量が一定値近傍に維持される。従って、第2の実施形態は、第1の実施形態と同様の効果を得ることができる。

#### [0084]

第2の実施形態によるダミーブロックDBに含まれるダミーストリングの本数は、第1の実施形態と同様に、3本以上であってもよい。このとき、第1の実施形態と同様に、各ダミートランジスタのサイズ(ゲート幅 / ゲート長)を小さくしてもよい。さらに、第1の実施形態の変形例を第2の実施形態に適用することもできる。

【図面の簡単な説明】

[0085]

【図1】本発明に係る実施形態に従った強誘電体メモリの一例を示す構成図。

【図2】本実施形態によるセルブロックCBおよびリファレンス生成回路RGを示す回路図。

.

10

20

【図3】本実施形態によるダミーブロック D B およびダミーブロック選択トランジスタ S T d b 1 を示す回路図。

【図4】ダミーブロックデコーダDBDおよびダミーワード線ドライバDWLDの内部構成を示す回路図。

【 図 5 】第 1 の実施形態による強誘電体メモリのデータ読出し動作の一例を示すタイミン グ図。

【図6】第2の実施形態によるダミーブロックDBを示す回路図。

【図7】第2の実施形態に従ったダミーワード線ドライバDWLDの内部構成を示す回路図。

【符号の説明】

[0086]

B L … ビット線、W L … ワード線、C B … セルブロック、D B … ダミーブロック、S / A … センスアンプ、W L D … ワード線ドライバ、D W L D … ダミーワード線ドライバ、U C 0 ~ U C 7 … ユニットセル、F C … 強誘電体キャパシタ、C T … セルトランジスタ、S T 0、S T 1 … 選択トランジスタ、R G … リファレンス生成回路、D T 0 0 ~ D T 3 1 … ダミートランジスタ、D W L < 0 > ~ D W L < 3 > … ダミーワード線、D S 0、D S 1 … ダミーストリング

【図2】

【図3】

【図4】

# 【図5】

# 【図6】

# 【図7】

# フロントページの続き

(72)発明者 滝 澤 亮 介 東京都港区芝浦一丁目 1 番 1 号 株式会社東芝内

(72)発明者 白 武 慎一郎

東京都港区芝浦一丁目1番1号 株式会社東芝内